データ転送装置、演算装置、それを備えた装置およびデータ転送方法

【課題】 データ転送装置から記憶装置へのデータ転送のスループットを向上する。

【解決手段】 データ転送装置1は、複数の一時保存部2(21,・・・2n(nは2以上の整数))と、順序制御部3と、データ読み出し部4と、転送制御部5とを有する。各一時保存部2(21,・・・2n)は、転送先の格納位置を示すアドレス情報付きのデータが入力されるデータ入力部6を通ってデータ転送装置1に入力したデータを保存する。データ読み出し部4は、各一時保存部2から、並列に、データを読み出す。転送制御部5は、その読み出された各データを、当該データに添付されているアドレス情報に基づいた転送先に対応しているデータ出力部7に出力する。順序制御部3は、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2毎にデータの読み出し順を設定する。

【解決手段】 データ転送装置1は、複数の一時保存部2(21,・・・2n(nは2以上の整数))と、順序制御部3と、データ読み出し部4と、転送制御部5とを有する。各一時保存部2(21,・・・2n)は、転送先の格納位置を示すアドレス情報付きのデータが入力されるデータ入力部6を通ってデータ転送装置1に入力したデータを保存する。データ読み出し部4は、各一時保存部2から、並列に、データを読み出す。転送制御部5は、その読み出された各データを、当該データに添付されているアドレス情報に基づいた転送先に対応しているデータ出力部7に出力する。順序制御部3は、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2毎にデータの読み出し順を設定する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、データを格納する記憶部に向けてデータを転送するデータ転送装置、演算装置、それを備えた装置およびデータ転送方法に関する。

【背景技術】

【0002】

図17は、データ転送装置を備えた演算装置の一例を、概略的に示すブロック構成図である(例えば特許文献1参照)。この演算装置60は、演算部61と、データ転送装置62と、記憶装置63とを備えている。演算部61は、複数の演算処理を並列的に行うことが可能な機能(例えばベクトル演算機能)を備えている。記憶装置63は、データを保存する複数の記憶部641〜64r(rは、2以上の整数)を有している。

【0003】

データ転送装置62は、複数の入力パス651〜65p(pは、2以上の整数)によって、演算部61と接続している。また、データ転送装置62は、複数の出力パス661〜66q(qは、2以上の整数)によって、記憶装置63と接続している。データ転送装置62は、演算部61から受信したデータを、当該データに添付されている転送先のアドレス情報に基づいて、記憶装置63に転送する機能を備えている。

【0004】

ところで、演算部61は、並列処理が可能であることから、複数のデータを同時にデータ転送装置62に出力する場合がある。この場合に、それらデータの転送先の記憶部が互いに異なっている場合には、データ転送装置62は、それらデータを、それぞれ、互いに異なる出力パス661〜66qを通して記憶装置63に出力する。一方、演算部61からデータ転送装置62に同時に出力された複数のデータの転送先の記憶部が同じ場合には、データ転送装置62は、例えば、データの競合調停により、それらデータを一つずつ順次、同じ出力パスを通して記憶装置63に出力する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−342306号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のように、データ転送装置62が演算部61から複数のデータを同時に受け取っても、それらデータの転送先の記憶部が同じ場合には、データの競合調停に起因して、データは、データ転送装置62から記憶部63へ、一つずつ順次出力される。このために、データ転送装置62から記憶装置63へのデータ転送において、同時入力した複数のデータの転送先の記憶部が同じ場合には、転送速度が遅くなる、換言すれば、スループットが低下するという問題が生じる。

【0007】

本発明は上記課題を解決するためになされた。すなわち、本発明の主な目的は、データ転送装置から記憶装置へのデータ転送のスループットを向上できるデータ転送装置、演算装置、それを備えた装置およびデータ転送方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明のデータ転送装置は、

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部にそれぞれ対応し、かつ、当該データ入力部を通った前記データをそれぞれ保存する複数の一時保存部と、

一グループを構成する複数の前記データがそれぞれ前記各データ入力部を通って前記各一時保存部に分散保存された場合に、前記各一時保存部から、並列に、同じグループの前記データを読み出すデータ読み出し部と、

前記転送先に関連付けられている複数のデータ出力部に接続し、前記データ読み出し部により読み出された前記データを、当該データのアドレス情報に基づいた転送先に対応する前記データ出力部に向けて出力する転送制御部と、

前記データ読み出し部によって前記各一時保存部から並列に読み出される前記各データの転送先に対応する前記データ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定する順序制御部と、

を有している。

【0009】

本発明の演算装置は、

演算処理を行う演算部と、

複数の記憶部を有する記憶装置と、

前記演算部から出力されたデータを前記記憶装置に転送する上記本発明のデータ転送装置と

を有する。

【0010】

本発明における演算装置を装備した装置は、本発明の上記演算装置を有している。

【0011】

本発明のデータ転送方法は、

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部をそれぞれ通って、一グループを構成する複数の前記データが入力された場合に、それらデータを、前記各データ入力部にそれぞれ対応する一時保存部に分散保存し、

前記各一時保存部から並列に読み出される前記各データの転送先に対応するデータ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定し、

その設定された読み出し順に従って、前記各一時保存部から、並列に、同じグループの前記データを読み出して転送先に向けて出力する。

【発明の効果】

【0012】

本発明によれば、データ転送装置から記憶装置へのデータ転送のスループットを向上できる。

【図面の簡単な説明】

【0013】

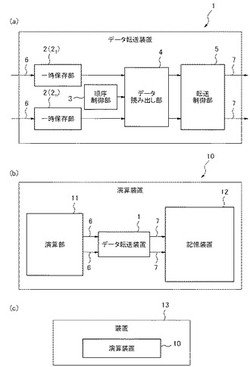

【図1】本発明に係る第1実施形態の構成を概略的に示すブロック図である。

【図2】本発明に係る第2実施形態のデータ転送装置および演算装置の構成を示すブロック図である。

【図3】本発明に係る第2実施形態において演算部から記憶装置に転送される要素の構成を模式的に示すイメージ図である。

【図4】本発明に係る第2実施形態のデータ転送装置を構成するアクセス制御部の構成を示すブロック図である。

【図5】一時保存部から読み出される要素の読み出し順の一例を示す図である。

【図6】要素に付与される読み出し順に関する情報の一例を示す図である。

【図7】本発明に係る第2実施形態における出力順保証部の構成を示すブロック図である。

【図8】出力順保証部を構成するレジスタの要素の保持(格納)・出力に関する説明に利用する図である。

【図9】出力順保証部を構成する判定部の動作状態の遷移を示す模式図である。

【図10】判定部の動作の一例の説明に利用する図である。

【図11】本発明に係る第2実施形態のデータ転送装置と比較する比較例としてのデータ転送装置の構成を示すブロック図である。

【図12】データ転送装置における要素の流れの一例を示すタイムチャートである。

【図13】さらに、データ転送装置における要素の別の流れの一例を示すタイムチャートである。

【図14】本発明に係る第3実施形態のデータ転送装置を構成する出力順保証部の構成を示すブロック図である。

【図15】本発明に係る第3実施形態のデータ転送装置における要素の流れの一例を示すタイムチャートである。

【図16】本発明に係る第3実施形態における出力順保証部の判定部の動作の一例の説明に利用する図である。

【図17】演算装置の一例を示すブロック図である。

【発明を実施するための形態】

【0014】

以下に、本発明に係る実施形態を図面を参照して説明する。

【0015】

(第1実施形態)

図1(a)は、本発明に係る第1実施形態のデータ転送装置の構成を概略的に示すブロック構成図である。図1(b)は、そのデータ転送装置を備えた第1実施形態の演算装置の構成を概略的に示すブロック構成図である。

【0016】

第1実施形態の演算装置10は、図1(b)に示されるように、演算処理を行う演算部11と、データを記憶する機能を備えた記憶装置12とを有すると共に、下記に示すデータ転送装置1を有している。

【0017】

第1実施形態のデータ転送装置1は、演算部11から受け取ったデータを記憶装置12に転送する装置である。当該データ転送装置1は、図1(a)に示されるように、複数の一時保存部2(21,・・・2n(nは2以上の整数))と、順序制御部3と、データ読み出し部4と、転送制御部(クロスバ部)5とを有している。

【0018】

すなわち、各一時保存部2(21,・・・2n)は、個別に対応するデータ入力部6と接続している。データ入力部6は、転送先の格納位置を示すアドレス情報付きのデータをデータ転送装置1に導入する経路である。各一時保存部2は、接続しているデータ入力部6を通ってデータ転送装置1に入力されたデータを保存する機能を有している。

【0019】

データ読み出し部4は、各一時保存部2から、並列(換言すれば、同時又はほぼ同時)に、データを読み出す機能を備えている。

【0020】

転送制御部5は、複数のデータ出力部7に接続している。それらデータ出力部7は、それぞれ、データの転送先に関連付けられている。転送制御部5は、データ読み出し部4により読み出された各データを、当該データに添付されているアドレス情報に基づいた転送先に対応しているデータ出力部7に出力する。

【0021】

順序制御部3は、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2毎にデータの読み出し順を設定する機能を有している。

【0022】

この第1実施形態のデータ転送装置1は、上記のように、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2からのデータの読み出し順を制御する構成を有している。このため、第1実施形態のデータ転送装置1および演算装置10は、次にような効果を得ることができる。すなわち、その効果とは、転送制御部5がデータ出力部7を通してデータを記憶装置12に転送する際に、転送制御部5におけるデータの競合調停を回避できるという効果である。この効果によって、第1実施形態のデータ転送装置1および演算装置10は、データの競合調停に起因した記憶装置へのデータの転送速度が遅くなる、換言すれば、スループットが悪化するという問題を防止できる。

【0023】

上記したような第1実施形態のデータ転送装置1およびそれを有する演算装置10は、図1(c)に示されるような演算装置を装備した装置13を構成することができる。この装置13は、第1実施形態のデータ転送装置1を有しているので、データ転送のスループットが向上し、これにより、演算処理速度のより高速化を図ることができる。

【0024】

(第2実施形態)

以下に、本発明に係る第2実施形態を説明する。

【0025】

図2は、第2実施形態のデータ転送装置を備えた演算装置の構成を簡略化して示したブロック図である。この第2実施形態の演算装置20は、演算部21と、データ転送装置22と、記憶装置23とを有している。なお、具体的には、CPU(Central Processing Unit)が、記憶装置(記憶装置23と同じ、あるいは別の記憶装置)に予め格納されたコンピュータプログラムに基づき動作することによって、演算部21およびデータ転送装置22が実現される。つまり、CPUが、演算部21およびデータ転送装置22として機能する。

【0026】

記憶装置23は、例えばハードディスク装置等の記憶媒体により構成される複数の記憶部25(この第2実施形態では、少なくとも4つの記憶部251〜254)を有している。なお、ここでは、それら記憶部251〜254は同型とする。

【0027】

演算部21は、ベクトル演算処理が可能な機能を有する。この演算部21は、ベクトル演算によるデータを含む次に示すような要素を複数個、同時又はほぼ同時(並列的)にデータ転送装置22に向けて出力する機能を有する。図3(a)は、その要素の構成をイメージで表した図である。つまり、演算部21から出力される要素とは、データに、当該データの格納(書き込み)を指令するコマンドと、要素番号と、当該データの格納位置(記憶位置)を示すアドレス情報とが添付されている情報のまとまりである。

【0028】

この第2実施形態では、説明を分かり易くするために、演算部21は、一グループを構成する16個の要素を4個ずつ並列出力することとし、かつ、それら16個の要素のアドレスは連続していることとする。より具体的に説明すると、それら16個の各要素には、e0〜e15の要素番号が付与されている。かつ、各要素のデータのデータ幅は、8バイトとする。かつ、記憶装置23における各要素の格納位置であるアドレスは、要素番号の小さいものから0番地、8番地、・・・というように、8バイトずつ変位する連続アドレスであるとする。さらに、それらアドレスの0〜31番地は、記憶部251に対応し、アドレスの32〜63番地は、記憶部252に対応し、アドレスの64〜95番地は、記憶部253に対応し、アドレスの96〜127番地は、記憶部254に対応しているものとする。

【0029】

この第2実施形態では、演算部21は、要素番号e0〜e3を並列(同時又はほぼ同時)に別々の演算パス26a〜26dに出力する。そして、次の出力タイミング(次のクロック)では、演算部21は、要素番号e4〜e7を別々の演算パス26a〜26dに並列出力する。このように、演算部21は、一グループの要素番号の小さいものから順に4個ずつ別々の演算パス26a〜26dに並列出力する。換言すれば、この第2実施形態では、演算部21は、記憶部251行きの4つの要素(要素番号e0〜e3)をそれぞれ並列に出力するというように、行き先の記憶部25が同じ4つの要素を並列に各演算パス26に出力する。なお、この第2実施形態では、要素e0は演算パス26aに、要素e1は演算パス26bに、要素e3は演算パス26cに、要素e4は演算パス26dに、それぞれ、出力されるというように、並列出力される4つの要素は、その要素番号の小さいものから順に演算パス26a〜26dに対応して出力される。

【0030】

また、演算部21は、上記のような要素を出力すると共に、その要素の処理に関わる制御情報(例えば、転送タイミングを知らせる情報や、グループに関する情報など)を、データ転送装置22に向けて出力する機能を有している。

【0031】

データ転送装置22は、複数の演算パス26(ここでは、4本の演算パス26a〜26d)、および、制御パス27によって、演算部21に接続している。演算パス26は、上記したような要素(データ)をデータ転送装置22に導入する経路(データ入力部)である。制御パス27は、上記したような要素の制御情報が通る情報の経路である。

【0032】

データ転送装置22は、演算部21から受け取ったデータ(要素)を記憶装置23に転送する機能を備えている。つまり、当該データ転送装置22は、転送管理部28と、順序制御部29と、複数のアクセス制御部30と、転送制御部である競合調停部(クロスバ部)31と、複数の出力順保証部32とを有している。

【0033】

転送管理部28は、演算部21から出力される制御情報に基づいて、データ転送装置22の要素(データ)の転送の開始と終了を管理する機能を備えている。

【0034】

アクセス制御部30は、演算パス26a〜26dに対応して設けられている。つまり、この第2実施形態のデータ転送装置22は、演算パス26a〜26dにそれぞれ一対一に対応して接続するアクセス制御部30a〜30dを有している。また、各アクセス制御部30a〜30dは、順序制御部29に接続している。

【0035】

各アクセス制御部30a〜30dは、図4に示されるように、範囲情報添付部34と、一時保存部35と、出力制御部36とを有している。

【0036】

一時保存部35は、演算パス26を通ってデータ転送装置22に入力してきた要素(データ)を保存する機能を有する。この第2実施形態では、図5に示されるように、アクセス制御部30aの一時保存部35は、演算パス26aを通った要素e0,e4,e8,e12を保存する。アクセス制御部30bの一時保存部35は、演算パス26bを通った要素e1,e5,e9,e13を保存する。アクセス制御部30cの一時保存部35は、演算パス26cを通った要素e2,e6,e10,e14を保存する。アクセス制御部30dの一時保存部35は、演算パス26dを通った要素e3,e7,e11,e15を保存する。

【0037】

出力制御部36は、制御パス33によって後述する順序制御部29から加えられる読み出し順の情報に従って、一時保存部35に保存されている要素を順次読み出す機能を備えている。この第2実施形態では、アクセス制御部30a〜30dの各出力制御部36は、順序制御部29からの指示によって、読み出しタイミングを合わせて要素を読み出す。すなわち、この第2実施形態では、アクセス制御部30a〜30dの出力制御部36は、各一時保存部35から、データ(要素)を並列に読み出すデータ読み出し部としての機能を有する。

【0038】

さらに、出力制御部36は、上記のように読み出した要素(データ)を競合調停部31に向けて出力する機能を有している。

【0039】

範囲情報添付部34は、上記のように出力制御部36によって一時保存部35から読み出された要素の同じグループ内における読み出し順に関する情報を、各データに添付する機能を備えている。第2実施形態では、範囲情報添付部34は、図3(b)に示されるように、各データに、読み出し順が最初か否かを示すデータSと、読み出し順が最後か否かを示すデータEとを添付する。具体的には、範囲情報添付部34は、一時保存部35に保存される同じグループの4個の要素のうち、最初に読み出された要素には、図6に示されるように、データSとして「1」を、また、データEには「0」を添付する。また、範囲情報添付部34は、最後に読み出された要素には、データSとして「0」を、また、データEには「1」を添付する。さらに、範囲情報添付部34は、それ以外の読み出し順(中間)の要素には、データS,Eとして、それぞれ「0」を添付する。なお、一グループを構成する要素の数が少なくて一時保存部35に保存される同じグループの要素が1個のみである場合がある。この場合には、範囲情報添付部34は、その要素には、データS,Eとして、それぞれ「1」を添付する。さらにまた、要素が無効である場合がある。この場合には、範囲情報添付部34は、要素に、データS,Eとして、それぞれ「0」を添付する。

【0040】

順序制御部29は、転送管理部28から動作開始指令を受信した場合に、出力制御部36および範囲情報添付部34に向けて動作開始指令を出力すると共に、出力制御部36には次に示すような読み出し順の情報をも送信する機能を備えている。つまり、順序制御部29は、出力制御部36による要素の読み出し順を設定する機能を有している。

【0041】

その読み出し順は、次のように設定されている。つまり、後述する競合調停部31は、データ出力部として機能する複数の転送パス38(38a〜38d)に接続している。その転送パス38aは記憶装置23の記憶部251に、また、転送パス38bは記憶部252に、さらに、転送パス38cは記憶部253に、さらにまた、転送パス38dは記憶部254に、それぞれ、対応している。この第2実施形態では、各アクセス制御部30a〜30dの出力制御部36による各一時保存部35からの読み出し順は、並列に読み出される各要素の転送先に関連付けられている転送パス38が互いに異なるように設定されている。具体的には、第2実施形態では、図6に示されるように、アクセス制御部30aでは、一時保存部35における同じグループの要素e0,e4,e8,e12は、格納順に、つまり、要素番号e0→e4→e8→e12の順に、読み出されるように、その読み出し順が設定される。また、アクセス制御部30bでは、一時保存部35における同じグループの要素e1,e5,e9,e13は、4番目に格納した要素から、つまり、要素番号e13→e1→e5→e9の順に、読み出されるように、その読み出し順が設定される。アクセス制御部30cでは、一時保存部35における同じグループの要素e2,e6,e10,e14は、3番目に格納した要素から、つまり、要素番号e10→e14→e2→e6の順に、読み出されるように、その読み出し順が設定される。アクセス制御部30dでは、一時保存部35における同じグループの要素e3,e7,e11,e15は、2番目に格納した要素から、つまり、要素番号e7→e11→e15→e3の順に、読み出されるように、その読み出し順が設定される。このように、読み出し順が設定されることによって、読み出し順が同じ4個の要素の各転送先が対応している転送パス38は、互いに異なることになる。

【0042】

競合調停部31は、上記のように、記憶装置23の各記憶部251〜254と一対一の関係を持つ4本の転送パス38(38a〜38d)に接続している。なお、この第2実施形態では、転送パス38の数は、演算パス26の数と同じであったが、当該転送パス38の数は、演算パス26の数と同じでなくともよい。

【0043】

競合調停部31は、アクセス制御部30a〜30dから並列出力された複数(4個)の要素を受け取ると、それら各要素を、それぞれ、アドレス情報に基づいた転送先に対応している転送パス38に向けて出力(転送)する機能を有している。この第2実施形態では、上記のように、競合調停部31がアクセス制御部30a〜30dから並列に受け取る4個の要素は、対応する転送パス38が互いに異なる転送先を持つ要素である。この場合、競合調停部31は、それら受け取った4個の要素を、並列(同時又はほぼ同時)に、対応する転送パス38に向けて出力する。

【0044】

なお、競合調停部31は、受け取った複数の要素のうち、少なくとも2個の要素の出力先となる転送パス38が同じ場合には、競合調停により、それら要素を順次1個ずつ転送パス38に出力する機能をも備えている。このように、第2実施形態では、競合調停部31は、競合調停の機能を有しているが、前述したように、対応する転送パス38が互いに異なる転送先を持つ要素が並列に入力するので、その競合調停を行わなくて済む。

【0045】

出力順保証部32(32a〜32d)は、転送パス38a〜38dにそれぞれ介設されている。これら出力順保証部32は、競合調停部31から各転送パス38a〜38dに順次出力された要素の順番を、予め定めた条件に従って並べ換えて、記憶装置23に送出する機能を備えている。

【0046】

図7は、第2実施形態における出力順保証部32(32a〜32d)の構成を示すブロック図である。つまり、この第2実施形態では、出力順保証部32は、第1レジスタ40と、第2レジスタ41と、判定部42と、比較部43,44とを有している。第1レジスタ40および第2レジスタ41は、競合調停部31から出力された要素を保持する機能を備えている。ここでは、転送パス38から出力保証部32に入力した要素は、まず、第1レジスタ40に保持され、ここで保持された要素が、後述する判定部42の動作によって、第2レジスタ41に転送されて保持される。換言すれば、第2レジスタ41は、先行する要素を保持する先行レジスタであり、第1レジスタ40は、その先行する要素に続く後続の要素を保持する後続レジスタである。

【0047】

比較部43は、第1レジスタ40に保持されている要素の要素番号と、第2レジスタ41に保持されている要素の要素番号とを比較し、この比較の結果による第1レジスタ40の要素番号と、第2レジスタ41の要素番号との大小関係に応じた信号を出力する。

【0048】

比較部44は、第1レジスタ40に保持されている要素のアドレスと、第2レジスタ41に保持されている要素のアドレスとを比較する。そして、比較部44は、第1レジスタ40のアドレスと、第2レジスタ41のアドレスとが一致しているか不一致であるかに応じた信号を出力する。

【0049】

判定部42は、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせと、比較部43,44からの出力信号(比較結果)とに基づいて、次のような要素の順序保証(出力順保証)に関わる動作を実行する機能を有している。

【0050】

図8は、第1レジスタ40と、第2レジスタ41とにそれぞれ保持されている要素のデータS,Eの組み合わせと、第2レジスタ41の次の状態との関係を表にまとめて示している。なお、図8において、データSとデータEの両方が「0」である場合は、一グループの要素の読み出し順が中間であることを示すだけでなく、第1レジスタ40や第2レジスタ41に要素が保持されていない場合もある。例えば、項番1’は、第1レジスタ40にも第2レジスタ41にも要素が格納されていない状態である。

【0051】

図9は、要素番号とアドレスの比較(監視)に関わる判定部42の動作状態の遷移を模式的に表した図である。この図9中における矢印に付されている各符号は、それぞれ、図8中の項番に対応している。

【0052】

図10は、比較部43,44の比較結果と、判定部42の順序保証動作との関係を表により示している。

【0053】

判定部42は、図8〜図10に示すような動作規定に従って要素の順序保証の動作を行う。この第2実施形態では、一グループの16個の要素e0〜e15は、全て、互いに格納位置を示すアドレスが異なっている。このため、判定部42は、図10の動作規定に従って、順序保証動作を行わない。つまり、判定部42は、競合調停部31から受け取った要素を、まず、第1レジスタ40に格納する。そして、判定部42は、例えば次のクロックで、その第1レジスタ40の要素を第2レジスタ41に転送すると共に、競合調停部31から次に受け取った要素を、第1レジスタ40に格納する。さらに、判定部42は、その次のクロックで、第2レジスタ41の要素を転送パス38を通して記憶装置23に出力し、かつ、上記同様に、第1レジスタ40の要素を第2レジスタ41に転送し、さらに、競合調停部31から次に受け取った要素を、第1レジスタ40に格納する。つまり、この第2実施形態では、一グループの要素は転送先のアドレスが連続しており、当該要素の転送は、連続アドレスのメモリアクセス命令に基づく転送である。このような場合には、競合調停部31から各転送パス38に上記の如く出力される要素の順序保証は不要である。このため、各出力順保証部32(32a〜32d)の判定部42は、順序保証を行うことなく、第2レジスタ41の要素を転送パス38を通して記憶装置23に向けて出力する。

【0054】

記憶装置23は、上記のように、データ転送装置22(出力順保証部32)から出力された要素のデータを、アドレス情報に示される格納位置に格納する。

【0055】

この第2実施形態では、上記のような構成を有しているから、競合調停部31において、要素(データ)の競合調停を行わなくて済む。このため、この第2実施形態におけるデータ転送装置22および演算装置20は、要素(データ)の競合調停に起因した要素(データ)の転送速度の低下(スループットの悪化)を防止できる。この効果を以下に具体的に説明する。

【0056】

ここで、比較例としての図11に示すデータ転送装置の構成を簡単に説明する。なお、図11のデータ転送装置の説明において、第2実施形態のデータ転送装置22と同様な構成部分には同一符号を付し、その共通部分の重複説明は省略する。

【0057】

図11のデータ転送装置46は、第2実施形態のデータ転送装置22における順序制御部29および出力順保証部32が省略され、かつ、順序制御部29の省略に伴い、読み出し順の制御に関わるアクセス制御部30の範囲情報添付部34も省略されている。

【0058】

このデータ転送装置46において、出力制御部36’は、転送管理部28から要素の出力指令を受け取ると、一時保存部35に保持されている要素を、保持された順で読み出して競合調停部31に向けて出力する。つまり、このデータ転送装置46では、各アクセス制御部30’(30a’〜30d’)は、演算部21から受け取った要素を、受け取った順に競合調停部31に向けて出力する。このため、例えば、同じ転送パス38aを通って記憶装置23に転送される4個の要素e0〜e3を、演算部21からデータ転送装置46が受け取った場合には、当該データ転送装置46の競合調停部31は、それら4個の要素を同時又はほぼ同時に受け取る。この場合には、それら要素の転送先に対応する転送パス38が同じであるから、競合調停部31は、競合調停により、4個の要素を、1つずつ順次、記憶装置23に向けて出力する。競合調停部31は、上記4個の要素を全て出力し終えなければ、次の4個の要素を受け取らない。

【0059】

図12(b)は、データ転送装置46の動作による要素の流れを模式的に示したタイムチャートである。このタイムチャートを参照しながら、データ転送装置46における動作例を説明する。例えば、演算部21は、データ転送装置46に、一グループを構成する連続アドレスの16個の要素e0〜e15を、前記同様に、出力する。データ転送装置46は、それら受け取った各要素e0〜e15を、それぞれ、各アクセス制御部30’(30a’〜30d’)の一時保存部35で保持する。

【0060】

そして、転送管理部28の転送指令に基づき、各アクセス制御部30a’〜30d’の出力制御部36は、それぞれ、一時保存部35に格納されている要素を格納順に読み出して、競合調停部31に向けて出力する。つまり、まず、各アクセス制御部30a’〜30d’の出力制御部36は、要素e0〜e3を競合調停部31に出力する(図12(b)に示す時刻t0)。それら要素e0〜e3は、転送先に対応する転送パス38(38a)が同じである。このため、競合調停部31は、受け取った要素e0〜e3を、競合調停により、1個ずつ1クロック毎に順次、転送パス38aを通して記憶装置23に出力する(時刻t2〜t5)。

【0061】

ところで、競合調停部31は、要素e0〜e3の全てを出力し終えないと、次の要素e4〜e7を受け取ることができない。このため、アクセス制御部30a’〜30d’は、次の要素e4〜e7を競合調停部31に出力しようとしても出力できず時刻t1〜時刻t5に亘り待機状態になる。

【0062】

時刻t5において、競合調停部31が要素e0〜e3の全てを出力し終えると、アクセス制御部30a’〜30d’は、要素e4〜e7を競合調停部31に並列出力する。これ以降、データ転送装置46は、上記同様の動作を繰り返して、一グループの16個の要素e0〜e15を全て記憶装置23に転送する。データ転送装置46が要素e0〜e15の転送を開始してから終了するまでに要する時間は、図12(b)に示されるように、16クロック(16サイクル(16T))である。

【0063】

図12(a)は、第2実施形態のデータ転送装置22の動作による要素の流れを模式的に示したタイムチャートである。このタイムチャートを参照して、データ転送装置22による要素の流れの一例を説明する。

【0064】

第2実施形態では、データ転送装置22は、演算部21から同じグループの16個の要素e0〜e15を前記の如く受け取ると、それらを各アクセス制御部30a〜30dの一時保存部35に保持する。そして、図12(a)に示す時刻t0において、出力制御部36が、各一時保存部35から、順序制御部29により規定された読み出し順で、4個の要素e0,e13,e10,e17を読み出して、競合調停部31に向けて出力する。それら4個の要素e0,e13,e10,e17は、対応する転送パス38が互いに異なる。これにより、競合調停部31は、受け取った4個の要素の競合調停が不要であるので、時刻t2において、それら4個の要素を並列(同時又はほぼ同時)に、転送先に対応している転送パス38にそれぞれ出力する。このように、競合調停部31は、並列に受け取った4個の要素の全てを、受け取った次のクロックで出力できるので、当該競合調停部31は、1クロック毎に、アクセス制御部30から4個の要素を受け取ることが可能である。

【0065】

前記の如く競合調停部31から出力された各要素は、対応する出力順保証部32(32a〜32d)に入力し、まず、第1レジスタ40に保持される(時刻t2)。そして、次のクロック(時刻t3)で、それら各第1レジスタ40に保持された要素e0,e13,e10,e17は、第2レジスタ41に転送される。ここでは、同じグループの各要素の格納位置が互いに異なっているから、出力順保証部32は、図10に示される動作規定に従い順序保証動作は行わない。このため、次のクロック(時刻t4)で、各出力順保証部32a〜32dは、第2レジスタ41にそれぞれ保持されていた要素e0,e13,e10,e17を、転送先に対応している転送パス38に出力する。記憶装置23は、受け取った要素e0,e13,e10,e17を、アドレス情報に基づいた格納位置に格納する。

【0066】

第2実施形態のデータ転送装置22は、前述したように、各アクセス制御部30a〜30dから競合調停部31に並列出力する4個の要素の組み合わせが、競合調停部31において競合調停不要な組み合わせとなる構成を有している。これにより、競合調停に起因した転送速度の遅延(スループットの低下)を防止できる。すなわち、競合調停が必要な前記データ転送装置46では、データ転送装置46から記憶装置23へ16個の要素e0〜e15を転送するのに要する時間は16クロック(16T)である。これに対して、競合調停を行わなくて済むデータ転送装置22では、データ転送装置22から記憶装置23へ16個の要素e0〜e15を転送するのに要する時間は4クロック(4T)であり、データ転送装置46に比べて、転送速度(スループット)が改善している。

【0067】

なお、上記では、連続アドレスのメモリアクセス命令に基づいた要素を利用して、第2実施形態のデータ転送装置23等を説明したが、この第2実施形態のデータ転送装置23等は、間接参照のアドレスのメモリアクセス命令(リストストア命令)にも適用できる。

【0068】

図13は、データ転送装置22における、リストストア命令に関わる16個の要素e0〜e15の流れの一例を示すタイムチャートである。以下に、図13を参照して、データ転送装置22の、リストストア命令に関わる要素の転送動作の一例を説明する。

【0069】

ここで、要素e0〜e3の格納位置は0番地(記憶部251)、要素e4〜e7の格納位置は32番地(記憶部252)、要素e8〜e11の格納位置は64番地(記憶部253)、要素e12〜e15の格納位置は96番地(記憶部254)であるとする。また、演算部21は、要素e0〜e3を、並列に、かつ、互いに異なる演算パス26(26a〜26d)を通して、データ転送装置22に出力する。さらに、演算部21は、前記同様に、要素e4〜e7の組と、要素e8〜e11の組と、要素e12〜e15の組とを、順次、1クロック毎に、データ転送装置22に出力することとする。

【0070】

データ転送装置22は、演算部21から出力された16個の要素e0〜e15を、それぞれ、対応するアクセス制御部30a〜30dの一時保存部35に保持する。そして、アクセス制御部30a〜30dの出力制御部36は、前記同様に、順序制御部29により規定された読み出し順でもって各一時保存部35から要素を読み出して、競合調停部31に出力する(図13の時刻t0)。競合調停部31は、前記同様に、競合調停が不要であるから、受け取った要素を順次、出力する(時刻t2〜時刻t5)。

【0071】

一方、出力順保証部32(32a〜32d)は、競合調停部31から受け取った要素を順次、第1レジスタ40に保持すると共に、図8〜図10に基づく動作規定に従って動作する。以下では、出力順保証部32の動作を、出力順保証部32cを例にして説明する。

【0072】

出力順保証部32cには、4個の要素e8〜e11が、e10→e11→e8→e9の順で入力する。要素e10は読み出し順が最初であるから、要素e10のデータSは「1」、データEは「0」である。要素e9は読み出し順が最後であるから、要素e9のデータSは「0」、データEは「1」である。

【0073】

出力順保証部32cが図9に示す状態1(初期状態)であるときに、時刻t2において、出力順保証部32cは、要素e10を受け取ると、当該要素e10を第1レジスタ40に保持する。これにより、第1レジスタ40に保持されている要素のデータSが「1」であるから、出力順保証部32cは、図8(項番3)と図9に基づいて、状態1(初期状態)から状態2に遷移する。つまり、出力順保証部32c(判定部42)は、第1レジスタ40と第2レジスタ41に保持されている要素の要素番号とアドレス情報の監視を開始する。

【0074】

次のクロック(時刻t3)で、出力順保証部32cは、第1レジスタ40の要素e10を第2レジスタ41に転送し、一方で、次の要素e11を競合調停部31から受け取って、当該要素e11を第1レジスタ40に保持する。そして、判定部42は、比較部43の比較結果に基づいて、第1レジスタ40の要素番号e11が第2レジスタ41の要素番号e10よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第2レジスタ41の要素e10を削除する。また、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番8である。これにより、出力順保証部32cは、図9の状態2から状態3に遷移する。

【0075】

次のクロック(時刻t4)で、出力順保証部32cは、第1レジスタ40の要素e11を第2レジスタ41に転送し、一方で、次の要素e8を競合調停部31から受け取って、当該要素e8を第1レジスタ40に保持する。そして、判定部42は、比較部43の比較結果に基づいて、第2レジスタ41の要素番号e11が第1レジスタ40の要素番号e8よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第1レジスタ41の要素e8を削除する。一方、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番1である。これにより、出力順保証部32cは、図9の状態3を継続する。

【0076】

さらに、次のクロック(時刻t5)で、出力順保証部32cは、次の要素e9を競合調停部31から受け取って、当該要素e9を第1レジスタ40に保持する。このとき、第2レジスタ41は要素e11を継続的に保持している。そして、判定部42は、比較部43の比較結果に基づいて、第2レジスタ41の要素番号e11が第1レジスタ40の要素番号e9よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第1レジスタ41の要素e9を削除する。一方、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番2である。これにより、出力順保証部32cは、図9の状態3から状態4に遷移する。これにより、判定部42は、アドレス・要素番号の監視動作を終了する。

【0077】

さらに、次のクロック(時刻t6)において、出力順保証部32c(判定部42)は、第1レジスタ40の要素e11を、第2レジスタ41に転送する。これにより、第1レジスタ40には要素が保持されていない状態になる。このため、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番5になるから、出力順保証部32cは、図9の状態4から状態1に遷移する。なお、要素e11が第2レジスタ41に遷移したときに、別のグループの要素が第1レジスタ40に保持される場合が想定される。この場合には、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番6あるいは項番7である。この場合には、出力順保証部32cは、図9の状態4から状態2あるいは状態5に遷移する。

【0078】

さらに、次のクロック(時刻t7)において、出力順保証部32cは、第2レジスタ41の要素e11を記憶装置23に向けて出力する。

【0079】

上記同様に、他の出力順保証部32a,32b,32dも動作して、時刻t7において、各出力順保証部32a,32b,32dは、要素e3,e7,e15をそれぞれ記憶装置23に向けて出力する。

【0080】

上記のように、データ転送装置22は、時刻t7で要素を出力するが、間接参照に関わる要素(データ)の記憶装置23への転送処理においては、時刻t4から時刻t7に掛けて出力していると等価な状態となる。つまり、この場合においても、データ転送装置22は、4クロック(4T)で、一グループの16個の要素を記憶装置23に転送する。

【0081】

上記のように、第2実施形態のデータ転送装置22は、連続アドレスのメモリアクセス命令だけでなく、間接参照のアドレスのメモリアクセス命令に基づいた要素の転送に関しても、前記同様に、転送速度を改善できる。これにより、この第2実施形態のデータ転送装置22を備えた演算装置20は、演算時間を短縮できる。このような演算装置20は、例えば、画像処理を行う装置に組み込んで、その効果をよりs発揮することができる。

【0082】

(第3実施形態)

以下に、本発明に係る第3実施形態を説明する。なお、この第3実施形態の説明において、第2実施形態と同様な構成部分には同一符号を付し、その共通部分の重複説明は省略する。

【0083】

図14は、第3実施形態において特徴的な出力順保証部32’(32a’〜32d’)の構成を示したブロック図である。この第3実施形態では、出力順保証部32’は、第2レジスタとして、複数のレジスタ411,・・・41n(nは、2以上の整数)を有している。さらに、出力順保証部32’は、複数の比較部431,・・・43n(nは、2以上の整数)を有している。これら比較部431,・・・43nは、それぞれ、第1レジスタ40に保持されている要素の番号と、レジスタ411〜41nのうちの対応する一つのレジスタに保持されている要素の番号とを比較し、それら要素番号の大小関係を示す信号を出力する機能を備えている。さらにまた、出力順保証部32’は、複数の比較部441,・・・44n(nは、2以上の整数)をも有している。これら比較部441,・・・44nは、それぞれ、第2レジスタであるレジスタ411〜41nのうちの対応する一つのレジスタに保持されている要素のアドレスと、第1レジスタ40に保持されている要素のアドレスとを比較する。そして、各比較部441,・・・44nは、アドレスの一致・不一致を示す信号を出力する機能を備えている。

【0084】

この第3実施形態における上記以外の構成は、第2実施形態と同様である。

【0085】

この第3実施形態のデータ転送装置22は、上記の如く、出力順保証部以外の構成は、第2実施形態と同様である。これにより、この第3実施形態のデータ転送装置22における、出力順保証が不要な連続アドレスのメモリアクセス命令に基づいた要素の転送動作は、第2実施形態と同様である。このため、ここでは、その説明は省略する。

【0086】

図15は、この第3実施形態における、間接参照のアドレスのメモリアクセス命令に基づく要素の流れの一例を示したタイムチャートである。この図15を参照しながら、第3実施形態における出力順保証部32’の動作の一例を説明する。前提条件として、要素e0〜e3の格納位置は、それぞれ、0番地、8番地、16番地、0番地(何れも記憶部251)、要素e4〜e7の格納位置は、それぞれ、32番地、40番地、48番地、32番地(何れも記憶部252)、要素e8〜e11の格納位置はそれぞれ、64番地、72番地、80番地、64番地(何れも記憶部253)、要素e12〜e15の格納位置は、それぞれ、96番地、104番地、112番地、96番地(何れも記憶部254)であるとする。また、演算部21は、要素e0〜e3を、並列的に、かつ、互いに異なる演算パス26(26a〜26d)を通して、データ転送装置22に出力する。さらに、演算部21は、上記同様に、要素e4〜e7の組と、要素e8〜e11の組と、要素e12〜e15の組とを、順次、1クロック毎に、データ転送装置22に出力することとする。

【0087】

この第3実施形態においても、第2実施形態と同様に、図15に示す時刻t2において、競合調停部31は、4個の要素e0,e13,e10,e7を、並列的に、出力する。それら要素e0,e13,e10,e7は、それぞれ、対応する出力順保証部32a’〜32d’に入力する。出力順保証部32’の動作の説明を、分かり易くするために、ここでは、出力順保証部32c’に着目して説明する。

【0088】

出力順保証部32c’は、要素e10が入力すると(時刻t2)、当該要素e10を第1レジスタ40に保持する。

【0089】

次のクロック(時刻t3)において、出力順保証部32c’は、要素e10を第1レジスタ40から第2レジスタ411に転送し、また、入力してきた要素e11を第1レジスタ40に保持する。そして、判定部42は、比較部441の比較結果により、第1レジスタ40の要素e11のアドレスと、第2レジスタ411の要素e10のアドレスとが不一致であることを検知する。なお、図15では、出力順保証部32c’の第2レジスタの保持状態のみ図示している。

【0090】

次のクロック(時刻t4)において、判定部42は、上記アドレスの比較結果および図16に示す動作規定に従って、第2レジスタ411の要素e10はそのまま保持した状態で、第1レジスタ40の要素e11を、空いている第2レジスタ412に転送する。また、出力順保証部32c’は、次に入力してきた要素e8を第1レジスタ40に保持する。そして、判定部42は、第1レジスタ40の要素e8と、第2レジスタ411の要素e10とのアドレスが一致していることを検知する。また、判定部42は、第2レジスタ411の要素番号e10が、第1レジスタ40の要素番号e8よりも大きいことを検知する。これにより、判定部42は、図16の動作規定に従って、要素番号e8を削除する。

【0091】

次のクロック(時刻t5)において、出力順保証部32c’は、入力してきた要素e9を第1レジスタ40に保持する。そして、判定部42は、比較部441の比較結果により、第1レジスタ40の要素e11のアドレスと、第2レジスタ411の要素e10のアドレスとが不一致であることを検知する。これにより、判定部42は、図16の動作規定に従って、第1レジスタ40の要素e9を空き第2レジスタ413に転送する。

【0092】

同じグループの要素の入力は要素e9が最後であることから、次のクロック(時刻t6)以降、出力順保証部32cは、第2レジスタ411,412,413に保持されている要素e9,e10,e8を順次、記憶装置23に向けて出力する。

【0093】

この第3実施形態においても、第2実施形態と同様に、一グループの16個の要素をデータ転送装置22から記憶装置23に転送するのに要する時間は、4クロック(4T)である。つまり、この第3実施形態のデータ転送装置22においても、第2実施形態と同様に、競合調停部31で、競合調停を行わずに済む構成を備えているので、転送時間の低下(スループットの悪化)を防止できる。

【0094】

さらに、この第3実施形態では、出力順保証部32’は、第2レジスタとして、複数のレジスタを有している。このため、演算部21から並列的に出力される複数の要素の中の一部に、格納位置が同じ複数の要素が含まれている場合においても、順序保証を行うことが可能になる。

【0095】

なお、この発明は、第1〜第3の各実施の形態に限定されるものではなく、様々な実施の形態を採り得る。例えば、第2や第3の実施形態では、記憶装置23の記憶部25は4個であったが、記憶装置23が有する記憶部25の数は、4個に限定されず、4個以外の複数の記憶部25を設けてもよい。

【符号の説明】

【0096】

1,22 データ転送装置

2,35 一時保存部

3,29 順序制御部

4 データ読み出し部

5 転送制御部

10,20 演算装置

11,21 演算部

12,23 記憶装置

31 競合調停部

32 出力順保証部

34 範囲情報添付部

36 出力制御部

【技術分野】

【0001】

本発明は、データを格納する記憶部に向けてデータを転送するデータ転送装置、演算装置、それを備えた装置およびデータ転送方法に関する。

【背景技術】

【0002】

図17は、データ転送装置を備えた演算装置の一例を、概略的に示すブロック構成図である(例えば特許文献1参照)。この演算装置60は、演算部61と、データ転送装置62と、記憶装置63とを備えている。演算部61は、複数の演算処理を並列的に行うことが可能な機能(例えばベクトル演算機能)を備えている。記憶装置63は、データを保存する複数の記憶部641〜64r(rは、2以上の整数)を有している。

【0003】

データ転送装置62は、複数の入力パス651〜65p(pは、2以上の整数)によって、演算部61と接続している。また、データ転送装置62は、複数の出力パス661〜66q(qは、2以上の整数)によって、記憶装置63と接続している。データ転送装置62は、演算部61から受信したデータを、当該データに添付されている転送先のアドレス情報に基づいて、記憶装置63に転送する機能を備えている。

【0004】

ところで、演算部61は、並列処理が可能であることから、複数のデータを同時にデータ転送装置62に出力する場合がある。この場合に、それらデータの転送先の記憶部が互いに異なっている場合には、データ転送装置62は、それらデータを、それぞれ、互いに異なる出力パス661〜66qを通して記憶装置63に出力する。一方、演算部61からデータ転送装置62に同時に出力された複数のデータの転送先の記憶部が同じ場合には、データ転送装置62は、例えば、データの競合調停により、それらデータを一つずつ順次、同じ出力パスを通して記憶装置63に出力する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−342306号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記のように、データ転送装置62が演算部61から複数のデータを同時に受け取っても、それらデータの転送先の記憶部が同じ場合には、データの競合調停に起因して、データは、データ転送装置62から記憶部63へ、一つずつ順次出力される。このために、データ転送装置62から記憶装置63へのデータ転送において、同時入力した複数のデータの転送先の記憶部が同じ場合には、転送速度が遅くなる、換言すれば、スループットが低下するという問題が生じる。

【0007】

本発明は上記課題を解決するためになされた。すなわち、本発明の主な目的は、データ転送装置から記憶装置へのデータ転送のスループットを向上できるデータ転送装置、演算装置、それを備えた装置およびデータ転送方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明のデータ転送装置は、

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部にそれぞれ対応し、かつ、当該データ入力部を通った前記データをそれぞれ保存する複数の一時保存部と、

一グループを構成する複数の前記データがそれぞれ前記各データ入力部を通って前記各一時保存部に分散保存された場合に、前記各一時保存部から、並列に、同じグループの前記データを読み出すデータ読み出し部と、

前記転送先に関連付けられている複数のデータ出力部に接続し、前記データ読み出し部により読み出された前記データを、当該データのアドレス情報に基づいた転送先に対応する前記データ出力部に向けて出力する転送制御部と、

前記データ読み出し部によって前記各一時保存部から並列に読み出される前記各データの転送先に対応する前記データ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定する順序制御部と、

を有している。

【0009】

本発明の演算装置は、

演算処理を行う演算部と、

複数の記憶部を有する記憶装置と、

前記演算部から出力されたデータを前記記憶装置に転送する上記本発明のデータ転送装置と

を有する。

【0010】

本発明における演算装置を装備した装置は、本発明の上記演算装置を有している。

【0011】

本発明のデータ転送方法は、

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部をそれぞれ通って、一グループを構成する複数の前記データが入力された場合に、それらデータを、前記各データ入力部にそれぞれ対応する一時保存部に分散保存し、

前記各一時保存部から並列に読み出される前記各データの転送先に対応するデータ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定し、

その設定された読み出し順に従って、前記各一時保存部から、並列に、同じグループの前記データを読み出して転送先に向けて出力する。

【発明の効果】

【0012】

本発明によれば、データ転送装置から記憶装置へのデータ転送のスループットを向上できる。

【図面の簡単な説明】

【0013】

【図1】本発明に係る第1実施形態の構成を概略的に示すブロック図である。

【図2】本発明に係る第2実施形態のデータ転送装置および演算装置の構成を示すブロック図である。

【図3】本発明に係る第2実施形態において演算部から記憶装置に転送される要素の構成を模式的に示すイメージ図である。

【図4】本発明に係る第2実施形態のデータ転送装置を構成するアクセス制御部の構成を示すブロック図である。

【図5】一時保存部から読み出される要素の読み出し順の一例を示す図である。

【図6】要素に付与される読み出し順に関する情報の一例を示す図である。

【図7】本発明に係る第2実施形態における出力順保証部の構成を示すブロック図である。

【図8】出力順保証部を構成するレジスタの要素の保持(格納)・出力に関する説明に利用する図である。

【図9】出力順保証部を構成する判定部の動作状態の遷移を示す模式図である。

【図10】判定部の動作の一例の説明に利用する図である。

【図11】本発明に係る第2実施形態のデータ転送装置と比較する比較例としてのデータ転送装置の構成を示すブロック図である。

【図12】データ転送装置における要素の流れの一例を示すタイムチャートである。

【図13】さらに、データ転送装置における要素の別の流れの一例を示すタイムチャートである。

【図14】本発明に係る第3実施形態のデータ転送装置を構成する出力順保証部の構成を示すブロック図である。

【図15】本発明に係る第3実施形態のデータ転送装置における要素の流れの一例を示すタイムチャートである。

【図16】本発明に係る第3実施形態における出力順保証部の判定部の動作の一例の説明に利用する図である。

【図17】演算装置の一例を示すブロック図である。

【発明を実施するための形態】

【0014】

以下に、本発明に係る実施形態を図面を参照して説明する。

【0015】

(第1実施形態)

図1(a)は、本発明に係る第1実施形態のデータ転送装置の構成を概略的に示すブロック構成図である。図1(b)は、そのデータ転送装置を備えた第1実施形態の演算装置の構成を概略的に示すブロック構成図である。

【0016】

第1実施形態の演算装置10は、図1(b)に示されるように、演算処理を行う演算部11と、データを記憶する機能を備えた記憶装置12とを有すると共に、下記に示すデータ転送装置1を有している。

【0017】

第1実施形態のデータ転送装置1は、演算部11から受け取ったデータを記憶装置12に転送する装置である。当該データ転送装置1は、図1(a)に示されるように、複数の一時保存部2(21,・・・2n(nは2以上の整数))と、順序制御部3と、データ読み出し部4と、転送制御部(クロスバ部)5とを有している。

【0018】

すなわち、各一時保存部2(21,・・・2n)は、個別に対応するデータ入力部6と接続している。データ入力部6は、転送先の格納位置を示すアドレス情報付きのデータをデータ転送装置1に導入する経路である。各一時保存部2は、接続しているデータ入力部6を通ってデータ転送装置1に入力されたデータを保存する機能を有している。

【0019】

データ読み出し部4は、各一時保存部2から、並列(換言すれば、同時又はほぼ同時)に、データを読み出す機能を備えている。

【0020】

転送制御部5は、複数のデータ出力部7に接続している。それらデータ出力部7は、それぞれ、データの転送先に関連付けられている。転送制御部5は、データ読み出し部4により読み出された各データを、当該データに添付されているアドレス情報に基づいた転送先に対応しているデータ出力部7に出力する。

【0021】

順序制御部3は、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2毎にデータの読み出し順を設定する機能を有している。

【0022】

この第1実施形態のデータ転送装置1は、上記のように、各一時保存部2から並列に読み出される各データの転送先に対応するデータ出力部7が互いに異なるように、一時保存部2からのデータの読み出し順を制御する構成を有している。このため、第1実施形態のデータ転送装置1および演算装置10は、次にような効果を得ることができる。すなわち、その効果とは、転送制御部5がデータ出力部7を通してデータを記憶装置12に転送する際に、転送制御部5におけるデータの競合調停を回避できるという効果である。この効果によって、第1実施形態のデータ転送装置1および演算装置10は、データの競合調停に起因した記憶装置へのデータの転送速度が遅くなる、換言すれば、スループットが悪化するという問題を防止できる。

【0023】

上記したような第1実施形態のデータ転送装置1およびそれを有する演算装置10は、図1(c)に示されるような演算装置を装備した装置13を構成することができる。この装置13は、第1実施形態のデータ転送装置1を有しているので、データ転送のスループットが向上し、これにより、演算処理速度のより高速化を図ることができる。

【0024】

(第2実施形態)

以下に、本発明に係る第2実施形態を説明する。

【0025】

図2は、第2実施形態のデータ転送装置を備えた演算装置の構成を簡略化して示したブロック図である。この第2実施形態の演算装置20は、演算部21と、データ転送装置22と、記憶装置23とを有している。なお、具体的には、CPU(Central Processing Unit)が、記憶装置(記憶装置23と同じ、あるいは別の記憶装置)に予め格納されたコンピュータプログラムに基づき動作することによって、演算部21およびデータ転送装置22が実現される。つまり、CPUが、演算部21およびデータ転送装置22として機能する。

【0026】

記憶装置23は、例えばハードディスク装置等の記憶媒体により構成される複数の記憶部25(この第2実施形態では、少なくとも4つの記憶部251〜254)を有している。なお、ここでは、それら記憶部251〜254は同型とする。

【0027】

演算部21は、ベクトル演算処理が可能な機能を有する。この演算部21は、ベクトル演算によるデータを含む次に示すような要素を複数個、同時又はほぼ同時(並列的)にデータ転送装置22に向けて出力する機能を有する。図3(a)は、その要素の構成をイメージで表した図である。つまり、演算部21から出力される要素とは、データに、当該データの格納(書き込み)を指令するコマンドと、要素番号と、当該データの格納位置(記憶位置)を示すアドレス情報とが添付されている情報のまとまりである。

【0028】

この第2実施形態では、説明を分かり易くするために、演算部21は、一グループを構成する16個の要素を4個ずつ並列出力することとし、かつ、それら16個の要素のアドレスは連続していることとする。より具体的に説明すると、それら16個の各要素には、e0〜e15の要素番号が付与されている。かつ、各要素のデータのデータ幅は、8バイトとする。かつ、記憶装置23における各要素の格納位置であるアドレスは、要素番号の小さいものから0番地、8番地、・・・というように、8バイトずつ変位する連続アドレスであるとする。さらに、それらアドレスの0〜31番地は、記憶部251に対応し、アドレスの32〜63番地は、記憶部252に対応し、アドレスの64〜95番地は、記憶部253に対応し、アドレスの96〜127番地は、記憶部254に対応しているものとする。

【0029】

この第2実施形態では、演算部21は、要素番号e0〜e3を並列(同時又はほぼ同時)に別々の演算パス26a〜26dに出力する。そして、次の出力タイミング(次のクロック)では、演算部21は、要素番号e4〜e7を別々の演算パス26a〜26dに並列出力する。このように、演算部21は、一グループの要素番号の小さいものから順に4個ずつ別々の演算パス26a〜26dに並列出力する。換言すれば、この第2実施形態では、演算部21は、記憶部251行きの4つの要素(要素番号e0〜e3)をそれぞれ並列に出力するというように、行き先の記憶部25が同じ4つの要素を並列に各演算パス26に出力する。なお、この第2実施形態では、要素e0は演算パス26aに、要素e1は演算パス26bに、要素e3は演算パス26cに、要素e4は演算パス26dに、それぞれ、出力されるというように、並列出力される4つの要素は、その要素番号の小さいものから順に演算パス26a〜26dに対応して出力される。

【0030】

また、演算部21は、上記のような要素を出力すると共に、その要素の処理に関わる制御情報(例えば、転送タイミングを知らせる情報や、グループに関する情報など)を、データ転送装置22に向けて出力する機能を有している。

【0031】

データ転送装置22は、複数の演算パス26(ここでは、4本の演算パス26a〜26d)、および、制御パス27によって、演算部21に接続している。演算パス26は、上記したような要素(データ)をデータ転送装置22に導入する経路(データ入力部)である。制御パス27は、上記したような要素の制御情報が通る情報の経路である。

【0032】

データ転送装置22は、演算部21から受け取ったデータ(要素)を記憶装置23に転送する機能を備えている。つまり、当該データ転送装置22は、転送管理部28と、順序制御部29と、複数のアクセス制御部30と、転送制御部である競合調停部(クロスバ部)31と、複数の出力順保証部32とを有している。

【0033】

転送管理部28は、演算部21から出力される制御情報に基づいて、データ転送装置22の要素(データ)の転送の開始と終了を管理する機能を備えている。

【0034】

アクセス制御部30は、演算パス26a〜26dに対応して設けられている。つまり、この第2実施形態のデータ転送装置22は、演算パス26a〜26dにそれぞれ一対一に対応して接続するアクセス制御部30a〜30dを有している。また、各アクセス制御部30a〜30dは、順序制御部29に接続している。

【0035】

各アクセス制御部30a〜30dは、図4に示されるように、範囲情報添付部34と、一時保存部35と、出力制御部36とを有している。

【0036】

一時保存部35は、演算パス26を通ってデータ転送装置22に入力してきた要素(データ)を保存する機能を有する。この第2実施形態では、図5に示されるように、アクセス制御部30aの一時保存部35は、演算パス26aを通った要素e0,e4,e8,e12を保存する。アクセス制御部30bの一時保存部35は、演算パス26bを通った要素e1,e5,e9,e13を保存する。アクセス制御部30cの一時保存部35は、演算パス26cを通った要素e2,e6,e10,e14を保存する。アクセス制御部30dの一時保存部35は、演算パス26dを通った要素e3,e7,e11,e15を保存する。

【0037】

出力制御部36は、制御パス33によって後述する順序制御部29から加えられる読み出し順の情報に従って、一時保存部35に保存されている要素を順次読み出す機能を備えている。この第2実施形態では、アクセス制御部30a〜30dの各出力制御部36は、順序制御部29からの指示によって、読み出しタイミングを合わせて要素を読み出す。すなわち、この第2実施形態では、アクセス制御部30a〜30dの出力制御部36は、各一時保存部35から、データ(要素)を並列に読み出すデータ読み出し部としての機能を有する。

【0038】

さらに、出力制御部36は、上記のように読み出した要素(データ)を競合調停部31に向けて出力する機能を有している。

【0039】

範囲情報添付部34は、上記のように出力制御部36によって一時保存部35から読み出された要素の同じグループ内における読み出し順に関する情報を、各データに添付する機能を備えている。第2実施形態では、範囲情報添付部34は、図3(b)に示されるように、各データに、読み出し順が最初か否かを示すデータSと、読み出し順が最後か否かを示すデータEとを添付する。具体的には、範囲情報添付部34は、一時保存部35に保存される同じグループの4個の要素のうち、最初に読み出された要素には、図6に示されるように、データSとして「1」を、また、データEには「0」を添付する。また、範囲情報添付部34は、最後に読み出された要素には、データSとして「0」を、また、データEには「1」を添付する。さらに、範囲情報添付部34は、それ以外の読み出し順(中間)の要素には、データS,Eとして、それぞれ「0」を添付する。なお、一グループを構成する要素の数が少なくて一時保存部35に保存される同じグループの要素が1個のみである場合がある。この場合には、範囲情報添付部34は、その要素には、データS,Eとして、それぞれ「1」を添付する。さらにまた、要素が無効である場合がある。この場合には、範囲情報添付部34は、要素に、データS,Eとして、それぞれ「0」を添付する。

【0040】

順序制御部29は、転送管理部28から動作開始指令を受信した場合に、出力制御部36および範囲情報添付部34に向けて動作開始指令を出力すると共に、出力制御部36には次に示すような読み出し順の情報をも送信する機能を備えている。つまり、順序制御部29は、出力制御部36による要素の読み出し順を設定する機能を有している。

【0041】

その読み出し順は、次のように設定されている。つまり、後述する競合調停部31は、データ出力部として機能する複数の転送パス38(38a〜38d)に接続している。その転送パス38aは記憶装置23の記憶部251に、また、転送パス38bは記憶部252に、さらに、転送パス38cは記憶部253に、さらにまた、転送パス38dは記憶部254に、それぞれ、対応している。この第2実施形態では、各アクセス制御部30a〜30dの出力制御部36による各一時保存部35からの読み出し順は、並列に読み出される各要素の転送先に関連付けられている転送パス38が互いに異なるように設定されている。具体的には、第2実施形態では、図6に示されるように、アクセス制御部30aでは、一時保存部35における同じグループの要素e0,e4,e8,e12は、格納順に、つまり、要素番号e0→e4→e8→e12の順に、読み出されるように、その読み出し順が設定される。また、アクセス制御部30bでは、一時保存部35における同じグループの要素e1,e5,e9,e13は、4番目に格納した要素から、つまり、要素番号e13→e1→e5→e9の順に、読み出されるように、その読み出し順が設定される。アクセス制御部30cでは、一時保存部35における同じグループの要素e2,e6,e10,e14は、3番目に格納した要素から、つまり、要素番号e10→e14→e2→e6の順に、読み出されるように、その読み出し順が設定される。アクセス制御部30dでは、一時保存部35における同じグループの要素e3,e7,e11,e15は、2番目に格納した要素から、つまり、要素番号e7→e11→e15→e3の順に、読み出されるように、その読み出し順が設定される。このように、読み出し順が設定されることによって、読み出し順が同じ4個の要素の各転送先が対応している転送パス38は、互いに異なることになる。

【0042】

競合調停部31は、上記のように、記憶装置23の各記憶部251〜254と一対一の関係を持つ4本の転送パス38(38a〜38d)に接続している。なお、この第2実施形態では、転送パス38の数は、演算パス26の数と同じであったが、当該転送パス38の数は、演算パス26の数と同じでなくともよい。

【0043】

競合調停部31は、アクセス制御部30a〜30dから並列出力された複数(4個)の要素を受け取ると、それら各要素を、それぞれ、アドレス情報に基づいた転送先に対応している転送パス38に向けて出力(転送)する機能を有している。この第2実施形態では、上記のように、競合調停部31がアクセス制御部30a〜30dから並列に受け取る4個の要素は、対応する転送パス38が互いに異なる転送先を持つ要素である。この場合、競合調停部31は、それら受け取った4個の要素を、並列(同時又はほぼ同時)に、対応する転送パス38に向けて出力する。

【0044】

なお、競合調停部31は、受け取った複数の要素のうち、少なくとも2個の要素の出力先となる転送パス38が同じ場合には、競合調停により、それら要素を順次1個ずつ転送パス38に出力する機能をも備えている。このように、第2実施形態では、競合調停部31は、競合調停の機能を有しているが、前述したように、対応する転送パス38が互いに異なる転送先を持つ要素が並列に入力するので、その競合調停を行わなくて済む。

【0045】

出力順保証部32(32a〜32d)は、転送パス38a〜38dにそれぞれ介設されている。これら出力順保証部32は、競合調停部31から各転送パス38a〜38dに順次出力された要素の順番を、予め定めた条件に従って並べ換えて、記憶装置23に送出する機能を備えている。

【0046】

図7は、第2実施形態における出力順保証部32(32a〜32d)の構成を示すブロック図である。つまり、この第2実施形態では、出力順保証部32は、第1レジスタ40と、第2レジスタ41と、判定部42と、比較部43,44とを有している。第1レジスタ40および第2レジスタ41は、競合調停部31から出力された要素を保持する機能を備えている。ここでは、転送パス38から出力保証部32に入力した要素は、まず、第1レジスタ40に保持され、ここで保持された要素が、後述する判定部42の動作によって、第2レジスタ41に転送されて保持される。換言すれば、第2レジスタ41は、先行する要素を保持する先行レジスタであり、第1レジスタ40は、その先行する要素に続く後続の要素を保持する後続レジスタである。

【0047】

比較部43は、第1レジスタ40に保持されている要素の要素番号と、第2レジスタ41に保持されている要素の要素番号とを比較し、この比較の結果による第1レジスタ40の要素番号と、第2レジスタ41の要素番号との大小関係に応じた信号を出力する。

【0048】

比較部44は、第1レジスタ40に保持されている要素のアドレスと、第2レジスタ41に保持されている要素のアドレスとを比較する。そして、比較部44は、第1レジスタ40のアドレスと、第2レジスタ41のアドレスとが一致しているか不一致であるかに応じた信号を出力する。

【0049】

判定部42は、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせと、比較部43,44からの出力信号(比較結果)とに基づいて、次のような要素の順序保証(出力順保証)に関わる動作を実行する機能を有している。

【0050】

図8は、第1レジスタ40と、第2レジスタ41とにそれぞれ保持されている要素のデータS,Eの組み合わせと、第2レジスタ41の次の状態との関係を表にまとめて示している。なお、図8において、データSとデータEの両方が「0」である場合は、一グループの要素の読み出し順が中間であることを示すだけでなく、第1レジスタ40や第2レジスタ41に要素が保持されていない場合もある。例えば、項番1’は、第1レジスタ40にも第2レジスタ41にも要素が格納されていない状態である。

【0051】

図9は、要素番号とアドレスの比較(監視)に関わる判定部42の動作状態の遷移を模式的に表した図である。この図9中における矢印に付されている各符号は、それぞれ、図8中の項番に対応している。

【0052】

図10は、比較部43,44の比較結果と、判定部42の順序保証動作との関係を表により示している。

【0053】

判定部42は、図8〜図10に示すような動作規定に従って要素の順序保証の動作を行う。この第2実施形態では、一グループの16個の要素e0〜e15は、全て、互いに格納位置を示すアドレスが異なっている。このため、判定部42は、図10の動作規定に従って、順序保証動作を行わない。つまり、判定部42は、競合調停部31から受け取った要素を、まず、第1レジスタ40に格納する。そして、判定部42は、例えば次のクロックで、その第1レジスタ40の要素を第2レジスタ41に転送すると共に、競合調停部31から次に受け取った要素を、第1レジスタ40に格納する。さらに、判定部42は、その次のクロックで、第2レジスタ41の要素を転送パス38を通して記憶装置23に出力し、かつ、上記同様に、第1レジスタ40の要素を第2レジスタ41に転送し、さらに、競合調停部31から次に受け取った要素を、第1レジスタ40に格納する。つまり、この第2実施形態では、一グループの要素は転送先のアドレスが連続しており、当該要素の転送は、連続アドレスのメモリアクセス命令に基づく転送である。このような場合には、競合調停部31から各転送パス38に上記の如く出力される要素の順序保証は不要である。このため、各出力順保証部32(32a〜32d)の判定部42は、順序保証を行うことなく、第2レジスタ41の要素を転送パス38を通して記憶装置23に向けて出力する。

【0054】

記憶装置23は、上記のように、データ転送装置22(出力順保証部32)から出力された要素のデータを、アドレス情報に示される格納位置に格納する。

【0055】

この第2実施形態では、上記のような構成を有しているから、競合調停部31において、要素(データ)の競合調停を行わなくて済む。このため、この第2実施形態におけるデータ転送装置22および演算装置20は、要素(データ)の競合調停に起因した要素(データ)の転送速度の低下(スループットの悪化)を防止できる。この効果を以下に具体的に説明する。

【0056】

ここで、比較例としての図11に示すデータ転送装置の構成を簡単に説明する。なお、図11のデータ転送装置の説明において、第2実施形態のデータ転送装置22と同様な構成部分には同一符号を付し、その共通部分の重複説明は省略する。

【0057】

図11のデータ転送装置46は、第2実施形態のデータ転送装置22における順序制御部29および出力順保証部32が省略され、かつ、順序制御部29の省略に伴い、読み出し順の制御に関わるアクセス制御部30の範囲情報添付部34も省略されている。

【0058】

このデータ転送装置46において、出力制御部36’は、転送管理部28から要素の出力指令を受け取ると、一時保存部35に保持されている要素を、保持された順で読み出して競合調停部31に向けて出力する。つまり、このデータ転送装置46では、各アクセス制御部30’(30a’〜30d’)は、演算部21から受け取った要素を、受け取った順に競合調停部31に向けて出力する。このため、例えば、同じ転送パス38aを通って記憶装置23に転送される4個の要素e0〜e3を、演算部21からデータ転送装置46が受け取った場合には、当該データ転送装置46の競合調停部31は、それら4個の要素を同時又はほぼ同時に受け取る。この場合には、それら要素の転送先に対応する転送パス38が同じであるから、競合調停部31は、競合調停により、4個の要素を、1つずつ順次、記憶装置23に向けて出力する。競合調停部31は、上記4個の要素を全て出力し終えなければ、次の4個の要素を受け取らない。

【0059】

図12(b)は、データ転送装置46の動作による要素の流れを模式的に示したタイムチャートである。このタイムチャートを参照しながら、データ転送装置46における動作例を説明する。例えば、演算部21は、データ転送装置46に、一グループを構成する連続アドレスの16個の要素e0〜e15を、前記同様に、出力する。データ転送装置46は、それら受け取った各要素e0〜e15を、それぞれ、各アクセス制御部30’(30a’〜30d’)の一時保存部35で保持する。

【0060】

そして、転送管理部28の転送指令に基づき、各アクセス制御部30a’〜30d’の出力制御部36は、それぞれ、一時保存部35に格納されている要素を格納順に読み出して、競合調停部31に向けて出力する。つまり、まず、各アクセス制御部30a’〜30d’の出力制御部36は、要素e0〜e3を競合調停部31に出力する(図12(b)に示す時刻t0)。それら要素e0〜e3は、転送先に対応する転送パス38(38a)が同じである。このため、競合調停部31は、受け取った要素e0〜e3を、競合調停により、1個ずつ1クロック毎に順次、転送パス38aを通して記憶装置23に出力する(時刻t2〜t5)。

【0061】

ところで、競合調停部31は、要素e0〜e3の全てを出力し終えないと、次の要素e4〜e7を受け取ることができない。このため、アクセス制御部30a’〜30d’は、次の要素e4〜e7を競合調停部31に出力しようとしても出力できず時刻t1〜時刻t5に亘り待機状態になる。

【0062】

時刻t5において、競合調停部31が要素e0〜e3の全てを出力し終えると、アクセス制御部30a’〜30d’は、要素e4〜e7を競合調停部31に並列出力する。これ以降、データ転送装置46は、上記同様の動作を繰り返して、一グループの16個の要素e0〜e15を全て記憶装置23に転送する。データ転送装置46が要素e0〜e15の転送を開始してから終了するまでに要する時間は、図12(b)に示されるように、16クロック(16サイクル(16T))である。

【0063】

図12(a)は、第2実施形態のデータ転送装置22の動作による要素の流れを模式的に示したタイムチャートである。このタイムチャートを参照して、データ転送装置22による要素の流れの一例を説明する。

【0064】

第2実施形態では、データ転送装置22は、演算部21から同じグループの16個の要素e0〜e15を前記の如く受け取ると、それらを各アクセス制御部30a〜30dの一時保存部35に保持する。そして、図12(a)に示す時刻t0において、出力制御部36が、各一時保存部35から、順序制御部29により規定された読み出し順で、4個の要素e0,e13,e10,e17を読み出して、競合調停部31に向けて出力する。それら4個の要素e0,e13,e10,e17は、対応する転送パス38が互いに異なる。これにより、競合調停部31は、受け取った4個の要素の競合調停が不要であるので、時刻t2において、それら4個の要素を並列(同時又はほぼ同時)に、転送先に対応している転送パス38にそれぞれ出力する。このように、競合調停部31は、並列に受け取った4個の要素の全てを、受け取った次のクロックで出力できるので、当該競合調停部31は、1クロック毎に、アクセス制御部30から4個の要素を受け取ることが可能である。

【0065】

前記の如く競合調停部31から出力された各要素は、対応する出力順保証部32(32a〜32d)に入力し、まず、第1レジスタ40に保持される(時刻t2)。そして、次のクロック(時刻t3)で、それら各第1レジスタ40に保持された要素e0,e13,e10,e17は、第2レジスタ41に転送される。ここでは、同じグループの各要素の格納位置が互いに異なっているから、出力順保証部32は、図10に示される動作規定に従い順序保証動作は行わない。このため、次のクロック(時刻t4)で、各出力順保証部32a〜32dは、第2レジスタ41にそれぞれ保持されていた要素e0,e13,e10,e17を、転送先に対応している転送パス38に出力する。記憶装置23は、受け取った要素e0,e13,e10,e17を、アドレス情報に基づいた格納位置に格納する。

【0066】

第2実施形態のデータ転送装置22は、前述したように、各アクセス制御部30a〜30dから競合調停部31に並列出力する4個の要素の組み合わせが、競合調停部31において競合調停不要な組み合わせとなる構成を有している。これにより、競合調停に起因した転送速度の遅延(スループットの低下)を防止できる。すなわち、競合調停が必要な前記データ転送装置46では、データ転送装置46から記憶装置23へ16個の要素e0〜e15を転送するのに要する時間は16クロック(16T)である。これに対して、競合調停を行わなくて済むデータ転送装置22では、データ転送装置22から記憶装置23へ16個の要素e0〜e15を転送するのに要する時間は4クロック(4T)であり、データ転送装置46に比べて、転送速度(スループット)が改善している。

【0067】

なお、上記では、連続アドレスのメモリアクセス命令に基づいた要素を利用して、第2実施形態のデータ転送装置23等を説明したが、この第2実施形態のデータ転送装置23等は、間接参照のアドレスのメモリアクセス命令(リストストア命令)にも適用できる。

【0068】

図13は、データ転送装置22における、リストストア命令に関わる16個の要素e0〜e15の流れの一例を示すタイムチャートである。以下に、図13を参照して、データ転送装置22の、リストストア命令に関わる要素の転送動作の一例を説明する。

【0069】

ここで、要素e0〜e3の格納位置は0番地(記憶部251)、要素e4〜e7の格納位置は32番地(記憶部252)、要素e8〜e11の格納位置は64番地(記憶部253)、要素e12〜e15の格納位置は96番地(記憶部254)であるとする。また、演算部21は、要素e0〜e3を、並列に、かつ、互いに異なる演算パス26(26a〜26d)を通して、データ転送装置22に出力する。さらに、演算部21は、前記同様に、要素e4〜e7の組と、要素e8〜e11の組と、要素e12〜e15の組とを、順次、1クロック毎に、データ転送装置22に出力することとする。

【0070】

データ転送装置22は、演算部21から出力された16個の要素e0〜e15を、それぞれ、対応するアクセス制御部30a〜30dの一時保存部35に保持する。そして、アクセス制御部30a〜30dの出力制御部36は、前記同様に、順序制御部29により規定された読み出し順でもって各一時保存部35から要素を読み出して、競合調停部31に出力する(図13の時刻t0)。競合調停部31は、前記同様に、競合調停が不要であるから、受け取った要素を順次、出力する(時刻t2〜時刻t5)。

【0071】

一方、出力順保証部32(32a〜32d)は、競合調停部31から受け取った要素を順次、第1レジスタ40に保持すると共に、図8〜図10に基づく動作規定に従って動作する。以下では、出力順保証部32の動作を、出力順保証部32cを例にして説明する。

【0072】

出力順保証部32cには、4個の要素e8〜e11が、e10→e11→e8→e9の順で入力する。要素e10は読み出し順が最初であるから、要素e10のデータSは「1」、データEは「0」である。要素e9は読み出し順が最後であるから、要素e9のデータSは「0」、データEは「1」である。

【0073】

出力順保証部32cが図9に示す状態1(初期状態)であるときに、時刻t2において、出力順保証部32cは、要素e10を受け取ると、当該要素e10を第1レジスタ40に保持する。これにより、第1レジスタ40に保持されている要素のデータSが「1」であるから、出力順保証部32cは、図8(項番3)と図9に基づいて、状態1(初期状態)から状態2に遷移する。つまり、出力順保証部32c(判定部42)は、第1レジスタ40と第2レジスタ41に保持されている要素の要素番号とアドレス情報の監視を開始する。

【0074】

次のクロック(時刻t3)で、出力順保証部32cは、第1レジスタ40の要素e10を第2レジスタ41に転送し、一方で、次の要素e11を競合調停部31から受け取って、当該要素e11を第1レジスタ40に保持する。そして、判定部42は、比較部43の比較結果に基づいて、第1レジスタ40の要素番号e11が第2レジスタ41の要素番号e10よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第2レジスタ41の要素e10を削除する。また、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番8である。これにより、出力順保証部32cは、図9の状態2から状態3に遷移する。

【0075】

次のクロック(時刻t4)で、出力順保証部32cは、第1レジスタ40の要素e11を第2レジスタ41に転送し、一方で、次の要素e8を競合調停部31から受け取って、当該要素e8を第1レジスタ40に保持する。そして、判定部42は、比較部43の比較結果に基づいて、第2レジスタ41の要素番号e11が第1レジスタ40の要素番号e8よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第1レジスタ41の要素e8を削除する。一方、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番1である。これにより、出力順保証部32cは、図9の状態3を継続する。

【0076】

さらに、次のクロック(時刻t5)で、出力順保証部32cは、次の要素e9を競合調停部31から受け取って、当該要素e9を第1レジスタ40に保持する。このとき、第2レジスタ41は要素e11を継続的に保持している。そして、判定部42は、比較部43の比較結果に基づいて、第2レジスタ41の要素番号e11が第1レジスタ40の要素番号e9よりも大きく、かつ、比較部44の比較結果により、第1レジスタ40と第2レジスタ41の各要素のアドレスが一致していることを検知する。これにより、判定部42は、図10に示される動作規定に従って、第1レジスタ41の要素e9を削除する。一方、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番2である。これにより、出力順保証部32cは、図9の状態3から状態4に遷移する。これにより、判定部42は、アドレス・要素番号の監視動作を終了する。

【0077】

さらに、次のクロック(時刻t6)において、出力順保証部32c(判定部42)は、第1レジスタ40の要素e11を、第2レジスタ41に転送する。これにより、第1レジスタ40には要素が保持されていない状態になる。このため、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番5になるから、出力順保証部32cは、図9の状態4から状態1に遷移する。なお、要素e11が第2レジスタ41に遷移したときに、別のグループの要素が第1レジスタ40に保持される場合が想定される。この場合には、第1レジスタ40と第2レジスタ41の要素のデータS,Eの組み合わせは、図8の項番6あるいは項番7である。この場合には、出力順保証部32cは、図9の状態4から状態2あるいは状態5に遷移する。

【0078】

さらに、次のクロック(時刻t7)において、出力順保証部32cは、第2レジスタ41の要素e11を記憶装置23に向けて出力する。

【0079】

上記同様に、他の出力順保証部32a,32b,32dも動作して、時刻t7において、各出力順保証部32a,32b,32dは、要素e3,e7,e15をそれぞれ記憶装置23に向けて出力する。

【0080】

上記のように、データ転送装置22は、時刻t7で要素を出力するが、間接参照に関わる要素(データ)の記憶装置23への転送処理においては、時刻t4から時刻t7に掛けて出力していると等価な状態となる。つまり、この場合においても、データ転送装置22は、4クロック(4T)で、一グループの16個の要素を記憶装置23に転送する。

【0081】

上記のように、第2実施形態のデータ転送装置22は、連続アドレスのメモリアクセス命令だけでなく、間接参照のアドレスのメモリアクセス命令に基づいた要素の転送に関しても、前記同様に、転送速度を改善できる。これにより、この第2実施形態のデータ転送装置22を備えた演算装置20は、演算時間を短縮できる。このような演算装置20は、例えば、画像処理を行う装置に組み込んで、その効果をよりs発揮することができる。

【0082】

(第3実施形態)

以下に、本発明に係る第3実施形態を説明する。なお、この第3実施形態の説明において、第2実施形態と同様な構成部分には同一符号を付し、その共通部分の重複説明は省略する。

【0083】

図14は、第3実施形態において特徴的な出力順保証部32’(32a’〜32d’)の構成を示したブロック図である。この第3実施形態では、出力順保証部32’は、第2レジスタとして、複数のレジスタ411,・・・41n(nは、2以上の整数)を有している。さらに、出力順保証部32’は、複数の比較部431,・・・43n(nは、2以上の整数)を有している。これら比較部431,・・・43nは、それぞれ、第1レジスタ40に保持されている要素の番号と、レジスタ411〜41nのうちの対応する一つのレジスタに保持されている要素の番号とを比較し、それら要素番号の大小関係を示す信号を出力する機能を備えている。さらにまた、出力順保証部32’は、複数の比較部441,・・・44n(nは、2以上の整数)をも有している。これら比較部441,・・・44nは、それぞれ、第2レジスタであるレジスタ411〜41nのうちの対応する一つのレジスタに保持されている要素のアドレスと、第1レジスタ40に保持されている要素のアドレスとを比較する。そして、各比較部441,・・・44nは、アドレスの一致・不一致を示す信号を出力する機能を備えている。

【0084】

この第3実施形態における上記以外の構成は、第2実施形態と同様である。

【0085】

この第3実施形態のデータ転送装置22は、上記の如く、出力順保証部以外の構成は、第2実施形態と同様である。これにより、この第3実施形態のデータ転送装置22における、出力順保証が不要な連続アドレスのメモリアクセス命令に基づいた要素の転送動作は、第2実施形態と同様である。このため、ここでは、その説明は省略する。

【0086】

図15は、この第3実施形態における、間接参照のアドレスのメモリアクセス命令に基づく要素の流れの一例を示したタイムチャートである。この図15を参照しながら、第3実施形態における出力順保証部32’の動作の一例を説明する。前提条件として、要素e0〜e3の格納位置は、それぞれ、0番地、8番地、16番地、0番地(何れも記憶部251)、要素e4〜e7の格納位置は、それぞれ、32番地、40番地、48番地、32番地(何れも記憶部252)、要素e8〜e11の格納位置はそれぞれ、64番地、72番地、80番地、64番地(何れも記憶部253)、要素e12〜e15の格納位置は、それぞれ、96番地、104番地、112番地、96番地(何れも記憶部254)であるとする。また、演算部21は、要素e0〜e3を、並列的に、かつ、互いに異なる演算パス26(26a〜26d)を通して、データ転送装置22に出力する。さらに、演算部21は、上記同様に、要素e4〜e7の組と、要素e8〜e11の組と、要素e12〜e15の組とを、順次、1クロック毎に、データ転送装置22に出力することとする。

【0087】

この第3実施形態においても、第2実施形態と同様に、図15に示す時刻t2において、競合調停部31は、4個の要素e0,e13,e10,e7を、並列的に、出力する。それら要素e0,e13,e10,e7は、それぞれ、対応する出力順保証部32a’〜32d’に入力する。出力順保証部32’の動作の説明を、分かり易くするために、ここでは、出力順保証部32c’に着目して説明する。

【0088】

出力順保証部32c’は、要素e10が入力すると(時刻t2)、当該要素e10を第1レジスタ40に保持する。

【0089】

次のクロック(時刻t3)において、出力順保証部32c’は、要素e10を第1レジスタ40から第2レジスタ411に転送し、また、入力してきた要素e11を第1レジスタ40に保持する。そして、判定部42は、比較部441の比較結果により、第1レジスタ40の要素e11のアドレスと、第2レジスタ411の要素e10のアドレスとが不一致であることを検知する。なお、図15では、出力順保証部32c’の第2レジスタの保持状態のみ図示している。

【0090】

次のクロック(時刻t4)において、判定部42は、上記アドレスの比較結果および図16に示す動作規定に従って、第2レジスタ411の要素e10はそのまま保持した状態で、第1レジスタ40の要素e11を、空いている第2レジスタ412に転送する。また、出力順保証部32c’は、次に入力してきた要素e8を第1レジスタ40に保持する。そして、判定部42は、第1レジスタ40の要素e8と、第2レジスタ411の要素e10とのアドレスが一致していることを検知する。また、判定部42は、第2レジスタ411の要素番号e10が、第1レジスタ40の要素番号e8よりも大きいことを検知する。これにより、判定部42は、図16の動作規定に従って、要素番号e8を削除する。

【0091】

次のクロック(時刻t5)において、出力順保証部32c’は、入力してきた要素e9を第1レジスタ40に保持する。そして、判定部42は、比較部441の比較結果により、第1レジスタ40の要素e11のアドレスと、第2レジスタ411の要素e10のアドレスとが不一致であることを検知する。これにより、判定部42は、図16の動作規定に従って、第1レジスタ40の要素e9を空き第2レジスタ413に転送する。

【0092】

同じグループの要素の入力は要素e9が最後であることから、次のクロック(時刻t6)以降、出力順保証部32cは、第2レジスタ411,412,413に保持されている要素e9,e10,e8を順次、記憶装置23に向けて出力する。

【0093】

この第3実施形態においても、第2実施形態と同様に、一グループの16個の要素をデータ転送装置22から記憶装置23に転送するのに要する時間は、4クロック(4T)である。つまり、この第3実施形態のデータ転送装置22においても、第2実施形態と同様に、競合調停部31で、競合調停を行わずに済む構成を備えているので、転送時間の低下(スループットの悪化)を防止できる。

【0094】

さらに、この第3実施形態では、出力順保証部32’は、第2レジスタとして、複数のレジスタを有している。このため、演算部21から並列的に出力される複数の要素の中の一部に、格納位置が同じ複数の要素が含まれている場合においても、順序保証を行うことが可能になる。

【0095】

なお、この発明は、第1〜第3の各実施の形態に限定されるものではなく、様々な実施の形態を採り得る。例えば、第2や第3の実施形態では、記憶装置23の記憶部25は4個であったが、記憶装置23が有する記憶部25の数は、4個に限定されず、4個以外の複数の記憶部25を設けてもよい。

【符号の説明】

【0096】

1,22 データ転送装置

2,35 一時保存部

3,29 順序制御部

4 データ読み出し部

5 転送制御部

10,20 演算装置

11,21 演算部

12,23 記憶装置

31 競合調停部

32 出力順保証部

34 範囲情報添付部

36 出力制御部

【特許請求の範囲】

【請求項1】

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部にそれぞれ対応し、かつ、当該データ入力部を通った前記データをそれぞれ保存する複数の一時保存部と、

一グループを構成する複数の前記データがそれぞれ前記各データ入力部を通って前記各一時保存部に分散保存された場合に、前記各一時保存部から、並列に、同じグループの前記データを読み出すデータ読み出し部と、

前記転送先に関連付けられている複数のデータ出力部に接続し、前記データ読み出し部により読み出された前記データを、当該データのアドレス情報に基づいた転送先に対応する前記データ出力部に向けて出力する転送制御部と、

前記データ読み出し部によって前記各一時保存部から並列に読み出される前記各データの転送先に対応する前記データ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定する順序制御部と、

を有しているデータ転送装置。

【請求項2】

前記各データには、同じグループ内において互いに異なる番号の情報がさらに添付されており、

その番号情報に基づいて、前記転送制御部から前記データ出力部に向けて出力された同じグループの前記データの並び換えを行う機能を備えている出力順保証部をさらに有する請求項1記載のデータ転送装置。

【請求項3】

前記出力順保証部は、転送先が同じ複数の前記データが同じグループ内にある場合には、それら転送先が同じ前記データの中から予め与えられた条件に適合する前記データを選択して前記データ出力部に向けて出力するデータ選択機能をさらに備えている請求項2記載のデータ転送装置。

【請求項4】

前記一時保存部からの読み出し順に関する情報を前記各データに添付する範囲情報添付部をさらに有し、

前記出力順保証部は、前記読み出し順に関する情報に基づいた範囲内の複数の前記データの並び換え又はデータ選択を行う前記機能を実行する請求項2又は請求項3記載のデータ転送装置。

【請求項5】

前記出力順保証部は、前記データを保持する複数のデータ保持部を有する請求項2又は請求項3又は請求項4記載のデータ転送装置。

【請求項6】

演算処理を行う演算部と、

複数の記憶部を有する記憶装置と、

前記演算部から出力されたデータを前記記憶装置に転送する請求項1乃至請求項5の何れか一つに記載のデータ転送装置と

を有する演算装置。

【請求項7】

前記演算部は、ベクトル演算を行う機能を備えている請求項6記載の演算装置。

【請求項8】

請求項6又は請求項7記載の演算装置を備えた装置。

【請求項9】

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部をそれぞれ通って、一グループを構成する複数の前記データが入力された場合に、それらデータを、前記各データ入力部にそれぞれ対応する一時保存部に分散保存し、

前記各一時保存部から並列に読み出される前記各データの転送先に対応するデータ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定し、

その設定された読み出し順に従って、前記各一時保存部から、並列に、同じグループの前記データを読み出して転送先に向けて出力するデータ転送方法。

【請求項1】

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部にそれぞれ対応し、かつ、当該データ入力部を通った前記データをそれぞれ保存する複数の一時保存部と、

一グループを構成する複数の前記データがそれぞれ前記各データ入力部を通って前記各一時保存部に分散保存された場合に、前記各一時保存部から、並列に、同じグループの前記データを読み出すデータ読み出し部と、

前記転送先に関連付けられている複数のデータ出力部に接続し、前記データ読み出し部により読み出された前記データを、当該データのアドレス情報に基づいた転送先に対応する前記データ出力部に向けて出力する転送制御部と、

前記データ読み出し部によって前記各一時保存部から並列に読み出される前記各データの転送先に対応する前記データ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定する順序制御部と、

を有しているデータ転送装置。

【請求項2】

前記各データには、同じグループ内において互いに異なる番号の情報がさらに添付されており、

その番号情報に基づいて、前記転送制御部から前記データ出力部に向けて出力された同じグループの前記データの並び換えを行う機能を備えている出力順保証部をさらに有する請求項1記載のデータ転送装置。

【請求項3】

前記出力順保証部は、転送先が同じ複数の前記データが同じグループ内にある場合には、それら転送先が同じ前記データの中から予め与えられた条件に適合する前記データを選択して前記データ出力部に向けて出力するデータ選択機能をさらに備えている請求項2記載のデータ転送装置。

【請求項4】

前記一時保存部からの読み出し順に関する情報を前記各データに添付する範囲情報添付部をさらに有し、

前記出力順保証部は、前記読み出し順に関する情報に基づいた範囲内の複数の前記データの並び換え又はデータ選択を行う前記機能を実行する請求項2又は請求項3記載のデータ転送装置。

【請求項5】

前記出力順保証部は、前記データを保持する複数のデータ保持部を有する請求項2又は請求項3又は請求項4記載のデータ転送装置。

【請求項6】

演算処理を行う演算部と、

複数の記憶部を有する記憶装置と、

前記演算部から出力されたデータを前記記憶装置に転送する請求項1乃至請求項5の何れか一つに記載のデータ転送装置と

を有する演算装置。

【請求項7】

前記演算部は、ベクトル演算を行う機能を備えている請求項6記載の演算装置。

【請求項8】

請求項6又は請求項7記載の演算装置を備えた装置。

【請求項9】

転送先の格納位置を示すアドレス情報付きのデータが入力される複数のデータ入力部をそれぞれ通って、一グループを構成する複数の前記データが入力された場合に、それらデータを、前記各データ入力部にそれぞれ対応する一時保存部に分散保存し、

前記各一時保存部から並列に読み出される前記各データの転送先に対応するデータ出力部が互いに異なるように、前記一時保存部毎に同じグループの前記データの読み出し順を設定し、

その設定された読み出し順に従って、前記各一時保存部から、並列に、同じグループの前記データを読み出して転送先に向けて出力するデータ転送方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−99004(P2012−99004A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2010−247570(P2010−247570)

【出願日】平成22年11月4日(2010.11.4)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成22年11月4日(2010.11.4)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]