トランジスタおよびメモリアレイ

【課題】大きな順方向−逆方向電流比を有するスイッチングデバイスを提供する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【解決手段】トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、スイッチングデバイスのさまざまな実施形態に向けられ、より特定的には、トランジスタに向けられる。

【背景技術】

【0002】

背景

不揮発性メモリ技術は着実に進歩しており、三次元(3D)アレイが、望まれる高密度を達成するための最良の選択肢であり得るというポイントまで到達した。大きな順方向−逆方向電流比を有するスイッチングデバイスは、より簡単にメモリセルの3D積層を可能にする。多くの標準的な半導体スイッチは、必要とされる比率を提供せず、かつ、メモリ装置製造には相容れない高温処理を必要とし得る。したがって、新しいスイッチングデバイスの必要性が残されている。

【発明の概要】

【課題を解決するための手段】

【0003】

簡単な要約

本開示の1つの特定の実施形態は、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含むトランジスタである。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【0004】

本開示のほかの特定の実施形態は、複数のメモリユニットを含む第1のメモリアレイ層を含み、各メモリユニットはメモリセルに電気的に結合されたトランジスタを有する。実施形態は、複数のメモリユニットを含む第2のメモリアレイ層を含み、各メモリユニットはメモリセルに電気的に結合されたトランジスタを有する。トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【0005】

本開示のさらに他の特定の実施形態は、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含むトランジスタである。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。そして、ソースバリヤおよびドレインバリヤは、それらがゲートに近接するよりもアイランドにより薄く近接する。

【0006】

これらのおよびさまざまな他の特徴および利点は、以下の詳細な説明を読むことによって明らかになるであろう。

【0007】

本開示は、添付の図面に関連する本開示のさまざまな実施形態についての以下の詳細な説明を考慮して、より完全に理解され得る。

【図面の簡単な説明】

【0008】

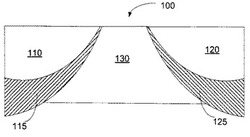

【図1A】開示されるトランジスタの例示的な実施形態の概略図である。

【図1B】開示されるトランジスタの他の例示的な実施形態の概略図である。

【図2A】バイアスがなく、かつゲート電位が印加されていない場合の、電気的バンド配列の概略図である。

【図2B】バイアスがあり、かつゲート電位が印加されていない場合の、電気的バンド配列の概略図である。

【図2C】バイアスがなく、かつゲート電位が印加されている場合の、電気的バンド配列の概略図である。

【図3】縦型構造を有する開示されたトランジスタの例示的な実施形態の概略図である。

【図4】例示的な3Dメモリアレイの分解斜視概略図である。

【発明を実施するための形態】

【0009】

図は、必ずしも縮尺とおりではない。図において用いられる同じ符合は、同じ要素を参照する。しかしながら、所与の図において要素を参照するための符号の使用は、同じ符号で表示される他の図の要素を限定することを意図したものではないことが理解されるであろう。

【0010】

詳細な説明

本開示は、スイッチングデバイスのさまざまな実施形態に向けられ、より特定的には、トランジスタに向けられる。

【0011】

以下の説明においては、本明細書の一部を形成する一組の添付の図面が参照され、それにおいては、いくつかの特定の実施形態が例示として示される。他の実施形態が、本開示の範囲または精神から逸脱することなく予期され、かつなされることが理解されるべきである。したがって、以下の詳細な説明は、限定の意味で採用されるべきではない。本明細書で与えられる任意の定義は、本明細書で頻繁に用いられる特定の用語の理解を容易にするためのものであり、本開示の範囲を制限することを意図したものではない。

【0012】

特にそうでないと示されない場合は、明細書および特許請求の範囲で用いられるフィーチャサイズ、量、および物理的特性を表現するすべての数値は、「約(about)」の語句によって、全ての事例において修正されるものとして理解されるべきである。したがって、反対であることが示されない場合には、先の明細書および添付の特許請求の範囲に記載される数値パラメータは、本明細書に開示される技術を利用して当業者が取得しようとする所望の特性に応じて変化し得る概算値である。

【0013】

本明細書および添付の特許請求の範囲において用いられるように、単数形式の「a」、「an」および「the」は、そうでないと明確に示されていない場合は、複数の参照を有する実施形態を包含する。本明細書および添付の特許請求の範囲において用いられるように、用語「または(or)」は、そうでないと明確に示されていない場合は、一般的に「および/または(and/or)」を含む意味で採用される。

【0014】

本開示はあまり限定されないが、本開示のさまざまな局面の用途は、以下に提供される例の議論を通して増加されるであろう。

【0015】

図1Aは、ソース110と、ドレイン120と、ゲート領域130と、ソースバリヤ115と、ドレインバリヤ125とを含む例示的なトランジスタ100を示す。本明細書においては示されていないが、トランジスタ100は、基板上または基板内に形成され得る。一般的に、ゲート領域130は、ソース110とドレイン120との間に配置される。開示されたトランジスタは、ソースバリヤ115およびドレインバリヤ125も含む。ソースバリヤ115はソースをゲート領域130から分離し、ドレインバリヤ125はドレインをゲート領域130から分離する。ソースバリヤ115およびドレインバリヤ125は、ソース110およびドレイン120をそれぞれゲート領域から物理的に分離し、ソース110およびドレイン120をそれぞれゲート領域から電気的に分離し、または、ソース110およびドレイン120をそれぞれゲート領域から物理的かつ電気的の双方に分離し得る。

【0016】

図1Bは、ゲート領域130をより詳細に示す、他の例示的なトランジスタ100を示す。ゲート領域130は、より具体的には、アイランド140と、ゲート酸化物150と、ゲート160とを含み得る。一般的に、ゲート酸化物150は、アイランド140とゲート160との間に配置される。ゲート酸化物150は、アイランド140をゲート160から物理的に分離し、アイランド140をゲート160から電気的に分離し、または、アイランド140をゲート160から物理的かつ電気的の双方に分離し得る。実施形態においては、ゲート160、ゲート酸化物150、およびアイランド140は、ゲート領域130に対するソース110およびドレイン120の相対位置に垂直な(または直交する)方向に積層され得る。

【0017】

ゲート160およびアイランド140は、互いに同時活性的に結合される。実施形態においては、ゲート160は、ゲート酸化物150を通してアイランド140に同時活性的に結合される。「同時活性的に結合される」2つの構造は、概して、2つの構造がそれらの振る舞いにおいて接続されることを意味する。実施形態においては、(ゲート160およびアイランド140のような)2つの構造は、電気的に同時活性的に結合され、これは、2つの構造の電気的な振る舞いが接続されることを意味する。たとえば、正の電荷を一方の構造に印加することは、他方の構造に負の電荷を誘発し得る。実施形態においては、ゲート160への(正または負のいずれかの)電荷の印加は、ゲート160にもっとも近接しているアイランド140の領域に、反対の電荷(負または正のいずれか)を増大させる。実施形態においては、ゲート上に印加されたバイアスは、ゲート酸化物に近接する領域に、電荷キャリア(電子またはホール)の蓄積を生成し得る。電荷キャリアの蓄積は、反対の端部のアイランドの領域において電荷キャリアを枯渇させる。したがって、この枯渇した領域のバンド構造は変化し、エネルギバリヤの増加をもたらし得る。

【0018】

ソース110およびドレイン120は、概して、n型またはp型のいずれかにドープされたシリコン(Si)で作られる。ソース110およびドレイン120は、概して、両方n型、または両方p型のいずれかにドープされたシリコンである。ゲート160は、概して、金属、金属酸化物、またはポリシリコンで作られ得る。ゲート160に用いられ得る例示的な金属は、タンタラム、タングステン、窒化タンタラム、および窒化チタンのような、適切なバンドギャップを有する金属を含む。ゲート160に用いられ得る例示的な金属酸化物は、ルテニウム酸化物、SrRuO3、CaRuO3、および(Sr,Ca)RuO3を含み得る。ポリシリコンがゲート160のために用いられる実施形態においては、そのポリシリコンは、高度にドープされたポリシリコンであり得る。ゲート酸化物150は、概して、二酸化ケイ素(SiO2)、または(SiO2に比べて)高い誘電率(k)を有する材料で作られ得る。例示的な高k材料は、二酸化ジルコニウム(ZrO2)、酸化イットリウム(Y2O3)、二酸化ハフニウム(HfO2)、およびシリコン酸窒化物(SiOxNy)を含み得る。(上記で列挙したもののような)高k材料の固溶体も、ゲート酸化物のために利用され得る。ソースバリヤ115およびドレインバリヤ125は、概して、SiO2、または(SiO2に比べて)高い誘電率(k)を有する材料で作られ得る。例示的な高k材料は、ZrO2、Y2O3)、HfO2、およびSiOxNyを含み得る。(上記で列挙したもののような)高k材料の固溶体も、ソースバリヤ115およびドレインバリヤ125のために利用され得る。アイランド140は、概して、特定レベルのキャリア集中を有する適切にドープされたシリコンで作られ、実施形態においては、シリコンは、縮退レベルまでドープされ得る。アイランド140は、概して、n型またはp型のドープSi、または半導体酸化物で作られ得る。例示的な半導体酸化物は、酸化スズ(SnO)、非化学量的(non-stoichiometric)酸化スズ(Sn2O3)、および酸化インジウム(In2O3)を含み得る。(上記で列挙したもののような)半導体酸化物の固溶体も、アイランド140のために利用され得る。

【0019】

実施形態においては、ゲート160は縮退ポリシリコンで作られ得る。実施形態においては、ゲート酸化物150はSiO2で作られ得る。実施形態においては、ソースバリヤ115およびドレインバリヤ125は、SiO2で作られ得る。実施形態においては、アイランド140は、ドープSiで作られ得る。実施形態においては、ゲート160は、縮退ポリシリコンで作られ、ゲート酸化物150はSiO2で作られ、ソースバリヤ115およびドレインバリヤ125はSiO2で作られ、アイランド140はドープSiで作られ得る。

【0020】

本明細書で開示されるトランジスタは、金属酸化物半導体電界効果(MOSFET)を利用する。図2Aは、バイアスが0Vでありゲート電位が0Vである場合の、例示的なトランジスタのエネルギバンド図を示す。ゲートへ印加される任意の電位(または、しきい値電圧未満)を用いないことによって、たとえ、アイランドのエネルギバリヤ(中間の領域)が低くても、(ポテンシャルエネルギの高さによって示されるように)電気バリヤが高いので、ソースとドレインとの間で、いずれの方向へもほとんどまたは全く導通しない。図2Bは、バイアスが0Vより大きく、かつゲート電位が0V(または、しきい値電圧未満)である場合の、例示的なトランジスタのエネルギバンド図を示す。ここで見られるように、ドレインバリヤの電気バリヤは、ドレインからソースへ、電気的に下り坂であるが、依然としてトンネリング電流を停止するように寄与する。

【0021】

図2Cは、バイアスが0Vであり、かつゲート電位がしきい値電圧以上である場合の、例示的なトランジスタのエネルギバンド図を示す。正のゲート電位の印加は、同時活性的に結合されたゲートおよびアイランドであるので、アイランド内の電子をゲート酸化物に向かって引き込む。これは、次に、ソースからドレインへトンネリングする電子に対するバリヤを低減する。これは、図2Cにおいて、アイランドについての低減されたエネルギレベルによって示される。ゲート電位がしきい値電圧より大きい場合およびより小さい場合のバリヤの物理的厚さの大きな差は、順方向電流と逆方向電流との間の大きな比率を生成する。

【0022】

実施形態においては、ソースバリヤおよびドレインバリヤは、変化する厚さを有する。実施形態においては、ソースバリヤおよびドレインバリヤは、それらがゲートと近接しているよりも、アイランドへより薄く近接し得る。図1Bに見られるように、(たとえば)ソースバリヤ115は、ソース110をアイランド140から分離するところが、ソース110をゲート160から分離するところよりも薄い。実施形態においては、ソースバリヤ115およびドレインバリヤ125は、2倍の係数で、ゲート160に近接するよりもアイランド140に薄く近接し得る厚さを有し得る。このような変化する厚さは、ソースバリヤおよびドレインバリヤを作りあげる前駆体物質の、たとえば、イオンミリングを通して生成され得る。ゲートよりもアイランドに薄く近接するソースバリヤおよびドレインバリヤを有することは、トンネリング電流が存在する、より薄いチャネルを生成し得る。これは、ゲート酸化物に近い領域を通した大きな漏れ電流を防止し得る。

【0023】

図3は、開示されるトランジスタの他の例示的な実施形態を示す。この例示的なトランジスタ300は、概して、上述と同じ構成要素を含み、ソース310と、ドレイン320と、ゲート酸化物350によって分離されるゲート360およびアイランド340を含むゲート領域330と、ソースバリヤ315と、ドレインバリヤ325とを含む。要素の材料および特性は、概して、上述のものと同じであり得る。ソース310、ソースバリヤ315、アイランド340、ドレインバリヤ325、およびドレイン320は、積層されるものとして特徴付けられ得る。一実施形態においては、これらの要素は、基板上に縦型構造に積層され得る。ゲート領域330は、先に示した積層された要素の一部分上に積層され、それによって、ソースバリヤ315およびドレインバリヤ325は、それぞれソース310およびドレイン320を、ゲート領域330から分離する。例示的な一実施形態において、ゲート領域330の少なくともアイランド340が、ソースバリヤ315およびドレインバリヤ325に接する。他の例示的な実施形態においては、ゲート領域330のアイランド340のみが、ソースバリヤ315およびドレインバリヤ325に接する必要があり、ゲート酸化物350およびゲート360はスタックの残りの部分から変位され得る。このような実施形態においては、ゲート360は、ゲート酸化物350には接するが、ソースバリヤ315またはドレインバリヤ325には接しない。実施形態においては、ゲート360は、ゲート酸化物350には接するが、(もしあれば、基板を除く)トランジスタ300の他の要素には接しない。

【0024】

このような例示的なトランジスタは、(図1Aおよび図1Bに示された実施形態よりも)より大きな接合表面および電流を産み出し、それは、より大きな順方向電流密度をもたらす。図3に示されるもののような実施形態においては、ソースバリヤは、ドレインバリヤよりも厚くすることができるが、それは必ずしも必要ではない。異なる厚みを有するソースバリヤおよびドレインバリヤを有することは、(図3に示される例示的な実施形態において、ドレインバリヤ325の面積をソースバリヤ315の面積と比較して)、存在し得る異なる接合面積を補償するように機能し得る。

【0025】

図4は、例示的な3Dメモリアレイ200の分解斜視概略図である。3Dメモリアレイ200は、メモリアレイ200を形成するために連続的に積層された複数のメモリアレイ層210,211,212,213を含み得る。3Dメモリアレイ200は、ベース回路層202も任意的に含み得る。各メモリアレイ層210,211,212,213は、ベース回路層202に電気的に結合され得る。各メモリアレイ層210,211,212,213は、上述のように、メモリセル224に電気的に結合されるトランジスタ222を含む複数のメモリユニット220を含み得る。各メモリユニット220は、クロスポイント構造を形成する行ラインおよび列ラインの交点に配置され得る。

【0026】

メモリセル224は、スピントルクトランスファランダムアクセスメモリ(STRAM)セル、または抵抗性ランダムアクセスメモリ(RRAM(登録商標))セルであり得る。複数のメモリアレイ層210,211,212,213は、層の各々が互いに電気的に絶縁された形態である、同一平面配列で積層され得る。複数のメモリアレイ層210,211,212,213の各々は、ベース回路層202に電気的に結合されるとともに、ベース回路層202によって動作され得る。

【0027】

このように、「トンネリングトランジスタ」の実施形態が開示される。上記実行例および他の実行例は、以下の請求項の範囲内である。本開示は、これらの開示されたもの以外の実施形態によっても実現できることが、当業者は理解できるであろう。開示された実施形態は、例示の目的のために提示されており、限定ではなく、本開示は以下の特許請求の範囲によってのみ限定される。

【符号の説明】

【0028】

100,300 トランジスタ、110,310 ソース、115,315 ソースバリヤ、120,320 ドレイン、125,325 ドレインバリヤ、130,330 ゲート領 、140,340 アイランド、150,350 ゲート酸化物、160,360 ゲート、200 メモリアレイ、202 ベース回路層、210,211,212,213 メモリアレイ層、220 メモリユニット、224 メモリセル。

【技術分野】

【0001】

本開示は、スイッチングデバイスのさまざまな実施形態に向けられ、より特定的には、トランジスタに向けられる。

【背景技術】

【0002】

背景

不揮発性メモリ技術は着実に進歩しており、三次元(3D)アレイが、望まれる高密度を達成するための最良の選択肢であり得るというポイントまで到達した。大きな順方向−逆方向電流比を有するスイッチングデバイスは、より簡単にメモリセルの3D積層を可能にする。多くの標準的な半導体スイッチは、必要とされる比率を提供せず、かつ、メモリ装置製造には相容れない高温処理を必要とし得る。したがって、新しいスイッチングデバイスの必要性が残されている。

【発明の概要】

【課題を解決するための手段】

【0003】

簡単な要約

本開示の1つの特定の実施形態は、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含むトランジスタである。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【0004】

本開示のほかの特定の実施形態は、複数のメモリユニットを含む第1のメモリアレイ層を含み、各メモリユニットはメモリセルに電気的に結合されたトランジスタを有する。実施形態は、複数のメモリユニットを含む第2のメモリアレイ層を含み、各メモリユニットはメモリセルに電気的に結合されたトランジスタを有する。トランジスタは、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含む。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。

【0005】

本開示のさらに他の特定の実施形態は、ソースと、ドレインと、ゲート領域と、ソースバリヤと、ドレインバリヤとを含むトランジスタである。ゲート領域は、ゲートと、アイランドと、ゲート酸化物とを含み、ゲート酸化物は、ゲートとアイランドとの間に配置される。ゲートおよびアイランドは、互いに、同時活性的に結合される。ソースバリヤはゲート領域からソースを分離し、ドレインバリヤはゲート領域からドレインを分離する。そして、ソースバリヤおよびドレインバリヤは、それらがゲートに近接するよりもアイランドにより薄く近接する。

【0006】

これらのおよびさまざまな他の特徴および利点は、以下の詳細な説明を読むことによって明らかになるであろう。

【0007】

本開示は、添付の図面に関連する本開示のさまざまな実施形態についての以下の詳細な説明を考慮して、より完全に理解され得る。

【図面の簡単な説明】

【0008】

【図1A】開示されるトランジスタの例示的な実施形態の概略図である。

【図1B】開示されるトランジスタの他の例示的な実施形態の概略図である。

【図2A】バイアスがなく、かつゲート電位が印加されていない場合の、電気的バンド配列の概略図である。

【図2B】バイアスがあり、かつゲート電位が印加されていない場合の、電気的バンド配列の概略図である。

【図2C】バイアスがなく、かつゲート電位が印加されている場合の、電気的バンド配列の概略図である。

【図3】縦型構造を有する開示されたトランジスタの例示的な実施形態の概略図である。

【図4】例示的な3Dメモリアレイの分解斜視概略図である。

【発明を実施するための形態】

【0009】

図は、必ずしも縮尺とおりではない。図において用いられる同じ符合は、同じ要素を参照する。しかしながら、所与の図において要素を参照するための符号の使用は、同じ符号で表示される他の図の要素を限定することを意図したものではないことが理解されるであろう。

【0010】

詳細な説明

本開示は、スイッチングデバイスのさまざまな実施形態に向けられ、より特定的には、トランジスタに向けられる。

【0011】

以下の説明においては、本明細書の一部を形成する一組の添付の図面が参照され、それにおいては、いくつかの特定の実施形態が例示として示される。他の実施形態が、本開示の範囲または精神から逸脱することなく予期され、かつなされることが理解されるべきである。したがって、以下の詳細な説明は、限定の意味で採用されるべきではない。本明細書で与えられる任意の定義は、本明細書で頻繁に用いられる特定の用語の理解を容易にするためのものであり、本開示の範囲を制限することを意図したものではない。

【0012】

特にそうでないと示されない場合は、明細書および特許請求の範囲で用いられるフィーチャサイズ、量、および物理的特性を表現するすべての数値は、「約(about)」の語句によって、全ての事例において修正されるものとして理解されるべきである。したがって、反対であることが示されない場合には、先の明細書および添付の特許請求の範囲に記載される数値パラメータは、本明細書に開示される技術を利用して当業者が取得しようとする所望の特性に応じて変化し得る概算値である。

【0013】

本明細書および添付の特許請求の範囲において用いられるように、単数形式の「a」、「an」および「the」は、そうでないと明確に示されていない場合は、複数の参照を有する実施形態を包含する。本明細書および添付の特許請求の範囲において用いられるように、用語「または(or)」は、そうでないと明確に示されていない場合は、一般的に「および/または(and/or)」を含む意味で採用される。

【0014】

本開示はあまり限定されないが、本開示のさまざまな局面の用途は、以下に提供される例の議論を通して増加されるであろう。

【0015】

図1Aは、ソース110と、ドレイン120と、ゲート領域130と、ソースバリヤ115と、ドレインバリヤ125とを含む例示的なトランジスタ100を示す。本明細書においては示されていないが、トランジスタ100は、基板上または基板内に形成され得る。一般的に、ゲート領域130は、ソース110とドレイン120との間に配置される。開示されたトランジスタは、ソースバリヤ115およびドレインバリヤ125も含む。ソースバリヤ115はソースをゲート領域130から分離し、ドレインバリヤ125はドレインをゲート領域130から分離する。ソースバリヤ115およびドレインバリヤ125は、ソース110およびドレイン120をそれぞれゲート領域から物理的に分離し、ソース110およびドレイン120をそれぞれゲート領域から電気的に分離し、または、ソース110およびドレイン120をそれぞれゲート領域から物理的かつ電気的の双方に分離し得る。

【0016】

図1Bは、ゲート領域130をより詳細に示す、他の例示的なトランジスタ100を示す。ゲート領域130は、より具体的には、アイランド140と、ゲート酸化物150と、ゲート160とを含み得る。一般的に、ゲート酸化物150は、アイランド140とゲート160との間に配置される。ゲート酸化物150は、アイランド140をゲート160から物理的に分離し、アイランド140をゲート160から電気的に分離し、または、アイランド140をゲート160から物理的かつ電気的の双方に分離し得る。実施形態においては、ゲート160、ゲート酸化物150、およびアイランド140は、ゲート領域130に対するソース110およびドレイン120の相対位置に垂直な(または直交する)方向に積層され得る。

【0017】

ゲート160およびアイランド140は、互いに同時活性的に結合される。実施形態においては、ゲート160は、ゲート酸化物150を通してアイランド140に同時活性的に結合される。「同時活性的に結合される」2つの構造は、概して、2つの構造がそれらの振る舞いにおいて接続されることを意味する。実施形態においては、(ゲート160およびアイランド140のような)2つの構造は、電気的に同時活性的に結合され、これは、2つの構造の電気的な振る舞いが接続されることを意味する。たとえば、正の電荷を一方の構造に印加することは、他方の構造に負の電荷を誘発し得る。実施形態においては、ゲート160への(正または負のいずれかの)電荷の印加は、ゲート160にもっとも近接しているアイランド140の領域に、反対の電荷(負または正のいずれか)を増大させる。実施形態においては、ゲート上に印加されたバイアスは、ゲート酸化物に近接する領域に、電荷キャリア(電子またはホール)の蓄積を生成し得る。電荷キャリアの蓄積は、反対の端部のアイランドの領域において電荷キャリアを枯渇させる。したがって、この枯渇した領域のバンド構造は変化し、エネルギバリヤの増加をもたらし得る。

【0018】

ソース110およびドレイン120は、概して、n型またはp型のいずれかにドープされたシリコン(Si)で作られる。ソース110およびドレイン120は、概して、両方n型、または両方p型のいずれかにドープされたシリコンである。ゲート160は、概して、金属、金属酸化物、またはポリシリコンで作られ得る。ゲート160に用いられ得る例示的な金属は、タンタラム、タングステン、窒化タンタラム、および窒化チタンのような、適切なバンドギャップを有する金属を含む。ゲート160に用いられ得る例示的な金属酸化物は、ルテニウム酸化物、SrRuO3、CaRuO3、および(Sr,Ca)RuO3を含み得る。ポリシリコンがゲート160のために用いられる実施形態においては、そのポリシリコンは、高度にドープされたポリシリコンであり得る。ゲート酸化物150は、概して、二酸化ケイ素(SiO2)、または(SiO2に比べて)高い誘電率(k)を有する材料で作られ得る。例示的な高k材料は、二酸化ジルコニウム(ZrO2)、酸化イットリウム(Y2O3)、二酸化ハフニウム(HfO2)、およびシリコン酸窒化物(SiOxNy)を含み得る。(上記で列挙したもののような)高k材料の固溶体も、ゲート酸化物のために利用され得る。ソースバリヤ115およびドレインバリヤ125は、概して、SiO2、または(SiO2に比べて)高い誘電率(k)を有する材料で作られ得る。例示的な高k材料は、ZrO2、Y2O3)、HfO2、およびSiOxNyを含み得る。(上記で列挙したもののような)高k材料の固溶体も、ソースバリヤ115およびドレインバリヤ125のために利用され得る。アイランド140は、概して、特定レベルのキャリア集中を有する適切にドープされたシリコンで作られ、実施形態においては、シリコンは、縮退レベルまでドープされ得る。アイランド140は、概して、n型またはp型のドープSi、または半導体酸化物で作られ得る。例示的な半導体酸化物は、酸化スズ(SnO)、非化学量的(non-stoichiometric)酸化スズ(Sn2O3)、および酸化インジウム(In2O3)を含み得る。(上記で列挙したもののような)半導体酸化物の固溶体も、アイランド140のために利用され得る。

【0019】

実施形態においては、ゲート160は縮退ポリシリコンで作られ得る。実施形態においては、ゲート酸化物150はSiO2で作られ得る。実施形態においては、ソースバリヤ115およびドレインバリヤ125は、SiO2で作られ得る。実施形態においては、アイランド140は、ドープSiで作られ得る。実施形態においては、ゲート160は、縮退ポリシリコンで作られ、ゲート酸化物150はSiO2で作られ、ソースバリヤ115およびドレインバリヤ125はSiO2で作られ、アイランド140はドープSiで作られ得る。

【0020】

本明細書で開示されるトランジスタは、金属酸化物半導体電界効果(MOSFET)を利用する。図2Aは、バイアスが0Vでありゲート電位が0Vである場合の、例示的なトランジスタのエネルギバンド図を示す。ゲートへ印加される任意の電位(または、しきい値電圧未満)を用いないことによって、たとえ、アイランドのエネルギバリヤ(中間の領域)が低くても、(ポテンシャルエネルギの高さによって示されるように)電気バリヤが高いので、ソースとドレインとの間で、いずれの方向へもほとんどまたは全く導通しない。図2Bは、バイアスが0Vより大きく、かつゲート電位が0V(または、しきい値電圧未満)である場合の、例示的なトランジスタのエネルギバンド図を示す。ここで見られるように、ドレインバリヤの電気バリヤは、ドレインからソースへ、電気的に下り坂であるが、依然としてトンネリング電流を停止するように寄与する。

【0021】

図2Cは、バイアスが0Vであり、かつゲート電位がしきい値電圧以上である場合の、例示的なトランジスタのエネルギバンド図を示す。正のゲート電位の印加は、同時活性的に結合されたゲートおよびアイランドであるので、アイランド内の電子をゲート酸化物に向かって引き込む。これは、次に、ソースからドレインへトンネリングする電子に対するバリヤを低減する。これは、図2Cにおいて、アイランドについての低減されたエネルギレベルによって示される。ゲート電位がしきい値電圧より大きい場合およびより小さい場合のバリヤの物理的厚さの大きな差は、順方向電流と逆方向電流との間の大きな比率を生成する。

【0022】

実施形態においては、ソースバリヤおよびドレインバリヤは、変化する厚さを有する。実施形態においては、ソースバリヤおよびドレインバリヤは、それらがゲートと近接しているよりも、アイランドへより薄く近接し得る。図1Bに見られるように、(たとえば)ソースバリヤ115は、ソース110をアイランド140から分離するところが、ソース110をゲート160から分離するところよりも薄い。実施形態においては、ソースバリヤ115およびドレインバリヤ125は、2倍の係数で、ゲート160に近接するよりもアイランド140に薄く近接し得る厚さを有し得る。このような変化する厚さは、ソースバリヤおよびドレインバリヤを作りあげる前駆体物質の、たとえば、イオンミリングを通して生成され得る。ゲートよりもアイランドに薄く近接するソースバリヤおよびドレインバリヤを有することは、トンネリング電流が存在する、より薄いチャネルを生成し得る。これは、ゲート酸化物に近い領域を通した大きな漏れ電流を防止し得る。

【0023】

図3は、開示されるトランジスタの他の例示的な実施形態を示す。この例示的なトランジスタ300は、概して、上述と同じ構成要素を含み、ソース310と、ドレイン320と、ゲート酸化物350によって分離されるゲート360およびアイランド340を含むゲート領域330と、ソースバリヤ315と、ドレインバリヤ325とを含む。要素の材料および特性は、概して、上述のものと同じであり得る。ソース310、ソースバリヤ315、アイランド340、ドレインバリヤ325、およびドレイン320は、積層されるものとして特徴付けられ得る。一実施形態においては、これらの要素は、基板上に縦型構造に積層され得る。ゲート領域330は、先に示した積層された要素の一部分上に積層され、それによって、ソースバリヤ315およびドレインバリヤ325は、それぞれソース310およびドレイン320を、ゲート領域330から分離する。例示的な一実施形態において、ゲート領域330の少なくともアイランド340が、ソースバリヤ315およびドレインバリヤ325に接する。他の例示的な実施形態においては、ゲート領域330のアイランド340のみが、ソースバリヤ315およびドレインバリヤ325に接する必要があり、ゲート酸化物350およびゲート360はスタックの残りの部分から変位され得る。このような実施形態においては、ゲート360は、ゲート酸化物350には接するが、ソースバリヤ315またはドレインバリヤ325には接しない。実施形態においては、ゲート360は、ゲート酸化物350には接するが、(もしあれば、基板を除く)トランジスタ300の他の要素には接しない。

【0024】

このような例示的なトランジスタは、(図1Aおよび図1Bに示された実施形態よりも)より大きな接合表面および電流を産み出し、それは、より大きな順方向電流密度をもたらす。図3に示されるもののような実施形態においては、ソースバリヤは、ドレインバリヤよりも厚くすることができるが、それは必ずしも必要ではない。異なる厚みを有するソースバリヤおよびドレインバリヤを有することは、(図3に示される例示的な実施形態において、ドレインバリヤ325の面積をソースバリヤ315の面積と比較して)、存在し得る異なる接合面積を補償するように機能し得る。

【0025】

図4は、例示的な3Dメモリアレイ200の分解斜視概略図である。3Dメモリアレイ200は、メモリアレイ200を形成するために連続的に積層された複数のメモリアレイ層210,211,212,213を含み得る。3Dメモリアレイ200は、ベース回路層202も任意的に含み得る。各メモリアレイ層210,211,212,213は、ベース回路層202に電気的に結合され得る。各メモリアレイ層210,211,212,213は、上述のように、メモリセル224に電気的に結合されるトランジスタ222を含む複数のメモリユニット220を含み得る。各メモリユニット220は、クロスポイント構造を形成する行ラインおよび列ラインの交点に配置され得る。

【0026】

メモリセル224は、スピントルクトランスファランダムアクセスメモリ(STRAM)セル、または抵抗性ランダムアクセスメモリ(RRAM(登録商標))セルであり得る。複数のメモリアレイ層210,211,212,213は、層の各々が互いに電気的に絶縁された形態である、同一平面配列で積層され得る。複数のメモリアレイ層210,211,212,213の各々は、ベース回路層202に電気的に結合されるとともに、ベース回路層202によって動作され得る。

【0027】

このように、「トンネリングトランジスタ」の実施形態が開示される。上記実行例および他の実行例は、以下の請求項の範囲内である。本開示は、これらの開示されたもの以外の実施形態によっても実現できることが、当業者は理解できるであろう。開示された実施形態は、例示の目的のために提示されており、限定ではなく、本開示は以下の特許請求の範囲によってのみ限定される。

【符号の説明】

【0028】

100,300 トランジスタ、110,310 ソース、115,315 ソースバリヤ、120,320 ドレイン、125,325 ドレインバリヤ、130,330 ゲート領 、140,340 アイランド、150,350 ゲート酸化物、160,360 ゲート、200 メモリアレイ、202 ベース回路層、210,211,212,213 メモリアレイ層、220 メモリユニット、224 メモリセル。

【特許請求の範囲】

【請求項1】

トランジスタであって、

ソースと、

ドレインと、

ゲート領域とを備え、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを含み、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに備え、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離する、トランジスタ。

【請求項2】

前記ソースバリヤおよび前記ドレインバリヤは、変化する厚みを有する、請求項1に記載のトランジスタ。

【請求項3】

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、請求項2に記載のトランジスタ。

【請求項4】

前記ソースおよび前記ドレインは、nタイプドープシリコンまたはpタイプドープシリコンを含む、請求項1に記載のトランジスタ。

【請求項5】

前記ゲートは、金属、金属酸化物、またはポリシリコンを含む、請求項1に記載のトランジスタ。

【請求項6】

前記ゲート酸化物は、SiO2または高誘電率を有する材料を含む、請求項1に記載のトランジスタ。

【請求項7】

前記ゲート酸化物は、ZrO2、Y2O3、HfO2、SiOxNy、またはその固溶体を含む、請求項6に記載のトランジスタ。

【請求項8】

前記ソースバリヤおよび前記ドレインバリヤは、SiO2または高誘電率を有する材料を独立して含む、請求項1に記載のトランジスタ。

【請求項9】

前記ソースバリヤおよび前記ドレインバリヤは、ZrO2、Y2O3、HfO2、SiOxNy、またはその固溶体を独立して含む、請求項8に記載のトランジスタ。

【請求項10】

前記アイランドは、nタイプまたはpタイプのドープシリコンあるいは半導体酸化物を含む、請求項1に記載のトランジスタ。

【請求項11】

前記アイランドは、SnO、Sn2O3、In2O3、またはその固溶体を含む、請求項10に記載のトランジスタ。

【請求項12】

前記ソース、前記ソースバリヤ、前記アイランド、前記ドレインバリヤ、前記ドレインは、基板上に積層される、請求項1に記載のトランジスタ。

【請求項13】

前記ソースバリヤは、前記ドレインバリヤよりも厚い、請求項12に記載のトランジスタ。

【請求項14】

前記ゲート領域の少なくとも前記アイランドは、前記ソースバリヤおよび前記ドレインバリヤの双方に接する、請求項12に記載のトランジスタ。

【請求項15】

前記ゲートは、前記ゲート酸化物のみに接する、請求項14に記載のトランジスタ。

【請求項16】

メモリアレイであって、

複数のメモリユニットを含む第1のメモリアレイ層を備え、各メモリユニットは、メモリセルに電気的に結合されるトランジスタを含み、

前記メモリアレイは、

複数のメモリユニットを含む第2のメモリアレイ層をさらに備え、各メモリユニットは、メモリセルに電気的に結合されるトランジスタを含み、

前記トランジスタは、

ソースと、

ドレインと、

ゲート領域とを含み、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを有し、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに含み、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離する、メモリアレイ。

【請求項17】

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、請求項16に記載のメモリアレイ。

【請求項18】

前記第1のメモリアレイ層および前記第2のメモリアレイ層は、メモリユニットの複数の行および列を含む、請求項16に記載のメモリアレイ。

【請求項19】

連続的に積層されて前記メモリアレイを形成する3つまたはより多くのメモリアレイをさらに備える、請求項16に記載のメモリアレイ。

【請求項20】

トランジスタであって、

ソースと、

ドレインと、

ゲート領域とを備え、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを含み、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに備え、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離し、

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、トランジスタ。

【請求項1】

トランジスタであって、

ソースと、

ドレインと、

ゲート領域とを備え、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを含み、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに備え、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離する、トランジスタ。

【請求項2】

前記ソースバリヤおよび前記ドレインバリヤは、変化する厚みを有する、請求項1に記載のトランジスタ。

【請求項3】

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、請求項2に記載のトランジスタ。

【請求項4】

前記ソースおよび前記ドレインは、nタイプドープシリコンまたはpタイプドープシリコンを含む、請求項1に記載のトランジスタ。

【請求項5】

前記ゲートは、金属、金属酸化物、またはポリシリコンを含む、請求項1に記載のトランジスタ。

【請求項6】

前記ゲート酸化物は、SiO2または高誘電率を有する材料を含む、請求項1に記載のトランジスタ。

【請求項7】

前記ゲート酸化物は、ZrO2、Y2O3、HfO2、SiOxNy、またはその固溶体を含む、請求項6に記載のトランジスタ。

【請求項8】

前記ソースバリヤおよび前記ドレインバリヤは、SiO2または高誘電率を有する材料を独立して含む、請求項1に記載のトランジスタ。

【請求項9】

前記ソースバリヤおよび前記ドレインバリヤは、ZrO2、Y2O3、HfO2、SiOxNy、またはその固溶体を独立して含む、請求項8に記載のトランジスタ。

【請求項10】

前記アイランドは、nタイプまたはpタイプのドープシリコンあるいは半導体酸化物を含む、請求項1に記載のトランジスタ。

【請求項11】

前記アイランドは、SnO、Sn2O3、In2O3、またはその固溶体を含む、請求項10に記載のトランジスタ。

【請求項12】

前記ソース、前記ソースバリヤ、前記アイランド、前記ドレインバリヤ、前記ドレインは、基板上に積層される、請求項1に記載のトランジスタ。

【請求項13】

前記ソースバリヤは、前記ドレインバリヤよりも厚い、請求項12に記載のトランジスタ。

【請求項14】

前記ゲート領域の少なくとも前記アイランドは、前記ソースバリヤおよび前記ドレインバリヤの双方に接する、請求項12に記載のトランジスタ。

【請求項15】

前記ゲートは、前記ゲート酸化物のみに接する、請求項14に記載のトランジスタ。

【請求項16】

メモリアレイであって、

複数のメモリユニットを含む第1のメモリアレイ層を備え、各メモリユニットは、メモリセルに電気的に結合されるトランジスタを含み、

前記メモリアレイは、

複数のメモリユニットを含む第2のメモリアレイ層をさらに備え、各メモリユニットは、メモリセルに電気的に結合されるトランジスタを含み、

前記トランジスタは、

ソースと、

ドレインと、

ゲート領域とを含み、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを有し、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに含み、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離する、メモリアレイ。

【請求項17】

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、請求項16に記載のメモリアレイ。

【請求項18】

前記第1のメモリアレイ層および前記第2のメモリアレイ層は、メモリユニットの複数の行および列を含む、請求項16に記載のメモリアレイ。

【請求項19】

連続的に積層されて前記メモリアレイを形成する3つまたはより多くのメモリアレイをさらに備える、請求項16に記載のメモリアレイ。

【請求項20】

トランジスタであって、

ソースと、

ドレインと、

ゲート領域とを備え、前記ゲート領域は、

ゲートと、

アイランドと、

ゲート酸化物とを含み、

前記ゲート酸化物は、前記ゲートと前記アイランドとの間に配置され、

前記ゲートおよび前記アイランドは、互いに、同時活性的に結合され、

前記トランジスタは、

ソースバリヤとドレインバリヤとをさらに備え、

前記ソースバリヤは、前記ゲート領域から前記ソースを分離し、前記ドレインバリヤは、前記ゲート領域から前記ドレインを分離し、

前記ソースバリヤおよび前記ドレインバリヤは、それらが前記ゲートに近接するよりも、前記アイランドにより薄く近接する、トランジスタ。

【図1A】

【図1B】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図1B】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【公開番号】特開2012−134480(P2012−134480A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2011−268936(P2011−268936)

【出願日】平成23年12月8日(2011.12.8)

【出願人】(500373758)シーゲイト テクノロジー エルエルシー (278)

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成23年12月8日(2011.12.8)

【出願人】(500373758)シーゲイト テクノロジー エルエルシー (278)

【Fターム(参考)】

[ Back to top ]