トランジスタ保護回路

【課題】スイッチング周波数が高くても、適切にトランジスタの保護を行うことが可能なトランジスタ保護回路を提供する。

【解決手段】本発明の一実施形態に係るトランジスタ保護回路10は、駆動回路30によって電源40の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタ20の保護を行うためのトランジスタ保護回路である。このトランジスタ保護回路10は、トランジスタ20の保護を実行する保護指令を受けたときに、電源40の高電位側電圧を次第に低下させる電源制御部12を備える。

【解決手段】本発明の一実施形態に係るトランジスタ保護回路10は、駆動回路30によって電源40の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタ20の保護を行うためのトランジスタ保護回路である。このトランジスタ保護回路10は、トランジスタ20の保護を実行する保護指令を受けたときに、電源40の高電位側電圧を次第に低下させる電源制御部12を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パワーエレクトロニクス回路等におけるトランジスタの保護を行うトランジスタ保護回路に関するものである。

【背景技術】

【0002】

パワーエレクトロニクス回路等におけるトランジスタが異常動作状態(例えば、過電流、過電圧、高温度等)となるときに、このトランジスタの保護を行う保護回路が考案されている。特許文献1には、インバータにおける電圧駆動型のトランジスタを流れる電流を制限する過電流保護回路が開示されている。この過電流保護回路40では、トランジスタSWを流れる電流が過電流であることを検出したときに、ソフト遮断回路49内のトランジスタをオン状態とすることによってトランジスタSWのゲート端子に印加する電圧を次第に低下させ、トランジスタSWのソフト遮断を行う。このソフト遮断により、遮断時に過大なサージ電圧が発生することを抑制することができるとしている。

【0003】

また、過電流保護回路40は、ソフト遮断を行う際、トランジスタSWを駆動するための駆動回路30に、トランジスタSWのゲート端子に印加する電圧の供給も停止させる。具体的には、駆動回路30において、高電位側電圧を供給するためのトランジスタ31p、及び、低電位側電圧を供給するためのトランジスタ31nをオフ状態とさせる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−141841号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、近年、極めて低いスイッチング損失を実現することが可能なSiCデバイス等の出現により、パワーエレクトロニクス回路等においてスイッチング周波数の増加が望まれている(例えば、5〜10倍程度、100kHzオーバー)。

【0006】

しかしながら、スイッチング周波数が高くなると、特許文献1に記載の保護回路では、駆動回路30の動作遅延時間により、適切にソフト遮断を行うことができなくなる可能性がある。詳説すれば、ソフト遮断を行う際、ソフト遮断回路49内のトランジスタがオン状態となるときには、駆動回路30内のトランジスタ31p,31nが同時にオフ状態になる必要がある。しかしながら、駆動回路30における制御回路35などの遅延時間のため、トランジスタ31p,31nがオフ状態となるのが遅れ、その結果、ソフト遮断の状態になるのが遅れる可能性がある。スイッチング周波数が高くなると、この遅れ時間が問題となる。

【0007】

そこで、本発明は、スイッチング周波数が高くても、適切にトランジスタの保護を行うことが可能なトランジスタ保護回路を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明のトランジスタ保護回路は、駆動回路によって電源の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタの保護を行うためのトランジスタ保護回路であって、トランジスタの保護を実行する保護指令を受けたときに、電源の高電位側電圧を次第に低下させる電源制御部を備えることを特徴とする。

【0009】

このトランジスタ保護回路によれば、電源制御部によって、電源の高電位側電圧、すなわち、トランジスタのゲート端子に印加される電圧を次第に低下させるので、駆動回路の動作遅延時間に依存することなく、トランジスタを次第にオフ状態とするソフト遮断を適切に行うことができる。したがって、スイッチング周波数に依存することなく、適切にトランジスタの保護を行うことが可能となる。

【0010】

上記したトランジスタ保護回路は、トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するためのゲート短絡部と、保護指令に応じて、トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する短絡制御部とを更に備え、短絡制御部は、保護指令を受けてから所定遅延時間経過後にトランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するようにゲート短絡部を制御してもよい。

【0011】

この構成によれば、所定遅延時間経過後に、電源制御部による電源の高電位側電圧の低下を停止することができる。例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されることがある。このような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0012】

上記した所定遅延時間は、トランジスタのゲート端子に印加される電圧がトランジスタのしきい値電圧に低下する時間以上であってもよい。

【0013】

これによれば、短絡制御部は、トランジスタのゲート電圧がしきい値電圧以下に低下した後に、トランジスタのゲート端子を短絡させることとなるので、短絡時に過大なサージ電圧が発生することを回避することができる。

【0014】

また、上記したトランジスタ保護回路は、保護指令に応じて、電源の高電位側電圧をトランジスタのゲート端子に印加することを停止するように駆動回路を制御する駆動制御部を更に備え、駆動制御部は、保護指令を受けてから所定遅延時間経過後に、電源の高電位側電圧をトランジスタのゲート端子に印加することを停止するように前記駆動回路を制御してもよい。なお、駆動制御部における所定遅延時間は、上記した短絡制御部における所定遅延時間と同一であってもよい。

【0015】

この構成によれば、所定遅延時間経過後に、電源制御部による電源の高電位側電圧の低下を停止することができる。これにより、例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されるような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0016】

上記した駆動制御部は、保護指令を受けてから所定遅延時間経過前には、電源の高電位側電圧をトランジスタのゲート端子に印加することを継続するように前記駆動回路を制御してもよい。

【0017】

これによれば、所定遅延時間経過前には、電源制御部によってトランジスタのソフト遮断を適切に行うことができる。

【発明の効果】

【0018】

本発明によれば、スイッチング周波数が高くても、適切にトランジスタの保護を行うことができる。

【図面の簡単な説明】

【0019】

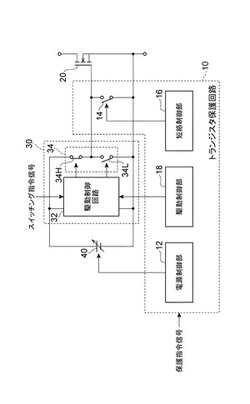

【図1】本発明の実施形態に係るトランジスタ保護回路を示す回路図である。

【図2】図1に示すトランジスタ保護回路における各部波形を示す図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して本発明の好適な実施形態について詳細に説明する。なお、各図面において同一又は相当の部分に対しては同一の符号を附すこととする。

【0021】

図1は、本発明の実施形態に係るトランジスタ保護回路を示す回路図である。図1には、トランジスタ保護回路10の保護対象であるトランジスタ20を含むパワーエレクトロニクス回路の一部が例示されている。

【0022】

まず、トランジスタ保護回路10を説明する前に、例示のパワーエレクトロニクス回路について説明する。例えば、パワーエレクトロニクス回路としてはインバータが挙げられ、インバータでは、トランジスタ20が2つ直列に接続された直列回路を2つ又は3つ並列に備える。トランジスタ20としては、IGBTやFET等の電圧駆動型のトランジスタが例示され、この種のトランジスタ20は、図1に示すように、駆動回路30によって電圧駆動される。

【0023】

駆動回路30は、電源40からの電源電圧で動作する。駆動回路30は、駆動制御回路32と選択回路34とを有する。選択回路34は、2つのスイッチ素子34H,34Lが電源40の高圧側電位と低圧側電位との間に直列に接続されており、スイッチ素子34H,34Lとの中間ノードがトランジスタ20のゲート端子に接続されている。トランジスタ20のエミッタ又はソース端子は電源40の低圧側電位に接続されている。駆動回路30は、例えば、インバータの出力を制御するためのスイッチング指令信号に応じて、トランジスタ20のオン/オフをPWM制御する。具体的には、駆動制御回路32によってスイッチ素子34Hをオン状態とすると共に、スイッチ素子34Lをオフ状態とすると、トランジスタ20のゲート端子には高電位側電圧が供給され、駆動制御回路32によってスイッチ素子34Hをオフ状態とすると共に、スイッチ素子34Lをオン状態とすると、トランジスタ20のゲート端子には低電位側電圧が供給される。

【0024】

この種のトランジスタ20が異常動作状態(例えば、過電流、過電圧、高温度等)となることが検出回路(図示せず)によって検出されると、トランジスタ保護回路10に、トランジスタの保護を実行する保護指令信号が入力される。トランジスタ保護回路10は、この保護指令信号を受けたときに、トランジスタ20の保護動作を実行することとなる。

【0025】

トランジスタ保護回路10は、電源制御部12と、ゲート短絡部14と、短絡制御部16と、駆動制御部18とを備える。

【0026】

電源制御部12は、保護指令信号に応じて電源40を制御し、電源電圧を低下させる。具体的には、電源制御部12は、保護指令信号を受けた直後から、電源40の高電位側電圧を次第に低下させる。ここで、保護指令信号を受けるときは、選択回路34におけるスイッチ素子34Hがオン状態である。よって、電源制御部12は、トランジスタ20のゲート端子に印加する電圧を次第に低下させることとなる(ソフト遮断)。

【0027】

ゲート短絡部14は、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡するためのスイッチ素子を含み、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子(すなわち、電源40の低電位側)との間に接続されている。ゲート短絡部14は、短絡制御部16によって制御される。

【0028】

短絡制御部16は、保護指令信号に応じてゲート短絡部14を制御し、トランジスタ20のゲート端子を短絡させる。具体的には、短絡制御部16は、保護指令信号を受けてから所定遅延時間経過後に、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡させる。例えば、所定遅延時間は、トランジスタ20のゲート電圧がしきい値電圧に低下する時間以上に設定される。このような所定遅延時間は、電源電圧の低下の時定数等から予測可能であり、例えば予め設定可能である。

【0029】

駆動制御部18は、保護指令信号に応じて駆動回路30を制御し、トランジスタ20のゲート端子への電圧供給を制御する。具体的には、駆動制御部18は、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Hをオフ状態として、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを停止させる。このとき、駆動制御部18は、選択回路34のスイッチ素子34Lをオン状態として、トランジスタ20のゲート端子を短絡させてもよい。

【0030】

また、駆動制御部18は、保護指令信号を受けてから所定遅延時間経過前には、選択回路34のスイッチ素子34Hをオン状態のまま保持して、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを継続させる。

【0031】

次に、このトランジスタ保護回路10の動作を説明する。図2は、トランジスタ保護回路10、及び、保護・制御対象における各部波形を示す図である。

【0032】

まず、トランジスタ20が正常動作状態である場合、スイッチング指令信号に応じて(a)、駆動回路30における選択回路34のスイッチ素子34H,34Lが交互にオン/オフし(b),(c)、トランジスタ20のゲート端子に駆動電圧が供給される(g)。

【0033】

その後、時刻t1において、トランジスタ20が異常動作状態であることが検出され、ハイレベルの保護指令信号を受けると(e)、トランジスタ保護回路10では、電源制御部12が電源40の出力電圧を次第に低下させる(f)。このとき、駆動制御部18は、選択回路34のスイッチ素子34Hをオン状態のまま保持させる(b)。これにより、トランジスタ20のゲート電圧を次第に低下させて、トランジスタ20のソフト遮断を行う(g)。

【0034】

時刻t1から所定遅延時間経過後、時刻t2において、短絡制御部16及びゲート短絡部14によって、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡させる(d)。このとき、駆動制御部18は、選択回路34のスイッチ素子34Hをオフ状態とする(b)。また、駆動制御部18は、選択回路34のスイッチ素子34Lをオン状態とする(c)。このとき、トランジスタ20に印加する電圧はトランジスタ20のしきい値電圧以下に低下しており、短絡しても過大なサージ電圧が発生することはない。

【0035】

なお、電源制御部12は、電源40の電圧が低下し切らない適切なタイミングで、電源40の出力電圧を低下することを停止することとなる(f)。

【0036】

その後、トランジスタ20が正常動作状態に復帰し、保護指令信号がローレベルになると、短絡制御部16及びゲート短絡部14がトランジスタ20のゲート端子の短絡を解除すると共に(d)、駆動制御部18が選択回路34のスイッチ素子34Lの短絡を解除し、上述したトランジスタ20の正常動作状態に復帰する。

【0037】

以上説明したように、本実施形態のトランジスタ保護回路10によれば、電源制御部12によって、保護指令信号を受けた直後から、電源40の高電位側電圧、すなわち、トランジスタ20のゲート端子に印加される電圧を次第に低下させるので、駆動回路30の動作遅延時間に依存することなく、駆動回路30の動作遅延時間よりも短い遅延時間で、トランジスタ20を次第にオフ状態とするソフト遮断を適切に行うことができる。したがって、スイッチング周波数に依存することなく、スイッチング周波数が高くても、適切にトランジスタ20の保護を行うことが可能となる。

【0038】

また、本実施形態のトランジスタ保護回路10によれば、短絡制御部16及びゲート短絡部14によって、保護指令信号を受けてから所定遅延時間経過後にトランジスタのゲート端子を短絡させるので、所定遅延時間経過後に、電源制御部12による電源の高電位側電圧の低下を停止することができる。例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されることがある。このような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0039】

また、本実施形態のトランジスタ保護回路10によれば、短絡制御部16は、トランジスタ20のゲート電圧がしきい値電圧以下に低下した後に、トランジスタ20のゲート端子を短絡させることとなるので、短絡時に過大なサージ電圧が発生することを回避することができる。

【0040】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Hをオフ状態として、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを停止させるので、所定遅延時間経過後に、電源制御部12による電源の高電位側電圧の低下を停止することができる。これにより、例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されるような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。また、ゲート短絡部14の短絡時に過大な電流が流れることを回避することができる。

【0041】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Lをオン状態とするので、トランジスタ20のゲート端子の短絡を補助することができる。

【0042】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過前では、選択回路34のスイッチ素子34Hをオン状態のまま保持して、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを継続させるので、所定遅延時間経過前では、電源制御部12によってトランジスタ20のソフト遮断を適切に行うことができる。

【0043】

なお、本発明は上記した本実施形態に限定されることなく種々の変形が可能である。例えば、本実施形態では、電源制御部12と、短絡制御部16(及びゲート短絡部14)と、駆動制御部18とを全て備えるトランジスタ保護回路10を例示したが、トランジスタ保護回路は、電源制御部12と短絡制御部16(及びゲート短絡部14)とのみを備える形態であってもよく、電源制御部12と駆動制御部18とのみを備える形態であってもよく、更には、電源制御部12のみを備える形態であってもよい。

【0044】

また、本実施形態では、駆動制御部18における所定遅延時間と短絡制御部16における所定遅延時間とを同一としたが、駆動制御部18における所定遅延時間は、短絡制御部16における所定遅延時間より短くてもよい。すなわち、少なくとも短絡制御部16によってトランジスタ20のゲート端子が短絡されるときには、駆動制御部18によって駆動回路30における選択回路34のスイッチ素子34Hがオフ状態になっていればよい。

【符号の説明】

【0045】

10…トランジスタ保護回路、12…電源制御部、14…ゲート短絡部、16…短絡制御部、18…駆動制御部、20…トランジスタ、30…駆動回路、32…駆動制御回路、34…選択回路、34H,34L…スイッチ素子、40…電源。

【技術分野】

【0001】

本発明は、パワーエレクトロニクス回路等におけるトランジスタの保護を行うトランジスタ保護回路に関するものである。

【背景技術】

【0002】

パワーエレクトロニクス回路等におけるトランジスタが異常動作状態(例えば、過電流、過電圧、高温度等)となるときに、このトランジスタの保護を行う保護回路が考案されている。特許文献1には、インバータにおける電圧駆動型のトランジスタを流れる電流を制限する過電流保護回路が開示されている。この過電流保護回路40では、トランジスタSWを流れる電流が過電流であることを検出したときに、ソフト遮断回路49内のトランジスタをオン状態とすることによってトランジスタSWのゲート端子に印加する電圧を次第に低下させ、トランジスタSWのソフト遮断を行う。このソフト遮断により、遮断時に過大なサージ電圧が発生することを抑制することができるとしている。

【0003】

また、過電流保護回路40は、ソフト遮断を行う際、トランジスタSWを駆動するための駆動回路30に、トランジスタSWのゲート端子に印加する電圧の供給も停止させる。具体的には、駆動回路30において、高電位側電圧を供給するためのトランジスタ31p、及び、低電位側電圧を供給するためのトランジスタ31nをオフ状態とさせる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−141841号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、近年、極めて低いスイッチング損失を実現することが可能なSiCデバイス等の出現により、パワーエレクトロニクス回路等においてスイッチング周波数の増加が望まれている(例えば、5〜10倍程度、100kHzオーバー)。

【0006】

しかしながら、スイッチング周波数が高くなると、特許文献1に記載の保護回路では、駆動回路30の動作遅延時間により、適切にソフト遮断を行うことができなくなる可能性がある。詳説すれば、ソフト遮断を行う際、ソフト遮断回路49内のトランジスタがオン状態となるときには、駆動回路30内のトランジスタ31p,31nが同時にオフ状態になる必要がある。しかしながら、駆動回路30における制御回路35などの遅延時間のため、トランジスタ31p,31nがオフ状態となるのが遅れ、その結果、ソフト遮断の状態になるのが遅れる可能性がある。スイッチング周波数が高くなると、この遅れ時間が問題となる。

【0007】

そこで、本発明は、スイッチング周波数が高くても、適切にトランジスタの保護を行うことが可能なトランジスタ保護回路を提供することを目的としている。

【課題を解決するための手段】

【0008】

本発明のトランジスタ保護回路は、駆動回路によって電源の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタの保護を行うためのトランジスタ保護回路であって、トランジスタの保護を実行する保護指令を受けたときに、電源の高電位側電圧を次第に低下させる電源制御部を備えることを特徴とする。

【0009】

このトランジスタ保護回路によれば、電源制御部によって、電源の高電位側電圧、すなわち、トランジスタのゲート端子に印加される電圧を次第に低下させるので、駆動回路の動作遅延時間に依存することなく、トランジスタを次第にオフ状態とするソフト遮断を適切に行うことができる。したがって、スイッチング周波数に依存することなく、適切にトランジスタの保護を行うことが可能となる。

【0010】

上記したトランジスタ保護回路は、トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するためのゲート短絡部と、保護指令に応じて、トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する短絡制御部とを更に備え、短絡制御部は、保護指令を受けてから所定遅延時間経過後にトランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するようにゲート短絡部を制御してもよい。

【0011】

この構成によれば、所定遅延時間経過後に、電源制御部による電源の高電位側電圧の低下を停止することができる。例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されることがある。このような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0012】

上記した所定遅延時間は、トランジスタのゲート端子に印加される電圧がトランジスタのしきい値電圧に低下する時間以上であってもよい。

【0013】

これによれば、短絡制御部は、トランジスタのゲート電圧がしきい値電圧以下に低下した後に、トランジスタのゲート端子を短絡させることとなるので、短絡時に過大なサージ電圧が発生することを回避することができる。

【0014】

また、上記したトランジスタ保護回路は、保護指令に応じて、電源の高電位側電圧をトランジスタのゲート端子に印加することを停止するように駆動回路を制御する駆動制御部を更に備え、駆動制御部は、保護指令を受けてから所定遅延時間経過後に、電源の高電位側電圧をトランジスタのゲート端子に印加することを停止するように前記駆動回路を制御してもよい。なお、駆動制御部における所定遅延時間は、上記した短絡制御部における所定遅延時間と同一であってもよい。

【0015】

この構成によれば、所定遅延時間経過後に、電源制御部による電源の高電位側電圧の低下を停止することができる。これにより、例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されるような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0016】

上記した駆動制御部は、保護指令を受けてから所定遅延時間経過前には、電源の高電位側電圧をトランジスタのゲート端子に印加することを継続するように前記駆動回路を制御してもよい。

【0017】

これによれば、所定遅延時間経過前には、電源制御部によってトランジスタのソフト遮断を適切に行うことができる。

【発明の効果】

【0018】

本発明によれば、スイッチング周波数が高くても、適切にトランジスタの保護を行うことができる。

【図面の簡単な説明】

【0019】

【図1】本発明の実施形態に係るトランジスタ保護回路を示す回路図である。

【図2】図1に示すトランジスタ保護回路における各部波形を示す図である。

【発明を実施するための形態】

【0020】

以下、図面を参照して本発明の好適な実施形態について詳細に説明する。なお、各図面において同一又は相当の部分に対しては同一の符号を附すこととする。

【0021】

図1は、本発明の実施形態に係るトランジスタ保護回路を示す回路図である。図1には、トランジスタ保護回路10の保護対象であるトランジスタ20を含むパワーエレクトロニクス回路の一部が例示されている。

【0022】

まず、トランジスタ保護回路10を説明する前に、例示のパワーエレクトロニクス回路について説明する。例えば、パワーエレクトロニクス回路としてはインバータが挙げられ、インバータでは、トランジスタ20が2つ直列に接続された直列回路を2つ又は3つ並列に備える。トランジスタ20としては、IGBTやFET等の電圧駆動型のトランジスタが例示され、この種のトランジスタ20は、図1に示すように、駆動回路30によって電圧駆動される。

【0023】

駆動回路30は、電源40からの電源電圧で動作する。駆動回路30は、駆動制御回路32と選択回路34とを有する。選択回路34は、2つのスイッチ素子34H,34Lが電源40の高圧側電位と低圧側電位との間に直列に接続されており、スイッチ素子34H,34Lとの中間ノードがトランジスタ20のゲート端子に接続されている。トランジスタ20のエミッタ又はソース端子は電源40の低圧側電位に接続されている。駆動回路30は、例えば、インバータの出力を制御するためのスイッチング指令信号に応じて、トランジスタ20のオン/オフをPWM制御する。具体的には、駆動制御回路32によってスイッチ素子34Hをオン状態とすると共に、スイッチ素子34Lをオフ状態とすると、トランジスタ20のゲート端子には高電位側電圧が供給され、駆動制御回路32によってスイッチ素子34Hをオフ状態とすると共に、スイッチ素子34Lをオン状態とすると、トランジスタ20のゲート端子には低電位側電圧が供給される。

【0024】

この種のトランジスタ20が異常動作状態(例えば、過電流、過電圧、高温度等)となることが検出回路(図示せず)によって検出されると、トランジスタ保護回路10に、トランジスタの保護を実行する保護指令信号が入力される。トランジスタ保護回路10は、この保護指令信号を受けたときに、トランジスタ20の保護動作を実行することとなる。

【0025】

トランジスタ保護回路10は、電源制御部12と、ゲート短絡部14と、短絡制御部16と、駆動制御部18とを備える。

【0026】

電源制御部12は、保護指令信号に応じて電源40を制御し、電源電圧を低下させる。具体的には、電源制御部12は、保護指令信号を受けた直後から、電源40の高電位側電圧を次第に低下させる。ここで、保護指令信号を受けるときは、選択回路34におけるスイッチ素子34Hがオン状態である。よって、電源制御部12は、トランジスタ20のゲート端子に印加する電圧を次第に低下させることとなる(ソフト遮断)。

【0027】

ゲート短絡部14は、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡するためのスイッチ素子を含み、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子(すなわち、電源40の低電位側)との間に接続されている。ゲート短絡部14は、短絡制御部16によって制御される。

【0028】

短絡制御部16は、保護指令信号に応じてゲート短絡部14を制御し、トランジスタ20のゲート端子を短絡させる。具体的には、短絡制御部16は、保護指令信号を受けてから所定遅延時間経過後に、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡させる。例えば、所定遅延時間は、トランジスタ20のゲート電圧がしきい値電圧に低下する時間以上に設定される。このような所定遅延時間は、電源電圧の低下の時定数等から予測可能であり、例えば予め設定可能である。

【0029】

駆動制御部18は、保護指令信号に応じて駆動回路30を制御し、トランジスタ20のゲート端子への電圧供給を制御する。具体的には、駆動制御部18は、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Hをオフ状態として、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを停止させる。このとき、駆動制御部18は、選択回路34のスイッチ素子34Lをオン状態として、トランジスタ20のゲート端子を短絡させてもよい。

【0030】

また、駆動制御部18は、保護指令信号を受けてから所定遅延時間経過前には、選択回路34のスイッチ素子34Hをオン状態のまま保持して、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを継続させる。

【0031】

次に、このトランジスタ保護回路10の動作を説明する。図2は、トランジスタ保護回路10、及び、保護・制御対象における各部波形を示す図である。

【0032】

まず、トランジスタ20が正常動作状態である場合、スイッチング指令信号に応じて(a)、駆動回路30における選択回路34のスイッチ素子34H,34Lが交互にオン/オフし(b),(c)、トランジスタ20のゲート端子に駆動電圧が供給される(g)。

【0033】

その後、時刻t1において、トランジスタ20が異常動作状態であることが検出され、ハイレベルの保護指令信号を受けると(e)、トランジスタ保護回路10では、電源制御部12が電源40の出力電圧を次第に低下させる(f)。このとき、駆動制御部18は、選択回路34のスイッチ素子34Hをオン状態のまま保持させる(b)。これにより、トランジスタ20のゲート電圧を次第に低下させて、トランジスタ20のソフト遮断を行う(g)。

【0034】

時刻t1から所定遅延時間経過後、時刻t2において、短絡制御部16及びゲート短絡部14によって、トランジスタ20のゲート端子と、ソース端子またはエミッタ端子とを短絡させる(d)。このとき、駆動制御部18は、選択回路34のスイッチ素子34Hをオフ状態とする(b)。また、駆動制御部18は、選択回路34のスイッチ素子34Lをオン状態とする(c)。このとき、トランジスタ20に印加する電圧はトランジスタ20のしきい値電圧以下に低下しており、短絡しても過大なサージ電圧が発生することはない。

【0035】

なお、電源制御部12は、電源40の電圧が低下し切らない適切なタイミングで、電源40の出力電圧を低下することを停止することとなる(f)。

【0036】

その後、トランジスタ20が正常動作状態に復帰し、保護指令信号がローレベルになると、短絡制御部16及びゲート短絡部14がトランジスタ20のゲート端子の短絡を解除すると共に(d)、駆動制御部18が選択回路34のスイッチ素子34Lの短絡を解除し、上述したトランジスタ20の正常動作状態に復帰する。

【0037】

以上説明したように、本実施形態のトランジスタ保護回路10によれば、電源制御部12によって、保護指令信号を受けた直後から、電源40の高電位側電圧、すなわち、トランジスタ20のゲート端子に印加される電圧を次第に低下させるので、駆動回路30の動作遅延時間に依存することなく、駆動回路30の動作遅延時間よりも短い遅延時間で、トランジスタ20を次第にオフ状態とするソフト遮断を適切に行うことができる。したがって、スイッチング周波数に依存することなく、スイッチング周波数が高くても、適切にトランジスタ20の保護を行うことが可能となる。

【0038】

また、本実施形態のトランジスタ保護回路10によれば、短絡制御部16及びゲート短絡部14によって、保護指令信号を受けてから所定遅延時間経過後にトランジスタのゲート端子を短絡させるので、所定遅延時間経過後に、電源制御部12による電源の高電位側電圧の低下を停止することができる。例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されることがある。このような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。

【0039】

また、本実施形態のトランジスタ保護回路10によれば、短絡制御部16は、トランジスタ20のゲート電圧がしきい値電圧以下に低下した後に、トランジスタ20のゲート端子を短絡させることとなるので、短絡時に過大なサージ電圧が発生することを回避することができる。

【0040】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Hをオフ状態として、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを停止させるので、所定遅延時間経過後に、電源制御部12による電源の高電位側電圧の低下を停止することができる。これにより、例えば、この電源電圧が、パワーエレクトロニクス回路における他の回路にも使用されるような場合に、電源電圧を必要以上に低下させることを回避して、他の回路の動作停止を回避することができる。また、ゲート短絡部14の短絡時に過大な電流が流れることを回避することができる。

【0041】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過後に、選択回路34のスイッチ素子34Lをオン状態とするので、トランジスタ20のゲート端子の短絡を補助することができる。

【0042】

また、本実施形態のトランジスタ保護回路10によれば、駆動制御部18によって、保護指令信号を受けてから所定遅延時間経過前では、選択回路34のスイッチ素子34Hをオン状態のまま保持して、電源40の高電位側電圧をトランジスタ20のゲート端子に印加することを継続させるので、所定遅延時間経過前では、電源制御部12によってトランジスタ20のソフト遮断を適切に行うことができる。

【0043】

なお、本発明は上記した本実施形態に限定されることなく種々の変形が可能である。例えば、本実施形態では、電源制御部12と、短絡制御部16(及びゲート短絡部14)と、駆動制御部18とを全て備えるトランジスタ保護回路10を例示したが、トランジスタ保護回路は、電源制御部12と短絡制御部16(及びゲート短絡部14)とのみを備える形態であってもよく、電源制御部12と駆動制御部18とのみを備える形態であってもよく、更には、電源制御部12のみを備える形態であってもよい。

【0044】

また、本実施形態では、駆動制御部18における所定遅延時間と短絡制御部16における所定遅延時間とを同一としたが、駆動制御部18における所定遅延時間は、短絡制御部16における所定遅延時間より短くてもよい。すなわち、少なくとも短絡制御部16によってトランジスタ20のゲート端子が短絡されるときには、駆動制御部18によって駆動回路30における選択回路34のスイッチ素子34Hがオフ状態になっていればよい。

【符号の説明】

【0045】

10…トランジスタ保護回路、12…電源制御部、14…ゲート短絡部、16…短絡制御部、18…駆動制御部、20…トランジスタ、30…駆動回路、32…駆動制御回路、34…選択回路、34H,34L…スイッチ素子、40…電源。

【特許請求の範囲】

【請求項1】

駆動回路によって電源の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタの保護を行うためのトランジスタ保護回路であって、

前記トランジスタの保護を実行する保護指令を受けたときに、前記電源の高電位側電圧を次第に低下させる電源制御部を備えることを特徴とする、

トランジスタ保護回路。

【請求項2】

前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するためのゲート短絡部と、

前記保護指令に応じて、前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する短絡制御部と、

を更に備え、

前記短絡制御部は、前記保護指令を受けてから所定遅延時間経過後に前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する、

請求項1に記載のトランジスタ保護回路。

【請求項3】

前記所定遅延時間は、前記トランジスタのゲート端子に印加される電圧が前記トランジスタのしきい値電圧に低下する時間以上である、請求項2に記載のトランジスタ保護回路。

【請求項4】

前記保護指令に応じて、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する駆動制御部を更に備え、

前記駆動制御部は、前記保護指令を受けてから所定遅延時間経過後に、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する、

請求項1に記載のトランジスタ保護回路。

【請求項5】

前記保護指令に応じて、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する駆動制御部を更に備え、

前記駆動制御部は、前記保護指令を受けてから前記所定遅延時間経過後に、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する、

請求項2又は3に記載のトランジスタ保護回路。

【請求項6】

前記駆動制御部は、前記保護指令を受けてから前記所定遅延時間経過前には、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを継続するように前記駆動回路を制御する、請求項4又は5に記載のトランジスタ保護回路。

【請求項1】

駆動回路によって電源の高電位側電圧または低電位側電圧がゲート端子に印加されて、スイッチング制御される電圧駆動型のトランジスタの保護を行うためのトランジスタ保護回路であって、

前記トランジスタの保護を実行する保護指令を受けたときに、前記電源の高電位側電圧を次第に低下させる電源制御部を備えることを特徴とする、

トランジスタ保護回路。

【請求項2】

前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するためのゲート短絡部と、

前記保護指令に応じて、前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する短絡制御部と、

を更に備え、

前記短絡制御部は、前記保護指令を受けてから所定遅延時間経過後に前記トランジスタのゲート端子と、ソース端子またはエミッタ端子とを短絡するように前記ゲート短絡部を制御する、

請求項1に記載のトランジスタ保護回路。

【請求項3】

前記所定遅延時間は、前記トランジスタのゲート端子に印加される電圧が前記トランジスタのしきい値電圧に低下する時間以上である、請求項2に記載のトランジスタ保護回路。

【請求項4】

前記保護指令に応じて、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する駆動制御部を更に備え、

前記駆動制御部は、前記保護指令を受けてから所定遅延時間経過後に、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する、

請求項1に記載のトランジスタ保護回路。

【請求項5】

前記保護指令に応じて、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する駆動制御部を更に備え、

前記駆動制御部は、前記保護指令を受けてから前記所定遅延時間経過後に、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを停止するように前記駆動回路を制御する、

請求項2又は3に記載のトランジスタ保護回路。

【請求項6】

前記駆動制御部は、前記保護指令を受けてから前記所定遅延時間経過前には、前記電源の高電位側電圧を前記トランジスタのゲート端子に印加することを継続するように前記駆動回路を制御する、請求項4又は5に記載のトランジスタ保護回路。

【図1】

【図2】

【図2】

【公開番号】特開2013−106446(P2013−106446A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−249238(P2011−249238)

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(304027349)国立大学法人豊橋技術科学大学 (391)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月15日(2011.11.15)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(304027349)国立大学法人豊橋技術科学大学 (391)

【Fターム(参考)】

[ Back to top ]