トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタ回路に関し、特に、エミッタフォロア回路、ソースフォロア回路として構成されるトランジスタ回路に関する。

【背景技術】

【0002】

高速の入力電圧に対し、低インピーダンス負荷回路やスイッチトキャパシタ回路を駆動する有効な回路として、一般にエミッタフォロア回路、あるいはソースフォロア回路が挙げられる(例えば特許文献1参照)。エミッタフォロア回路、ソースフォロア回路は、ゲインを持たない(ゲイン≒0dB)。

ただし、エミッタフォロア回路については、入力がバイポーラトランジスタのベースに接続されることでハイインピーダンスになる。また、ソースフォロア回路については、入力がMOSトランジスタのゲートに接続されることでハイインピーダンスになる。さらに、エミッタフォロア回路、ソースフォロア回路のいずれもが、トランジスタのトランスコンダクタンス(gm)で出力負荷を駆動できるため、大きな負荷を駆動する場合や高周波の信号を処理する場合でも、低消費電力で低歪みの信号を出力することが可能である。

【0003】

図13は、代表的なエミッタフォロア回路700を説明するための図である。エミッタフォロア回路は、バイポーラトランジスタ701を含み、バイポーラトランジスタ701のコレクタには正電源(正電源の端子を図中に704の符号を付して示す)が接続されている。エミッタは、出力電圧Voutに接続される。出力電圧Voutの一方と負電源との間には電流源702が接続されてバイポーラトランジスタ701に電流が供給される。また、他方と負電源との間には、外部に接続される容量性の負荷を疑似的に示し、容量性負荷703と記す。

【0004】

図14は、代表的なソースフォロア回路800を説明するための図である。ソースフォロア回路800は、図7に示したエミッタフォロア回路700のバイポーラトランジスタ701をMOSトランジスタ801に代えた構成を有している。このため、ソースフォロア回路800を図14に示し、その説明を略すものとする。

エミッタフォロア回路700、ソースフォロア回路800の出力電圧Voutの電圧は、以下の式(1)で表される。なお、式(1)中のVbeは、バイポーラトランジスタ701のベース・エミッタ間電圧(ソースフォロア回路800ではMOSトランジスタ801のゲート、ソース間電圧)。Vbeはエミッタ電流とトランジスタのプロセス条件によって決まる値である。このため、エミッタ電流が一定の環境下ではVbeが一定なので、Voutの変化量は常にVinの変化量に追随し、VoutはAC的にVinと同じ電圧になる。

【0005】

Vout=Vin−Vbe …式(1)

図15は、図13に示したエミッタフォロア回路700において、入力電圧Vinが高電圧に向かっている状態を示している。また、図16は、エミッタフォロア回路700において、入力電圧Vinが低電圧に向かっている状態を示している。以下、図15、図16に示したエミッタフォロア回路の動作について説明する。

【0006】

先ず、図15に示したように、入力電圧Vinが高電圧に向かう場合、バイポーラトランジスタNPN1がONの状態になり、図示しない正電源の端子704からバイポーラトランジスタ701のコレクタ、エミッタを通って電荷が容量性負荷703にチャージされる。このときのAC帯域は、バイポーラトランジスタ701のトランスコンダクタンス(gm)によって決まる。

【0007】

また、図16に示したように、入力電圧Vinが低電圧に向かう場合、バイポーラトランジスタ701はオフ状態になる。このとき、電流源702に流れる電流により、容量性負荷703に電荷がディスチャージされる。AC帯域は、電流源の電流量によって決まる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭59−168720号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、バイポーラトランジスタ701のトランスコンダクタンス(gm)は、比較的大きいため、容量性負荷703に電荷をチャージする力がディスチャージする力よりも大きくなる。このため、エミッタフォロア回路では、出力電圧Voutに歪みが発生する。

図17(a)、(b)は、出力電圧Voutの歪みを説明するための図である。図17(a)、(b)の縦軸は出力電圧Voutの信号レベル、横軸は時間を示している。図17(a)は、入力電圧Vinが高電圧に向かう場合と低電圧側に向かう場合とで出力電圧Voutの振幅が同じ状態になる場合を示している。図17(b)は、入力電圧Vinが高電圧に向かう場合と低電圧側に向かう場合とで出力電圧Voutの振幅が異なる場合を示している。図17(b)に示したVoutでは、出力電圧Voutの正弦波の下半分の振幅が小さくなり、3次の高調波歪みが発生している。

【0010】

図17(b)に示した歪みを解消するためには、エミッタフォロア回路、ソースフォロア回路のディスチャージの能力とチャージ能力とを近づける必要がある。エミッタフォロア回路、ソースフォロア回路のディスチャージ能力を高めるためには、電流源702から供給される電流量を多くすればよい。つまり、出力電圧Voutの歪み特性とエミッタフォロア回路、あるいはソースフォロア回路全体の電流量とは、トレードオフの関係にあるといえる。

【0011】

このようなエミッタフォロア回路、ソースフォロア回路は、いわば、チャージする力は十分であるにもかかわらず、ディスチャージする力が足りないために、トランジスタの特長(高いトランスコンダクタンスを持っていること)を最大限に利用していないと言える。

本発明は、上記した点に鑑みてなされたものであって、少ない電流量で出力電圧の歪みを低減できるエミッタフォロア回路、ソースフォロア回路として構成される、トランジスタ回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

以上の課題を解決するため、本発明のトランジスタ回路は、第1の電流入出力端子(例えばエミッタまたはソース)と、第2の電流入出力端子(例えばコレクタまたはドレイン)と、これら第1及び第2の電流入出力端子間の電流量を制御する電圧が印加される制御端子(例えばベースまたはゲート)と、を備え、前記第2の入出力端子が容量性の負荷(例えば図1に示した容量性負荷103)に接続されるトランジスタ(例えばバイポーラトランジスタ、またはMOSトランジスタ)と、前記トランジスタの前記第2の電流入出力端子に接続され、当該第2の電流入出力端子に電流を供給する第1電流源(例えば図1に示した機能付電流源102)と、前記制御端子に入力される前記電圧の大きさに応じて前記第1電流源の電流を制御する制御回路(例えば図1に示したコントロール回路105)と、を備えたことを特徴とする。

【0013】

また、本発明のトランジスタ回路は、上記した発明において、前記制御回路が、前記第2の電流入出力端子から出力された電流による電荷が前記容量性負荷に充電されるときよりも、前記容量性負荷から電荷が放電されるときに前記第2の電流入出力端子から出力された電流による電圧が大きくなるように、前記第1電流源の電流を制御することが望ましい。

【0014】

また、本発明のトランジスタ回路は、上記した発明において、前記制御回路が、入力信号としての前記制御端子に入力される前記電圧を反転して出力する反転回路(例えば図2に示した反転回路301)を備え、この反転回路の出力に応じて、前記第1電流源の電流量を制御することが望ましい。

また、本発明のMOSトランジスタは、上記した発明において、前記制御回路が、入力信号としての前記制御端子に入力される前記電圧(例えば図5に示した入力端子106aから入力される電圧)を一の差動入力信号とした場合の他の差動入力信号(例えば図5に示した入力端子106bから入力される電圧)に応じて、前記第1電流源の電流量を制御することが望ましい。

【0015】

また、本発明のトランジスタ回路は、上記した発明において、前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子(例えば図7に示した容量素子712)と、前記電流源用トランジスタの制御端子に所定の電圧を供給する電圧源(例えば図7に示した電圧源715)と、前記電流源用トランジスタの制御端子と前記電圧源との間に接続された抵抗素子(例えば図7に示した可変抵抗素子714)と、を備えることが望ましい。

【0016】

また、本発明のトランジスタ回路は、上記した発明において、前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタとともにカレントミラー回路を構成する制御用トランジスタ(例えば図9に示したMOSトランジスタ903)と、この制御用トランジスタの電流入出力端子に電流を供給する第2電流源(例えば図9に示した機能付き電流源902)と、を備えることが望ましい。

【0017】

また、本発明のトランジスタ回路は、上記した発明において、前記抵抗素子が、抵抗値を変更することが可能であることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記容量素子が、容量値を変更することが可能であることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記第2電流源が、前記制御用トランジスタの入力端子に供給する電流の電流量を変更することが可能であることが望ましい。

【0018】

また、本発明のトランジスタ回路は、上記した発明において、前記電流源用トランジスタの制御端子と並列に、前記電流源用トランジスタの出力端子と接続される第3電流源をさらに含むことが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

【0019】

また、本発明のトランジスタ回路は、上記した発明において、前記電流源用トランジスタが、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記制御用トランジスタが、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

【発明の効果】

【0020】

上記した本発明によれば、入力電圧が低電圧側に向かう際に、エミッタフォロア(もしくはソースフォロア)回路の電流源に流す電流量を若干増やすことにより、ディスチャージする力を増やすことが可能となる。これにより、チャージする力とディスチャージする力が同じになるように調整することが出来、出力の歪みを低減することが可能となる。従来技術では電流源の電流量を増やすことでのみ歪みを抑えてきたが、本発明により、電流量を増やすことなく低歪みが実現できるため、エミッタフォロア(もしくはソースフォロア)回路全体の電力を大幅に低減することが可能となる。

【図面の簡単な説明】

【0021】

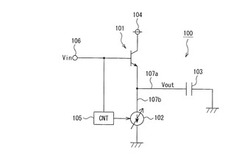

【図1】本発明の実施形態1のエミッタフォロア回路を説明するための図である。

【図2】本発明の実施形態1のソースフォロア回路を示した図である。

【図3】本発明の実施形態2のエミッタフォロア回路を説明するための図である。

【図4】本発明の実施形態2のソースフォロア回路を示した図である。

【図5】本発明の実施形態3のエミッタフォロア回路を説明するための図である。

【図6】本発明の実施形態3のソースフォロア回路を示した図である。

【図7】本発明の実施形態4のエミッタフォロア回路を説明するための図である。

【図8】本発明の実施形態4のソースフォロア回路を示した図である。

【図9】本発明の実施形態5のエミッタフォロア回路を説明するための図である。

【図10】本発明の実施形態5のソースフォロア回路を示した図である。

【図11】本発明の実施形態6のエミッタフォロア回路を説明するための図である。

【図12】本発明の実施形態6のソースフォロア回路を示した図である。

【図13】代表的なエミッタフォロア回路を説明するための図である。

【図14】代表的なソースフォロア回路を説明するための図である。

【図15】図13に示したエミッタフォロア回路において、入力電圧Vinが高電圧に向かっている状態を示した図である。

【図16】図13に示したエミッタフォロア回路において、入力電圧Vinが低電圧に向かっている状態を示した図である。

【図17】出力電圧Voutの歪みを説明するための図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態1〜6のトランジスタ回路を説明する。なお、実施形態1〜6のトランジスタ回路は、いずれもエミッタフォロア回路またはソースフォロア回路として構成されている。本明細書では、エミッタフォロア回路として構成されたトランジスタ回路を、以降エミッタフォロア回路と記す。また、ソースフォロア回路として構成されたトランジスタ回路を、ソースフォロア回路と記す。

【0023】

実施形態1〜6のエミッタフォロア回路とソースフォロア回路とは、エミッタフォロア回路がバイポーラトランジスタを含み、ソースフォロア回路がMOSトランジスタを含む点で相違している。また、バイポーラトランジスタのベース(制御端子)がMOSトランジスタのゲート(制御端子)に対応し、バイポーラトランジスタのコレクタ(第1の電流入出力端子または第2の電流入出力端子)がMOSトランジスタのドレイン(第1の電流入出力端子または第2の電流入出力端子)に対応し、バイポーラトランジスタのエミッタ(第1の電流入出力端子または第2の電流入出力端子)がMOSトランジスタのソース(第1の電流入出力端子または第2の電流入出力端子)に対応している。

【0024】

このため、本明細書では、エミッタフォロアトランジスタ回路について説明をし、エミッタフォロア回路と他の構成が同一のソースフォロア回路については図示をし、その説明を略すものとする。

(実施形態1)

図1は、本発明の実施形態1のエミッタフォロア回路100を説明するための図である。図1に示したエミッタフォロア回路100は、NPN型のバイポーラトランジスタ101を含んでいる。バイポーラトランジスタ101のベースには入力電圧Vinが入力されていて、入力電圧Vinが入力される端子106とバイポーラトランジスタ101のベースとの間にコントロール回路(図中CNTと記す)105が接続されている。

【0025】

また、バイポーラトランジスタ101のコレクタには図示しない正電源の端子104が接続されている。また、バイポーラトランジスタ101のエミッタからは出力電圧Voutが出力される。出力電圧Voutの出力端子にはノード107aが接続されていて、ノード107aには、エミッタフォロア回路100の外部に接続される容量性の負荷が接続されている。容量性の負荷によって生じる容量を、図1では、容量の記号を使って擬似的に示し、これを容量性負荷103と記す。

【0026】

また、出力電圧Voutの出力端子にはノード107bが接続され、ノード107bと負電源との間には機能付電流源102が接続されている。機能付電流源102は、供給される電流の値を変更できる、所謂可変電流源である。機能付電流源102によって供給される電流の値は、コントロール回路105によって制御されている。

コントロール回路105は、入力電圧Vinの値が上昇する(高電圧側に向かう)場合には特に動作をすることがない。このため、機能付電流源102には、予め定められた一定電の電流Icが流れる。しかし、コントロール回路105は、入力電圧Vinの値が低下する(低電圧側に向かう)場合には、電流Icよりも大きな値の電流がバイポーラトランジスタ101のエミッタに供給されるように、機能付電流源102を制御する。

【0027】

このとき、コントロール回路105は、入力電圧Vinが上昇して容量性負荷103がチャージされるときに出力される出力電圧Voutと同程度のVoutが得られるように、機能付電流源102から供給される電流量を制御する。このようなコントロール回路105の制御によれば、図11(b)に示した出力電圧Voutのコモンから見た上下の振幅を同じにすることができる。このため、実施形態1のエミッタフォロア回路は、出力電圧の歪みを低減することができる。

【0028】

また、実施形態1は、上記したように、容量性負荷103がチャージされるときには電流量の制御を行わず、容量性負荷103がディスチャージされるときにのみ容量性負荷103がチャージされるときの出力電圧Voutが得られるように機能付電流源102から供給される電流量を制御する。このため、実施形態1は、出力電圧の歪みを修正するにあたって電流の増加を必要最小限度に抑えることができる。

【0029】

図2は、実施形態1のソースフォロア回路を示した図である。図2に示したソースフォロア回路は、図1に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備える点で図1のエミッタフォロア回路と相違する。なお、実施形態1では、入力電圧Vinが低下するときに容量性負荷103がディスチャージされる。このため、実施形態1のMOSトランジスタ201には、入力電圧Vinの低下時にコンダクタンスが低下する、n型MOSトランジスタが適用される。図2においては、図1に示した構成と同様の構成については同様の符号を付し、その説明を略す。

【0030】

以上説明した実施形態1は、エミッタフォロア回路のバイポーラトランジスタ101をNPN型のバイポーラトランジスタとし、ソースフォロア回路のMOSトランジスタ201をn型のMOSトランジスタとしている。しかし、実施形態1は、このような構成に限定されるものではない。すなわち、実施形態1は、エミッタフォロア回路にPNP型のバイポーラトランジスタを適用することもできる。また、ソースフォロア回路にp型のMOSトランジスタを適用することもできる。

【0031】

なお、エミッタフォロア回路にPNP型のバイポーラトランジスタを適用する場合には、入力電圧Vinの値が上昇する場合に、電流Icよりも大きな値の電流がバイポーラトランジスタ101のエミッタに供給されるように、機能付電流源102を制御する。また、ソースフォロア回路にp型のバイポーラトランジスタを適用する場合には、入力電圧Vinの値が上昇する場合に、電流Icよりも大きな値の電流がバイポーラトランジスタ101のソースに供給されるように、機能付電流源102を制御する。

【0032】

(実施形態2)

次に、本発明の実施形態2のエミッタフォロア回路、ソースフォロア回路について説明する。図3は、実施形態2のエミッタフォロア回路300を説明するための図である。図3において、図1に示したエミッタフォロア回路100に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0033】

実施形態2のエミッタフォロア回路300では、実施形態1のエミッタフォロア回路に加えて、入力電圧Vinが入力される端子とコントロール回路105との間に反転回路(インバータ)301が挿入されている。

実施形態2のエミッタフォロア回路300においては、入力電圧Vinが反転されてコントロール回路105に入力される。コントロール回路105は、入力された信号を、機能付電流源102を制御する信号(以下、制御信号と記す)として機能付電流源102に入力する。

【0034】

実施形態2では、機能付電流源102をバイポーラトランジスタ101と導電型が同じバイポーラトランジスタで構成する。そして、制御信号が、このバイポーラトランジスタのベースに入力されるものとする。このような場合、例えば、入力電圧Vinが低下するとき、機能付電流源102としてのバイポーラトランジスタのベースの電圧が高くなる。このため、実施形態2のエミッタフォロア回路では、機能付電流源102から供給される電流量が増加し、ディスチャージ時の出力電圧Voutを高めることができる。

【0035】

なお、実施形態2のエミッタフォロア回路は、コントロール回路105を、反転回路301を内蔵するように構成することによっても実現することができる。ただし、コントロール回路105の入力部分に反転回路301を挿入すれば、コントロール回路105内で信号を反転させる必要が無くなる。このため、図3に示したエミッタフォロア回路では、コントロール回路105内で信号を反転させる必要が無くなる。

【0036】

図4は、実施形態2のソースフォロア回路400を示した図である。実施形態2のソースフォロア回路400は、バイポーラトランジスタ101に代えて、MOSトランジスタ201を備えている点でのみ図3に示したエミッタフォロア回路300と相違する。また、図4に示したソースフォロア回路400では、機能付電流源102がMOSトランジスタ201と同じ導電型のMOSトランジスタを含み、コントローラ回路105から出力される制御信号が、このMOSトランジスタのゲートに入力されるものとする。

【0037】

(実施形態3)

次に、本発明の実施形態3のエミッタフォロア回路、ソースフォロア回路について説明する。図5は、実施形態3のエミッタフォロア回路500を説明するための図である。図5において、図1に示したエミッタフォロア回路100に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0038】

図5に示すエミッタフォロア回路500は、コントロール回路105が入力端子106aと差動の入力電圧−Vinが入力される入力端子106bに接続されている点で図1に示したエミッタフォロア回路100と異なっている。また、エミッタフォロア回路500においても、機能付電流源102がバイポーラトランジスタ101と同じ導電型のバイポーラトランジスタを含み、入力電圧−Vinは、このバイポーラトランジスタのベースに入力するものとする。

【0039】

実施形態3のエミッタフォロア回路500の構成によれば、図3に示した反転回路301を挿入することなく、コントロール回路105に入力電圧Vinを反転した信号を入力することができる。このため、コントロール回路105内で信号を反転させる必要がなくなる。

図6は、実施形態3のソースフォロア回路600を示した図である。実施形態3のソースフォロア回路600は、バイポーラトランジスタ101に代えて、MOSトランジスタ201を備えている点でのみ図5に示したエミッタフォロア回路500と相違する。ソースフォロア回路600は、機能付電流源102がMOSトランジスタ201と同じ導電型のMOSトランジスタを含み、入力電圧−Vinは、このMOSトランジスタのゲートに入力するものとする。

【0040】

(実施形態4)

次に、本発明の実施形態3のエミッタフォロア回路、ソースフォロア回路について説明する。図7は、実施形態4のエミッタフォロア回路710を説明するための図である。図7において、図5に示したエミッタフォロア回路500に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0041】

実施形態4のエミッタフォロア回路は、容量がCpuの容量素子712、抵抗値が変更可能な可変抵抗素子714(抵抗値をRcntと記す)、電圧がVbの電圧源715、バイポーラトランジスタ711を備え、図5に示した機能付電流源102、コントロール回路105を備えていない点で実施形態3のエミッタフォロア回路と相違する。実施形態4のエミッタフォロア回路では、容量素子712、可変抵抗素子714、電圧源715が図5に示したコントロール回路105の機能を持つ。また、バイポーラトランジスタ711が、機能付電流源102として機能する。

【0042】

実施形態5のエミッタフォロア回路710において、入力電圧−Vinが入力される入力端子106bは、容量素子712を介してバイポーラトランジスタ711のベースが接続されているノード(電圧Vcntが印加されている)713と接続される。また、ノード713は、可変抵抗素子714を介して電圧源715に接続される。電源715の電圧Vbの値は、バイポーラトランジスタ711に合わせて設定される。

【0043】

このような実施形態4のエミッタフォロア回路710では、可変抵抗素子714の抵抗値Rcntを調整することにより、入力電圧−Vinからみた、ノード713におけるポール位置と位相変化とを調整し、ノード713における電圧Vcntの振幅及び位相を調整できる。

例えば、可変抵抗素子714の抵抗値Rcntを小さくすれば、ポール(エミッタフォロア回路の電圧利得の周波数に対する傾きが変化する周波数)は高周波側にシフトし、信号はより減衰し、位相はマイナス側にシフトする。入力電圧Vinが低下するときと、高まるときとのチャージ、ディスチャージのバランスが最適となるポールの位置(周波数)が存在する。

【0044】

このため、実施形態4では、可変抵抗素子714の抵抗値Rcntを調節することによってポールをチャージ、ディスチャージのバランスが最適にし、出力電圧Voutの歪みを最小限に抑えることが可能となる。なお、実施形態4の構成では、容量素子712の容量Cpuの容量値を変えることによってもポール位置の調整は可能である。

図8は、実施形態4のソースフォロア回路810を示した図である。図8に示したソースフォロア回路810は、エミッタフォロア回路710のバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備える点のみでエミッタフォロア回路710と相違する。

【0045】

(実施形態5)

次に、本発明の実施形態5のエミッタフォロア回路、ソースフォロア回路について説明する。図9は、実施形態5のエミッタフォロア回路900を説明するための図である。図9において、図7に示したエミッタフォロア回路710に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0046】

実施形態5のエミッタフォロア回路900は、エミッタフォロア回路710の可変抵抗素子714及び電圧源715を備えていない。そして、可変抵抗素子714、電圧源715の代わりに、バイポーラトランジスタ903と、バイポーラトランジスタ903のコレクタに接続される機能付電流源902とを備えている。バイポーラトランジスタ903は、カレントミラー元として使用される。

【0047】

バイポーラトランジスタ711、903のベースに接続されたノード713は、バイポーラトランジスタ903のベースとコレクタとをショートするように、バイポーラトランジスタ903にダイオード接続されている。また、ノード713には機能付電流源902も接続され、電流源902に接続される正電源の端子を端子901とする。

このような実施形態5によれば、バイポーラトランジスタ903は、カレントミラーのミラー元として機能する。

【0048】

また、前述した実施形態4において、入力電圧−Vinから見るポールが、容量素子712の容量Cpu及び可変抵抗素子714の抵抗値Rcntで決まっていた。しかし、実施形態5において、入力電圧−Vinから見るポールは、バイポーラトランジスタ903のトランスコンダクタンスgm、すなわち、バイポーラトランジスタ903のサイズと機能付電流源902に流れる電流量Ic1によって決する。

【0049】

つまり、実施形態5は、電流源902の電流Ic1を調整することで、入力電圧−Vinからみた、ノード713における電圧Vcntのポール位置と位相変化を調整し、電圧Vcntの振幅及び位相を調整できる。

例えば、電流Ic1を大きくすれば、バイポーラトランジスタ903のトランスコンダクタンスgmは大きくなり、ポールの位置は高周波側にシフトする。このとき、電圧Vcntはより減衰し、その位相はマイナス側にシフトする。ポールには、入力電圧Vinが低下するときと高まるときのチャージ、ディスチャージのバランスが最適となる位置(周波数)が存在する。このため、実施形態5では、電流源902の電流Ic1を調節し、出力電圧Voutの歪みを最小限に抑えることが可能となる。

【0050】

なお、実施形態5では、容量素子712の容量Cpuを変えることによってもポール位置の調整が可能である。

図10は、実施形態5のソースフォロア回路110を示した図である。図10に示したソースフォロア回路110は、図9に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備え、バイポーラトランジスタ903に代えてMOSトランジスタ113を備える点でのみエミッタフォロア回路900と相違する。

【0051】

(実施形態6)

次に、本発明の実施形態6のエミッタフォロア回路、ソースフォロア回路について説明する。図11は、実施形態6のエミッタフォロア回路120を説明するための図である。図11において、図9に示したエミッタフォロア回路900に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0052】

実施形態6のエミッタフォロア回路120は、出力電圧Voutが出力されるノード107aに、電流Ic2を供給する電流源121を並列に接続した点でのみ実施形態5のエミッタフォロア回路900と相違する。実施形態6のエミッタフォロア回路120は、電流Ic2を供給する電流源121を接続したことによってチャージ、ディスチャージのバランス関係にオフセットを入れることができる。このため、実施形態5は、出力電圧Voutのバランスを最適な状態に調整することが可能になる。

【0053】

図12は、実施形態6のソースフォロア回路130を示した図である。ソースフォロア回路130は、図11に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備え、バイポーラトランジスタ903に代えてMOSトランジスタ113を備える点でのみエミッタフォロア回路120と相違する。

【0054】

以上説明した各実施形態は、例えば、各トランジスタの構成やサイズ、各コンデンサの容量及び接続位置等については本発明が理解、実施できる程度に概略的に示したものにすぎない。したがって、本発明は、以上の実施形態に限定されるものではなく、エミッタフォロア回路、ソースフォロア回路を構成するバッファ等の設計要素に合わせて、特許請求の範囲に示される技術的思想の範囲を逸脱しない限り様々な形態に変更することができる。また、本発明の各実施形態は、バッファ単体としてではなく、例えばゲインアンプの出力バッファ部分に前述したエミッタフォロア回路、あるいはソースフォロア回路を使用することもできる。その他、各実施形態のエミッタフォロア回路、ソースフォロア回路は、様々な回路において適応可能な技術である。

【産業上の利用可能性】

【0055】

本発明は、バッファ等を構成するエミッタフォロア回路、ソースフォロア回路に適用される。

【符号の説明】

【0056】

100、300、500、700、900、120 エミッタフォロア回路

101、711、903、 バイポーラトランジスタ

102、902 機能付電流源

103 容量性負荷

104 端子

105 コントロール回路

106、106a、106b 入力端子

107a、107b ノード

110、130、200、400、600、810 ソースフォロア回路

113、201、811 MOSトランジスタ

121 電流源

301 反転回路

712 容量素子

715 電圧源

【技術分野】

【0001】

本発明は、トランジスタ回路に関し、特に、エミッタフォロア回路、ソースフォロア回路として構成されるトランジスタ回路に関する。

【背景技術】

【0002】

高速の入力電圧に対し、低インピーダンス負荷回路やスイッチトキャパシタ回路を駆動する有効な回路として、一般にエミッタフォロア回路、あるいはソースフォロア回路が挙げられる(例えば特許文献1参照)。エミッタフォロア回路、ソースフォロア回路は、ゲインを持たない(ゲイン≒0dB)。

ただし、エミッタフォロア回路については、入力がバイポーラトランジスタのベースに接続されることでハイインピーダンスになる。また、ソースフォロア回路については、入力がMOSトランジスタのゲートに接続されることでハイインピーダンスになる。さらに、エミッタフォロア回路、ソースフォロア回路のいずれもが、トランジスタのトランスコンダクタンス(gm)で出力負荷を駆動できるため、大きな負荷を駆動する場合や高周波の信号を処理する場合でも、低消費電力で低歪みの信号を出力することが可能である。

【0003】

図13は、代表的なエミッタフォロア回路700を説明するための図である。エミッタフォロア回路は、バイポーラトランジスタ701を含み、バイポーラトランジスタ701のコレクタには正電源(正電源の端子を図中に704の符号を付して示す)が接続されている。エミッタは、出力電圧Voutに接続される。出力電圧Voutの一方と負電源との間には電流源702が接続されてバイポーラトランジスタ701に電流が供給される。また、他方と負電源との間には、外部に接続される容量性の負荷を疑似的に示し、容量性負荷703と記す。

【0004】

図14は、代表的なソースフォロア回路800を説明するための図である。ソースフォロア回路800は、図7に示したエミッタフォロア回路700のバイポーラトランジスタ701をMOSトランジスタ801に代えた構成を有している。このため、ソースフォロア回路800を図14に示し、その説明を略すものとする。

エミッタフォロア回路700、ソースフォロア回路800の出力電圧Voutの電圧は、以下の式(1)で表される。なお、式(1)中のVbeは、バイポーラトランジスタ701のベース・エミッタ間電圧(ソースフォロア回路800ではMOSトランジスタ801のゲート、ソース間電圧)。Vbeはエミッタ電流とトランジスタのプロセス条件によって決まる値である。このため、エミッタ電流が一定の環境下ではVbeが一定なので、Voutの変化量は常にVinの変化量に追随し、VoutはAC的にVinと同じ電圧になる。

【0005】

Vout=Vin−Vbe …式(1)

図15は、図13に示したエミッタフォロア回路700において、入力電圧Vinが高電圧に向かっている状態を示している。また、図16は、エミッタフォロア回路700において、入力電圧Vinが低電圧に向かっている状態を示している。以下、図15、図16に示したエミッタフォロア回路の動作について説明する。

【0006】

先ず、図15に示したように、入力電圧Vinが高電圧に向かう場合、バイポーラトランジスタNPN1がONの状態になり、図示しない正電源の端子704からバイポーラトランジスタ701のコレクタ、エミッタを通って電荷が容量性負荷703にチャージされる。このときのAC帯域は、バイポーラトランジスタ701のトランスコンダクタンス(gm)によって決まる。

【0007】

また、図16に示したように、入力電圧Vinが低電圧に向かう場合、バイポーラトランジスタ701はオフ状態になる。このとき、電流源702に流れる電流により、容量性負荷703に電荷がディスチャージされる。AC帯域は、電流源の電流量によって決まる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭59−168720号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、バイポーラトランジスタ701のトランスコンダクタンス(gm)は、比較的大きいため、容量性負荷703に電荷をチャージする力がディスチャージする力よりも大きくなる。このため、エミッタフォロア回路では、出力電圧Voutに歪みが発生する。

図17(a)、(b)は、出力電圧Voutの歪みを説明するための図である。図17(a)、(b)の縦軸は出力電圧Voutの信号レベル、横軸は時間を示している。図17(a)は、入力電圧Vinが高電圧に向かう場合と低電圧側に向かう場合とで出力電圧Voutの振幅が同じ状態になる場合を示している。図17(b)は、入力電圧Vinが高電圧に向かう場合と低電圧側に向かう場合とで出力電圧Voutの振幅が異なる場合を示している。図17(b)に示したVoutでは、出力電圧Voutの正弦波の下半分の振幅が小さくなり、3次の高調波歪みが発生している。

【0010】

図17(b)に示した歪みを解消するためには、エミッタフォロア回路、ソースフォロア回路のディスチャージの能力とチャージ能力とを近づける必要がある。エミッタフォロア回路、ソースフォロア回路のディスチャージ能力を高めるためには、電流源702から供給される電流量を多くすればよい。つまり、出力電圧Voutの歪み特性とエミッタフォロア回路、あるいはソースフォロア回路全体の電流量とは、トレードオフの関係にあるといえる。

【0011】

このようなエミッタフォロア回路、ソースフォロア回路は、いわば、チャージする力は十分であるにもかかわらず、ディスチャージする力が足りないために、トランジスタの特長(高いトランスコンダクタンスを持っていること)を最大限に利用していないと言える。

本発明は、上記した点に鑑みてなされたものであって、少ない電流量で出力電圧の歪みを低減できるエミッタフォロア回路、ソースフォロア回路として構成される、トランジスタ回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

以上の課題を解決するため、本発明のトランジスタ回路は、第1の電流入出力端子(例えばエミッタまたはソース)と、第2の電流入出力端子(例えばコレクタまたはドレイン)と、これら第1及び第2の電流入出力端子間の電流量を制御する電圧が印加される制御端子(例えばベースまたはゲート)と、を備え、前記第2の入出力端子が容量性の負荷(例えば図1に示した容量性負荷103)に接続されるトランジスタ(例えばバイポーラトランジスタ、またはMOSトランジスタ)と、前記トランジスタの前記第2の電流入出力端子に接続され、当該第2の電流入出力端子に電流を供給する第1電流源(例えば図1に示した機能付電流源102)と、前記制御端子に入力される前記電圧の大きさに応じて前記第1電流源の電流を制御する制御回路(例えば図1に示したコントロール回路105)と、を備えたことを特徴とする。

【0013】

また、本発明のトランジスタ回路は、上記した発明において、前記制御回路が、前記第2の電流入出力端子から出力された電流による電荷が前記容量性負荷に充電されるときよりも、前記容量性負荷から電荷が放電されるときに前記第2の電流入出力端子から出力された電流による電圧が大きくなるように、前記第1電流源の電流を制御することが望ましい。

【0014】

また、本発明のトランジスタ回路は、上記した発明において、前記制御回路が、入力信号としての前記制御端子に入力される前記電圧を反転して出力する反転回路(例えば図2に示した反転回路301)を備え、この反転回路の出力に応じて、前記第1電流源の電流量を制御することが望ましい。

また、本発明のMOSトランジスタは、上記した発明において、前記制御回路が、入力信号としての前記制御端子に入力される前記電圧(例えば図5に示した入力端子106aから入力される電圧)を一の差動入力信号とした場合の他の差動入力信号(例えば図5に示した入力端子106bから入力される電圧)に応じて、前記第1電流源の電流量を制御することが望ましい。

【0015】

また、本発明のトランジスタ回路は、上記した発明において、前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子(例えば図7に示した容量素子712)と、前記電流源用トランジスタの制御端子に所定の電圧を供給する電圧源(例えば図7に示した電圧源715)と、前記電流源用トランジスタの制御端子と前記電圧源との間に接続された抵抗素子(例えば図7に示した可変抵抗素子714)と、を備えることが望ましい。

【0016】

また、本発明のトランジスタ回路は、上記した発明において、前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタとともにカレントミラー回路を構成する制御用トランジスタ(例えば図9に示したMOSトランジスタ903)と、この制御用トランジスタの電流入出力端子に電流を供給する第2電流源(例えば図9に示した機能付き電流源902)と、を備えることが望ましい。

【0017】

また、本発明のトランジスタ回路は、上記した発明において、前記抵抗素子が、抵抗値を変更することが可能であることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記容量素子が、容量値を変更することが可能であることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記第2電流源が、前記制御用トランジスタの入力端子に供給する電流の電流量を変更することが可能であることが望ましい。

【0018】

また、本発明のトランジスタ回路は、上記した発明において、前記電流源用トランジスタの制御端子と並列に、前記電流源用トランジスタの出力端子と接続される第3電流源をさらに含むことが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

【0019】

また、本発明のトランジスタ回路は、上記した発明において、前記電流源用トランジスタが、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

また、本発明のトランジスタ回路は、上記した発明において、前記制御用トランジスタが、バイポーラトランジスタまたはMOSトランジスタであることが望ましい。

【発明の効果】

【0020】

上記した本発明によれば、入力電圧が低電圧側に向かう際に、エミッタフォロア(もしくはソースフォロア)回路の電流源に流す電流量を若干増やすことにより、ディスチャージする力を増やすことが可能となる。これにより、チャージする力とディスチャージする力が同じになるように調整することが出来、出力の歪みを低減することが可能となる。従来技術では電流源の電流量を増やすことでのみ歪みを抑えてきたが、本発明により、電流量を増やすことなく低歪みが実現できるため、エミッタフォロア(もしくはソースフォロア)回路全体の電力を大幅に低減することが可能となる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施形態1のエミッタフォロア回路を説明するための図である。

【図2】本発明の実施形態1のソースフォロア回路を示した図である。

【図3】本発明の実施形態2のエミッタフォロア回路を説明するための図である。

【図4】本発明の実施形態2のソースフォロア回路を示した図である。

【図5】本発明の実施形態3のエミッタフォロア回路を説明するための図である。

【図6】本発明の実施形態3のソースフォロア回路を示した図である。

【図7】本発明の実施形態4のエミッタフォロア回路を説明するための図である。

【図8】本発明の実施形態4のソースフォロア回路を示した図である。

【図9】本発明の実施形態5のエミッタフォロア回路を説明するための図である。

【図10】本発明の実施形態5のソースフォロア回路を示した図である。

【図11】本発明の実施形態6のエミッタフォロア回路を説明するための図である。

【図12】本発明の実施形態6のソースフォロア回路を示した図である。

【図13】代表的なエミッタフォロア回路を説明するための図である。

【図14】代表的なソースフォロア回路を説明するための図である。

【図15】図13に示したエミッタフォロア回路において、入力電圧Vinが高電圧に向かっている状態を示した図である。

【図16】図13に示したエミッタフォロア回路において、入力電圧Vinが低電圧に向かっている状態を示した図である。

【図17】出力電圧Voutの歪みを説明するための図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態1〜6のトランジスタ回路を説明する。なお、実施形態1〜6のトランジスタ回路は、いずれもエミッタフォロア回路またはソースフォロア回路として構成されている。本明細書では、エミッタフォロア回路として構成されたトランジスタ回路を、以降エミッタフォロア回路と記す。また、ソースフォロア回路として構成されたトランジスタ回路を、ソースフォロア回路と記す。

【0023】

実施形態1〜6のエミッタフォロア回路とソースフォロア回路とは、エミッタフォロア回路がバイポーラトランジスタを含み、ソースフォロア回路がMOSトランジスタを含む点で相違している。また、バイポーラトランジスタのベース(制御端子)がMOSトランジスタのゲート(制御端子)に対応し、バイポーラトランジスタのコレクタ(第1の電流入出力端子または第2の電流入出力端子)がMOSトランジスタのドレイン(第1の電流入出力端子または第2の電流入出力端子)に対応し、バイポーラトランジスタのエミッタ(第1の電流入出力端子または第2の電流入出力端子)がMOSトランジスタのソース(第1の電流入出力端子または第2の電流入出力端子)に対応している。

【0024】

このため、本明細書では、エミッタフォロアトランジスタ回路について説明をし、エミッタフォロア回路と他の構成が同一のソースフォロア回路については図示をし、その説明を略すものとする。

(実施形態1)

図1は、本発明の実施形態1のエミッタフォロア回路100を説明するための図である。図1に示したエミッタフォロア回路100は、NPN型のバイポーラトランジスタ101を含んでいる。バイポーラトランジスタ101のベースには入力電圧Vinが入力されていて、入力電圧Vinが入力される端子106とバイポーラトランジスタ101のベースとの間にコントロール回路(図中CNTと記す)105が接続されている。

【0025】

また、バイポーラトランジスタ101のコレクタには図示しない正電源の端子104が接続されている。また、バイポーラトランジスタ101のエミッタからは出力電圧Voutが出力される。出力電圧Voutの出力端子にはノード107aが接続されていて、ノード107aには、エミッタフォロア回路100の外部に接続される容量性の負荷が接続されている。容量性の負荷によって生じる容量を、図1では、容量の記号を使って擬似的に示し、これを容量性負荷103と記す。

【0026】

また、出力電圧Voutの出力端子にはノード107bが接続され、ノード107bと負電源との間には機能付電流源102が接続されている。機能付電流源102は、供給される電流の値を変更できる、所謂可変電流源である。機能付電流源102によって供給される電流の値は、コントロール回路105によって制御されている。

コントロール回路105は、入力電圧Vinの値が上昇する(高電圧側に向かう)場合には特に動作をすることがない。このため、機能付電流源102には、予め定められた一定電の電流Icが流れる。しかし、コントロール回路105は、入力電圧Vinの値が低下する(低電圧側に向かう)場合には、電流Icよりも大きな値の電流がバイポーラトランジスタ101のエミッタに供給されるように、機能付電流源102を制御する。

【0027】

このとき、コントロール回路105は、入力電圧Vinが上昇して容量性負荷103がチャージされるときに出力される出力電圧Voutと同程度のVoutが得られるように、機能付電流源102から供給される電流量を制御する。このようなコントロール回路105の制御によれば、図11(b)に示した出力電圧Voutのコモンから見た上下の振幅を同じにすることができる。このため、実施形態1のエミッタフォロア回路は、出力電圧の歪みを低減することができる。

【0028】

また、実施形態1は、上記したように、容量性負荷103がチャージされるときには電流量の制御を行わず、容量性負荷103がディスチャージされるときにのみ容量性負荷103がチャージされるときの出力電圧Voutが得られるように機能付電流源102から供給される電流量を制御する。このため、実施形態1は、出力電圧の歪みを修正するにあたって電流の増加を必要最小限度に抑えることができる。

【0029】

図2は、実施形態1のソースフォロア回路を示した図である。図2に示したソースフォロア回路は、図1に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備える点で図1のエミッタフォロア回路と相違する。なお、実施形態1では、入力電圧Vinが低下するときに容量性負荷103がディスチャージされる。このため、実施形態1のMOSトランジスタ201には、入力電圧Vinの低下時にコンダクタンスが低下する、n型MOSトランジスタが適用される。図2においては、図1に示した構成と同様の構成については同様の符号を付し、その説明を略す。

【0030】

以上説明した実施形態1は、エミッタフォロア回路のバイポーラトランジスタ101をNPN型のバイポーラトランジスタとし、ソースフォロア回路のMOSトランジスタ201をn型のMOSトランジスタとしている。しかし、実施形態1は、このような構成に限定されるものではない。すなわち、実施形態1は、エミッタフォロア回路にPNP型のバイポーラトランジスタを適用することもできる。また、ソースフォロア回路にp型のMOSトランジスタを適用することもできる。

【0031】

なお、エミッタフォロア回路にPNP型のバイポーラトランジスタを適用する場合には、入力電圧Vinの値が上昇する場合に、電流Icよりも大きな値の電流がバイポーラトランジスタ101のエミッタに供給されるように、機能付電流源102を制御する。また、ソースフォロア回路にp型のバイポーラトランジスタを適用する場合には、入力電圧Vinの値が上昇する場合に、電流Icよりも大きな値の電流がバイポーラトランジスタ101のソースに供給されるように、機能付電流源102を制御する。

【0032】

(実施形態2)

次に、本発明の実施形態2のエミッタフォロア回路、ソースフォロア回路について説明する。図3は、実施形態2のエミッタフォロア回路300を説明するための図である。図3において、図1に示したエミッタフォロア回路100に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0033】

実施形態2のエミッタフォロア回路300では、実施形態1のエミッタフォロア回路に加えて、入力電圧Vinが入力される端子とコントロール回路105との間に反転回路(インバータ)301が挿入されている。

実施形態2のエミッタフォロア回路300においては、入力電圧Vinが反転されてコントロール回路105に入力される。コントロール回路105は、入力された信号を、機能付電流源102を制御する信号(以下、制御信号と記す)として機能付電流源102に入力する。

【0034】

実施形態2では、機能付電流源102をバイポーラトランジスタ101と導電型が同じバイポーラトランジスタで構成する。そして、制御信号が、このバイポーラトランジスタのベースに入力されるものとする。このような場合、例えば、入力電圧Vinが低下するとき、機能付電流源102としてのバイポーラトランジスタのベースの電圧が高くなる。このため、実施形態2のエミッタフォロア回路では、機能付電流源102から供給される電流量が増加し、ディスチャージ時の出力電圧Voutを高めることができる。

【0035】

なお、実施形態2のエミッタフォロア回路は、コントロール回路105を、反転回路301を内蔵するように構成することによっても実現することができる。ただし、コントロール回路105の入力部分に反転回路301を挿入すれば、コントロール回路105内で信号を反転させる必要が無くなる。このため、図3に示したエミッタフォロア回路では、コントロール回路105内で信号を反転させる必要が無くなる。

【0036】

図4は、実施形態2のソースフォロア回路400を示した図である。実施形態2のソースフォロア回路400は、バイポーラトランジスタ101に代えて、MOSトランジスタ201を備えている点でのみ図3に示したエミッタフォロア回路300と相違する。また、図4に示したソースフォロア回路400では、機能付電流源102がMOSトランジスタ201と同じ導電型のMOSトランジスタを含み、コントローラ回路105から出力される制御信号が、このMOSトランジスタのゲートに入力されるものとする。

【0037】

(実施形態3)

次に、本発明の実施形態3のエミッタフォロア回路、ソースフォロア回路について説明する。図5は、実施形態3のエミッタフォロア回路500を説明するための図である。図5において、図1に示したエミッタフォロア回路100に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0038】

図5に示すエミッタフォロア回路500は、コントロール回路105が入力端子106aと差動の入力電圧−Vinが入力される入力端子106bに接続されている点で図1に示したエミッタフォロア回路100と異なっている。また、エミッタフォロア回路500においても、機能付電流源102がバイポーラトランジスタ101と同じ導電型のバイポーラトランジスタを含み、入力電圧−Vinは、このバイポーラトランジスタのベースに入力するものとする。

【0039】

実施形態3のエミッタフォロア回路500の構成によれば、図3に示した反転回路301を挿入することなく、コントロール回路105に入力電圧Vinを反転した信号を入力することができる。このため、コントロール回路105内で信号を反転させる必要がなくなる。

図6は、実施形態3のソースフォロア回路600を示した図である。実施形態3のソースフォロア回路600は、バイポーラトランジスタ101に代えて、MOSトランジスタ201を備えている点でのみ図5に示したエミッタフォロア回路500と相違する。ソースフォロア回路600は、機能付電流源102がMOSトランジスタ201と同じ導電型のMOSトランジスタを含み、入力電圧−Vinは、このMOSトランジスタのゲートに入力するものとする。

【0040】

(実施形態4)

次に、本発明の実施形態3のエミッタフォロア回路、ソースフォロア回路について説明する。図7は、実施形態4のエミッタフォロア回路710を説明するための図である。図7において、図5に示したエミッタフォロア回路500に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0041】

実施形態4のエミッタフォロア回路は、容量がCpuの容量素子712、抵抗値が変更可能な可変抵抗素子714(抵抗値をRcntと記す)、電圧がVbの電圧源715、バイポーラトランジスタ711を備え、図5に示した機能付電流源102、コントロール回路105を備えていない点で実施形態3のエミッタフォロア回路と相違する。実施形態4のエミッタフォロア回路では、容量素子712、可変抵抗素子714、電圧源715が図5に示したコントロール回路105の機能を持つ。また、バイポーラトランジスタ711が、機能付電流源102として機能する。

【0042】

実施形態5のエミッタフォロア回路710において、入力電圧−Vinが入力される入力端子106bは、容量素子712を介してバイポーラトランジスタ711のベースが接続されているノード(電圧Vcntが印加されている)713と接続される。また、ノード713は、可変抵抗素子714を介して電圧源715に接続される。電源715の電圧Vbの値は、バイポーラトランジスタ711に合わせて設定される。

【0043】

このような実施形態4のエミッタフォロア回路710では、可変抵抗素子714の抵抗値Rcntを調整することにより、入力電圧−Vinからみた、ノード713におけるポール位置と位相変化とを調整し、ノード713における電圧Vcntの振幅及び位相を調整できる。

例えば、可変抵抗素子714の抵抗値Rcntを小さくすれば、ポール(エミッタフォロア回路の電圧利得の周波数に対する傾きが変化する周波数)は高周波側にシフトし、信号はより減衰し、位相はマイナス側にシフトする。入力電圧Vinが低下するときと、高まるときとのチャージ、ディスチャージのバランスが最適となるポールの位置(周波数)が存在する。

【0044】

このため、実施形態4では、可変抵抗素子714の抵抗値Rcntを調節することによってポールをチャージ、ディスチャージのバランスが最適にし、出力電圧Voutの歪みを最小限に抑えることが可能となる。なお、実施形態4の構成では、容量素子712の容量Cpuの容量値を変えることによってもポール位置の調整は可能である。

図8は、実施形態4のソースフォロア回路810を示した図である。図8に示したソースフォロア回路810は、エミッタフォロア回路710のバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備える点のみでエミッタフォロア回路710と相違する。

【0045】

(実施形態5)

次に、本発明の実施形態5のエミッタフォロア回路、ソースフォロア回路について説明する。図9は、実施形態5のエミッタフォロア回路900を説明するための図である。図9において、図7に示したエミッタフォロア回路710に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0046】

実施形態5のエミッタフォロア回路900は、エミッタフォロア回路710の可変抵抗素子714及び電圧源715を備えていない。そして、可変抵抗素子714、電圧源715の代わりに、バイポーラトランジスタ903と、バイポーラトランジスタ903のコレクタに接続される機能付電流源902とを備えている。バイポーラトランジスタ903は、カレントミラー元として使用される。

【0047】

バイポーラトランジスタ711、903のベースに接続されたノード713は、バイポーラトランジスタ903のベースとコレクタとをショートするように、バイポーラトランジスタ903にダイオード接続されている。また、ノード713には機能付電流源902も接続され、電流源902に接続される正電源の端子を端子901とする。

このような実施形態5によれば、バイポーラトランジスタ903は、カレントミラーのミラー元として機能する。

【0048】

また、前述した実施形態4において、入力電圧−Vinから見るポールが、容量素子712の容量Cpu及び可変抵抗素子714の抵抗値Rcntで決まっていた。しかし、実施形態5において、入力電圧−Vinから見るポールは、バイポーラトランジスタ903のトランスコンダクタンスgm、すなわち、バイポーラトランジスタ903のサイズと機能付電流源902に流れる電流量Ic1によって決する。

【0049】

つまり、実施形態5は、電流源902の電流Ic1を調整することで、入力電圧−Vinからみた、ノード713における電圧Vcntのポール位置と位相変化を調整し、電圧Vcntの振幅及び位相を調整できる。

例えば、電流Ic1を大きくすれば、バイポーラトランジスタ903のトランスコンダクタンスgmは大きくなり、ポールの位置は高周波側にシフトする。このとき、電圧Vcntはより減衰し、その位相はマイナス側にシフトする。ポールには、入力電圧Vinが低下するときと高まるときのチャージ、ディスチャージのバランスが最適となる位置(周波数)が存在する。このため、実施形態5では、電流源902の電流Ic1を調節し、出力電圧Voutの歪みを最小限に抑えることが可能となる。

【0050】

なお、実施形態5では、容量素子712の容量Cpuを変えることによってもポール位置の調整が可能である。

図10は、実施形態5のソースフォロア回路110を示した図である。図10に示したソースフォロア回路110は、図9に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備え、バイポーラトランジスタ903に代えてMOSトランジスタ113を備える点でのみエミッタフォロア回路900と相違する。

【0051】

(実施形態6)

次に、本発明の実施形態6のエミッタフォロア回路、ソースフォロア回路について説明する。図11は、実施形態6のエミッタフォロア回路120を説明するための図である。図11において、図9に示したエミッタフォロア回路900に含まれる構成については同様の符号を付し、その説明を一部略すものとする。

【0052】

実施形態6のエミッタフォロア回路120は、出力電圧Voutが出力されるノード107aに、電流Ic2を供給する電流源121を並列に接続した点でのみ実施形態5のエミッタフォロア回路900と相違する。実施形態6のエミッタフォロア回路120は、電流Ic2を供給する電流源121を接続したことによってチャージ、ディスチャージのバランス関係にオフセットを入れることができる。このため、実施形態5は、出力電圧Voutのバランスを最適な状態に調整することが可能になる。

【0053】

図12は、実施形態6のソースフォロア回路130を示した図である。ソースフォロア回路130は、図11に示したバイポーラトランジスタ101に代えてMOSトランジスタ201を備え、バイポーラトランジスタ711に代えてMOSトランジスタ811を備え、バイポーラトランジスタ903に代えてMOSトランジスタ113を備える点でのみエミッタフォロア回路120と相違する。

【0054】

以上説明した各実施形態は、例えば、各トランジスタの構成やサイズ、各コンデンサの容量及び接続位置等については本発明が理解、実施できる程度に概略的に示したものにすぎない。したがって、本発明は、以上の実施形態に限定されるものではなく、エミッタフォロア回路、ソースフォロア回路を構成するバッファ等の設計要素に合わせて、特許請求の範囲に示される技術的思想の範囲を逸脱しない限り様々な形態に変更することができる。また、本発明の各実施形態は、バッファ単体としてではなく、例えばゲインアンプの出力バッファ部分に前述したエミッタフォロア回路、あるいはソースフォロア回路を使用することもできる。その他、各実施形態のエミッタフォロア回路、ソースフォロア回路は、様々な回路において適応可能な技術である。

【産業上の利用可能性】

【0055】

本発明は、バッファ等を構成するエミッタフォロア回路、ソースフォロア回路に適用される。

【符号の説明】

【0056】

100、300、500、700、900、120 エミッタフォロア回路

101、711、903、 バイポーラトランジスタ

102、902 機能付電流源

103 容量性負荷

104 端子

105 コントロール回路

106、106a、106b 入力端子

107a、107b ノード

110、130、200、400、600、810 ソースフォロア回路

113、201、811 MOSトランジスタ

121 電流源

301 反転回路

712 容量素子

715 電圧源

【特許請求の範囲】

【請求項1】

第1の電流入出力端子と、第2の電流入出力端子と、これら第1及び第2の電流入出力端子間の電流量を制御する電圧が印加される制御端子と、を備え、前記第2の入出力端子が容量性の負荷に接続されるトランジスタと、

前記トランジスタの前記第2の電流入出力端子に接続され、当該第2の電流入出力端子に電流を供給する第1電流源と、

前記制御端子に入力される前記電圧の大きさに応じて前記第1電流源の電流を制御する制御回路と、

を備えたことを特徴とするトランジスタ回路。

【請求項2】

前記制御回路は、前記第2の電流入出力端子から出力された電流による電荷が前記容量性負荷に充電されるときよりも、前記容量性負荷から電荷が放電されるときに前記第2の電流入出力端子から出力された電流による電圧が大きくなるように、前記第1電流源の電流を制御することを特徴とする請求項1記載のトランジスタ回路。

【請求項3】

前記制御回路は、入力信号としての前記制御端子に入力される前記電圧を反転して出力する反転回路を備え、前記反転回路の出力に応じて、前記第1電流源の電流量を制御することを特徴とする請求項1または請求項2記載のトランジスタ回路。

【請求項4】

前記制御回路は、入力信号としての前記制御端子に入力される前記電圧を一の差動入力信号とした場合の他の差動入力信号に応じて、前記第1電流源の電流量を制御することを特徴とする請求項1または請求項2記載のトランジスタ回路。

【請求項5】

前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、

前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタの制御端子に所定の電圧を供給する電圧源と、前記電流源用トランジスタの制御端子と前記電圧源との間に接続された抵抗素子と、を備えることを特徴とする請求項3または請求項4記載のトランジスタ回路。

【請求項6】

前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、

前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタとともにカレントミラー回路を構成する制御用トランジスタと、この制御用トランジスタの電流入出力端子に電流を供給する第2電流源と、を備えることを特徴とする請求項3または請求項4記載のトランジスタ回路。

【請求項7】

前記抵抗素子は、抵抗値を変更することが可能であることを特徴とする請求項5に記載のトランジスタ回路。

【請求項8】

前記容量素子は、容量値を変更することが可能であることを特徴とする請求項5または請求項6に記載のトランジスタ回路。

【請求項9】

前記第2電流源は、前記制御用トランジスタの入力端子に供給する電流の電流量を変更することが可能であることを特徴とする請求項6に記載のトランジスタ回路。

【請求項10】

前記電流源用トランジスタの制御端子と並列に、前記電流源用トランジスタの出力端子と接続される第3電流源をさらに含むことを特徴とする請求項6に記載のトランジスタ回路。

【請求項11】

前記トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項1〜10のいずれか1項に記載のトランジスタ回路。

【請求項12】

前記電流源用トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項5または6に記載のトランジスタ回路。

【請求項13】

前記制御用トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項6に記載のトランジスタ回路。

【請求項1】

第1の電流入出力端子と、第2の電流入出力端子と、これら第1及び第2の電流入出力端子間の電流量を制御する電圧が印加される制御端子と、を備え、前記第2の入出力端子が容量性の負荷に接続されるトランジスタと、

前記トランジスタの前記第2の電流入出力端子に接続され、当該第2の電流入出力端子に電流を供給する第1電流源と、

前記制御端子に入力される前記電圧の大きさに応じて前記第1電流源の電流を制御する制御回路と、

を備えたことを特徴とするトランジスタ回路。

【請求項2】

前記制御回路は、前記第2の電流入出力端子から出力された電流による電荷が前記容量性負荷に充電されるときよりも、前記容量性負荷から電荷が放電されるときに前記第2の電流入出力端子から出力された電流による電圧が大きくなるように、前記第1電流源の電流を制御することを特徴とする請求項1記載のトランジスタ回路。

【請求項3】

前記制御回路は、入力信号としての前記制御端子に入力される前記電圧を反転して出力する反転回路を備え、前記反転回路の出力に応じて、前記第1電流源の電流量を制御することを特徴とする請求項1または請求項2記載のトランジスタ回路。

【請求項4】

前記制御回路は、入力信号としての前記制御端子に入力される前記電圧を一の差動入力信号とした場合の他の差動入力信号に応じて、前記第1電流源の電流量を制御することを特徴とする請求項1または請求項2記載のトランジスタ回路。

【請求項5】

前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、

前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタの制御端子に所定の電圧を供給する電圧源と、前記電流源用トランジスタの制御端子と前記電圧源との間に接続された抵抗素子と、を備えることを特徴とする請求項3または請求項4記載のトランジスタ回路。

【請求項6】

前記第1電流源が、前記トランジスタと同じ導電型の電流源用トランジスタを含み、

前記制御回路は、前記電流源用トランジスタの制御端子と前記他の差動入力信号が供給される端子との間に接続された容量素子と、前記電流源用トランジスタとともにカレントミラー回路を構成する制御用トランジスタと、この制御用トランジスタの電流入出力端子に電流を供給する第2電流源と、を備えることを特徴とする請求項3または請求項4記載のトランジスタ回路。

【請求項7】

前記抵抗素子は、抵抗値を変更することが可能であることを特徴とする請求項5に記載のトランジスタ回路。

【請求項8】

前記容量素子は、容量値を変更することが可能であることを特徴とする請求項5または請求項6に記載のトランジスタ回路。

【請求項9】

前記第2電流源は、前記制御用トランジスタの入力端子に供給する電流の電流量を変更することが可能であることを特徴とする請求項6に記載のトランジスタ回路。

【請求項10】

前記電流源用トランジスタの制御端子と並列に、前記電流源用トランジスタの出力端子と接続される第3電流源をさらに含むことを特徴とする請求項6に記載のトランジスタ回路。

【請求項11】

前記トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項1〜10のいずれか1項に記載のトランジスタ回路。

【請求項12】

前記電流源用トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項5または6に記載のトランジスタ回路。

【請求項13】

前記制御用トランジスタは、バイポーラトランジスタまたはMOSトランジスタであることを特徴とする請求項6に記載のトランジスタ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−115489(P2013−115489A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−257710(P2011−257710)

【出願日】平成23年11月25日(2011.11.25)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月25日(2011.11.25)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

[ Back to top ]