トランジスタ駆動装置

【課題】負荷を駆動するブリッジ回路のローサイド側のトランジスタを駆動するのに好適なトランジスタ駆動装置を提供する。

【解決手段】トランジスタ駆動装置100を、駆動制御部10と、駆動電力供給部11と、電流レベル検出部12とを含んだ構成とし、駆動電力供給部11は、Hブリッジ回路のローサイド側のDMOSFETであるQ2又はQ4を、最初はPTr2のみで駆動し、Hブリッジ回路の電流検出抵抗の電圧レベルと、そのハーフ・オン状態時の電圧レベルとを比較する電流レベル検出部12からの比較信号から、Q2又はQ4がハーフ・オン状態になったと判別したときに、PTr2に加えてPTr3をオンにし、これら2つのトランジスタを介してQ2又はQ4のゲート端子に駆動電流を供給する。

【解決手段】トランジスタ駆動装置100を、駆動制御部10と、駆動電力供給部11と、電流レベル検出部12とを含んだ構成とし、駆動電力供給部11は、Hブリッジ回路のローサイド側のDMOSFETであるQ2又はQ4を、最初はPTr2のみで駆動し、Hブリッジ回路の電流検出抵抗の電圧レベルと、そのハーフ・オン状態時の電圧レベルとを比較する電流レベル検出部12からの比較信号から、Q2又はQ4がハーフ・オン状態になったと判別したときに、PTr2に加えてPTr3をオンにし、これら2つのトランジスタを介してQ2又はQ4のゲート端子に駆動電流を供給する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、モータ等の負荷を駆動するブリッジ回路のローサイド側のトランジスタをオフ状態からオン状態へと駆動するのに好適なトランジスタ駆動装置に関する。

【背景技術】

【0002】

従来、モータなどの負荷を駆動する回路として、高電位側(ハイサイド側)のトランジスタと、低電位側(ローサイド側)のトランジスタとから構成されるハーフ・ブリッジ回路、フル・ブリッジ回路などがある。このようなブリッジ回路は、ハイサイド側のトランジスタと、ローサイド側のトランジスタとがそれぞれ独立にオン又はオフに駆動制御され、負荷を通電又は非通電の状態にする。

【0003】

また、比較的高い電力を必要とし且つ高速なスイッチング動作を要求される負荷に対しては、ブリッジ回路を構成するトランジスタとして大電力用に設計されたMOSFET(metal-oxide-semiconductor field-effect transistor)が用いられる。大電力用のMOSFETとしては、例えば、DMOS(Double-Diffused MOSFET)などがある。

また、ブリッジ回路のローサイド側のトランジスタを駆動する回路としては、例えば、非特許文献1に記載のロー・サイド・ゲート・ドライブ回路がある。かかるゲート・ドライブ回路は、図14に示すように、NPNバイポーラ型トランジスタであるNPNTrと、PNPバイポーラ型トランジスタであるPNPTrと、ゲート直列抵抗RGと、ショットキ・バリア・ダイオードSDとを含んで構成される。NPNTrのエミッタ端子とPNPTrのエミッタ端子とが接続されており、更に、NPNTrのコレクタ端子が電源に接続され、PNPTrのコレクタ端子が接地されて、エミッタ・フォロア回路を構成している。NPNTrとPNPTrとの接続部はゲート直列抵抗RGを介してブリッジ回路のローサイド側のFETQ2のゲート端子に電気的に接続されている。更に、RGと並列にSDが、Q2のターン・オン時にはオフとなる方向に接続されている。

【0004】

従って、NPNTrとPNPTrの共通の入力端子にパルス・ジェネレータ(以下、PGという)からハイレベル(以下、Hレベルという)の信号が入力されると、NPNTrがオン状態に、PNPTr、SDはオフ状態になる。これによって、NPNTrのコレクタ−エミッタ間を電流が流れ、この電流がRGを介してQ2のゲートに流れ込む。この流れ込む電流は、Q2の入力容量Ciss(電極間容量+α)をチャージして、Q2のゲート電圧を駆動電位にまで引き上げ、Q2をオン状態へと駆動する。

【0005】

一方、入力端子にPGからローレベル(以下、Lレベルという)の信号が入力されると、PNPTr、SDがオン状態に、NPNTrはオフ状態になる。これにより、Q2のゲート電流(Cissの蓄積電荷)がRGをパスしてSDを流れ、PNPTrのエミッタ−コレクタ間を通ってグラウンド(低電位側)に放出される。そして、Cissの蓄積電荷が放出されるとQ2がオフ状態となる。

【非特許文献1】パワーMOSFET活用の基礎と実際、稲葉 保著、CQ出版社、2004年初版、P.053〜054

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上記従来技術においては、Q2がオフ状態からオン状態へと移行する途中において、Q2トランジスタのゲート−ドレイン間容量Cgdによるミラー効果の影響によって、図15に示すように、Q2のゲート電位(入力波形)とドレイン電位(出力波形)とが中間電位で一定になる状態(ハーフ・オン状態)が発生する。図15において、横軸は時間[μs]、縦軸は電圧[V]である。特に、Q2のCgdが大きくなるほどハーフ・オン状態の期間は長くなり、ブリッジ回路の動作に不具合を引き起こす恐れがある。また、このハーフ・オン状態は、特にHブリッジ回路のトランジスタのオン・オフ動作時にハイサイド側のトランジスタとローサイド側のトランジスタとの間に多大な貫通電流を生じさせて、消費電流の増大化を引き起こす恐れがあった。

【0007】

そこで、本発明は、このような従来の技術の有する未解決の課題に着目してなされたものであって、負荷を駆動するブリッジ回路のローサイド側のトランジスタを駆動するのに好適なトランジスタ駆動装置を提供することを目的としている。

【課題を解決するための手段】

【0008】

〔形態1〕 上記目的を達成するために、形態1のトランジスタ駆動装置は、駆動対象である負荷に電気的に接続されるハイサイド側の第1のトランジスタとローサイド側の第2のトランジスタとを含み、前記第1及び第2のトランジスタをオン又はオフにすることで前記負荷が通電又は非通電の状態となるブリッジ回路の前記第2のトランジスタを駆動するトランジスタ駆動装置であって、第1電源電位の供給される第1電源ノードと、前記第1電源電位よりも低電位の第2電源電位の供給される第2電源ノードと、前記第1電源ノードと前記第2電源ノードとの間に並列に接続された、第1の入力でオン・オフする第3のトランジスタ及び第2の入力でオン・オフする第4のトランジスタとを含み、前記第3及び第4のトランジスタの電流供給端子を前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタの前記駆動端子に駆動電力を供給する駆動電力供給手段と、前記第2のトランジスタのオフからオンへの移行途中における、該第2のトランジスタの出力電圧が中間電位で略一定となるハーフ・オン状態を検出する駆動状態検出手段と、前記第2のトランジスタをオフからオンにするときに、前記第1及び第2の入力を制御して前記第4のトランジスタよりも先に前記第3のトランジスタをオンにし、前記駆動状態検出手段で前記ハーフ・オン状態が検出されると前記第1及び第2の入力を制御して前記第3のトランジスタに加えて前記第4のトランジスタをオンにする駆動制御手段と、を備える。

【0009】

このような構成であれば、駆動制御手段が、第1及び第2の入力を制御して第3のトランジスタをオン状態にすると、第2のトランジスタに駆動電位が供給され駆動電流の供給が開始される。駆動電流が供給されると、第2のトランジスタはその入力容量がチャージされチャージ量の増加に伴いオフからオンへと移行していく。このオフからオンへの移行途中において、駆動状態検出手段によって、第2のトランジスタがハーフ・オン状態となったことが検出されると、駆動制御手段は、第1及び第2の入力を制御して、第3のトランジスタに加えて第4のトランジスタをオンにする。第4のトランジスタがオンされると、第2のトランジスタには、第3のトランジスタからの駆動電流に加え、第4のトランジスタからの駆動電流が供給される。

【0010】

これによって、第2のトランジスタには、ハーフ・オン状態のときに2つのトランジスタからの駆動電流が流れ込むことになり、入力容量のチャージ速度が上がって、従来のトランジスタ1つの駆動と比較して、ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

更に、ハーフ・オン状態が検出されるまでは第3のトランジスタだけをオンにして電流を供給し、ハーフ・オン状態が検出されてから第4のトランジスタもオンにするようにしたので、トランジスタがハーフ・オン状態になるまでの急激な電位変動の発生を低減しつつ、ハーフ・オン状態の期間を短くすることができるという効果が得られる。

【0011】

ここで、トランジスタがハーフ・オン状態になるまでに発生する急激な電位変動は負荷に接続する配線等のインダクタ成分によるサージ電圧を発生させやすくし、これによるトランジスタの破壊(ゲート膜破壊やドレイン端子破壊など)を引き起こしやすくする。

また、特にHブリッジ回路では、縦に接続された、ハイサイド側の第1のトランジスタと、ローサイド側の第2のトランジスタとが同時にオン状態となる場合があるため、このときに両者に貫通電流が流れる。そのため、例えば、第3及び第4のトランジスタを同時にオンにしたり、最初から第3のトランジスタよりも電流供給能力の大きいトランジスタを用いたりして、第2のトランジスタを駆動した場合は、トランジスタのゲート電位が第3のトランジスタだけで駆動したときよりも高くなり(VTHより高い電位で一度フラットになる)、両者に流れる貫通電流を大きくしてしまう可能性がある。

【0012】

つまり、ハーフ・オン状態になるまでは、比較的ゆっくりと入力容量のチャージを行ない、ハーフ・オン状態になってから一気にチャージを行うことで、サージ電圧の発生や貫通電流の増加を引き起こし難くしつつ、チャージ速度を増加させることができる。

ここで、上記ハーフ・オン状態とは、トランジスタの入力容量のチャージ中に、ミラー効果の影響で入力容量が増加するために発生する状態であり、トランジスタの出力電圧が中間の電位で略一定となる状態のことである。具体例を挙げると、例えば、トランジスタがMOSFETである場合は、ゲート駆動によって入力容量のチャージ中に、該MOSFETのゲート電圧がミラー効果の影響で中間電位で略一定となる期間が発生する。この期間では、FETの出力電圧(ドレイン電圧)も略一定となる。

また、上記電流供給端子は、第3及び第4のトランジスタが、バイポーラトランジスタであれば、例えば、エミッタ端子となり、FETであれば、例えば、ドレイン端子となる。

【0013】

〔形態2〕 更に、形態2のトランジスタ駆動装置は、形態1に記載のトランジスタ駆動装置において、前記第4のトランジスタは、前記第3のトランジスタよりも電流供給能力の大きいトランジスタサイズである。

【0014】

このような構成であれば、前記ハーフ・オン状態になるまでは、サイズの比較的小さい(電流供給能力の小さい)第3のトランジスタで第2のトランジスタの入力容量をチャージし、前記ハーフ・オン状態となると、第3のトランジスタに加えてサイズの比較的大きい(電流供給能力の大きい)第4のトランジスタで第2のトランジスタの入力容量をチャージすることができる。これにより、前記ハーフ・オン状態となるまでは、比較的少ない電流量でチャージし、前記ハーフ・オン状態となると比較的大きい電流量で一気に入力容量をチャージすることができるという効果が得られる。

【0015】

〔形態3〕 更に、形態3のトランジスタ駆動装置は、形態2に記載のトランジスタ駆動装置において、前記駆動制御手段は、前記ハーフ・オン状態が検出されると前記第3のトランジスタに代えて前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御する。

このような構成であれば、前記ハーフ・オン状態になるまでは、サイズの比較的小さい(電流供給能力の小さい)第3のトランジスタで第2のトランジスタの入力容量をチャージし、前記ハーフ・オン状態となると、第3のトランジスタに代えてサイズの比較的大きい(電流供給能力の大きい)第4のトランジスタで第2のトランジスタの入力容量をチャージすることができる。つまり、第3及び第4のトランジスタのサイズが異なる場合(電流供給能力の異なる場合)は、ハーフ・オン状態になったときに、2つともオンにするのではなく、第4のトランジスタだけをオン状態にする。

【0016】

〔形態4〕 更に、形態4のトランジスタ駆動装置は、形態1乃至3のいずれか1に記載のトランジスタ駆動装置において、前記第1及び第2のトランジスタは、電界効果トランジスタであり、前記第2のトランジスタの駆動端子はゲート端子である。

このような構成であれば、電界効果トランジスタである第2のトランジスタのターン・オン時間(入力容量のチャージ時間)を短縮することができ、従来と比較して、前記ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

【0017】

ここで、上記電界効果トランジスタ(FET)が、例えば、大電力用に設計されたものである場合は、第2のトランジスタの入力容量が比較的大きくなり、それだけ前記ハーフ・オン状態の期間が長くなる。この入力容量は、電流量やオン状態時の抵抗の大きさなどとのトレードオフとなる。つまり、FETを大電流且つ低抵抗にしたい場合は、トランジスタサイズを大きくする必要があり入力容量も大きくなる。

【0018】

〔形態5〕 更に、形態5のトランジスタ駆動装置は、形態1乃至請求項4のいずれか1に記載のトランジスタ駆動装置において、前記駆動状態検出手段は、前記負荷を通って前記第2のトランジスタに流れる電流の電流レベルを検出する電流検出部と、前記電流検出部で検出した電流レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電流レベルとを比較する電流レベル比較部とを有し、前記電流検出部で検出される電流レベルが前記所定の電流レベルとなったときに、前記ハーフ・オン状態を検出する。

【0019】

このような構成であれば、第3のトランジスタがオン状態になり、第2のトランジスタに駆動電流が供給されると、駆動状態検出手段は、電流検出部において、負荷を通って第2のトランジスタに流れる電流の電流レベルを検出する。電流レベルが検出されると、電流レベル比較部において、検出された電流レベルと予め用意された前記ハーフ・オン状態時の電流レベル(以下、不完全電流レベルという)とが比較される。そして、駆動制御手段は、この比較結果から、検出された電流レベルの方が不完全電流レベルよりも小さいレベルであれば、第3のトランジスタのみをオン状態にする。一方、検出された電流レベルが不完全電流レベル以上となった場合は、第3のトランジスタに加えて又は代えて、第4のトランジスタをオン状態にする。

【0020】

これにより、負荷の特性や第2のトランジスタの特性などに応じた不完全電流レベルを予め実験等によって得ておくことで、前記ハーフ・オン状態を確実に検出することができるという効果が得られる。

ここで、上記電流レベルの比較は、電流レベルを電圧レベルに変換して行っても良い。

【0021】

〔形態6〕 更に、形態6のトランジスタ駆動装置は、形態1乃至4のいずれか1に記載のトランジスタ駆動装置において、前記駆動状態検出手段は、前記第2のトランジスタの前記負荷との接続部の電圧レベルを検出する電圧検出部と、前記電圧検出部で検出される前記電圧レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電圧レベルとを比較する電圧レベル比較部とを有し、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなったときに、前記ハーフ・オン状態を検出する。

【0022】

このような構成であれば、第3のトランジスタがオン状態になり、第2のトランジスタに駆動電流が供給されると、駆動状態検出手段は、電圧検出部において、第2のトランジスタと負荷との電気的な接続部の電圧レベルを検出する。電圧レベルが検出されると、電圧レベル比較部において、検出された電圧レベルと予め用意された前記ハーフ・オン状態時の電圧レベル(以下、不完全電圧レベルという)とが比較される。そして、駆動制御手段は、この比較結果から、検出された電圧レベルの方が不完全電圧レベルよりも小さいレベルであれば、第3のトランジスタのみをオン状態にする。一方、検出された電圧レベルが不完全電圧レベル以上となった場合は、第3のトランジスタに加えて又は代えて、第4のトランジスタをオン状態にする。

【0023】

これにより、負荷の特性や第2のトランジスタの特性などに応じた不完全電圧レベルを予め実験等によって得ておくことで、前記ハーフ・オン状態を確実に検出することができるという効果が得られる。

【0024】

〔形態7〕 更に、形態7のトランジスタ駆動装置は、形態6に記載のトランジスタ駆動装置において、前記第2のトランジスタに駆動電流が供給されてからの経過時間を計測する時間計測手段と、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなるときの前記時間計測部の計測時間の情報を記録する時間記録手段とを更に備え、前記駆動制御手段は、前記時間記録手段によって計測時間が記録されると、以降は、前記時間計測手段の計測時間が前記記録した計測時間になるタイミングで、前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御する。

【0025】

このような構成であれば、第3のトランジスタがオンされ、第2のトランジスタに駆動電流が供給されると、時間計測手段によって、駆動電流の供給が開始されてからの時間が計測される。一方、電圧検出部では接続部の電圧レベルが検出され、電圧レベル比較部において、検出された電圧レベルと不完全電圧レベルとが比較される。そして、検出された電圧レベルが不完全電圧レベルになると、時間記録手段において、そのときの時間計測手段の計測時間が記録される。計測時間が記録されると、以降は、駆動制御手段は、第2のトランジスタをオフ状態からオン状態にするときに、時間計測手段の計測時間が、記録された計測時間になるまでは、第3のトランジスタのみをオンにして駆動電流を供給し、時間計測手段の計測時間が記録された計測時間になるタイミングで、第3のトランジスタに加えて又は代えて、第4のトランジスタをオンにする。

【0026】

これにより、前記ハーフ・オン状態をより確実に検出することができるという効果が得られる。

更に、例えば、起動後に変動の少ない負荷(例えば、PCのファンモータなど)を駆動するときは、計測時間の記録後に、電圧レベル比較部の動作を完全に停止することができるので、低消費電流化できるという効果も得られる。

【0027】

ここで、時間計測部は、第2のトランジスタに駆動電流の供給が開始されてからの経過時間を、例えば、カウンタ回路によって、外部から又は内部で供給されるクロックをカウントすることで計測する。そして、時間記録部は、不完全オン状態が発生したときのカウント値を記録し、次回からは、時間計測部のカウント値が記録されたカウント値になったときに不完全オン状態が発生したと判断する。

【0028】

〔形態8〕 更に、形態8のトランジスタ駆動装置は、形態1乃至7のいずれか1に記載のトランジスタ駆動装置において、前記ブリッジ回路は、ハイサイド側の一対の前記第1のトランジスタと、ローサイド側の一対の前記第2のトランジスタとから構成され、前記負荷への通電方向に応じて、対角に位置する第1のトランジスタ及び第2のトランジスタがオン又はオフされるHブリッジ型の回路である。

【0029】

このような構成であれば、負荷への通電方向を任意に変えることができるHブリッジ型の回路のローサイド側の第2のトランジスタに対しても、従来と比較して、ハーフ・オン状態への移行時の急激な電位変動の発生を抑えつつ、前記ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

【0030】

〔形態9〕 更に、形態9のトランジスタ駆動装置は、形態1乃至8のいずれか1に記載のトランジスタ駆動装置において、前記駆動電力供給手段は、前記第3のトランジスタと前記第2電源ノードとの間に直列に接続された、第3の入力でオン・オフする第5のトランジスタと、前記第4のトランジスタと前記第2電源ノードとの間に直列に接続された、第4の入力でオン・オフする第6のトランジスタとを更に含み、前記第3及び第5のトランジスタの接続部と、前記第4及び第6のトランジスタの接続部とを前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタをオフにし且つ前記第5及び第6のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタから前記第2電源ノード側に電流を引き込む構成となっており、前記駆動制御手段は、前記第2のトランジスタをオン状態からオフ状態にするときに、前記第3及び第4のトランジスタを両方ともオフ状態にし、前記第5及び第6のトランジスタを両方ともオン状態にするように前記第1〜第4の入力を制御する。

【0031】

このような構成であれば、第2のトランジスタをオン状態からオフ状態にするときに、その入力容量として蓄積された電荷を2つのトランジスタを介して第2電源ノード側に引き込むことができるので、トランジスタ1つで引き込んでいた従来と比較して第2のトランジスタのターン・オフ時間を短縮することができる。これにより、オフ状態への移行中に発生する不完全オン状態の期間を従来と比較して短くすることができるという効果が得られる。

【発明を実施するための最良の形態】

【0032】

〔第1の実施の形態〕

以下、本発明の第1の実施の形態を図面に基づき説明する。図1〜図9は、本発明に係るトランジスタ駆動装置の第1の実施の形態を示す図である。

本実施の形態において、本発明に係るトランジスタ駆動装置を、モータを駆動するHブリッジ回路に適用し、このHブリッジ回路のローサイド側のトランジスタを駆動する構成とした。

【0033】

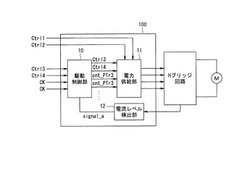

まず、本発明に係るモータ駆動装置1の構成を図1に基づき説明する。図1は、本発明に係るモータ駆動装置1の構成を示すブロック図である。

モータ駆動装置1は、図1に示すように、トランジスタ駆動装置100と、Hブリッジ回路200とを含んで構成される。

トランジスタ駆動装置100は、不図示のマイコンからの制御信号に基づき、Hブリッジ回路200を構成する各トランジスタを駆動する。

【0034】

Hブリッジ回路200は、自身を構成するハイサイド側のトランジスタとローサイド側のトランジスタとが、トランジスタ駆動装置100によってそれぞれ独立に駆動制御されると、その制御内容に応じて、駆動対象である直流モータ2を、正回転駆動、逆回転駆動、ブレーキ駆動などする。

【0035】

次に、図2に基づき、Hブリッジ回路200の詳細な構成を説明する。

ここで、図2は、Hブリッジ回路200の詳細な構成を示す図である。

Hブリッジ回路200は、図2に示すように、スイッチング素子としての役割を果たす4つのNチャンネル型のDMOSFETQ1〜Q4を、Q1、Q3をハイサイド側に、Q2、Q4をローサイド側に配してHブリッジ型に接続して構成される。

具体的に、Q1のソース端子とQ2のドレイン端子とを電気的に接続し、Q3のソース端子とQ4のドレイン端子とを電気的に接続し、Q1及びQ2の接続部から出力を取り出す出力端子OUTAと、Q3及びQ4の接続部から出力を取り出す出力端子OUTBとをそれぞれ形成して構成される。そして、このOUTA及びOUTBには、直流モータ2が接続されている。また、D1〜D4は、Q1〜Q4の内部に寄生的に作られたボディダイオードである。

【0036】

このHブリッジ回路200のハイサイド側(Q1、Q3のドレイン端子)には、モータの駆動電源から駆動電圧VBBが供給されるようになっている。一方、ローサイド側(Q2、Q4のソース端子側)は、電流検出用の抵抗Rsを介してグラウンドに接続されている。

Hブリッジ回路200のQ1〜Q4のゲート端子には、トランジスタ駆動装置100からの駆動線がそれぞれ電気的に接続されており、該駆動線を介して供給される駆動電位及び駆動電流に基づきQ1〜Q4がそれぞれ独立に駆動制御される。

【0037】

次に、図3に基づき、DMOSFET(Q1〜Q4)の入力容量について説明する。

ここで、図3は、DMOSFETの等価回路を示す図である。

DMOSFETは、図3に示すように、ゲート−ドレイン電極間の電極間容量Cgdと、ゲート−ソース電極間の電極間容量Cgsとを有する。ゲート電圧が0[V]のときのCgdとCgsとの和は入力容量Cissと呼ばれる。このようなDMOSFETをオン状態に駆動するには、Cissをチャージする必要がある。しかしながら、DMOSFETがオフからオンへと移行する過程において、ゲート−ソース間電圧VGSの変化によって、Cgdの容量が大きく変化するためCissの容量も大きく変化する(ミラー効果)。この見かけのCissは、下式(1)によって算出できる。

Ciss=Cgs+(1−AV)・Cgd ・・・(1)

上式(1)において、AVは電流増幅率である。

【0038】

ミラー効果の影響によって、オフからオンへと移行時のVGSが中間の電位で略一定になる状態が発生する。この状態が発生している期間は、ドレイン−ソース間電圧VDSも中間電位で略一定となる。この状態をハーフ・オン状態と呼ぶ。このハーフ・オン状態の期間は、Cissの容量の大きさに比例して長くなる。例えば、レイアウト換算で、300〜500[pF]などの大容量となると、ハーフ・オン状態の期間が長くなり、チャージ時間、放出時間の増加も重なって、ターン・オン時間、ターン・オフ時間も長くなる。

【0039】

ハーフ・オン状態の期間が長いと、高抵抗状態のドレイン−ソース間に電流が流れる期間が長くなるため、DMOSFETの発熱による自身のゲート膜の破壊などの不具合が生じる可能性がある。従って、ハーフ・オン状態の期間は短ければ短いほどよく、本発明は、Hブリッジ回路200のローサイド側のトランジスタ(Q2、Q4)について、ハーフ・オン状態の期間を短くすることを目的としている。

【0040】

次に、図4に基づき、トランジスタ駆動装置100の構成を説明する。

ここで、図4は、トランジスタ駆動装置100の概略構成を示すブロック図である。

トランジスタ駆動装置100は、図4に示すように、駆動制御部10と、駆動電力供給部11と、電流レベル検出部12とを含んで構成される。

駆動制御部10は、不図示のマイコンからの制御信号と電流レベル検出部12からの信号とに基づき、駆動電力供給部11の動作を制御する。

【0041】

駆動電力供給部11は、ハイサイド側のQ1、Q3をそれぞれ独立に制御するハイサイド用の駆動回路と、ローサイド側のQ2、Q4をそれぞれ独立に制御するローサイド用の駆動回路を有し、マイコンからの制御信号及び駆動制御部10からの制御信号に基づき、Hブリッジ回路200のQ1〜Q4のオン・オフ動作を独立に制御する。

電流レベル検出部12は、Hブリッジ回路200の電流検出抵抗Rsを流れる電流のレベルを検出する。更に、検出した電流レベルを電圧レベルに変換し、該電圧レベルと基準電圧レベルとを比較して、この比較結果を示す信号(以下、比較信号signal_aという)を駆動制御部10に出力する。

【0042】

次に、図5に基づき、駆動制御部10及び駆動電力供給部11の内部構成を説明する。

ここで、図5は、駆動制御部10及び駆動電力供給部11の内部構成を示すブロック図である。

駆動制御部10は、図5に示すように、駆動電力供給部11の第1LST(ローサイド・トランジスタ)駆動回路11cを制御する第1のTG(タイミングジェネレート)回路10aと、第2LST駆動回路11dを制御する第2のTG回路10bとを含んで構成される。

【0043】

第1のTG回路10aは、マイコンからの制御信号ctrl3と不図示のオシレータからのクロック信号CKと電流レベル検出部12からの比較信号signal_aとに基づき第1LST駆動回路11cの動作を制御する制御信号cnt_PTr3(詳細は後述)を生成し、これを第1LST駆動回路11cに供給する。

第2のTG回路10bは、マイコンからの制御信号ctrl4とクロック信号CKと電流レベル検出部12からの比較信号signal_aとに基づき第2LST駆動回路11dの動作を制御する制御信号cnt_PTr3を生成し、これを第2LST駆動回路11dに供給する。

【0044】

次に、駆動電力供給部11は、図5に示すように、マイコンからの制御信号ctrl1に基づき、Hブリッジ回路200のQ1のオン・オフ動作を制御する第1HST駆動回路11aと、マイコンからの制御信号ctrl2に基づき、Q3のオン・オフ動作を制御する第2HST駆動回路11bとを含んで構成される。

更に、駆動電力供給部11は、マイコンからの制御信号ctrl3と、制御信号cnt_PTr2(詳細は後述)とに基づき、Hブリッジ回路200のQ2のオン・オフ動作を制御する第1LST駆動回路11cと、マイコンからの制御信号ctrl4と、第1のTG回路10aからの制御信号cnt_PTr3とに基づき、Q4のオン・オフ動作を制御する第2LST駆動回路11dとを含んで構成される。

【0045】

ここで、マイコンからの制御信号ctrl1〜ctrl4は、モータの駆動内容に応じてQ1〜Q4のオン・オフを制御する信号(例えば、PWM信号)であり、Q1〜Q4は、トランジスタ駆動装置100において、各DMOSFETに対応する制御信号がLレベルでオンに、Hレベルでオフに駆動制御される。

【0046】

次に、図6に基づき、第1HST駆動回路11aの詳細な回路構成を説明する。

ここで、図6は、第1HST駆動回路11aの詳細な回路構成を示す図である。

第1HST駆動回路11aは、図6に示すように、Pチャンネル型の電界効果トランジスタPTr1、PTr10と、Nチャンネル型の電界効果トランジスタNTr1、NTr10と、レベルシフタ30と、電圧クランプ回路32とを含んで構成される。

PTr1とNTr1とは、電源電位VBB+VGL(VGH)の供給されるVGHノードと、電源電位VBBの供給されるVBBノードとの間に直列に接続されている。ここで、VBBはモータ駆動電位、VGHは、ハイサイド側のDMOSFET(Q1、Q3)のゲート駆動電位、VGLは、ローサイド側のDMOSFET(Q2、Q4)のゲート駆動電位である。

【0047】

より具体的に、PTr1のソース端子はVGHノードに電気的に接続され、ドレイン端子はNTr1のドレイン端子に電気的に接続され、NTr1のソース端子はVBBノードに電気的に接続されている。PTr10のソース端子はVGHノードに電気的に接続され、ドレイン端子はNTr10のドレイン端子に電気的に接続され、PTr10及びNTr10のゲート端子は電圧クランプ回路32に電気的に接続され、NTr10のソース端子は、電圧クランプ回路32とQ1及びQ2の接続部(OUTA)と電気的に接続されている。

【0048】

PTr1とNTr1のゲート端子は、共通線でレベルシフタ30の出力端子と電気的に接続されている。PTr1とNTr1のドレイン接続部は、PTr10とNTr10のゲート接続部と電気的に接続され、PTr10とNTr10のドレイン接続部は、Q1のゲート端子に電気的に接続されている。

レベルシフタ30は、VGLと、VBBと、VGHとの3種類の電源電位に基づき、入力信号の電圧レベル0[V]〜VGL[V]を、VBB[V]〜VGH[V]にレベルシフトして、その信号を出力する回路である。

【0049】

具体的に、マイコンからの制御信号ctrl1の信号電位V1がLレベル(例えば0[V])のときは、この信号の電圧レベルをVBB[V]までシフトして、VBB[V]の信号を出力する。この場合は、PTr1がオン、NTr1がオフとなり、PTr1を介して駆動電流がQ1のゲート端子に供給され、Q1をオフからオンへと駆動する。

一方、マイコンからの制御信号の信号電位V1がHレベル(例えば5[V])のときは、この信号の電圧レベルをVGH[V]にレベルシフトして、VGH[V]の信号を出力する。この場合は、NTr1がオン、PTr1がオフとなり、NTr1を介して、Q1の入力容量Cissに蓄積された電荷をVBBノード側へと引き込む。

【0050】

電圧クランプ回路32は、ツェナーダイオード等で構成されており、NTr10のゲート−ソース間に定格電圧以上の高い電圧が印加されないように保護する回路である。

なお、第2HST駆動回路11bは、駆動制御する対象がQ3となるだけで、第1HST駆動回路11aと同様の構成となる。

【0051】

次に、図7に基づき、第1LST駆動回路11cの詳細な回路構成を説明する。

ここで、図7は、第1LST駆動回路11cの詳細な回路構成を示す図である。

第1LST駆動回路11cは、図7に示すように、Pチャンネル型の電界効果トランジスタPTr2と、Nチャンネル型の電界効果トランジスタNTr2、NTr3と、PTr2よりも電流供給能力の大きいPチャンネル型の電界効果トランジスタPTr3と、レベルシフタ31とを含んで構成される。

【0052】

PTr2とNTr2とは、電源電位VGLの供給されるVGLノード(第1電源ノード)と、接地電位の供給される接地ノード(第2電源ノード)との間に直列に接続されており、PTr3とNTr3とは、VGLノードと、接地ノードとの間に直列に接続されている。そして、これら直列接続されたPTr2及びNTr2と、PTr3及びNTr3とは並列に接続されている。

【0053】

より具体的に、PTr2のソース端子は、VGLノードに電気的に接続され、ドレイン端子はNTr2のドレイン端子に電気的に接続され、NTr2のソース端子は接地ノードに電気的に接続されている。PTr3のソース端子は、VGLノードに電気的に接続され、ドレイン端子はNTr3のドレイン端子に電気的に接続され、NTr3のソース端子は接地ノードに電気的に接続されている。

【0054】

PTr2とNTr2のゲート端子は、共通線でレベルシフタ31の出力端子と電気的に接続されている。PTr2とNTr2のドレイン接続部はQ2のゲート端子に電気的に接続されている。

PTr3のゲート端子は、マイコンからの制御信号を入力する不図示の端子に電気的に接続されている。NTr3のゲート端子はレベルシフタ31の出力端子に電気的に接続されている。PTr3とNTr3の接続部はQ2のゲート端子に電気的に接続されている。

【0055】

レベルシフタ31は、VGLと、マイコンからの制御信号の電位V2と接地電位との3種類の電源電位に基づき、入力信号の電圧レベルV2[V]をVGL[V]にレベルシフトした信号を出力する回路である。なお、V2が0[V]の場合は、0[V](接地電位)の信号を出力するように構成されている。

具体的に、マイコンからの制御信号の信号電位V2がLレベル(例えば0[V])のときは、Lレベルの信号(0[V]の信号)を制御信号cnt_PTr2(第1の入力)として出力する。この場合は、PTr2がオン、NTr2がオフとなり、PTr2を介して駆動電流がQ2のゲート端子に供給される。

【0056】

一方、マイコンからの制御信号がHレベル(例えば5[V])のときは、この信号の電圧レベルをVGL[V]にレベルシフトして、VGL[V]の信号を制御信号cnt_PTr2として出力する。この場合は、NTr2がオン、NTr3がオン、PTr2がオフとなり、NTr2、NTr3を介して、Q2の入力容量Cissに蓄積された電荷を接地ノード側へと引き込む。

【0057】

つまり、2つのトランジスタを介して入力容量Cissにチャージされた電荷を引き込むようにしたので、トランジスタ1つで引き込む場合と比較して、オン状態からオフ状態への移行時のハーフ・オン状態の期間を短くできると共に、Q2のターン・オフ時間も短くすることができる。

更に、第1のTG回路10aからのLレベル(例えば0[V])の制御信号cnt_PTr3(第2の入力)がPTr3のゲート端子に入力されると、PTr3がオンとなり、PTr3を介して駆動電流がQ2のゲート端子に供給される。このPTr3を、PTr2と同時にオンにすると、PTr2及びPTr3の2つのトランジスタを介して駆動電流がQ2へと供給される。しかも、PTr2よりも電流供給能力の大きいPTr3が加わるため、これにより、入力容量のチャージ速度が急激に上がり、ハーフ・オン状態の期間を短縮することができる。

【0058】

従って、駆動制御部10における第1のTG回路10aは、PTr2とPTr3の両方を用いて、Q2をオフからオン状態に駆動するタイミングの制御信号cnt_PTr3を生成し、第1LST駆動回路11cに供給するようになっている。第2のTG回路10bについても、対象が第2LST駆動回路11dとなるだけで同様である。

本発明は、このPTr3を設け、Q2(Q4)をオン駆動するときにPTr2に加えてPTr3をオンにする点と、PTr3をオンにするタイミングとに主な特徴がある。PTr3をオンにするタイミングについては後述する。

【0059】

なお、第2LST駆動回路11dは、駆動制御する対象がQ4となるだけで、第1LST駆動回路11cと同様の構成となる。

また、PTr2とPTr3のトランジスタサイズを「PTr2<PTr3」としたが、PTr2のトランジスタサイズは、Q2、Q4のデバイス特性に基づき決定する。また、PTr3のトランジスタサイズは、Q2、Q4のターン・オン時間、ターン・オフ時間、ターン・オン、オフ時の伝播遅延時間などに基づき決定する。

【0060】

例えば、Q2、Q4のデバイス特性が、スレッショルド電圧VTHが「1.4±0.2[V]」、オン状態における抵抗RONが「0.30Ω・mm2以下」、ブレークダウン電圧BVDS「60[V]以上」、電流容量「1.0[A]〜1.5[A]」であるとすると、これらの特性に基づき、Q2、Q4のゲートをドライブ可能なサイズにPTr2のトランジスタサイズを決定する。

【0061】

また、Q2、Q4の伝播遅延時間が「出力電流IO=±1.3[A]、50%to90%ENABLEオンからシンク出力オン1.0[μs]」、「出力電流IO=±1.3[A]、50%to90%ENABLEオフからシンク出力オフ0.8[μs]」であるとすると、これらの遅延時間に基づきPTr3のトランジスタサイズを決定する。

【0062】

次に、図8に基づき、電流レベル検出部12の構成を説明する。

ここで、図8は、電流レベル検出部12の構成を示す図である。

電流レベル検出部12は、図8に示すように、I/V変換回路12aと、比較器12bとを含んで構成される。

I/V変換回路12aは、その入力端子がHブリッジ回路200の電流検出抵抗Rsの両端に電気的に接続されており、その出力端子が比較器12bの入力端子に電気的に接続されている。そして、Hブリッジ回路のRsを流れる電流が入力されると、その電流を電圧に変換して比較器12bに入力する。

【0063】

比較器12bは、その出力端子が、駆動制御部10の第1のTG回路10a及び第2のTG回路10bの入力端子に電気的に接続されている。そして、I/V変換回路12aから入力された電圧Vsと、基準電圧Vrefとを比較して、Vsの電圧レベルがVrefのレベル以上であればHレベルの比較信号signal_aを出力し、Vsの電圧レベルがVrefのレベル未満であればLレベルの比較信号signal_aを出力する。

【0064】

ここで、Rsを流れる電流Isは、例えば、図8に示すように、Hブリッジ回路200のQ3がオン状態のときで、且つQ2がオフ状態からオン状態へと移行し、Q2のドレイン−ソース間を電流が流れる状態となったときに、モータ2のコイルMLを通過して流れる電流である(図中の点線矢印)。

本実施の形態においては、検出電圧Vsのレベルが、先述したハーフ・オン状態となるレベル(中間電位)を予め実験で得るか、負荷(モータ)や回路を構成する各素子の特性等から算出などして得ておき、そのレベルの電圧を基準電圧Vrefとして比較器12bに入力する。

【0065】

つまり、電流レベル検出部12は、Rsを流れるIsのレベルを電圧レベルVsに変換してVrefと比較し、この比較結果を駆動制御部10に出力する。

従って、この比較結果を示す信号signal_aは、検出電圧Vsが中間電位の状態にあるときはHレベルの信号となり、そうでないときはLレベルの信号となる。

【0066】

次に、図9に基づき、第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングについて説明する。

ここで、図9は、第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングを示すタイミングチャートである。

本発明は、Q2、Q4のオフ状態からオン状態への移行時のハーフ・オン状態の期間を短くするために、第1及び第2LST駆動回路11c及び11dのPTr2及びPTr3をオン・オフのタイミングを制御する。なお、PTr2及びPTr3のタイミング制御については、第1及び第2LST駆動回路11c及び11dの双方において同様の制御内容となるので、以下、第1LST駆動回路11cのPTr2及びPTr3のタイミング制御について説明する。

【0067】

本実施の形態においては、マイコンからの制御信号ctrl3がそのまま第1LST駆動回路11cに入力される。そして、第1LST駆動回路11cは、ctrl3がHレベルの信号の場合はレベルシフタ31でゲートの駆動電位VGLまでレベルシフトして、この信号をPTr2のゲート端子に供給する。一方、ctrl3がLレベルの場合はそのままPTr2のゲート端子に供給する。

【0068】

従って、ctrl3がLレベルの信号であればPTr2を制御する制御信号cnt_PTr2はLレベルの信号となり、PTr2をオンにする。これにより、PTr2を介してQ2のゲート端子に駆動電流が供給され、入力容量Cissのチャージが開始される。

一方、第1のTG回路10aは、マイコンからの制御信号であるctrl3と、電流レベル検出部12の比較器12bから入力されるsignal_aとに基づきPTr3のオン・オフを制御する制御信号cnt_PTr3を生成する。

【0069】

具体的に、マイコンからのctrl3がLレベルの信号であり、図9に示すように、比較器12bからのsignal_aがLレベルの信号であるときは、Q2はハーフ・オン状態ではないと判断できるので、cnt_PTr3としてHレベルの信号を生成し、この信号をPTr3のゲート端子に供給する。この場合、PTr3はオフとなる。

一方、ctrl3がLレベルの信号であり、図9に示すように、signal_aがHレベルの信号であるときは、Q2がハーフ・オン状態になっていると判断できるので、cnt_PTr3としてLレベルの信号を生成し、この信号をPTr3のゲート端子に供給する。この場合、PTr3はオン状態となる。このとき、cnt_PTr2をLレベルに維持してPTr2のオン状態を維持する。従って、PTr2及びPTr3の2つのトランジスタを介して、Q2のゲート端子に駆動電流が供給される。

【0070】

また、ctrl3がLレベルからHレベルの信号になると、図9に示すように、cnt_PTr2もHレベルの信号となり、PTr2をオフにする。cnt_PTr2はNTr2及びNTr3のゲート端子にも供給されるので、NTr2及びNTr3が共にオン状態となる。そして、これら2つのトランジスタを介して、Q2のCissにチャージされた電荷が接地ノード側に引き込まれ放出される。

【0071】

一方、図9に示すように、ctrl3(cnt_PTr2)がHレベルの信号になると、第1のTG回路10aは、cnt_PTr3としてHレベル(VGL)の信号を生成し、この信号をPTr3のゲート端子に供給する。これにより、PTr3はオフとなる。

なお、本実施の形態においては、PTr3を、PTr2よりも電流供給能力の大きなトランジスタサイズで形成しているため、PTr3をオンにするときに、PTr2をオフにしてもよい。

【0072】

以上、本実施の形態のトランジスタ駆動装置100は、モータ2を駆動するHブリッジ回路200のローサイド側のトランジスタQ2、Q4をオフからオンに駆動する際に、Q2、Q4をオンに駆動するトランジスタであるPTr2及びPTr3における、PTr2を先にオンにして、PTr2のみでQ2又はQ4のゲートに駆動電流を供給し、電流レベル検出部12の比較結果から、Q2又はQ4のハーフ・オン状態が検出されたときは、PTr2に加えてPTr3をオンにして、PTr2及びPTr3の2つのトランジスタを介して、Q2のゲートに駆動電流を供給するようにした。

【0073】

これにより、トランジスタがハーフ・オン状態になるまでの急激な電位変動の発生を低減しつつ、オフからオンに移行時のハーフ・オン状態の期間を短くすることができる。

更に、Q2、Q4をオンからオフに駆動する際に、NTr2及びNTr3の2つのトランジスタをオンにして、Q2、Q4の入力容量Cissにチャージされた電荷が接地ノード側に引き込むこうにした。

【0074】

これにより、オンからオフへの移行時のハーフ・オン状態の期間を短くすることができる。

上記第1の実施の形態において、駆動電力供給部11は、形態1又は9に記載の駆動電力供給手段に対応し、駆動制御部10及びマイコンによる駆動電力供給部11の制御処理は、形態1、3及び9のいずれか1に記載の駆動制御手段に対応し、電流レベル検出部12は、形態1又は5に記載の駆動状態検出手段に対応する。

【0075】

〔第2の実施の形態〕

次に、本発明の第2の実施の形態を図面に基づき説明する。図10〜図13は、本発明に係るトランジスタ駆動装置の第2の実施の形態を示す図である。

【0076】

本実施の形態は、上記第1の実施の形態のHブリッジ回路200のQ2、Q4のハーフ・オン状態を判断するのに、Q2、Q4のドレイン−ソース間電圧VDSを基準電圧Vrefと比較する点と、Q2、Q4をオフ状態からオン状態に駆動するときに、最初の1回目は、PTr2のみを駆動したときの、Q2、Q4に駆動電流の供給を開始してからハーフ・オン状態となるまでの時間(カウント値)を計測して記録し、2回目以降は、カウント値が記録した値となったときに、PTr2に加えてPTr3をオンに駆動する点とが上記第1の実施の形態と異なる。

【0077】

以下、上記第1の実施の形態と同様の構成部については同じ符号を付して説明を適宜省略し、異なる部分について詳細に説明する。

まず、図10に基づき、本実施の形態に係るトランジスタ駆動装置100’の構成を説明する。

ここで、図10は、トランジスタ駆動装置100’の構成を示すブロック図である。

【0078】

トランジスタ駆動装置100’は、図10に示すように、駆動制御部13と、駆動電力供給部11と、電圧レベル検出部14とを含んで構成される。

駆動制御部13は、第1及び第2LST駆動回路11c及び11dからのPTr2の出力信号out_PTr2(Q2のゲートに供給される信号)と電圧レベル検出部14からの信号とに基づき、駆動電力供給部11の動作を制御する。

【0079】

電圧レベル検出部14は、Hブリッジ回路200のQ2、Q4のVDSを検出し、この電圧レベルと基準電圧レベルとを比較して、この比較結果を示す信号(以下、比較信号outCompという)を駆動制御部13に出力する。

【0080】

次に、図11に基づき、駆動制御部13の内部構成を説明する。

ここで、図11は、駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

駆動制御部13は、図11に示すように、第1LST駆動回路11cを制御する第1制御回路13aと、第2LST駆動回路11dを制御する第2制御回路13bとを含んで構成される。

【0081】

第1制御回路13aは、第1LST駆動回路11cからの出力信号out_PTr2と不図示のオシレータからのクロック信号CKと電圧レベル検出部14からの比較信号outComp1とに基づき第1LST駆動回路11cのPTr3のオン・オフ動作を制御する制御信号cnt_PTr3を生成し、これを第1LST駆動回路11cに供給する。

【0082】

第2制御回路13bは、第2LST駆動回路11dからの出力信号out_PTr2とクロック信号CKと電圧レベル検出部14からの比較信号outComp2とに基づき第2LST駆動回路11dのPTr3のオン・オフ動作を制御する制御信号cnt_PTr3を生成し、これを第2LST駆動回路11dに供給する。

なお、図示しないが、第1LST駆動回路11cから出力信号out_PTr2を得るために、第1制御回路13aのout_PTr2の入力端子と、第1LST駆動回路11cのPTr2の出力端子とが電気的に接続されている。

同様に、第2制御回路13bのout_PTr2の入力端子と、第2LST駆動回路11dのPTr2の出力端子とが電気的に接続されている。

【0083】

次に、図12に基づき、電圧レベル検出部14の構成を説明する。

ここで、図12は、電圧レベル検出部14の構成を示す図である。

電圧レベル検出部14は、図12に示すように、第1比較器14aと、第2比較器14bとを含んで構成される。

【0084】

第1比較器14aは、入力端子にHブリッジ回路200のQ1とQ2との接続部N1が電気的に接続されており、出力端子が駆動制御部10の第1制御回路13aの入力端子に電気的に接続されている。そして、入力端子に入力される接続部N1の電位(Q2のVDS)と、基準電圧Vrefとを比較して、VDSの電圧レベルがVrefのレベル以上であればHレベルの第1比較信号outComp1を出力し、VDSの電圧レベルがVrefのレベル未満であればLレベルの第1比較信号outComp1を出力する。

【0085】

第2比較器14bは、入力端子にHブリッジ回路200のQ3とQ4との接続部N2が電気的に接続されており、出力端子が駆動制御部10の第2制御回路13bの入力端子に電気的に接続されている。そして、入力端子に入力される接続部N2の電位(Q4のVDS)と、基準電圧Vrefとを比較して、VDSの電圧レベルがVrefのレベル以上であればHレベルの第2比較信号outComp2を出力し、VDSの電圧レベルがVrefのレベル未満であればLレベルの第2比較信号outComp2を出力する。

【0086】

ここで、VDSのレベルは、Q2又はQ4の入力容量のチャージ量と比例する。そこで、本実施の形態では、VDSのレベルがハーフ・オン状態となるレベルか否かを検出する。

なお、本実施の形態においては、Q2及びQ4のVDSのレベルが、先述したハーフ・オン状態となるレベル(中間電位)を予め実験で得るか、負荷(モータ)や回路を構成する各素子の特性等から算出などして得ておき、そのレベルの電圧を基準電圧Vrefとして比較器12bに入力する。

【0087】

つまり、電圧レベル検出部14は、接続部N1、N2の電圧レベルVDSとVrefとを比較し、この比較結果を駆動制御部13に出力する。

従って、この比較結果を示す信号outComp1、outComp2は、Q2、Q4のVDSが中間電位の状態にあるときはHレベルの信号となり、そうでないときはLレベルの信号となる。

【0088】

次に、図13に基づき、第1制御回路13aの詳細な回路構成を説明する。

ここで、図13は、第1制御回路13aの詳細な回路構成を示す図である。

第1制御回路13aは、図13に示すように、第1TG(タイミングジェネレータ)40と、カウンタ41と、FF(フリップフロップ)回路42と、比較器43と、第2TG44とを含んで構成される。

【0089】

第1TG40は、カウンタ41及びFF回路42とそれぞれ電気的に接続されており、第1LST駆動回路11cからの信号cnt_PTr2と、電圧レベル検出部14からの比較信号outComp1と、オシレータからのクロック信号CKとに基づき、カウンタのリセット信号と、FF回路42のラッチタイミング信号とを生成し、それぞれに出力する。カウンタ41のリセット信号は、cnt_PTr2のレベルがHレベルからLレベルに変化したときにカウンタ41に出力される。ラッチタイミング信号は、最初の1回だけ、outComp1がLレベルからHレベルに変化したときに、例えばLレベルからHレベルに変化する信号がFF回路42に出力される。

【0090】

カウンタ41は、FF回路42と比較器43とそれぞれ電気的に接続されており、オシレータから入力されるCKをカウントし、そのカウント値を示すカウント信号をFF回路42及び比較器43に出力する。また、第1TG40からリセット信号が入力されると、カウンタを初期値へとリセットする。

FF回路42は、第1TG40から入力されるラッチタイミング信号に基づき、カウンタ41から入力されるカウント信号(各ビットの信号)をラッチし、ラッチしたカウント値の信号を比較器43に出力する。なお、ラッチタイミング信号は、ラッチしたカウント値を保持し続けるように制御される(例えばLレベルに固定)。つまり、Q2に駆動電流が供給されてからハーフ・オン状態になる時間(カウント値)がFF回路42に記録(保持)されることになる。

【0091】

比較器43は、第2TG44と電気的に接続されており、カウンタ41から入力されるカウント信号と、FF回路42から入力されるラッチされたカウント信号とを比較し、カウント信号のカウント値が、ラッチされたカウント信号のカウント値未満であるときは、Lレベルの信号を第2TG44に出力する。一方、カウント信号のカウント値が、ラッチされたカウント信号のカウント値以上のときは、Hレベルの信号を第2TG44に出力する。つまり、Q2がハーフ・オン状態になったときにHレベルの信号が第2TG44に出力される。

【0092】

第2TG44は、第1LST駆動回路11cのPTr3のゲート端子に電気的に接続されており、比較器43から、Hレベルの信号が入力されたときにLレベルの制御信号cnt_PTr3をPTr3のゲート端子に出力し、Lレベルの信号が入力されたときにHレベルの制御信号cnt_PTr3をPTr3のゲート端子に出力する。

【0093】

つまり、第1制御回路13aは、電源が投入されてから、Q2をオフ状態からオン状態に駆動する最初の1回目は、Q2のゲート端子に供給される信号out_PTr2がHレベルになってからQ2がハーフ・オン状態になるまでの時間(CKのカウント数)を計測して、これをFF回路42に保持する。そして、2回目以降は、outComp1を無視して、保持したカウント値とカウンタ41のカウント値とを比較し、カウンタ41のカウント値がFF42に保持されたカウント値以上になったときに、PTr3をオンにするLレベルのcnt_PTr3を出力する。これにより、マイコンからのctrl3が第1LST駆動回路11cに入力されると、Q2は、最初にPTr2だけで駆動電流が供給され、やがてQ2がハーフ・オン状態になると、PTr2に加えてPTr3がオンとなり、PTr2及びPTr3の2つのトランジスタによって駆動電流が供給される。

【0094】

なお、第1LST駆動回路11cの動作は、上記第1の実施の形態と同様となる。

また、第2制御回路13bは、駆動制御する対象が第2LST駆動回路11dのPTr3となるだけで、第1制御回路13aと同様の構成及び動作となる。

一方、本実施の形態では、上記2回目以降の動作において、電圧レベル検出部14の第1比較器14a及び第2比較器14bへの電源供給のオン/オフを切り替えることが可能な不図示のスイッチを切り替えて、電圧レベル検出部14の第1比較器14aへの電流供給を停止する。なお、Q4の2回目以降の動作に対しては、第2比較器14bへの電流供給を停止する。

【0095】

なお、電流供給の停止(オフ)タイミングは、例えば、モータ2が、変動の少ない負荷であれば、2回目以降の動作において、ずっと停止状態にする。また、モータ2が、動作状態(通常回転、逆回転、ブレーキなど)が変わるまでは変動が少ないような負荷である場合は、動作状態が変わるまで停止状態にするなど、負荷の性質に応じてタイミングを制御することができる。

【0096】

以上、本実施の形態のトランジスタ駆動装置100’は、ハーフ・オン状態の検出において、電圧レベル検出部14によって、Q2、Q4のVDSを検出し、この電圧レベルと、予め得ておいたハーフ・オン状態のときの電圧レベルVrefとを比較して、VDSがVref以上となったときにハーフ・オン状態になったことを示す信号を出力することができる。

これにより、Q2、Q4の入力容量と関係の深いゲートにかかる電圧で判断をすることができるので、ハーフ・オン状態の検出をより正確に行うことができる。

【0097】

更に、最初の1回目のオフ状態からオン状態への駆動時において、Q2又はQ4に駆動電流が供給されてからハーフ・オン状態となるまでの経過時間(カウント値)を計測して、これを保持し、2回目以降は、この保持された経過時間と、計測時間とを比較し、計測時間が保持された経過時間以上となったときに、Q2又はQ4がハーフ・オン状態になったと判断し、PTr3をオンに駆動する信号を生成して出力することができる。更に、Q2、Q4の2回目以降の動作において、第1比較器14a、第2比較器14bへの電源供給を停止することができる。

【0098】

これにより、ハーフ・オン状態になるまでの経過時間が記録されると、比較器の動作を停止して、カウンタ41のカウント値に基づく制御を行うことができるので、低消費電流化できる。

上記第2の実施の形態において、駆動電力供給部11は、形態1又は9に記載の駆動電力供給手段に対応し、駆動制御部13及びマイコンによる駆動電力供給部11の制御処理は、形態7又は9に記載の駆動制御手段に対応し、電圧レベル検出部14は、形態6に記載の駆動状態検出手段に対応する。

【0099】

なお、上記第1及び第2の実施の形態においては、Q2、Q4をオン状態からオフ状態にするときに、最初からNTr2及びNTr3を両方ともオンにする構成としたが、これに限らず、PTr2及びPTr3と同様に、最初にNTr2だけをオンにし、ハーフ・オン状態が検出されたら、NTr2に加えてNTr3をオンにする構成としてもよい。この場合において、NTr2とNTr3のトランジスタサイズを「NTr2<NTr3」としてもよい。また、「NTr2<NTr3」とした場合は、ハーフ・オン状態が検出されたら、NTr2に代えてNTr3をオンさせる構成としてもよい。

【0100】

また、上記第1及び第2の実施の形態においては、第1及び第2HST駆動回路11a及び11bと第1及び第2LST駆動回路11c及び11dとを、電界効果トランジスタ(NTr1〜3,10及びPTr1〜3,10)で構成したが、これに限らず、Q1〜Q4を駆動可能なバイポーラトランジスタで構成してもよい。

また、上記第1及び第2の実施の形態においては、Q1〜Q4を全てNチャンネル型のDMOSFETとしたが、これに限らず、ハイサイド側のQ1、Q3をPチャンネル型で構成したり、DMOSFETに限らず、他のパワートランジスタや、IGBT(Insulated Gate Bipolar Transistor)などで構成したりしてもよい。

【0101】

また、上記第1及び第2の実施の形態においては、本発明を直流モータを駆動するHブリッジ回路に適用したが、これに限らず、電磁弁などの負荷を駆動するブリッジ回路に本発明を適用してもよい。特に、電磁弁は、開弁側又は閉弁側への一方向の通電を行えばよいため、ブリッジ回路をハーフブリッジ構成とすることができる。

【図面の簡単な説明】

【0102】

【図1】本発明に係るモータ駆動装置1の構成を示すブロック図である。

【図2】Hブリッジ回路200の詳細な構成を示す図である。

【図3】DMOSFETの等価回路を示す図である。

【図4】トランジスタ駆動装置100の概略構成を示すブロック図である。

【図5】駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

【図6】第1HST駆動回路11aの詳細な回路構成を示す図である。

【図7】第1LST駆動回路11cの詳細な回路構成を示す図である。

【図8】電流レベル検出部12の構成を示す図である。

【図9】第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングを示すタイミングチャートである。

【図10】トランジスタ駆動装置100’の構成を示すブロック図である。

【図11】駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

【図12】電圧レベル検出部14の構成を示す図である。

【図13】第1制御回路13aの詳細な回路構成を示す図である。

【図14】従来のローサイド側のトランジスタのゲート駆動回路の一例を示す図である。

【図15】ハーフ・オン状態の例を示す波形図である。

【符号の説明】

【0103】

1…モータ駆動装置、2…直流モータ、100…トランジスタ駆動装置、200…Hブリッジ回路、Q1〜Q4…Nチャンネル型のDMOSFET、10,13…駆動制御回路、10a,10b…第1、第2TG回路、11…駆動電力供給部、11a,11b…第1,第2HST駆動回路、11c,11d…第1,第2LST駆動回路、12…電流レベル検出部、12a…I/V変換回路、12b…比較器、13a、13b…第1、第2制御回路、14…電圧レベル検出部、14a,14b…第1、第2比較器、PTr1〜PTr3,PTr10…Pチャンネル型の電界効果トランジスタ、NTr1〜NTr3,NTr10…Nチャンネル型の電界効果トランジスタ、41…カウンタ、42…FF回路、43…比較器

【技術分野】

【0001】

本発明は、モータ等の負荷を駆動するブリッジ回路のローサイド側のトランジスタをオフ状態からオン状態へと駆動するのに好適なトランジスタ駆動装置に関する。

【背景技術】

【0002】

従来、モータなどの負荷を駆動する回路として、高電位側(ハイサイド側)のトランジスタと、低電位側(ローサイド側)のトランジスタとから構成されるハーフ・ブリッジ回路、フル・ブリッジ回路などがある。このようなブリッジ回路は、ハイサイド側のトランジスタと、ローサイド側のトランジスタとがそれぞれ独立にオン又はオフに駆動制御され、負荷を通電又は非通電の状態にする。

【0003】

また、比較的高い電力を必要とし且つ高速なスイッチング動作を要求される負荷に対しては、ブリッジ回路を構成するトランジスタとして大電力用に設計されたMOSFET(metal-oxide-semiconductor field-effect transistor)が用いられる。大電力用のMOSFETとしては、例えば、DMOS(Double-Diffused MOSFET)などがある。

また、ブリッジ回路のローサイド側のトランジスタを駆動する回路としては、例えば、非特許文献1に記載のロー・サイド・ゲート・ドライブ回路がある。かかるゲート・ドライブ回路は、図14に示すように、NPNバイポーラ型トランジスタであるNPNTrと、PNPバイポーラ型トランジスタであるPNPTrと、ゲート直列抵抗RGと、ショットキ・バリア・ダイオードSDとを含んで構成される。NPNTrのエミッタ端子とPNPTrのエミッタ端子とが接続されており、更に、NPNTrのコレクタ端子が電源に接続され、PNPTrのコレクタ端子が接地されて、エミッタ・フォロア回路を構成している。NPNTrとPNPTrとの接続部はゲート直列抵抗RGを介してブリッジ回路のローサイド側のFETQ2のゲート端子に電気的に接続されている。更に、RGと並列にSDが、Q2のターン・オン時にはオフとなる方向に接続されている。

【0004】

従って、NPNTrとPNPTrの共通の入力端子にパルス・ジェネレータ(以下、PGという)からハイレベル(以下、Hレベルという)の信号が入力されると、NPNTrがオン状態に、PNPTr、SDはオフ状態になる。これによって、NPNTrのコレクタ−エミッタ間を電流が流れ、この電流がRGを介してQ2のゲートに流れ込む。この流れ込む電流は、Q2の入力容量Ciss(電極間容量+α)をチャージして、Q2のゲート電圧を駆動電位にまで引き上げ、Q2をオン状態へと駆動する。

【0005】

一方、入力端子にPGからローレベル(以下、Lレベルという)の信号が入力されると、PNPTr、SDがオン状態に、NPNTrはオフ状態になる。これにより、Q2のゲート電流(Cissの蓄積電荷)がRGをパスしてSDを流れ、PNPTrのエミッタ−コレクタ間を通ってグラウンド(低電位側)に放出される。そして、Cissの蓄積電荷が放出されるとQ2がオフ状態となる。

【非特許文献1】パワーMOSFET活用の基礎と実際、稲葉 保著、CQ出版社、2004年初版、P.053〜054

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上記従来技術においては、Q2がオフ状態からオン状態へと移行する途中において、Q2トランジスタのゲート−ドレイン間容量Cgdによるミラー効果の影響によって、図15に示すように、Q2のゲート電位(入力波形)とドレイン電位(出力波形)とが中間電位で一定になる状態(ハーフ・オン状態)が発生する。図15において、横軸は時間[μs]、縦軸は電圧[V]である。特に、Q2のCgdが大きくなるほどハーフ・オン状態の期間は長くなり、ブリッジ回路の動作に不具合を引き起こす恐れがある。また、このハーフ・オン状態は、特にHブリッジ回路のトランジスタのオン・オフ動作時にハイサイド側のトランジスタとローサイド側のトランジスタとの間に多大な貫通電流を生じさせて、消費電流の増大化を引き起こす恐れがあった。

【0007】

そこで、本発明は、このような従来の技術の有する未解決の課題に着目してなされたものであって、負荷を駆動するブリッジ回路のローサイド側のトランジスタを駆動するのに好適なトランジスタ駆動装置を提供することを目的としている。

【課題を解決するための手段】

【0008】

〔形態1〕 上記目的を達成するために、形態1のトランジスタ駆動装置は、駆動対象である負荷に電気的に接続されるハイサイド側の第1のトランジスタとローサイド側の第2のトランジスタとを含み、前記第1及び第2のトランジスタをオン又はオフにすることで前記負荷が通電又は非通電の状態となるブリッジ回路の前記第2のトランジスタを駆動するトランジスタ駆動装置であって、第1電源電位の供給される第1電源ノードと、前記第1電源電位よりも低電位の第2電源電位の供給される第2電源ノードと、前記第1電源ノードと前記第2電源ノードとの間に並列に接続された、第1の入力でオン・オフする第3のトランジスタ及び第2の入力でオン・オフする第4のトランジスタとを含み、前記第3及び第4のトランジスタの電流供給端子を前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタの前記駆動端子に駆動電力を供給する駆動電力供給手段と、前記第2のトランジスタのオフからオンへの移行途中における、該第2のトランジスタの出力電圧が中間電位で略一定となるハーフ・オン状態を検出する駆動状態検出手段と、前記第2のトランジスタをオフからオンにするときに、前記第1及び第2の入力を制御して前記第4のトランジスタよりも先に前記第3のトランジスタをオンにし、前記駆動状態検出手段で前記ハーフ・オン状態が検出されると前記第1及び第2の入力を制御して前記第3のトランジスタに加えて前記第4のトランジスタをオンにする駆動制御手段と、を備える。

【0009】

このような構成であれば、駆動制御手段が、第1及び第2の入力を制御して第3のトランジスタをオン状態にすると、第2のトランジスタに駆動電位が供給され駆動電流の供給が開始される。駆動電流が供給されると、第2のトランジスタはその入力容量がチャージされチャージ量の増加に伴いオフからオンへと移行していく。このオフからオンへの移行途中において、駆動状態検出手段によって、第2のトランジスタがハーフ・オン状態となったことが検出されると、駆動制御手段は、第1及び第2の入力を制御して、第3のトランジスタに加えて第4のトランジスタをオンにする。第4のトランジスタがオンされると、第2のトランジスタには、第3のトランジスタからの駆動電流に加え、第4のトランジスタからの駆動電流が供給される。

【0010】

これによって、第2のトランジスタには、ハーフ・オン状態のときに2つのトランジスタからの駆動電流が流れ込むことになり、入力容量のチャージ速度が上がって、従来のトランジスタ1つの駆動と比較して、ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

更に、ハーフ・オン状態が検出されるまでは第3のトランジスタだけをオンにして電流を供給し、ハーフ・オン状態が検出されてから第4のトランジスタもオンにするようにしたので、トランジスタがハーフ・オン状態になるまでの急激な電位変動の発生を低減しつつ、ハーフ・オン状態の期間を短くすることができるという効果が得られる。

【0011】

ここで、トランジスタがハーフ・オン状態になるまでに発生する急激な電位変動は負荷に接続する配線等のインダクタ成分によるサージ電圧を発生させやすくし、これによるトランジスタの破壊(ゲート膜破壊やドレイン端子破壊など)を引き起こしやすくする。

また、特にHブリッジ回路では、縦に接続された、ハイサイド側の第1のトランジスタと、ローサイド側の第2のトランジスタとが同時にオン状態となる場合があるため、このときに両者に貫通電流が流れる。そのため、例えば、第3及び第4のトランジスタを同時にオンにしたり、最初から第3のトランジスタよりも電流供給能力の大きいトランジスタを用いたりして、第2のトランジスタを駆動した場合は、トランジスタのゲート電位が第3のトランジスタだけで駆動したときよりも高くなり(VTHより高い電位で一度フラットになる)、両者に流れる貫通電流を大きくしてしまう可能性がある。

【0012】

つまり、ハーフ・オン状態になるまでは、比較的ゆっくりと入力容量のチャージを行ない、ハーフ・オン状態になってから一気にチャージを行うことで、サージ電圧の発生や貫通電流の増加を引き起こし難くしつつ、チャージ速度を増加させることができる。

ここで、上記ハーフ・オン状態とは、トランジスタの入力容量のチャージ中に、ミラー効果の影響で入力容量が増加するために発生する状態であり、トランジスタの出力電圧が中間の電位で略一定となる状態のことである。具体例を挙げると、例えば、トランジスタがMOSFETである場合は、ゲート駆動によって入力容量のチャージ中に、該MOSFETのゲート電圧がミラー効果の影響で中間電位で略一定となる期間が発生する。この期間では、FETの出力電圧(ドレイン電圧)も略一定となる。

また、上記電流供給端子は、第3及び第4のトランジスタが、バイポーラトランジスタであれば、例えば、エミッタ端子となり、FETであれば、例えば、ドレイン端子となる。

【0013】

〔形態2〕 更に、形態2のトランジスタ駆動装置は、形態1に記載のトランジスタ駆動装置において、前記第4のトランジスタは、前記第3のトランジスタよりも電流供給能力の大きいトランジスタサイズである。

【0014】

このような構成であれば、前記ハーフ・オン状態になるまでは、サイズの比較的小さい(電流供給能力の小さい)第3のトランジスタで第2のトランジスタの入力容量をチャージし、前記ハーフ・オン状態となると、第3のトランジスタに加えてサイズの比較的大きい(電流供給能力の大きい)第4のトランジスタで第2のトランジスタの入力容量をチャージすることができる。これにより、前記ハーフ・オン状態となるまでは、比較的少ない電流量でチャージし、前記ハーフ・オン状態となると比較的大きい電流量で一気に入力容量をチャージすることができるという効果が得られる。

【0015】

〔形態3〕 更に、形態3のトランジスタ駆動装置は、形態2に記載のトランジスタ駆動装置において、前記駆動制御手段は、前記ハーフ・オン状態が検出されると前記第3のトランジスタに代えて前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御する。

このような構成であれば、前記ハーフ・オン状態になるまでは、サイズの比較的小さい(電流供給能力の小さい)第3のトランジスタで第2のトランジスタの入力容量をチャージし、前記ハーフ・オン状態となると、第3のトランジスタに代えてサイズの比較的大きい(電流供給能力の大きい)第4のトランジスタで第2のトランジスタの入力容量をチャージすることができる。つまり、第3及び第4のトランジスタのサイズが異なる場合(電流供給能力の異なる場合)は、ハーフ・オン状態になったときに、2つともオンにするのではなく、第4のトランジスタだけをオン状態にする。

【0016】

〔形態4〕 更に、形態4のトランジスタ駆動装置は、形態1乃至3のいずれか1に記載のトランジスタ駆動装置において、前記第1及び第2のトランジスタは、電界効果トランジスタであり、前記第2のトランジスタの駆動端子はゲート端子である。

このような構成であれば、電界効果トランジスタである第2のトランジスタのターン・オン時間(入力容量のチャージ時間)を短縮することができ、従来と比較して、前記ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

【0017】

ここで、上記電界効果トランジスタ(FET)が、例えば、大電力用に設計されたものである場合は、第2のトランジスタの入力容量が比較的大きくなり、それだけ前記ハーフ・オン状態の期間が長くなる。この入力容量は、電流量やオン状態時の抵抗の大きさなどとのトレードオフとなる。つまり、FETを大電流且つ低抵抗にしたい場合は、トランジスタサイズを大きくする必要があり入力容量も大きくなる。

【0018】

〔形態5〕 更に、形態5のトランジスタ駆動装置は、形態1乃至請求項4のいずれか1に記載のトランジスタ駆動装置において、前記駆動状態検出手段は、前記負荷を通って前記第2のトランジスタに流れる電流の電流レベルを検出する電流検出部と、前記電流検出部で検出した電流レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電流レベルとを比較する電流レベル比較部とを有し、前記電流検出部で検出される電流レベルが前記所定の電流レベルとなったときに、前記ハーフ・オン状態を検出する。

【0019】

このような構成であれば、第3のトランジスタがオン状態になり、第2のトランジスタに駆動電流が供給されると、駆動状態検出手段は、電流検出部において、負荷を通って第2のトランジスタに流れる電流の電流レベルを検出する。電流レベルが検出されると、電流レベル比較部において、検出された電流レベルと予め用意された前記ハーフ・オン状態時の電流レベル(以下、不完全電流レベルという)とが比較される。そして、駆動制御手段は、この比較結果から、検出された電流レベルの方が不完全電流レベルよりも小さいレベルであれば、第3のトランジスタのみをオン状態にする。一方、検出された電流レベルが不完全電流レベル以上となった場合は、第3のトランジスタに加えて又は代えて、第4のトランジスタをオン状態にする。

【0020】

これにより、負荷の特性や第2のトランジスタの特性などに応じた不完全電流レベルを予め実験等によって得ておくことで、前記ハーフ・オン状態を確実に検出することができるという効果が得られる。

ここで、上記電流レベルの比較は、電流レベルを電圧レベルに変換して行っても良い。

【0021】

〔形態6〕 更に、形態6のトランジスタ駆動装置は、形態1乃至4のいずれか1に記載のトランジスタ駆動装置において、前記駆動状態検出手段は、前記第2のトランジスタの前記負荷との接続部の電圧レベルを検出する電圧検出部と、前記電圧検出部で検出される前記電圧レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電圧レベルとを比較する電圧レベル比較部とを有し、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなったときに、前記ハーフ・オン状態を検出する。

【0022】

このような構成であれば、第3のトランジスタがオン状態になり、第2のトランジスタに駆動電流が供給されると、駆動状態検出手段は、電圧検出部において、第2のトランジスタと負荷との電気的な接続部の電圧レベルを検出する。電圧レベルが検出されると、電圧レベル比較部において、検出された電圧レベルと予め用意された前記ハーフ・オン状態時の電圧レベル(以下、不完全電圧レベルという)とが比較される。そして、駆動制御手段は、この比較結果から、検出された電圧レベルの方が不完全電圧レベルよりも小さいレベルであれば、第3のトランジスタのみをオン状態にする。一方、検出された電圧レベルが不完全電圧レベル以上となった場合は、第3のトランジスタに加えて又は代えて、第4のトランジスタをオン状態にする。

【0023】

これにより、負荷の特性や第2のトランジスタの特性などに応じた不完全電圧レベルを予め実験等によって得ておくことで、前記ハーフ・オン状態を確実に検出することができるという効果が得られる。

【0024】

〔形態7〕 更に、形態7のトランジスタ駆動装置は、形態6に記載のトランジスタ駆動装置において、前記第2のトランジスタに駆動電流が供給されてからの経過時間を計測する時間計測手段と、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなるときの前記時間計測部の計測時間の情報を記録する時間記録手段とを更に備え、前記駆動制御手段は、前記時間記録手段によって計測時間が記録されると、以降は、前記時間計測手段の計測時間が前記記録した計測時間になるタイミングで、前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御する。

【0025】

このような構成であれば、第3のトランジスタがオンされ、第2のトランジスタに駆動電流が供給されると、時間計測手段によって、駆動電流の供給が開始されてからの時間が計測される。一方、電圧検出部では接続部の電圧レベルが検出され、電圧レベル比較部において、検出された電圧レベルと不完全電圧レベルとが比較される。そして、検出された電圧レベルが不完全電圧レベルになると、時間記録手段において、そのときの時間計測手段の計測時間が記録される。計測時間が記録されると、以降は、駆動制御手段は、第2のトランジスタをオフ状態からオン状態にするときに、時間計測手段の計測時間が、記録された計測時間になるまでは、第3のトランジスタのみをオンにして駆動電流を供給し、時間計測手段の計測時間が記録された計測時間になるタイミングで、第3のトランジスタに加えて又は代えて、第4のトランジスタをオンにする。

【0026】

これにより、前記ハーフ・オン状態をより確実に検出することができるという効果が得られる。

更に、例えば、起動後に変動の少ない負荷(例えば、PCのファンモータなど)を駆動するときは、計測時間の記録後に、電圧レベル比較部の動作を完全に停止することができるので、低消費電流化できるという効果も得られる。

【0027】

ここで、時間計測部は、第2のトランジスタに駆動電流の供給が開始されてからの経過時間を、例えば、カウンタ回路によって、外部から又は内部で供給されるクロックをカウントすることで計測する。そして、時間記録部は、不完全オン状態が発生したときのカウント値を記録し、次回からは、時間計測部のカウント値が記録されたカウント値になったときに不完全オン状態が発生したと判断する。

【0028】

〔形態8〕 更に、形態8のトランジスタ駆動装置は、形態1乃至7のいずれか1に記載のトランジスタ駆動装置において、前記ブリッジ回路は、ハイサイド側の一対の前記第1のトランジスタと、ローサイド側の一対の前記第2のトランジスタとから構成され、前記負荷への通電方向に応じて、対角に位置する第1のトランジスタ及び第2のトランジスタがオン又はオフされるHブリッジ型の回路である。

【0029】

このような構成であれば、負荷への通電方向を任意に変えることができるHブリッジ型の回路のローサイド側の第2のトランジスタに対しても、従来と比較して、ハーフ・オン状態への移行時の急激な電位変動の発生を抑えつつ、前記ハーフ・オン状態となる期間を短くすることができるという効果が得られる。

【0030】

〔形態9〕 更に、形態9のトランジスタ駆動装置は、形態1乃至8のいずれか1に記載のトランジスタ駆動装置において、前記駆動電力供給手段は、前記第3のトランジスタと前記第2電源ノードとの間に直列に接続された、第3の入力でオン・オフする第5のトランジスタと、前記第4のトランジスタと前記第2電源ノードとの間に直列に接続された、第4の入力でオン・オフする第6のトランジスタとを更に含み、前記第3及び第5のトランジスタの接続部と、前記第4及び第6のトランジスタの接続部とを前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタをオフにし且つ前記第5及び第6のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタから前記第2電源ノード側に電流を引き込む構成となっており、前記駆動制御手段は、前記第2のトランジスタをオン状態からオフ状態にするときに、前記第3及び第4のトランジスタを両方ともオフ状態にし、前記第5及び第6のトランジスタを両方ともオン状態にするように前記第1〜第4の入力を制御する。

【0031】

このような構成であれば、第2のトランジスタをオン状態からオフ状態にするときに、その入力容量として蓄積された電荷を2つのトランジスタを介して第2電源ノード側に引き込むことができるので、トランジスタ1つで引き込んでいた従来と比較して第2のトランジスタのターン・オフ時間を短縮することができる。これにより、オフ状態への移行中に発生する不完全オン状態の期間を従来と比較して短くすることができるという効果が得られる。

【発明を実施するための最良の形態】

【0032】

〔第1の実施の形態〕

以下、本発明の第1の実施の形態を図面に基づき説明する。図1〜図9は、本発明に係るトランジスタ駆動装置の第1の実施の形態を示す図である。

本実施の形態において、本発明に係るトランジスタ駆動装置を、モータを駆動するHブリッジ回路に適用し、このHブリッジ回路のローサイド側のトランジスタを駆動する構成とした。

【0033】

まず、本発明に係るモータ駆動装置1の構成を図1に基づき説明する。図1は、本発明に係るモータ駆動装置1の構成を示すブロック図である。

モータ駆動装置1は、図1に示すように、トランジスタ駆動装置100と、Hブリッジ回路200とを含んで構成される。

トランジスタ駆動装置100は、不図示のマイコンからの制御信号に基づき、Hブリッジ回路200を構成する各トランジスタを駆動する。

【0034】

Hブリッジ回路200は、自身を構成するハイサイド側のトランジスタとローサイド側のトランジスタとが、トランジスタ駆動装置100によってそれぞれ独立に駆動制御されると、その制御内容に応じて、駆動対象である直流モータ2を、正回転駆動、逆回転駆動、ブレーキ駆動などする。

【0035】

次に、図2に基づき、Hブリッジ回路200の詳細な構成を説明する。

ここで、図2は、Hブリッジ回路200の詳細な構成を示す図である。

Hブリッジ回路200は、図2に示すように、スイッチング素子としての役割を果たす4つのNチャンネル型のDMOSFETQ1〜Q4を、Q1、Q3をハイサイド側に、Q2、Q4をローサイド側に配してHブリッジ型に接続して構成される。

具体的に、Q1のソース端子とQ2のドレイン端子とを電気的に接続し、Q3のソース端子とQ4のドレイン端子とを電気的に接続し、Q1及びQ2の接続部から出力を取り出す出力端子OUTAと、Q3及びQ4の接続部から出力を取り出す出力端子OUTBとをそれぞれ形成して構成される。そして、このOUTA及びOUTBには、直流モータ2が接続されている。また、D1〜D4は、Q1〜Q4の内部に寄生的に作られたボディダイオードである。

【0036】

このHブリッジ回路200のハイサイド側(Q1、Q3のドレイン端子)には、モータの駆動電源から駆動電圧VBBが供給されるようになっている。一方、ローサイド側(Q2、Q4のソース端子側)は、電流検出用の抵抗Rsを介してグラウンドに接続されている。

Hブリッジ回路200のQ1〜Q4のゲート端子には、トランジスタ駆動装置100からの駆動線がそれぞれ電気的に接続されており、該駆動線を介して供給される駆動電位及び駆動電流に基づきQ1〜Q4がそれぞれ独立に駆動制御される。

【0037】

次に、図3に基づき、DMOSFET(Q1〜Q4)の入力容量について説明する。

ここで、図3は、DMOSFETの等価回路を示す図である。

DMOSFETは、図3に示すように、ゲート−ドレイン電極間の電極間容量Cgdと、ゲート−ソース電極間の電極間容量Cgsとを有する。ゲート電圧が0[V]のときのCgdとCgsとの和は入力容量Cissと呼ばれる。このようなDMOSFETをオン状態に駆動するには、Cissをチャージする必要がある。しかしながら、DMOSFETがオフからオンへと移行する過程において、ゲート−ソース間電圧VGSの変化によって、Cgdの容量が大きく変化するためCissの容量も大きく変化する(ミラー効果)。この見かけのCissは、下式(1)によって算出できる。

Ciss=Cgs+(1−AV)・Cgd ・・・(1)

上式(1)において、AVは電流増幅率である。

【0038】

ミラー効果の影響によって、オフからオンへと移行時のVGSが中間の電位で略一定になる状態が発生する。この状態が発生している期間は、ドレイン−ソース間電圧VDSも中間電位で略一定となる。この状態をハーフ・オン状態と呼ぶ。このハーフ・オン状態の期間は、Cissの容量の大きさに比例して長くなる。例えば、レイアウト換算で、300〜500[pF]などの大容量となると、ハーフ・オン状態の期間が長くなり、チャージ時間、放出時間の増加も重なって、ターン・オン時間、ターン・オフ時間も長くなる。

【0039】

ハーフ・オン状態の期間が長いと、高抵抗状態のドレイン−ソース間に電流が流れる期間が長くなるため、DMOSFETの発熱による自身のゲート膜の破壊などの不具合が生じる可能性がある。従って、ハーフ・オン状態の期間は短ければ短いほどよく、本発明は、Hブリッジ回路200のローサイド側のトランジスタ(Q2、Q4)について、ハーフ・オン状態の期間を短くすることを目的としている。

【0040】

次に、図4に基づき、トランジスタ駆動装置100の構成を説明する。

ここで、図4は、トランジスタ駆動装置100の概略構成を示すブロック図である。

トランジスタ駆動装置100は、図4に示すように、駆動制御部10と、駆動電力供給部11と、電流レベル検出部12とを含んで構成される。

駆動制御部10は、不図示のマイコンからの制御信号と電流レベル検出部12からの信号とに基づき、駆動電力供給部11の動作を制御する。

【0041】

駆動電力供給部11は、ハイサイド側のQ1、Q3をそれぞれ独立に制御するハイサイド用の駆動回路と、ローサイド側のQ2、Q4をそれぞれ独立に制御するローサイド用の駆動回路を有し、マイコンからの制御信号及び駆動制御部10からの制御信号に基づき、Hブリッジ回路200のQ1〜Q4のオン・オフ動作を独立に制御する。

電流レベル検出部12は、Hブリッジ回路200の電流検出抵抗Rsを流れる電流のレベルを検出する。更に、検出した電流レベルを電圧レベルに変換し、該電圧レベルと基準電圧レベルとを比較して、この比較結果を示す信号(以下、比較信号signal_aという)を駆動制御部10に出力する。

【0042】

次に、図5に基づき、駆動制御部10及び駆動電力供給部11の内部構成を説明する。

ここで、図5は、駆動制御部10及び駆動電力供給部11の内部構成を示すブロック図である。

駆動制御部10は、図5に示すように、駆動電力供給部11の第1LST(ローサイド・トランジスタ)駆動回路11cを制御する第1のTG(タイミングジェネレート)回路10aと、第2LST駆動回路11dを制御する第2のTG回路10bとを含んで構成される。

【0043】

第1のTG回路10aは、マイコンからの制御信号ctrl3と不図示のオシレータからのクロック信号CKと電流レベル検出部12からの比較信号signal_aとに基づき第1LST駆動回路11cの動作を制御する制御信号cnt_PTr3(詳細は後述)を生成し、これを第1LST駆動回路11cに供給する。

第2のTG回路10bは、マイコンからの制御信号ctrl4とクロック信号CKと電流レベル検出部12からの比較信号signal_aとに基づき第2LST駆動回路11dの動作を制御する制御信号cnt_PTr3を生成し、これを第2LST駆動回路11dに供給する。

【0044】

次に、駆動電力供給部11は、図5に示すように、マイコンからの制御信号ctrl1に基づき、Hブリッジ回路200のQ1のオン・オフ動作を制御する第1HST駆動回路11aと、マイコンからの制御信号ctrl2に基づき、Q3のオン・オフ動作を制御する第2HST駆動回路11bとを含んで構成される。

更に、駆動電力供給部11は、マイコンからの制御信号ctrl3と、制御信号cnt_PTr2(詳細は後述)とに基づき、Hブリッジ回路200のQ2のオン・オフ動作を制御する第1LST駆動回路11cと、マイコンからの制御信号ctrl4と、第1のTG回路10aからの制御信号cnt_PTr3とに基づき、Q4のオン・オフ動作を制御する第2LST駆動回路11dとを含んで構成される。

【0045】

ここで、マイコンからの制御信号ctrl1〜ctrl4は、モータの駆動内容に応じてQ1〜Q4のオン・オフを制御する信号(例えば、PWM信号)であり、Q1〜Q4は、トランジスタ駆動装置100において、各DMOSFETに対応する制御信号がLレベルでオンに、Hレベルでオフに駆動制御される。

【0046】

次に、図6に基づき、第1HST駆動回路11aの詳細な回路構成を説明する。

ここで、図6は、第1HST駆動回路11aの詳細な回路構成を示す図である。

第1HST駆動回路11aは、図6に示すように、Pチャンネル型の電界効果トランジスタPTr1、PTr10と、Nチャンネル型の電界効果トランジスタNTr1、NTr10と、レベルシフタ30と、電圧クランプ回路32とを含んで構成される。

PTr1とNTr1とは、電源電位VBB+VGL(VGH)の供給されるVGHノードと、電源電位VBBの供給されるVBBノードとの間に直列に接続されている。ここで、VBBはモータ駆動電位、VGHは、ハイサイド側のDMOSFET(Q1、Q3)のゲート駆動電位、VGLは、ローサイド側のDMOSFET(Q2、Q4)のゲート駆動電位である。

【0047】

より具体的に、PTr1のソース端子はVGHノードに電気的に接続され、ドレイン端子はNTr1のドレイン端子に電気的に接続され、NTr1のソース端子はVBBノードに電気的に接続されている。PTr10のソース端子はVGHノードに電気的に接続され、ドレイン端子はNTr10のドレイン端子に電気的に接続され、PTr10及びNTr10のゲート端子は電圧クランプ回路32に電気的に接続され、NTr10のソース端子は、電圧クランプ回路32とQ1及びQ2の接続部(OUTA)と電気的に接続されている。

【0048】

PTr1とNTr1のゲート端子は、共通線でレベルシフタ30の出力端子と電気的に接続されている。PTr1とNTr1のドレイン接続部は、PTr10とNTr10のゲート接続部と電気的に接続され、PTr10とNTr10のドレイン接続部は、Q1のゲート端子に電気的に接続されている。

レベルシフタ30は、VGLと、VBBと、VGHとの3種類の電源電位に基づき、入力信号の電圧レベル0[V]〜VGL[V]を、VBB[V]〜VGH[V]にレベルシフトして、その信号を出力する回路である。

【0049】

具体的に、マイコンからの制御信号ctrl1の信号電位V1がLレベル(例えば0[V])のときは、この信号の電圧レベルをVBB[V]までシフトして、VBB[V]の信号を出力する。この場合は、PTr1がオン、NTr1がオフとなり、PTr1を介して駆動電流がQ1のゲート端子に供給され、Q1をオフからオンへと駆動する。

一方、マイコンからの制御信号の信号電位V1がHレベル(例えば5[V])のときは、この信号の電圧レベルをVGH[V]にレベルシフトして、VGH[V]の信号を出力する。この場合は、NTr1がオン、PTr1がオフとなり、NTr1を介して、Q1の入力容量Cissに蓄積された電荷をVBBノード側へと引き込む。

【0050】

電圧クランプ回路32は、ツェナーダイオード等で構成されており、NTr10のゲート−ソース間に定格電圧以上の高い電圧が印加されないように保護する回路である。

なお、第2HST駆動回路11bは、駆動制御する対象がQ3となるだけで、第1HST駆動回路11aと同様の構成となる。

【0051】

次に、図7に基づき、第1LST駆動回路11cの詳細な回路構成を説明する。

ここで、図7は、第1LST駆動回路11cの詳細な回路構成を示す図である。

第1LST駆動回路11cは、図7に示すように、Pチャンネル型の電界効果トランジスタPTr2と、Nチャンネル型の電界効果トランジスタNTr2、NTr3と、PTr2よりも電流供給能力の大きいPチャンネル型の電界効果トランジスタPTr3と、レベルシフタ31とを含んで構成される。

【0052】

PTr2とNTr2とは、電源電位VGLの供給されるVGLノード(第1電源ノード)と、接地電位の供給される接地ノード(第2電源ノード)との間に直列に接続されており、PTr3とNTr3とは、VGLノードと、接地ノードとの間に直列に接続されている。そして、これら直列接続されたPTr2及びNTr2と、PTr3及びNTr3とは並列に接続されている。

【0053】

より具体的に、PTr2のソース端子は、VGLノードに電気的に接続され、ドレイン端子はNTr2のドレイン端子に電気的に接続され、NTr2のソース端子は接地ノードに電気的に接続されている。PTr3のソース端子は、VGLノードに電気的に接続され、ドレイン端子はNTr3のドレイン端子に電気的に接続され、NTr3のソース端子は接地ノードに電気的に接続されている。

【0054】

PTr2とNTr2のゲート端子は、共通線でレベルシフタ31の出力端子と電気的に接続されている。PTr2とNTr2のドレイン接続部はQ2のゲート端子に電気的に接続されている。

PTr3のゲート端子は、マイコンからの制御信号を入力する不図示の端子に電気的に接続されている。NTr3のゲート端子はレベルシフタ31の出力端子に電気的に接続されている。PTr3とNTr3の接続部はQ2のゲート端子に電気的に接続されている。

【0055】

レベルシフタ31は、VGLと、マイコンからの制御信号の電位V2と接地電位との3種類の電源電位に基づき、入力信号の電圧レベルV2[V]をVGL[V]にレベルシフトした信号を出力する回路である。なお、V2が0[V]の場合は、0[V](接地電位)の信号を出力するように構成されている。

具体的に、マイコンからの制御信号の信号電位V2がLレベル(例えば0[V])のときは、Lレベルの信号(0[V]の信号)を制御信号cnt_PTr2(第1の入力)として出力する。この場合は、PTr2がオン、NTr2がオフとなり、PTr2を介して駆動電流がQ2のゲート端子に供給される。

【0056】

一方、マイコンからの制御信号がHレベル(例えば5[V])のときは、この信号の電圧レベルをVGL[V]にレベルシフトして、VGL[V]の信号を制御信号cnt_PTr2として出力する。この場合は、NTr2がオン、NTr3がオン、PTr2がオフとなり、NTr2、NTr3を介して、Q2の入力容量Cissに蓄積された電荷を接地ノード側へと引き込む。

【0057】

つまり、2つのトランジスタを介して入力容量Cissにチャージされた電荷を引き込むようにしたので、トランジスタ1つで引き込む場合と比較して、オン状態からオフ状態への移行時のハーフ・オン状態の期間を短くできると共に、Q2のターン・オフ時間も短くすることができる。

更に、第1のTG回路10aからのLレベル(例えば0[V])の制御信号cnt_PTr3(第2の入力)がPTr3のゲート端子に入力されると、PTr3がオンとなり、PTr3を介して駆動電流がQ2のゲート端子に供給される。このPTr3を、PTr2と同時にオンにすると、PTr2及びPTr3の2つのトランジスタを介して駆動電流がQ2へと供給される。しかも、PTr2よりも電流供給能力の大きいPTr3が加わるため、これにより、入力容量のチャージ速度が急激に上がり、ハーフ・オン状態の期間を短縮することができる。

【0058】

従って、駆動制御部10における第1のTG回路10aは、PTr2とPTr3の両方を用いて、Q2をオフからオン状態に駆動するタイミングの制御信号cnt_PTr3を生成し、第1LST駆動回路11cに供給するようになっている。第2のTG回路10bについても、対象が第2LST駆動回路11dとなるだけで同様である。

本発明は、このPTr3を設け、Q2(Q4)をオン駆動するときにPTr2に加えてPTr3をオンにする点と、PTr3をオンにするタイミングとに主な特徴がある。PTr3をオンにするタイミングについては後述する。

【0059】

なお、第2LST駆動回路11dは、駆動制御する対象がQ4となるだけで、第1LST駆動回路11cと同様の構成となる。

また、PTr2とPTr3のトランジスタサイズを「PTr2<PTr3」としたが、PTr2のトランジスタサイズは、Q2、Q4のデバイス特性に基づき決定する。また、PTr3のトランジスタサイズは、Q2、Q4のターン・オン時間、ターン・オフ時間、ターン・オン、オフ時の伝播遅延時間などに基づき決定する。

【0060】

例えば、Q2、Q4のデバイス特性が、スレッショルド電圧VTHが「1.4±0.2[V]」、オン状態における抵抗RONが「0.30Ω・mm2以下」、ブレークダウン電圧BVDS「60[V]以上」、電流容量「1.0[A]〜1.5[A]」であるとすると、これらの特性に基づき、Q2、Q4のゲートをドライブ可能なサイズにPTr2のトランジスタサイズを決定する。

【0061】

また、Q2、Q4の伝播遅延時間が「出力電流IO=±1.3[A]、50%to90%ENABLEオンからシンク出力オン1.0[μs]」、「出力電流IO=±1.3[A]、50%to90%ENABLEオフからシンク出力オフ0.8[μs]」であるとすると、これらの遅延時間に基づきPTr3のトランジスタサイズを決定する。

【0062】

次に、図8に基づき、電流レベル検出部12の構成を説明する。

ここで、図8は、電流レベル検出部12の構成を示す図である。

電流レベル検出部12は、図8に示すように、I/V変換回路12aと、比較器12bとを含んで構成される。

I/V変換回路12aは、その入力端子がHブリッジ回路200の電流検出抵抗Rsの両端に電気的に接続されており、その出力端子が比較器12bの入力端子に電気的に接続されている。そして、Hブリッジ回路のRsを流れる電流が入力されると、その電流を電圧に変換して比較器12bに入力する。

【0063】

比較器12bは、その出力端子が、駆動制御部10の第1のTG回路10a及び第2のTG回路10bの入力端子に電気的に接続されている。そして、I/V変換回路12aから入力された電圧Vsと、基準電圧Vrefとを比較して、Vsの電圧レベルがVrefのレベル以上であればHレベルの比較信号signal_aを出力し、Vsの電圧レベルがVrefのレベル未満であればLレベルの比較信号signal_aを出力する。

【0064】

ここで、Rsを流れる電流Isは、例えば、図8に示すように、Hブリッジ回路200のQ3がオン状態のときで、且つQ2がオフ状態からオン状態へと移行し、Q2のドレイン−ソース間を電流が流れる状態となったときに、モータ2のコイルMLを通過して流れる電流である(図中の点線矢印)。

本実施の形態においては、検出電圧Vsのレベルが、先述したハーフ・オン状態となるレベル(中間電位)を予め実験で得るか、負荷(モータ)や回路を構成する各素子の特性等から算出などして得ておき、そのレベルの電圧を基準電圧Vrefとして比較器12bに入力する。

【0065】

つまり、電流レベル検出部12は、Rsを流れるIsのレベルを電圧レベルVsに変換してVrefと比較し、この比較結果を駆動制御部10に出力する。

従って、この比較結果を示す信号signal_aは、検出電圧Vsが中間電位の状態にあるときはHレベルの信号となり、そうでないときはLレベルの信号となる。

【0066】

次に、図9に基づき、第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングについて説明する。

ここで、図9は、第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングを示すタイミングチャートである。

本発明は、Q2、Q4のオフ状態からオン状態への移行時のハーフ・オン状態の期間を短くするために、第1及び第2LST駆動回路11c及び11dのPTr2及びPTr3をオン・オフのタイミングを制御する。なお、PTr2及びPTr3のタイミング制御については、第1及び第2LST駆動回路11c及び11dの双方において同様の制御内容となるので、以下、第1LST駆動回路11cのPTr2及びPTr3のタイミング制御について説明する。

【0067】

本実施の形態においては、マイコンからの制御信号ctrl3がそのまま第1LST駆動回路11cに入力される。そして、第1LST駆動回路11cは、ctrl3がHレベルの信号の場合はレベルシフタ31でゲートの駆動電位VGLまでレベルシフトして、この信号をPTr2のゲート端子に供給する。一方、ctrl3がLレベルの場合はそのままPTr2のゲート端子に供給する。

【0068】

従って、ctrl3がLレベルの信号であればPTr2を制御する制御信号cnt_PTr2はLレベルの信号となり、PTr2をオンにする。これにより、PTr2を介してQ2のゲート端子に駆動電流が供給され、入力容量Cissのチャージが開始される。

一方、第1のTG回路10aは、マイコンからの制御信号であるctrl3と、電流レベル検出部12の比較器12bから入力されるsignal_aとに基づきPTr3のオン・オフを制御する制御信号cnt_PTr3を生成する。

【0069】

具体的に、マイコンからのctrl3がLレベルの信号であり、図9に示すように、比較器12bからのsignal_aがLレベルの信号であるときは、Q2はハーフ・オン状態ではないと判断できるので、cnt_PTr3としてHレベルの信号を生成し、この信号をPTr3のゲート端子に供給する。この場合、PTr3はオフとなる。

一方、ctrl3がLレベルの信号であり、図9に示すように、signal_aがHレベルの信号であるときは、Q2がハーフ・オン状態になっていると判断できるので、cnt_PTr3としてLレベルの信号を生成し、この信号をPTr3のゲート端子に供給する。この場合、PTr3はオン状態となる。このとき、cnt_PTr2をLレベルに維持してPTr2のオン状態を維持する。従って、PTr2及びPTr3の2つのトランジスタを介して、Q2のゲート端子に駆動電流が供給される。

【0070】

また、ctrl3がLレベルからHレベルの信号になると、図9に示すように、cnt_PTr2もHレベルの信号となり、PTr2をオフにする。cnt_PTr2はNTr2及びNTr3のゲート端子にも供給されるので、NTr2及びNTr3が共にオン状態となる。そして、これら2つのトランジスタを介して、Q2のCissにチャージされた電荷が接地ノード側に引き込まれ放出される。

【0071】

一方、図9に示すように、ctrl3(cnt_PTr2)がHレベルの信号になると、第1のTG回路10aは、cnt_PTr3としてHレベル(VGL)の信号を生成し、この信号をPTr3のゲート端子に供給する。これにより、PTr3はオフとなる。

なお、本実施の形態においては、PTr3を、PTr2よりも電流供給能力の大きなトランジスタサイズで形成しているため、PTr3をオンにするときに、PTr2をオフにしてもよい。

【0072】

以上、本実施の形態のトランジスタ駆動装置100は、モータ2を駆動するHブリッジ回路200のローサイド側のトランジスタQ2、Q4をオフからオンに駆動する際に、Q2、Q4をオンに駆動するトランジスタであるPTr2及びPTr3における、PTr2を先にオンにして、PTr2のみでQ2又はQ4のゲートに駆動電流を供給し、電流レベル検出部12の比較結果から、Q2又はQ4のハーフ・オン状態が検出されたときは、PTr2に加えてPTr3をオンにして、PTr2及びPTr3の2つのトランジスタを介して、Q2のゲートに駆動電流を供給するようにした。

【0073】

これにより、トランジスタがハーフ・オン状態になるまでの急激な電位変動の発生を低減しつつ、オフからオンに移行時のハーフ・オン状態の期間を短くすることができる。

更に、Q2、Q4をオンからオフに駆動する際に、NTr2及びNTr3の2つのトランジスタをオンにして、Q2、Q4の入力容量Cissにチャージされた電荷が接地ノード側に引き込むこうにした。

【0074】

これにより、オンからオフへの移行時のハーフ・オン状態の期間を短くすることができる。

上記第1の実施の形態において、駆動電力供給部11は、形態1又は9に記載の駆動電力供給手段に対応し、駆動制御部10及びマイコンによる駆動電力供給部11の制御処理は、形態1、3及び9のいずれか1に記載の駆動制御手段に対応し、電流レベル検出部12は、形態1又は5に記載の駆動状態検出手段に対応する。

【0075】

〔第2の実施の形態〕

次に、本発明の第2の実施の形態を図面に基づき説明する。図10〜図13は、本発明に係るトランジスタ駆動装置の第2の実施の形態を示す図である。

【0076】

本実施の形態は、上記第1の実施の形態のHブリッジ回路200のQ2、Q4のハーフ・オン状態を判断するのに、Q2、Q4のドレイン−ソース間電圧VDSを基準電圧Vrefと比較する点と、Q2、Q4をオフ状態からオン状態に駆動するときに、最初の1回目は、PTr2のみを駆動したときの、Q2、Q4に駆動電流の供給を開始してからハーフ・オン状態となるまでの時間(カウント値)を計測して記録し、2回目以降は、カウント値が記録した値となったときに、PTr2に加えてPTr3をオンに駆動する点とが上記第1の実施の形態と異なる。

【0077】

以下、上記第1の実施の形態と同様の構成部については同じ符号を付して説明を適宜省略し、異なる部分について詳細に説明する。

まず、図10に基づき、本実施の形態に係るトランジスタ駆動装置100’の構成を説明する。

ここで、図10は、トランジスタ駆動装置100’の構成を示すブロック図である。

【0078】

トランジスタ駆動装置100’は、図10に示すように、駆動制御部13と、駆動電力供給部11と、電圧レベル検出部14とを含んで構成される。

駆動制御部13は、第1及び第2LST駆動回路11c及び11dからのPTr2の出力信号out_PTr2(Q2のゲートに供給される信号)と電圧レベル検出部14からの信号とに基づき、駆動電力供給部11の動作を制御する。

【0079】

電圧レベル検出部14は、Hブリッジ回路200のQ2、Q4のVDSを検出し、この電圧レベルと基準電圧レベルとを比較して、この比較結果を示す信号(以下、比較信号outCompという)を駆動制御部13に出力する。

【0080】

次に、図11に基づき、駆動制御部13の内部構成を説明する。

ここで、図11は、駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

駆動制御部13は、図11に示すように、第1LST駆動回路11cを制御する第1制御回路13aと、第2LST駆動回路11dを制御する第2制御回路13bとを含んで構成される。

【0081】

第1制御回路13aは、第1LST駆動回路11cからの出力信号out_PTr2と不図示のオシレータからのクロック信号CKと電圧レベル検出部14からの比較信号outComp1とに基づき第1LST駆動回路11cのPTr3のオン・オフ動作を制御する制御信号cnt_PTr3を生成し、これを第1LST駆動回路11cに供給する。

【0082】

第2制御回路13bは、第2LST駆動回路11dからの出力信号out_PTr2とクロック信号CKと電圧レベル検出部14からの比較信号outComp2とに基づき第2LST駆動回路11dのPTr3のオン・オフ動作を制御する制御信号cnt_PTr3を生成し、これを第2LST駆動回路11dに供給する。

なお、図示しないが、第1LST駆動回路11cから出力信号out_PTr2を得るために、第1制御回路13aのout_PTr2の入力端子と、第1LST駆動回路11cのPTr2の出力端子とが電気的に接続されている。

同様に、第2制御回路13bのout_PTr2の入力端子と、第2LST駆動回路11dのPTr2の出力端子とが電気的に接続されている。

【0083】

次に、図12に基づき、電圧レベル検出部14の構成を説明する。

ここで、図12は、電圧レベル検出部14の構成を示す図である。

電圧レベル検出部14は、図12に示すように、第1比較器14aと、第2比較器14bとを含んで構成される。

【0084】

第1比較器14aは、入力端子にHブリッジ回路200のQ1とQ2との接続部N1が電気的に接続されており、出力端子が駆動制御部10の第1制御回路13aの入力端子に電気的に接続されている。そして、入力端子に入力される接続部N1の電位(Q2のVDS)と、基準電圧Vrefとを比較して、VDSの電圧レベルがVrefのレベル以上であればHレベルの第1比較信号outComp1を出力し、VDSの電圧レベルがVrefのレベル未満であればLレベルの第1比較信号outComp1を出力する。

【0085】

第2比較器14bは、入力端子にHブリッジ回路200のQ3とQ4との接続部N2が電気的に接続されており、出力端子が駆動制御部10の第2制御回路13bの入力端子に電気的に接続されている。そして、入力端子に入力される接続部N2の電位(Q4のVDS)と、基準電圧Vrefとを比較して、VDSの電圧レベルがVrefのレベル以上であればHレベルの第2比較信号outComp2を出力し、VDSの電圧レベルがVrefのレベル未満であればLレベルの第2比較信号outComp2を出力する。

【0086】

ここで、VDSのレベルは、Q2又はQ4の入力容量のチャージ量と比例する。そこで、本実施の形態では、VDSのレベルがハーフ・オン状態となるレベルか否かを検出する。

なお、本実施の形態においては、Q2及びQ4のVDSのレベルが、先述したハーフ・オン状態となるレベル(中間電位)を予め実験で得るか、負荷(モータ)や回路を構成する各素子の特性等から算出などして得ておき、そのレベルの電圧を基準電圧Vrefとして比較器12bに入力する。

【0087】

つまり、電圧レベル検出部14は、接続部N1、N2の電圧レベルVDSとVrefとを比較し、この比較結果を駆動制御部13に出力する。

従って、この比較結果を示す信号outComp1、outComp2は、Q2、Q4のVDSが中間電位の状態にあるときはHレベルの信号となり、そうでないときはLレベルの信号となる。

【0088】

次に、図13に基づき、第1制御回路13aの詳細な回路構成を説明する。

ここで、図13は、第1制御回路13aの詳細な回路構成を示す図である。

第1制御回路13aは、図13に示すように、第1TG(タイミングジェネレータ)40と、カウンタ41と、FF(フリップフロップ)回路42と、比較器43と、第2TG44とを含んで構成される。

【0089】

第1TG40は、カウンタ41及びFF回路42とそれぞれ電気的に接続されており、第1LST駆動回路11cからの信号cnt_PTr2と、電圧レベル検出部14からの比較信号outComp1と、オシレータからのクロック信号CKとに基づき、カウンタのリセット信号と、FF回路42のラッチタイミング信号とを生成し、それぞれに出力する。カウンタ41のリセット信号は、cnt_PTr2のレベルがHレベルからLレベルに変化したときにカウンタ41に出力される。ラッチタイミング信号は、最初の1回だけ、outComp1がLレベルからHレベルに変化したときに、例えばLレベルからHレベルに変化する信号がFF回路42に出力される。

【0090】

カウンタ41は、FF回路42と比較器43とそれぞれ電気的に接続されており、オシレータから入力されるCKをカウントし、そのカウント値を示すカウント信号をFF回路42及び比較器43に出力する。また、第1TG40からリセット信号が入力されると、カウンタを初期値へとリセットする。

FF回路42は、第1TG40から入力されるラッチタイミング信号に基づき、カウンタ41から入力されるカウント信号(各ビットの信号)をラッチし、ラッチしたカウント値の信号を比較器43に出力する。なお、ラッチタイミング信号は、ラッチしたカウント値を保持し続けるように制御される(例えばLレベルに固定)。つまり、Q2に駆動電流が供給されてからハーフ・オン状態になる時間(カウント値)がFF回路42に記録(保持)されることになる。

【0091】

比較器43は、第2TG44と電気的に接続されており、カウンタ41から入力されるカウント信号と、FF回路42から入力されるラッチされたカウント信号とを比較し、カウント信号のカウント値が、ラッチされたカウント信号のカウント値未満であるときは、Lレベルの信号を第2TG44に出力する。一方、カウント信号のカウント値が、ラッチされたカウント信号のカウント値以上のときは、Hレベルの信号を第2TG44に出力する。つまり、Q2がハーフ・オン状態になったときにHレベルの信号が第2TG44に出力される。

【0092】

第2TG44は、第1LST駆動回路11cのPTr3のゲート端子に電気的に接続されており、比較器43から、Hレベルの信号が入力されたときにLレベルの制御信号cnt_PTr3をPTr3のゲート端子に出力し、Lレベルの信号が入力されたときにHレベルの制御信号cnt_PTr3をPTr3のゲート端子に出力する。

【0093】

つまり、第1制御回路13aは、電源が投入されてから、Q2をオフ状態からオン状態に駆動する最初の1回目は、Q2のゲート端子に供給される信号out_PTr2がHレベルになってからQ2がハーフ・オン状態になるまでの時間(CKのカウント数)を計測して、これをFF回路42に保持する。そして、2回目以降は、outComp1を無視して、保持したカウント値とカウンタ41のカウント値とを比較し、カウンタ41のカウント値がFF42に保持されたカウント値以上になったときに、PTr3をオンにするLレベルのcnt_PTr3を出力する。これにより、マイコンからのctrl3が第1LST駆動回路11cに入力されると、Q2は、最初にPTr2だけで駆動電流が供給され、やがてQ2がハーフ・オン状態になると、PTr2に加えてPTr3がオンとなり、PTr2及びPTr3の2つのトランジスタによって駆動電流が供給される。

【0094】

なお、第1LST駆動回路11cの動作は、上記第1の実施の形態と同様となる。

また、第2制御回路13bは、駆動制御する対象が第2LST駆動回路11dのPTr3となるだけで、第1制御回路13aと同様の構成及び動作となる。

一方、本実施の形態では、上記2回目以降の動作において、電圧レベル検出部14の第1比較器14a及び第2比較器14bへの電源供給のオン/オフを切り替えることが可能な不図示のスイッチを切り替えて、電圧レベル検出部14の第1比較器14aへの電流供給を停止する。なお、Q4の2回目以降の動作に対しては、第2比較器14bへの電流供給を停止する。

【0095】

なお、電流供給の停止(オフ)タイミングは、例えば、モータ2が、変動の少ない負荷であれば、2回目以降の動作において、ずっと停止状態にする。また、モータ2が、動作状態(通常回転、逆回転、ブレーキなど)が変わるまでは変動が少ないような負荷である場合は、動作状態が変わるまで停止状態にするなど、負荷の性質に応じてタイミングを制御することができる。

【0096】

以上、本実施の形態のトランジスタ駆動装置100’は、ハーフ・オン状態の検出において、電圧レベル検出部14によって、Q2、Q4のVDSを検出し、この電圧レベルと、予め得ておいたハーフ・オン状態のときの電圧レベルVrefとを比較して、VDSがVref以上となったときにハーフ・オン状態になったことを示す信号を出力することができる。

これにより、Q2、Q4の入力容量と関係の深いゲートにかかる電圧で判断をすることができるので、ハーフ・オン状態の検出をより正確に行うことができる。

【0097】

更に、最初の1回目のオフ状態からオン状態への駆動時において、Q2又はQ4に駆動電流が供給されてからハーフ・オン状態となるまでの経過時間(カウント値)を計測して、これを保持し、2回目以降は、この保持された経過時間と、計測時間とを比較し、計測時間が保持された経過時間以上となったときに、Q2又はQ4がハーフ・オン状態になったと判断し、PTr3をオンに駆動する信号を生成して出力することができる。更に、Q2、Q4の2回目以降の動作において、第1比較器14a、第2比較器14bへの電源供給を停止することができる。

【0098】

これにより、ハーフ・オン状態になるまでの経過時間が記録されると、比較器の動作を停止して、カウンタ41のカウント値に基づく制御を行うことができるので、低消費電流化できる。

上記第2の実施の形態において、駆動電力供給部11は、形態1又は9に記載の駆動電力供給手段に対応し、駆動制御部13及びマイコンによる駆動電力供給部11の制御処理は、形態7又は9に記載の駆動制御手段に対応し、電圧レベル検出部14は、形態6に記載の駆動状態検出手段に対応する。

【0099】

なお、上記第1及び第2の実施の形態においては、Q2、Q4をオン状態からオフ状態にするときに、最初からNTr2及びNTr3を両方ともオンにする構成としたが、これに限らず、PTr2及びPTr3と同様に、最初にNTr2だけをオンにし、ハーフ・オン状態が検出されたら、NTr2に加えてNTr3をオンにする構成としてもよい。この場合において、NTr2とNTr3のトランジスタサイズを「NTr2<NTr3」としてもよい。また、「NTr2<NTr3」とした場合は、ハーフ・オン状態が検出されたら、NTr2に代えてNTr3をオンさせる構成としてもよい。

【0100】

また、上記第1及び第2の実施の形態においては、第1及び第2HST駆動回路11a及び11bと第1及び第2LST駆動回路11c及び11dとを、電界効果トランジスタ(NTr1〜3,10及びPTr1〜3,10)で構成したが、これに限らず、Q1〜Q4を駆動可能なバイポーラトランジスタで構成してもよい。

また、上記第1及び第2の実施の形態においては、Q1〜Q4を全てNチャンネル型のDMOSFETとしたが、これに限らず、ハイサイド側のQ1、Q3をPチャンネル型で構成したり、DMOSFETに限らず、他のパワートランジスタや、IGBT(Insulated Gate Bipolar Transistor)などで構成したりしてもよい。

【0101】

また、上記第1及び第2の実施の形態においては、本発明を直流モータを駆動するHブリッジ回路に適用したが、これに限らず、電磁弁などの負荷を駆動するブリッジ回路に本発明を適用してもよい。特に、電磁弁は、開弁側又は閉弁側への一方向の通電を行えばよいため、ブリッジ回路をハーフブリッジ構成とすることができる。

【図面の簡単な説明】

【0102】

【図1】本発明に係るモータ駆動装置1の構成を示すブロック図である。

【図2】Hブリッジ回路200の詳細な構成を示す図である。

【図3】DMOSFETの等価回路を示す図である。

【図4】トランジスタ駆動装置100の概略構成を示すブロック図である。

【図5】駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

【図6】第1HST駆動回路11aの詳細な回路構成を示す図である。

【図7】第1LST駆動回路11cの詳細な回路構成を示す図である。

【図8】電流レベル検出部12の構成を示す図である。

【図9】第1又は第2LST駆動回路11c又は11dのPTr2及びPTr3の駆動タイミングを示すタイミングチャートである。

【図10】トランジスタ駆動装置100’の構成を示すブロック図である。

【図11】駆動制御部13及び駆動電力供給部11の内部構成を示すブロック図である。

【図12】電圧レベル検出部14の構成を示す図である。

【図13】第1制御回路13aの詳細な回路構成を示す図である。

【図14】従来のローサイド側のトランジスタのゲート駆動回路の一例を示す図である。

【図15】ハーフ・オン状態の例を示す波形図である。

【符号の説明】

【0103】

1…モータ駆動装置、2…直流モータ、100…トランジスタ駆動装置、200…Hブリッジ回路、Q1〜Q4…Nチャンネル型のDMOSFET、10,13…駆動制御回路、10a,10b…第1、第2TG回路、11…駆動電力供給部、11a,11b…第1,第2HST駆動回路、11c,11d…第1,第2LST駆動回路、12…電流レベル検出部、12a…I/V変換回路、12b…比較器、13a、13b…第1、第2制御回路、14…電圧レベル検出部、14a,14b…第1、第2比較器、PTr1〜PTr3,PTr10…Pチャンネル型の電界効果トランジスタ、NTr1〜NTr3,NTr10…Nチャンネル型の電界効果トランジスタ、41…カウンタ、42…FF回路、43…比較器

【特許請求の範囲】

【請求項1】

駆動対象である負荷に電気的に接続されるハイサイド側の第1のトランジスタとローサイド側の第2のトランジスタとを含み、前記第1及び第2のトランジスタをオン又はオフにすることで前記負荷が通電又は非通電の状態となるブリッジ回路の前記第2のトランジスタを駆動するトランジスタ駆動装置であって、

第1電源電位の供給される第1電源ノードと、前記第1電源電位よりも低電位の第2電源電位の供給される第2電源ノードと、前記第1電源ノードと前記第2電源ノードとの間に並列に接続された、第1の入力でオン・オフする第3のトランジスタ及び第2の入力でオン・オフする第4のトランジスタとを含み、前記第3及び第4のトランジスタの電流供給端子を前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタの前記駆動端子に駆動電力を供給する駆動電力供給手段と、

前記第2のトランジスタのオフからオンへの移行途中における、該第2のトランジスタの出力電圧が中間電位で略一定となるハーフ・オン状態を検出する駆動状態検出手段と、

前記第2のトランジスタをオフからオンにするときに、前記第1及び第2の入力を制御して前記第4のトランジスタよりも先に前記第3のトランジスタをオンにし、前記駆動状態検出手段で前記ハーフ・オン状態が検出されると前記第1及び第2の入力を制御して前記第3のトランジスタに加えて前記第4のトランジスタをオンにする駆動制御手段と、を備えることを特徴とするトランジスタ駆動装置。

【請求項2】

前記第4のトランジスタは、前記第3のトランジスタよりも電流供給能力の大きいトランジスタサイズであることを特徴とする請求項1に記載のトランジスタ駆動装置。

【請求項3】

前記駆動制御手段は、前記ハーフ・オン状態が検出されると前記第3のトランジスタに代えて前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御することを特徴とする請求項2に記載のトランジスタ駆動装置。

【請求項4】

前記第1及び第2のトランジスタは、電界効果トランジスタであり、前記第2のトランジスタの駆動端子はゲート端子であることを特徴とする請求項1乃至請求項3のいずれか1項に記載のトランジスタ駆動装置。

【請求項5】

前記駆動状態検出手段は、前記負荷を通って前記第2のトランジスタに流れる電流の電流レベルを検出する電流検出部と、前記電流検出部で検出した電流レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電流レベルとを比較する電流レベル比較部とを有し、前記電流検出部で検出される電流レベルが前記所定の電流レベルとなったときに、前記ハーフ・オン状態を検出することを特徴とする請求項1乃至請求項4のいずれか1項に記載のトランジスタ駆動装置。

【請求項6】

前記駆動状態検出手段は、前記第2のトランジスタの前記負荷との電気的な接続部の電圧レベルを検出する電圧検出部と、前記電圧検出部で検出される前記電圧レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電圧レベルとを比較する電圧レベル比較部とを有し、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなったときに、前記ハーフ・オン状態を検出することを特徴とする請求項1乃至請求項4のいずれか1項に記載のトランジスタ駆動装置。

【請求項7】

前記第2のトランジスタに駆動電流が供給されてからの経過時間を計測する時間計測手段と、

前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなるときの前記時間計測部の計測時間の情報を記録する時間記録手段とを更に備え、

前記駆動制御手段は、前記時間記録手段によって計測時間が記録されると、以降は、前記時間計測手段の計測時間が前記記録した計測時間になるタイミングで、前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御することを特徴とする請求項6に記載のトランジスタ駆動装置。

【請求項8】

前記ブリッジ回路は、ハイサイド側の一対の前記第1のトランジスタと、ローサイド側の一対の前記第2のトランジスタとから構成され、前記負荷への通電方向に応じて、対角に位置する第1のトランジスタ及び第2のトランジスタがオン又はオフされるHブリッジ型の回路であることを特徴とする請求項1乃至請求項7のいずれか1項に記載のトランジスタ駆動装置。

【請求項9】

前記駆動電力供給手段は、前記第3のトランジスタと前記第2電源ノードとの間に直列に接続された、第3の入力でオン・オフする第5のトランジスタと、前記第4のトランジスタと前記第2電源ノードとの間に直列に接続された、第4の入力でオン・オフする第6のトランジスタとを更に含み、前記第3及び第5のトランジスタの接続部と、前記第4及び第6のトランジスタの接続部とを前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタをオフにし且つ前記第5及び第6のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタから前記第2電源ノード側に電流を引き込む構成となっており、

前記駆動制御手段は、前記第2のトランジスタをオン状態からオフ状態にするときに、前記第3及び第4のトランジスタを両方ともオフ状態にし、前記第5及び第6のトランジスタを両方ともオン状態にするように前記第1〜第4の入力を制御することを特徴とする請求項1乃至請求項8のいずれか1項に記載のトランジスタ駆動装置。

【請求項1】

駆動対象である負荷に電気的に接続されるハイサイド側の第1のトランジスタとローサイド側の第2のトランジスタとを含み、前記第1及び第2のトランジスタをオン又はオフにすることで前記負荷が通電又は非通電の状態となるブリッジ回路の前記第2のトランジスタを駆動するトランジスタ駆動装置であって、

第1電源電位の供給される第1電源ノードと、前記第1電源電位よりも低電位の第2電源電位の供給される第2電源ノードと、前記第1電源ノードと前記第2電源ノードとの間に並列に接続された、第1の入力でオン・オフする第3のトランジスタ及び第2の入力でオン・オフする第4のトランジスタとを含み、前記第3及び第4のトランジスタの電流供給端子を前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタの前記駆動端子に駆動電力を供給する駆動電力供給手段と、

前記第2のトランジスタのオフからオンへの移行途中における、該第2のトランジスタの出力電圧が中間電位で略一定となるハーフ・オン状態を検出する駆動状態検出手段と、

前記第2のトランジスタをオフからオンにするときに、前記第1及び第2の入力を制御して前記第4のトランジスタよりも先に前記第3のトランジスタをオンにし、前記駆動状態検出手段で前記ハーフ・オン状態が検出されると前記第1及び第2の入力を制御して前記第3のトランジスタに加えて前記第4のトランジスタをオンにする駆動制御手段と、を備えることを特徴とするトランジスタ駆動装置。

【請求項2】

前記第4のトランジスタは、前記第3のトランジスタよりも電流供給能力の大きいトランジスタサイズであることを特徴とする請求項1に記載のトランジスタ駆動装置。

【請求項3】

前記駆動制御手段は、前記ハーフ・オン状態が検出されると前記第3のトランジスタに代えて前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御することを特徴とする請求項2に記載のトランジスタ駆動装置。

【請求項4】

前記第1及び第2のトランジスタは、電界効果トランジスタであり、前記第2のトランジスタの駆動端子はゲート端子であることを特徴とする請求項1乃至請求項3のいずれか1項に記載のトランジスタ駆動装置。

【請求項5】

前記駆動状態検出手段は、前記負荷を通って前記第2のトランジスタに流れる電流の電流レベルを検出する電流検出部と、前記電流検出部で検出した電流レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電流レベルとを比較する電流レベル比較部とを有し、前記電流検出部で検出される電流レベルが前記所定の電流レベルとなったときに、前記ハーフ・オン状態を検出することを特徴とする請求項1乃至請求項4のいずれか1項に記載のトランジスタ駆動装置。

【請求項6】

前記駆動状態検出手段は、前記第2のトランジスタの前記負荷との電気的な接続部の電圧レベルを検出する電圧検出部と、前記電圧検出部で検出される前記電圧レベルと前記第2のトランジスタが前記ハーフ・オン状態となるときの所定の電圧レベルとを比較する電圧レベル比較部とを有し、前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなったときに、前記ハーフ・オン状態を検出することを特徴とする請求項1乃至請求項4のいずれか1項に記載のトランジスタ駆動装置。

【請求項7】

前記第2のトランジスタに駆動電流が供給されてからの経過時間を計測する時間計測手段と、

前記電圧検出部で検出される電圧レベルが前記所定の電圧レベルとなるときの前記時間計測部の計測時間の情報を記録する時間記録手段とを更に備え、

前記駆動制御手段は、前記時間記録手段によって計測時間が記録されると、以降は、前記時間計測手段の計測時間が前記記録した計測時間になるタイミングで、前記第4のトランジスタをオンにするように前記第1及び第2の入力を制御することを特徴とする請求項6に記載のトランジスタ駆動装置。

【請求項8】

前記ブリッジ回路は、ハイサイド側の一対の前記第1のトランジスタと、ローサイド側の一対の前記第2のトランジスタとから構成され、前記負荷への通電方向に応じて、対角に位置する第1のトランジスタ及び第2のトランジスタがオン又はオフされるHブリッジ型の回路であることを特徴とする請求項1乃至請求項7のいずれか1項に記載のトランジスタ駆動装置。

【請求項9】

前記駆動電力供給手段は、前記第3のトランジスタと前記第2電源ノードとの間に直列に接続された、第3の入力でオン・オフする第5のトランジスタと、前記第4のトランジスタと前記第2電源ノードとの間に直列に接続された、第4の入力でオン・オフする第6のトランジスタとを更に含み、前記第3及び第5のトランジスタの接続部と、前記第4及び第6のトランジスタの接続部とを前記第2のトランジスタの駆動端子に電気的に接続して、前記第3及び第4のトランジスタをオフにし且つ前記第5及び第6のトランジスタの一方又は両方をオンにしたときに前記第2のトランジスタから前記第2電源ノード側に電流を引き込む構成となっており、

前記駆動制御手段は、前記第2のトランジスタをオン状態からオフ状態にするときに、前記第3及び第4のトランジスタを両方ともオフ状態にし、前記第5及び第6のトランジスタを両方ともオン状態にするように前記第1〜第4の入力を制御することを特徴とする請求項1乃至請求項8のいずれか1項に記載のトランジスタ駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2009−201256(P2009−201256A)

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願番号】特願2008−40359(P2008−40359)

【出願日】平成20年2月21日(2008.2.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願日】平成20年2月21日(2008.2.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]