トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に半導体デバイスに関し、より詳細には、改善された高周波性能を有する金属酸化物半導体(MOS)デバイスおよびそれを形成する方法に関する。

【背景技術】

【0002】

横拡散MOS(LDMOS)デバイスなどのMOSデバイスは、例えば無線通信システムの電力増幅器のような様々な用途で使用されている。LDMOSデバイスの直流(DC)性能に関して、低オン状態抵抗および高相互コンダクタンスを有することが一般に望ましい。低電圧(例えば、約10ボルト未満の破壊電圧)LDMOSデバイスのオン状態抵抗は、デバイスのチャネル領域の抵抗で主に支配される。例えば、低電圧LDMOSデバイスでは、デバイスの全オン状態抵抗の約80パーセントをチャネル抵抗が占めている。比較では、高電圧電力MOS電界効果トランジスタ(MOSFET)デバイスのオン状態抵抗は、デバイスのドリフト領域の抵抗で主に支配されている。

【0003】

低オン状態抵抗および/またはより高い電力処理能力を達成するためには、一般により広いチャネルが必要である。しかし、より広いチャネルを有するデバイスの形成は、デバイスの平面性のためにより大きなチップ面積を費やす。さらに、デバイスのP−N接合の周辺長の関数であるデバイスの出力キャパシタンスが、それに応じて、チャネル幅の関数として増加する。デバイスの出力キャパシタンスの増加は、LDMOSデバイスの高周波性能に望ましくない影響を及ぼす(例えば、約1ギガヘルツ(GHz)より上で)。

【0004】

「Folded Gate LDMOS Transistor with On−Resistanse and High Transconductance」という題目の、IEEE Transactions on Electron Devices、Vol.48、No.12、Dec.2001のYuanzheng Zhu et.al.による論文に記載されているように、折畳みゲートLDMOS構造を使用することによって、必ずしも大きな追加のチップ面積を費やすことなしに、LDMOSのチャネル幅を増やすことが知られている。この論文は、参照して本明細書に組み込む。しかし、LDMOSデバイスの折畳みゲート構成で、チップ面積を大きく増やすことなしに、オン状態抵抗の減少したデバイスを製作することができるが、この方法は、基本的に高周波性能を向上させるのにメリットがない。というのは、デバイスのP−N接合の周辺長は、したがって接合キャパシタンスは、チャネル領域が実質的に平面で形成されている場合と同じであるからである。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】Yuanzheng Zhu et.al.、「Folded Gate LDMOS Transistor with On−Resistanse and High Transconductance」、IEEE Transactions on Electron Devices、Vol.48、No.12、Dec.(2001)

【発明の概要】

【発明が解決しようとする課題】

【0006】

したがって、従来のMOSデバイスに一般に影響を及ぼす1つまたは複数の上述の欠陥の問題のない、改善された高周波性能およびオン状態特性を可能にするMOSデバイスが必要とされている。さらに、そのようなMOSデバイスが標準集積回路(IC)プロセス技術と完全に両立できることが望ましい。

【課題を解決するための手段】

【0007】

本発明は、デバイスの出力キャパシタンスを大きく増加させることなしに、MOSデバイスのオン状態抵抗を減少させる技術を提供し、それによって、デバイスの高周波性能およびDC性能を改善する。さらに、従来のCMOS適合プロセス技術を使用するICデバイス例えばLDMOSデバイスを、本発明の技術を使用して製造することができる。その結果として、ICデバイスを製造するコストは著しくは高くならない。

【0008】

本発明の一態様に従って、MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間で、半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

【0009】

特定のソース/ドレイン領域は、半導体層の上面に近接して半導体層中に形成された複数のトレンチを含むことができる。トレンチの間隔は、2つの隣り合うトレンチを隔離する壁が実質的に完全に第2の伝導型の材料で構成されるように整えられている。このようにして、MOSデバイスに関連した接合キャパシタンスは、トレンチの深さと実質的に無関係であり、代わりに特定のソース/ドレイン領域の直線幅の関数である。したがって、有利なことに、MOSデバイスのオン状態抵抗は、デバイスの接合キャパシタンスの大きな増加なしに、減少する。

【0010】

本発明の他の態様に従って、提供される金属酸化物半導体デバイスを形成する方法は、第1の伝導型の第1および第2のソース/ドレイン領域を第2の伝導型の半導体層中に形成する工程であって、第1および第2のソース/ドレイン領域が半導体層の上面に近接して形成され、かつ互いに間隔を開けて配置されている工程と、半導体層の上に半導体層から電気的に絶縁されているゲートを形成する工程であって、ゲートが少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に形成される工程と含む。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形成される。

【0011】

本発明のこれらおよび他の特徴および有利点は、本発明の例示の実施形態についての以下の詳細な説明から明らかになるであろう。この詳細な説明は、添付の図面に関連して読むべきである。

【図面の簡単な説明】

【0012】

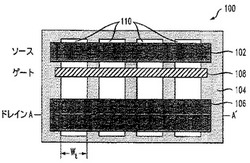

【図1】本発明の技術を実施することができる模範的なMOSデバイスの少なくとも一部を示す上面図である。

【図2】線A−A’に沿った図1に示すMOSデバイスの少なくとも一部を示す断面図である。

【図3】線A−A’に沿った図1に示すMOSデバイスの少なくとも一部を示す断面図であり、本発明の技術が実施されている。

【図4】本発明の他の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図5】本発明の第3の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図6】本発明の第4の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図7A】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7B】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7C】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7D】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8A】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8B】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8C】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【発明を実施するための形態】

【0013】

本発明は、DMOSトランジスタ並びに他のデバイスおよび/または回路を形成するのに適した例示のCMOS半導体製造技術の背景で、本明細書で説明する。しかし、理解すべきことであるが、本発明は、これまたは任意の特定のデバイスまたは回路の製造に限定されない。それどころか、本発明は、有利なことにデバイスで費やされるチップ面積の量を著しく増加させることなくデバイスの電気的性能(例えば、オン状態抵抗の減少)および高周波性能を改善する新規なトレンチ拡散配列を備えるMOSデバイスにもっと一般的に応用することができる。

【0014】

本発明の実施は、MOSデバイスおよび相補型金属酸化物半導体(CMOS)製造プロセスを特に参照して本明細書で説明するが、理解すべきことであるが、本発明の技術は、例えばバイポーラ接合トランジスタ(BJT)、縦型拡散MOS(DMOS)デバイス、延長ドレインMOS電界効果トランジスタ(MOSFET)デバイスなどのような、しかしこれらに限定されない他のデバイスの他の製造プロセス(例えば、バイポーラ)および/または形成に、修正してまたは修正なしに、同様に応用することができるが、そのことは、当業者は理解するであろう。さらに、本発明は、本明細書で、NチャネルMOSデバイスの背景で説明するが、当業者はよく分かっていることであるが、Nチャネルの実施形態で与えられた極性にただ単に反対の極性を代入することで、PチャネルMOSデバイスが形成されるだろうし、また本発明の技術および有利点は他の実施形態に同様に当てはまる。

【0015】

理解すべきことであるが、添付の図に示す様々な層および/または領域は一定の比率に応じて描かれていないことがあり、また、そのような集積回路構造で一般に使用される種類の1つまたは複数の半導体層および/領域は、説明を容易にするために、特定の図ではっきり示されていないことがある。このことは、はっきり示されていない半導体層および/または領域が実際の集積回路構造で省略されることを意味しない。

【0016】

図1および2は、それぞれ、本発明の技術を実施することができる模範的なMOSデバイス100の少なくとも一部の上面図および断面図を示す。MOSデバイス100は、好ましくは、基板112上に形成されたエピタキシャル層104を含む。基板112は、一般に、単結晶シリコンで形成されるが、ゲルマニウム、ガリウム砒素などのような、しかしこれらに限定されない代替え材料を使用することができる。その上、例えば拡散工程または打込み工程などによって、不純物すなわちドーパントを加えて材料の伝導性(例えば、N型またはP型)を変えることで、基板112を変えることができる。本発明の好ましい実施形態では、基板112は、「+」表示を付けて表されることが多い高濃度にドープされたP型伝導性であるので、P+基板と呼ぶことができる。P+基板112は、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を、例えば拡散工程または打込み工程などによって、基板材料に加えて形成することができる。好ましくは、知られている濃度レベルのP型不純物をエピタキシャル層104にドープして、望み通りに材料の伝導性を選択的に変える。もしくは、エピタキシャル層104は、例えば従来の拡散プロセスを使用して、P型拡散層として形成することができる。エピタキシャル層104のドーピング濃度は、好ましくは、基板112のドーピング濃度に比べて低い(例えば、1立方センチメートル当たり約1015から約1016原子)。

【0017】

本明細書で使用されることがあるような「半導体層」という用語は、他の材料をその上および/またはその中に形成できる任意の半導体材料のことを言う。半導体層は、基板112上に形成することができ、例えばエピタキシャル層104のような単一の層を備えることができる。または、半導体層は、異なる材料の複数の層および/または異なるドーピング濃度を有する同じ材料の複数の層を備えることができる。

【0018】

ソース領域102およびドレイン領域106は、それぞれ、エピタキシャル層の上面に近接してエピタキシャル層104中に形成され、互いに間隔を開けて配置されている。好ましくは、例えば打込みプロセスまたは拡散プロセスなどを使用して、知られている濃度レベルの不純物(例えば、燐、砒素、その他)をソースおよびドレイン領域102、106にドープして、望み通りに材料の伝導性を選択的に変える。好ましくは、ソースおよびドレイン領域102、106は、エピタキシャル層104の伝導型(conductivity type)と反対の関連した伝導型を有し、その結果、能動領域をデバイスに形成することができるようになる。本発明の好ましい実施形態では、ソースおよびドレイン領域102、106は、高濃度にドープされたN型伝導性であるので、N+ソースおよびドレイン領域と呼ぶことができる。N+ソースおよびドレイン領域102、106とP型エピタキシャル層104との間の境界は、本明細書でP−N接合と呼ぶことができる。

【0019】

理解すべきことであるが、簡単なMOSデバイスの場合、MOSデバイスは本質的に対称で、したがって双方向性であるので、MOSデバイスにおけるソースおよびドレインの表示は、基本的に任意である。したがって、ソースおよびドレイン領域は、一般的に、それぞれ第1および第2のソース/ドレイン領域と呼ぶことができる。ここで、この背景での「ソース/ドレイン」という用語は、ソース領域またはドレイン領域を示す。

【0020】

ゲート108は、エピタキシャル層104の上に形成され、少なくとも部分的にソース領域102とドレイン領域106との間に配置されている。ゲート108は、一般に、好ましくは酸化物(例えば、二酸化珪素)である絶縁層(図示しない)上に形成される。すなわち、ソースおよびドレイン領域102、106からゲートを電気的に絶縁するようにエピタキシャル層の少なくとも一部の上に形成される。ゲート108は、好ましくは、例えばポリシリコン材料のような導電性材料で形成されるが、適切な代替え材料(例えば、金属、その他)を同様に使用することができる。ゲート108の抵抗は、ゲートにシリサイド層(図示しない)を付けて減らすことができる。このことは、特定の高周波用途で使用するために特に有利であることがある。チャネル領域(図示しない)は、ゲートに加えられた正電位の作用によって集められた主に電子によって、ゲート108に近接したMOSデバイス100のボディ領域(図示しない)に形成される。図示しないが、低濃度ドープ・ドレイン(LDD)領域を、エピタキシャル層の上面に近接してエピタキシャル層104中に形成し、かつゲート108とドレイン領域106との間に配置することができる。

【0021】

MOSデバイス100の電気伝導を高め、それによってオン状態抵抗を減少させることが望ましい。MOSデバイスの伝導を高める1つの方法は、デバイスの有効チャネル幅Weffを増加させることである。これを達成するために、複数のトレンチ110をエピタキシャル層104に形成することができる。このトレンチの各々は、ソース領域102とドレイン領域106との間に水平に(例えば、基板112に対して実質的に平行な面で)延びている。図2を参照して、この図は、図1の線A−A’に沿った模範的なMOSデバイス100のドレイン領域106の少なくとも一部の断面図であり、トレンチ110の存在によって、大きな追加のチップ面積を費やすことなしに、デバイスの表面積が増加して、デバイスの有効幅が本質的に増加する。例えば、各トレンチ110の深さDをトレンチの幅Wtに実質的に等しくすることで、MOSデバイス100のチャネル領域の密度は効果的に2倍になり、相互コンダクタンスの向上およびオン状態抵抗の減少をもたらす。表面積を増加させるために同様な方法を使用するデバイスは、折畳みゲートLDMOSデバイスと呼ぶことができ、前に引用した「Folded Gate LDMOS Transistor with Low On−Resistance and High Transconductance」という題名のYuanzheng Zhu他による論文に記載されている。

【0022】

しかし、折畳みゲートLDMOS構造は、大きな追加のチップ面積を費やすことなしにオン状態抵抗を減少させる点で特定の利益をもたらすことができるが、この配列は、デバイスの高周波性能の改善に関して利益をもたらすことは実質的にない。これは、主に、デバイスのP−N接合の幅の関数であるデバイスの接合キャパシタンスCjが、MOSデバイスの実効幅に比例することのせいである。MOSデバイス100の接合キャパシタンスの減少は、トレンチ深さに無関係であるので、MOSデバイス100の接合キャパシタンスは、チャネル領域が実質的に平面で形成された場合(例えば、トレンチがない)と本質的に同じである。

【0023】

P−N接合の幅はN+ドレイン領域106の周辺長を合計して求めることができ、このN+ドレイン領域106は、チャネル領域の幅全体にわたってトレンチ110に沿ってP型エピタキシャル領域104と部分的に重なっている。留意されたいことであるが、図2に2次元断面として示すが、トレンチ110は、実際は、デバイスのソース領域102とドレイン領域106との間で3次元的に延びている。したがって、与えられたトレンチ110のキャパシタンスへの寄与は、トレンチのP−N接合の周辺長の関数であり、この周辺長は、トレンチ深さの約2倍にトレンチ幅をプラスしたものである(例えば、2D+Wt)。同様に、2つの隣り合うトレンチ110の間のドレイン領域106の各部分(本明細書でメサ114と呼ぶことができる)のキャパシタンスへの寄与は、メサのP−N接合の周辺長の関数であり、この周辺長は、この実施形態では、トレンチ深さの約2倍にメサの厚さTを加えたものである(例えば、2D+T)。

【0024】

図3は、本発明の技術が実施された模範的なMOSデバイス300の少なくとも一部の断面図である。MOSデバイス300は、追加のチップ面積を費やすことなく、かつデバイスの接合キャパシタンスを著しく増加させることなく、デバイスの電気伝導を有利に高めて、オン状態抵抗を減少させるように構成されている。したがって、接合キャパシタンスCjは、デバイスの実効チャネル幅Weffに比例しない。その結果、MOSデバイス300は、標準的なMOSデバイスと比較して向上した高周波性能を実現する。これを達成するために、模範的なMOSデバイス300は、少なくともデバイスの伝導を決定する目的のために、デバイスのP−N接合の幅よりも実質的に大きな実効幅Weffに形成される。

【0025】

図2に示すMOSデバイス100のように、模範的なMOSデバイス300は、P+基板302および基板上に形成されたP型エピタキシャル層304を備える。複数のトレンチ310をエピタキシャル層304に形成して、前に説明したようにデバイスの表面積を増加させる。例えば打込みプロセスおよび/または拡散プロセスなどを使用して、N+ドレイン領域306をエピタキシャル層に形成する。ドレイン領域306は、MOSデバイス300の上面に近接して形成されるので、トレンチ310に起因するデバイスの波形の上面外形に実質的に沿っている。MOSデバイス300のドレイン領域だけを図3に示したが、デバイスのソース領域を同様に形成することができることは理解すべきである。LDMOSデバイスの場合、ソース領域は一般に基板に電気的に接続されており、ソース領域のキャパシタンスへの寄与は一般に無視できる程度である。

【0026】

図2に示すMOSデバイス100の配列と違って、模範的なMOSデバイス300では、トレンチ310の間隔Sは、有利なことに、ドレイン領域306を形成した後で、隣り合うトレンチの各対の間のメサ308がN型伝導性を有する材料で実質的に完全に構成されるように形作られる。MOSデバイス300の実効幅Weffは、デバイスのトレンチ310の深さおよび数の関数として決定される。メサ308には実質的にP−N接合が形成されていないので、デバイスの全体的な出力キャパシタンスに対するメサの接合キャパシタンスの寄与は、実質的にゼロになる。このように、少なくとも接合キャパシタンスを決定する目的のために、ドレイン領域のP−N接合の幅は、少なくとも部分的に、ドレイン領域の全体にわたってP−N接合の直線幅WLINにトレンチ深さの2倍を加えたもの(WLIN+2D)に基づいている。

【0027】

一般に、P−N接合の直線幅はトレンチ深さよりも実質的に長いので、メサ308に起因する接合キャパシタンスはトレンチ深さに本質的に無関係である。本発明の好ましい実施形態では、約1マイクロメートル(μm)から約50μmまでのトレンチ深さを使用することができ、MOSデバイス300の電気伝導はトレンチ深さの関数として高くなる。図3に示す模範的なMOSデバイス300では、デバイスの実効幅Weffに比例したP−N接合キャパシタンスCjの減少が、少なくとも部分的に次式に基づいて達成される。

Cj∝Weff−2nD

ここで、nは使用されるトレンチの数であり、Dはトレンチの深さである。上の式から理解できるように、特定の実効幅Weffに関して、デバイスの接合キャパシタンスCjは、トレンチの深さの増加のみならず、デバイスで使用されるトレンチの数の増加とともに減少する。

【0028】

好ましい実施形態では、MOSデバイス300のドレイン領域306の断面厚さは約0.3μmである。ドレイン領域306を形成するために使用されるN型不純物は、2つの隣り合うトレンチ310の側壁から各メサ308の中に拡散するので、約0.6μm以下のトレンチ間隔では、メサ中のP型エピタキシャル材料の実質的にすべてがN+ドレイン領域で確実に費やされるようになる。理解すべきことであるが、MOSデバイス300はトレンチ310の特定の間隔に限定されない。例えばMOSデバイス300のドレイン領域306の断面厚さを大きくして、0.6μmよりも大きなトレンチ間隔を使用することができる。

【0029】

図4は、本発明の他の実施形態に従って形成された模範的なMOSデバイス400の少なくとも一部を示す断面図である。図は、主に、MOSデバイス400のドレイン領域を示している。図3に示すMOSデバイス300と同じように、模範的なMOSデバイス400は、デバイスの実効幅WeffがデバイスのP−N接合の幅よりも実質的に大きくなるように形作られ、それによって、大きな追加のチップ面積を費やすことなく、かつデバイスの接合キャパシタンスを増加させることなく、デバイスのオン状態抵抗の有利な減少を実現している。

【0030】

模範的なMOSデバイス400は、P+基板402上に形成されたP型エピタキシャル層404を含む。エピタキシャル層の上面に近接してエピタキシャル層404中に、複数のトレンチ410が形成される。隣り合う2つのトレンチ410の間のエピタキシャル領域を、本明細書でメサ412と呼ぶ。メサ412の中心部分は、好ましくは、例えば酸化物(例えば、二酸化珪素)のような絶縁材料408を備える。絶縁材料408は、好ましくは、エピタキシャル層404中のトレンチ410の深さ(例えば、約1μmから約50μm)に実質的に等しい深さで形成される。

【0031】

例えば打込みプロセスおよび/または拡散プロセスなどを使用して、N+ドレイン領域406をエピタキシャル層404中に形成する。図から明らかなように、ドレイン領域406は、好ましくは、エピタキシャル層404の上面に近接して形成されるので、トレンチ410に起因するエピタキシャル層の上面の波形の外形に沿っている。しかし、MOSデバイス400では、ドレイン領域406は連続した領域として形成されないで、代わりに別個のセグメントとして形成され、そのドレイン領域セグメントはメサ412に形成された絶縁材料408で互いに分離されている。ドレイン領域セグメント406は、主にトレンチ410の側壁および底壁に限定されているので、対応するトレンチ410の形になる。MOSデバイス400のドレイン領域406の断面だけを図4に示したが、理解すべきことであるが、本明細書で説明する本発明の技術はデバイスのソース領域を形成する際に同様に使用することができる。

【0032】

MOSデバイス400のチャネル領域の実効幅Weffは、デバイスのドレイン領域セグメント406すべての周辺長の和として決定することができる。この周辺長の和は、与えられたトレンチの場合、トレンチの深さDの2倍にトレンチの幅Wを加えたもの(すなわち、2D+W)の関数である。MOSデバイス400の接合キャパシタンスを決定する際に、デバイスのP−N接合の幅は、本質的に、トレンチの幅の関数だけである。というのは、絶縁材料408が存在するためにメサ412にP−N接合が形成されないからである。したがって、図3に示すMOSデバイス300と同じように、MOSデバイス400は、チャネル領域の実効幅がデバイスのドレイン領域のP−N接合の幅よりも実質的に大きくなるように形作られる。

【0033】

図5は、本発明の第3の実施形態に従って形成された模範的なMOSデバイス500の少なくとも一部を示す断面図である。この図では、MOSデバイス500のドレイン領域506の断面を主に示す。MOSデバイス500は、好ましくは、P+基板502上に形成されたP型エピタキシャル層504を含む。図3に示すMOSデバイス300と同様に、MOSデバイス500は、エピタキシャル層の上面に近接してエピタキシャル層504中に形成された複数のトレンチ510を含む。図3のMOSデバイス300のトレンチ310と比較して、MOSデバイス500のトレンチ510は、好ましくは、下を切り取られた側壁514を有して形成されるので、その結果、与えられたトレンチの底壁がトレンチの上の開口よりも広くなっている。下を切り取られた側壁は、例えば、異方性エッチング・プロセスを使用して形成することができる。このようにして、所望の傾斜(例えば、正および/または負の傾斜)の側壁を有するトレンチ510を形成することができる。

【0034】

好ましくは、ドレイン領域がエピタキシャル層504中に形成された後で、2つの隣り合うトレンチの底壁に近接したドレイン領域の部分が互いに実質的に合体して、トレンチの底壁を横切って実質的に連続した水平なP−N接合を形成するように、N+ドレイン領域506の厚さと共に、2つの隣り合うトレンチ510の間隔が形作られる。したがって、隣り合うトレンチの間に形成されたメサ512は、P型コア材料508をエピタキシャル層504から電気的に絶縁するようにN+ドレイン領域506で実質的に囲まれたP型エピタキシャル材料の中心コア508を備える。

【0035】

MOSデバイス500のチャネル領域の実効幅Weffは、デバイスのドレイン領域506に関連したすべてのセグメントの和として決定することができ、このセグメントの和は、与えられたトレンチでは、トレンチの深さDの約2倍よりも僅かに大きいもの(例えば、傾斜した側壁514の角度に基づいている)にトレンチの幅Wを加えたものの関数である。MOSデバイス500の接合キャパシタンスを決定する際に、デバイスのP−N接合の幅は、本質的に、P−N接合の直線幅WLINの関数に過ぎない。というのは、少なくとも部分的に、メサのP型材料508を基本的にピンチ・オフするドレイン領域506が存在するために、メサ512に形成された能動的なP−N接合はないからである。特にデバイスの全接合キャパシタンスに比べると、メサ512に起因する接合キャパシタンスは、基本的にゼロになる。したがって、図3および4に示すそれぞれMOSデバイス300および400と同じように、MOSデバイス500のチャネル領域の実効幅は、デバイスのP−N接合の幅よりも実質的に大きい。

【0036】

図6は、本発明の第4の実施形態に従って形成された模範的なMOSデバイス600の少なくとも一部を示す断面図である。この図は、主に、MOSデバイス600のドレイン領域606を示している。図3〜5に関連して前に説明した例示のMOSデバイス実施形態と同じように、模範的なMOSデバイス600は、有利なことに、デバイスのチャネル領域の実効幅WeffがデバイスのP−N接合の幅よりも実質的に大きくなるように形作られる。このために、MOSデバイス600の電気伝導性を有利に高めることができるようになり、それによって、デバイスの接合キャパシタンスの大きな増加なしに、オン状態抵抗を減少させる。

【0037】

MOSデバイス600は、好ましくは、P+基板602上に形成されたP型エピタキシャル層604を含む。エピタキシャル層の上面に近接してエピタキシャル層604中に、複数のトレンチ610が形成されている。隣り合うトレンチ610の間に形成されたメサ612は、好ましくは、例えば打込みプロセスおよび/または拡散プロセスなどを使用して、知られている濃度レベル(例えば、1立方センチメートル当たり約1014原子から約1015原子)の低濃度ドープN型材料608(例えば、砒素または燐)で実質的に構成されている。それから、もっと高濃度ドープのN+ドレイン領域606(例えば、1立方センチメートル当たり約1015原子から約1016原子)がエピタキシャル層604の上面に近接して形成され、それでトレンチ610に起因するエピタキシャル層の上面の波形の外形に実質的に沿っている。波形ドレイン領域606の配列によって、前に説明したように、MOSデバイス600のチャネル領域の実効幅が増加する。

【0038】

MOSデバイス600の実効幅は、デバイスのドレイン領域606の全周辺長の和に基づいて決定され、この全周辺長は、トレンチ610の深さD、トレンチの幅W、およびメサ612の厚さTの関数である。他方で、デバイスのP−N接合の幅は、P型エピタキシャル層604と各トレンチの底壁に近接したN+ドレイン領域606との間の接合の周辺長の関数として主に決定することができ、実質的にトレンチ深さに無関係である。P−N接合は、また、エピタキシャル層604とメサの低濃度ドープN型材料608との間にも形成される。しかし、N型材料608のドーピング濃度はN+ドレイン領域606のドーピング濃度よりも相当に低いので、メサ612に関連したP−N接合に起因する接合キャパシタンスは実質的により小さくなる。図3〜5に図示した模範的なMOSデバイス実施形態と同じように、ソース領域(図示しない)は、ドレイン領域606の形成に似たやり方でMOSデバイス600に形成することができる。

【0039】

一般性を失うことなく、デバイスのP−N接合の幅よりも実質的に大きな実効幅を有するように形作られたMOSデバイスを形成するための様々な例示の実施形態を、本明細書で説明しまた図示した。本発明の技術および有利点は、他のデバイスを形成するように容易に展開することができるが、このことは、当業者には明らかになるであろう。

【0040】

図7A〜7Dは、本発明の一実施形態に従って、図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す。例示の方法は、従来のCMOS適合半導体製造プロセス技術の背景で説明する。理解すべきことであるが、本発明は、本デバイスを製造するためのこの方法または任意の特定の方法に限定されない。前に述べたように図に示す様々な層および/または領域は、一定の比率に応じて描かれていないことがあり、また、説明を容易にするためにある特定の半導体層は省略されていることがある。

【0041】

図7Aを参照して、本発明の技術を実施することができる模範的な半導体ウェハ700の少なくとも一部を示す。ウェハ700は、好ましくは、基板702を備える。基板702は、好ましくは、高伝導性を有するP+型基板であるが、代わりにN+型基板を使用することができる。当業者は理解するように、P+基板は、例えば拡散工程または打込み工程などによって、基板材料に所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を基板材料に加えて、望み通りに材料の伝導性を変えることによって、形成することができる。それから、エピタキシャル層704を、好ましくは、ウェハ700の全表面にわたって成長させる。エピタキシャル層704は、また、P型不純物を加えて変えることもできる。

【0042】

例えばウェハ700の上面に対応するトレンチを画定する開口を作るなどによって、エピタキシャル層704に第1の複数のトレンチ706を形成することができる。ウェハ700の上面にフォトレジストの層(図示しない)を堆積し、さらに従来のフォトリソグラフィ・パターン形成工程、それに続いてウェハの不要部分を除去するエッチング工程を使用して、開口を形成することができる。トレンチ706は、好ましくは、(例えば、反応性イオン・エッチング(RIE)、ドライ・エッチング、その他を使用して)エピタキシャル層704中に所望の深さで形成する。それから、図7Bに示すように、例えば従来のトレンチ充填プロセスを使用して、トレンチ706に酸化物(例えば、二酸化珪素)のような絶縁材料を充填して、充填酸化物領域708を形成する。充填酸化物領域708は、好ましくは、エピタキシャル層704の上面と実質的に平面であるように形成する。

【0043】

図7Cを参照して、次に、エピタキシャル層の上面に近接してエピタキシャル層704中に第2の複数のトレンチ710を形成する。第2の複数のトレンチ710は、好ましくは、充填酸化物領域708で互いに分離され、各充填酸化物領域が好ましくは2つの隣り合うトレンチ710の間に配置されている。その後、図7Dに示すように、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のN型不純物すなわちドーパント712(例えば、燐または砒素)をエピタキシャル層に加えて、トレンチ710の側壁および底壁に近接したエピタキシャル層704中に、ドレイン領域714を形成する。ドレイン領域714は、例えば打込み工程または拡散工程を使用して形成して、望み通りに材料の伝導性を変えることができる。

【0044】

図8A〜8Cは、本発明の他の実施形態に従って、図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す。例示の方法は、従来CMOS適合半導体製造プロセス技術の背景で説明する。理解すべきことであるが、本発明はデバイスを製造するこの方法または任意の特定の方法に限定されない。

【0045】

図8Aを参照して、本発明の技術を実施することができる模範的な半導体ウェハ800の少なくとも一部を示す。ウェハ800は、好ましくは、基板802を備える。基板802は、好ましくは、高伝導性を有するP+型基板であるが、N+型基板を代わりに使用することができる。当業者は理解するように、P+基板は、例えば拡散工程または打込み工程などによって、基板材料に所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を基板材料に加えて、望み通りに材料の伝導性を変えることによって、形成することができる。それから、エピタキシャル層804を、好ましくは、ウェハ800の全表面にわたって成長させる。エピタキシャル層804は、また、P型不純物を加えて変えることもできるが、好ましくは基板802よりも低濃度である。低濃度ドープN型層806は、好ましくは、例えば打込みプロセスまたは拡散プロセスなどを使用して望み通りにエピタキシャル材料の伝導性を変えることによって、エピタキシャル層804の少なくとも一部に形成する。

【0046】

図8Bに示すように、例えばウェハ800の上面に対応するトレンチを画定する開口を作るなどによって、低濃度ドープN型層806に複数のトレンチ808を形成する。ウェハ800の上面にフォトレジストの層(図示しない)を堆積し、さらに従来のフォトリソグラフィ・パターン形成工程、それに続いてウェハの不要部分を除去するエッチング工程を使用して、開口を形成することができる。トレンチ808は、好ましくは、(例えば、反応性イオン・エッチング(RIE)、ドライ・エッチング、その他を使用して)低濃度ドープN型層806中に所望の深さで形成する。トレンチ808を形成するとき、エピタキシャル層804をエッチング停止として使用することができ、それによって、トレンチの底壁を通じてエピタキシャル層の少なくとも一部を露出させる。ただし、エピタキシャルを露出させる必要はない。

【0047】

図8Cを参照して、その後、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のN型不純物すなわちドーパント812(例えば、燐または砒素)をN型層に加えて、低濃度ドープN型層806にドレイン領域810を形成する。ドレイン領域810は、好ましくは、ウェハ800の上面に近接して形成されるので、トレンチ808に起因する実質的に波形の外形になる。ドレイン領域810は、例えば打込み工程または拡散工程を使用して形成して、望み通りに材料の伝導性を変えることができる。ドレイン領域810の断面厚さthは、好ましくは、約0.3μmであるが、ドレイン領域はどんな特定の寸法および/または形状にも限定されない。

【0048】

本発明のMOSデバイスは、少なくとも部分的に集積回路中に実現することができる。集積回路の形成において、複数の同一チップは、一般に、半導体ウェハの表面にパターンを繰り返して製造される。各チップは本明細書で説明したデバイスを含み、さらに他の構造または回路を含むことができる。個々のチップをウェハから切断しすなわちダイシングし、そして集積回路としてパッケージする。当業者は、ウェハをダイシングし、チップをパッケージして集積回路をつくる方法を知っているだろう。そのように製造された集積回路は、この発明の一部と考えられる。

【0049】

本発明の例示の実施形態は本明細書で添付の図面を参照して説明したが、理解すべきことであるが、本発明はまさにその実施形態に限定されることなく、また当業者は添付の特許請求の範囲の範囲から逸脱することなく、その実施形態に様々な他の変更および修正を加えることができる。

【技術分野】

【0001】

本発明は、一般的に半導体デバイスに関し、より詳細には、改善された高周波性能を有する金属酸化物半導体(MOS)デバイスおよびそれを形成する方法に関する。

【背景技術】

【0002】

横拡散MOS(LDMOS)デバイスなどのMOSデバイスは、例えば無線通信システムの電力増幅器のような様々な用途で使用されている。LDMOSデバイスの直流(DC)性能に関して、低オン状態抵抗および高相互コンダクタンスを有することが一般に望ましい。低電圧(例えば、約10ボルト未満の破壊電圧)LDMOSデバイスのオン状態抵抗は、デバイスのチャネル領域の抵抗で主に支配される。例えば、低電圧LDMOSデバイスでは、デバイスの全オン状態抵抗の約80パーセントをチャネル抵抗が占めている。比較では、高電圧電力MOS電界効果トランジスタ(MOSFET)デバイスのオン状態抵抗は、デバイスのドリフト領域の抵抗で主に支配されている。

【0003】

低オン状態抵抗および/またはより高い電力処理能力を達成するためには、一般により広いチャネルが必要である。しかし、より広いチャネルを有するデバイスの形成は、デバイスの平面性のためにより大きなチップ面積を費やす。さらに、デバイスのP−N接合の周辺長の関数であるデバイスの出力キャパシタンスが、それに応じて、チャネル幅の関数として増加する。デバイスの出力キャパシタンスの増加は、LDMOSデバイスの高周波性能に望ましくない影響を及ぼす(例えば、約1ギガヘルツ(GHz)より上で)。

【0004】

「Folded Gate LDMOS Transistor with On−Resistanse and High Transconductance」という題目の、IEEE Transactions on Electron Devices、Vol.48、No.12、Dec.2001のYuanzheng Zhu et.al.による論文に記載されているように、折畳みゲートLDMOS構造を使用することによって、必ずしも大きな追加のチップ面積を費やすことなしに、LDMOSのチャネル幅を増やすことが知られている。この論文は、参照して本明細書に組み込む。しかし、LDMOSデバイスの折畳みゲート構成で、チップ面積を大きく増やすことなしに、オン状態抵抗の減少したデバイスを製作することができるが、この方法は、基本的に高周波性能を向上させるのにメリットがない。というのは、デバイスのP−N接合の周辺長は、したがって接合キャパシタンスは、チャネル領域が実質的に平面で形成されている場合と同じであるからである。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】Yuanzheng Zhu et.al.、「Folded Gate LDMOS Transistor with On−Resistanse and High Transconductance」、IEEE Transactions on Electron Devices、Vol.48、No.12、Dec.(2001)

【発明の概要】

【発明が解決しようとする課題】

【0006】

したがって、従来のMOSデバイスに一般に影響を及ぼす1つまたは複数の上述の欠陥の問題のない、改善された高周波性能およびオン状態特性を可能にするMOSデバイスが必要とされている。さらに、そのようなMOSデバイスが標準集積回路(IC)プロセス技術と完全に両立できることが望ましい。

【課題を解決するための手段】

【0007】

本発明は、デバイスの出力キャパシタンスを大きく増加させることなしに、MOSデバイスのオン状態抵抗を減少させる技術を提供し、それによって、デバイスの高周波性能およびDC性能を改善する。さらに、従来のCMOS適合プロセス技術を使用するICデバイス例えばLDMOSデバイスを、本発明の技術を使用して製造することができる。その結果として、ICデバイスを製造するコストは著しくは高くならない。

【0008】

本発明の一態様に従って、MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間で、半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

【0009】

特定のソース/ドレイン領域は、半導体層の上面に近接して半導体層中に形成された複数のトレンチを含むことができる。トレンチの間隔は、2つの隣り合うトレンチを隔離する壁が実質的に完全に第2の伝導型の材料で構成されるように整えられている。このようにして、MOSデバイスに関連した接合キャパシタンスは、トレンチの深さと実質的に無関係であり、代わりに特定のソース/ドレイン領域の直線幅の関数である。したがって、有利なことに、MOSデバイスのオン状態抵抗は、デバイスの接合キャパシタンスの大きな増加なしに、減少する。

【0010】

本発明の他の態様に従って、提供される金属酸化物半導体デバイスを形成する方法は、第1の伝導型の第1および第2のソース/ドレイン領域を第2の伝導型の半導体層中に形成する工程であって、第1および第2のソース/ドレイン領域が半導体層の上面に近接して形成され、かつ互いに間隔を開けて配置されている工程と、半導体層の上に半導体層から電気的に絶縁されているゲートを形成する工程であって、ゲートが少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間に形成される工程と含む。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形成される。

【0011】

本発明のこれらおよび他の特徴および有利点は、本発明の例示の実施形態についての以下の詳細な説明から明らかになるであろう。この詳細な説明は、添付の図面に関連して読むべきである。

【図面の簡単な説明】

【0012】

【図1】本発明の技術を実施することができる模範的なMOSデバイスの少なくとも一部を示す上面図である。

【図2】線A−A’に沿った図1に示すMOSデバイスの少なくとも一部を示す断面図である。

【図3】線A−A’に沿った図1に示すMOSデバイスの少なくとも一部を示す断面図であり、本発明の技術が実施されている。

【図4】本発明の他の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図5】本発明の第3の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図6】本発明の第4の実施形態に従って形成された模範的なMOSデバイスの少なくとも一部を示す断面図である。

【図7A】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7B】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7C】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図7D】本発明の一実施形態に従って図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8A】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8B】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【図8C】本発明の他の実施形態に従って図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す図である。

【発明を実施するための形態】

【0013】

本発明は、DMOSトランジスタ並びに他のデバイスおよび/または回路を形成するのに適した例示のCMOS半導体製造技術の背景で、本明細書で説明する。しかし、理解すべきことであるが、本発明は、これまたは任意の特定のデバイスまたは回路の製造に限定されない。それどころか、本発明は、有利なことにデバイスで費やされるチップ面積の量を著しく増加させることなくデバイスの電気的性能(例えば、オン状態抵抗の減少)および高周波性能を改善する新規なトレンチ拡散配列を備えるMOSデバイスにもっと一般的に応用することができる。

【0014】

本発明の実施は、MOSデバイスおよび相補型金属酸化物半導体(CMOS)製造プロセスを特に参照して本明細書で説明するが、理解すべきことであるが、本発明の技術は、例えばバイポーラ接合トランジスタ(BJT)、縦型拡散MOS(DMOS)デバイス、延長ドレインMOS電界効果トランジスタ(MOSFET)デバイスなどのような、しかしこれらに限定されない他のデバイスの他の製造プロセス(例えば、バイポーラ)および/または形成に、修正してまたは修正なしに、同様に応用することができるが、そのことは、当業者は理解するであろう。さらに、本発明は、本明細書で、NチャネルMOSデバイスの背景で説明するが、当業者はよく分かっていることであるが、Nチャネルの実施形態で与えられた極性にただ単に反対の極性を代入することで、PチャネルMOSデバイスが形成されるだろうし、また本発明の技術および有利点は他の実施形態に同様に当てはまる。

【0015】

理解すべきことであるが、添付の図に示す様々な層および/または領域は一定の比率に応じて描かれていないことがあり、また、そのような集積回路構造で一般に使用される種類の1つまたは複数の半導体層および/領域は、説明を容易にするために、特定の図ではっきり示されていないことがある。このことは、はっきり示されていない半導体層および/または領域が実際の集積回路構造で省略されることを意味しない。

【0016】

図1および2は、それぞれ、本発明の技術を実施することができる模範的なMOSデバイス100の少なくとも一部の上面図および断面図を示す。MOSデバイス100は、好ましくは、基板112上に形成されたエピタキシャル層104を含む。基板112は、一般に、単結晶シリコンで形成されるが、ゲルマニウム、ガリウム砒素などのような、しかしこれらに限定されない代替え材料を使用することができる。その上、例えば拡散工程または打込み工程などによって、不純物すなわちドーパントを加えて材料の伝導性(例えば、N型またはP型)を変えることで、基板112を変えることができる。本発明の好ましい実施形態では、基板112は、「+」表示を付けて表されることが多い高濃度にドープされたP型伝導性であるので、P+基板と呼ぶことができる。P+基板112は、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を、例えば拡散工程または打込み工程などによって、基板材料に加えて形成することができる。好ましくは、知られている濃度レベルのP型不純物をエピタキシャル層104にドープして、望み通りに材料の伝導性を選択的に変える。もしくは、エピタキシャル層104は、例えば従来の拡散プロセスを使用して、P型拡散層として形成することができる。エピタキシャル層104のドーピング濃度は、好ましくは、基板112のドーピング濃度に比べて低い(例えば、1立方センチメートル当たり約1015から約1016原子)。

【0017】

本明細書で使用されることがあるような「半導体層」という用語は、他の材料をその上および/またはその中に形成できる任意の半導体材料のことを言う。半導体層は、基板112上に形成することができ、例えばエピタキシャル層104のような単一の層を備えることができる。または、半導体層は、異なる材料の複数の層および/または異なるドーピング濃度を有する同じ材料の複数の層を備えることができる。

【0018】

ソース領域102およびドレイン領域106は、それぞれ、エピタキシャル層の上面に近接してエピタキシャル層104中に形成され、互いに間隔を開けて配置されている。好ましくは、例えば打込みプロセスまたは拡散プロセスなどを使用して、知られている濃度レベルの不純物(例えば、燐、砒素、その他)をソースおよびドレイン領域102、106にドープして、望み通りに材料の伝導性を選択的に変える。好ましくは、ソースおよびドレイン領域102、106は、エピタキシャル層104の伝導型(conductivity type)と反対の関連した伝導型を有し、その結果、能動領域をデバイスに形成することができるようになる。本発明の好ましい実施形態では、ソースおよびドレイン領域102、106は、高濃度にドープされたN型伝導性であるので、N+ソースおよびドレイン領域と呼ぶことができる。N+ソースおよびドレイン領域102、106とP型エピタキシャル層104との間の境界は、本明細書でP−N接合と呼ぶことができる。

【0019】

理解すべきことであるが、簡単なMOSデバイスの場合、MOSデバイスは本質的に対称で、したがって双方向性であるので、MOSデバイスにおけるソースおよびドレインの表示は、基本的に任意である。したがって、ソースおよびドレイン領域は、一般的に、それぞれ第1および第2のソース/ドレイン領域と呼ぶことができる。ここで、この背景での「ソース/ドレイン」という用語は、ソース領域またはドレイン領域を示す。

【0020】

ゲート108は、エピタキシャル層104の上に形成され、少なくとも部分的にソース領域102とドレイン領域106との間に配置されている。ゲート108は、一般に、好ましくは酸化物(例えば、二酸化珪素)である絶縁層(図示しない)上に形成される。すなわち、ソースおよびドレイン領域102、106からゲートを電気的に絶縁するようにエピタキシャル層の少なくとも一部の上に形成される。ゲート108は、好ましくは、例えばポリシリコン材料のような導電性材料で形成されるが、適切な代替え材料(例えば、金属、その他)を同様に使用することができる。ゲート108の抵抗は、ゲートにシリサイド層(図示しない)を付けて減らすことができる。このことは、特定の高周波用途で使用するために特に有利であることがある。チャネル領域(図示しない)は、ゲートに加えられた正電位の作用によって集められた主に電子によって、ゲート108に近接したMOSデバイス100のボディ領域(図示しない)に形成される。図示しないが、低濃度ドープ・ドレイン(LDD)領域を、エピタキシャル層の上面に近接してエピタキシャル層104中に形成し、かつゲート108とドレイン領域106との間に配置することができる。

【0021】

MOSデバイス100の電気伝導を高め、それによってオン状態抵抗を減少させることが望ましい。MOSデバイスの伝導を高める1つの方法は、デバイスの有効チャネル幅Weffを増加させることである。これを達成するために、複数のトレンチ110をエピタキシャル層104に形成することができる。このトレンチの各々は、ソース領域102とドレイン領域106との間に水平に(例えば、基板112に対して実質的に平行な面で)延びている。図2を参照して、この図は、図1の線A−A’に沿った模範的なMOSデバイス100のドレイン領域106の少なくとも一部の断面図であり、トレンチ110の存在によって、大きな追加のチップ面積を費やすことなしに、デバイスの表面積が増加して、デバイスの有効幅が本質的に増加する。例えば、各トレンチ110の深さDをトレンチの幅Wtに実質的に等しくすることで、MOSデバイス100のチャネル領域の密度は効果的に2倍になり、相互コンダクタンスの向上およびオン状態抵抗の減少をもたらす。表面積を増加させるために同様な方法を使用するデバイスは、折畳みゲートLDMOSデバイスと呼ぶことができ、前に引用した「Folded Gate LDMOS Transistor with Low On−Resistance and High Transconductance」という題名のYuanzheng Zhu他による論文に記載されている。

【0022】

しかし、折畳みゲートLDMOS構造は、大きな追加のチップ面積を費やすことなしにオン状態抵抗を減少させる点で特定の利益をもたらすことができるが、この配列は、デバイスの高周波性能の改善に関して利益をもたらすことは実質的にない。これは、主に、デバイスのP−N接合の幅の関数であるデバイスの接合キャパシタンスCjが、MOSデバイスの実効幅に比例することのせいである。MOSデバイス100の接合キャパシタンスの減少は、トレンチ深さに無関係であるので、MOSデバイス100の接合キャパシタンスは、チャネル領域が実質的に平面で形成された場合(例えば、トレンチがない)と本質的に同じである。

【0023】

P−N接合の幅はN+ドレイン領域106の周辺長を合計して求めることができ、このN+ドレイン領域106は、チャネル領域の幅全体にわたってトレンチ110に沿ってP型エピタキシャル領域104と部分的に重なっている。留意されたいことであるが、図2に2次元断面として示すが、トレンチ110は、実際は、デバイスのソース領域102とドレイン領域106との間で3次元的に延びている。したがって、与えられたトレンチ110のキャパシタンスへの寄与は、トレンチのP−N接合の周辺長の関数であり、この周辺長は、トレンチ深さの約2倍にトレンチ幅をプラスしたものである(例えば、2D+Wt)。同様に、2つの隣り合うトレンチ110の間のドレイン領域106の各部分(本明細書でメサ114と呼ぶことができる)のキャパシタンスへの寄与は、メサのP−N接合の周辺長の関数であり、この周辺長は、この実施形態では、トレンチ深さの約2倍にメサの厚さTを加えたものである(例えば、2D+T)。

【0024】

図3は、本発明の技術が実施された模範的なMOSデバイス300の少なくとも一部の断面図である。MOSデバイス300は、追加のチップ面積を費やすことなく、かつデバイスの接合キャパシタンスを著しく増加させることなく、デバイスの電気伝導を有利に高めて、オン状態抵抗を減少させるように構成されている。したがって、接合キャパシタンスCjは、デバイスの実効チャネル幅Weffに比例しない。その結果、MOSデバイス300は、標準的なMOSデバイスと比較して向上した高周波性能を実現する。これを達成するために、模範的なMOSデバイス300は、少なくともデバイスの伝導を決定する目的のために、デバイスのP−N接合の幅よりも実質的に大きな実効幅Weffに形成される。

【0025】

図2に示すMOSデバイス100のように、模範的なMOSデバイス300は、P+基板302および基板上に形成されたP型エピタキシャル層304を備える。複数のトレンチ310をエピタキシャル層304に形成して、前に説明したようにデバイスの表面積を増加させる。例えば打込みプロセスおよび/または拡散プロセスなどを使用して、N+ドレイン領域306をエピタキシャル層に形成する。ドレイン領域306は、MOSデバイス300の上面に近接して形成されるので、トレンチ310に起因するデバイスの波形の上面外形に実質的に沿っている。MOSデバイス300のドレイン領域だけを図3に示したが、デバイスのソース領域を同様に形成することができることは理解すべきである。LDMOSデバイスの場合、ソース領域は一般に基板に電気的に接続されており、ソース領域のキャパシタンスへの寄与は一般に無視できる程度である。

【0026】

図2に示すMOSデバイス100の配列と違って、模範的なMOSデバイス300では、トレンチ310の間隔Sは、有利なことに、ドレイン領域306を形成した後で、隣り合うトレンチの各対の間のメサ308がN型伝導性を有する材料で実質的に完全に構成されるように形作られる。MOSデバイス300の実効幅Weffは、デバイスのトレンチ310の深さおよび数の関数として決定される。メサ308には実質的にP−N接合が形成されていないので、デバイスの全体的な出力キャパシタンスに対するメサの接合キャパシタンスの寄与は、実質的にゼロになる。このように、少なくとも接合キャパシタンスを決定する目的のために、ドレイン領域のP−N接合の幅は、少なくとも部分的に、ドレイン領域の全体にわたってP−N接合の直線幅WLINにトレンチ深さの2倍を加えたもの(WLIN+2D)に基づいている。

【0027】

一般に、P−N接合の直線幅はトレンチ深さよりも実質的に長いので、メサ308に起因する接合キャパシタンスはトレンチ深さに本質的に無関係である。本発明の好ましい実施形態では、約1マイクロメートル(μm)から約50μmまでのトレンチ深さを使用することができ、MOSデバイス300の電気伝導はトレンチ深さの関数として高くなる。図3に示す模範的なMOSデバイス300では、デバイスの実効幅Weffに比例したP−N接合キャパシタンスCjの減少が、少なくとも部分的に次式に基づいて達成される。

Cj∝Weff−2nD

ここで、nは使用されるトレンチの数であり、Dはトレンチの深さである。上の式から理解できるように、特定の実効幅Weffに関して、デバイスの接合キャパシタンスCjは、トレンチの深さの増加のみならず、デバイスで使用されるトレンチの数の増加とともに減少する。

【0028】

好ましい実施形態では、MOSデバイス300のドレイン領域306の断面厚さは約0.3μmである。ドレイン領域306を形成するために使用されるN型不純物は、2つの隣り合うトレンチ310の側壁から各メサ308の中に拡散するので、約0.6μm以下のトレンチ間隔では、メサ中のP型エピタキシャル材料の実質的にすべてがN+ドレイン領域で確実に費やされるようになる。理解すべきことであるが、MOSデバイス300はトレンチ310の特定の間隔に限定されない。例えばMOSデバイス300のドレイン領域306の断面厚さを大きくして、0.6μmよりも大きなトレンチ間隔を使用することができる。

【0029】

図4は、本発明の他の実施形態に従って形成された模範的なMOSデバイス400の少なくとも一部を示す断面図である。図は、主に、MOSデバイス400のドレイン領域を示している。図3に示すMOSデバイス300と同じように、模範的なMOSデバイス400は、デバイスの実効幅WeffがデバイスのP−N接合の幅よりも実質的に大きくなるように形作られ、それによって、大きな追加のチップ面積を費やすことなく、かつデバイスの接合キャパシタンスを増加させることなく、デバイスのオン状態抵抗の有利な減少を実現している。

【0030】

模範的なMOSデバイス400は、P+基板402上に形成されたP型エピタキシャル層404を含む。エピタキシャル層の上面に近接してエピタキシャル層404中に、複数のトレンチ410が形成される。隣り合う2つのトレンチ410の間のエピタキシャル領域を、本明細書でメサ412と呼ぶ。メサ412の中心部分は、好ましくは、例えば酸化物(例えば、二酸化珪素)のような絶縁材料408を備える。絶縁材料408は、好ましくは、エピタキシャル層404中のトレンチ410の深さ(例えば、約1μmから約50μm)に実質的に等しい深さで形成される。

【0031】

例えば打込みプロセスおよび/または拡散プロセスなどを使用して、N+ドレイン領域406をエピタキシャル層404中に形成する。図から明らかなように、ドレイン領域406は、好ましくは、エピタキシャル層404の上面に近接して形成されるので、トレンチ410に起因するエピタキシャル層の上面の波形の外形に沿っている。しかし、MOSデバイス400では、ドレイン領域406は連続した領域として形成されないで、代わりに別個のセグメントとして形成され、そのドレイン領域セグメントはメサ412に形成された絶縁材料408で互いに分離されている。ドレイン領域セグメント406は、主にトレンチ410の側壁および底壁に限定されているので、対応するトレンチ410の形になる。MOSデバイス400のドレイン領域406の断面だけを図4に示したが、理解すべきことであるが、本明細書で説明する本発明の技術はデバイスのソース領域を形成する際に同様に使用することができる。

【0032】

MOSデバイス400のチャネル領域の実効幅Weffは、デバイスのドレイン領域セグメント406すべての周辺長の和として決定することができる。この周辺長の和は、与えられたトレンチの場合、トレンチの深さDの2倍にトレンチの幅Wを加えたもの(すなわち、2D+W)の関数である。MOSデバイス400の接合キャパシタンスを決定する際に、デバイスのP−N接合の幅は、本質的に、トレンチの幅の関数だけである。というのは、絶縁材料408が存在するためにメサ412にP−N接合が形成されないからである。したがって、図3に示すMOSデバイス300と同じように、MOSデバイス400は、チャネル領域の実効幅がデバイスのドレイン領域のP−N接合の幅よりも実質的に大きくなるように形作られる。

【0033】

図5は、本発明の第3の実施形態に従って形成された模範的なMOSデバイス500の少なくとも一部を示す断面図である。この図では、MOSデバイス500のドレイン領域506の断面を主に示す。MOSデバイス500は、好ましくは、P+基板502上に形成されたP型エピタキシャル層504を含む。図3に示すMOSデバイス300と同様に、MOSデバイス500は、エピタキシャル層の上面に近接してエピタキシャル層504中に形成された複数のトレンチ510を含む。図3のMOSデバイス300のトレンチ310と比較して、MOSデバイス500のトレンチ510は、好ましくは、下を切り取られた側壁514を有して形成されるので、その結果、与えられたトレンチの底壁がトレンチの上の開口よりも広くなっている。下を切り取られた側壁は、例えば、異方性エッチング・プロセスを使用して形成することができる。このようにして、所望の傾斜(例えば、正および/または負の傾斜)の側壁を有するトレンチ510を形成することができる。

【0034】

好ましくは、ドレイン領域がエピタキシャル層504中に形成された後で、2つの隣り合うトレンチの底壁に近接したドレイン領域の部分が互いに実質的に合体して、トレンチの底壁を横切って実質的に連続した水平なP−N接合を形成するように、N+ドレイン領域506の厚さと共に、2つの隣り合うトレンチ510の間隔が形作られる。したがって、隣り合うトレンチの間に形成されたメサ512は、P型コア材料508をエピタキシャル層504から電気的に絶縁するようにN+ドレイン領域506で実質的に囲まれたP型エピタキシャル材料の中心コア508を備える。

【0035】

MOSデバイス500のチャネル領域の実効幅Weffは、デバイスのドレイン領域506に関連したすべてのセグメントの和として決定することができ、このセグメントの和は、与えられたトレンチでは、トレンチの深さDの約2倍よりも僅かに大きいもの(例えば、傾斜した側壁514の角度に基づいている)にトレンチの幅Wを加えたものの関数である。MOSデバイス500の接合キャパシタンスを決定する際に、デバイスのP−N接合の幅は、本質的に、P−N接合の直線幅WLINの関数に過ぎない。というのは、少なくとも部分的に、メサのP型材料508を基本的にピンチ・オフするドレイン領域506が存在するために、メサ512に形成された能動的なP−N接合はないからである。特にデバイスの全接合キャパシタンスに比べると、メサ512に起因する接合キャパシタンスは、基本的にゼロになる。したがって、図3および4に示すそれぞれMOSデバイス300および400と同じように、MOSデバイス500のチャネル領域の実効幅は、デバイスのP−N接合の幅よりも実質的に大きい。

【0036】

図6は、本発明の第4の実施形態に従って形成された模範的なMOSデバイス600の少なくとも一部を示す断面図である。この図は、主に、MOSデバイス600のドレイン領域606を示している。図3〜5に関連して前に説明した例示のMOSデバイス実施形態と同じように、模範的なMOSデバイス600は、有利なことに、デバイスのチャネル領域の実効幅WeffがデバイスのP−N接合の幅よりも実質的に大きくなるように形作られる。このために、MOSデバイス600の電気伝導性を有利に高めることができるようになり、それによって、デバイスの接合キャパシタンスの大きな増加なしに、オン状態抵抗を減少させる。

【0037】

MOSデバイス600は、好ましくは、P+基板602上に形成されたP型エピタキシャル層604を含む。エピタキシャル層の上面に近接してエピタキシャル層604中に、複数のトレンチ610が形成されている。隣り合うトレンチ610の間に形成されたメサ612は、好ましくは、例えば打込みプロセスおよび/または拡散プロセスなどを使用して、知られている濃度レベル(例えば、1立方センチメートル当たり約1014原子から約1015原子)の低濃度ドープN型材料608(例えば、砒素または燐)で実質的に構成されている。それから、もっと高濃度ドープのN+ドレイン領域606(例えば、1立方センチメートル当たり約1015原子から約1016原子)がエピタキシャル層604の上面に近接して形成され、それでトレンチ610に起因するエピタキシャル層の上面の波形の外形に実質的に沿っている。波形ドレイン領域606の配列によって、前に説明したように、MOSデバイス600のチャネル領域の実効幅が増加する。

【0038】

MOSデバイス600の実効幅は、デバイスのドレイン領域606の全周辺長の和に基づいて決定され、この全周辺長は、トレンチ610の深さD、トレンチの幅W、およびメサ612の厚さTの関数である。他方で、デバイスのP−N接合の幅は、P型エピタキシャル層604と各トレンチの底壁に近接したN+ドレイン領域606との間の接合の周辺長の関数として主に決定することができ、実質的にトレンチ深さに無関係である。P−N接合は、また、エピタキシャル層604とメサの低濃度ドープN型材料608との間にも形成される。しかし、N型材料608のドーピング濃度はN+ドレイン領域606のドーピング濃度よりも相当に低いので、メサ612に関連したP−N接合に起因する接合キャパシタンスは実質的により小さくなる。図3〜5に図示した模範的なMOSデバイス実施形態と同じように、ソース領域(図示しない)は、ドレイン領域606の形成に似たやり方でMOSデバイス600に形成することができる。

【0039】

一般性を失うことなく、デバイスのP−N接合の幅よりも実質的に大きな実効幅を有するように形作られたMOSデバイスを形成するための様々な例示の実施形態を、本明細書で説明しまた図示した。本発明の技術および有利点は、他のデバイスを形成するように容易に展開することができるが、このことは、当業者には明らかになるであろう。

【0040】

図7A〜7Dは、本発明の一実施形態に従って、図4に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す。例示の方法は、従来のCMOS適合半導体製造プロセス技術の背景で説明する。理解すべきことであるが、本発明は、本デバイスを製造するためのこの方法または任意の特定の方法に限定されない。前に述べたように図に示す様々な層および/または領域は、一定の比率に応じて描かれていないことがあり、また、説明を容易にするためにある特定の半導体層は省略されていることがある。

【0041】

図7Aを参照して、本発明の技術を実施することができる模範的な半導体ウェハ700の少なくとも一部を示す。ウェハ700は、好ましくは、基板702を備える。基板702は、好ましくは、高伝導性を有するP+型基板であるが、代わりにN+型基板を使用することができる。当業者は理解するように、P+基板は、例えば拡散工程または打込み工程などによって、基板材料に所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を基板材料に加えて、望み通りに材料の伝導性を変えることによって、形成することができる。それから、エピタキシャル層704を、好ましくは、ウェハ700の全表面にわたって成長させる。エピタキシャル層704は、また、P型不純物を加えて変えることもできる。

【0042】

例えばウェハ700の上面に対応するトレンチを画定する開口を作るなどによって、エピタキシャル層704に第1の複数のトレンチ706を形成することができる。ウェハ700の上面にフォトレジストの層(図示しない)を堆積し、さらに従来のフォトリソグラフィ・パターン形成工程、それに続いてウェハの不要部分を除去するエッチング工程を使用して、開口を形成することができる。トレンチ706は、好ましくは、(例えば、反応性イオン・エッチング(RIE)、ドライ・エッチング、その他を使用して)エピタキシャル層704中に所望の深さで形成する。それから、図7Bに示すように、例えば従来のトレンチ充填プロセスを使用して、トレンチ706に酸化物(例えば、二酸化珪素)のような絶縁材料を充填して、充填酸化物領域708を形成する。充填酸化物領域708は、好ましくは、エピタキシャル層704の上面と実質的に平面であるように形成する。

【0043】

図7Cを参照して、次に、エピタキシャル層の上面に近接してエピタキシャル層704中に第2の複数のトレンチ710を形成する。第2の複数のトレンチ710は、好ましくは、充填酸化物領域708で互いに分離され、各充填酸化物領域が好ましくは2つの隣り合うトレンチ710の間に配置されている。その後、図7Dに示すように、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のN型不純物すなわちドーパント712(例えば、燐または砒素)をエピタキシャル層に加えて、トレンチ710の側壁および底壁に近接したエピタキシャル層704中に、ドレイン領域714を形成する。ドレイン領域714は、例えば打込み工程または拡散工程を使用して形成して、望み通りに材料の伝導性を変えることができる。

【0044】

図8A〜8Cは、本発明の他の実施形態に従って、図6に示す模範的なMOSデバイスを形成するために使用することができる例示の方法の工程を示す。例示の方法は、従来CMOS適合半導体製造プロセス技術の背景で説明する。理解すべきことであるが、本発明はデバイスを製造するこの方法または任意の特定の方法に限定されない。

【0045】

図8Aを参照して、本発明の技術を実施することができる模範的な半導体ウェハ800の少なくとも一部を示す。ウェハ800は、好ましくは、基板802を備える。基板802は、好ましくは、高伝導性を有するP+型基板であるが、N+型基板を代わりに使用することができる。当業者は理解するように、P+基板は、例えば拡散工程または打込み工程などによって、基板材料に所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のP型不純物すなわちドーパント(例えば、ホウ素)を基板材料に加えて、望み通りに材料の伝導性を変えることによって、形成することができる。それから、エピタキシャル層804を、好ましくは、ウェハ800の全表面にわたって成長させる。エピタキシャル層804は、また、P型不純物を加えて変えることもできるが、好ましくは基板802よりも低濃度である。低濃度ドープN型層806は、好ましくは、例えば打込みプロセスまたは拡散プロセスなどを使用して望み通りにエピタキシャル材料の伝導性を変えることによって、エピタキシャル層804の少なくとも一部に形成する。

【0046】

図8Bに示すように、例えばウェハ800の上面に対応するトレンチを画定する開口を作るなどによって、低濃度ドープN型層806に複数のトレンチ808を形成する。ウェハ800の上面にフォトレジストの層(図示しない)を堆積し、さらに従来のフォトリソグラフィ・パターン形成工程、それに続いてウェハの不要部分を除去するエッチング工程を使用して、開口を形成することができる。トレンチ808は、好ましくは、(例えば、反応性イオン・エッチング(RIE)、ドライ・エッチング、その他を使用して)低濃度ドープN型層806中に所望の深さで形成する。トレンチ808を形成するとき、エピタキシャル層804をエッチング停止として使用することができ、それによって、トレンチの底壁を通じてエピタキシャル層の少なくとも一部を露出させる。ただし、エピタキシャルを露出させる必要はない。

【0047】

図8Cを参照して、その後、所望の濃度(例えば、1立方センチメートル当たり約5×1018から約5×1019原子)のN型不純物すなわちドーパント812(例えば、燐または砒素)をN型層に加えて、低濃度ドープN型層806にドレイン領域810を形成する。ドレイン領域810は、好ましくは、ウェハ800の上面に近接して形成されるので、トレンチ808に起因する実質的に波形の外形になる。ドレイン領域810は、例えば打込み工程または拡散工程を使用して形成して、望み通りに材料の伝導性を変えることができる。ドレイン領域810の断面厚さthは、好ましくは、約0.3μmであるが、ドレイン領域はどんな特定の寸法および/または形状にも限定されない。

【0048】

本発明のMOSデバイスは、少なくとも部分的に集積回路中に実現することができる。集積回路の形成において、複数の同一チップは、一般に、半導体ウェハの表面にパターンを繰り返して製造される。各チップは本明細書で説明したデバイスを含み、さらに他の構造または回路を含むことができる。個々のチップをウェハから切断しすなわちダイシングし、そして集積回路としてパッケージする。当業者は、ウェハをダイシングし、チップをパッケージして集積回路をつくる方法を知っているだろう。そのように製造された集積回路は、この発明の一部と考えられる。

【0049】

本発明の例示の実施形態は本明細書で添付の図面を参照して説明したが、理解すべきことであるが、本発明はまさにその実施形態に限定されることなく、また当業者は添付の特許請求の範囲の範囲から逸脱することなく、その実施形態に様々な他の変更および修正を加えることができる。

【特許請求の範囲】

【請求項1】

第1の伝導型の半導体層と、

前記半導体層の上面に近接して前記半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域であって、互いに間隔を開けて配置されている第1および第2のソース/ドレイン領域と、

前記半導体層の上に形成され、かつ前記半導体層から電気的に絶縁されている特定のトランジスタのゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備える金属酸化物半導体デバイスであって、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られ、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、金属酸化物半導体デバイス。

【請求項2】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの間隔は、2つの隣り合うトレンチを隔離する前記半導体層の少なくとも部分が前記第2の伝導型の材料で実質的に完全に構成されるように、整えられている、請求項1に記載のデバイス。

【請求項3】

前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅に対する前記デバイスの実効幅の比が、前記半導体層中の前記トレンチの各々の深さの関数である、請求項2に記載のデバイス。

【請求項4】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合は、2つの隣り合うトレンチを隔離する前記半導体層の部分の幅が前記特定のソース/ドレイン領域の断面厚さの2倍よりも小さいように、すなわち前記2つの隣り合うトレンチを隔離する前記半導体層の前記部分が第2の伝導型の材料で実質的に完全に構成されるように、形作られている、請求項1に記載のデバイス。

【請求項5】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に複数のトレンチを形成しかつ前記半導体の上面に近接した前記半導体層中に前記第2の伝導型の不純物を打ち込むことで形成され、前記トレンチの間隔は、2つの隣り合うトレンチを隔離する前記半導体層の少なくとも部分が前記第2の伝導型の材料に実質的代わるように、形作られている、請求項1に記載のデバイス。

【請求項6】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを有して形成され、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える側壁および底壁を有して形成され、前記トレンチは、少なくとも2つの隣り合うトレンチの前記底壁が前記半導体層中に少なくとも2つの隣り合うトレンチの間に前記第2の伝導型の実質的に連続した領域を形成するように形作られている、請求項1に記載のデバイス。

【請求項7】

第1の伝導型の第1の半導体層と、

前記第1の半導体層の上に形成された第2の伝導型の第2の半導体層と、

前記第2の半導体層中に形成された前記第2の伝導型の、互いに間隔を開けて配置された第1および第2のソース/ドレイン領域であって、第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記第1の半導体層と前記特定のソース/ドレイン領域との間に少なくとも1つの接合を形成するものである第1および第2のソース/ドレイン領域と、

前記第2の半導体層の上に形成され、かつ前記第2の半導体層から電気的に絶縁されているゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備える金属酸化物半導体デバイスであって、

少なくとも前記特定のソース/ドレイン領域は、前記第1の半導体層と前記特定のソース/ドレイン領域との間の前記少なくとも1つの接合の幅よりも実質的に大きな実効幅を有して形作られ、前記第1の半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、金属酸化物半導体デバイス。

【請求項8】

金属酸化物半導体デバイスを形成する方法であって、

第1の伝導型の第1および第2のソース/ドレイン領域を第2の伝導型の半導体層中に形成する工程であって、前記第1および第2のソース/ドレイン領域が前記半導体層の上面に近接して形成され、かつ互いに間隔を開けて配置されている工程と、

前記半導体層の上に前記半導体層から電気的に絶縁されたゲートを形成する工程であって、前記ゲートが前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に形成される工程とを備え、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形成され、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、方法。

【請求項9】

少なくとも1つの金属酸化物半導体デバイスを含む集積回路であって、前記少なくとも1つの金属酸化物半導体デバイスが、

第1の伝導型の半導体層と、

前記半導体層の上面に近接して前記半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域であって、前記第1および第2のソース/ドレイン領域のうちの少なくとも1つが前記第2の伝導型の材料で実質的に完全に構成される隆起したメサ構造を少なくとも1つ備え、互いに間隔を開けて配置された第1および第2のソース/ドレイン領域と、

前記半導体層の上に形成され前記半導体層から電気的に絶縁されているゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備え、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られ、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、集積回路。

【請求項1】

第1の伝導型の半導体層と、

前記半導体層の上面に近接して前記半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域であって、互いに間隔を開けて配置されている第1および第2のソース/ドレイン領域と、

前記半導体層の上に形成され、かつ前記半導体層から電気的に絶縁されている特定のトランジスタのゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備える金属酸化物半導体デバイスであって、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られ、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、金属酸化物半導体デバイス。

【請求項2】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの間隔は、2つの隣り合うトレンチを隔離する前記半導体層の少なくとも部分が前記第2の伝導型の材料で実質的に完全に構成されるように、整えられている、請求項1に記載のデバイス。

【請求項3】

前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅に対する前記デバイスの実効幅の比が、前記半導体層中の前記トレンチの各々の深さの関数である、請求項2に記載のデバイス。

【請求項4】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合は、2つの隣り合うトレンチを隔離する前記半導体層の部分の幅が前記特定のソース/ドレイン領域の断面厚さの2倍よりも小さいように、すなわち前記2つの隣り合うトレンチを隔離する前記半導体層の前記部分が第2の伝導型の材料で実質的に完全に構成されるように、形作られている、請求項1に記載のデバイス。

【請求項5】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に複数のトレンチを形成しかつ前記半導体の上面に近接した前記半導体層中に前記第2の伝導型の不純物を打ち込むことで形成され、前記トレンチの間隔は、2つの隣り合うトレンチを隔離する前記半導体層の少なくとも部分が前記第2の伝導型の材料に実質的代わるように、形作られている、請求項1に記載のデバイス。

【請求項6】

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを有して形成され、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える側壁および底壁を有して形成され、前記トレンチは、少なくとも2つの隣り合うトレンチの前記底壁が前記半導体層中に少なくとも2つの隣り合うトレンチの間に前記第2の伝導型の実質的に連続した領域を形成するように形作られている、請求項1に記載のデバイス。

【請求項7】

第1の伝導型の第1の半導体層と、

前記第1の半導体層の上に形成された第2の伝導型の第2の半導体層と、

前記第2の半導体層中に形成された前記第2の伝導型の、互いに間隔を開けて配置された第1および第2のソース/ドレイン領域であって、第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記第1の半導体層と前記特定のソース/ドレイン領域との間に少なくとも1つの接合を形成するものである第1および第2のソース/ドレイン領域と、

前記第2の半導体層の上に形成され、かつ前記第2の半導体層から電気的に絶縁されているゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備える金属酸化物半導体デバイスであって、

少なくとも前記特定のソース/ドレイン領域は、前記第1の半導体層と前記特定のソース/ドレイン領域との間の前記少なくとも1つの接合の幅よりも実質的に大きな実効幅を有して形作られ、前記第1の半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、金属酸化物半導体デバイス。

【請求項8】

金属酸化物半導体デバイスを形成する方法であって、

第1の伝導型の第1および第2のソース/ドレイン領域を第2の伝導型の半導体層中に形成する工程であって、前記第1および第2のソース/ドレイン領域が前記半導体層の上面に近接して形成され、かつ互いに間隔を開けて配置されている工程と、

前記半導体層の上に前記半導体層から電気的に絶縁されたゲートを形成する工程であって、前記ゲートが前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に形成される工程とを備え、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形成され、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、方法。

【請求項9】

少なくとも1つの金属酸化物半導体デバイスを含む集積回路であって、前記少なくとも1つの金属酸化物半導体デバイスが、

第1の伝導型の半導体層と、

前記半導体層の上面に近接して前記半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域であって、前記第1および第2のソース/ドレイン領域のうちの少なくとも1つが前記第2の伝導型の材料で実質的に完全に構成される隆起したメサ構造を少なくとも1つ備え、互いに間隔を開けて配置された第1および第2のソース/ドレイン領域と、

前記半導体層の上に形成され前記半導体層から電気的に絶縁されているゲートであって、前記第1のソース/ドレイン領域と前記第2のソース/ドレイン領域との間に少なくとも部分的に配置されているゲートとを備え、

前記第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つが、前記半導体層と前記特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られ、前記半導体層と前記特定のソース/ドレイン領域との間の接合に対応するキャパシタンスは、前記特定のソース/ドレイン領域の実効幅に比例せず、

少なくとも前記特定のソース/ドレイン領域が、前記半導体層の上面に近接して前記半導体層中に形成された複数のトレンチを備え、前記トレンチの少なくとも部分集合の各々が、前記第2の伝導型の材料を備える傾斜した側壁および底壁を有して形成され、2つの隣り合うトレンチの前記側壁は、前記隣り合うトレンチの底壁に近接した前記第2の伝導型の材料が合体して前記半導体層中に前記第2の伝導型の実質的に連続した領域を形成するように形作られ、

前記トレンチの少なくとも部分集合の各々の側壁は、前記底壁が前記トレンチの上の開口よりも広くなるように、傾斜されている、集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図8A】

【図8B】

【図8C】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図8A】

【図8B】

【図8C】

【公開番号】特開2013−42169(P2013−42169A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2012−235816(P2012−235816)

【出願日】平成24年10月25日(2012.10.25)

【分割の表示】特願2005−277004(P2005−277004)の分割

【原出願日】平成17年9月26日(2005.9.26)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成24年10月25日(2012.10.25)

【分割の表示】特願2005−277004(P2005−277004)の分割

【原出願日】平成17年9月26日(2005.9.26)

【出願人】(500587067)アギア システムズ インコーポレーテッド (302)

【Fターム(参考)】

[ Back to top ]