ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ドライバ及びその使用方法に関し、特に、複数の出力端子を有し、複数の駆動対象を駆動制御することができるドライバ及びその使用方法に関する。

【背景技術】

【0002】

従来から、液晶表示装置のバックライトや遊技機の電飾として、多くの発光ダイオード(LED:Light Emitted Diode)が使用されているが、このときそれらのLEDをまとめて発光制御するのがLEDドライバ(駆動装置)であり、典型的には、専用のIC(集積回路)として具現化されている。

【0003】

かかるLEDドライバICにおいては、接続されるLEDの輝度調整を実現するのにパルス幅変調(PWM:Pulse Width Modulation)制御がごく一般的に採用されている。図5は、従来のドライバIC1000Aの出力端子2近傍の構成と、それにLED31を接続したときの動作を説明するための図である。ここで、各ドライバトランジスタ16a〜16d(数は任意)にパルス幅変調されたパルス(例えば、同図においては、ディーティ比25%)が入力される構成となっており、ドライバトランジスタ16はパルスの立ち上がりでオンし、ハイレベルの間、オンを維持するので、その間各抵抗成分32a〜32dを介して各LED31a〜31dに電流が流れてそれらが点灯する。従って、ディーティ比を変えることにより輝度調整が行えるという駆動制御となる。

【0004】

図5に示した従来の駆動制御の方法においては、各ドライバトランジスタ16a〜16dに入力される各パルスは、同一タイミングで立ち上がっており、故に、各ドライバトランジスタ16a〜16dは同一タイミングでオンすることとなる。なお、各ドライバトランジスタ16a〜16dごとにデューティ比を異ならせることもできるが、その場合においても、図1(b)に示すように、立ち上がりのタイミングはそれぞれ一致している。

【0005】

しかしながら、上述の従来の技術においては、パルスの立ち上がりのタイミングで、ドライバIC1000A内を流れる電流が急激に変化し、それに伴い各ドライバトランジスタ16a〜16dに供給される電圧が変動することによるノイズが発生し、それに伴いLEDへの配線、電源の配線から不要輻射が放出され、IC外部の基板及びハーネス等へも不要輻射が放出されるという課題があった。特に、それは駆動制御されるLEDの数が多くなればなるほど顕著となる。そこで、かかる課題を解決するために、各ドライバトランジスタに入力されるパルスを時間的にずらして立ち上がるタイミングをずらし、各ドライバトランジスタが同時にオンしないようにする技術が開発されている(例えば、特許文献1及び2参照)。

【0006】

図6は、その技術を簡単に説明するための図であり、同図においては、例えば4つのドライバトランジスタ16a〜16dについて、一周期を4分割してそれぞれにデューティ比25%のパルスを割り当てて、各ドライバトランジスタ16a〜16dがオンするタイミングをずらしている。但し、特許文献2にあるように、各パルスのある程度の重なりを許容することもできる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2008−262966号公報

【特許文献2】特開2009−188135号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述のようなPWMのパルス生成方法によれば、そのパルス発生のためにタイミングをとるための制御系回路が複雑となり、またその規模が大きくなるという欠点がある。

【0009】

ところで、とりわけ遊技機に使用されるLEDの駆動制御においては、多くのLEDが使用されており、複数のLEDをブロックとして形成し、LEDドライバの1つの出力端子に、そのブロックを一括で接続して制御するということも行われている。

【0010】

一方、遊技機においては、近似、一層の遊興効果を高めるために、LEDドライバのユーザがその出力端子のいくつかを並列的に束ねてLEDを点灯しようとする場合がある。図7は、かかる場合の回路構成を示す図である。なお、同図においては、模式的にLED31ad1つとしているが、前述のブロックのように複数接続されていても構わない。

【0011】

この場合において、図6に示したように、各ドライバトランジスタ16a〜16dのオンのタイミングをずらしている場合を考える。図6に示したように、各ドライバトランジスタ16a〜16dの最大許容電流が25mAであって、各出力端子2a〜2dの個々に、20mAの負荷となる各LED31a〜31dを接続する場合、当然正常動作となるものの、図8に示したように、出力端子2a〜2dを束ねて全体で80mAの負荷となるLED31adを接続した場合、任意の時刻において、オンしているドライバトランジスタは1つしかないので、そのオンしている1つのドライバトランジスタに対して80mAの全ての負荷が掛かり、オーバーロードであり、破壊の危険性がある。

【0012】

なお、以上の説明は、LEDドライバの場合で説明したが、例えばモータのような他の機器を駆動制御するドライバであっても同様の事情がある。

【0013】

本発明は上述のような事情から為されたものであり、本発明の目的は、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えることができるドライバを提供することにある。また、他の目的は、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるドライバの使用方法を提供することにある。

【課題を解決するための手段】

【0014】

上記目的を達成するため、本発明のドライバは、駆動対象が接続される複数の出力端子と、前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、を備えたドライバであって、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させることを要旨とする。

【0015】

それに加えて、前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを要旨とする。

【0016】

ここで、前記複数の制御部の各々は、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させて、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスを生成する。

【0017】

具体的には、前記複数の制御部の各々は、所定の上限カウント値から下限カウント値までを減算的、かつ巡廻的に計数した第1計数値と、その計数と並行して、前記下限カウント値から前記上限カウント値までを加算的、かつ巡廻的に計数した第2計数値を並行出力する計数部と、前記計数部からの前記第1計数値及び前記第2計数値を入力して、それらをカウンタフレーム期間ごとに切り替えて出力する選択器と、第1の入力端子に、前記選択器から出力された計数値を入力すると共に、第2の入力端子に設定デューティ比に対応する値を入力し、それらの入力端子に入力される値を比較し、それらの値の大小に応じて、ロー/ハイレベルの信号を出力する比較器と、前記比較器の出力信号を入力してオン/オフするトランジスタと、を有する。

【0018】

更に具体的には、前記計数部は、前記第1計数値を出力する第1カウンタと、前記第2計数値を出力する第2カウンタを有する。あるいは、前記計数部は、前記第1計数値を出力する特定カウンタと、その特定カウンタからの前記第1計数値を入力して1を加算して出力する加算器と、その加算器からの値を反転し、その結果を前記第2計数値として出力するインバータとを有する。

【0019】

また、前記駆動対象は、発光ダイオードであり得る。前記発光ダイオードは、遊技機に使用されるものであり得る。また、特に、前記複数の出力端子の各々に、複数の発光ダイオードが縦並列的に接続されることもあり得る。一方、前記駆動対象は、モータであり得る。

【0020】

また、上記目的を達成するため、本発明のドライバの使用方法は、駆動対象が接続される複数の出力端子と、前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、を備え、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させるドライバの使用方法であって、前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを要旨とする。

【発明の効果】

【0021】

本発明のドライバによれば、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えることができる。また、複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、デューティ比を同一とすることにより、個々の制御部に電流が集中して流れる瞬間が生じることを回避できる。

【0022】

また、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスは、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させることで生成できるので、簡易な構成で実現できる。

【0023】

本発明のドライバの使用方法によれば、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できる。特に、ドライバのユーザが、その出力端子のいくつかを束ねて使用する場合にも、それらに係るデューティ比を同一とすることにより、個々の制御部に電流が集中して流れる瞬間が生じることを回避できる。

【図面の簡単な説明】

【0024】

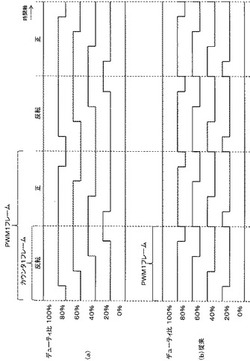

【図1】本発明のドライバの一実施形態における、ドライバトランジスタに入力されるPWMに係る各パルスと、従来における、ドライバトランジスタに入力されるPWMに係る各パルスの比較を示す図であり、同図(a)が本発明の一実施形態を示しており、同図(b)が従来を示している。

【図2】本発明のドライバの一実施形態たるドライバICの構成と、それに各LEDが接続された状態を示す図である。

【図3】各駆動電流制御回路の構成を示す図である。

【図4】具体例を説明するための図である。

【図5】従来技術を説明するための図である。

【図6】従来技術を説明するための図である。

【図7】従来技術を説明するための図である。

【発明を実施するための形態】

【0025】

以下、図面を参照して、本発明の実施の形態について詳細に説明する。

本発明においては、デューティ比を変えることをもってして、パルスの立ち上がり(立ち下がり)のタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらすことが特徴である。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避するということが特徴である。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

【0026】

図1は、本発明のドライバの一実施形態における、ドライバトランジスタに入力されるPWMに係る各パルスと、従来における、ドライバトランジスタに入力されるPWMに係る各パルスの比較を示す図であり、同図(a)が本発明の一実施形態を示しており、同図(b)が従来を示している。

【0027】

本発明の一実施形態においては、図1(a)に示すような、各デューティ比のパルスを生成してドライバトランジスタに入力させることにより、各ドライバトランジスタの同時オンを回避する。なお、図1においては、20%間隔の離散的な6つのパルス(デューティ比0%及び100%を含む)を描いているが、これは単に説明の便宜によるものであり、デューティ比0%〜100%の任意のデューティ比のパルスを生成できる。

【0028】

図1(a)と図1(b)を比較参照すれば分かるように、本発明の一実施形態におけるパルスは、従来におけるパルスをPWM1フレーム置きに反転させることで生成できることが分かる。従って、本発明の一実施形態におけるパルスにおいては、従来におけるPWMフレームの2つ分の時間長でPWM1フレームが形成されていると捉えることができる。

【0029】

図2は、本発明のドライバの一実施形態たるドライバICの構成と、それに各LEDが接続された状態を示す図である。同図に示したドライバIC100は、少なくとも、駆動電流制御回路1a,1b,・・・と、それらに対応した出力端子2a,2b,・・・とを備えている。また、それらの出力端子2a,2b,・・・には、各抵抗成分32a,32b,・・・を有するLED31a,31b,・・・が接続されている。ここで、例えば、出力端子2の数は、24である。なお、図2に示す場合は、出力端子を束ねない場合を示している。

【0030】

図3(a)は、各駆動電流制御回路1の構成の一例を示す図である。同図に示す駆動電流制御回路1は、少なくとも、第1カウンタ11及び第2カウンタ12と、カウンタ選択用レジスタ13と、第1カウンタ11及び第2カウンタの出力の各々が2つの入力端子に入力されると共に、カウンタ選択用レジスタ13の出力が選択制御信号として入力される選択器14と、選択器14の出力が第1の入力端子(−)に入力されると共に、設定デューティ比の値が第2の入力端子(+)に入力される比較器15と、比較器15の出力信号が、ベース端子に入力されるドライバトランジスタ16とを備えている。

【0031】

ここで、第1カウンタ11は、従来のPWM1フレーム期間において上限カウント値として例えば99の値から下限カウント値として例えば0の値までを減算的に計数すると共に、かつ下限カウント値から上限カウント値に戻るように巡廻的に計数するリングカウンタであり、他方、第2カウンタ12は、従来のPWM1フレーム期間(本発明においては、これを「カウンタ1フレーム」と称す)において上記下限カウント値から上記上限カウント値までを加算的に計数すると共に、かつ上限カウント値から下限カウント値に戻るように巡廻的に計数するリングカウンタである。また、カウンタ選択用レジスタ13は、カウンタ1フレーム期間ごとに、値‘0’と値‘1’とを交互に出力するレジスタである。選択器14は、カウンタ選択用レジスタ13から値‘0’が入力されている間は、第1カウンタ11からの計数値を選択して出力し、一方、カウンタ選択用レジスタ13から値‘1’が入力されている間は、第2カウンタ12からの計数値を選択して出力する。従って、比較器14は、最初のカウンタ1フレーム期間で下限カウント値から上限カウント値(0から99)までを出力し、次のカウンタ1フレーム期間で上限カウント値から下限カウント値(99から0)までを出力し、以降これを繰り返すこととなる。

【0032】

比較器15は、第1の入力端子に入力される値と、第2の入力端子に入力される値とを比較し、第1の入力端子に入力される値の方が大きいときは、値‘0’(ローレベル)を出力し、逆に、第1の入力端子に入力される値の方が小さいときは、値‘1’(ハイレベル)を出力する。そこで、例えば、第2の入力端子に、設定デューティ比の値として‘80’が与えられている場合を考える。そこで、最初のカウンタ1フレーム期間においては、前述のように第1カウンタ11からの計数値を選択して出力するので、比較器15の第1の入力端子には上限カウント値(99)から減算されていく値が供給される。従って、比較器15の出力は、計数値が80に減算されるまではローレベルを出力し、計数値が79に達した時点でハイレベルに変化する。また、次のカウンタ1フレーム期間においては、前述のように第2カウンタ11からの計数値を選択して出力するので、比較器15の第1の入力端子には下限カウント値(0)から加算されていく値が供給される。従って、比較器15の出力は、計数値が80に加算されるまではハイレベルを出力し、計数値が81に達した時点でローレベルに変化する。その結果、比較器15の出力は、本発明のPWM1フレーム期間においては、図1(a)のデューティ比80%で示すパルス波形を出力することとなる。そして、以降、それを繰り返す。なお、他の設定デューティ比にした場合でも同様である。

【0033】

なお、図3(a)に示した一例では、第1カウンタ11及び第2カウンタ12の2種類のカウンタを用いた場合を示したが、このような例に限るものではなく、第1カウンタ11及び第2カウンタ12の代わりに、図3(b)に示すように、特定カウンタ17、「+1」加算器18、及びインバータ19からなる組み合わせ回路で構成することで回路構成の一層の簡単化を図ることができる。この場合、2のべき乗のカウント値として64を使用した場合、一般的には0から63までのカウント動作を行うものであるが、本例の特定カウンタ17としては、1つ手前の62を上限カウント値とし、0から62までを加算的に計数して戻るように巡廻的に計数するリングカウンタで構成する。一方、特定カウンタ17は、選択器14へのカウント値の出力とは別に、同じカウント値を「+1」加算器18にも出力する。「+1」加算器18は、特定カウンタ17からの値に1を加え、結果をインバータ19に出力する。インバータ19は、入力した値をビット列シリアル信号レベル反転して出力する。その結果、特定カウンタ17が、選択器14に0から62を出力している間に、並行して、インバータ19、選択器14に対して、減算的に62から0までを出力することとなり、これが巡廻的に繰り返される。

【0034】

図3(b)に示した他の例においては、比較器15の第2の入力端子には、設定デューティ比値×0.63の値を整数化した値を入力させることとなるので、例えば、デューティ比として80%としたい場合には、第2の入力端子には、‘50’を入力させる。そこで、最初のカウンタ1フレーム期間においては、前述のように特定カウンタ17からの計数値を選択して出力するので、比較器15の第1の入力端子には上限カウント値、すなわち62から減算されていく値が供給される。従って、比較器15の出力は、計数値が50に減算されるまではローレベルを出力し、計数値が49に達した時点でハイレベルに変化する。また、次のカウンタ1フレーム期間においては、インバータ19からの計数値を選択して出力するので、比較器15の第1の入力端子には0から加算されていく値が供給される。従って、比較器15の出力は、計数値が50に加算されるまではハイレベルを出力し、計数値が51に達した時点でローレベルに変化する。その結果、比較器15の出力は、本発明のPWM1フレーム期間においては、図1(a)のデューティ比80%のパルス波形とほぼ同様の波形を出力することとなる。そして、以降、それを繰り返す。なお、他の設定デューティ比にした場合でも同様である。

【0035】

図4は、具体例を説明するための図である。なお、図4においては、図3に示した駆動電流制御回路の構成のうち、比較器15までの構成を省略し、代わりに、比較器15までで生成されたパルス波形を示している。

【0036】

同図に示した具体例では、出力端子2a〜2dを束ねて、抵抗成分32adを介したLED31adを接続している。そのとき、出力端子2a〜2dに対応する駆動電流制御回路1a〜1dにおいては、例えば共通の80%デューティ比のパルスを生成している。また、出力端子2e,2fの各々に関しては、他と束ねることなく、それぞれ、LED31eとLED31fを接続している。そのとき、それぞれに対応する駆動電流制御回路1e,1fにおいては、他と異なった60%と40%のデューティ比のパルスを生成している。これにより、駆動電流制御回路1a〜1dと、駆動電流制御回路1eと、駆動電流制御回路1fとの間の関係においては、デューティ比を変えることにより、同時オンによるIC内での急激な電流変化を回避し、一方、出力端子2a〜2dを束ねた駆動電流制御回路1a〜1dの互いの関係においては、デューティ比を同じにしてオン期間を一致させて個々のドライバトランジスタ16a〜16dに電流が集中してしまうことを回避している。

【0037】

なお、上述した実施形態においては、パルスの立ち上がりでドライバトランジスタがオンする構成としたが、パルスの立ち下がりでドライバトランジスタがオンする構成のものでもよい。

【0038】

また、説明の途中でも簡単に記したが、図に表された1つのLEDは、物理的な1つのLEDを必ずしも表しているのではなく、複数が縦並列的に接続されたLED群でもあり得るものである。

【0039】

更に、上述の実施形態では、駆動する対象をLEDとしたが、これに限られることはなく、例えばモータを駆動するようなドライバについても適用できる。

【0040】

本発明のドライバの一実施形態によれば、デューティ比を変えることをもってして、各ドライバトランジスタ16の同時オンを回避している。これによりドライバIC100内での急激な電流変化を回避し、ノイズの発生源を除いている。これは例えば図3に示したような簡易な回路で構成できる。

【0041】

また、いくつかの出力端子2を束ねて使用する場合には、それらに対応する駆動電流制御回路1の互いの関係においては、デューティ比を同じにしてオン期間を一致させ、個々のドライバトランジスタ16に電流が集中する瞬間が生じることを回避している。

【産業上の利用可能性】

【0042】

本発明のドライバ及びその使用方法は、遊技機、各種電飾機器、バックライト等のLEDや、モータを駆動するときに適用できる。

【符号の説明】

【0043】

100 ドライバIC

1 駆動電流制御回路

11 第1カウンタ

12 第2カウンタ

13 カウンタ選択用レジスタ

14 選択器

15 比較器

16 ドライバトランジスタ

17 特定カウンタ

18 +1加算器

19 インバータ

2 出力端子

31 LED

32 抵抗成分

1000A,1000B ドライバIC

【技術分野】

【0001】

本発明は、ドライバ及びその使用方法に関し、特に、複数の出力端子を有し、複数の駆動対象を駆動制御することができるドライバ及びその使用方法に関する。

【背景技術】

【0002】

従来から、液晶表示装置のバックライトや遊技機の電飾として、多くの発光ダイオード(LED:Light Emitted Diode)が使用されているが、このときそれらのLEDをまとめて発光制御するのがLEDドライバ(駆動装置)であり、典型的には、専用のIC(集積回路)として具現化されている。

【0003】

かかるLEDドライバICにおいては、接続されるLEDの輝度調整を実現するのにパルス幅変調(PWM:Pulse Width Modulation)制御がごく一般的に採用されている。図5は、従来のドライバIC1000Aの出力端子2近傍の構成と、それにLED31を接続したときの動作を説明するための図である。ここで、各ドライバトランジスタ16a〜16d(数は任意)にパルス幅変調されたパルス(例えば、同図においては、ディーティ比25%)が入力される構成となっており、ドライバトランジスタ16はパルスの立ち上がりでオンし、ハイレベルの間、オンを維持するので、その間各抵抗成分32a〜32dを介して各LED31a〜31dに電流が流れてそれらが点灯する。従って、ディーティ比を変えることにより輝度調整が行えるという駆動制御となる。

【0004】

図5に示した従来の駆動制御の方法においては、各ドライバトランジスタ16a〜16dに入力される各パルスは、同一タイミングで立ち上がっており、故に、各ドライバトランジスタ16a〜16dは同一タイミングでオンすることとなる。なお、各ドライバトランジスタ16a〜16dごとにデューティ比を異ならせることもできるが、その場合においても、図1(b)に示すように、立ち上がりのタイミングはそれぞれ一致している。

【0005】

しかしながら、上述の従来の技術においては、パルスの立ち上がりのタイミングで、ドライバIC1000A内を流れる電流が急激に変化し、それに伴い各ドライバトランジスタ16a〜16dに供給される電圧が変動することによるノイズが発生し、それに伴いLEDへの配線、電源の配線から不要輻射が放出され、IC外部の基板及びハーネス等へも不要輻射が放出されるという課題があった。特に、それは駆動制御されるLEDの数が多くなればなるほど顕著となる。そこで、かかる課題を解決するために、各ドライバトランジスタに入力されるパルスを時間的にずらして立ち上がるタイミングをずらし、各ドライバトランジスタが同時にオンしないようにする技術が開発されている(例えば、特許文献1及び2参照)。

【0006】

図6は、その技術を簡単に説明するための図であり、同図においては、例えば4つのドライバトランジスタ16a〜16dについて、一周期を4分割してそれぞれにデューティ比25%のパルスを割り当てて、各ドライバトランジスタ16a〜16dがオンするタイミングをずらしている。但し、特許文献2にあるように、各パルスのある程度の重なりを許容することもできる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2008−262966号公報

【特許文献2】特開2009−188135号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述のようなPWMのパルス生成方法によれば、そのパルス発生のためにタイミングをとるための制御系回路が複雑となり、またその規模が大きくなるという欠点がある。

【0009】

ところで、とりわけ遊技機に使用されるLEDの駆動制御においては、多くのLEDが使用されており、複数のLEDをブロックとして形成し、LEDドライバの1つの出力端子に、そのブロックを一括で接続して制御するということも行われている。

【0010】

一方、遊技機においては、近似、一層の遊興効果を高めるために、LEDドライバのユーザがその出力端子のいくつかを並列的に束ねてLEDを点灯しようとする場合がある。図7は、かかる場合の回路構成を示す図である。なお、同図においては、模式的にLED31ad1つとしているが、前述のブロックのように複数接続されていても構わない。

【0011】

この場合において、図6に示したように、各ドライバトランジスタ16a〜16dのオンのタイミングをずらしている場合を考える。図6に示したように、各ドライバトランジスタ16a〜16dの最大許容電流が25mAであって、各出力端子2a〜2dの個々に、20mAの負荷となる各LED31a〜31dを接続する場合、当然正常動作となるものの、図8に示したように、出力端子2a〜2dを束ねて全体で80mAの負荷となるLED31adを接続した場合、任意の時刻において、オンしているドライバトランジスタは1つしかないので、そのオンしている1つのドライバトランジスタに対して80mAの全ての負荷が掛かり、オーバーロードであり、破壊の危険性がある。

【0012】

なお、以上の説明は、LEDドライバの場合で説明したが、例えばモータのような他の機器を駆動制御するドライバであっても同様の事情がある。

【0013】

本発明は上述のような事情から為されたものであり、本発明の目的は、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えることができるドライバを提供することにある。また、他の目的は、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるドライバの使用方法を提供することにある。

【課題を解決するための手段】

【0014】

上記目的を達成するため、本発明のドライバは、駆動対象が接続される複数の出力端子と、前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、を備えたドライバであって、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させることを要旨とする。

【0015】

それに加えて、前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを要旨とする。

【0016】

ここで、前記複数の制御部の各々は、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させて、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスを生成する。

【0017】

具体的には、前記複数の制御部の各々は、所定の上限カウント値から下限カウント値までを減算的、かつ巡廻的に計数した第1計数値と、その計数と並行して、前記下限カウント値から前記上限カウント値までを加算的、かつ巡廻的に計数した第2計数値を並行出力する計数部と、前記計数部からの前記第1計数値及び前記第2計数値を入力して、それらをカウンタフレーム期間ごとに切り替えて出力する選択器と、第1の入力端子に、前記選択器から出力された計数値を入力すると共に、第2の入力端子に設定デューティ比に対応する値を入力し、それらの入力端子に入力される値を比較し、それらの値の大小に応じて、ロー/ハイレベルの信号を出力する比較器と、前記比較器の出力信号を入力してオン/オフするトランジスタと、を有する。

【0018】

更に具体的には、前記計数部は、前記第1計数値を出力する第1カウンタと、前記第2計数値を出力する第2カウンタを有する。あるいは、前記計数部は、前記第1計数値を出力する特定カウンタと、その特定カウンタからの前記第1計数値を入力して1を加算して出力する加算器と、その加算器からの値を反転し、その結果を前記第2計数値として出力するインバータとを有する。

【0019】

また、前記駆動対象は、発光ダイオードであり得る。前記発光ダイオードは、遊技機に使用されるものであり得る。また、特に、前記複数の出力端子の各々に、複数の発光ダイオードが縦並列的に接続されることもあり得る。一方、前記駆動対象は、モータであり得る。

【0020】

また、上記目的を達成するため、本発明のドライバの使用方法は、駆動対象が接続される複数の出力端子と、前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、を備え、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させるドライバの使用方法であって、前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを要旨とする。

【発明の効果】

【0021】

本発明のドライバによれば、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えることができる。また、複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、デューティ比を同一とすることにより、個々の制御部に電流が集中して流れる瞬間が生じることを回避できる。

【0022】

また、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスは、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させることで生成できるので、簡易な構成で実現できる。

【0023】

本発明のドライバの使用方法によれば、簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できる。特に、ドライバのユーザが、その出力端子のいくつかを束ねて使用する場合にも、それらに係るデューティ比を同一とすることにより、個々の制御部に電流が集中して流れる瞬間が生じることを回避できる。

【図面の簡単な説明】

【0024】

【図1】本発明のドライバの一実施形態における、ドライバトランジスタに入力されるPWMに係る各パルスと、従来における、ドライバトランジスタに入力されるPWMに係る各パルスの比較を示す図であり、同図(a)が本発明の一実施形態を示しており、同図(b)が従来を示している。

【図2】本発明のドライバの一実施形態たるドライバICの構成と、それに各LEDが接続された状態を示す図である。

【図3】各駆動電流制御回路の構成を示す図である。

【図4】具体例を説明するための図である。

【図5】従来技術を説明するための図である。

【図6】従来技術を説明するための図である。

【図7】従来技術を説明するための図である。

【発明を実施するための形態】

【0025】

以下、図面を参照して、本発明の実施の形態について詳細に説明する。

本発明においては、デューティ比を変えることをもってして、パルスの立ち上がり(立ち下がり)のタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらすことが特徴である。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避するということが特徴である。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

【0026】

図1は、本発明のドライバの一実施形態における、ドライバトランジスタに入力されるPWMに係る各パルスと、従来における、ドライバトランジスタに入力されるPWMに係る各パルスの比較を示す図であり、同図(a)が本発明の一実施形態を示しており、同図(b)が従来を示している。

【0027】

本発明の一実施形態においては、図1(a)に示すような、各デューティ比のパルスを生成してドライバトランジスタに入力させることにより、各ドライバトランジスタの同時オンを回避する。なお、図1においては、20%間隔の離散的な6つのパルス(デューティ比0%及び100%を含む)を描いているが、これは単に説明の便宜によるものであり、デューティ比0%〜100%の任意のデューティ比のパルスを生成できる。

【0028】

図1(a)と図1(b)を比較参照すれば分かるように、本発明の一実施形態におけるパルスは、従来におけるパルスをPWM1フレーム置きに反転させることで生成できることが分かる。従って、本発明の一実施形態におけるパルスにおいては、従来におけるPWMフレームの2つ分の時間長でPWM1フレームが形成されていると捉えることができる。

【0029】

図2は、本発明のドライバの一実施形態たるドライバICの構成と、それに各LEDが接続された状態を示す図である。同図に示したドライバIC100は、少なくとも、駆動電流制御回路1a,1b,・・・と、それらに対応した出力端子2a,2b,・・・とを備えている。また、それらの出力端子2a,2b,・・・には、各抵抗成分32a,32b,・・・を有するLED31a,31b,・・・が接続されている。ここで、例えば、出力端子2の数は、24である。なお、図2に示す場合は、出力端子を束ねない場合を示している。

【0030】

図3(a)は、各駆動電流制御回路1の構成の一例を示す図である。同図に示す駆動電流制御回路1は、少なくとも、第1カウンタ11及び第2カウンタ12と、カウンタ選択用レジスタ13と、第1カウンタ11及び第2カウンタの出力の各々が2つの入力端子に入力されると共に、カウンタ選択用レジスタ13の出力が選択制御信号として入力される選択器14と、選択器14の出力が第1の入力端子(−)に入力されると共に、設定デューティ比の値が第2の入力端子(+)に入力される比較器15と、比較器15の出力信号が、ベース端子に入力されるドライバトランジスタ16とを備えている。

【0031】

ここで、第1カウンタ11は、従来のPWM1フレーム期間において上限カウント値として例えば99の値から下限カウント値として例えば0の値までを減算的に計数すると共に、かつ下限カウント値から上限カウント値に戻るように巡廻的に計数するリングカウンタであり、他方、第2カウンタ12は、従来のPWM1フレーム期間(本発明においては、これを「カウンタ1フレーム」と称す)において上記下限カウント値から上記上限カウント値までを加算的に計数すると共に、かつ上限カウント値から下限カウント値に戻るように巡廻的に計数するリングカウンタである。また、カウンタ選択用レジスタ13は、カウンタ1フレーム期間ごとに、値‘0’と値‘1’とを交互に出力するレジスタである。選択器14は、カウンタ選択用レジスタ13から値‘0’が入力されている間は、第1カウンタ11からの計数値を選択して出力し、一方、カウンタ選択用レジスタ13から値‘1’が入力されている間は、第2カウンタ12からの計数値を選択して出力する。従って、比較器14は、最初のカウンタ1フレーム期間で下限カウント値から上限カウント値(0から99)までを出力し、次のカウンタ1フレーム期間で上限カウント値から下限カウント値(99から0)までを出力し、以降これを繰り返すこととなる。

【0032】

比較器15は、第1の入力端子に入力される値と、第2の入力端子に入力される値とを比較し、第1の入力端子に入力される値の方が大きいときは、値‘0’(ローレベル)を出力し、逆に、第1の入力端子に入力される値の方が小さいときは、値‘1’(ハイレベル)を出力する。そこで、例えば、第2の入力端子に、設定デューティ比の値として‘80’が与えられている場合を考える。そこで、最初のカウンタ1フレーム期間においては、前述のように第1カウンタ11からの計数値を選択して出力するので、比較器15の第1の入力端子には上限カウント値(99)から減算されていく値が供給される。従って、比較器15の出力は、計数値が80に減算されるまではローレベルを出力し、計数値が79に達した時点でハイレベルに変化する。また、次のカウンタ1フレーム期間においては、前述のように第2カウンタ11からの計数値を選択して出力するので、比較器15の第1の入力端子には下限カウント値(0)から加算されていく値が供給される。従って、比較器15の出力は、計数値が80に加算されるまではハイレベルを出力し、計数値が81に達した時点でローレベルに変化する。その結果、比較器15の出力は、本発明のPWM1フレーム期間においては、図1(a)のデューティ比80%で示すパルス波形を出力することとなる。そして、以降、それを繰り返す。なお、他の設定デューティ比にした場合でも同様である。

【0033】

なお、図3(a)に示した一例では、第1カウンタ11及び第2カウンタ12の2種類のカウンタを用いた場合を示したが、このような例に限るものではなく、第1カウンタ11及び第2カウンタ12の代わりに、図3(b)に示すように、特定カウンタ17、「+1」加算器18、及びインバータ19からなる組み合わせ回路で構成することで回路構成の一層の簡単化を図ることができる。この場合、2のべき乗のカウント値として64を使用した場合、一般的には0から63までのカウント動作を行うものであるが、本例の特定カウンタ17としては、1つ手前の62を上限カウント値とし、0から62までを加算的に計数して戻るように巡廻的に計数するリングカウンタで構成する。一方、特定カウンタ17は、選択器14へのカウント値の出力とは別に、同じカウント値を「+1」加算器18にも出力する。「+1」加算器18は、特定カウンタ17からの値に1を加え、結果をインバータ19に出力する。インバータ19は、入力した値をビット列シリアル信号レベル反転して出力する。その結果、特定カウンタ17が、選択器14に0から62を出力している間に、並行して、インバータ19、選択器14に対して、減算的に62から0までを出力することとなり、これが巡廻的に繰り返される。

【0034】

図3(b)に示した他の例においては、比較器15の第2の入力端子には、設定デューティ比値×0.63の値を整数化した値を入力させることとなるので、例えば、デューティ比として80%としたい場合には、第2の入力端子には、‘50’を入力させる。そこで、最初のカウンタ1フレーム期間においては、前述のように特定カウンタ17からの計数値を選択して出力するので、比較器15の第1の入力端子には上限カウント値、すなわち62から減算されていく値が供給される。従って、比較器15の出力は、計数値が50に減算されるまではローレベルを出力し、計数値が49に達した時点でハイレベルに変化する。また、次のカウンタ1フレーム期間においては、インバータ19からの計数値を選択して出力するので、比較器15の第1の入力端子には0から加算されていく値が供給される。従って、比較器15の出力は、計数値が50に加算されるまではハイレベルを出力し、計数値が51に達した時点でローレベルに変化する。その結果、比較器15の出力は、本発明のPWM1フレーム期間においては、図1(a)のデューティ比80%のパルス波形とほぼ同様の波形を出力することとなる。そして、以降、それを繰り返す。なお、他の設定デューティ比にした場合でも同様である。

【0035】

図4は、具体例を説明するための図である。なお、図4においては、図3に示した駆動電流制御回路の構成のうち、比較器15までの構成を省略し、代わりに、比較器15までで生成されたパルス波形を示している。

【0036】

同図に示した具体例では、出力端子2a〜2dを束ねて、抵抗成分32adを介したLED31adを接続している。そのとき、出力端子2a〜2dに対応する駆動電流制御回路1a〜1dにおいては、例えば共通の80%デューティ比のパルスを生成している。また、出力端子2e,2fの各々に関しては、他と束ねることなく、それぞれ、LED31eとLED31fを接続している。そのとき、それぞれに対応する駆動電流制御回路1e,1fにおいては、他と異なった60%と40%のデューティ比のパルスを生成している。これにより、駆動電流制御回路1a〜1dと、駆動電流制御回路1eと、駆動電流制御回路1fとの間の関係においては、デューティ比を変えることにより、同時オンによるIC内での急激な電流変化を回避し、一方、出力端子2a〜2dを束ねた駆動電流制御回路1a〜1dの互いの関係においては、デューティ比を同じにしてオン期間を一致させて個々のドライバトランジスタ16a〜16dに電流が集中してしまうことを回避している。

【0037】

なお、上述した実施形態においては、パルスの立ち上がりでドライバトランジスタがオンする構成としたが、パルスの立ち下がりでドライバトランジスタがオンする構成のものでもよい。

【0038】

また、説明の途中でも簡単に記したが、図に表された1つのLEDは、物理的な1つのLEDを必ずしも表しているのではなく、複数が縦並列的に接続されたLED群でもあり得るものである。

【0039】

更に、上述の実施形態では、駆動する対象をLEDとしたが、これに限られることはなく、例えばモータを駆動するようなドライバについても適用できる。

【0040】

本発明のドライバの一実施形態によれば、デューティ比を変えることをもってして、各ドライバトランジスタ16の同時オンを回避している。これによりドライバIC100内での急激な電流変化を回避し、ノイズの発生源を除いている。これは例えば図3に示したような簡易な回路で構成できる。

【0041】

また、いくつかの出力端子2を束ねて使用する場合には、それらに対応する駆動電流制御回路1の互いの関係においては、デューティ比を同じにしてオン期間を一致させ、個々のドライバトランジスタ16に電流が集中する瞬間が生じることを回避している。

【産業上の利用可能性】

【0042】

本発明のドライバ及びその使用方法は、遊技機、各種電飾機器、バックライト等のLEDや、モータを駆動するときに適用できる。

【符号の説明】

【0043】

100 ドライバIC

1 駆動電流制御回路

11 第1カウンタ

12 第2カウンタ

13 カウンタ選択用レジスタ

14 選択器

15 比較器

16 ドライバトランジスタ

17 特定カウンタ

18 +1加算器

19 インバータ

2 出力端子

31 LED

32 抵抗成分

1000A,1000B ドライバIC

【特許請求の範囲】

【請求項1】

駆動対象が接続される複数の出力端子と、

前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、

を備えたドライバであって、

前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させることを特徴とするドライバ。

【請求項2】

前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを特徴とする請求項1に記載のドライバ。

【請求項3】

前記複数の制御部の各々は、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させて、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスを生成することを特徴とする請求項1に記載のドライバ。

【請求項4】

前記複数の制御部の各々は、

所定の上限カウント値から下限カウント値までを減算的、かつ巡廻的に計数した第1計数値と、その計数と並行して、前記下限カウント値から前記上限カウント値までを加算的、かつ巡廻的に計数した第2計数値を並行出力する計数部と、

前記計数部からの前記第1計数値及び前記第2計数値を入力して、それらをカウンタフレーム期間ごとに切り替えて出力する選択器と、

第1の入力端子に、前記選択器から出力された計数値を入力すると共に、第2の入力端子に設定デューティ比に対応する値を入力し、それらの入力端子に入力される値を比較し、それらの値の大小に応じて、ロー/ハイレベルの信号を出力する比較器と、

前記比較器の出力信号を入力してオン/オフするトランジスタと、

を有することを特徴とする請求項3に記載のドライバ。

【請求項5】

前記計数部は、前記第1計数値を出力する第1カウンタと、前記第2計数値を出力する第2カウンタを有することを特徴とする請求項4に記載のドライバ。

【請求項6】

前記計数部は、前記第1計数値を出力する特定カウンタと、その特定カウンタからの前記第1計数値を入力して1を加算して出力する加算器と、その加算器からの値を反転し、その結果を前記第2計数値として出力するインバータとを有することを特徴とする請求項4に記載のドライバ。

【請求項7】

前記駆動対象は、発光ダイオードであることを特徴とする請求項1に記載のドライバ。

【請求項8】

前記発光ダイオードは、遊技機に使用されるものであることを特徴とする請求項7に記載のドライバ。

【請求項9】

前記複数の出力端子の各々に、複数の発光ダイオードが縦並列的に接続されることを請求項7又は8に記載のドライバ。

【請求項10】

前記駆動対象は、モータであることを特徴とする請求項1に記載のドライバ。

【請求項11】

駆動対象が接続される複数の出力端子と、

前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、

を備え、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させるドライバの使用方法であって、

前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを特徴とするドライバの使用方法。

【請求項1】

駆動対象が接続される複数の出力端子と、

前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、

を備えたドライバであって、

前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させることを特徴とするドライバ。

【請求項2】

前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを特徴とする請求項1に記載のドライバ。

【請求項3】

前記複数の制御部の各々は、パルス幅変調により生成された、1フレーム期間の頭で立ち上がる又は立ち下がる任意のデューティ比を有するパルスについて、1フレーム置きに反転させて、異なるデューティ比で、立ち上がり又は立ち下がりのタイミングの異なるパルスを生成することを特徴とする請求項1に記載のドライバ。

【請求項4】

前記複数の制御部の各々は、

所定の上限カウント値から下限カウント値までを減算的、かつ巡廻的に計数した第1計数値と、その計数と並行して、前記下限カウント値から前記上限カウント値までを加算的、かつ巡廻的に計数した第2計数値を並行出力する計数部と、

前記計数部からの前記第1計数値及び前記第2計数値を入力して、それらをカウンタフレーム期間ごとに切り替えて出力する選択器と、

第1の入力端子に、前記選択器から出力された計数値を入力すると共に、第2の入力端子に設定デューティ比に対応する値を入力し、それらの入力端子に入力される値を比較し、それらの値の大小に応じて、ロー/ハイレベルの信号を出力する比較器と、

前記比較器の出力信号を入力してオン/オフするトランジスタと、

を有することを特徴とする請求項3に記載のドライバ。

【請求項5】

前記計数部は、前記第1計数値を出力する第1カウンタと、前記第2計数値を出力する第2カウンタを有することを特徴とする請求項4に記載のドライバ。

【請求項6】

前記計数部は、前記第1計数値を出力する特定カウンタと、その特定カウンタからの前記第1計数値を入力して1を加算して出力する加算器と、その加算器からの値を反転し、その結果を前記第2計数値として出力するインバータとを有することを特徴とする請求項4に記載のドライバ。

【請求項7】

前記駆動対象は、発光ダイオードであることを特徴とする請求項1に記載のドライバ。

【請求項8】

前記発光ダイオードは、遊技機に使用されるものであることを特徴とする請求項7に記載のドライバ。

【請求項9】

前記複数の出力端子の各々に、複数の発光ダイオードが縦並列的に接続されることを請求項7又は8に記載のドライバ。

【請求項10】

前記駆動対象は、モータであることを特徴とする請求項1に記載のドライバ。

【請求項11】

駆動対象が接続される複数の出力端子と、

前記複数の出力端子の各々に対応するものであって、パルス幅変調による電流制御により前記駆動対象を駆動制御する複数の制御部と、

を備え、前記複数の制御部の相互間において、前記パルス幅変調におけるデューティ比を変えることで、前記電流制御の電流が流れ始めるタイミングを変化させるドライバの使用方法であって、

前記複数の出力端子のうちの少なくとも2つを束ねて前記駆動対象を接続する場合には、対応する複数の制御部の相互間においては、前記デューティ比を同一とすることを特徴とするドライバの使用方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−99005(P2013−99005A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−236536(P2011−236536)

【出願日】平成23年10月27日(2011.10.27)

【出願人】(398034168)株式会社アクセル (80)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【出願人】(398034168)株式会社アクセル (80)

【Fターム(参考)】

[ Back to top ]