ドライブ回路及びスイッチング電源装置

【課題】スイッチング素子の主回路電流やゲート電圧を検出することなくスイッチング素子のゲート電流を調整して、スイッチング素子のスイッチング損失を低減できるドライブ回路。

【解決手段】フィードバック信号に基づいてスイッチング素子Q1のオン期間とオフ期間とを制御する制御信号を生成する制御回路とスイッチング素子との間に接続され、スイッチング素子のゲートにゲート電流を供給するドライブ回路10であって、制御信号のオン期間におけるドライブ回路のゲート電流は、所定の期間だけ生成される第1電流成分とフィードバック信号に基づいて生成される第2電流成分との合成電流とする。

【解決手段】フィードバック信号に基づいてスイッチング素子Q1のオン期間とオフ期間とを制御する制御信号を生成する制御回路とスイッチング素子との間に接続され、スイッチング素子のゲートにゲート電流を供給するドライブ回路10であって、制御信号のオン期間におけるドライブ回路のゲート電流は、所定の期間だけ生成される第1電流成分とフィードバック信号に基づいて生成される第2電流成分との合成電流とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子をドライブするドライブ回路及びスイッチング電源装置に関する。

【背景技術】

【0002】

従来の技術として、特許文献1に記載されたスイッチング素子のゲート駆動回路が知られている。図7に、特許文献1に記載されたスイッチング素子のゲート駆動回路の一例を示す。このゲート駆動回路では、駆動・保護回路51とIGBT31のゲートとに接続されるゲート駆動回路の出力段は、ゲート抵抗41とNPNトランジスタ42とPNPトランジスタ43とにより構成されている。

【0003】

また、ゲート駆動回路には、IGBT31のゲートの電圧を判定するゲート電圧判定機52と、IGBT31の主回路に流れるIGBT電流を判定する主回路電流判定機53とが設けられている。主回路電流が大きい場合には、主回路電流判定機53により主回路電流が大きいと判定され、且つ、ゲート電圧判定機52によりゲート電圧がミラー期間の間に、PMOSFET44をオンさせることで、ゲート抵抗を小さくし、ゲート電流を制御している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−228447号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、図7に示す特許文献1に記載の例では、スイッチング素子の主回路電流やゲート電圧を検出し、その検出値に基づいてゲート電流を調整し、スイッチング素子のスイッチング損失を低減している。このため、スイッチング素子の主回路電流やゲート電圧を検出する手段が必要である。

【0006】

本発明の課題は、スイッチング素子の主回路電流やゲート電圧を検出することなくスイッチング素子のゲート電流を調整して、スイッチング素子のスイッチング損失を低減することができるドライブ回路及びスイッチング電源装置を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のドライブ回路は、フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路であって、前記制御信号の前記オン期間における前記ドライブ回路の前記ゲート電流は、所定の期間だけ生成される第1電流成分と前記フィードバック信号に基づいて生成される第2電流成分との合成電流とすることを特徴とする。

【0008】

本発明のスイッチング電源装置は、直流電源の直流電圧を断続してトランスの一次巻線に供給するスイッチング素子と、前記トランスの二次巻線に発生した電圧を整流平滑する整流平滑回路と、前記整流平滑回路の出力電圧を示す信号をフィードバック信号とし、前記フィードバック信号に基づいて前記スイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と、前記制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路と、を有し、前記ドライブ回路は、請求項1乃至請求項4のいずれか1項記載のドライブ回路であることを特徴とする。

【発明の効果】

【0009】

本発明によれば、フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号のオン期間におけるゲート電流を、所定の期間だけ生成される第1電流成分とフィードバック信号に基づいて生成される第2電流成分との合成電流とすることにより、スイッチング素子のスイッチング損失を低減することができるドライブ回路及びスイッチング電源装置を提供することができる。

【図面の簡単な説明】

【0010】

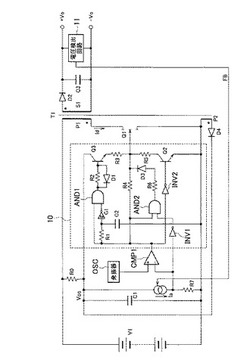

【図1】実施例1のドライブ回路を有するスイッチング電源装置の構成図である。

【図2】実施例1のドライブ回路の各部の動作波形を示す図である。

【図3】実施例2のドライブ回路を有するスイッチング電源装置の構成図である。

【図4】実施例2のドライブ回路の各部の動作波形を示す図である。

【図5】実施例3のドライブ回路を有するスイッチング電源装置の構成図である。

【図6】実施例3のドライブ回路の各部の動作波形を示す図である。

【図7】従来のスイッチング素子のゲート駆動回路の一例を示す構成図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態のドライブ回路及びスイッチング電源装置を図面を参照しながら詳細に説明する。

【0012】

本発明のドライブ回路は、フィードバック信号の信号値に応じて、スイッチング素子のゲート電流を調整することにより、スイッチング素子のスイッチング損失を低減することを特徴とするもので、この方法として、以下の3つの実施例を説明する。

【実施例1】

【0013】

図1は、実施例1のドライブ回路を有するスイッチング電源装置の構成図である。実施例1のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値により抵抗R6が選択されて、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0014】

図1に示すスイッチング電源装置において、直流電源V1の両端には、トランスT1の一次巻線P1と窒化ガリウム(GaN)デバイスのGaNFETからなるスイッチング素子Q1との直列回路が接続されている。

【0015】

トランスT1の二次巻線S1の一端にはダイオードD2のアノードが接続され、ダイオードD2のカソードとコンデンサC3の一端とは出力端子の一端(+Vo)に接続され、コンデンサC3の他端は、出力端子の他端(−Vo)と二次巻線S1の他端に接続されている。ダイオードD2とコンデンサC3とは、整流平滑回路を構成している。出力端子(+Vo,−Vo)には、図示しない負荷が接続されている。

【0016】

トランスT1の補助巻線P2の一端にはダイオードD4のアノードが接続され、ダイオードD4のカソードはコンデンサC1の一端に接続され、補助巻線P2の他端は、コンデンサC1の他端と直流電源V1の負極に接続されている。

【0017】

直流電源V1の正極とコンデンサC1の一端との間には起動抵抗R0が接続されている。コンデンサC1の両端には、電流源Iaと抵抗R7との直列回路が接続されるとともに、トランジスタQ3と抵抗R3と抵抗R5とトランジスタQ2との直列回路が接続されている。

【0018】

電圧検出回路11は、コンデンサC3の出力電圧を検出し、その出力電圧を示す信号をフィードバック信号FBとして電流源Iaに出力し、フィードバック信号FBの電流値(フィードバック電流IFB)に応じて電流源Iaの電流値を可変させる。

【0019】

電流源Iaと抵抗R7との接続点にはコンパレータCMP1の反転入力端子(−)が接続され、コンパレータCMP1の非反転入力端子(+)には発振器OSCが接続されている。発振器OSCは、三角波信号を発生し、三角波信号をコンパレータCMP1に出力する。

【0020】

コンパレータCMP1は、発振器OSCからの三角波信号と、抵抗R7に流れるフィードバック信号FBに応じた電流により発生する電圧(フィードバック電圧)とを比較することにより、フィードバック信号FBに応じてオン期間を可変した制御信号を生成する。

【0021】

コンパレータCMP1の出力端子は、抵抗R4を介して抵抗R3と抵抗R5との接続点とスイッチング素子Q1のゲート(制御端子)とに接続されている。コンパレータCMP1の出力端子は、インバータINV2を介してトランジスタQ2のベースに接続されている。コンパレータCMP1の出力端子は、アンド回路AND1の一方の入力端子とアンド回路AND2の一方の入力端子と抵抗R1の一端とに接続されている。

【0022】

電流源Iaと抵抗R7との接続点は、インバータINV1を介してアンド回路AND2の他方の入力端子に接続され、アンド回路AND2の出力端子は抵抗R6とダイオードD3を介してスイッチング素子Q1のゲートに接続されている。

【0023】

抵抗R1の他端はコンデンサC2の一端とインバータG1を介してアンド回路AND1の他方の入力端子とに接続され、アンド回路AND1の出力端子は抵抗R2とダイオードD1との並列回路を介してトランジスタQ3のベースに接続されている。

【0024】

なお、電圧検出回路11、電流源Ia、抵抗R7、発振器OSC及びコンパレータCMP1は、スイッチング素子Q1のオン期間(ton)とオフ期間(toff)とを制御する制御信号を生成する制御回路を構成する。また、抵抗R1〜R3、コンデンサC2、インバータG1、アンド回路AND1、ダイオードD1及びトランジスタQ3は、オン期間よりも短い所定の期間、例えば、スイッチング素子Q1のゲート電圧がゲート閾値電圧に上昇するまでの期間を予め設定し、その設定期間だけ第1電流成分を生成する第1電流成分生成回路を構成し、インバータINV1、アンド回路AND2、抵抗R6、ダイオードD3及び抵抗R4は、フィードバック電流IFBに基づいて第2電流成分を生成する第2電流成分生成回路を構成し、インバータINV2、トランジスタQ2及び抵抗R5は、オフ期間のゲート電流を生成するオフゲート電流生成回路を構成する。ドライブ回路10は、第1電流成分生成回路、第2電流成分生成回路及びオフゲート電流生成回路で構成される。なお、第1電流成分生成回路及び第2電流成分生成回路によって、オン期間のゲート電流を生成するオンゲート電流生成回路を構成している。

【0025】

次にこのように構成された実施例1のドライブ回路及びスイッチング電源装置の動作を図2に示す動作波形を参照しながら、詳細に説明する。

【0026】

まず、重負荷時(時刻t7以前)には、図2に示すように、電圧検出回路11からのフィードバック電流IFBが小さくなる。

【0027】

フィードバック電流IFBは、抵抗R7によりフィードバック電圧に変換され、フィードバック電圧と三角波信号とがコンパレータCMP1で比較されてHレベルの出力がアンド回路AND1に出力されると、時刻t1において、トランジスタQ3がオンする。

【0028】

また、フィードバック電圧がインバータINV1の閾値電圧未満であるので、インバータINV1の出力はHレベルとなる。このHレベルの出力がアンド回路AND2に入力されると、アンド回路AND2はHレベルを出力するので、ダイオードD3が導通する。このため、スイッチング素子Q1のゲート電流Ig1は、抵抗R3に流れる電流と抵抗R4に流れる電流と抵抗R6に流れる電流との合成電流になる。抵抗R3に流れる電流が第1電流成分に対応し、抵抗R4,R6に流れる電流の合計が第2電流成分に対応する。

【0029】

次に、時刻t2において、コンデンサC2の電圧がインバータG1の閾値電圧を超えると、インバータG1はLレベルの出力をアンド回路AND1に出力するので、アンド回路AND1の出力がLレベルとなり、トランジスタQ3がオフする。このため、スイッチング素子Q1のゲート電流Ig2は、抵抗R4に流れる電流と抵抗R6に流れる電流との合成電流になる。

【0030】

並列回路の合成抵抗は、抵抗R4より小さくなる。このため、時刻t2〜t3においては、抵抗R4だけの時と比べ大きなゲート電流Ig2がスイッチング素子Q1のゲート電流となる。

【0031】

次に、時刻t3〜t4において、コンパレータCMP1がLレベルを出力すると、このLレベルの出力により、インバータINV2はHレベルを出力するので、トランジスタQ2がオンし、スイッチング素子Q1のゲート電流はゼロとなる。時刻t4〜t6においても重負荷時の動作である。

【0032】

次に、軽負荷時(時刻t7以降)になると、図2に示すように、電圧検出回路11からのフィードバック電流IFBが大きくなる。このフィードバック電流IFBは、抵抗R7によりフィードバック電圧に変換され、フィードバック電圧と三角波信号とがコンパレータCMP1で比較されてHレベルの出力がアンド回路AND1に出力されると、時刻t8において、トランジスタQ3がオンする。

【0033】

また、フィードバック電圧がインバータINV1の閾値電圧を超えているので、インバータINV1の出力はLレベルとなる。このLレベルの出力がアンド回路AND2に入力されると、アンド回路AND2の出力はLレベルとなるため、抵抗R6とダイオードD3との直列回路は開放状態となる。

【0034】

このため、スイッチング素子Q1のゲート電流Ig3は、抵抗R3に流れる電流と抵抗R4に流れる電流との合成電流になる。

【0035】

次に、時刻t9において、コンデンサC2の電圧がインバータG1の閾値電圧を超えると、インバータG1はLレベルの出力をアンド回路AND1に出力するので、アンド回路AND1の出力がLレベルとなり、トランジスタQ3がオフする。このため、スイッチング素子Q1のゲート電流Ig4は、抵抗R4に流れる電流になる。時刻t9〜t10におけるゲート電流Ig4は時刻t2〜t3におけるゲート電流Ig2よりも小さくなる。

【0036】

このように、実施例1のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値により抵抗R6が選択されて、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0037】

また、実施例1のスイッチング電源装置によれば、ドライブ回路の効果が得られるとともに、直流電源V1の直流電圧をトランスT1の一次巻線P1を介してスイッチング素子Q1によりオン/オフさせ、二次巻線S1に発生した電圧をダイオードD2とコンデンサC3とで整流平滑して、安定した直流出力電圧を得ることができる。また、補助巻線P2に発生した電圧をダイオードD4とコンデンサC1とで整流平滑して、制御回路及びドライブ回路10の電源として供給することができる。

【実施例2】

【0038】

図3は、実施例2のドライブ回路を有するスイッチング電源装置の構成図である。図3に示す実施例2のドライブ回路は、図1に示すドライブ回路に対して、以下の点が異なる。図1に示すインバータINV1、アンド回路AND2、抵抗R4,R6、ダイオードD3を削除し、代わりに、インバータINV3、ダイオードD5、抵抗R8,R9、トランジスタQ4〜Q6、コンデンサC4を設けたことを特徴とする。

【0039】

実施例2のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値により時定数回路が作動して、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0040】

コンパレータCMP1の出力端子には、インバータINV3を介してダイオードD5と抵抗R8との並列回路の一端が接続され、この並列回路の他端は、コンデンサC4を介して直流電源V1の負極に接続されるとともに、抵抗R9の一端に接続されている。

【0041】

トランジスタQ4のソースとトランジスタQ5,Q6のエミッタとはコンデンサC1の一端に接続されている。

【0042】

トランジスタQ4のゲートはコンパレータCMP1の出力端子に接続され、トランジスタQ4のドレインとトランジスタQ5のコレクタとトランジスタQ5,Q6のベースとは抵抗R9の他端に接続されている。トランジスタQ6のコレクタは、抵抗R5を介してトランジスタQ2のコレクタに接続されている。

【0043】

トランジスタQ4は、スイッチング素子Q1のオフ期間にはカレントミラー回路Q5,Q6が動作しないようにするスイッチの働きを有する。

【0044】

次にこのように構成された実施例2のドライブ回路及びスイッチング電源装置の動作を図4に示す動作波形を参照しながら、詳細に説明する。

【0045】

まず、スイッチング素子Q1のターンオン時、即ち、時刻t1には、コンパレータCMP1の出力はHレベルとなり、トランジスタQ3がオンし、スイッチング素子Q1のゲートにゲート電流が流れる。

【0046】

また、インバータINV3の出力がLレベルとなるので、コンデンサC4と抵抗R8との時定数回路で決定される時定数でコンデンサC4が放電して、コンデンサC4の両端電圧Vc4が低下していく。

【0047】

このため、電圧Vc4とトランジスタQ5のコレクタとの間の電圧が変化することにより、抵抗R9を流れる電流Icの値が可変する。この例では、時刻t1〜時刻t3において、電流Icが増加していく。この可変した電流Icをカレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに供給する。スイッチング素子Q1のオン期間が短い時には、カレントミラー回路Q5,Q6を介したベース電流は小さくなり、ドライブ回路10aの電力を低減させることができる。トランジスタQ6のコレクタ電流が第2電流成分に対応する。なお、時刻t2において、トランジスタQ3がオフする。

【0048】

次に、スイッチング素子Q1のターンオフ時には、即ち、時刻t3には、コンパレータCMP1の出力はLレベルとなり、カレントミラー回路Q5,Q6は、動作を停止する。また、インバータINV3の出力は、Hレベルとなるので、コンデンサC4はダイオードD5を介して充電されていく。このため、トランジスタQ5と抵抗R9とを介してコンデンサC4を流れる電流Icは殆どゼロとなる。

【0049】

なお、スイッチング素子Q1のゲート電流において、時刻t1〜t3では、重負荷時のゲート電流を示し、時刻t4〜t6では、中負荷時のゲート電流を示し、時刻t7〜t9では、軽負荷時のゲート電流を示している。重負荷から軽負荷になるに連れて、フィードバック電流IFBが大きくなるので、抵抗R7の両端に発生する電圧が大きくなる。

【0050】

このため、コンパレータCMP1から出力される制御信号のオン期間(ton)が短くなり、コンデンサC4の放電時間が短くなるため、電流Icが小さくなり、ゲート電流が小さくなる。

【0051】

このように、実施例2のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値により時定数回路(R8,C4)が作動して、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0052】

また、実施例2のスイッチング電源装置によれば、実施例1のスイッチング電源装置と同様な効果が得られる。

【実施例3】

【0053】

図5は、実施例3のドライブ回路を有するスイッチング電源装置の構成図である。図5に示す実施例3のドライブ回路は、図3に示すドライブ回路に対して、以下の点が異なる。図3に示すインバータINV3、ダイオードD5、抵抗R8、コンデンサC4を削除し、代わりに、電流源Ib、抵抗R10,R11を設けたことを特徴とする。

【0054】

実施例3のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値に反比例して、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0055】

電流源Ibは、電圧検出回路11からのフィードバック信号FBの信号値に応じて電流を可変させる。電流源Ibの一端には電源Vccが接続され、電流源Ibの他端は抵抗R11を介して抵抗R9の一端と抵抗R10の一端に接続され、抵抗R10の他端は直流電源V1の負極に接続されている。

【0056】

次にこのように構成された実施例3のドライブ回路及びスイッチング電源装置の動作を図6に示す動作波形を参照しながら、詳細に説明する。

【0057】

図6に示すスイッチング素子Q1のゲート電流において、時刻t1〜t3では、重負荷時のゲート電流を示し、時刻t5〜t7では、中負荷時のゲート電流を示し、時刻t9〜t11では、軽負荷時のゲート電流を示している。

【0058】

まず、電圧検出回路11からのフィードバック電流IFBを抵抗R7により電圧に変換する。

【0059】

重負荷時(時刻t1〜t3)には、フィードバック電流IFBが小さいので、抵抗R7における電圧降下がより小さくなる。また、フィードバック電流IFBが小さいので、電流源Ibには、より小さい電流が流れる。このため、電流源Ibから抵抗R11を介して抵抗R10に流れる電流が小さいため、抵抗R10の両端電圧は小さくなる。このため、抵抗R9の両端電圧はより大きくなるので、カレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに流れるゲート電流が大きくなる。

【0060】

また、軽負荷時(時刻t9〜t11)には、フィードバック電流IFBが大きいので、抵抗R7における電圧降下がより大きくなる。また、フィードバック電流IFBが大きいので、電流源Ibには、より大きい電流が流れる。このため、電流源Ibから抵抗R11を介して抵抗R10に流れる電流が大きくなるため、抵抗R10の両端電圧は大きくなる。このため、抵抗R9の両端電圧はより小さくなるので、カレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに流れるゲート電流が小さくなる。

【0061】

なお、時刻t1〜t2、時刻t5〜t6、時刻t9〜t10におけるゲート電流には、トランジスタQ3に流れる電流が重畳されている。

【0062】

このように、実施例3のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値に反比例して、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0063】

また、実施例3のスイッチング電源装置によれば、実施例1のスイッチング電源装置と同様な効果が得られる。

【0064】

なお、本発明は、上述した実施例1乃至3のドライブ回路及びスイッチング電源装置に限定されるものではない。実施例1乃至3では、スイッチング電源装置としてフライバックコンバータを例示したが、本発明は、例えばフォワードコンバータ、共振型コンバータにも適用可能である。

【0065】

また、本発明は、昇圧チョッパ回路、降圧チョッパ回路、同期整流回路等にも適用可能である。

【0066】

また、実施例1乃至3では、フライバックコンバータの出力電圧を示す信号が負荷の軽重を示す信号にもなることからフィードバック信号としたが、本発明は、スイッチング素子のオン期間とオフ期間とを制御する制御信号が生成できるような信号であれば、フィードバック信号とすることができる。

【産業上の利用可能性】

【0067】

本発明は、電源装置に適用可能である。

【符号の説明】

【0068】

V1 直流電源

T1 トランス

P1 一次巻線

P2 補助巻線

S1 二次巻線

Q1 スイッチング素子

Q2〜Q6 トランジスタ

OSC 発振器

INV1,INV2,INV3,G1 インバータ

Ia,Ib 電流源

CMP1 コンパレータ

D1〜D5 ダイオード

C1〜C4 コンデンサ

R0 起動抵抗

R1〜R11 抵抗

10.10a,10b ドライブ回路

11 電圧検出回路

AND1,AND2 アンド回路

【技術分野】

【0001】

本発明は、半導体スイッチング素子をドライブするドライブ回路及びスイッチング電源装置に関する。

【背景技術】

【0002】

従来の技術として、特許文献1に記載されたスイッチング素子のゲート駆動回路が知られている。図7に、特許文献1に記載されたスイッチング素子のゲート駆動回路の一例を示す。このゲート駆動回路では、駆動・保護回路51とIGBT31のゲートとに接続されるゲート駆動回路の出力段は、ゲート抵抗41とNPNトランジスタ42とPNPトランジスタ43とにより構成されている。

【0003】

また、ゲート駆動回路には、IGBT31のゲートの電圧を判定するゲート電圧判定機52と、IGBT31の主回路に流れるIGBT電流を判定する主回路電流判定機53とが設けられている。主回路電流が大きい場合には、主回路電流判定機53により主回路電流が大きいと判定され、且つ、ゲート電圧判定機52によりゲート電圧がミラー期間の間に、PMOSFET44をオンさせることで、ゲート抵抗を小さくし、ゲート電流を制御している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−228447号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、図7に示す特許文献1に記載の例では、スイッチング素子の主回路電流やゲート電圧を検出し、その検出値に基づいてゲート電流を調整し、スイッチング素子のスイッチング損失を低減している。このため、スイッチング素子の主回路電流やゲート電圧を検出する手段が必要である。

【0006】

本発明の課題は、スイッチング素子の主回路電流やゲート電圧を検出することなくスイッチング素子のゲート電流を調整して、スイッチング素子のスイッチング損失を低減することができるドライブ回路及びスイッチング電源装置を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のドライブ回路は、フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路であって、前記制御信号の前記オン期間における前記ドライブ回路の前記ゲート電流は、所定の期間だけ生成される第1電流成分と前記フィードバック信号に基づいて生成される第2電流成分との合成電流とすることを特徴とする。

【0008】

本発明のスイッチング電源装置は、直流電源の直流電圧を断続してトランスの一次巻線に供給するスイッチング素子と、前記トランスの二次巻線に発生した電圧を整流平滑する整流平滑回路と、前記整流平滑回路の出力電圧を示す信号をフィードバック信号とし、前記フィードバック信号に基づいて前記スイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と、前記制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路と、を有し、前記ドライブ回路は、請求項1乃至請求項4のいずれか1項記載のドライブ回路であることを特徴とする。

【発明の効果】

【0009】

本発明によれば、フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号のオン期間におけるゲート電流を、所定の期間だけ生成される第1電流成分とフィードバック信号に基づいて生成される第2電流成分との合成電流とすることにより、スイッチング素子のスイッチング損失を低減することができるドライブ回路及びスイッチング電源装置を提供することができる。

【図面の簡単な説明】

【0010】

【図1】実施例1のドライブ回路を有するスイッチング電源装置の構成図である。

【図2】実施例1のドライブ回路の各部の動作波形を示す図である。

【図3】実施例2のドライブ回路を有するスイッチング電源装置の構成図である。

【図4】実施例2のドライブ回路の各部の動作波形を示す図である。

【図5】実施例3のドライブ回路を有するスイッチング電源装置の構成図である。

【図6】実施例3のドライブ回路の各部の動作波形を示す図である。

【図7】従来のスイッチング素子のゲート駆動回路の一例を示す構成図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態のドライブ回路及びスイッチング電源装置を図面を参照しながら詳細に説明する。

【0012】

本発明のドライブ回路は、フィードバック信号の信号値に応じて、スイッチング素子のゲート電流を調整することにより、スイッチング素子のスイッチング損失を低減することを特徴とするもので、この方法として、以下の3つの実施例を説明する。

【実施例1】

【0013】

図1は、実施例1のドライブ回路を有するスイッチング電源装置の構成図である。実施例1のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値により抵抗R6が選択されて、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0014】

図1に示すスイッチング電源装置において、直流電源V1の両端には、トランスT1の一次巻線P1と窒化ガリウム(GaN)デバイスのGaNFETからなるスイッチング素子Q1との直列回路が接続されている。

【0015】

トランスT1の二次巻線S1の一端にはダイオードD2のアノードが接続され、ダイオードD2のカソードとコンデンサC3の一端とは出力端子の一端(+Vo)に接続され、コンデンサC3の他端は、出力端子の他端(−Vo)と二次巻線S1の他端に接続されている。ダイオードD2とコンデンサC3とは、整流平滑回路を構成している。出力端子(+Vo,−Vo)には、図示しない負荷が接続されている。

【0016】

トランスT1の補助巻線P2の一端にはダイオードD4のアノードが接続され、ダイオードD4のカソードはコンデンサC1の一端に接続され、補助巻線P2の他端は、コンデンサC1の他端と直流電源V1の負極に接続されている。

【0017】

直流電源V1の正極とコンデンサC1の一端との間には起動抵抗R0が接続されている。コンデンサC1の両端には、電流源Iaと抵抗R7との直列回路が接続されるとともに、トランジスタQ3と抵抗R3と抵抗R5とトランジスタQ2との直列回路が接続されている。

【0018】

電圧検出回路11は、コンデンサC3の出力電圧を検出し、その出力電圧を示す信号をフィードバック信号FBとして電流源Iaに出力し、フィードバック信号FBの電流値(フィードバック電流IFB)に応じて電流源Iaの電流値を可変させる。

【0019】

電流源Iaと抵抗R7との接続点にはコンパレータCMP1の反転入力端子(−)が接続され、コンパレータCMP1の非反転入力端子(+)には発振器OSCが接続されている。発振器OSCは、三角波信号を発生し、三角波信号をコンパレータCMP1に出力する。

【0020】

コンパレータCMP1は、発振器OSCからの三角波信号と、抵抗R7に流れるフィードバック信号FBに応じた電流により発生する電圧(フィードバック電圧)とを比較することにより、フィードバック信号FBに応じてオン期間を可変した制御信号を生成する。

【0021】

コンパレータCMP1の出力端子は、抵抗R4を介して抵抗R3と抵抗R5との接続点とスイッチング素子Q1のゲート(制御端子)とに接続されている。コンパレータCMP1の出力端子は、インバータINV2を介してトランジスタQ2のベースに接続されている。コンパレータCMP1の出力端子は、アンド回路AND1の一方の入力端子とアンド回路AND2の一方の入力端子と抵抗R1の一端とに接続されている。

【0022】

電流源Iaと抵抗R7との接続点は、インバータINV1を介してアンド回路AND2の他方の入力端子に接続され、アンド回路AND2の出力端子は抵抗R6とダイオードD3を介してスイッチング素子Q1のゲートに接続されている。

【0023】

抵抗R1の他端はコンデンサC2の一端とインバータG1を介してアンド回路AND1の他方の入力端子とに接続され、アンド回路AND1の出力端子は抵抗R2とダイオードD1との並列回路を介してトランジスタQ3のベースに接続されている。

【0024】

なお、電圧検出回路11、電流源Ia、抵抗R7、発振器OSC及びコンパレータCMP1は、スイッチング素子Q1のオン期間(ton)とオフ期間(toff)とを制御する制御信号を生成する制御回路を構成する。また、抵抗R1〜R3、コンデンサC2、インバータG1、アンド回路AND1、ダイオードD1及びトランジスタQ3は、オン期間よりも短い所定の期間、例えば、スイッチング素子Q1のゲート電圧がゲート閾値電圧に上昇するまでの期間を予め設定し、その設定期間だけ第1電流成分を生成する第1電流成分生成回路を構成し、インバータINV1、アンド回路AND2、抵抗R6、ダイオードD3及び抵抗R4は、フィードバック電流IFBに基づいて第2電流成分を生成する第2電流成分生成回路を構成し、インバータINV2、トランジスタQ2及び抵抗R5は、オフ期間のゲート電流を生成するオフゲート電流生成回路を構成する。ドライブ回路10は、第1電流成分生成回路、第2電流成分生成回路及びオフゲート電流生成回路で構成される。なお、第1電流成分生成回路及び第2電流成分生成回路によって、オン期間のゲート電流を生成するオンゲート電流生成回路を構成している。

【0025】

次にこのように構成された実施例1のドライブ回路及びスイッチング電源装置の動作を図2に示す動作波形を参照しながら、詳細に説明する。

【0026】

まず、重負荷時(時刻t7以前)には、図2に示すように、電圧検出回路11からのフィードバック電流IFBが小さくなる。

【0027】

フィードバック電流IFBは、抵抗R7によりフィードバック電圧に変換され、フィードバック電圧と三角波信号とがコンパレータCMP1で比較されてHレベルの出力がアンド回路AND1に出力されると、時刻t1において、トランジスタQ3がオンする。

【0028】

また、フィードバック電圧がインバータINV1の閾値電圧未満であるので、インバータINV1の出力はHレベルとなる。このHレベルの出力がアンド回路AND2に入力されると、アンド回路AND2はHレベルを出力するので、ダイオードD3が導通する。このため、スイッチング素子Q1のゲート電流Ig1は、抵抗R3に流れる電流と抵抗R4に流れる電流と抵抗R6に流れる電流との合成電流になる。抵抗R3に流れる電流が第1電流成分に対応し、抵抗R4,R6に流れる電流の合計が第2電流成分に対応する。

【0029】

次に、時刻t2において、コンデンサC2の電圧がインバータG1の閾値電圧を超えると、インバータG1はLレベルの出力をアンド回路AND1に出力するので、アンド回路AND1の出力がLレベルとなり、トランジスタQ3がオフする。このため、スイッチング素子Q1のゲート電流Ig2は、抵抗R4に流れる電流と抵抗R6に流れる電流との合成電流になる。

【0030】

並列回路の合成抵抗は、抵抗R4より小さくなる。このため、時刻t2〜t3においては、抵抗R4だけの時と比べ大きなゲート電流Ig2がスイッチング素子Q1のゲート電流となる。

【0031】

次に、時刻t3〜t4において、コンパレータCMP1がLレベルを出力すると、このLレベルの出力により、インバータINV2はHレベルを出力するので、トランジスタQ2がオンし、スイッチング素子Q1のゲート電流はゼロとなる。時刻t4〜t6においても重負荷時の動作である。

【0032】

次に、軽負荷時(時刻t7以降)になると、図2に示すように、電圧検出回路11からのフィードバック電流IFBが大きくなる。このフィードバック電流IFBは、抵抗R7によりフィードバック電圧に変換され、フィードバック電圧と三角波信号とがコンパレータCMP1で比較されてHレベルの出力がアンド回路AND1に出力されると、時刻t8において、トランジスタQ3がオンする。

【0033】

また、フィードバック電圧がインバータINV1の閾値電圧を超えているので、インバータINV1の出力はLレベルとなる。このLレベルの出力がアンド回路AND2に入力されると、アンド回路AND2の出力はLレベルとなるため、抵抗R6とダイオードD3との直列回路は開放状態となる。

【0034】

このため、スイッチング素子Q1のゲート電流Ig3は、抵抗R3に流れる電流と抵抗R4に流れる電流との合成電流になる。

【0035】

次に、時刻t9において、コンデンサC2の電圧がインバータG1の閾値電圧を超えると、インバータG1はLレベルの出力をアンド回路AND1に出力するので、アンド回路AND1の出力がLレベルとなり、トランジスタQ3がオフする。このため、スイッチング素子Q1のゲート電流Ig4は、抵抗R4に流れる電流になる。時刻t9〜t10におけるゲート電流Ig4は時刻t2〜t3におけるゲート電流Ig2よりも小さくなる。

【0036】

このように、実施例1のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値により抵抗R6が選択されて、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0037】

また、実施例1のスイッチング電源装置によれば、ドライブ回路の効果が得られるとともに、直流電源V1の直流電圧をトランスT1の一次巻線P1を介してスイッチング素子Q1によりオン/オフさせ、二次巻線S1に発生した電圧をダイオードD2とコンデンサC3とで整流平滑して、安定した直流出力電圧を得ることができる。また、補助巻線P2に発生した電圧をダイオードD4とコンデンサC1とで整流平滑して、制御回路及びドライブ回路10の電源として供給することができる。

【実施例2】

【0038】

図3は、実施例2のドライブ回路を有するスイッチング電源装置の構成図である。図3に示す実施例2のドライブ回路は、図1に示すドライブ回路に対して、以下の点が異なる。図1に示すインバータINV1、アンド回路AND2、抵抗R4,R6、ダイオードD3を削除し、代わりに、インバータINV3、ダイオードD5、抵抗R8,R9、トランジスタQ4〜Q6、コンデンサC4を設けたことを特徴とする。

【0039】

実施例2のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値により時定数回路が作動して、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0040】

コンパレータCMP1の出力端子には、インバータINV3を介してダイオードD5と抵抗R8との並列回路の一端が接続され、この並列回路の他端は、コンデンサC4を介して直流電源V1の負極に接続されるとともに、抵抗R9の一端に接続されている。

【0041】

トランジスタQ4のソースとトランジスタQ5,Q6のエミッタとはコンデンサC1の一端に接続されている。

【0042】

トランジスタQ4のゲートはコンパレータCMP1の出力端子に接続され、トランジスタQ4のドレインとトランジスタQ5のコレクタとトランジスタQ5,Q6のベースとは抵抗R9の他端に接続されている。トランジスタQ6のコレクタは、抵抗R5を介してトランジスタQ2のコレクタに接続されている。

【0043】

トランジスタQ4は、スイッチング素子Q1のオフ期間にはカレントミラー回路Q5,Q6が動作しないようにするスイッチの働きを有する。

【0044】

次にこのように構成された実施例2のドライブ回路及びスイッチング電源装置の動作を図4に示す動作波形を参照しながら、詳細に説明する。

【0045】

まず、スイッチング素子Q1のターンオン時、即ち、時刻t1には、コンパレータCMP1の出力はHレベルとなり、トランジスタQ3がオンし、スイッチング素子Q1のゲートにゲート電流が流れる。

【0046】

また、インバータINV3の出力がLレベルとなるので、コンデンサC4と抵抗R8との時定数回路で決定される時定数でコンデンサC4が放電して、コンデンサC4の両端電圧Vc4が低下していく。

【0047】

このため、電圧Vc4とトランジスタQ5のコレクタとの間の電圧が変化することにより、抵抗R9を流れる電流Icの値が可変する。この例では、時刻t1〜時刻t3において、電流Icが増加していく。この可変した電流Icをカレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに供給する。スイッチング素子Q1のオン期間が短い時には、カレントミラー回路Q5,Q6を介したベース電流は小さくなり、ドライブ回路10aの電力を低減させることができる。トランジスタQ6のコレクタ電流が第2電流成分に対応する。なお、時刻t2において、トランジスタQ3がオフする。

【0048】

次に、スイッチング素子Q1のターンオフ時には、即ち、時刻t3には、コンパレータCMP1の出力はLレベルとなり、カレントミラー回路Q5,Q6は、動作を停止する。また、インバータINV3の出力は、Hレベルとなるので、コンデンサC4はダイオードD5を介して充電されていく。このため、トランジスタQ5と抵抗R9とを介してコンデンサC4を流れる電流Icは殆どゼロとなる。

【0049】

なお、スイッチング素子Q1のゲート電流において、時刻t1〜t3では、重負荷時のゲート電流を示し、時刻t4〜t6では、中負荷時のゲート電流を示し、時刻t7〜t9では、軽負荷時のゲート電流を示している。重負荷から軽負荷になるに連れて、フィードバック電流IFBが大きくなるので、抵抗R7の両端に発生する電圧が大きくなる。

【0050】

このため、コンパレータCMP1から出力される制御信号のオン期間(ton)が短くなり、コンデンサC4の放電時間が短くなるため、電流Icが小さくなり、ゲート電流が小さくなる。

【0051】

このように、実施例2のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値により時定数回路(R8,C4)が作動して、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0052】

また、実施例2のスイッチング電源装置によれば、実施例1のスイッチング電源装置と同様な効果が得られる。

【実施例3】

【0053】

図5は、実施例3のドライブ回路を有するスイッチング電源装置の構成図である。図5に示す実施例3のドライブ回路は、図3に示すドライブ回路に対して、以下の点が異なる。図3に示すインバータINV3、ダイオードD5、抵抗R8、コンデンサC4を削除し、代わりに、電流源Ib、抵抗R10,R11を設けたことを特徴とする。

【0054】

実施例3のドライブ回路では、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとしている。このフィードバック信号FBの信号値に反比例して、スイッチング素子Q1のゲート電流が調整されることを特徴とする。また、スイッチング素子Q1のオン期間とオフ期間とを制御する制御信号はフィードバック信号FBに基づいて生成される。

【0055】

電流源Ibは、電圧検出回路11からのフィードバック信号FBの信号値に応じて電流を可変させる。電流源Ibの一端には電源Vccが接続され、電流源Ibの他端は抵抗R11を介して抵抗R9の一端と抵抗R10の一端に接続され、抵抗R10の他端は直流電源V1の負極に接続されている。

【0056】

次にこのように構成された実施例3のドライブ回路及びスイッチング電源装置の動作を図6に示す動作波形を参照しながら、詳細に説明する。

【0057】

図6に示すスイッチング素子Q1のゲート電流において、時刻t1〜t3では、重負荷時のゲート電流を示し、時刻t5〜t7では、中負荷時のゲート電流を示し、時刻t9〜t11では、軽負荷時のゲート電流を示している。

【0058】

まず、電圧検出回路11からのフィードバック電流IFBを抵抗R7により電圧に変換する。

【0059】

重負荷時(時刻t1〜t3)には、フィードバック電流IFBが小さいので、抵抗R7における電圧降下がより小さくなる。また、フィードバック電流IFBが小さいので、電流源Ibには、より小さい電流が流れる。このため、電流源Ibから抵抗R11を介して抵抗R10に流れる電流が小さいため、抵抗R10の両端電圧は小さくなる。このため、抵抗R9の両端電圧はより大きくなるので、カレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに流れるゲート電流が大きくなる。

【0060】

また、軽負荷時(時刻t9〜t11)には、フィードバック電流IFBが大きいので、抵抗R7における電圧降下がより大きくなる。また、フィードバック電流IFBが大きいので、電流源Ibには、より大きい電流が流れる。このため、電流源Ibから抵抗R11を介して抵抗R10に流れる電流が大きくなるため、抵抗R10の両端電圧は大きくなる。このため、抵抗R9の両端電圧はより小さくなるので、カレントミラー回路Q5,Q6を介してスイッチング素子Q1のゲートに流れるゲート電流が小さくなる。

【0061】

なお、時刻t1〜t2、時刻t5〜t6、時刻t9〜t10におけるゲート電流には、トランジスタQ3に流れる電流が重畳されている。

【0062】

このように、実施例3のドライブ回路によれば、トランスT1の二次巻線S1に発生した電圧を整流平滑する整流平滑回路の出力電圧を示す信号をフィードバック信号FBとし、このフィードバック信号FBの信号値に反比例して、スイッチング素子Q1のゲート電流が調整されることにより、スイッチング素子のスイッチング損失を低減することができる。

【0063】

また、実施例3のスイッチング電源装置によれば、実施例1のスイッチング電源装置と同様な効果が得られる。

【0064】

なお、本発明は、上述した実施例1乃至3のドライブ回路及びスイッチング電源装置に限定されるものではない。実施例1乃至3では、スイッチング電源装置としてフライバックコンバータを例示したが、本発明は、例えばフォワードコンバータ、共振型コンバータにも適用可能である。

【0065】

また、本発明は、昇圧チョッパ回路、降圧チョッパ回路、同期整流回路等にも適用可能である。

【0066】

また、実施例1乃至3では、フライバックコンバータの出力電圧を示す信号が負荷の軽重を示す信号にもなることからフィードバック信号としたが、本発明は、スイッチング素子のオン期間とオフ期間とを制御する制御信号が生成できるような信号であれば、フィードバック信号とすることができる。

【産業上の利用可能性】

【0067】

本発明は、電源装置に適用可能である。

【符号の説明】

【0068】

V1 直流電源

T1 トランス

P1 一次巻線

P2 補助巻線

S1 二次巻線

Q1 スイッチング素子

Q2〜Q6 トランジスタ

OSC 発振器

INV1,INV2,INV3,G1 インバータ

Ia,Ib 電流源

CMP1 コンパレータ

D1〜D5 ダイオード

C1〜C4 コンデンサ

R0 起動抵抗

R1〜R11 抵抗

10.10a,10b ドライブ回路

11 電圧検出回路

AND1,AND2 アンド回路

【特許請求の範囲】

【請求項1】

フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路であって、

前記制御信号の前記オン期間における前記ドライブ回路の前記ゲート電流は、所定の期間だけ生成される第1電流成分と前記フィードバック信号に基づいて生成される第2電流成分との合成電流とすることを特徴とするドライブ回路。

【請求項2】

前記第2電流成分の電流値は、前記フィードバック信号の信号値により抵抗値が選択されて調整されることを特徴とする請求項1記載のドライブ回路。

【請求項3】

前記第2電流成分の電流値は、前記フィードバック信号の信号値により時定数回路が作動して調整されることを特徴とする請求項1記載のドライブ回路。

【請求項4】

前記第2電流成分の電流値は、前記フィードバック信号の信号値に反比例するように調整されることを特徴とする請求項1記載のドライブ回路。

【請求項5】

直流電源の直流電圧を断続してトランスの一次巻線に供給するスイッチング素子と、

前記トランスの二次巻線に発生した電圧を整流平滑する整流平滑回路と、

前記整流平滑回路の出力電圧を示す信号をフィードバック信号とし、前記フィードバック信号に基づいて前記スイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と、

前記制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路と、を有し、

前記ドライブ回路は、請求項1乃至請求項4のいずれか1項記載のドライブ回路であることを特徴とするスイッチング電源装置。

【請求項1】

フィードバック信号に基づいてスイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路であって、

前記制御信号の前記オン期間における前記ドライブ回路の前記ゲート電流は、所定の期間だけ生成される第1電流成分と前記フィードバック信号に基づいて生成される第2電流成分との合成電流とすることを特徴とするドライブ回路。

【請求項2】

前記第2電流成分の電流値は、前記フィードバック信号の信号値により抵抗値が選択されて調整されることを特徴とする請求項1記載のドライブ回路。

【請求項3】

前記第2電流成分の電流値は、前記フィードバック信号の信号値により時定数回路が作動して調整されることを特徴とする請求項1記載のドライブ回路。

【請求項4】

前記第2電流成分の電流値は、前記フィードバック信号の信号値に反比例するように調整されることを特徴とする請求項1記載のドライブ回路。

【請求項5】

直流電源の直流電圧を断続してトランスの一次巻線に供給するスイッチング素子と、

前記トランスの二次巻線に発生した電圧を整流平滑する整流平滑回路と、

前記整流平滑回路の出力電圧を示す信号をフィードバック信号とし、前記フィードバック信号に基づいて前記スイッチング素子のオン期間とオフ期間とを制御する制御信号を生成する制御回路と、

前記制御回路と前記スイッチング素子との間に接続され、前記スイッチング素子のゲートにゲート電流を供給するドライブ回路と、を有し、

前記ドライブ回路は、請求項1乃至請求項4のいずれか1項記載のドライブ回路であることを特徴とするスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−157215(P2012−157215A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−16314(P2011−16314)

【出願日】平成23年1月28日(2011.1.28)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年1月28日(2011.1.28)

【出願人】(000106276)サンケン電気株式会社 (982)

【Fターム(参考)】

[ Back to top ]