ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はアナログ−デジタル変換器に関する。特に、ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器に関する。

【背景技術】

【0002】

アナログ−デジタル変換器(以下、AD変換器という)は、連続的なアナログ信号を離散的なデジタル信号に変換する回路である。AD変換器には様々な型式があるが、高速変換を必要とする場合には、並列型AD変換器の一つであるフラッシュ型AD変換器がよく用いられる。このフラッシュ型AD変換器は、直列に接続された複数の分圧用抵抗により複数の基準電圧を生成し、それぞれの基準電圧とアナログ入力信号電圧を各コンパレータで比較し、その比較結果に基づいてアナログ入力信号に対応するデジタル信号を出力するものである。

【0003】

フラッシュ型AD変換器では、nビットの分解能を得るために2n−1個のコンパレータを必要とする。そのため分解能が上がるにつれて回路規模が指数関数的に増大し、これに伴って消費電力が増加するという問題があった。さらに、コンパレータ自体も一般のCMOS(相補型金属酸化膜半導体)論理ゲートなどと比べると、回路構造が複雑で回路規模も大きく、消費電力も大きい。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−6679号公報

【特許文献2】国際公開番号 WO96/30855

【特許文献3】特開平7−226085号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

フラッシュ型AD変換器は、分解能を高くしようとするとレイアウト面積及び消費電力が指数関数的に増加する。本発明は、回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一実施形態によると、第1のCMOS回路と、共通するフローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路の出力に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【0007】

前記ニューロンCMOS回路は、電源電圧が印加され、第1の容量を有する第1のゲートと、アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えてもよい。

【0008】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の2n−1倍に等しく、前記第3の容量は前記基本容量の(2n−1−i)倍に等しく、前記iは1番目の前記ニューロンCMOS回路から2n−1−1番目の前記ニューロンCMOS回路に対応する整数であってもよい。

【0009】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であってもよい。

【0010】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する2n−1個のCMOS回路を備えてもよい。

【0011】

前記エンコード部は、前記量子化出力電圧をVi(i=1〜2n−1−1)、前記デジタル変換出力端子に出力される電圧をVOi(i=1〜n−2)とすると、i番目のデジタル変換出力端子に出力される電圧VOi(i=1〜n−2)と、前記量子化出力電圧をVi(i=1〜2n−1−1)とは、以下の式の関係を満たしてもよい。

【数1】

【0012】

本発明の一実施形態によると、第1のCMOS回路と、共通するフローティングゲートを有し、3個のゲートがフローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路の出力に接続する7個のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続する4個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【0013】

前記ニューロンCMOS回路は、電源電圧が印加され、第1の容量を有する第1のゲートと、アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えてもよい。

【0014】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の8倍に等しく、前記第3の容量は前記基本容量の(8−i)倍に等しく、前記iは1番目の前記ニューロンCMOS回路から7番目の前記ニューロンCMOS回路に対応する整数であってもよい。

【0015】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であってもよい。

【0016】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する8個のCMOS回路を備えてもよい。

【0017】

前記エンコード部は、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路にそれぞれ直列に接続する3個のCMOS回路と、奇数番目の前記ニューロンCMOS回路に接続する4個の前記CMOS回路と、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する3個の前記CMOS回路と、に接続し、7個の前記CMOS回路から出力される量子化出力電圧を演算する7個のNAND回路と、前記7個のNAND回路に接続する1個のNAND回路と、2番目及び6番目の前記ニューロンCMOS回路に接続する前記CMOS回路と、4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路と、に接続し、3個の前記CMOS回路から出力される量子化出力電圧を演算する3個のNAND回路と、前記3個のNAND回路に接続する1個のNAND回路と、を備えてもよい。

【0018】

前記デジタル変換出力端子は、前記第1のCMOS回路に直列に接続するCMOS回路に接続し、第1のビットを出力する第1のデジタル変換出力端子と、前記4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路に接続し、第2のビットを出力する第2のデジタル変換出力端子と、前記3個のNAND回路に接続するNAND回路に接続し、第3のビットを出力する第3のデジタル変換出力端子と、前記7個のNAND回路に接続するNAND回路に接続し、第4のビットを出力する第4のデジタル変換出力端子と、を備えてもよい。

【発明の効果】

【0019】

本発明によると、分解能を高くしても、回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器が提供される。

【図面の簡単な説明】

【0020】

【図1】4ビットAD変換器900の回路図である。

【図2】(a)は図1のニューロンCMOS回路901の回路図であり、(b)はニューロンCMOS回路901の等価回路991の回路図を示す。

【図3】4ビットAD変換器900のアナログ入力電圧と、量子化出力電圧及びAD変換出力との関係を示す図である。

【図4】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路図である。

【図5】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100のニューロンCMOS回路とその等価回路。

【図6】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路のアナログ入力電圧と、量子化出力電圧及びAD変換出力との関係を示す図である。

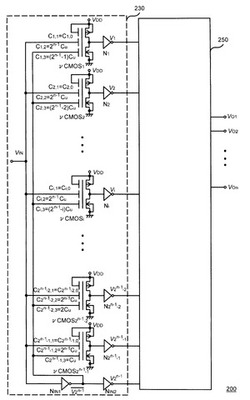

【図7】本発明の一実施形態に係るnビットフラッシュ型AD変換器200の回路図である。

【図8】本発明の一実施形態に係るnビットフラッシュ型AD変換器200のニューロンCMOS回路とその等価回路。

【図9】本発明の一実施形態に係るnビットフラッシュ型AD変換器300の回路図である。

【図10】本発明の一実施形態に係るnビットフラッシュ型AD変換器300のニューロンCMOS回路(νCMOSi(i=1〜2n−1−1))とその等価回路。

【図11】本発明の一実施形態に係るnビットフラッシュ型AD変換器300のニューロンCMOS回路(νCMOSj(j=2n−1+1〜2n−1))とその等価回路。

【図12】4ビットフラッシュ型AD変換器100のシミュレーション結果を示す図である。

【発明を実施するための形態】

【0021】

本発明においては、上記課題を解決するために、コンパレータよりも回路構造が簡単で、回路規模及び消費電力の少ないニューロンCMOS回路を用いてフラッシュ型AD変換器を構成することを鋭意検討した。本発明者らは、電源電圧の1/2を閾値とするCMOS回路を用いて、アナログ入力電圧が電源電圧の1/2以上の場合と、アナログ入力電圧が電源電圧の1/2未満の場合とで、ニューロンCMOS回路に印加する電圧を切り替えることにより、従来のフラッシュ型AD変換器を構成する場合に必要とされたコンパレータの約半分の2n−1−1個のニューロンCMOS回路でフラッシュ型AD変換器を構成できることを見出した。

【0022】

以下、図面を参照して本発明に係るフラッシュ型AD変換器について詳細に説明する。但し、本発明のフラッシュ型AD変換器は多くの異なる態様で実施することも可能であり、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、本実施の形態及び実施例で参照する図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0023】

(4ビットAD変換器)

ここで、後述する本願発明に係るフラッシュ型AD変換器の理解をしやすくするために、本発明者らが以前に発明し、2010年2月4日に財団法人北九州産業学術推進機構の主催による「第2回ユニーク・自作チップ・コンテストinひびきの」において発表した4ビットAD変換器について、まず説明する。図1は、4ビットAD変換器900の回路図である。また、図2(a)はニューロンCMOS回路901であり、図2(b)はニューロンCMOS回路901の等価回路991の回路図である。

【0024】

4ビットAD変換器900は、8個のCMOS回路と、3個のニューロンCMOS回路とを含む。図1においてNi(i=1〜8)はCMOS回路を示し、νCMOSi(i=1〜3)はニューロンCMOS回路を示す。なお、νCMOS1はニューロンCMOS回路901で、νCMOS2はニューロンCMOS回路903で、νCMOS3はニューロンCMOS回路905で構成される。

【0025】

ここで、ニューロンCMOS回路とは、CMOSのフローティングゲートに複数のゲートを配設した回路である。図1及び図2においては、ニューロンCMOS回路のnチャネルMOSFET(以下、NMOSという)とpチャネルMOSFET(以下、PMOSという)のフローティングゲートを共通にして、複数のゲートを配設した構成を示したが、NMOSとPMOSのそれぞれのフローティングゲートに並列に接続する複数のゲートを配設することもできる。本願発明に係るニューロンCMOS回路には、回路構成がシンプルであるため、NMOSとPMOSのフローティングゲートを共通にして、複数のゲートを配設したニューロンCMOS回路が好ましい。

【0026】

ニューロンCMOS回路901は、PMOSのソースに電源電圧VDDが印加され、NMOSのソースは接地する。また、ニューロンCMOS回路901には、容量C1,1のゲートと容量C1,2のゲートが配設される。ニューロンCMOS回路903には、容量C2,1のゲート、容量C2,2のゲート及び容量C2,3のゲートが配設される。ニューロンCMOS回路905には、容量C3,1のゲート、容量C3,2のゲート、容量C3,3のゲート及び容量C3,4のゲートが配設される。

【0027】

4ビットAD変換器900において、各CMOS回路の閾値は電源電圧VDDの1/2、各ニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。Ci,1(i=1〜3)、Ci,2(i=1〜3)、Ci,3(i=2〜3)及びC3,4はニューロンCMOS回路の閾値を決定するための容量であり、以下の式(2)〜(5)の関係を有する。

【数2】

ただし、nはビット数を表す自然数であり、4ビットAD変換器900においては4である。なお、Cuは半導体の設計上で最適に設定される基本容量である。

【数3】

【数4】

【数5】

ただし、4ビットAD変換器900においては、C3,4=Cuである。

【0028】

4ビットAD変換器900において、アナログ入力電圧VINはCMOS回路N1と、νCMOSi(i=1〜3)の容量Ci,1(i=1〜3)を有する各ゲートとに入力される。CMOS回路N1は、アナログ入力電圧VINがVDD/2以上の場合には0Vを出力し、アナログ入力電圧VINがVDD/2未満の場合には電源電圧VDDを出力する。CMOS回路N1に接続するCMOS回路N2は、CMOS回路N1の量子化出力電圧を反転してAD変換出力VO1をデジタル変換出力端子に出力する。また、CMOS回路N2からの量子化出力電圧は、CMOS回路N3により反転され、νCMOSi(i=1〜3)の容量Ci,2(i=1〜3)を有する各ゲートに入力される。

【0029】

νCMOS1は、2つのゲートに入力される電圧に応じて、式(6)のように量子化出力電圧V1を出力する。

【数6】

【0030】

式(6)に式(2)〜(3)を代入して、AD変換出力VO1が0の場合と、VDDの場合とで整理すると、式(7)のようになる。

【数7】

【0031】

電圧V1はCMOS回路N4により反転され、AD変換出力VO2としてデジタル変換出力端子に出力される。また、CMOS回路N5は、CMOS回路N4からの量子化出力電圧を更に反転した電圧をC2,3及びC3,3に印加する。なお、電圧V1をCMOS回路N4とN5により2度反転してC2,3及びC3,3に印加しているが、これは波形整形のためである。

【0032】

νCMOS2は、3つのゲートに入力される電圧に応じて、式(8)のように電圧V2を出力する。

【数8】

【0033】

【数9】

【0034】

電圧V2はCMOS回路N6により反転され、AD変換出力VO3としてデジタル変換出力端子に出力される。また、CMOS回路N7は、CMOS回路N6からの量子化出力電圧を更に反転した電圧をC3,4に印加する。なお、電圧V2をCMOS回路N6とN7により2度反転してC3,4に印加しているが、これは波形整形のためである。

【0035】

νCMOS3は、4つのゲートに入力される電圧に応じて、式(10)のように量子化出力電圧V3を出力する。

【数10】

【0036】

【0037】

したがって、図3に示すように、4ビットAD変換器900は、アナログ入力電圧VINに応じて4ビットのAD変換出力VO1〜VO4を4個のデジタル変換出力端子に出力することができる。4ビットAD変換器900は、回路中に抵抗器やコンパレータを用いることなく、3つのニューロンCMOS回路901〜905及び8個のCMOS回路N1〜N8のみを用いてシンプルな回路構造を構成することができ、優れたAD変換器を実現することができる。

【0038】

しかし、4ビットAD変換器900は、nビットに拡張するのが難しい。4ビットAD変換器900をnビットに拡張する場合、n−1個のニューロンCMOS回路が必要となる。このとき、n−1番目のニューロンCMOS回路には、n個のゲートの入力端子を備えることになる。すなわち、n−1番目のニューロンCMOS回路には、容量の異なるn個のゲートを備える必要があり、変換出力のビット数が増加するに連れて回路の製造が困難になる。また、ゲート数の増加に伴って、フローティングゲートの電圧変化が小さくなり動作が不安定になる。

【0039】

(本発明に係る4ビットフラッシュ型AD変換器)

上述の課題を解決し、4ビットAD変換器900の問題点を解消する、本発明に係るフラッシュ型AD変換器について、以下に説明する。本発明に係るフラッシュ型AD変換器は、3つのゲートを有するニューロンCMOS回路を2n−1−1個用いることにより、nビット(ここで、nは3以上の整数)のフラッシュ型AD変換器を構成することができる。本発明に係るフラッシュ型AD変換器の構成を理解するために、本実施形態においては、まず、4ビットのフラッシュ型AD変換器100を例に説明する。その後、nビットに拡張した場合について説明する。

【0040】

図4は、本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路図である。4ビットフラッシュ型AD変換器100は、量子化出力部130とエンコード部150を有する。図4においてNi(i=1〜7)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜7)はニューロンCMOS回路である。ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜7)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。本実施形態に係る4ビットフラッシュ型AD変換器100は、アナログ入力電圧VINを入力する端子と並列に接続する7個のニューロンCMOS回路νCMOSi(i=1〜7)とを量子化出力部130に備える。また、量子化出力部130には、それぞれのニューロンCMOS回路νCMOSi(i=1〜7)に直列に接続する7個の波形整形用のCMOS回路Ni(i=1〜7)と、CMOS回路NIN1に直列に接続するCMOS回路NIN2と、を備える。

【0041】

また、4ビットフラッシュ型AD変換器100は、エンコード部150を更に備える。エンコード部150は、偶数番目のCMOS回路N2、N4及びN6にそれぞれ接続するCMOS回路N2a、N4a及びN6aを有し、奇数番目のCMOS回路N1、N3、N5及びN7と、偶数番目のCMOS回路に接続するCMOS回路N2a、N4a及びN6aと、からの量子化出力電圧を演算するNAND回路NAND1〜NAND8を有する。NAND回路NAND8はNAND回路NAND1〜NAND7の量子化出力電圧を演算して、AD変換出力VO1をデジタル変換出力端子に出力する。また、エンコード部150は、CMOS回路N2、N4a及びN6からの量子化出力電圧を演算するNAND回路NAND9〜NAND12を有し、NAND回路NAND12はNAND回路NAND9〜NAND11の量子化出力電圧を演算して、AD変換出力VO2をデジタル変換出力端子に出力する。4ビットフラッシュ型AD変換器100は、CMOS回路N4の量子化出力電圧をAD変換出力VO3としてデジタル変換出力端子に出力し、CMOS回路NIN2の量子化出力電圧をAD変換出力VO4としてデジタル変換出力端子に出力する。

【0042】

図5は、図4のi番目のニューロンCMOS回路νCMOSiとその等価回路である。ニューロンCMOS回路νCMOSiにおいて、Ci,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(11)のように、フローティングゲート−基板間容量Ci,0(図示していない)と同容量である。このように、容量Ci,1と、フローティングゲート−基板間容量Ci,0とを同容量にすることにより、閾値への影響を抑えるニューロンCMOS回路は、これまで報告されていない。

【数11】

【0043】

Ci,2、Ci,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(12)、式(13)の関係を満たす。

【数12】

【数13】

【0044】

なお、Cuは半導体の設計上で最適に設定される基本容量で、例えば、0.05pFを用いることができる。また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0045】

図5において、Ci,0はフローティングゲート−基板間容量、Φiは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φiは、次に示す式(14)のようになる。

【数14】

【0046】

ニューロンCMOS回路は、フローティングゲートの電圧がVDD/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSiの出力をCMOS回路Niにより反転した電圧が量子化出力電圧Vi(i=1〜7)であり、量子化出力電圧Viは式(15)のようになる。

【数15】

【0047】

式(15)に、式(11)、式(12)、式(13)を代入し整理すると、式(16)のようになる。

【数16】

【0048】

【数17】

【0049】

【0050】

【数18】

【0051】

【数19】

【0052】

式(18)及び式(19)より、式(20)のようになる。

【数20】

【0053】

式(20)より、アナログ入力電圧VINを0Vから電源電圧VDDまで徐々に増加させると、量子化出力電圧Vi(i=1〜7)は、i・VDD/16以上になると0VからVDDに変化し、VDD/2になると0に反転し、VDD−i・VDD/16以上になると0VからVDDに反転する。すなわち、アナログ入力電圧VINを0Vから電源電圧VDDまで徐々に増加させると、アナログ入力電圧VINがVDD/16増える毎に、量子化出力電圧V1、V2、V3、V4、V5、V6、V7が順次0VからVDDに変化して、入力電圧VINがVDD/2以上になると量子化出力電圧V8がVDDとなり、量子化出力電圧Vi(i=1〜7)が0になる。

【0054】

さらに、アナログ入力電圧VINがVDD/16増える毎に量子化出力電圧V7、V6、V5、V4、V3、V2、V1の順番で0VからVDDに反転する。量子化出力電圧Vi(i=1〜7)及びV8は、エンコード部150に入力され、エンコード部150により4ビットのAD変換出力に変換している。図6は、図4の回路のアナログ入力電圧VINと、量子化出力電圧V1〜V8及びAD変換出力VO1〜VO4の関係を表す図である。

【0055】

本実施形態に係る4ビットフラッシュ型AD変換器100は、上述したように、アナログ入力電圧VINに応じて4ビットのAD変換出力VO1〜VO4を4個のデジタル変換出力端子に出力することができる。4ビットフラッシュ型AD変換器100は、回路中に抵抗器やコンパレータを用いることなく、フローティングゲートに3つのゲートを有するニューロンCMOS回路を7個用いて回路構造を構成することができる。nビットに拡張する場合にも、4ビットAD変換器900のように容量の異なるn個のゲートを備えたニューロンCMOS回路を用いる必要はない。

【0056】

【0057】

nビットフラッシュ型AD変換器200は、量子化出力部230とエンコード部250を有する。図7においてNi(i=1〜2n−1−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)はニューロンCMOS回路である。ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。本実施形態に係るnビットフラッシュ型AD変換器200は、アナログ入力電圧VINを入力する端子と並列に接続する2n−1−1個のニューロンCMOS回路νCMOSi(i=1〜2n−1−1)と1個のCMOS回路NIN1とを量子化出力部230に備える。また、量子化出力部230には、それぞれのニューロンCMOS回路に接続する2n−1−1個の波形整形用のCMOS回路Ni(i=1〜2n−1−1)と、CMOS回路NIN1に直列に接続するCMOS回路NIN2と、を備える。

【0058】

また、nビットフラッシュ型AD変換器200は、エンコード部250を更に有する。

nビットの場合のAD変換出力VOi(i=1〜n−2)を得るための回路は、式(21)により設計できる。

【数21】

【0059】

Ci,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(22)のように、フローティングゲート−基板間容量Ci,0(図示していない)と同容量である。

【数22】

【0060】

Ci,2、Ci,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(23)、式(24)の関係を満たす。

【数23】

【数24】

【0061】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0062】

図8は、図7の上からi番目のニューロンCMOS回路νCMOSiの回路とその等価回路である。図8において、Ci,0はフローティングゲート−基板間容量、Φiは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φiは、次に示す式(25)のようになる。

【数25】

【0063】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSiの出力を回路Niにより反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、量子化出力電圧Viは式(26)のようになる。

【数26】

【0064】

式(26)に、式(22)、式(23)、式(24)を代入し整理すると、式(27)のようになる。

【数27】

【0065】

【数28】

【0066】

【0067】

【数29】

【0068】

【数30】

【0069】

式(29)及び式(30)より、式(31)のようになる。

【数31】

【0070】

【0071】

【0072】

以上説明したように、4ビットフラッシュ型AD変換器100は、nビットフラッシュ型AD変換器200に拡張することができる。本実施形態に係るnビットフラッシュ型AD変換器200は、回路中に抵抗器やコンパレータを用いることなく、3つのゲートを有するニューロンCMOS回路を2n−1−1個用いて回路構造を構成することができる。nビットフラッシュ型AD変換器200は、4ビットAD変換器900のように容量の異なるn個のゲートを備えたニューロンCMOS回路を用いる必要はない。また、本実施形態に係るnビットフラッシュ型AD変換器200は、電圧を比較する素子としてコンパレータに比べて回路規模が小さく消費電力の少ないニューロンCMOS回路を用いると共に1個のニューロンCMOS回路に2個の電圧レベルを判定する機能を持たせることにより使用する素子数を半減しており、回路規模が小さく低消費電力特性を有するフラッシュ型AD変換器を提供できる。

【0073】

【0074】

nビットフラッシュ型AD変換器300は、量子化出力部330とエンコード部350を有する。図9は、本発明の一実施形態に係るnビットフラッシュ型AD変換器300の回路図である。nビットフラッシュ型AD変換器300においては、構成に必要なニューロンCMOS回路の数は従来のフラッシュ型AD変換器を構成するコンパレータ数に比べて1個少ないだけである。図9においてNi(i=1〜2n−1−1)、Nj(j=2n−1+1〜2n−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)、νCMOSj(j=2n−1+1〜2n−1)はニューロンCMOS回路である。nビットフラッシュ型AD変換器300は、νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)、すなわち、2n−2個のニューロンCMOS回路と1個のCMOS回路NIN1とがアナログ入力電圧VINを入力する端子に接続し、各ニューロンCMOS回路には波形整形用のCMOS回路が1個ずつ直列に接続し、CMOS回路NIN1にはCMOS回路NIN2が直列に接続する。

【0075】

ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)及びCj,1、Cj,2、Cj,3(j=2n−1+1〜2n−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。nビットフラッシュ型AD変換器300においては、ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)の容量Ci,1(i=1〜2n−1−1)及びCj,1(j=2n−1+1〜2n−1)を有するゲートには電源電圧VDDが印加され、容量Ci,2(i=1〜2n−1−1)及びCj,2(j=2n−1+1〜2n−1)を有するゲートにはアナログ入力電圧VINが印加される。νCMOSi(i=1〜2n−1−1)の容量Ci,3(i=1〜2n−1−1)を有するゲートには電源電圧VDDが印加され、νCMOSj(j=2n−1+1〜2n−1)の容量Cj,3(j=2n−1+1〜2n−1)を有するゲートは接地される。アナログ入力電圧VINは、CMOS回路NIN2に直列に接続したCMOS回路NIN1にも印加される。

【0076】

また、nビットフラッシュ型AD変換器300は、エンコード部350を更に有する。nビットの場合のAD変換出力VOi(i=1〜n−1)を得るための回路は、式(32)により設計できる。

【数32】

【0077】

Ci,1、Cj,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(33)、式(34)のように、フローティングゲート−基板間容量Ci,0(図示していない)、Cj,0(図示していない)と同容量である。

【0078】

【数33】

【数34】

【0079】

Ci,2、Ci,3、Cj,2、Cj,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(35)〜式(38)の関係を満たす。

【数35】

【数36】

【数37】

【数38】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0080】

図10は、図9の上からi番目(i=1〜2n−1−1)のニューロンCMOS回路νCMOSiの回路とその等価回路であり、図11は図9の上からj番目(j=2n−1+1〜2n−1)のニューロンCMOS回路νCMOSjの回路とその等価回路である。図10、図11において、Ci,0、Cj,0はフローティングゲート−基板間容量、Φi及びΦjは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φi、Φjは、次に示す式(39)、(40)のようになる。

【数39】

【数40】

【0081】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)の出力を回路Ni(i=1〜2n−1−1)により反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、ニューロンCMOS回路νCMOSj(j=2n−1+1〜2n−1)の出力をCMOS回路Nj(j=2n−1+1〜2n−1)により反転した電圧が量子化出力電圧Vj(j=2n−1+1〜2n−1)である。したがって、量子化出力電圧Vi(i=1〜2n−1)及びVj(j=2n−1+1〜2n−1)は、式(41)、式(42)のようになる。

【数41】

【数42】

【0082】

式(41)に、式(33)、式(35)、式(36)を代入し整理すると、式(43)のようになる。また、式(42)に式(34)、式(37)、式(38)を代入し整理すると、式(44)のようになる。

【数43】

【数44】

【0083】

【0084】

【0085】

【0086】

すななち、nビットフラッシュ型AD変換器200は、最上位ビットを得るために必要な電源電圧VDDの1/2を閾値とする信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に2個の閾値を判定させることにより回路規模を1/2にしている。同様に、上位2ビットの信号またはこれを得るために必要な電源電圧VDDの1/4、2/4、3/4を閾値とする信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に4個の閾値を判定させることにより回路規模を1/4にすることも可能である。さらに、上位kビットの信号またはこれを得るために必要な信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に2k個の閾値を判定させることにより回路規模を1/2kにすることも可能である。

【実施例】

【0087】

(実施例)

図12は、図4に示した本発明の実施形態に係る4ビットフラッシュ型AD変換器100のシミュレーション結果である。本実施例のシミュレーションは、回路シミュレータHSPICEを用いて行なった。本実施例においては、Cuを0.05pFとして計算した。図12に示したように、4ビットフラッシュ型AD変換器100は、アナログ入力電圧VINを4ビットのデジタル値に変換してAD変換出力VO1〜VO4を出力することができる。

【符号の説明】

【0088】

100:4ビットフラッシュ型AD変換器、130:量子化出力部、150:エンコード部、200:nビットフラッシュ型AD変換器、230:量子化出力部、250:エンコード部、300:nビットフラッシュ型AD変換器、330:量子化出力部、350:エンコード部、900:4ビットAD変換器、901:ニューロンCMOS回路、903:ニューロンCMOS回路、905:ニューロンCMOS回路、991:ニューロンCMOS回路901の等価回路

【技術分野】

【0001】

本発明はアナログ−デジタル変換器に関する。特に、ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器に関する。

【背景技術】

【0002】

アナログ−デジタル変換器(以下、AD変換器という)は、連続的なアナログ信号を離散的なデジタル信号に変換する回路である。AD変換器には様々な型式があるが、高速変換を必要とする場合には、並列型AD変換器の一つであるフラッシュ型AD変換器がよく用いられる。このフラッシュ型AD変換器は、直列に接続された複数の分圧用抵抗により複数の基準電圧を生成し、それぞれの基準電圧とアナログ入力信号電圧を各コンパレータで比較し、その比較結果に基づいてアナログ入力信号に対応するデジタル信号を出力するものである。

【0003】

フラッシュ型AD変換器では、nビットの分解能を得るために2n−1個のコンパレータを必要とする。そのため分解能が上がるにつれて回路規模が指数関数的に増大し、これに伴って消費電力が増加するという問題があった。さらに、コンパレータ自体も一般のCMOS(相補型金属酸化膜半導体)論理ゲートなどと比べると、回路構造が複雑で回路規模も大きく、消費電力も大きい。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−6679号公報

【特許文献2】国際公開番号 WO96/30855

【特許文献3】特開平7−226085号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

フラッシュ型AD変換器は、分解能を高くしようとするとレイアウト面積及び消費電力が指数関数的に増加する。本発明は、回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一実施形態によると、第1のCMOS回路と、共通するフローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路の出力に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【0007】

前記ニューロンCMOS回路は、電源電圧が印加され、第1の容量を有する第1のゲートと、アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えてもよい。

【0008】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の2n−1倍に等しく、前記第3の容量は前記基本容量の(2n−1−i)倍に等しく、前記iは1番目の前記ニューロンCMOS回路から2n−1−1番目の前記ニューロンCMOS回路に対応する整数であってもよい。

【0009】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であってもよい。

【0010】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する2n−1個のCMOS回路を備えてもよい。

【0011】

前記エンコード部は、前記量子化出力電圧をVi(i=1〜2n−1−1)、前記デジタル変換出力端子に出力される電圧をVOi(i=1〜n−2)とすると、i番目のデジタル変換出力端子に出力される電圧VOi(i=1〜n−2)と、前記量子化出力電圧をVi(i=1〜2n−1−1)とは、以下の式の関係を満たしてもよい。

【数1】

【0012】

本発明の一実施形態によると、第1のCMOS回路と、共通するフローティングゲートを有し、3個のゲートがフローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路の出力に接続する7個のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続する4個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

【0013】

前記ニューロンCMOS回路は、電源電圧が印加され、第1の容量を有する第1のゲートと、アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えてもよい。

【0014】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の8倍に等しく、前記第3の容量は前記基本容量の(8−i)倍に等しく、前記iは1番目の前記ニューロンCMOS回路から7番目の前記ニューロンCMOS回路に対応する整数であってもよい。

【0015】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であってもよい。

【0016】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する8個のCMOS回路を備えてもよい。

【0017】

前記エンコード部は、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路にそれぞれ直列に接続する3個のCMOS回路と、奇数番目の前記ニューロンCMOS回路に接続する4個の前記CMOS回路と、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する3個の前記CMOS回路と、に接続し、7個の前記CMOS回路から出力される量子化出力電圧を演算する7個のNAND回路と、前記7個のNAND回路に接続する1個のNAND回路と、2番目及び6番目の前記ニューロンCMOS回路に接続する前記CMOS回路と、4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路と、に接続し、3個の前記CMOS回路から出力される量子化出力電圧を演算する3個のNAND回路と、前記3個のNAND回路に接続する1個のNAND回路と、を備えてもよい。

【0018】

前記デジタル変換出力端子は、前記第1のCMOS回路に直列に接続するCMOS回路に接続し、第1のビットを出力する第1のデジタル変換出力端子と、前記4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路に接続し、第2のビットを出力する第2のデジタル変換出力端子と、前記3個のNAND回路に接続するNAND回路に接続し、第3のビットを出力する第3のデジタル変換出力端子と、前記7個のNAND回路に接続するNAND回路に接続し、第4のビットを出力する第4のデジタル変換出力端子と、を備えてもよい。

【発明の効果】

【0019】

本発明によると、分解能を高くしても、回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器が提供される。

【図面の簡単な説明】

【0020】

【図1】4ビットAD変換器900の回路図である。

【図2】(a)は図1のニューロンCMOS回路901の回路図であり、(b)はニューロンCMOS回路901の等価回路991の回路図を示す。

【図3】4ビットAD変換器900のアナログ入力電圧と、量子化出力電圧及びAD変換出力との関係を示す図である。

【図4】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路図である。

【図5】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100のニューロンCMOS回路とその等価回路。

【図6】本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路のアナログ入力電圧と、量子化出力電圧及びAD変換出力との関係を示す図である。

【図7】本発明の一実施形態に係るnビットフラッシュ型AD変換器200の回路図である。

【図8】本発明の一実施形態に係るnビットフラッシュ型AD変換器200のニューロンCMOS回路とその等価回路。

【図9】本発明の一実施形態に係るnビットフラッシュ型AD変換器300の回路図である。

【図10】本発明の一実施形態に係るnビットフラッシュ型AD変換器300のニューロンCMOS回路(νCMOSi(i=1〜2n−1−1))とその等価回路。

【図11】本発明の一実施形態に係るnビットフラッシュ型AD変換器300のニューロンCMOS回路(νCMOSj(j=2n−1+1〜2n−1))とその等価回路。

【図12】4ビットフラッシュ型AD変換器100のシミュレーション結果を示す図である。

【発明を実施するための形態】

【0021】

本発明においては、上記課題を解決するために、コンパレータよりも回路構造が簡単で、回路規模及び消費電力の少ないニューロンCMOS回路を用いてフラッシュ型AD変換器を構成することを鋭意検討した。本発明者らは、電源電圧の1/2を閾値とするCMOS回路を用いて、アナログ入力電圧が電源電圧の1/2以上の場合と、アナログ入力電圧が電源電圧の1/2未満の場合とで、ニューロンCMOS回路に印加する電圧を切り替えることにより、従来のフラッシュ型AD変換器を構成する場合に必要とされたコンパレータの約半分の2n−1−1個のニューロンCMOS回路でフラッシュ型AD変換器を構成できることを見出した。

【0022】

以下、図面を参照して本発明に係るフラッシュ型AD変換器について詳細に説明する。但し、本発明のフラッシュ型AD変換器は多くの異なる態様で実施することも可能であり、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、本実施の形態及び実施例で参照する図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0023】

(4ビットAD変換器)

ここで、後述する本願発明に係るフラッシュ型AD変換器の理解をしやすくするために、本発明者らが以前に発明し、2010年2月4日に財団法人北九州産業学術推進機構の主催による「第2回ユニーク・自作チップ・コンテストinひびきの」において発表した4ビットAD変換器について、まず説明する。図1は、4ビットAD変換器900の回路図である。また、図2(a)はニューロンCMOS回路901であり、図2(b)はニューロンCMOS回路901の等価回路991の回路図である。

【0024】

4ビットAD変換器900は、8個のCMOS回路と、3個のニューロンCMOS回路とを含む。図1においてNi(i=1〜8)はCMOS回路を示し、νCMOSi(i=1〜3)はニューロンCMOS回路を示す。なお、νCMOS1はニューロンCMOS回路901で、νCMOS2はニューロンCMOS回路903で、νCMOS3はニューロンCMOS回路905で構成される。

【0025】

ここで、ニューロンCMOS回路とは、CMOSのフローティングゲートに複数のゲートを配設した回路である。図1及び図2においては、ニューロンCMOS回路のnチャネルMOSFET(以下、NMOSという)とpチャネルMOSFET(以下、PMOSという)のフローティングゲートを共通にして、複数のゲートを配設した構成を示したが、NMOSとPMOSのそれぞれのフローティングゲートに並列に接続する複数のゲートを配設することもできる。本願発明に係るニューロンCMOS回路には、回路構成がシンプルであるため、NMOSとPMOSのフローティングゲートを共通にして、複数のゲートを配設したニューロンCMOS回路が好ましい。

【0026】

ニューロンCMOS回路901は、PMOSのソースに電源電圧VDDが印加され、NMOSのソースは接地する。また、ニューロンCMOS回路901には、容量C1,1のゲートと容量C1,2のゲートが配設される。ニューロンCMOS回路903には、容量C2,1のゲート、容量C2,2のゲート及び容量C2,3のゲートが配設される。ニューロンCMOS回路905には、容量C3,1のゲート、容量C3,2のゲート、容量C3,3のゲート及び容量C3,4のゲートが配設される。

【0027】

4ビットAD変換器900において、各CMOS回路の閾値は電源電圧VDDの1/2、各ニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。Ci,1(i=1〜3)、Ci,2(i=1〜3)、Ci,3(i=2〜3)及びC3,4はニューロンCMOS回路の閾値を決定するための容量であり、以下の式(2)〜(5)の関係を有する。

【数2】

ただし、nはビット数を表す自然数であり、4ビットAD変換器900においては4である。なお、Cuは半導体の設計上で最適に設定される基本容量である。

【数3】

【数4】

【数5】

ただし、4ビットAD変換器900においては、C3,4=Cuである。

【0028】

4ビットAD変換器900において、アナログ入力電圧VINはCMOS回路N1と、νCMOSi(i=1〜3)の容量Ci,1(i=1〜3)を有する各ゲートとに入力される。CMOS回路N1は、アナログ入力電圧VINがVDD/2以上の場合には0Vを出力し、アナログ入力電圧VINがVDD/2未満の場合には電源電圧VDDを出力する。CMOS回路N1に接続するCMOS回路N2は、CMOS回路N1の量子化出力電圧を反転してAD変換出力VO1をデジタル変換出力端子に出力する。また、CMOS回路N2からの量子化出力電圧は、CMOS回路N3により反転され、νCMOSi(i=1〜3)の容量Ci,2(i=1〜3)を有する各ゲートに入力される。

【0029】

νCMOS1は、2つのゲートに入力される電圧に応じて、式(6)のように量子化出力電圧V1を出力する。

【数6】

【0030】

式(6)に式(2)〜(3)を代入して、AD変換出力VO1が0の場合と、VDDの場合とで整理すると、式(7)のようになる。

【数7】

【0031】

電圧V1はCMOS回路N4により反転され、AD変換出力VO2としてデジタル変換出力端子に出力される。また、CMOS回路N5は、CMOS回路N4からの量子化出力電圧を更に反転した電圧をC2,3及びC3,3に印加する。なお、電圧V1をCMOS回路N4とN5により2度反転してC2,3及びC3,3に印加しているが、これは波形整形のためである。

【0032】

νCMOS2は、3つのゲートに入力される電圧に応じて、式(8)のように電圧V2を出力する。

【数8】

【0033】

【数9】

【0034】

電圧V2はCMOS回路N6により反転され、AD変換出力VO3としてデジタル変換出力端子に出力される。また、CMOS回路N7は、CMOS回路N6からの量子化出力電圧を更に反転した電圧をC3,4に印加する。なお、電圧V2をCMOS回路N6とN7により2度反転してC3,4に印加しているが、これは波形整形のためである。

【0035】

νCMOS3は、4つのゲートに入力される電圧に応じて、式(10)のように量子化出力電圧V3を出力する。

【数10】

【0036】

【0037】

したがって、図3に示すように、4ビットAD変換器900は、アナログ入力電圧VINに応じて4ビットのAD変換出力VO1〜VO4を4個のデジタル変換出力端子に出力することができる。4ビットAD変換器900は、回路中に抵抗器やコンパレータを用いることなく、3つのニューロンCMOS回路901〜905及び8個のCMOS回路N1〜N8のみを用いてシンプルな回路構造を構成することができ、優れたAD変換器を実現することができる。

【0038】

しかし、4ビットAD変換器900は、nビットに拡張するのが難しい。4ビットAD変換器900をnビットに拡張する場合、n−1個のニューロンCMOS回路が必要となる。このとき、n−1番目のニューロンCMOS回路には、n個のゲートの入力端子を備えることになる。すなわち、n−1番目のニューロンCMOS回路には、容量の異なるn個のゲートを備える必要があり、変換出力のビット数が増加するに連れて回路の製造が困難になる。また、ゲート数の増加に伴って、フローティングゲートの電圧変化が小さくなり動作が不安定になる。

【0039】

(本発明に係る4ビットフラッシュ型AD変換器)

上述の課題を解決し、4ビットAD変換器900の問題点を解消する、本発明に係るフラッシュ型AD変換器について、以下に説明する。本発明に係るフラッシュ型AD変換器は、3つのゲートを有するニューロンCMOS回路を2n−1−1個用いることにより、nビット(ここで、nは3以上の整数)のフラッシュ型AD変換器を構成することができる。本発明に係るフラッシュ型AD変換器の構成を理解するために、本実施形態においては、まず、4ビットのフラッシュ型AD変換器100を例に説明する。その後、nビットに拡張した場合について説明する。

【0040】

図4は、本発明の一実施形態に係る4ビットフラッシュ型AD変換器100の回路図である。4ビットフラッシュ型AD変換器100は、量子化出力部130とエンコード部150を有する。図4においてNi(i=1〜7)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜7)はニューロンCMOS回路である。ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜7)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。本実施形態に係る4ビットフラッシュ型AD変換器100は、アナログ入力電圧VINを入力する端子と並列に接続する7個のニューロンCMOS回路νCMOSi(i=1〜7)とを量子化出力部130に備える。また、量子化出力部130には、それぞれのニューロンCMOS回路νCMOSi(i=1〜7)に直列に接続する7個の波形整形用のCMOS回路Ni(i=1〜7)と、CMOS回路NIN1に直列に接続するCMOS回路NIN2と、を備える。

【0041】

また、4ビットフラッシュ型AD変換器100は、エンコード部150を更に備える。エンコード部150は、偶数番目のCMOS回路N2、N4及びN6にそれぞれ接続するCMOS回路N2a、N4a及びN6aを有し、奇数番目のCMOS回路N1、N3、N5及びN7と、偶数番目のCMOS回路に接続するCMOS回路N2a、N4a及びN6aと、からの量子化出力電圧を演算するNAND回路NAND1〜NAND8を有する。NAND回路NAND8はNAND回路NAND1〜NAND7の量子化出力電圧を演算して、AD変換出力VO1をデジタル変換出力端子に出力する。また、エンコード部150は、CMOS回路N2、N4a及びN6からの量子化出力電圧を演算するNAND回路NAND9〜NAND12を有し、NAND回路NAND12はNAND回路NAND9〜NAND11の量子化出力電圧を演算して、AD変換出力VO2をデジタル変換出力端子に出力する。4ビットフラッシュ型AD変換器100は、CMOS回路N4の量子化出力電圧をAD変換出力VO3としてデジタル変換出力端子に出力し、CMOS回路NIN2の量子化出力電圧をAD変換出力VO4としてデジタル変換出力端子に出力する。

【0042】

図5は、図4のi番目のニューロンCMOS回路νCMOSiとその等価回路である。ニューロンCMOS回路νCMOSiにおいて、Ci,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(11)のように、フローティングゲート−基板間容量Ci,0(図示していない)と同容量である。このように、容量Ci,1と、フローティングゲート−基板間容量Ci,0とを同容量にすることにより、閾値への影響を抑えるニューロンCMOS回路は、これまで報告されていない。

【数11】

【0043】

Ci,2、Ci,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(12)、式(13)の関係を満たす。

【数12】

【数13】

【0044】

なお、Cuは半導体の設計上で最適に設定される基本容量で、例えば、0.05pFを用いることができる。また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0045】

図5において、Ci,0はフローティングゲート−基板間容量、Φiは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φiは、次に示す式(14)のようになる。

【数14】

【0046】

ニューロンCMOS回路は、フローティングゲートの電圧がVDD/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSiの出力をCMOS回路Niにより反転した電圧が量子化出力電圧Vi(i=1〜7)であり、量子化出力電圧Viは式(15)のようになる。

【数15】

【0047】

式(15)に、式(11)、式(12)、式(13)を代入し整理すると、式(16)のようになる。

【数16】

【0048】

【数17】

【0049】

【0050】

【数18】

【0051】

【数19】

【0052】

式(18)及び式(19)より、式(20)のようになる。

【数20】

【0053】

式(20)より、アナログ入力電圧VINを0Vから電源電圧VDDまで徐々に増加させると、量子化出力電圧Vi(i=1〜7)は、i・VDD/16以上になると0VからVDDに変化し、VDD/2になると0に反転し、VDD−i・VDD/16以上になると0VからVDDに反転する。すなわち、アナログ入力電圧VINを0Vから電源電圧VDDまで徐々に増加させると、アナログ入力電圧VINがVDD/16増える毎に、量子化出力電圧V1、V2、V3、V4、V5、V6、V7が順次0VからVDDに変化して、入力電圧VINがVDD/2以上になると量子化出力電圧V8がVDDとなり、量子化出力電圧Vi(i=1〜7)が0になる。

【0054】

さらに、アナログ入力電圧VINがVDD/16増える毎に量子化出力電圧V7、V6、V5、V4、V3、V2、V1の順番で0VからVDDに反転する。量子化出力電圧Vi(i=1〜7)及びV8は、エンコード部150に入力され、エンコード部150により4ビットのAD変換出力に変換している。図6は、図4の回路のアナログ入力電圧VINと、量子化出力電圧V1〜V8及びAD変換出力VO1〜VO4の関係を表す図である。

【0055】

本実施形態に係る4ビットフラッシュ型AD変換器100は、上述したように、アナログ入力電圧VINに応じて4ビットのAD変換出力VO1〜VO4を4個のデジタル変換出力端子に出力することができる。4ビットフラッシュ型AD変換器100は、回路中に抵抗器やコンパレータを用いることなく、フローティングゲートに3つのゲートを有するニューロンCMOS回路を7個用いて回路構造を構成することができる。nビットに拡張する場合にも、4ビットAD変換器900のように容量の異なるn個のゲートを備えたニューロンCMOS回路を用いる必要はない。

【0056】

【0057】

nビットフラッシュ型AD変換器200は、量子化出力部230とエンコード部250を有する。図7においてNi(i=1〜2n−1−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)はニューロンCMOS回路である。ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。本実施形態に係るnビットフラッシュ型AD変換器200は、アナログ入力電圧VINを入力する端子と並列に接続する2n−1−1個のニューロンCMOS回路νCMOSi(i=1〜2n−1−1)と1個のCMOS回路NIN1とを量子化出力部230に備える。また、量子化出力部230には、それぞれのニューロンCMOS回路に接続する2n−1−1個の波形整形用のCMOS回路Ni(i=1〜2n−1−1)と、CMOS回路NIN1に直列に接続するCMOS回路NIN2と、を備える。

【0058】

また、nビットフラッシュ型AD変換器200は、エンコード部250を更に有する。

nビットの場合のAD変換出力VOi(i=1〜n−2)を得るための回路は、式(21)により設計できる。

【数21】

【0059】

Ci,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(22)のように、フローティングゲート−基板間容量Ci,0(図示していない)と同容量である。

【数22】

【0060】

Ci,2、Ci,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(23)、式(24)の関係を満たす。

【数23】

【数24】

【0061】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0062】

図8は、図7の上からi番目のニューロンCMOS回路νCMOSiの回路とその等価回路である。図8において、Ci,0はフローティングゲート−基板間容量、Φiは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φiは、次に示す式(25)のようになる。

【数25】

【0063】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSiの出力を回路Niにより反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、量子化出力電圧Viは式(26)のようになる。

【数26】

【0064】

式(26)に、式(22)、式(23)、式(24)を代入し整理すると、式(27)のようになる。

【数27】

【0065】

【数28】

【0066】

【0067】

【数29】

【0068】

【数30】

【0069】

式(29)及び式(30)より、式(31)のようになる。

【数31】

【0070】

【0071】

【0072】

以上説明したように、4ビットフラッシュ型AD変換器100は、nビットフラッシュ型AD変換器200に拡張することができる。本実施形態に係るnビットフラッシュ型AD変換器200は、回路中に抵抗器やコンパレータを用いることなく、3つのゲートを有するニューロンCMOS回路を2n−1−1個用いて回路構造を構成することができる。nビットフラッシュ型AD変換器200は、4ビットAD変換器900のように容量の異なるn個のゲートを備えたニューロンCMOS回路を用いる必要はない。また、本実施形態に係るnビットフラッシュ型AD変換器200は、電圧を比較する素子としてコンパレータに比べて回路規模が小さく消費電力の少ないニューロンCMOS回路を用いると共に1個のニューロンCMOS回路に2個の電圧レベルを判定する機能を持たせることにより使用する素子数を半減しており、回路規模が小さく低消費電力特性を有するフラッシュ型AD変換器を提供できる。

【0073】

【0074】

nビットフラッシュ型AD変換器300は、量子化出力部330とエンコード部350を有する。図9は、本発明の一実施形態に係るnビットフラッシュ型AD変換器300の回路図である。nビットフラッシュ型AD変換器300においては、構成に必要なニューロンCMOS回路の数は従来のフラッシュ型AD変換器を構成するコンパレータ数に比べて1個少ないだけである。図9においてNi(i=1〜2n−1−1)、Nj(j=2n−1+1〜2n−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)、νCMOSj(j=2n−1+1〜2n−1)はニューロンCMOS回路である。nビットフラッシュ型AD変換器300は、νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)、すなわち、2n−2個のニューロンCMOS回路と1個のCMOS回路NIN1とがアナログ入力電圧VINを入力する端子に接続し、各ニューロンCMOS回路には波形整形用のCMOS回路が1個ずつ直列に接続し、CMOS回路NIN1にはCMOS回路NIN2が直列に接続する。

【0075】

ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)及びCj,1、Cj,2、Cj,3(j=2n−1+1〜2n−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。nビットフラッシュ型AD変換器300においては、ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)の容量Ci,1(i=1〜2n−1−1)及びCj,1(j=2n−1+1〜2n−1)を有するゲートには電源電圧VDDが印加され、容量Ci,2(i=1〜2n−1−1)及びCj,2(j=2n−1+1〜2n−1)を有するゲートにはアナログ入力電圧VINが印加される。νCMOSi(i=1〜2n−1−1)の容量Ci,3(i=1〜2n−1−1)を有するゲートには電源電圧VDDが印加され、νCMOSj(j=2n−1+1〜2n−1)の容量Cj,3(j=2n−1+1〜2n−1)を有するゲートは接地される。アナログ入力電圧VINは、CMOS回路NIN2に直列に接続したCMOS回路NIN1にも印加される。

【0076】

また、nビットフラッシュ型AD変換器300は、エンコード部350を更に有する。nビットの場合のAD変換出力VOi(i=1〜n−1)を得るための回路は、式(32)により設計できる。

【数32】

【0077】

Ci,1、Cj,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、式(33)、式(34)のように、フローティングゲート−基板間容量Ci,0(図示していない)、Cj,0(図示していない)と同容量である。

【0078】

【数33】

【数34】

【0079】

Ci,2、Ci,3、Cj,2、Cj,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(35)〜式(38)の関係を満たす。

【数35】

【数36】

【数37】

【数38】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0080】

図10は、図9の上からi番目(i=1〜2n−1−1)のニューロンCMOS回路νCMOSiの回路とその等価回路であり、図11は図9の上からj番目(j=2n−1+1〜2n−1)のニューロンCMOS回路νCMOSjの回路とその等価回路である。図10、図11において、Ci,0、Cj,0はフローティングゲート−基板間容量、Φi及びΦjは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φi、Φjは、次に示す式(39)、(40)のようになる。

【数39】

【数40】

【0081】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)の出力を回路Ni(i=1〜2n−1−1)により反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、ニューロンCMOS回路νCMOSj(j=2n−1+1〜2n−1)の出力をCMOS回路Nj(j=2n−1+1〜2n−1)により反転した電圧が量子化出力電圧Vj(j=2n−1+1〜2n−1)である。したがって、量子化出力電圧Vi(i=1〜2n−1)及びVj(j=2n−1+1〜2n−1)は、式(41)、式(42)のようになる。

【数41】

【数42】

【0082】

式(41)に、式(33)、式(35)、式(36)を代入し整理すると、式(43)のようになる。また、式(42)に式(34)、式(37)、式(38)を代入し整理すると、式(44)のようになる。

【数43】

【数44】

【0083】

【0084】

【0085】

【0086】

すななち、nビットフラッシュ型AD変換器200は、最上位ビットを得るために必要な電源電圧VDDの1/2を閾値とする信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に2個の閾値を判定させることにより回路規模を1/2にしている。同様に、上位2ビットの信号またはこれを得るために必要な電源電圧VDDの1/4、2/4、3/4を閾値とする信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に4個の閾値を判定させることにより回路規模を1/4にすることも可能である。さらに、上位kビットの信号またはこれを得るために必要な信号を事前に発生させ、これをニューロンCMOS回路に印加し、1個のニューロンCMOS回路に2k個の閾値を判定させることにより回路規模を1/2kにすることも可能である。

【実施例】

【0087】

(実施例)

図12は、図4に示した本発明の実施形態に係る4ビットフラッシュ型AD変換器100のシミュレーション結果である。本実施例のシミュレーションは、回路シミュレータHSPICEを用いて行なった。本実施例においては、Cuを0.05pFとして計算した。図12に示したように、4ビットフラッシュ型AD変換器100は、アナログ入力電圧VINを4ビットのデジタル値に変換してAD変換出力VO1〜VO4を出力することができる。

【符号の説明】

【0088】

100:4ビットフラッシュ型AD変換器、130:量子化出力部、150:エンコード部、200:nビットフラッシュ型AD変換器、230:量子化出力部、250:エンコード部、300:nビットフラッシュ型AD変換器、330:量子化出力部、350:エンコード部、900:4ビットAD変換器、901:ニューロンCMOS回路、903:ニューロンCMOS回路、905:ニューロンCMOS回路、991:ニューロンCMOS回路901の等価回路

【特許請求の範囲】

【請求項1】

第1のCMOS回路と、

共通するフローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、

前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、

前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項2】

前記ニューロンCMOS回路は、

電源電圧が印加され、第1の容量を有する第1のゲートと、

アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、

前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えることを特徴とする請求項1に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項3】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の2n−1倍に等しく、前記第3の容量は前記基本容量の(2n−1−i)倍に等しく、

前記iは1番目の前記ニューロンCMOS回路から2n−1−1番目の前記ニューロンCMOS回路に対応する整数であることを特徴とする請求項1又は2に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項4】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であることを特徴とする請求項3に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項5】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する2n−1個のCMOS回路を備えることを特徴とする請求項1乃至4の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項6】

前記エンコード部は、前記量子化出力電圧をVi(i=1〜2n−1−1)、前記デジタル変換出力端子に出力される電圧をVOi(i=1〜n−2)とすると、i番目のデジタル変換出力端子に出力される電圧VOi(i=1〜n−2)と、前記量子化出力電圧をVi(i=1〜2n−1−1)とは、以下の式の関係を満たすことを特徴とする請求項1乃至5の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項7】

第1のCMOS回路と、

共通するフローティングゲートを有し、3個のゲートがフローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに接続する7個のニューロンCMOS回路と、を備える量子化出力部と、

前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、

前記量子化出力部又は前記エンコード部に接続する4個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項8】

前記ニューロンCMOS回路は、

電源電圧が印加され、第1の容量を有する第1のゲートと、

アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、

前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えることを特徴とする請求項7に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項9】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の8倍に等しく、前記第3の容量は前記基本容量の(8−i)倍に等しく、

前記iは1番目の前記ニューロンCMOS回路から7番目の前記ニューロンCMOS回路に対応する整数であることを特徴とする請求項7又は8に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項10】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であることを特徴とする請求項9に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項11】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する8個のCMOS回路を備えることを特徴とする請求項7乃至10の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項12】

前記エンコード部は、

偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路にそれぞれ直列に接続する3個のCMOS回路と、

奇数番目の前記ニューロンCMOS回路に接続する4個の前記CMOS回路と、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する3個の前記CMOS回路と、に接続し、7個の前記CMOS回路から出力される量子化出力電圧を演算する7個のNAND回路と、前記7個のNAND回路に接続する1個のNAND回路と、

2番目及び6番目の前記ニューロンCMOS回路に接続する前記CMOS回路と、4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路と、に接続し、3個の前記CMOS回路から出力される量子化出力電圧を演算する3個のNAND回路と、前記3個のNAND回路に接続する1個のNAND回路と、を備えることを特徴とする請求項7乃至11の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項13】

前記デジタル変換出力端子は、

前記第1のCMOS回路に直列に接続するCMOS回路に接続し、第1のビットを出力する第1のデジタル変換出力端子と、

前記4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路に接続し、第2のビットを出力する第2のデジタル変換出力端子と、

前記3個のNAND回路に接続するNAND回路に接続し、第3のビットを出力する第3のデジタル変換出力端子と、

前記7個のNAND回路に接続するNAND回路に接続し、第4のビットを出力する第4のデジタル変換出力端子と、を備えることを特徴とする請求項7乃至12の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項1】

第1のCMOS回路と、

共通するフローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、

前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、

前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項2】

前記ニューロンCMOS回路は、

電源電圧が印加され、第1の容量を有する第1のゲートと、

アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、

前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えることを特徴とする請求項1に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項3】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の2n−1倍に等しく、前記第3の容量は前記基本容量の(2n−1−i)倍に等しく、

前記iは1番目の前記ニューロンCMOS回路から2n−1−1番目の前記ニューロンCMOS回路に対応する整数であることを特徴とする請求項1又は2に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項4】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であることを特徴とする請求項3に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項5】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する2n−1個のCMOS回路を備えることを特徴とする請求項1乃至4の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項6】

前記エンコード部は、前記量子化出力電圧をVi(i=1〜2n−1−1)、前記デジタル変換出力端子に出力される電圧をVOi(i=1〜n−2)とすると、i番目のデジタル変換出力端子に出力される電圧VOi(i=1〜n−2)と、前記量子化出力電圧をVi(i=1〜2n−1−1)とは、以下の式の関係を満たすことを特徴とする請求項1乃至5の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項7】

第1のCMOS回路と、

共通するフローティングゲートを有し、3個のゲートがフローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに接続する7個のニューロンCMOS回路と、を備える量子化出力部と、

前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、

前記量子化出力部又は前記エンコード部に接続する4個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項8】

前記ニューロンCMOS回路は、

電源電圧が印加され、第1の容量を有する第1のゲートと、

アナログ入力電圧が印加され、第2の容量を有する第2のゲートと、

前記第1のCMOS回路と接続し、第3の容量を有する第3のゲートと、を備えることを特徴とする請求項7に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項9】

前記第1の容量は基板と前記フローティングゲートとの間の容量に等しく、前記第2の容量は基本容量の8倍に等しく、前記第3の容量は前記基本容量の(8−i)倍に等しく、

前記iは1番目の前記ニューロンCMOS回路から7番目の前記ニューロンCMOS回路に対応する整数であることを特徴とする請求項7又は8に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項10】

前記ニューロンCMOS回路の閾値と前記CMOS回路の閾値は、電源電圧の1/2であることを特徴とする請求項9に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項11】

前記量子化出力部は、前記ニューロンCMOS回路と前記第1のCMOS回路とにそれぞれ直列に接続する8個のCMOS回路を備えることを特徴とする請求項7乃至10の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項12】

前記エンコード部は、

偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路にそれぞれ直列に接続する3個のCMOS回路と、

奇数番目の前記ニューロンCMOS回路に接続する4個の前記CMOS回路と、偶数番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する3個の前記CMOS回路と、に接続し、7個の前記CMOS回路から出力される量子化出力電圧を演算する7個のNAND回路と、前記7個のNAND回路に接続する1個のNAND回路と、

2番目及び6番目の前記ニューロンCMOS回路に接続する前記CMOS回路と、4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路と、に接続し、3個の前記CMOS回路から出力される量子化出力電圧を演算する3個のNAND回路と、前記3個のNAND回路に接続する1個のNAND回路と、を備えることを特徴とする請求項7乃至11の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【請求項13】

前記デジタル変換出力端子は、

前記第1のCMOS回路に直列に接続するCMOS回路に接続し、第1のビットを出力する第1のデジタル変換出力端子と、

前記4番目の前記ニューロンCMOS回路に接続した前記CMOS回路に接続する前記CMOS回路に接続し、第2のビットを出力する第2のデジタル変換出力端子と、

前記3個のNAND回路に接続するNAND回路に接続し、第3のビットを出力する第3のデジタル変換出力端子と、

前記7個のNAND回路に接続するNAND回路に接続し、第4のビットを出力する第4のデジタル変換出力端子と、を備えることを特徴とする請求項7乃至12の何れか一に記載のニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−38546(P2013−38546A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−172095(P2011−172095)

【出願日】平成23年8月5日(2011.8.5)

【出願人】(000125369)学校法人東海大学 (352)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月5日(2011.8.5)

【出願人】(000125369)学校法人東海大学 (352)

【Fターム(参考)】

[ Back to top ]