ニューロンCMOS回路及びニューロンCMOS回路を備える電子回路

【課題】フローティングゲート−基板間容量の影響を抑制し、高度な閾値の制御を実現するニューロンCMOS回路を提供する。また、そのようなニューロンCMOS回路を備える電子回路を提供する。

【解決手段】本発明の一実施形態によると、基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路が提供される。

【解決手段】本発明の一実施形態によると、基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はフローティングゲートに複数のゲートを配設したニューロンCMOS回路に関する。特に、フローティングゲート−基板間容量の影響による閾値の変動を抑制したニューロンCMOS回路に関する。また、ニューロンCMOS回路を備える電子回路に関する。

【背景技術】

【0002】

一般に利用されるコンピュータは、あらかじめ決められたプログラムに従って1つ1つ命令を実行するノイマン方式の電子回路により構成される。ノイマン方式の電子回路は、単純な数値計算に対しては非常に高速な演算が可能である。一方、複雑な演算処理を実現するために、神経細胞の機能を模したニューロコンピュータの研究が進められ、神経細胞の構造を模したMOS型半導体素子(ニューロンMOSFET)が報告されている(特許文献1)。

【0003】

ニューロンMOSFETは、フローティングゲート電極と容量結合する2個以上の入力ゲート電極を有するMOSFETであり、入力ゲート電極の各々に印加した電圧に所定の重みをかけて線形加算した値が、所定の閾値より大となった場合にのみソース及びドレイン領域間が電気的に接続されるように構成されたMOS回路である。また、pチャネルニューロンMOSFET(以下、P−νMOSという)とnチャネルニューロンMOSFET(以下、N−νMOSという)のドレインを互いに接続し、P−νMOSとN−νMOSのフローティングゲートを共通ゲートとして、2個以上の入力ゲート電極を配設した

ニューロンCMOS回路が報告されている(特許文献1、2)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−6679号公報

【特許文献2】国際公開番号 WO96/30855

【発明の概要】

【発明が解決しようとする課題】

【0005】

ニューロンCMOS回路は、複数の入力ゲート電極が配設されることから、フローティングゲートとそれぞれの入力ゲート電極との間に結合容量がそれぞれ形成される。また、上述したように、入力ゲート電極の各々に印加した電圧に所定の重みをかけて線形加算した値が、所定の閾値より大となった場合にのみソース及びドレイン領域間が電気的に接続されるように構成された回路であるため、ニューロンCMOS回路においては、高度な閾値の制御が求められる。しかし、フローティングゲート−基板間容量の影響により、入力ゲートから見た閾値が変動するという問題があった。

【0006】

本発明は、フローティングゲート−基板間容量の影響を抑制し、高度な閾値の制御を実現するニューロンCMOS回路を提供することを目的とする。また、本発明は、そのようなニューロンCMOS回路を備える電子回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一実施形態によると、基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいニューロンCMOS回路が提供される。

【0008】

前記複数の入力ゲート電極は前記共通するフローティングゲートとそれぞれ所定の容量を有し、前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力してもよい。

【0009】

前記PMOSFETのソースと前記一つの入力ゲート電極とに、電源電圧が印加されてもよい。

【0010】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェルと、前記nウェルに形成された第1のp型拡散領域と、前記基板に形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、前記フローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記フローティングゲートとの間の容量と概略等しいニューロンCMOS回路が提供される。

【0011】

前記第1のp型拡散領域と、前記一つの入力ゲート電極とに接続し、電源電圧を印加する第1の配線層と、前記第1のn型拡散領域に接続し、接地する第2の配線層と、前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、を更に備えてもよい。

【0012】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェル及びpウェルと、前記nウェルに形成された第1のp型拡散領域と、前記pウェルに形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備えるニューロンCMOS回路が提供される。

【0013】

前記基板は、不純物を含まない基板、不純物濃度の低い基板または絶縁基板であってもよい。

【0014】

前記nウェルに形成された第2のn型拡散領域と、前記pウェルに形成された第2のp型拡散領域と、を更に備えてもよい。

【0015】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェルと、前記nウェルに形成された第1のp型拡散領域と、前記基板に形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、前記nウェルは、前記フローティングゲートの半分の面積と重なるように配置されるニューロンCMOS回路が提供される。

【0016】

前記nウェルに形成された第2のn型拡散領域と、前記基板に形成された第2のp型拡散領域と、を更に備えてもよい。

【0017】

前記第1のp型拡散領域に接続し、電源電圧を印加する第1の配線層と、前記第1のn型拡散領域に接続し、接地する第2の配線層と、前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、を更に備えてもよい。

【0018】

前記複数の入力ゲート電極はそれぞれ所定の容量を有し、前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力してもよい。

【0019】

また、本発明の一実施形態によると、上記の何れかのニューロンCMOS回路を備える電子回路が提供される。

【発明の効果】

【0020】

本発明によると、フローティングゲート−基板間容量の影響による閾値変動を抑制し、高度な閾値の制御を実現するニューロンCMOS回路が提供される。また、本発明によると、そのようなニューロンCMOS回路を備える電子回路が提供される。

【図面の簡単な説明】

【0021】

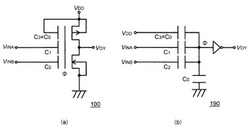

【図1】(a)は、従来のニューロンCMOS回路900の回路図であり、(b)はニューロンCMOS回路900の等価回路990の回路図である。

【図2】(a)は、本発明の一実施形態に係るニューロンCMOS回路100の回路図であり、(b)はニューロンCMOS回路100の等価回路190の回路図である。

【図3】本発明の一実施形態に係るニューロンCMOS回路100のレイアウトの一例を示す図である。

【図4】本発明の一実施形態に係るニューロンCMOS回路200のレイアウトの一例を示す図である。

【図5】本発明の一実施形態に係るニューロンCMOS回路200の等価回路290の回路図である。

【図6】本発明の一実施形態に係るニューロンCMOS回路300のレイアウトの一例を示す図である。

【図7】本発明の一実施形態に係るニューロンCMOS回路300の等価回路390の回路図である。

【図8】本発明の一実施例に係るnビットフラッシュ型AD変換器500の回路図である。

【図9】本発明の一実施例に係るニューロンCMOS回路νCMOSiの回路とその等価回路である。

【図10】本発明の一実施例に係るニューロンCMOS回路νCMOSjの回路とその等価回路である。

【発明を実施するための形態】

【0022】

以下、図面を参照して本発明に係るニューロンCMOS回路について詳細に説明する。但し、本発明のニューロンCMOS回路は多くの異なる態様で実施することも可能であり、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、本実施の形態及び実施例で参照する図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0023】

本発明者は、フローティングゲート−基板間容量の影響を抑制することにより、ニューロンCMOS回路の閾値の高度な制御が実現できることを見出した。すなわち、本発明は、フローティングゲート−基板間容量の影響による閾値の変動を抑制する機構をニューロンCMOS回路に配設することにより、ニューロンCMOS回路の閾値の高度な制御を実現するものである。なお、本発明に係るニューロンCMOS回路は、フローティングゲートにn個(nは2以上の整数)の入力ゲート電極を備える回路であるが、以下の実施形態においては、理解を容易にするため、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明する。

【0024】

(実施形態1)

図1(a)は、従来のニューロンCMOS回路900の回路図であり、図1(b)はニューロンCMOS回路900の等価回路990の回路図である。ここで、2つの入力ゲート電極を配設したニューロンCMOS回路900を例に説明する。C1、C2はニューロンCMOS回路900の閾値を決定するための容量であり、入力ゲート電極とフローティングゲートとの間の容量である。入力ゲート電極からはそれぞれ入力電圧VINA、入力電圧VINBが印加される。また、Φは基板電位を基準としたフローティングゲートの電圧であり、フローティングゲート−基板間の容量をC0とする。ニューロンCMOS回路900のpチャネルニューロンMOSFET(以下、PMOSという)のソースは電源電圧VDDが印加され、nチャネルMOSFET(以下、NMOSという)のソースは接地される。また、ニューロンCMOS回路900のPMOSとNMOSのドレインは、出力電圧VOYを出力する。

【0025】

このとき、ニューロンCMOS回路900のフローティングゲートの電圧Φは、次に示す式(1)のようになる。

【数1】

【0026】

ニューロンCMOS回路900は、電圧Φ<閾値電圧VTHのとき、出力電圧VOYとして電源電圧VDDを出力する。また、電圧Φ≧閾値電圧VTHのとき、出力電圧VOYとして接地電圧(一般に0V)を出力する。

【0027】

ここで、ニューロンCMOS回路900において、フローティングゲート−基板間容量C0は、フローティングゲートの面積に比例して生じる。フローティングゲートに配設する入力ゲート電極の数が増加すると、フローティングゲートの面積も増大し、結果として容量C0は無視できなくなる。このため、ニューロンCMOS回路の閾値は容量C0の影響を受けて変動する。したがって、フローティングゲート−基板間容量の影響による変動を抑制する機構が必要となる。

【0028】

図2(a)は、本発明の一実施形態に係るニューロンCMOS回路100の回路図であり、図2(b)はニューロンCMOS回路100の等価回路190の回路図である。ニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極がフローティングゲートに配設され、この入力ゲート電極に電源電圧VDDが印加される。それ以外の構成はニューロンCMOS回路900と同様である。本実施形態に係るニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3をフローティングゲートに備えることにより、容量C0の影響をキャンセルして、ニューロンCMOS回路100の閾値の高度な制御を実現することができる。なお、本実施形態において、フローティングゲート−基板間の容量C0と第3の入力ゲート電極とフローティングゲート間の容量C3とが等しいとは、理論上の値が等しいことを示し、実際の回路においては、回路の製造プロセスにおいて許容される範囲で容量が概略等しいことを意味する。

【0029】

フローティングゲート−基板間容量C0と等しい容量C3を設けることにより、フローティングゲート−基板間容量C0の影響をキャンセルできることを、数式を使って説明する。ニューロンCMOS回路100のフローティングゲートの電圧Φは、次に示す式(2)のようになる。

【数2】

【0030】

ニューロンCMOS回路100のフローティングゲート電圧に対する閾値を電源電圧VDDの1/2とすると、ニューロンCMOS回路100の出力は、式(3)のようになる。

【数3】

【0031】

式(3)に、C0=C3を代入し整理すると、式(4)となる。

【数4】

【0032】

式(4)より、ニューロンCMOS回路100は、フローティングゲート−基板間容量C0の影響を受けないことがわかる。

【0033】

図3は、ニューロンCMOS回路100のレイアウトの一例を示す図である。ニューロンCMOS回路100は、基板(図示せず)のnウェル101が形成された領域上にn型拡散領域111とp型拡散領域113が形成され、基板上にn型拡散領域115とp型拡散領域117が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極131、133及び135が配置される。フローティングゲート121と、入力ゲート電極131、133及び135との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路100に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路100の出力電圧VOYを出力するための配線である。

【0034】

配線層151と、n型拡散領域111、p型拡散領域113及び入力ゲート電極135とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域117とは、コンタクトホール161により接続される。入力ゲート電極131と配線層141、入力ゲート電極133と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0035】

ニューロンCMOS回路100は、入力ゲート電極131、133及び135の膜厚と面積を調整することにより、入力ゲート電極131、133及び135とフローティングゲート121との間の容量C1、C2及びC3を所望の容量に設計することができる。上述したように、容量C3は、フローティングゲート−基板間容量C0と等しくなるように設計する。本実施形態においては、回路の製造プロセスにおいて許容される範囲でフローティングゲート−基板間の容量C0と第3の入力ゲート電極とフローティングゲート間の容量C3とを概略等しくする。

【0036】

なお、本実施形態に係るニューロンCMOS回路100には、半導体装置に製造に用いられる公知の材料を利用することができる。また、ニューロンCMOS回路100の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路100に用いる材料及び製造方法の詳細な説明は省略する。

【0037】

このように、本実施形態に係るニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極をフローティングゲートに配設し、第3の入力ゲート電極に電源電圧VDDが印加することにより、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路100の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【0038】

(実施形態2)

実施形態1においては、フローティングゲート−基板間容量の影響による閾値の変動を抑制するために、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極をフローティングゲートに配設したが、本実施形態に係るニューロンCMOS回路200においては、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域、具体的には、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上にフローティングゲートを配置することで、フローティングゲート−基板間の容量を入力ゲート−フローティングゲート間の容量に比べて無視できるくらいに小さくし、フローティングゲート−基板間容量の影響を抑制したニューロンCMOS回路について説明する。

【0039】

図4は、本発明の一実施形態に係るニューロンCMOS回路200のレイアウトの一例を示す図である。また、図5は、ニューロンCMOS回路200の等価回路290の回路図である。ニューロンCMOS回路200は、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用いた場合に適用可能である。なお、ニューロンCMOS回路200において、ニューロンCMOS回路100と同様の構成には同じ符号を付した。

【0040】

ニューロンCMOS回路200は、フローティングゲート121を、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上、すわなち、nウェル101およびpウェル203と重ならないように配置することによりフローティングゲート−基板間容量を入力ゲート−フローティングゲート間の容量に比べて無視できるくらいに小さくしている。ニューロンCMOS回路200の等価回路290においてフローティングゲート−基板間容量C0が省略されているのはそのためである。

【0041】

ニューロンCMOS回路200は、基板(図示せず)のnウェル101が形成された領域上にn型拡散領域111とp型拡散領域113が形成され、基板のpウェル203が形成された領域上にとn型拡散領域115とp型拡散領域117が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。このときフローティングゲート121は、MOSFETを構成するのに必要な部分を除き、nウェル101、pウェル203と重ならないように配置する。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極231及び233が配置される。フローティングゲート121と、入力ゲート電極231及び233との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路200に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路200の出力電圧VOYを出力するための配線である。

【0042】

配線層151と、n型拡散領域111及びp型拡散領域113とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域117とは、コンタクトホール161により接続される。入力ゲート電極231と配線層141、入力ゲート電極233と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0043】

ニューロンCMOS回路200は、入力ゲート電極231及び233の面積を調整することにより、入力ゲート電極231及び233とフローティングゲート121との間の容量C1及びC2を所望の容量に設計することができる。

【0044】

なお、本実施形態に係るニューロンCMOS回路200には、不純物を含まない基板や不純物濃度の低い基板または絶縁基板であれば、半導体装置に製造に用いられる公知の材料を利用することができる。不純物濃度の低い基板としては、例えば、p型のシリコン基板で1015 atoms/cm3以下の不純物濃度の基板を用いることができる。また、ニューロンCMOS回路200の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路200に用いる材料及び製造方法の詳細な説明は省略する。

【0045】

このように、本実施形態に係るニューロンCMOS回路200は、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域、具体的には、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上にフローティングゲートを配置するように設計することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路200の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【0046】

(実施形態3)

実施形態2においては、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域上にフローティングゲートを配置するように設計することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制する例を説明したが、本実施形態に係るニューロンCMOS回路300においては、フローティングゲートの半分の面積をnウェルと重なるように設計することにより、フローティングゲート−基板間容量の影響を抑制したニューロンCMOS回路について説明する。

【0047】

図6は、本発明の一実施形態に係るニューロンCMOS回路300のレイアウトの一例を示す図である。また、図7は、ニューロンCMOS回路300の等価回路390の回路図である。図7において、容量CDはフローティングゲート−電源間容量である。なお、ニューロンCMOS回路300において、ニューロンCMOS回路100及びニューロンCMOS回路200と同様の構成には同じ符号を付した。

【0048】

ニューロンCMOS回路300はフローティングゲート121の半分の面積と重なるように、nウェル301を基板(図示せず)に形成する。nウェル301が形成された領域上にn型拡散領域311とp型拡散領域113が形成され、基板上にn型拡散領域115とp型拡散領域317が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極231及び233が配置される。フローティングゲート121と、入力ゲート電極231及び233との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路300に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路300の出力電圧VOYを出力するための配線である。

【0049】

配線層151と、n型拡散領域311及びp型拡散領域113とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域317とは、コンタクトホール161により接続される。入力ゲート電極231と配線層141、入力ゲート電極233と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0050】

ニューロンCMOS回路300は、入力ゲート電極231及び233の面積を調整することにより、入力ゲート電極231及び233とフローティングゲート121との間の容量C1及びC2を所望の容量に設計することができる。

【0051】

ニューロンCMOS回路300においては、フローティングゲート121の半分の面積と重なるようにnウェル301を配設することにより、フローティングゲート−基板間容量C0とフローティングゲート−電源間容量CDとが等しくなり、フローティングゲート121が基板や電源に対して持つ容量の影響によりニューロンCMOS回路の閾値電圧が変動するのを抑制することができる。

【0052】

このことを、数式を使って説明する。ニューロンCMOS回路300のフローティングゲートの電圧Φは、次に示す式(5)のようになる。

【数5】

【0053】

ニューロンMOS回路300のフローティングゲート電圧に対する閾値を電源電圧VDDの1/2とすると、ニューロンMOS回路300の出力は、式(6)のようになる。

【数6】

【0054】

式(6)に、C0=CDを代入し整理すると、式(7)となる。

【数7】

【0055】

式(7)より、本実施形態に係るニューロンCMOS回路300は、フローティングゲート−基板間容量C0の影響を受けないことがわかる。

【0056】

なお、本実施形態に係るニューロンCMOS回路300には、半導体装置に製造に用いられる公知の材料を利用することができる。また、ニューロンCMOS回路300の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路300に用いる材料及び製造方法の詳細な説明は省略する。

【0057】

このように、本実施形態に係るニューロンCMOS回路300は、フローティングゲートの半分の面積と重なるようにnウェルを配設することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路300の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態のおいては、p基板を用いた例について説明したが、n基板を用いた場合も、フローティングゲートの半分の面積をpウェルと重なるように設計することにより同様の効果を得ることができる。また、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【実施例】

【0058】

上述した本発明に係るニューロンCMOS回路を用いた電子回路の一例として、本発明の一実施形態に係るニューロンCMOS回路100と同等の回路を用いたnビットフラッシュ型AD変換器について以下に説明する。

【0059】

(nビットフラッシュ型AD変換器)

本実施例に係るnビットフラッシュ型AD変換器500は、量子化出力部530とエンコード部550を有する。図8は、本発明の一実施形態に係るnビットフラッシュ型AD変換器500の回路図である。図8においてNi(i=1〜2n−1−1)、Nj(j=2n−1+1〜2n−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)、νCMOSj(j=2n−1+1〜2n−1)はニューロンCMOS回路である。nビットフラッシュ型AD変換器500は、νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)、すなわち、2n−2個のニューロンCMOS回路と1個のCMOS回路NIN1とがアナログ入力電圧VINを入力する端子に接続し、各ニューロンCMOS回路には波形整形用のCMOS回路が1個ずつ直列に接続し、CMOS回路NIN1にはCMOS回路NIN2が直列に接続する。

【0060】

ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)及びCj,1、Cj,2、Cj,3(j=2n−1+1〜2n−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。nビットフラッシュ型AD変換器500においては、ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)の容量Ci,1(i=1〜2n−1−1)及びCj,1(j=2n−1+1〜2n−1)を有するゲートには電源電圧VDDが印加され、容量Ci,2(i=1〜2n−1−1)及びCj,2(j=2n−1+1〜2n−1)を有するゲートにはアナログ入力電圧VINが印加される。νCMOSi(i=1〜2n−1−1)の容量Ci,3(i=1〜2n−1−1)を有するゲートには電源電圧VDDが印加され、νCMOSj(j=2n−1+1〜2n−1)の容量Cj,3(j=2n−1+1〜2n−1)を有するゲートは接地される。アナログ入力電圧VINは、CMOS回路NIN2に直列に接続したCMOS回路NIN1にも印加される。

【0061】

また、nビットフラッシュ型AD変換器500は、エンコード部550を更に有する。nビットの場合のAD変換出力VOi(i=1〜n−1)を得るための回路は、式(8)により設計できる。

【数8】

【0062】

上述の実施形態において説明したように、容量Ci,1、Cj,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、入力ゲート電極とフローティングゲート間の容量である。したがって、容量Ci,1、Cj,1は、式(9)、式(10)のように、フローティングゲート−基板間容量Ci,0(図示していない)、Cj,0(図示していない)と同容量である。なお、実際の回路においては、回路の製造プロセスにおいて許容される範囲で容量が概略等しいことを意味する。

【0063】

【数9】

【数10】

【0064】

Ci,2、Ci,3、Cj,2、Cj,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(11)〜式(14)の関係を満たす。なお、Cuは半導体の設計上で最適に設定される基本容量である。

【数11】

【数12】

【数13】

【数14】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0065】

図9は、図8の上からi番目(i=1〜2n−1−1)のニューロンCMOS回路νCMOSiの回路とその等価回路であり、図10は図8の上からj番目(j=2n−1+1〜2n−1)のニューロンCMOS回路νCMOSjの回路とその等価回路である。図9、図10において、Ci,0、Cj,0はフローティングゲート−基板間容量、Φi及びΦjは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φi、Φjは、次に示す式(15)、式(16)のようになる。

【数15】

【数16】

【0066】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)の出力を回路Ni(i=1〜2n−1−1)により反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、ニューロンCMOS回路νCMOSj(j=2n−1+1〜2n−1)の出力をCMOS回路Nj(j=2n−1+1〜2n−1)により反転した電圧が量子化出力電圧Vj(j=2n−1+1〜2n−1)である。したがって、量子化出力電圧Vi(i=1〜2n−1)及びVj(j=2n−1+1〜2n−1)は、式(17)、式(18)のようになる。

【数17】

【数18】

【0067】

式(17)に、式(9)、式(11)、式(12)を代入し整理すると、式(19)のようになる。また、式(18)に式(10)、式(13)、式(14)を代入し整理すると、式(20)のようになる。

【数19】

【数20】

【0068】

【0069】

以上説明したように、本実施例に係るnビットフラッシュ型AD変換器500は、電圧を比較する素子としてコンパレータに比べて回路規模が小さく消費電力の少ないニューロンCMOS回路を用いるため、従来のフラッシュ型AD変換器に比して十分に消費電力の少ないフラッシュ型AD変換器を実現することができる。

【0070】

なお、本実施例においてはニューロンCMOS回路100と同等の回路を用いた例を説明したが、本実施例に係るnビットフラッシュ型AD変換器500には、ニューロンCMOS回路200またはニューロンCMOS回路300を利用することもできる。また、本実施例においてはnビットフラッシュ型AD変換器を例に説明したが、本発明に係るニューロンCMOS回路は、様々な電子回路に適用可能である。

【符号の説明】

【0071】

100:ニューロンCMOS回路、101:nウェル、111:n型拡散領域、113:p型拡散領域、115:n型拡散領域、117:p型拡散領域、121:フローティングゲート、131:入力ゲート電極、133:入力ゲート電極、135:入力ゲート電極、141:配線層、143:配線層、151:配線層、153:配線層、155:配線層、190:ニューロンCMOS回路100の等価回路、200:ニューロンCMOS回路、203:pウェル、231:入力ゲート電極、233:入力ゲート電極、290:ニューロンCMOS回路200の等価回路、300:ニューロンCMOS回路、301:nウェル、311:n型拡散領域、317:p型拡散領域、390:ニューロンCMOS回路300の等価回路、500:nビットフラッシュ型AD変換器、530:量子化出力部、550:エンコード部

【技術分野】

【0001】

本発明はフローティングゲートに複数のゲートを配設したニューロンCMOS回路に関する。特に、フローティングゲート−基板間容量の影響による閾値の変動を抑制したニューロンCMOS回路に関する。また、ニューロンCMOS回路を備える電子回路に関する。

【背景技術】

【0002】

一般に利用されるコンピュータは、あらかじめ決められたプログラムに従って1つ1つ命令を実行するノイマン方式の電子回路により構成される。ノイマン方式の電子回路は、単純な数値計算に対しては非常に高速な演算が可能である。一方、複雑な演算処理を実現するために、神経細胞の機能を模したニューロコンピュータの研究が進められ、神経細胞の構造を模したMOS型半導体素子(ニューロンMOSFET)が報告されている(特許文献1)。

【0003】

ニューロンMOSFETは、フローティングゲート電極と容量結合する2個以上の入力ゲート電極を有するMOSFETであり、入力ゲート電極の各々に印加した電圧に所定の重みをかけて線形加算した値が、所定の閾値より大となった場合にのみソース及びドレイン領域間が電気的に接続されるように構成されたMOS回路である。また、pチャネルニューロンMOSFET(以下、P−νMOSという)とnチャネルニューロンMOSFET(以下、N−νMOSという)のドレインを互いに接続し、P−νMOSとN−νMOSのフローティングゲートを共通ゲートとして、2個以上の入力ゲート電極を配設した

ニューロンCMOS回路が報告されている(特許文献1、2)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平3−6679号公報

【特許文献2】国際公開番号 WO96/30855

【発明の概要】

【発明が解決しようとする課題】

【0005】

ニューロンCMOS回路は、複数の入力ゲート電極が配設されることから、フローティングゲートとそれぞれの入力ゲート電極との間に結合容量がそれぞれ形成される。また、上述したように、入力ゲート電極の各々に印加した電圧に所定の重みをかけて線形加算した値が、所定の閾値より大となった場合にのみソース及びドレイン領域間が電気的に接続されるように構成された回路であるため、ニューロンCMOS回路においては、高度な閾値の制御が求められる。しかし、フローティングゲート−基板間容量の影響により、入力ゲートから見た閾値が変動するという問題があった。

【0006】

本発明は、フローティングゲート−基板間容量の影響を抑制し、高度な閾値の制御を実現するニューロンCMOS回路を提供することを目的とする。また、本発明は、そのようなニューロンCMOS回路を備える電子回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一実施形態によると、基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいニューロンCMOS回路が提供される。

【0008】

前記複数の入力ゲート電極は前記共通するフローティングゲートとそれぞれ所定の容量を有し、前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力してもよい。

【0009】

前記PMOSFETのソースと前記一つの入力ゲート電極とに、電源電圧が印加されてもよい。

【0010】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェルと、前記nウェルに形成された第1のp型拡散領域と、前記基板に形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、前記フローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記フローティングゲートとの間の容量と概略等しいニューロンCMOS回路が提供される。

【0011】

前記第1のp型拡散領域と、前記一つの入力ゲート電極とに接続し、電源電圧を印加する第1の配線層と、前記第1のn型拡散領域に接続し、接地する第2の配線層と、前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、を更に備えてもよい。

【0012】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェル及びpウェルと、前記nウェルに形成された第1のp型拡散領域と、前記pウェルに形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備えるニューロンCMOS回路が提供される。

【0013】

前記基板は、不純物を含まない基板、不純物濃度の低い基板または絶縁基板であってもよい。

【0014】

前記nウェルに形成された第2のn型拡散領域と、前記pウェルに形成された第2のp型拡散領域と、を更に備えてもよい。

【0015】

また、本発明の一実施形態によると、基板と、前記基板に形成されたnウェルと、前記nウェルに形成された第1のp型拡散領域と、前記基板に形成された第1のn型拡散領域と、前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、前記nウェルは、前記フローティングゲートの半分の面積と重なるように配置されるニューロンCMOS回路が提供される。

【0016】

前記nウェルに形成された第2のn型拡散領域と、前記基板に形成された第2のp型拡散領域と、を更に備えてもよい。

【0017】

前記第1のp型拡散領域に接続し、電源電圧を印加する第1の配線層と、前記第1のn型拡散領域に接続し、接地する第2の配線層と、前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、を更に備えてもよい。

【0018】

前記複数の入力ゲート電極はそれぞれ所定の容量を有し、前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力してもよい。

【0019】

また、本発明の一実施形態によると、上記の何れかのニューロンCMOS回路を備える電子回路が提供される。

【発明の効果】

【0020】

本発明によると、フローティングゲート−基板間容量の影響による閾値変動を抑制し、高度な閾値の制御を実現するニューロンCMOS回路が提供される。また、本発明によると、そのようなニューロンCMOS回路を備える電子回路が提供される。

【図面の簡単な説明】

【0021】

【図1】(a)は、従来のニューロンCMOS回路900の回路図であり、(b)はニューロンCMOS回路900の等価回路990の回路図である。

【図2】(a)は、本発明の一実施形態に係るニューロンCMOS回路100の回路図であり、(b)はニューロンCMOS回路100の等価回路190の回路図である。

【図3】本発明の一実施形態に係るニューロンCMOS回路100のレイアウトの一例を示す図である。

【図4】本発明の一実施形態に係るニューロンCMOS回路200のレイアウトの一例を示す図である。

【図5】本発明の一実施形態に係るニューロンCMOS回路200の等価回路290の回路図である。

【図6】本発明の一実施形態に係るニューロンCMOS回路300のレイアウトの一例を示す図である。

【図7】本発明の一実施形態に係るニューロンCMOS回路300の等価回路390の回路図である。

【図8】本発明の一実施例に係るnビットフラッシュ型AD変換器500の回路図である。

【図9】本発明の一実施例に係るニューロンCMOS回路νCMOSiの回路とその等価回路である。

【図10】本発明の一実施例に係るニューロンCMOS回路νCMOSjの回路とその等価回路である。

【発明を実施するための形態】

【0022】

以下、図面を参照して本発明に係るニューロンCMOS回路について詳細に説明する。但し、本発明のニューロンCMOS回路は多くの異なる態様で実施することも可能であり、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、本実施の形態及び実施例で参照する図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

【0023】

本発明者は、フローティングゲート−基板間容量の影響を抑制することにより、ニューロンCMOS回路の閾値の高度な制御が実現できることを見出した。すなわち、本発明は、フローティングゲート−基板間容量の影響による閾値の変動を抑制する機構をニューロンCMOS回路に配設することにより、ニューロンCMOS回路の閾値の高度な制御を実現するものである。なお、本発明に係るニューロンCMOS回路は、フローティングゲートにn個(nは2以上の整数)の入力ゲート電極を備える回路であるが、以下の実施形態においては、理解を容易にするため、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明する。

【0024】

(実施形態1)

図1(a)は、従来のニューロンCMOS回路900の回路図であり、図1(b)はニューロンCMOS回路900の等価回路990の回路図である。ここで、2つの入力ゲート電極を配設したニューロンCMOS回路900を例に説明する。C1、C2はニューロンCMOS回路900の閾値を決定するための容量であり、入力ゲート電極とフローティングゲートとの間の容量である。入力ゲート電極からはそれぞれ入力電圧VINA、入力電圧VINBが印加される。また、Φは基板電位を基準としたフローティングゲートの電圧であり、フローティングゲート−基板間の容量をC0とする。ニューロンCMOS回路900のpチャネルニューロンMOSFET(以下、PMOSという)のソースは電源電圧VDDが印加され、nチャネルMOSFET(以下、NMOSという)のソースは接地される。また、ニューロンCMOS回路900のPMOSとNMOSのドレインは、出力電圧VOYを出力する。

【0025】

このとき、ニューロンCMOS回路900のフローティングゲートの電圧Φは、次に示す式(1)のようになる。

【数1】

【0026】

ニューロンCMOS回路900は、電圧Φ<閾値電圧VTHのとき、出力電圧VOYとして電源電圧VDDを出力する。また、電圧Φ≧閾値電圧VTHのとき、出力電圧VOYとして接地電圧(一般に0V)を出力する。

【0027】

ここで、ニューロンCMOS回路900において、フローティングゲート−基板間容量C0は、フローティングゲートの面積に比例して生じる。フローティングゲートに配設する入力ゲート電極の数が増加すると、フローティングゲートの面積も増大し、結果として容量C0は無視できなくなる。このため、ニューロンCMOS回路の閾値は容量C0の影響を受けて変動する。したがって、フローティングゲート−基板間容量の影響による変動を抑制する機構が必要となる。

【0028】

図2(a)は、本発明の一実施形態に係るニューロンCMOS回路100の回路図であり、図2(b)はニューロンCMOS回路100の等価回路190の回路図である。ニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極がフローティングゲートに配設され、この入力ゲート電極に電源電圧VDDが印加される。それ以外の構成はニューロンCMOS回路900と同様である。本実施形態に係るニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3をフローティングゲートに備えることにより、容量C0の影響をキャンセルして、ニューロンCMOS回路100の閾値の高度な制御を実現することができる。なお、本実施形態において、フローティングゲート−基板間の容量C0と第3の入力ゲート電極とフローティングゲート間の容量C3とが等しいとは、理論上の値が等しいことを示し、実際の回路においては、回路の製造プロセスにおいて許容される範囲で容量が概略等しいことを意味する。

【0029】

フローティングゲート−基板間容量C0と等しい容量C3を設けることにより、フローティングゲート−基板間容量C0の影響をキャンセルできることを、数式を使って説明する。ニューロンCMOS回路100のフローティングゲートの電圧Φは、次に示す式(2)のようになる。

【数2】

【0030】

ニューロンCMOS回路100のフローティングゲート電圧に対する閾値を電源電圧VDDの1/2とすると、ニューロンCMOS回路100の出力は、式(3)のようになる。

【数3】

【0031】

式(3)に、C0=C3を代入し整理すると、式(4)となる。

【数4】

【0032】

式(4)より、ニューロンCMOS回路100は、フローティングゲート−基板間容量C0の影響を受けないことがわかる。

【0033】

図3は、ニューロンCMOS回路100のレイアウトの一例を示す図である。ニューロンCMOS回路100は、基板(図示せず)のnウェル101が形成された領域上にn型拡散領域111とp型拡散領域113が形成され、基板上にn型拡散領域115とp型拡散領域117が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極131、133及び135が配置される。フローティングゲート121と、入力ゲート電極131、133及び135との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路100に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路100の出力電圧VOYを出力するための配線である。

【0034】

配線層151と、n型拡散領域111、p型拡散領域113及び入力ゲート電極135とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域117とは、コンタクトホール161により接続される。入力ゲート電極131と配線層141、入力ゲート電極133と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0035】

ニューロンCMOS回路100は、入力ゲート電極131、133及び135の膜厚と面積を調整することにより、入力ゲート電極131、133及び135とフローティングゲート121との間の容量C1、C2及びC3を所望の容量に設計することができる。上述したように、容量C3は、フローティングゲート−基板間容量C0と等しくなるように設計する。本実施形態においては、回路の製造プロセスにおいて許容される範囲でフローティングゲート−基板間の容量C0と第3の入力ゲート電極とフローティングゲート間の容量C3とを概略等しくする。

【0036】

なお、本実施形態に係るニューロンCMOS回路100には、半導体装置に製造に用いられる公知の材料を利用することができる。また、ニューロンCMOS回路100の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路100に用いる材料及び製造方法の詳細な説明は省略する。

【0037】

このように、本実施形態に係るニューロンCMOS回路100は、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極をフローティングゲートに配設し、第3の入力ゲート電極に電源電圧VDDが印加することにより、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路100の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【0038】

(実施形態2)

実施形態1においては、フローティングゲート−基板間容量の影響による閾値の変動を抑制するために、フローティングゲート−基板間容量C0と等しい容量C3を有する第3の入力ゲート電極をフローティングゲートに配設したが、本実施形態に係るニューロンCMOS回路200においては、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域、具体的には、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上にフローティングゲートを配置することで、フローティングゲート−基板間の容量を入力ゲート−フローティングゲート間の容量に比べて無視できるくらいに小さくし、フローティングゲート−基板間容量の影響を抑制したニューロンCMOS回路について説明する。

【0039】

図4は、本発明の一実施形態に係るニューロンCMOS回路200のレイアウトの一例を示す図である。また、図5は、ニューロンCMOS回路200の等価回路290の回路図である。ニューロンCMOS回路200は、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用いた場合に適用可能である。なお、ニューロンCMOS回路200において、ニューロンCMOS回路100と同様の構成には同じ符号を付した。

【0040】

ニューロンCMOS回路200は、フローティングゲート121を、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上、すわなち、nウェル101およびpウェル203と重ならないように配置することによりフローティングゲート−基板間容量を入力ゲート−フローティングゲート間の容量に比べて無視できるくらいに小さくしている。ニューロンCMOS回路200の等価回路290においてフローティングゲート−基板間容量C0が省略されているのはそのためである。

【0041】

ニューロンCMOS回路200は、基板(図示せず)のnウェル101が形成された領域上にn型拡散領域111とp型拡散領域113が形成され、基板のpウェル203が形成された領域上にとn型拡散領域115とp型拡散領域117が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。このときフローティングゲート121は、MOSFETを構成するのに必要な部分を除き、nウェル101、pウェル203と重ならないように配置する。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極231及び233が配置される。フローティングゲート121と、入力ゲート電極231及び233との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路200に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路200の出力電圧VOYを出力するための配線である。

【0042】

配線層151と、n型拡散領域111及びp型拡散領域113とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域117とは、コンタクトホール161により接続される。入力ゲート電極231と配線層141、入力ゲート電極233と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0043】

ニューロンCMOS回路200は、入力ゲート電極231及び233の面積を調整することにより、入力ゲート電極231及び233とフローティングゲート121との間の容量C1及びC2を所望の容量に設計することができる。

【0044】

なお、本実施形態に係るニューロンCMOS回路200には、不純物を含まない基板や不純物濃度の低い基板または絶縁基板であれば、半導体装置に製造に用いられる公知の材料を利用することができる。不純物濃度の低い基板としては、例えば、p型のシリコン基板で1015 atoms/cm3以下の不純物濃度の基板を用いることができる。また、ニューロンCMOS回路200の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路200に用いる材料及び製造方法の詳細な説明は省略する。

【0045】

このように、本実施形態に係るニューロンCMOS回路200は、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域、具体的には、MOSFETを構成するのに必要な部分を除き、不純物が拡散されていない領域上にフローティングゲートを配置するように設計することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路200の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【0046】

(実施形態3)

実施形態2においては、不純物を含まない基板や不純物濃度の低い基板または絶縁基板を用い、なるべく不純物が拡散されていない領域上にフローティングゲートを配置するように設計することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制する例を説明したが、本実施形態に係るニューロンCMOS回路300においては、フローティングゲートの半分の面積をnウェルと重なるように設計することにより、フローティングゲート−基板間容量の影響を抑制したニューロンCMOS回路について説明する。

【0047】

図6は、本発明の一実施形態に係るニューロンCMOS回路300のレイアウトの一例を示す図である。また、図7は、ニューロンCMOS回路300の等価回路390の回路図である。図7において、容量CDはフローティングゲート−電源間容量である。なお、ニューロンCMOS回路300において、ニューロンCMOS回路100及びニューロンCMOS回路200と同様の構成には同じ符号を付した。

【0048】

ニューロンCMOS回路300はフローティングゲート121の半分の面積と重なるように、nウェル301を基板(図示せず)に形成する。nウェル301が形成された領域上にn型拡散領域311とp型拡散領域113が形成され、基板上にn型拡散領域115とp型拡散領域317が形成されている。p型拡散領域113とn型拡散領域115の上層には、第1の絶縁層(図示せず)を介してフローティングゲート121が配置される。フローティングゲート121は、p型拡散領域113とn型拡散領域115が形成された領域から引き出され、第2の絶縁層(図示せず)を介して入力ゲート電極231及び233が配置される。フローティングゲート121と、入力ゲート電極231及び233との上層には第3の絶縁層(図示せず)が形成され、その上層には配線層141、143、151、153及び155が形成される。ここで、配線層151はニューロンCMOS回路300に電源電圧VDDを印加する配線であり、配線層153は接地するための配線である。また、配線層155は、ニューロンCMOS回路300の出力電圧VOYを出力するための配線である。

【0049】

配線層151と、n型拡散領域311及びp型拡散領域113とは、コンタクトホール161により接続される。また、配線層153と、n型拡散領域115、p型拡散領域317とは、コンタクトホール161により接続される。入力ゲート電極231と配線層141、入力ゲート電極233と配線層143は、コンタクトホール161によりそれぞれ接続される。フローティングゲート121に対して配線層151が配置された領域とは反対側のp型拡散領域113の領域に、配線層155が配置され、コンタクトホール161によりp型拡散領域113と接続される。また、フローティングゲート121に対して配線層153が配置された領域とは反対側のn型拡散領域115の領域に、配線層155が配置され、コンタクトホール161によりn型拡散領域115と接続される。

【0050】

ニューロンCMOS回路300は、入力ゲート電極231及び233の面積を調整することにより、入力ゲート電極231及び233とフローティングゲート121との間の容量C1及びC2を所望の容量に設計することができる。

【0051】

ニューロンCMOS回路300においては、フローティングゲート121の半分の面積と重なるようにnウェル301を配設することにより、フローティングゲート−基板間容量C0とフローティングゲート−電源間容量CDとが等しくなり、フローティングゲート121が基板や電源に対して持つ容量の影響によりニューロンCMOS回路の閾値電圧が変動するのを抑制することができる。

【0052】

このことを、数式を使って説明する。ニューロンCMOS回路300のフローティングゲートの電圧Φは、次に示す式(5)のようになる。

【数5】

【0053】

ニューロンMOS回路300のフローティングゲート電圧に対する閾値を電源電圧VDDの1/2とすると、ニューロンMOS回路300の出力は、式(6)のようになる。

【数6】

【0054】

式(6)に、C0=CDを代入し整理すると、式(7)となる。

【数7】

【0055】

式(7)より、本実施形態に係るニューロンCMOS回路300は、フローティングゲート−基板間容量C0の影響を受けないことがわかる。

【0056】

なお、本実施形態に係るニューロンCMOS回路300には、半導体装置に製造に用いられる公知の材料を利用することができる。また、ニューロンCMOS回路300の製造には、公知の半導体装置の製造方法が適用可能である。従って、ニューロンCMOS回路300に用いる材料及び製造方法の詳細な説明は省略する。

【0057】

このように、本実施形態に係るニューロンCMOS回路300は、フローティングゲートの半分の面積と重なるようにnウェルを配設することにより、2つの入力ゲート電極のみで、フローティングゲート−基板間容量の影響による閾値の変動を抑制し、ニューロンCMOS回路300の閾値の高度な制御を実現することができる優れた効果を奏する。なお、本実施形態のおいては、p基板を用いた例について説明したが、n基板を用いた場合も、フローティングゲートの半分の面積をpウェルと重なるように設計することにより同様の効果を得ることができる。また、本実施形態においては、2つの入力ゲート電極からそれぞれ入力電圧VINA、入力電圧VINBが印加される例について説明したが、本発明はこれに限定されるものではなく、入力ゲート電極の数は任意に設定可能である。

【実施例】

【0058】

上述した本発明に係るニューロンCMOS回路を用いた電子回路の一例として、本発明の一実施形態に係るニューロンCMOS回路100と同等の回路を用いたnビットフラッシュ型AD変換器について以下に説明する。

【0059】

(nビットフラッシュ型AD変換器)

本実施例に係るnビットフラッシュ型AD変換器500は、量子化出力部530とエンコード部550を有する。図8は、本発明の一実施形態に係るnビットフラッシュ型AD変換器500の回路図である。図8においてNi(i=1〜2n−1−1)、Nj(j=2n−1+1〜2n−1)、NIN1、NIN2はCMOS回路、νCMOSi(i=1〜2n−1−1)、νCMOSj(j=2n−1+1〜2n−1)はニューロンCMOS回路である。nビットフラッシュ型AD変換器500は、νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)、すなわち、2n−2個のニューロンCMOS回路と1個のCMOS回路NIN1とがアナログ入力電圧VINを入力する端子に接続し、各ニューロンCMOS回路には波形整形用のCMOS回路が1個ずつ直列に接続し、CMOS回路NIN1にはCMOS回路NIN2が直列に接続する。

【0060】

ニューロンCMOS回路のゲートに付したCi,1、Ci,2、Ci,3(i=1〜2n−1−1)及びCj,1、Cj,2、Cj,3(j=2n−1+1〜2n−1)は、ニューロンCMOS回路の各入力端子とフローティングゲート間の結合容量である。nビットフラッシュ型AD変換器500においては、ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)及びνCMOSj(j=2n−1+1〜2n−1)の容量Ci,1(i=1〜2n−1−1)及びCj,1(j=2n−1+1〜2n−1)を有するゲートには電源電圧VDDが印加され、容量Ci,2(i=1〜2n−1−1)及びCj,2(j=2n−1+1〜2n−1)を有するゲートにはアナログ入力電圧VINが印加される。νCMOSi(i=1〜2n−1−1)の容量Ci,3(i=1〜2n−1−1)を有するゲートには電源電圧VDDが印加され、νCMOSj(j=2n−1+1〜2n−1)の容量Cj,3(j=2n−1+1〜2n−1)を有するゲートは接地される。アナログ入力電圧VINは、CMOS回路NIN2に直列に接続したCMOS回路NIN1にも印加される。

【0061】

また、nビットフラッシュ型AD変換器500は、エンコード部550を更に有する。nビットの場合のAD変換出力VOi(i=1〜n−1)を得るための回路は、式(8)により設計できる。

【数8】

【0062】

上述の実施形態において説明したように、容量Ci,1、Cj,1は、ニューロンCMOS回路の閾値がフローティングゲート−基板間容量の影響により変動するのを防ぐための容量であり、入力ゲート電極とフローティングゲート間の容量である。したがって、容量Ci,1、Cj,1は、式(9)、式(10)のように、フローティングゲート−基板間容量Ci,0(図示していない)、Cj,0(図示していない)と同容量である。なお、実際の回路においては、回路の製造プロセスにおいて許容される範囲で容量が概略等しいことを意味する。

【0063】

【数9】

【数10】

【0064】

Ci,2、Ci,3、Cj,2、Cj,3はニューロンCMOS回路の閾値を決定するための容量であり、それぞれ次に示す式(11)〜式(14)の関係を満たす。なお、Cuは半導体の設計上で最適に設定される基本容量である。

【数11】

【数12】

【数13】

【数14】

また、全てのCMOS回路の閾値は電源電圧VDDの1/2、全てのニューロンCMOS回路のフローティングゲートの電圧に対する閾値は電源電圧VDDの1/2とする。

【0065】

図9は、図8の上からi番目(i=1〜2n−1−1)のニューロンCMOS回路νCMOSiの回路とその等価回路であり、図10は図8の上からj番目(j=2n−1+1〜2n−1)のニューロンCMOS回路νCMOSjの回路とその等価回路である。図9、図10において、Ci,0、Cj,0はフローティングゲート−基板間容量、Φi及びΦjは基板電位を基準としたフローティングゲートの電圧である。フローティングゲートの電圧Φi、Φjは、次に示す式(15)、式(16)のようになる。

【数15】

【数16】

【0066】

ニューロンCMOS回路は、フローティングゲートの電圧が電源電圧VDDの1/2以上の場合に0V、VDD/2未満の場合に電源電圧VDDを出力する素子である。ニューロンCMOS回路νCMOSi(i=1〜2n−1−1)の出力を回路Ni(i=1〜2n−1−1)により反転した電圧が量子化出力電圧Vi(i=1〜2n−1−1)であり、ニューロンCMOS回路νCMOSj(j=2n−1+1〜2n−1)の出力をCMOS回路Nj(j=2n−1+1〜2n−1)により反転した電圧が量子化出力電圧Vj(j=2n−1+1〜2n−1)である。したがって、量子化出力電圧Vi(i=1〜2n−1)及びVj(j=2n−1+1〜2n−1)は、式(17)、式(18)のようになる。

【数17】

【数18】

【0067】

式(17)に、式(9)、式(11)、式(12)を代入し整理すると、式(19)のようになる。また、式(18)に式(10)、式(13)、式(14)を代入し整理すると、式(20)のようになる。

【数19】

【数20】

【0068】

【0069】

以上説明したように、本実施例に係るnビットフラッシュ型AD変換器500は、電圧を比較する素子としてコンパレータに比べて回路規模が小さく消費電力の少ないニューロンCMOS回路を用いるため、従来のフラッシュ型AD変換器に比して十分に消費電力の少ないフラッシュ型AD変換器を実現することができる。

【0070】

なお、本実施例においてはニューロンCMOS回路100と同等の回路を用いた例を説明したが、本実施例に係るnビットフラッシュ型AD変換器500には、ニューロンCMOS回路200またはニューロンCMOS回路300を利用することもできる。また、本実施例においてはnビットフラッシュ型AD変換器を例に説明したが、本発明に係るニューロンCMOS回路は、様々な電子回路に適用可能である。

【符号の説明】

【0071】

100:ニューロンCMOS回路、101:nウェル、111:n型拡散領域、113:p型拡散領域、115:n型拡散領域、117:p型拡散領域、121:フローティングゲート、131:入力ゲート電極、133:入力ゲート電極、135:入力ゲート電極、141:配線層、143:配線層、151:配線層、153:配線層、155:配線層、190:ニューロンCMOS回路100の等価回路、200:ニューロンCMOS回路、203:pウェル、231:入力ゲート電極、233:入力ゲート電極、290:ニューロンCMOS回路200の等価回路、300:ニューロンCMOS回路、301:nウェル、311:n型拡散領域、317:p型拡散領域、390:ニューロンCMOS回路300の等価回路、500:nビットフラッシュ型AD変換器、530:量子化出力部、550:エンコード部

【特許請求の範囲】

【請求項1】

基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、

前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路。

【請求項2】

前記複数の入力ゲート電極は前記共通するフローティングゲートとそれぞれ所定の容量を有し、

前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力することを特徴とする請求項1に記載のニューロンCMOS回路。

【請求項3】

前記PMOSFETのソースと前記一つの入力ゲート電極とに、電源電圧が印加されることを特徴とする請求項1又は2に記載のニューロンCMOS回路。

【請求項4】

基板と、

前記基板に形成されたnウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記基板に形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、

前記フローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記フローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路。

【請求項5】

前記第1のp型拡散領域と、前記一つの入力ゲート電極とに接続し、電源電圧を印加する第1の配線層と、

前記第1のn型拡散領域に接続し、接地する第2の配線層と、

前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、

を更に備えることを特徴とする請求項4に記載のニューロンCMOS回路。

【請求項6】

基板と、

前記基板に形成されたnウェル及びpウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記pウェルに形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備えることを特徴とするニューロンCMOS回路。

【請求項7】

前記基板は、不純物を含まない基板、不純物濃度の低い基板または絶縁基板であることを特徴とする請求項6に記載のニューロンCMOS回路。

【請求項8】

前記nウェルに形成された第2のn型拡散領域と、

前記pウェルに形成された第2のp型拡散領域と、

を更に備えることを特徴とする請求項6又は7に記載のニューロンCMOS回路。

【請求項9】

基板と、

前記基板に形成されたnウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記基板に形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、

前記nウェルは、前記フローティングゲートの半分の面積と重なるように配置されることを特徴とするニューロンCMOS回路。

【請求項10】

前記nウェルに形成された第2のn型拡散領域と、

前記基板に形成された第2のp型拡散領域と、

を更に備えることを特徴とする請求項9に記載のニューロンCMOS回路。

【請求項11】

前記第1のp型拡散領域に接続し、電源電圧を印加する第1の配線層と、

前記第1のn型拡散領域に接続し、接地する第2の配線層と、

前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、

を更に備えることを特徴とする請求項6乃至10の何れか一に記載のニューロンCMOS回路。

【請求項12】

前記複数の入力ゲート電極はそれぞれ所定の容量を有し、

前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力することを特徴とする請求項4乃至11の何れか一に記載のニューロンCMOS回路。

【請求項13】

請求項1乃至12の何れか一に記載のニューロンCMOS回路を備える電子回路。

【請求項1】

基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、

前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路。

【請求項2】

前記複数の入力ゲート電極は前記共通するフローティングゲートとそれぞれ所定の容量を有し、

前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力することを特徴とする請求項1に記載のニューロンCMOS回路。

【請求項3】

前記PMOSFETのソースと前記一つの入力ゲート電極とに、電源電圧が印加されることを特徴とする請求項1又は2に記載のニューロンCMOS回路。

【請求項4】

基板と、

前記基板に形成されたnウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記基板に形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、

前記フローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記フローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路。

【請求項5】

前記第1のp型拡散領域と、前記一つの入力ゲート電極とに接続し、電源電圧を印加する第1の配線層と、

前記第1のn型拡散領域に接続し、接地する第2の配線層と、

前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、

を更に備えることを特徴とする請求項4に記載のニューロンCMOS回路。

【請求項6】

基板と、

前記基板に形成されたnウェル及びpウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記pウェルに形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備えることを特徴とするニューロンCMOS回路。

【請求項7】

前記基板は、不純物を含まない基板、不純物濃度の低い基板または絶縁基板であることを特徴とする請求項6に記載のニューロンCMOS回路。

【請求項8】

前記nウェルに形成された第2のn型拡散領域と、

前記pウェルに形成された第2のp型拡散領域と、

を更に備えることを特徴とする請求項6又は7に記載のニューロンCMOS回路。

【請求項9】

基板と、

前記基板に形成されたnウェルと、

前記nウェルに形成された第1のp型拡散領域と、

前記基板に形成された第1のn型拡散領域と、

前記第1のp型拡散領域及び前記第1のn型拡散領域の上に配置されたフローティングゲートと、

前記フローティングゲートの上に配置された複数の入力ゲート電極と、を備え、

前記nウェルは、前記フローティングゲートの半分の面積と重なるように配置されることを特徴とするニューロンCMOS回路。

【請求項10】

前記nウェルに形成された第2のn型拡散領域と、

前記基板に形成された第2のp型拡散領域と、

を更に備えることを特徴とする請求項9に記載のニューロンCMOS回路。

【請求項11】

前記第1のp型拡散領域に接続し、電源電圧を印加する第1の配線層と、

前記第1のn型拡散領域に接続し、接地する第2の配線層と、

前記第1のp型拡散領域と前記第1のn型拡散領域とに接続し、出力電圧を出力する第3の配線層と、

を更に備えることを特徴とする請求項6乃至10の何れか一に記載のニューロンCMOS回路。

【請求項12】

前記複数の入力ゲート電極はそれぞれ所定の容量を有し、

前記複数の入力ゲート電極のそれぞれに入力される電圧に応じて、出力電圧を出力することを特徴とする請求項4乃至11の何れか一に記載のニューロンCMOS回路。

【請求項13】

請求項1乃至12の何れか一に記載のニューロンCMOS回路を備える電子回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−37737(P2013−37737A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−172100(P2011−172100)

【出願日】平成23年8月5日(2011.8.5)

【出願人】(000125369)学校法人東海大学 (352)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月5日(2011.8.5)

【出願人】(000125369)学校法人東海大学 (352)

【Fターム(参考)】

[ Back to top ]