ノード制御装置、ノード制御装置の制御方法、情報処理システム、及びコンピュータプログラム

【課題】複数のプロセッサノードと複数のIOノード間に、入出力データを交換するノード制御装置を設けることにより、多数の入出力装置を利用可能にする。

【解決手段】ノード制御装置のポート入力部300では、レジスタ400にIO空間のマップ先のメモリ空間のベースアドレスを、テーブル401にはIO空間のIO空間番号及びアドレスレンジを、それぞれ設定する。テーブル401には、また、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それともメモリにマップされたIO空間ではないのかを示す識別フラグを設定する。IO空間アクセス検出回路402は、対応するプロセッサノードから入力するフリット信号330のコマンドコード及びアドレスをデコードして、IO空間へのアクセスであることを検出して出力し、ターゲットのIOノードのノードIDを検出して出力する。

【解決手段】ノード制御装置のポート入力部300では、レジスタ400にIO空間のマップ先のメモリ空間のベースアドレスを、テーブル401にはIO空間のIO空間番号及びアドレスレンジを、それぞれ設定する。テーブル401には、また、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それともメモリにマップされたIO空間ではないのかを示す識別フラグを設定する。IO空間アクセス検出回路402は、対応するプロセッサノードから入力するフリット信号330のコマンドコード及びアドレスをデコードして、IO空間へのアクセスであることを検出して出力し、ターゲットのIOノードのノードIDを検出して出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はノード制御装置、ノード制御装置の制御方法、情報処理システム、及びコンピュータプログラムに係り、特に、1つのプロセッサノードで制御する入出力装置の台数が多数となり、これらの入出力装置を使用するために必要な記憶領域(以下、「IO空間」と称する)も大規模となる場合にも対応できるノード制御装置、ノード制御装置の制御方法、情報処理システム、及びコンピュータプログラムに関する。

【背景技術】

【0002】

近年、複数のIOノード(入出力装置)を含む大規模な情報処理システムにおいては、IO空間を使用する多数の入出力装置(以下、「IOデバイス」と称することもある)を全て接続して使用したいという要求があり、この場合、IO空間(データバッファ等)が不足するという問題点が生じることとなり、この問題点の解決が重要課題であった。

即ち、1つのプロセッサノードで制御する入出力装置の台数が多数になると、これらの入出力装置を使用するために必要な記憶領域(即ちIO空間)も大規模となるが、周知のPCI−ExpressなどのPCI仕様による定義では、全ての入出力装置に割り当てられるIO空間の合計が64KBに過ぎない。

よって、本発明でも、このような多数のIOデバイスを接続したいという要求を満たすために、1つのプロセッサノードで複数のIO空間を処理できるようにする手段の開発が課題の1つとなっている。

【0003】

なお、最近では、最新のOSとシステムファームウェア間には、複数のIO空間を設定して受け渡すインタフェースが定義されている。しかしながら、汎用の入出力装置を制御する制御装置用のLSIについては、複数のIO空間を認識して処理する手段は未だ開発されていない。一方、或る種の既成のOSでは、複数のIO空間を扱うことはできない。また、既成の汎用のIOノードのLSIにも、複数のIO空間を認識して処理する手段は設けられていない。

【0004】

この分野で先行して出願された特許の文献として、例えば、特許文献1では、インタコネクトを介して互いに接続されている複数の中央プロセッサユニット(CPU)ノードと、入力/出力(I/O)ノードと、メモリノードとを含む分散マルチノードコンピュータシステムが示されており、このコンピュータシステムは複数のドメインに分割されており、この各ドメインは、その独自のアドレス空間を有する独立したマシンとして機能するものとしており、また、各ドメイン上で、オペレーティングシステムが別々にランするものとしている。

【0005】

また、例えば、特許文献2では、計算機システムにおいて、LPAR制御プログラムが、1つの物理的なデバイスのメモリ空間及びIO空間を各OSに対して仮想的にマッピングする機能を有し、さらに、このLPAR制御プログラムは、1台の計算機システムを論理的な複数のパーティション(LPAR)に分割し、各LPARに対してLPARを特定するためのLPAR識別子を割当てる機能を有することを開示している。

【0006】

また、例えば、特許文献3では、2つのレジスタにコンフィグレーション空間のベースアドレス、サイズを設定することにより、メモリ空間に複数のコンフィグレーション空間をマップするものとし、コンフィグレーションアクセス検出回路が、フリット信号に含まれている、アクセス対象デバイスが接続されているバスのバス番号と上記バスを配下に持つIOノードに割り当てられているコンフィグレーション空間のセグメント番号とをマージしたインデックス信号を出力するものとしている。また、インデックス信号に対応するエントリに格納されているIOノードのノードIDを出力できるテーブルを設けると共に、フリット信号を上記ノードIDのIOノードへルーティングするクロスバースイッチを設けることが開示されている。

【0007】

さらに、例えば、特許文献4では、IO空間を有効利用可能として容量の制限を無くして、大容量IO空間を必要とするデバイスの接続を可能とすると共に、回路規模の増大を抑止低減することを意図し、IOアドレス空間を定める値が設定されるベースアドレスレジスタと、ベースアドレスレジスタの値と、前記システムバス上に送出されるアドレスとを比較し、両者が一致した場合に、前記システムバスに応答する共に選択信号をアクティブにするコンパレータと、システムバス上のアドレスと前記選択信号とを入力とし、エイリアス空間を避けるようにしてデバイスのマッピングを行ってデバイスの選択信号を生成するデコーダと、を備える構成の、システムバスのIOマッピング方式が開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−132037号公報

【特許文献2】特開2008−158710号公報

【特許文献3】特開2008−181389号公報

【特許文献4】特開平11−238029号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上記背景技術で述べた従来の情報処理システムにあっては、前述のとおり、PCI−Express等のPCI仕様の場合、入出力装置の制御に使用できるIO空間は16ビットのアドレスで指定する64Kバイトの空間である。しかしながら、複数のIOノードを含む大規模な情報処理システムにおいては、多数のIOデバイスを接続して制御したいという要求があり、これらのIOデバイスがIO空間を使用する場合、IO空間が足りなくなるという問題点が有った。

【0010】

なお、前述の特許文献1〜4に開示されている技術は、本発明のように、マップされていない1つのIO空間を扱う既成の制御システムとの互換を考慮していないので、この点で、いずれも本発明とは異なるものである。また、個別では、

前述の特許文献1に開示された技術の場合、本発明のようにノード制御装置を設ける構成ではなく、複数の中央プロセッサユニットのOSがノード制御装置の役割を果たすものである。

【0011】

前述の特許文献2に開示された技術の場合、計算機システム内で稼動するLPAR制御プログラムが、本発明のノード制御装置に近い役割を果たすものである。

前述の特許文献3に開示された技術の場合、本発明とは最も近い構成であるが、メモリ空間には、IO空間ではなく、複数のコンフィグレーション空間をマップするものとしている。また、ノード制御装置内にはレジスタが2つ設けられている。

前述の特許文献4に開示された技術の場合、前述のとおり、大容量IO空間を必要とするデバイスの接続を可能にすることを意図したものであり、本発明のように、個々のIOノードが備える複数のIO空間を全て取り扱えることを可能にして、多数のIOデバイスを接続することを意図したものではない。

【0012】

本発明は、上記従来の問題点に鑑みてなされたものであって、複数のプロセッサノードと複数のIOノードとの間に、入出力データを交換するノード制御装置を設けると共に、該ノード制御装置に、メモリ空間に複数のIO空間を予めマップする機能と、アドレスからIO空間番号をデコードして対応のIOノードへアクセスをルーティングする機能とを備えることにより、個々のIOノードが備える複数のIO空間を全て取り扱えることを可能にして、多数のIOデバイスを接続することができるノード制御装置及びノード制御装置の制御方法並びに情報処理システムを提供することを目的としている。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明に係るノード制御装置は、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置であって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルと、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定する手段と、を備えたことを特徴とする。

【0014】

また、本発明に係るノード制御装置の制御方法は、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置の制御方法であって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とする。

【0015】

また、本発明に係る情報処理システムとして、上述のノード制御装置を有する情報処理システムを提供するものである。

【0016】

さらに、本発明に係るコンピュータプログラムは、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置を制御させるためのコンピュータプログラムであって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とする。

【発明の効果】

【0017】

以上説明したように、本発明によれば、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数のIOノードとの間で入出力装置が担うデータの交換を行うノード制御装置において、IOノードの入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを設けると共に、データの交換の際に、プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定するIOノードと、該IOノードの入出力装置制御領域とを確定する構成としたので、多数の入出力装置を制御できるノード制御装置を提供することができる効果が有る。

【図面の簡単な説明】

【0018】

【図1】本発明の実施形態に係る情報処理システムの全体構成を示す構成図である。

【図2】IOノードの1例としての構成を示す構成図である。

【図3】本発明の実施形態に係るノード制御装置の構成を示す構成図である。

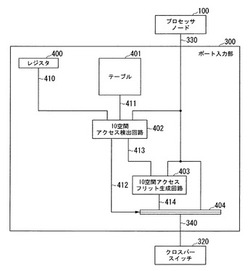

【図4】図3に示すノード制御装置130のポート入力部300の詳細構成を示す構成図である。

【図5】テーブル401のフォーマットを示すデータ構成図である。

【図6】IO空間及びその記憶装置上でのIO空間のマップを示すデータ構成図である。

【図7】本発明の情報処理システムにおいて情報を転送する際の転送フォーマットの1例を示すデータ構成図である。

【図8】図7に示すヘッダフリットのアドレスフィールドの、IO空間アクセスを行う場合の詳細構成を示すデータ構成図であり、図8(a)はメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマット(プロセッサノード発行)を示し、図8(b)は既成のIO空間アクセスのアドレスフォーマット(プロセッサノード及びノード制御装置発行)を示すものである。

【図9】図4に示すIO空間アクセス検出回路402において一致結果信号412及びノードID信号413を生成する際の処理手順を示すフローチャート図である。

【図10】2つのパーティションに区切った情報処理システムの1構成例を示す構成図である。

【発明を実施するための形態】

【0019】

本発明は、複数のIOノードを含む大規模な情報処理システムにおいて、少なくとも1台のノード制御装置を介することによって、PCI−ExpressなどのPCI仕様で定義されるIO空間(請求項に記載の入出力装置制御領域であり、データバッファを含む)を、複数設定して処理できるようにすることにより、既成のプロセッサが備えるIO空間よりも多数のIO空間を必要とするIOデバイスを接続可能にするものである。

また、従来どおり、1つのIO空間に全てのIOデバイスを割り当てて使用する既成のプロセッサによるIO空間の使用形態についても取り扱い可能とすることにより、複数のIO空間を認識できない既成の情報処理装置のOS(オペレーティングシステム)上でも動作可能にするものである。

【0020】

さらに、情報処理システムをパーティションに区切って、複数のOSを動作させる場合には、例えば、OS毎に、1つのIO空間のみを使うのか、それとも複数のIO空間を使うのかを選択できるように構成するものである。

このような、IO空間を使用するIOデバイスを、できるだけ多数接続したいという要求を実現するために、本発明では、システムファームウェアまたはサービスプロセッサによって制御される少なくとも1台のノード制御装置を設置することによって、1つのプロセッサで複数のIO空間を利用できるようにしている。

【0021】

以下、本発明のノード制御装置及びノード制御装置の制御方法並びに情報処理システム置の実施形態について、図面を参照して詳細に説明する。

図1は、本発明の実施形態に係る情報処理システムの全体構成を示す構成図である。

同図において、本実施形態の情報処理システムは、16個のプロセッサノード100〜115と、8個のIOノード120〜127と、4個のノード制御装置130〜133(本発明の実施形態に係るノード制御装置)と、を備える。

【0022】

8個のIOノード120〜127は、4個のノード制御装置130〜133に、2台づつ接続されている。4個のノード制御装置130〜133には、それぞれ4個のプロセッサノードと、2個のIOノードが接続されている。この4個のノード制御装置同士は、互いに1対1で接続されている。

図示しないが、プロセッサノード100〜115の各々は、1つまたは複数のプロセッサと主記憶を備える。

【0023】

本発明に係る情報処理システムは、図1に示す構成に限定されるものではなく、一般には、もっと小規模な構成(例えば、プロセッサノード2個、ノード制御装置1個、及びIOノード2個)といった構成や、もっと大規模な構成(例えば、プロセッサノード64個、IOノード32個、及びノード制御装置16)といった構成にすることも可能である。

図2は、IOノードの1例としての構成を示す構成図である。

同図に示すIOノードは、1台のIO制御装置200と、4台のIOデバイス210〜213とを備えて構成されている。

【0024】

IO制御装置200は、ノード制御装置130(本発明の実施形態に係るノード制御装置)とインタフェース160を介して接続されている。また、IO制御装置200は、IOデバイス210〜213と、それぞれインタフェース220〜223を介して接続されている。インタフェース220〜223は、PCI−ExpressなどのPCIの仕様に準拠するものとする。なお、図2に示す構成は1例であって、一般には、もっとIOデバイスの少ない構成や、もっとIOデバイスの多い構成にすることも可能である。

【0025】

図3は、本発明の実施形態に係るノード制御装置の構成を示す構成図である。

同図に示す本発明の実施形態に係るノード制御装置130は、9個のポート入力部300〜308と、9個のポート出力部310〜318と、クロスバースイッチ320と、を備えて構成される。ここで、一組のポート入力部とポート出力部とをポートと定義する。例えば、プロセッサノード100に接続するポートは、ポート入力部300とポート出力部310とから構成される。ノード制御装置130の9個のポートは、それぞれ、プロセッサノード100〜103、IOノード120〜121、及びノード制御装置131〜133を接続するためのものである。

【0026】

図4は、図3に示すノード制御装置130のポート入力部300の詳細構成を示す構成図である。

図3に示すノード制御装置130のポート入力部301〜308についても、図4に示すポート入力部300と同じ構成をとる。

レジスタ400は、本実施形態では16ビットのレジスタであり、メモリ空間にマップされるIO空間(入出力装置制御領域)のベースアドレスを指定する値を保持する。レジスタ400のビット15〜0は、ベースアドレスのビット47〜32に対応する。ベースアドレスの31〜0はオール0である。

【0027】

テーブル401は、レジスタで構成され、各IOノードに対応したエントリを備え、各IOノードに接続するIOデバイスに割り当てられるIO空間のレンジを指定する値を保持する。本実施形態では、IOノードは8個なので、8エントリのテーブルである。

【0028】

以下、図4を用いて、本発明の課題の具体的な解決手段を説明する。

レジスタ400には、IO空間のマップ先のメモリ空間のベースアドレスを設定する。

テーブル401は、情報処理システム内のIOノードの個数と等しいエントリを備え、各IOノードに接続するIOデバイスに割り当てられるIO空間の、IO空間番号及びアドレスレンジを設定する。

テーブル401には、また、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それともメモリにマップされたIO空間ではないのかを示す識別フラグを設定する。

【0029】

IO空間アクセス検出回路402は、対応するプロセッサノードから入力するフリット信号330(入出力データ情報)のコマンドコード及びアドレスをデコードして、IO空間へのアクセスであることを検出して出力し、ターゲットのIOノードのノードIDを検出して出力する。

IO空間アクセスフリット生成回路403及びセレクタ404は、メモリ空間にマップされたIO空間へのアクセスの場合は、IOノードが処理できるIO空間アクセスに変換し、さらに、ターゲットのIOノードのノードIDを指定してクロスバースイッチ320へ出力する。

【0030】

このようにして、本発明のノード制御装置では、複数のIO空間をメモリ空間にマップする機能を設けて、マップされたIO空間へのアクセスからIO空間番号を認識してターゲットのIOノードへ出力するので、複数のIO空間を扱うことが可能となり、よって、1つのプロセッサノードに対して、既成のノード制御装置と比較して多数のIOデバイスを接続することができる。さらに、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、既成のノード制御装置のIO空間なのかの識別フラグを設けることにより、複数のIO空間を扱うことのできない既成のOSでも動作可能とすることができる。

【0031】

図5は、テーブル401のフォーマットを示すデータ構成図である。

同図において、エントリ0〜7は、IOノード120〜127に対応する。ビット15は、メモリ空間マップを示すフラグであり、‘0’で従来のIO空間、‘1’でメモリ空間にマップされたIO空間であることを指定する。ビット14〜12はIO空間番号であり、メモリ空間にマップされたIO空間が割り当てられる場合に、IO空間番号を指定する。ビット11〜6は上限アドレスであり、また、ビット5〜0は下限アドレスであり、それぞれIO空間アドレスのビット15〜10に対応してIO空間内のアドレスレンジを指定する。ここで、アドレスレンジの上限のアドレス9〜0はオール1であり、アドレスレンジの下限のアドレス9〜0はオール0である。例えば、下限アドレスが000100(2進数)で、上限アドレスが000111(2進数)の場合、アドレスレンジは1000〜1FFF(16進数)になる。

【0032】

レジスタ400及びテーブル401は、プロセッサの初期化時にシステムファームウェアまたはサービスプロセッサによって設定されるが、これらの設定に関する詳細な構成については、当業者にとってよく知られており、また本発明とは直接関係しないので説明は省略する。

IO空間アクセス検出回路402は、プロセッサノード100から入力するフリット信号330がヘッダフリットの場合(ストローブフィールドが‘01’(2進数)の場合)に、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の保持する値とを比較して、一致結果信号412と、ノードID信号413を生成する。

【0033】

図6は、IO空間及びその記憶装置上でのIO空間のマップを示すデータ構成図である。

以下、図6を参照して、IO空間のメモリ空間へのマップ方法を説明する。

1つのIO空間は64Kバイトであり、複数のIO空間はアドレス空間の一部の領域に連続してマップされる。図6は、N+1個のIO空間を、ベースアドレス〜(ベースアドレス+サイズ−1)の領域にマップした場合の例を示している。ここで、サイズは(N+1)×64Kバイトである。また、各IO空間はIO空間番号0〜Nで識別される。

本実施形態では、複数のIO空間をメモリ空間にマップする場合に、ACPI仕様で定義されるDense Translation方式を前提としているが、Sparse

Translation方式に対応させることも可能である。また、テーブル401に識別フラグを追加することにより、前記の両方式に対応させることも可能である。

【0034】

図7は、本発明の情報処理システムにおいて情報を転送する際の転送フォーマットの1例を示すデータ構成図である。

ここでは、論理的な情報の転送単位をパケットと定義し、また、パケットはひとつ以上のフリットから構成されるものと定義している。図7に示す各フリットは所定の固定されたビット幅を備えるが、この例では90ビット幅としている。このフリットには、ヘッダフリットと、データフリットとの2種類が存在し、図7では各フリットの転送フォーマットを示している。

【0035】

フリットのビット89〜88はストローブであり、フリットが有効であること、及びフリットの種類を示している。ストローブが‘00’(2進数)の場合は該フリットが無効であることを示し、ストローブが‘01’(2進数)の場合はヘッダフリットであることを示し、ストローブが‘10’(2進数)の場合はデータフリットであることを示す。但し、このコード定義はあくまで1例である。なお、パケットは、図7に示す1個のヘッダフリットと、0個、1個、2個、4個または8個のデータフリットとから構成される。よって、本実施形態のパケットは、最小のものでも1個のフリットから構成され、最大のものでは9個のフリットから構成されることになる。

【0036】

一般に、このようなフリットには、エラーの検出や訂正の目的で、ECCやパリティが付加されるが、本発明とは直接関係しないので、ここでの説明は省略する。

ヘッダフリットのビット87〜0には、それぞれ8ビットの5個のフィールドと、48ビットのアドレスフィールドとが定義される。これらのフィールド定義はあくまで1例であるが、一般には、情報処理装置のリソース、プロトコル及びトポロジーに依存して決定されるものである。

図7に示すコマンドコードは、例えばメモリリード、メモリライト、IOリード、IOライト、リプライといった、ターゲットの装置に対する動作を指定するコードが格納されるフィールドである。

【0037】

ソースノードIDは、パケットの転送元のプロセッサノードまたはIOノードを識別するための固有の番号が格納されるフィールドである。

ターゲットノードIDは、パケットの転送先のプロセッサノードまたはIOノードまたはノード制御装置を識別するための固有の番号が格納されるフィールドである。

データレングスは、リードリクエストの場合に、ターゲットのデータレングスをバイト単位で指定するフィールドである。00(16進数)〜40(16進数)の場合、0〜64バイトを指定する。他の値は未定義である。

アドレスは、リクエストのターゲットとなるアドレスを格納するフィールドである。

データフリットのビット71〜64には、バイトイネーブルが定義され、ビット63〜0に定義される各バイトの指定の有効または無効を指定する。

【0038】

図8は、図7に示すヘッダフリットのアドレスフィールドの、IO空間アクセスを行う場合の詳細構成を示すデータ構成図であり、図8(a)はメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマット(プロセッサノード発行)を示し、図8(b)は既成のIO空間アクセスのアドレスフォーマット(プロセッサノード及びノード制御装置発行)を示すものである。

本発明の本来の方式であるメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマットでは、図8(a)において、ビット47〜32は、IO空間をマップするメモリ空間のベースアドレスである。また、ベースアドレスは、4Gバイト境界のアドレスを指定できるが、もっと細かい粒度で指定可能にすることもできる(例えば、ベースアドレスを47〜20にすれば、1Mバイト境界で指定することができる)。なお、ビット31〜19はオール0であり、使用しない。

【0039】

さらに、ビット18〜16は、IO空間番号であり、本実施形態では0〜7のいずれかの値をとるものとする。

情報処理システム内のIOノードの数が多い場合には、IO空間番号の取り得る値を広げることも可能である(例えば、IO空間番号を23〜16にして、0〜255の値を取るようにすることも可能である)。ビット15〜0は、IO空間のアドレスである。

他方、既成の方式であるIO空間アクセスのアドレスフォーマットでは、図8(b)において、ビット47〜36はオール0であり、使用されない。また、ビット15〜0はIO空間アドレスを示している。

【0040】

図9は、図4に示すIO空間アクセス検出回路402において一致結果信号412及びノードID信号413を生成する際の処理手順を示すフローチャート図である。

以下、図4〜8を参照しながら、図9に示すフローチャートを使用して、一致結果信号412及びノードID信号413の生成処理の手順を説明する。

この生成処理は、IO空間アクセス検出回路402において、システムファームウェアによって実行されるものである。

(ステップS1)

まず、ステップS1では、IO空間アクセス検出回路402は、プロセッサノード100から送出されたコマンド(図示は省略)のコマンドコードフィールドを検証する。

【0041】

(ステップS2)

次に、ステップS2では、IO空間アクセス検出回路402は、前記検証結果に基づき、前記コマンドコードフィールドがメモリ空間アクセス(メモリリードまたはメモリライト)を示している場合は制御の流れをステップS3に進め、前記コマンドコードフィールドがIO空間アクセス(IOリードまたはIOライト)を示している場合は制御の流れをステップS5に移す。

(ステップS3)

ステップS3では、IO空間アクセス検出回路402は、レジスタ400の値がアドレス47〜32の値と等しいか否かを検証し、レジスタ400の値がアドレス47〜32の値と等しい場合はステップS4に進み、レジスタ400の値がアドレス47〜32の値と等しくない場合はステップS5に移る。

【0042】

(ステップS4)

ステップS4では、IO空間アクセス検出回路402は、テーブル402の全エントリに関して、メモリ空間マップが1で、かつIO空間番号がアドレス18〜16と等しく、かつ下限アドレス≦アドレス15〜10の値≦上限アドレス値であることをチェックし、ステップS6に進む。

(ステップS5)

ステップS5では、IO空間アクセス検出回路402は、テーブル402の全エントリに関して、メモリマップが0で、かつ下限アドレス≦アドレス15〜10の値≦上限アドレス値であることをチェックし、ステップS6に移る。

【0043】

(ステップS6)

ステップS6では、IO空間アクセス検出回路402は、テーブル402にコマンドコードフィールドで指定された条件と一致するエントリが存在するか否かを検証し、テーブル402に前記条件と一致するエントリが存在する場合はステップS7に進み、テーブル402に前記条件と一致するエントリが存在しない場合はステップS8に移る。

(ステップS7)

ステップS7では、IO空間アクセス検出回路402は、一致結果信号412を‘1’にし、ノードID信号413を一致したエントリに対応するIOノードのノードIDにして出力し、処理を終了する。

【0044】

(ステップS8)

ステップS8では、IO空間アクセス検出回路402は、一致結果信号412を‘0’にして出力し、処理を終了する。

【0045】

なお、IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットの場合に、アドレスフィールドのビット47〜16をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、コマンドコードがメモリリードのコードならばIOリードのコードに差し替え、メモリライトのコードならばIOライトのコードに差し替えて、ヘッダフリット信号414として出力する。

セレクタ404は、一致結果信号412が‘0’ならばフリット信号330を選択し、一致結果信号412が‘1’ならばヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

【実施例】

【0046】

以下、本実施形態に係る情報処理システムの1実施例としての動作を説明する。

最初に、第1の実施例として、ノード制御装置130のポート入力部300が、複数のIO空間をメモリ空間にマップして使用する場合の動作について説明する。

まず、本実施形態に係る情報処理システムの初期化時の設定について説明する。

IO空間アクセス検出回路402のシステムファームウェアは、IOノード120〜127に関して、IO空間番号とIO空間内のアドレスレンジを割当てる。例えば、IOノード120〜127にIO空間番号0〜7を割り当てる。また、IOノード120には0000〜7FFF(16進数)のレンジを割り当て、IOノード121〜127には8000〜FFFF(16進数)のレンジを割り当てる。

【0047】

次に、前記システムファームウェアは、IO空間をマップするメモリ空間のベースアドレスを決定し、ノード制御装置130〜133のレジスタ400にセットする(ポート入力部301〜303にも同様にセットする)。例えば、ベースアドレスを1C0000000000(16進数)とすると、レジスタ400には1C00(16進数)をセットする。

さらに、前記システムファームウェアは、ノード制御装置130〜133のテーブル401に値をセットする(ポート入力部301〜303にも同様にセットする)。

【0048】

テーブル401のエントリ0の設定値は、メモリ空間マップが1、IO空間番号が000(2進数)、上限アドレスが011111(2進数)、下限アドレスが000000(2進数)である。また、エントリ1の設定値は、メモリ空間マップが1、IO空間番号が001(2進数)、上限アドレスが111111(2進数)、下限アドレスが100000(2進数)である。エントリ2〜7の設定値はIO空間番号を除きエントリ1と同じであり、IO空間番号は、それぞれ010〜111(2進数)である。これらの設定は、前記システムファームウェアの代わりにサービスプロセッサが行っても良い。

引き続き、プロセッサノード100から、IOノード124配下のIOデバイスに対して、IO空間アドレス8000(16進数)で、IOリードを行う場合について説明する。

【0049】

プロセッサノード100は、図7に示すヘッダフリットのフォーマットに関して、ストローブを01(2進数)とし、コマンドコードをメモリリードのコードとし、ソースノードIDをプロセッサノード100のノードIDとし、ターゲットノードIDをノード制御装置130のノードIDとし、データレングスをアクセス対象のデータ長に対応する値にして、フリット信号330を発行する。

ここで、トランザクションIDは、プロセッサノード100についてユニークな番号とする。また、図7のアドレスは、図8のアドレスフォーマットを参照して説明すると、ビット47〜32はベースアドレスの1C00(16進数)、ビット31〜19はオール0、ビット18〜16はIOノード124に割り当てられるIO空間番号の100(2進数)、ビット15〜0は8000(16進数)とする。つまり、プロセッサノード100からは、アドレス1C0000048000(16進数)に対するメモリリードが発行される。

【0050】

さらに、複数のIO空間をメモリ空間にマップして使用する場合のIO空間アクセス検出回路402の動作について、図9に示すフローチャート図を参照して説明する。

プロセッサ100からフリット信号330が入力すると、IO空間アクセス検出回路402は、入力したフリットのストローブフィールドが01(2進数)でヘッダフリットであるので、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の値との比較を行う。

ステップS1で、コマンドコードフィールドのチェックを行い、ステップS2で、メモリリードのコマンドコードであるため、メモリ空間アクセスであることを検出する。よって、ステップS3に進んで、レジスタ400とアドレス47〜32を比較し、両方の値が1C00(16進数)で等しいことを検出し、ステップS4に進む。

【0051】

ステップS4では、テーブル402のエントリ4に関して、メモリ空間マップが1で、かつIO空間番号が100(2進数)で、かつアドレス15〜30(100000(2進数))が下限アドレスから上限アドレスの範囲(100000〜111111(2進数))に含まれていることを検出する。よって、ステップS6では、エントリ4が条件と一致するエントリなのでステップ7に進み、ステップ7で、一致結果信号412を1にして出力し、ノードID信号413を、テーブル401のエントリ4に対応するIOノード214のノードIDにして出力して処理を終了する。

【0052】

IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットであるので、アドレスフィールドのビット47〜32をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、コマンドコードがメモリリードのコードなのでIOリードのコードに差し替えて、ヘッダフリット信号414として出力する。

セレクタ404は、一致結果信号412が1なので、ヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

【0053】

クロスバースイッチ320は、ターゲットノードIDに従って、フリットをポート出力部317へ出力する。なお、クロスバースイッチ320がターゲットノードIDに従って、出力先のポート出力部を決定する方法は、本発明とは直接関係しないので、その説明は省略する。

ポート出力部317から出力されたフリットは、ノード制御装置132を経由して、IOノード124へ出力され、IOノード124内に存在するターゲットのIOデバイスへ出力される。その後、ターゲットのIOデバイスからは、リプライデータがノード制御装置132及びノード制御装置130を経由して、プロセッサノード100に返却される。

【0054】

次に、第2の実施例として、1つのIO空間を使用する場合の動作について説明する。

まず、プロセッサの初期化時に実施する設定について説明する。

システムファームウェアは、IOノード120〜127に関して、IO空間内のアドレスレンジを割当てる。例えば、

IOノード120には0000〜1FFF(16進数)、

IOノード121には2000〜3FFF(16進数)、

IOノード122には4000〜5FFF(16進数)、

IOノード123には6000〜7FFF(16進数)、

IOノード124には8000〜9FFF(16進数)、

IOノード125にはA000〜BFFF(16進数)、

IOノード126にはC000〜DFFF(16進数)、

IOノード127にはE000〜FFFF(16進数)、

といったアドレスレンジを割り当てる。

【0055】

次に、システムファームウェアは、ノード制御装置130〜133のテーブル401に値をセットする(ポート入力部301〜303にも同様にセットする)。

テーブル401の全エントリに関して、メモリ空間マップは0、IO空間番号は000(2進数)である。

テーブル401の上限アドレス及び下限アドレスの設定値は、

エントリ0が000111及び000000(2進数)、

エントリ1が001111及び001000(2進数)、

エントリ2が010111及び010000(2進数)、

エントリ3が011111及び011000(2進数)、

エントリ4が100111及び100000(2進数)、

エントリ5が101111及び101000(2進数)、

エントリ6が110111及び110000(2進数)、

エントリ7が111111及び111000(2進数)、

である。

なお、これらの設定は、システムファームウェアの代わりにサービスプロセッサが行っても良い。

【0056】

次に、プロセッサノード100から、IOノード124配下のIOデバイスに対して、IO空間アドレス8000(16進数)で、IOリードを行う場合について説明する。

プロセッサノード100は、図7のヘッダフリットのフォーマットに関して、ストローブを01(2進数)とし、コマンドコードをIOリードのコードとし、ソースノードIDをプロセッサノード100のノードIDとし、ターゲットノードIDをノード制御装置130のノードIDとし、データレングスをアクセス対象のデータ長に対応する値にして、フリット信号330を発行する。ここで、トランザクションIDは、プロセッサノード100についてユニークな番号とする。また、図7のアドレスは、図8のアドレスフォーマットを参照して説明すると、ビット47〜16はオール0、ビット15〜0は8000(16進数)とする。つまり、プロセッサノード100からは、アドレス000000008000(16進数)に対するIOリードが発行される。

【0057】

さらに、IO空間アクセス検出回路402の動作について、図9に示すフローチャート図を参照して説明する。

プロセッサ100からフリット信号330が入力されると、IO空間アクセス検出回路402は、入力したフリットのストローブフィールドが01(2進数)でヘッダフリットであるので、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の値との比較を行う。

ステップS1で、コマンドコードフィールドのチェックを行い、ステップ2では、IOリードのコマンドコードであるため、IO空間アクセスであることを検出し、ステップS5に移る。

【0058】

ステップS5では、テーブル401のエントリ4に関して、メモリ空間マップが0で、かつアドレス15〜10(100000(2進数))が下限アドレスから上限アドレスの範囲(100000〜100111(2進数))に含まれていることを検出する。よって、上限に一致するエントリが有るので、ステップS7に進み、ステップ7で、一致結果信号412を‘1’にして出力し、ノードID信号413を、テーブル401のエントリ4に対応するIOノード214のノードIDにして出力し、処理を終了する。

この場合、IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットであるので、アドレスフィールドのビット47〜32をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、ヘッダフリット信号414として出力する。アドレスフィールドのビット47〜32の差し替えは、差し替え前及び差し替え後ともオール0なので、実施しないのと同等である。

【0059】

セレクタ405は、一致結果信号412が‘1’なので、ヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

クロスバースイッチ320は、ターゲットノードIDに従って、フリットをポート出力部317へ出力する。なお、クロスバースイッチ320がターゲットノードIDに従って、出力先のポート出力部を決定する方法は、本発明とは直接関係しないので、その説明は省略する。

ポート出力部317から出力されたフリットは、ノード制御装置132を経由して、IOノード124へ出力され、IOノード124内に存在するターゲットのIOデバイスへ出力される。その後、ターゲットのIOデバイスからは、リプライデータがノード制御装置132及びノード制御装置130を経由して、プロセッサノード100に返却される。

次に、第3の実施例として、情報処理システム全体を2つのパーティションに区切り、その一方では1つのIO空間のみを使用し、他方では複数のIO空間をメモリ空間にマップして使用する場合について説明する。

【0060】

図10は、2つのパーティションに区切った情報処理システムの1構成例を示す構成図である。

この実施例では、図10に示すように、図1に示す情報処理システムの構成を、パーティション500とパーティション501とに区切る構成とし、各々独立のOSで制御される場合の1実施例としての構成を示す。

この実施例では、パーティション500で、1つのIO空間のみを使用し、パーティション501では、複数のIO空間をメモリ空間にマップして使用するものとする。

各プロセッサノードの初期化時に実施する設定については、パーティション毎に行われる。ここで、ノード制御装置130及びノード制御装置131は2つのパーティション(500、501)に含まれるが、各ポート入力部300〜303には、接続するプロセッサノードが含まれるパーティションの設定のみが行われる。

【0061】

パーティション500に関しては、プロセッサノード100、101、104、105が含まれるので、ノード制御装置(130,131)のポート入力部(300,301)においては、テーブル401が設定される。

また、パーティション500には、IOノード(120,122)が含まれるので、テーブル401のエントリ0及びエントリ2のみに有効なレンジが設定される。ここで、パーティション500に存在しないIOノードに対応するエントリ(1、3〜7) には無効なレンジが設定される。このような無効なレンジの設定の1例としては、上限アドレスを000000(2進数)に設定し、下限アドレスを111111(2進数)に設定する方法が可能である。

【0062】

他方、パーティション501に関しては、プロセッサノード(102、103、106、107、108〜115)が含まれるので、ノード制御装置(130,131)のポート入力部(302,303)と、ノード制御装置(132,133)のポート入力部300〜303において、レジスタ400及びテーブル401が設定される。

パーティション501には、IOノード121、123〜127が含まれるので、テーブル401のエントリ1及びエントリ3〜7のみに有効なレンジが設定される。ここで、パーティション501に存在しないIOノードに対応するエントリ(0、2) には無効なレンジが設定される。この設定以降の動作は、先の説明と同様になるので、省略する。

【0063】

以上説明したように、本実施形態に係るノード制御装置及び情報処理システムでは、複数のIO空間をメモリ空間にマップする機能を設けて、マップされたIO空間へのアクセスからIO空間番号を認識してターゲットのIOノードへ出力しているので、複数のIO空間を扱うことが可能となり、よって、1つのプロセッサノードに多数のIOデバイスを接続して使用することができる効果が有る。

また、各IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それとも1つのIO空間なのかを判別するための識別フラグを設けたことにより、複数のIO空間を扱うことのできない既成のOSを使用しても動作可能とすることができる効果が得られる。

【0064】

さらに、前記ノード制御装置の入力ポート毎に処理回路を設け、個別に設定可能にすることにより、本発明に係る情報処理システムをパーティションに区切って使用すれば、複数のIO空間をサポートしているOSと、1つのIO空間しかサポートしていないOSとを組み合わせて使用することができる効果が得られる。

【0065】

なお、本発明に係るノード制御装置の各構成要素の処理の少なくとも一部をコンピュータ制御により実行するものとし、かつ、上記処理を、図9のフローチャートで示した手順によりコンピュータに実行せしめるプログラムは、半導体メモリを始め、CD−ROMや磁気テープなどのコンピュータ読み取り可能な記録媒体に格納して配付してもよい。そして、少なくともマイクロコンピュータ、パーソナルコンピュータ、汎用コンピュータを範疇に含むコンピュータが、上記の記録媒体から上記プログラムを読み出して、実行するものとしてもよい。

【産業上の利用可能性】

【0066】

本発明は、ノード制御装置及び情報処理システムの構築に適用可能であり、特に、1つのプロセッサノードで制御する入出力装置の台数が多数となり、これらの入出力装置を使用するために必要な記憶領域も大規模となる場合にも対応できるノード制御装置の構築と、該ノード制御装置を含む情報処理システムの構築に好適である。

【符号の説明】

【0067】

100〜115 プロセッサノード

120〜127 IOノード

130〜133 ノード制御装置

200 IO制御装置

210〜213 IOデバイス

300〜308 ポート入力部

310〜318 ポート出力部

320 クロスバースイッチ

400 レジスタ

401 テーブル(各IOノードの属性情報)

【技術分野】

【0001】

本発明はノード制御装置、ノード制御装置の制御方法、情報処理システム、及びコンピュータプログラムに係り、特に、1つのプロセッサノードで制御する入出力装置の台数が多数となり、これらの入出力装置を使用するために必要な記憶領域(以下、「IO空間」と称する)も大規模となる場合にも対応できるノード制御装置、ノード制御装置の制御方法、情報処理システム、及びコンピュータプログラムに関する。

【背景技術】

【0002】

近年、複数のIOノード(入出力装置)を含む大規模な情報処理システムにおいては、IO空間を使用する多数の入出力装置(以下、「IOデバイス」と称することもある)を全て接続して使用したいという要求があり、この場合、IO空間(データバッファ等)が不足するという問題点が生じることとなり、この問題点の解決が重要課題であった。

即ち、1つのプロセッサノードで制御する入出力装置の台数が多数になると、これらの入出力装置を使用するために必要な記憶領域(即ちIO空間)も大規模となるが、周知のPCI−ExpressなどのPCI仕様による定義では、全ての入出力装置に割り当てられるIO空間の合計が64KBに過ぎない。

よって、本発明でも、このような多数のIOデバイスを接続したいという要求を満たすために、1つのプロセッサノードで複数のIO空間を処理できるようにする手段の開発が課題の1つとなっている。

【0003】

なお、最近では、最新のOSとシステムファームウェア間には、複数のIO空間を設定して受け渡すインタフェースが定義されている。しかしながら、汎用の入出力装置を制御する制御装置用のLSIについては、複数のIO空間を認識して処理する手段は未だ開発されていない。一方、或る種の既成のOSでは、複数のIO空間を扱うことはできない。また、既成の汎用のIOノードのLSIにも、複数のIO空間を認識して処理する手段は設けられていない。

【0004】

この分野で先行して出願された特許の文献として、例えば、特許文献1では、インタコネクトを介して互いに接続されている複数の中央プロセッサユニット(CPU)ノードと、入力/出力(I/O)ノードと、メモリノードとを含む分散マルチノードコンピュータシステムが示されており、このコンピュータシステムは複数のドメインに分割されており、この各ドメインは、その独自のアドレス空間を有する独立したマシンとして機能するものとしており、また、各ドメイン上で、オペレーティングシステムが別々にランするものとしている。

【0005】

また、例えば、特許文献2では、計算機システムにおいて、LPAR制御プログラムが、1つの物理的なデバイスのメモリ空間及びIO空間を各OSに対して仮想的にマッピングする機能を有し、さらに、このLPAR制御プログラムは、1台の計算機システムを論理的な複数のパーティション(LPAR)に分割し、各LPARに対してLPARを特定するためのLPAR識別子を割当てる機能を有することを開示している。

【0006】

また、例えば、特許文献3では、2つのレジスタにコンフィグレーション空間のベースアドレス、サイズを設定することにより、メモリ空間に複数のコンフィグレーション空間をマップするものとし、コンフィグレーションアクセス検出回路が、フリット信号に含まれている、アクセス対象デバイスが接続されているバスのバス番号と上記バスを配下に持つIOノードに割り当てられているコンフィグレーション空間のセグメント番号とをマージしたインデックス信号を出力するものとしている。また、インデックス信号に対応するエントリに格納されているIOノードのノードIDを出力できるテーブルを設けると共に、フリット信号を上記ノードIDのIOノードへルーティングするクロスバースイッチを設けることが開示されている。

【0007】

さらに、例えば、特許文献4では、IO空間を有効利用可能として容量の制限を無くして、大容量IO空間を必要とするデバイスの接続を可能とすると共に、回路規模の増大を抑止低減することを意図し、IOアドレス空間を定める値が設定されるベースアドレスレジスタと、ベースアドレスレジスタの値と、前記システムバス上に送出されるアドレスとを比較し、両者が一致した場合に、前記システムバスに応答する共に選択信号をアクティブにするコンパレータと、システムバス上のアドレスと前記選択信号とを入力とし、エイリアス空間を避けるようにしてデバイスのマッピングを行ってデバイスの選択信号を生成するデコーダと、を備える構成の、システムバスのIOマッピング方式が開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−132037号公報

【特許文献2】特開2008−158710号公報

【特許文献3】特開2008−181389号公報

【特許文献4】特開平11−238029号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、上記背景技術で述べた従来の情報処理システムにあっては、前述のとおり、PCI−Express等のPCI仕様の場合、入出力装置の制御に使用できるIO空間は16ビットのアドレスで指定する64Kバイトの空間である。しかしながら、複数のIOノードを含む大規模な情報処理システムにおいては、多数のIOデバイスを接続して制御したいという要求があり、これらのIOデバイスがIO空間を使用する場合、IO空間が足りなくなるという問題点が有った。

【0010】

なお、前述の特許文献1〜4に開示されている技術は、本発明のように、マップされていない1つのIO空間を扱う既成の制御システムとの互換を考慮していないので、この点で、いずれも本発明とは異なるものである。また、個別では、

前述の特許文献1に開示された技術の場合、本発明のようにノード制御装置を設ける構成ではなく、複数の中央プロセッサユニットのOSがノード制御装置の役割を果たすものである。

【0011】

前述の特許文献2に開示された技術の場合、計算機システム内で稼動するLPAR制御プログラムが、本発明のノード制御装置に近い役割を果たすものである。

前述の特許文献3に開示された技術の場合、本発明とは最も近い構成であるが、メモリ空間には、IO空間ではなく、複数のコンフィグレーション空間をマップするものとしている。また、ノード制御装置内にはレジスタが2つ設けられている。

前述の特許文献4に開示された技術の場合、前述のとおり、大容量IO空間を必要とするデバイスの接続を可能にすることを意図したものであり、本発明のように、個々のIOノードが備える複数のIO空間を全て取り扱えることを可能にして、多数のIOデバイスを接続することを意図したものではない。

【0012】

本発明は、上記従来の問題点に鑑みてなされたものであって、複数のプロセッサノードと複数のIOノードとの間に、入出力データを交換するノード制御装置を設けると共に、該ノード制御装置に、メモリ空間に複数のIO空間を予めマップする機能と、アドレスからIO空間番号をデコードして対応のIOノードへアクセスをルーティングする機能とを備えることにより、個々のIOノードが備える複数のIO空間を全て取り扱えることを可能にして、多数のIOデバイスを接続することができるノード制御装置及びノード制御装置の制御方法並びに情報処理システムを提供することを目的としている。

【課題を解決するための手段】

【0013】

上記課題を解決するために、本発明に係るノード制御装置は、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置であって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルと、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定する手段と、を備えたことを特徴とする。

【0014】

また、本発明に係るノード制御装置の制御方法は、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置の制御方法であって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とする。

【0015】

また、本発明に係る情報処理システムとして、上述のノード制御装置を有する情報処理システムを提供するものである。

【0016】

さらに、本発明に係るコンピュータプログラムは、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置を制御させるためのコンピュータプログラムであって、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とする。

【発明の効果】

【0017】

以上説明したように、本発明によれば、1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数のIOノードとの間で入出力装置が担うデータの交換を行うノード制御装置において、IOノードの入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを設けると共に、データの交換の際に、プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定するIOノードと、該IOノードの入出力装置制御領域とを確定する構成としたので、多数の入出力装置を制御できるノード制御装置を提供することができる効果が有る。

【図面の簡単な説明】

【0018】

【図1】本発明の実施形態に係る情報処理システムの全体構成を示す構成図である。

【図2】IOノードの1例としての構成を示す構成図である。

【図3】本発明の実施形態に係るノード制御装置の構成を示す構成図である。

【図4】図3に示すノード制御装置130のポート入力部300の詳細構成を示す構成図である。

【図5】テーブル401のフォーマットを示すデータ構成図である。

【図6】IO空間及びその記憶装置上でのIO空間のマップを示すデータ構成図である。

【図7】本発明の情報処理システムにおいて情報を転送する際の転送フォーマットの1例を示すデータ構成図である。

【図8】図7に示すヘッダフリットのアドレスフィールドの、IO空間アクセスを行う場合の詳細構成を示すデータ構成図であり、図8(a)はメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマット(プロセッサノード発行)を示し、図8(b)は既成のIO空間アクセスのアドレスフォーマット(プロセッサノード及びノード制御装置発行)を示すものである。

【図9】図4に示すIO空間アクセス検出回路402において一致結果信号412及びノードID信号413を生成する際の処理手順を示すフローチャート図である。

【図10】2つのパーティションに区切った情報処理システムの1構成例を示す構成図である。

【発明を実施するための形態】

【0019】

本発明は、複数のIOノードを含む大規模な情報処理システムにおいて、少なくとも1台のノード制御装置を介することによって、PCI−ExpressなどのPCI仕様で定義されるIO空間(請求項に記載の入出力装置制御領域であり、データバッファを含む)を、複数設定して処理できるようにすることにより、既成のプロセッサが備えるIO空間よりも多数のIO空間を必要とするIOデバイスを接続可能にするものである。

また、従来どおり、1つのIO空間に全てのIOデバイスを割り当てて使用する既成のプロセッサによるIO空間の使用形態についても取り扱い可能とすることにより、複数のIO空間を認識できない既成の情報処理装置のOS(オペレーティングシステム)上でも動作可能にするものである。

【0020】

さらに、情報処理システムをパーティションに区切って、複数のOSを動作させる場合には、例えば、OS毎に、1つのIO空間のみを使うのか、それとも複数のIO空間を使うのかを選択できるように構成するものである。

このような、IO空間を使用するIOデバイスを、できるだけ多数接続したいという要求を実現するために、本発明では、システムファームウェアまたはサービスプロセッサによって制御される少なくとも1台のノード制御装置を設置することによって、1つのプロセッサで複数のIO空間を利用できるようにしている。

【0021】

以下、本発明のノード制御装置及びノード制御装置の制御方法並びに情報処理システム置の実施形態について、図面を参照して詳細に説明する。

図1は、本発明の実施形態に係る情報処理システムの全体構成を示す構成図である。

同図において、本実施形態の情報処理システムは、16個のプロセッサノード100〜115と、8個のIOノード120〜127と、4個のノード制御装置130〜133(本発明の実施形態に係るノード制御装置)と、を備える。

【0022】

8個のIOノード120〜127は、4個のノード制御装置130〜133に、2台づつ接続されている。4個のノード制御装置130〜133には、それぞれ4個のプロセッサノードと、2個のIOノードが接続されている。この4個のノード制御装置同士は、互いに1対1で接続されている。

図示しないが、プロセッサノード100〜115の各々は、1つまたは複数のプロセッサと主記憶を備える。

【0023】

本発明に係る情報処理システムは、図1に示す構成に限定されるものではなく、一般には、もっと小規模な構成(例えば、プロセッサノード2個、ノード制御装置1個、及びIOノード2個)といった構成や、もっと大規模な構成(例えば、プロセッサノード64個、IOノード32個、及びノード制御装置16)といった構成にすることも可能である。

図2は、IOノードの1例としての構成を示す構成図である。

同図に示すIOノードは、1台のIO制御装置200と、4台のIOデバイス210〜213とを備えて構成されている。

【0024】

IO制御装置200は、ノード制御装置130(本発明の実施形態に係るノード制御装置)とインタフェース160を介して接続されている。また、IO制御装置200は、IOデバイス210〜213と、それぞれインタフェース220〜223を介して接続されている。インタフェース220〜223は、PCI−ExpressなどのPCIの仕様に準拠するものとする。なお、図2に示す構成は1例であって、一般には、もっとIOデバイスの少ない構成や、もっとIOデバイスの多い構成にすることも可能である。

【0025】

図3は、本発明の実施形態に係るノード制御装置の構成を示す構成図である。

同図に示す本発明の実施形態に係るノード制御装置130は、9個のポート入力部300〜308と、9個のポート出力部310〜318と、クロスバースイッチ320と、を備えて構成される。ここで、一組のポート入力部とポート出力部とをポートと定義する。例えば、プロセッサノード100に接続するポートは、ポート入力部300とポート出力部310とから構成される。ノード制御装置130の9個のポートは、それぞれ、プロセッサノード100〜103、IOノード120〜121、及びノード制御装置131〜133を接続するためのものである。

【0026】

図4は、図3に示すノード制御装置130のポート入力部300の詳細構成を示す構成図である。

図3に示すノード制御装置130のポート入力部301〜308についても、図4に示すポート入力部300と同じ構成をとる。

レジスタ400は、本実施形態では16ビットのレジスタであり、メモリ空間にマップされるIO空間(入出力装置制御領域)のベースアドレスを指定する値を保持する。レジスタ400のビット15〜0は、ベースアドレスのビット47〜32に対応する。ベースアドレスの31〜0はオール0である。

【0027】

テーブル401は、レジスタで構成され、各IOノードに対応したエントリを備え、各IOノードに接続するIOデバイスに割り当てられるIO空間のレンジを指定する値を保持する。本実施形態では、IOノードは8個なので、8エントリのテーブルである。

【0028】

以下、図4を用いて、本発明の課題の具体的な解決手段を説明する。

レジスタ400には、IO空間のマップ先のメモリ空間のベースアドレスを設定する。

テーブル401は、情報処理システム内のIOノードの個数と等しいエントリを備え、各IOノードに接続するIOデバイスに割り当てられるIO空間の、IO空間番号及びアドレスレンジを設定する。

テーブル401には、また、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それともメモリにマップされたIO空間ではないのかを示す識別フラグを設定する。

【0029】

IO空間アクセス検出回路402は、対応するプロセッサノードから入力するフリット信号330(入出力データ情報)のコマンドコード及びアドレスをデコードして、IO空間へのアクセスであることを検出して出力し、ターゲットのIOノードのノードIDを検出して出力する。

IO空間アクセスフリット生成回路403及びセレクタ404は、メモリ空間にマップされたIO空間へのアクセスの場合は、IOノードが処理できるIO空間アクセスに変換し、さらに、ターゲットのIOノードのノードIDを指定してクロスバースイッチ320へ出力する。

【0030】

このようにして、本発明のノード制御装置では、複数のIO空間をメモリ空間にマップする機能を設けて、マップされたIO空間へのアクセスからIO空間番号を認識してターゲットのIOノードへ出力するので、複数のIO空間を扱うことが可能となり、よって、1つのプロセッサノードに対して、既成のノード制御装置と比較して多数のIOデバイスを接続することができる。さらに、IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、既成のノード制御装置のIO空間なのかの識別フラグを設けることにより、複数のIO空間を扱うことのできない既成のOSでも動作可能とすることができる。

【0031】

図5は、テーブル401のフォーマットを示すデータ構成図である。

同図において、エントリ0〜7は、IOノード120〜127に対応する。ビット15は、メモリ空間マップを示すフラグであり、‘0’で従来のIO空間、‘1’でメモリ空間にマップされたIO空間であることを指定する。ビット14〜12はIO空間番号であり、メモリ空間にマップされたIO空間が割り当てられる場合に、IO空間番号を指定する。ビット11〜6は上限アドレスであり、また、ビット5〜0は下限アドレスであり、それぞれIO空間アドレスのビット15〜10に対応してIO空間内のアドレスレンジを指定する。ここで、アドレスレンジの上限のアドレス9〜0はオール1であり、アドレスレンジの下限のアドレス9〜0はオール0である。例えば、下限アドレスが000100(2進数)で、上限アドレスが000111(2進数)の場合、アドレスレンジは1000〜1FFF(16進数)になる。

【0032】

レジスタ400及びテーブル401は、プロセッサの初期化時にシステムファームウェアまたはサービスプロセッサによって設定されるが、これらの設定に関する詳細な構成については、当業者にとってよく知られており、また本発明とは直接関係しないので説明は省略する。

IO空間アクセス検出回路402は、プロセッサノード100から入力するフリット信号330がヘッダフリットの場合(ストローブフィールドが‘01’(2進数)の場合)に、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の保持する値とを比較して、一致結果信号412と、ノードID信号413を生成する。

【0033】

図6は、IO空間及びその記憶装置上でのIO空間のマップを示すデータ構成図である。

以下、図6を参照して、IO空間のメモリ空間へのマップ方法を説明する。

1つのIO空間は64Kバイトであり、複数のIO空間はアドレス空間の一部の領域に連続してマップされる。図6は、N+1個のIO空間を、ベースアドレス〜(ベースアドレス+サイズ−1)の領域にマップした場合の例を示している。ここで、サイズは(N+1)×64Kバイトである。また、各IO空間はIO空間番号0〜Nで識別される。

本実施形態では、複数のIO空間をメモリ空間にマップする場合に、ACPI仕様で定義されるDense Translation方式を前提としているが、Sparse

Translation方式に対応させることも可能である。また、テーブル401に識別フラグを追加することにより、前記の両方式に対応させることも可能である。

【0034】

図7は、本発明の情報処理システムにおいて情報を転送する際の転送フォーマットの1例を示すデータ構成図である。

ここでは、論理的な情報の転送単位をパケットと定義し、また、パケットはひとつ以上のフリットから構成されるものと定義している。図7に示す各フリットは所定の固定されたビット幅を備えるが、この例では90ビット幅としている。このフリットには、ヘッダフリットと、データフリットとの2種類が存在し、図7では各フリットの転送フォーマットを示している。

【0035】

フリットのビット89〜88はストローブであり、フリットが有効であること、及びフリットの種類を示している。ストローブが‘00’(2進数)の場合は該フリットが無効であることを示し、ストローブが‘01’(2進数)の場合はヘッダフリットであることを示し、ストローブが‘10’(2進数)の場合はデータフリットであることを示す。但し、このコード定義はあくまで1例である。なお、パケットは、図7に示す1個のヘッダフリットと、0個、1個、2個、4個または8個のデータフリットとから構成される。よって、本実施形態のパケットは、最小のものでも1個のフリットから構成され、最大のものでは9個のフリットから構成されることになる。

【0036】

一般に、このようなフリットには、エラーの検出や訂正の目的で、ECCやパリティが付加されるが、本発明とは直接関係しないので、ここでの説明は省略する。

ヘッダフリットのビット87〜0には、それぞれ8ビットの5個のフィールドと、48ビットのアドレスフィールドとが定義される。これらのフィールド定義はあくまで1例であるが、一般には、情報処理装置のリソース、プロトコル及びトポロジーに依存して決定されるものである。

図7に示すコマンドコードは、例えばメモリリード、メモリライト、IOリード、IOライト、リプライといった、ターゲットの装置に対する動作を指定するコードが格納されるフィールドである。

【0037】

ソースノードIDは、パケットの転送元のプロセッサノードまたはIOノードを識別するための固有の番号が格納されるフィールドである。

ターゲットノードIDは、パケットの転送先のプロセッサノードまたはIOノードまたはノード制御装置を識別するための固有の番号が格納されるフィールドである。

データレングスは、リードリクエストの場合に、ターゲットのデータレングスをバイト単位で指定するフィールドである。00(16進数)〜40(16進数)の場合、0〜64バイトを指定する。他の値は未定義である。

アドレスは、リクエストのターゲットとなるアドレスを格納するフィールドである。

データフリットのビット71〜64には、バイトイネーブルが定義され、ビット63〜0に定義される各バイトの指定の有効または無効を指定する。

【0038】

図8は、図7に示すヘッダフリットのアドレスフィールドの、IO空間アクセスを行う場合の詳細構成を示すデータ構成図であり、図8(a)はメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマット(プロセッサノード発行)を示し、図8(b)は既成のIO空間アクセスのアドレスフォーマット(プロセッサノード及びノード制御装置発行)を示すものである。

本発明の本来の方式であるメモリ空間にマップされたIO空間へアクセスする場合のアドレスフォーマットでは、図8(a)において、ビット47〜32は、IO空間をマップするメモリ空間のベースアドレスである。また、ベースアドレスは、4Gバイト境界のアドレスを指定できるが、もっと細かい粒度で指定可能にすることもできる(例えば、ベースアドレスを47〜20にすれば、1Mバイト境界で指定することができる)。なお、ビット31〜19はオール0であり、使用しない。

【0039】

さらに、ビット18〜16は、IO空間番号であり、本実施形態では0〜7のいずれかの値をとるものとする。

情報処理システム内のIOノードの数が多い場合には、IO空間番号の取り得る値を広げることも可能である(例えば、IO空間番号を23〜16にして、0〜255の値を取るようにすることも可能である)。ビット15〜0は、IO空間のアドレスである。

他方、既成の方式であるIO空間アクセスのアドレスフォーマットでは、図8(b)において、ビット47〜36はオール0であり、使用されない。また、ビット15〜0はIO空間アドレスを示している。

【0040】

図9は、図4に示すIO空間アクセス検出回路402において一致結果信号412及びノードID信号413を生成する際の処理手順を示すフローチャート図である。

以下、図4〜8を参照しながら、図9に示すフローチャートを使用して、一致結果信号412及びノードID信号413の生成処理の手順を説明する。

この生成処理は、IO空間アクセス検出回路402において、システムファームウェアによって実行されるものである。

(ステップS1)

まず、ステップS1では、IO空間アクセス検出回路402は、プロセッサノード100から送出されたコマンド(図示は省略)のコマンドコードフィールドを検証する。

【0041】

(ステップS2)

次に、ステップS2では、IO空間アクセス検出回路402は、前記検証結果に基づき、前記コマンドコードフィールドがメモリ空間アクセス(メモリリードまたはメモリライト)を示している場合は制御の流れをステップS3に進め、前記コマンドコードフィールドがIO空間アクセス(IOリードまたはIOライト)を示している場合は制御の流れをステップS5に移す。

(ステップS3)

ステップS3では、IO空間アクセス検出回路402は、レジスタ400の値がアドレス47〜32の値と等しいか否かを検証し、レジスタ400の値がアドレス47〜32の値と等しい場合はステップS4に進み、レジスタ400の値がアドレス47〜32の値と等しくない場合はステップS5に移る。

【0042】

(ステップS4)

ステップS4では、IO空間アクセス検出回路402は、テーブル402の全エントリに関して、メモリ空間マップが1で、かつIO空間番号がアドレス18〜16と等しく、かつ下限アドレス≦アドレス15〜10の値≦上限アドレス値であることをチェックし、ステップS6に進む。

(ステップS5)

ステップS5では、IO空間アクセス検出回路402は、テーブル402の全エントリに関して、メモリマップが0で、かつ下限アドレス≦アドレス15〜10の値≦上限アドレス値であることをチェックし、ステップS6に移る。

【0043】

(ステップS6)

ステップS6では、IO空間アクセス検出回路402は、テーブル402にコマンドコードフィールドで指定された条件と一致するエントリが存在するか否かを検証し、テーブル402に前記条件と一致するエントリが存在する場合はステップS7に進み、テーブル402に前記条件と一致するエントリが存在しない場合はステップS8に移る。

(ステップS7)

ステップS7では、IO空間アクセス検出回路402は、一致結果信号412を‘1’にし、ノードID信号413を一致したエントリに対応するIOノードのノードIDにして出力し、処理を終了する。

【0044】

(ステップS8)

ステップS8では、IO空間アクセス検出回路402は、一致結果信号412を‘0’にして出力し、処理を終了する。

【0045】

なお、IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットの場合に、アドレスフィールドのビット47〜16をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、コマンドコードがメモリリードのコードならばIOリードのコードに差し替え、メモリライトのコードならばIOライトのコードに差し替えて、ヘッダフリット信号414として出力する。

セレクタ404は、一致結果信号412が‘0’ならばフリット信号330を選択し、一致結果信号412が‘1’ならばヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

【実施例】

【0046】

以下、本実施形態に係る情報処理システムの1実施例としての動作を説明する。

最初に、第1の実施例として、ノード制御装置130のポート入力部300が、複数のIO空間をメモリ空間にマップして使用する場合の動作について説明する。

まず、本実施形態に係る情報処理システムの初期化時の設定について説明する。

IO空間アクセス検出回路402のシステムファームウェアは、IOノード120〜127に関して、IO空間番号とIO空間内のアドレスレンジを割当てる。例えば、IOノード120〜127にIO空間番号0〜7を割り当てる。また、IOノード120には0000〜7FFF(16進数)のレンジを割り当て、IOノード121〜127には8000〜FFFF(16進数)のレンジを割り当てる。

【0047】

次に、前記システムファームウェアは、IO空間をマップするメモリ空間のベースアドレスを決定し、ノード制御装置130〜133のレジスタ400にセットする(ポート入力部301〜303にも同様にセットする)。例えば、ベースアドレスを1C0000000000(16進数)とすると、レジスタ400には1C00(16進数)をセットする。

さらに、前記システムファームウェアは、ノード制御装置130〜133のテーブル401に値をセットする(ポート入力部301〜303にも同様にセットする)。

【0048】

テーブル401のエントリ0の設定値は、メモリ空間マップが1、IO空間番号が000(2進数)、上限アドレスが011111(2進数)、下限アドレスが000000(2進数)である。また、エントリ1の設定値は、メモリ空間マップが1、IO空間番号が001(2進数)、上限アドレスが111111(2進数)、下限アドレスが100000(2進数)である。エントリ2〜7の設定値はIO空間番号を除きエントリ1と同じであり、IO空間番号は、それぞれ010〜111(2進数)である。これらの設定は、前記システムファームウェアの代わりにサービスプロセッサが行っても良い。

引き続き、プロセッサノード100から、IOノード124配下のIOデバイスに対して、IO空間アドレス8000(16進数)で、IOリードを行う場合について説明する。

【0049】

プロセッサノード100は、図7に示すヘッダフリットのフォーマットに関して、ストローブを01(2進数)とし、コマンドコードをメモリリードのコードとし、ソースノードIDをプロセッサノード100のノードIDとし、ターゲットノードIDをノード制御装置130のノードIDとし、データレングスをアクセス対象のデータ長に対応する値にして、フリット信号330を発行する。

ここで、トランザクションIDは、プロセッサノード100についてユニークな番号とする。また、図7のアドレスは、図8のアドレスフォーマットを参照して説明すると、ビット47〜32はベースアドレスの1C00(16進数)、ビット31〜19はオール0、ビット18〜16はIOノード124に割り当てられるIO空間番号の100(2進数)、ビット15〜0は8000(16進数)とする。つまり、プロセッサノード100からは、アドレス1C0000048000(16進数)に対するメモリリードが発行される。

【0050】

さらに、複数のIO空間をメモリ空間にマップして使用する場合のIO空間アクセス検出回路402の動作について、図9に示すフローチャート図を参照して説明する。

プロセッサ100からフリット信号330が入力すると、IO空間アクセス検出回路402は、入力したフリットのストローブフィールドが01(2進数)でヘッダフリットであるので、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の値との比較を行う。

ステップS1で、コマンドコードフィールドのチェックを行い、ステップS2で、メモリリードのコマンドコードであるため、メモリ空間アクセスであることを検出する。よって、ステップS3に進んで、レジスタ400とアドレス47〜32を比較し、両方の値が1C00(16進数)で等しいことを検出し、ステップS4に進む。

【0051】

ステップS4では、テーブル402のエントリ4に関して、メモリ空間マップが1で、かつIO空間番号が100(2進数)で、かつアドレス15〜30(100000(2進数))が下限アドレスから上限アドレスの範囲(100000〜111111(2進数))に含まれていることを検出する。よって、ステップS6では、エントリ4が条件と一致するエントリなのでステップ7に進み、ステップ7で、一致結果信号412を1にして出力し、ノードID信号413を、テーブル401のエントリ4に対応するIOノード214のノードIDにして出力して処理を終了する。

【0052】

IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットであるので、アドレスフィールドのビット47〜32をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、コマンドコードがメモリリードのコードなのでIOリードのコードに差し替えて、ヘッダフリット信号414として出力する。

セレクタ404は、一致結果信号412が1なので、ヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

【0053】

クロスバースイッチ320は、ターゲットノードIDに従って、フリットをポート出力部317へ出力する。なお、クロスバースイッチ320がターゲットノードIDに従って、出力先のポート出力部を決定する方法は、本発明とは直接関係しないので、その説明は省略する。

ポート出力部317から出力されたフリットは、ノード制御装置132を経由して、IOノード124へ出力され、IOノード124内に存在するターゲットのIOデバイスへ出力される。その後、ターゲットのIOデバイスからは、リプライデータがノード制御装置132及びノード制御装置130を経由して、プロセッサノード100に返却される。

【0054】

次に、第2の実施例として、1つのIO空間を使用する場合の動作について説明する。

まず、プロセッサの初期化時に実施する設定について説明する。

システムファームウェアは、IOノード120〜127に関して、IO空間内のアドレスレンジを割当てる。例えば、

IOノード120には0000〜1FFF(16進数)、

IOノード121には2000〜3FFF(16進数)、

IOノード122には4000〜5FFF(16進数)、

IOノード123には6000〜7FFF(16進数)、

IOノード124には8000〜9FFF(16進数)、

IOノード125にはA000〜BFFF(16進数)、

IOノード126にはC000〜DFFF(16進数)、

IOノード127にはE000〜FFFF(16進数)、

といったアドレスレンジを割り当てる。

【0055】

次に、システムファームウェアは、ノード制御装置130〜133のテーブル401に値をセットする(ポート入力部301〜303にも同様にセットする)。

テーブル401の全エントリに関して、メモリ空間マップは0、IO空間番号は000(2進数)である。

テーブル401の上限アドレス及び下限アドレスの設定値は、

エントリ0が000111及び000000(2進数)、

エントリ1が001111及び001000(2進数)、

エントリ2が010111及び010000(2進数)、

エントリ3が011111及び011000(2進数)、

エントリ4が100111及び100000(2進数)、

エントリ5が101111及び101000(2進数)、

エントリ6が110111及び110000(2進数)、

エントリ7が111111及び111000(2進数)、

である。

なお、これらの設定は、システムファームウェアの代わりにサービスプロセッサが行っても良い。

【0056】

次に、プロセッサノード100から、IOノード124配下のIOデバイスに対して、IO空間アドレス8000(16進数)で、IOリードを行う場合について説明する。

プロセッサノード100は、図7のヘッダフリットのフォーマットに関して、ストローブを01(2進数)とし、コマンドコードをIOリードのコードとし、ソースノードIDをプロセッサノード100のノードIDとし、ターゲットノードIDをノード制御装置130のノードIDとし、データレングスをアクセス対象のデータ長に対応する値にして、フリット信号330を発行する。ここで、トランザクションIDは、プロセッサノード100についてユニークな番号とする。また、図7のアドレスは、図8のアドレスフォーマットを参照して説明すると、ビット47〜16はオール0、ビット15〜0は8000(16進数)とする。つまり、プロセッサノード100からは、アドレス000000008000(16進数)に対するIOリードが発行される。

【0057】

さらに、IO空間アクセス検出回路402の動作について、図9に示すフローチャート図を参照して説明する。

プロセッサ100からフリット信号330が入力されると、IO空間アクセス検出回路402は、入力したフリットのストローブフィールドが01(2進数)でヘッダフリットであるので、ヘッダフリットのコマンドコードフィールド及びアドレスフィールドと、レジスタ400及びテーブル401の値との比較を行う。

ステップS1で、コマンドコードフィールドのチェックを行い、ステップ2では、IOリードのコマンドコードであるため、IO空間アクセスであることを検出し、ステップS5に移る。

【0058】

ステップS5では、テーブル401のエントリ4に関して、メモリ空間マップが0で、かつアドレス15〜10(100000(2進数))が下限アドレスから上限アドレスの範囲(100000〜100111(2進数))に含まれていることを検出する。よって、上限に一致するエントリが有るので、ステップS7に進み、ステップ7で、一致結果信号412を‘1’にして出力し、ノードID信号413を、テーブル401のエントリ4に対応するIOノード214のノードIDにして出力し、処理を終了する。

この場合、IO空間アクセスフリット生成回路403は、プロセッサノード100から入力するフリット信号330がヘッダフリットであるので、アドレスフィールドのビット47〜32をオール0に差し替え、ターゲットノードIDをIO空間アクセス検出回路402から入力するノードID信号413に差し替え、ヘッダフリット信号414として出力する。アドレスフィールドのビット47〜32の差し替えは、差し替え前及び差し替え後ともオール0なので、実施しないのと同等である。

【0059】

セレクタ405は、一致結果信号412が‘1’なので、ヘッダフリット信号414を選択して、フリット信号340をクロスバースイッチ320へ出力する。

クロスバースイッチ320は、ターゲットノードIDに従って、フリットをポート出力部317へ出力する。なお、クロスバースイッチ320がターゲットノードIDに従って、出力先のポート出力部を決定する方法は、本発明とは直接関係しないので、その説明は省略する。

ポート出力部317から出力されたフリットは、ノード制御装置132を経由して、IOノード124へ出力され、IOノード124内に存在するターゲットのIOデバイスへ出力される。その後、ターゲットのIOデバイスからは、リプライデータがノード制御装置132及びノード制御装置130を経由して、プロセッサノード100に返却される。

次に、第3の実施例として、情報処理システム全体を2つのパーティションに区切り、その一方では1つのIO空間のみを使用し、他方では複数のIO空間をメモリ空間にマップして使用する場合について説明する。

【0060】

図10は、2つのパーティションに区切った情報処理システムの1構成例を示す構成図である。

この実施例では、図10に示すように、図1に示す情報処理システムの構成を、パーティション500とパーティション501とに区切る構成とし、各々独立のOSで制御される場合の1実施例としての構成を示す。

この実施例では、パーティション500で、1つのIO空間のみを使用し、パーティション501では、複数のIO空間をメモリ空間にマップして使用するものとする。

各プロセッサノードの初期化時に実施する設定については、パーティション毎に行われる。ここで、ノード制御装置130及びノード制御装置131は2つのパーティション(500、501)に含まれるが、各ポート入力部300〜303には、接続するプロセッサノードが含まれるパーティションの設定のみが行われる。

【0061】

パーティション500に関しては、プロセッサノード100、101、104、105が含まれるので、ノード制御装置(130,131)のポート入力部(300,301)においては、テーブル401が設定される。

また、パーティション500には、IOノード(120,122)が含まれるので、テーブル401のエントリ0及びエントリ2のみに有効なレンジが設定される。ここで、パーティション500に存在しないIOノードに対応するエントリ(1、3〜7) には無効なレンジが設定される。このような無効なレンジの設定の1例としては、上限アドレスを000000(2進数)に設定し、下限アドレスを111111(2進数)に設定する方法が可能である。

【0062】

他方、パーティション501に関しては、プロセッサノード(102、103、106、107、108〜115)が含まれるので、ノード制御装置(130,131)のポート入力部(302,303)と、ノード制御装置(132,133)のポート入力部300〜303において、レジスタ400及びテーブル401が設定される。

パーティション501には、IOノード121、123〜127が含まれるので、テーブル401のエントリ1及びエントリ3〜7のみに有効なレンジが設定される。ここで、パーティション501に存在しないIOノードに対応するエントリ(0、2) には無効なレンジが設定される。この設定以降の動作は、先の説明と同様になるので、省略する。

【0063】

以上説明したように、本実施形態に係るノード制御装置及び情報処理システムでは、複数のIO空間をメモリ空間にマップする機能を設けて、マップされたIO空間へのアクセスからIO空間番号を認識してターゲットのIOノードへ出力しているので、複数のIO空間を扱うことが可能となり、よって、1つのプロセッサノードに多数のIOデバイスを接続して使用することができる効果が有る。

また、各IOノードに接続するIOデバイスに割り当てられるIO空間が、メモリにマップされたIO空間なのか、それとも1つのIO空間なのかを判別するための識別フラグを設けたことにより、複数のIO空間を扱うことのできない既成のOSを使用しても動作可能とすることができる効果が得られる。

【0064】

さらに、前記ノード制御装置の入力ポート毎に処理回路を設け、個別に設定可能にすることにより、本発明に係る情報処理システムをパーティションに区切って使用すれば、複数のIO空間をサポートしているOSと、1つのIO空間しかサポートしていないOSとを組み合わせて使用することができる効果が得られる。

【0065】

なお、本発明に係るノード制御装置の各構成要素の処理の少なくとも一部をコンピュータ制御により実行するものとし、かつ、上記処理を、図9のフローチャートで示した手順によりコンピュータに実行せしめるプログラムは、半導体メモリを始め、CD−ROMや磁気テープなどのコンピュータ読み取り可能な記録媒体に格納して配付してもよい。そして、少なくともマイクロコンピュータ、パーソナルコンピュータ、汎用コンピュータを範疇に含むコンピュータが、上記の記録媒体から上記プログラムを読み出して、実行するものとしてもよい。

【産業上の利用可能性】

【0066】

本発明は、ノード制御装置及び情報処理システムの構築に適用可能であり、特に、1つのプロセッサノードで制御する入出力装置の台数が多数となり、これらの入出力装置を使用するために必要な記憶領域も大規模となる場合にも対応できるノード制御装置の構築と、該ノード制御装置を含む情報処理システムの構築に好適である。

【符号の説明】

【0067】

100〜115 プロセッサノード

120〜127 IOノード

130〜133 ノード制御装置

200 IO制御装置

210〜213 IOデバイス

300〜308 ポート入力部

310〜318 ポート出力部

320 クロスバースイッチ

400 レジスタ

401 テーブル(各IOノードの属性情報)

【特許請求の範囲】

【請求項1】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置であって、

前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルと、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定する手段と、

を備えたことを特徴とするノード制御装置。

【請求項2】

前記照合の際に、前記入出力データ情報に指定された条件と一致する情報を保持したエントリが前記テーブルに存在する場合は、該エントリ内の情報を参照して前記IOノード及び該IOノードの前記入出力装置制御領域を確定し、他方、前記入出力データ情報に指定された条件と一致する情報を保持したエントリが前記テーブルに存在しない場合は、前記入出力データ情報を参照して前記IOノード及び該IOノードの前記入出力装置制御領域を確定することを特徴とする請求項1記載のノード制御装置。

【請求項3】

前記テーブル内の前記エントリの各々には、前記入出力装置制御領域が、記憶装置上にマップされた領域なのか否かを示す情報が含まれていることを特徴とする請求項1または請求項2記載のノード制御装置。

【請求項4】

前記テーブル内の前記エントリの各々には、前記入出力装置制御領域を一意に識別するための情報と、前記入出力装置制御領域の上限アドレス及び前記入出力装置制御領域の下限アドレスとが含まれていることを特徴とする請求項1乃至3のいずれか1項に記載のノード制御装置。

【請求項5】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置の制御方法であって、

前記ノード制御装置は、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とするノード制御装置の制御方法。

【請求項6】

請求項1乃至4のいずれか1項に記載のノード制御装置を有する情報処理システム。

【請求項7】

1つの入出力装置制御領域のみを使用する情報処理系と、記憶領域にマップされた複数の前記入出力装置制御領域を使用する情報処理系とに分割されていることを特徴とする請求項6記載の情報処理システム。

【請求項8】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置を制御させるためのコンピュータプログラムであって、

前記ノード制御装置は、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とするコンピュータプログラム。

【請求項1】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置であって、

前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルと、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定する手段と、

を備えたことを特徴とするノード制御装置。

【請求項2】

前記照合の際に、前記入出力データ情報に指定された条件と一致する情報を保持したエントリが前記テーブルに存在する場合は、該エントリ内の情報を参照して前記IOノード及び該IOノードの前記入出力装置制御領域を確定し、他方、前記入出力データ情報に指定された条件と一致する情報を保持したエントリが前記テーブルに存在しない場合は、前記入出力データ情報を参照して前記IOノード及び該IOノードの前記入出力装置制御領域を確定することを特徴とする請求項1記載のノード制御装置。

【請求項3】

前記テーブル内の前記エントリの各々には、前記入出力装置制御領域が、記憶装置上にマップされた領域なのか否かを示す情報が含まれていることを特徴とする請求項1または請求項2記載のノード制御装置。

【請求項4】

前記テーブル内の前記エントリの各々には、前記入出力装置制御領域を一意に識別するための情報と、前記入出力装置制御領域の上限アドレス及び前記入出力装置制御領域の下限アドレスとが含まれていることを特徴とする請求項1乃至3のいずれか1項に記載のノード制御装置。

【請求項5】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置の制御方法であって、

前記ノード制御装置は、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とするノード制御装置の制御方法。

【請求項6】

請求項1乃至4のいずれか1項に記載のノード制御装置を有する情報処理システム。

【請求項7】

1つの入出力装置制御領域のみを使用する情報処理系と、記憶領域にマップされた複数の前記入出力装置制御領域を使用する情報処理系とに分割されていることを特徴とする請求項6記載の情報処理システム。

【請求項8】

1つの入出力装置制御領域を使用して1または複数の入出力装置を制御する情報処理系を1単位のIOノードとし、複数のプロセッサノードと複数の前記IOノードとの間で前記入出力装置が担うデータの交換を行うノード制御装置を制御させるためのコンピュータプログラムであって、

前記ノード制御装置は、前記IOノードの前記入出力装置制御領域各々の属性情報を予め対応するエントリに記憶して成るテーブルを備え、

前記データの交換の際に、前記プロセッサノードから発行される入出力データ情報と前記テーブル内の前記エントリ各々の情報とを照合した照合結果により、該入出力データ情報が指定する前記IOノードと、該IOノードの前記入出力装置制御領域とを確定するステップを有することを特徴とするコンピュータプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2011−70296(P2011−70296A)

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願番号】特願2009−219093(P2009−219093)

【出願日】平成21年9月24日(2009.9.24)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成23年4月7日(2011.4.7)

【国際特許分類】

【出願日】平成21年9月24日(2009.9.24)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]