ハイパス型のノッチフィルタ及びこのフィルタを備えた電子機器

【課題】減衰域よりも高周波数帯域側に通過帯域を設定したハイパス型のノッチフィルタにおいて、前記通過帯域における挿入損失を抑えること。

【解決手段】入力ポート5と出力ポート6との間に2つのSAW共振子11、12からなる直列回路を直列に配置すると共に、これらSAW共振子11、12間にインダクタ素子15を並列に接続する。そして、SAW共振子11(12)に対して、容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を並列に接続する。更に、補助インダクタ素子31(32)のインダクタンス値が0.5nH〜1.6nHとなるようにする。

【解決手段】入力ポート5と出力ポート6との間に2つのSAW共振子11、12からなる直列回路を直列に配置すると共に、これらSAW共振子11、12間にインダクタ素子15を並列に接続する。そして、SAW共振子11(12)に対して、容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を並列に接続する。更に、補助インダクタ素子31(32)のインダクタンス値が0.5nH〜1.6nHとなるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ある周波数帯域に減衰域を設けると共に、この減衰域よりも高周波数側に通過帯域を設けたハイパス型のノッチフィルタ及びこのフィルタを備えた電子機器に関する。

【背景技術】

【0002】

SAW(surface acoustic wave:弾性表面波)を利用したフィルタの一つとして、ある周波数帯域に減衰域を設けると共に、この減衰域よりも高周波数側に通過帯域を設けたハイパス型のノッチフィルタが知られている。このフィルタは、図13に示すように、圧電基板上に互いに直列に接続した複数例えば2つのSAW共振子100を入力ポート101と出力ポート102との間に配置した構成が採られる。図13中103はインダクタ素子である。

【0003】

このフィルタにおいて、前記通過帯域を例えば800MHz以上もの高周波数帯域に設定しようとすると、当該高周波数帯域ではフィルタの挿入損失が劣化してしまう。即ち、このような高周波数帯域では、圧電基板上を伝搬する弾性表面波のうち一部が圧電基板の内部に向かって伝搬するバルク波などに変換されてしまうので、このバルク波の分だけエネルギー損失が起こってしまう。従って、SAW共振子100は、前記高周波数帯域では見かけ上Q値の悪い(小さい)コンデンサとなる。

【0004】

そこで、図14に示すように、SAW共振子100が既述の高周波数帯域において見かけ上Q値の良好な(高い)コンデンサとなるように、前記SAW共振子100に対して容量素子105を並列に接続する手法を採る場合もある。この場合には、通過帯域における挿入損失が改善されるが、前記挿入損失を更に低減させる技術が求められている。

特許文献1には、高域側減衰帯域の減衰極周波数を変更するために、付加インダクタ561及び付加キャパシタ562を直列腕共振器510に対して各々並列に接続したバンドパスフィルタについて記載されているが、既述の課題については検討されていない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−223147

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明はこのような事情に鑑みてなされたものであり、その目的は、減衰域よりも高周波数帯域側に通過帯域を設定したハイパス型のノッチフィルタにおいて、前記通過帯域における挿入損失を抑えることのできるノッチフィルタ及びこのフィルタを備えた電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本発明のノッチフィルタは、

減衰域よりも高周波数側の900MHz以上の周波数帯域に通過帯域を設けたハイパス型のノッチフィルタにおいて、

入力信号が入力される入力ポートと、

出力信号が取り出される出力ポートと、

前記減衰域を形成するために、前記入力ポート及び前記出力ポートの間に直列に配置され、この減衰域に対応する周波数で各々並列共振を起こす2つのSAW共振子からなる直列回路と、

これらSAW共振子間における接続点とアースとの間に接続されたインダクタ素子と、

前記SAW共振子のうち少なくとも一方のSAW共振子に設けられ、この一方のSAW共振子に対して並列となるように配置された容量素子及び補助インダクタ素子からなる直列回路と、を備え、

前記補助インダクタ素子のインダクタンス値は、前記通過帯域における挿入損失が0.5dB以下となるように構成されていることを特徴とする。

【0008】

前記容量素子及び前記補助インダクタ素子は、前記SAW共振子の各々に設けられていても良い。

前記SAW共振子の各々は、圧電基板上に配置され、

前記インダクタ素子は、前記圧電基板上に引き回された導電路であっても良い。

前記入力ポート及び前記出力ポートが配置される共通の基板を備え、

前記インダクタ素子は、前記基板上あるいは前記基板の内部に配置された導電路であっても良い。

また、本発明の電子機器は、

以上説明したノッチフィルタを備えたことを特徴とする。

【発明の効果】

【0009】

本発明は、ハイパス型のノッチフィルタにおいて、減衰域において各々並列共振を起こす2つのSAW共振子の直列回路を入力ポートと出力ポートとの間に直列に配置すると共に、これらSAW共振子の少なくとも一方のSAW共振子について、容量素子及び補助インダクタ素子からなる直列回路を並列となるように設けている。そして、通過帯域における挿入損失が0.5dB以下となるように補助インダクタ素子のインダクタンス値を設定している。そのため、フィルタのリターンロスが良好となり、外部の整合回路において整合を取りやすくなるので、前記通過帯域において良好な挿入損失のノッチフィルタを得ることができる。

【図面の簡単な説明】

【0010】

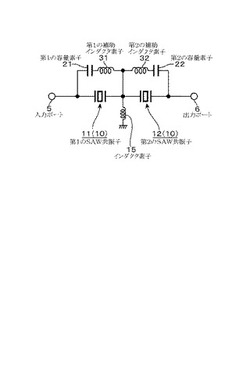

【図1】本発明のノッチフィルタの一例を示す回路図である。

【図2】前記フィルタの概観を模式的に示す斜視図である。

【図3】前記フィルタの概観を示す縦断面図である。

【図4】前記フィルタの圧電基板上のSAW共振子などの配置レイアウトを示す平面図である。

【図5】前記フィルタの周波数特性を示す特性図である。

【図6】前記フィルタの周波数特性を示す特性図である。

【図7】前記フィルタの周波数特性を示す特性図である。

【図8】前記フィルタの周波数特性を示す特性図である。

【図9】前記フィルタの他の例を示す電気回路図である。

【図10】前記フィルタの別の例を示す電気回路図である。

【図11】前記フィルタの更に別の例を示す電気回路図である。

【図12】前記フィルタの更にまた別の例の一部を示すパッケージ基板の縦断面図である。

【図13】従来のノッチフィルタを示す電気回路図である。

【図14】従来のノッチフィルタを示す電気回路図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態の一例であるノッチフィルタについて、図1〜図4を参照して説明する。先ず、フィルタの回路構成について説明する。このフィルタは、一部の周波数帯域この例では1GHz±2MHzを阻止域に設定すると共に、この阻止域よりも高域側(高周波数側)の1.1GHz〜3GHzまでを通過帯域としたハイパス型のノッチフィルタである。具体的には、このノッチフィルタは、図1に示すように、2つのSAW(surface acoustic wave:弾性表面波)共振子10からなる素子部を互いに直列に接続すると共に、これらSAW共振子10、10を入力ポート5と出力ポート6との間に直列に配置している。SAW共振子10、10の各々の反共振点(反共振周波数)は、前記阻止域に対応する周波数に設定されている。これらSAW共振子10、10の間には、はしご型回路を構成するためのインダクタ素子15が並列に接続されており、このインダクタ素子15は接地されている。尚、図1ではSAW共振子10について簡略化している。

【0012】

そして、前記2つのSAW共振子10、10のうち入力ポート5側のSAW共振子10及び出力ポート6側のSAW共振子10を夫々第1のSAW共振子11及び第2のSAW共振子12と呼ぶと、第1のSAW共振子11には、第1の容量素子21と第1の補助インダクタ素子31とからなる直列回路が並列に接続されている。即ち、前記直列回路の一端側が入力ポート5と第1のSAW共振子11との間の接続点に接続され、当該直列回路の他端側が2つのSAW共振子11、12間の接続点に接続されている。また、第2のSAW共振子12についても、第1のSAW共振子11と同様に第2の容量素子22と第2の補助インダクタ素子32とからなる直列回路が並列に接続されている。各々の容量素子21、22の容量値は例えば各々2pFに設定されている。また、各々のインダクタ素子31、32のインダクタンス値は、例えば3GHzにおいて各々0.5nH〜1.6nHこの例では1.2nHとなるように設定されている。これら容量素子21、22及び補助インダクタ素子31、32を設けた理由については、後で詳述する。

【0013】

次に、既述の図1の電気回路に対応する各部の構成及びノッチフィルタの概観について説明する。このフィルタは、図2及び図3に示すように、例えば水晶などからなる圧電基板41と、既述の容量素子21、22及びインダクタ素子15に夫々対応する電子部品42と、これら圧電基板41及び電子部品42が配置される共通の例えばアルミナ(Al2O3)などのセラミックスからなるパッケージ基板43と、を備えている。そして、これら電子部品42と圧電基板41(詳しくは圧電基板41の下方側に配置された後述のバンプ47)とは、パッケージ基板43上を引き回された引き回し電極44により、既述の図1の電気回路となるように互いに接続されている。図2及び図3中45は、パッケージ基板43の表面を覆う例えば樹脂などからなる封止材である。尚、図2及び図3では、夫々の電子部品42について、対応する容量素子21、22及びインダクタ素子15の符号を括弧書きで併記している。また、図3は、図2におけるA−A線にてパッケージ基板43を切断した縦断面図を示しており、引き回し電極44については描画を省略している。

【0014】

圧電基板41上には、図4に示すように、既述のSAW共振子11、12が当該圧電基板41の長手方向(X方向)に互いに離間するように配置されている。各々のSAW共振子11、12は、複数本の電極指51及び一対のバスバー52を備えたIDT(インターデジタルトランスデューサ)電極53と、このIDT電極53を弾性表面波(以後「弾性波」と言う)の伝搬方向(Y方向)における一方側及び他方側から挟み込むように各々配置された反射器54、54を備えている。以下において、第1のSAW共振子11側及び第2のSAW共振子12側を夫々「手前側」及び「奥側」と呼ぶ。図4中55は反射器電極指、56は反射器バスバーである。尚、図4は図1における圧電基板41を下方側(パッケージ基板43側)から見た様子を示している。

【0015】

ここで、既述の補助インダクタ素子31、32は、圧電基板41上に引き回された導電路46により構成されている。即ち、弾性波の伝搬方向における一方側及び他方側を夫々右方向及び左方向と呼ぶと、第1のSAW共振子11の左側には、第1の補助インダクタ素子31をなす導電路46が圧電基板41上を手前側から奥側に向かって例えば蛇腹状(メアンダ状)に伸びるように配置されている。また、第2のSAW共振子12の左側には、圧電基板41上を奥側から手前側に向かって同様に蛇腹状に伸びるように配置された導電路46が第2の補助インダクタ素子32として配置されている。これら補助インダクタ素子31、32は、夫々既述のインダクタンス値となるように、導電路46の厚み寸法、幅寸法及び長さ寸法が調整されている。

【0016】

そして、これらSAW共振子11、12及び補助インダクタ素子31、32は、パッケージ基板43上に配置された金属体例えば半田などからなる既述のバンプ47によって、パッケージ基板43上における引き回し電極44あるいはビアプラグ48に電気的に接続されている。具体的には、圧電基板41上には5つのバンプ47が配置されており、これらバンプ47の夫々に「a」〜「e」の添え字を付すと、第1のSAW共振子11の手前側のバスバー52はバンプ47aに接続されている。

【0017】

また、第1の補助インダクタ素子31の手前側の端部は、バンプ47bに接続されている。第1のSAW共振子11の奥側のバスバー52、第2のSAW共振子12の手前側のバスバー52、第1の補助インダクタ素子31の奥側の端部及び第2の補助インダクタ素子32の手前側の端部は、共通のバンプ47cに各々接続されている。第2のSAW共振子12の奥側のバスバー52はバンプ47dに接続され、第2の補助インダクタ素子32の奥側の端部はバンプ47eに接続されている。尚、これらバンプ47a〜47eは、実際にはパッケージ基板43側に設けられていて、圧電基板41を当該パッケージ基板43側に当接させることにより図4の状態となるが、図示を簡略化するために圧電基板41側に配置されているものとして説明している。

【0018】

これらバンプ47a〜47eのうちバンプ47a及びバンプ47dの下方側におけるパッケージ基板43には、当該パッケージ基板43を上下に貫通するように形成された電極であるビアプラグ48、48が各々形成されている。各々のビアプラグ48、48の下面には、電極膜からなる接続用端子部49が各々形成されており、バンプ47aに接続される接続用端子部49と、バンプ47dに接続される接続用端子部49とは、夫々入力ポート5及び出力ポート6をなしている。こうして圧電基板41におけるSAW共振子11、12及びインダクタ素子31、32の配置された面をパッケージ基板43に当接させることにより、バンプ47a〜47eを介して圧電基板41がパッケージ基板43上の引き回し電極44及びビアプラグ48に電気的に接続されると共に固定される。尚、バンプ47cの下方側におけるパッケージ基板43にもビアプラグ48が設けられていて、このビアプラグ48の下面側に配置された接続用端子部49を介してインダクタ素子15が接地されているが、ここでは図示を省略している。また、図4には、パッケージ基板43上に配置されるインダクタ素子15や容量素子21、22についても模式的に圧電基板41の外側に描画している。

【0019】

ここで、SAW共振子11(12)に容量素子21(22)及び補助インダクタ素子31(32)を並列に接続した理由について説明する。既述のように、このノッチフィルタでは通過帯域を1.1GHz以上もの高周波数帯域に設定しているので、このような高周波数帯域ではフィルタの挿入損失が劣化しやすい。即ち、このような高周波数帯域では、圧電基板41上を伝搬する弾性波のうち一部が圧電基板41の内部に向かって伝搬するバルク波などに変換される場合があり、その場合にはバルク波の分だけエネルギー損失が起こってしまう。従って、SAW共振子11(12)は、前記高周波数帯域では見かけ上Q値の悪い(小さい)コンデンサとなる。そのため、各々のSAW共振子11(12)が見かけ上Q値の良好な(高い)コンデンサとなるように、容量素子21(22)を並列に接続している。具体的には、これら容量素子21、22について、各々の容量値が1〜10pFこの例では2pFに設定している。そして、各々のSAW共振子11、12においてリターンロスが良好となり、外部の整合回路において整合を取りやすくするために、これら容量素子21、22に対して直列(SAW共振子11、12に対して並列)となるように、補助インダクタ素子31、32を設けている。この時、以下のシミュレーション結果に示すように、前記通過帯域における挿入損失が0.5dB以下となるように、3GHzにおいてこれら補助インダクタ素子31、32の各々のインダクタンス値が0.5nH〜1.6nHとなるようにしている。

【0020】

このように容量素子21、22に加えて補助インダクタ素子31、32を配置した場合と、補助インダクタ素子31、32を配置せずに容量素子21、22だけを設けた場合(従来、既述の図14の構成)との各々について、ノッチフィルタの特性を評価(シミュレーション)した。図5は、通過帯域の1.1GHzにおける特性を示している。容量素子21、22に加えてインダクタ素子31、32を設けることにより、従来よりも減衰量(挿入損失)が小さく(0.5dB以下に)なっていることが分かる。この時、インダクタンス値が0.5nHから2.0nHに向かって大きくなるにつれて、前記挿入損失が小さくなっている。

【0021】

また、通過帯域の2GHzでは、図6に示すように、図5と同様に容量素子21、22に加えて補助インダクタ素子31、32を設けることにより、従来よりも挿入損失が改善され(0.5dB以下となり)、更にインダクタンス値が大きくなる程挿入損失が小さくなっていた。一方、通過帯域の3GHzでは、図7に示すように、補助インダクタ素子31、32のインダクタンス値が0.5nH〜1.6nHの場合には、従来よりも挿入損失が良好となっていた。従って、1.1GHz〜3GHzに亘る通過帯域を形成し、当該通過帯域において良好な(0.5dB以下の)挿入損失が得られるようにしようとすると、補助インダクタ素子31、32の3GHzにおけるインダクタンス値は、0.5nH〜1.6nHの範囲内に設定する必要のあることが分かる。

【0022】

図8は、1GHz付近に減衰域が形成され、1.1GHz〜3GHzに亘って良好な減衰特性となるように既述の図1のようにノッチフィルタを構成すると共に、補助インダクタ素子31、32の3GHzにおけるインダクタンス値が各々例えば1.2nHとなるように設定したノッチフィルタの特性を示している。図8に「従来」として示した既述の図14の構成のフィルタの特性と比べて、本発明では通過帯域の低域側から高域側に亘って良好な減衰特性となっていることが分かる。従って、このノッチフィルタにおいて入力ポート5に入力された電気信号を出力ポート6から取り出すと、1GHz付近の減衰域において信号が減衰されると共に、当該減衰域よりも高域側において挿入損失の小さく抑えられた特性の信号が得られる。

【0023】

上述の実施の形態によれば、SAW共振子11(12)に対して、容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を並列に接続し、通過帯域における挿入損失が0.5dB以下となるように、補助インダクタ素子31(32)のインダクタンス値を設定している。具体的には、3GHzにおける補助インダクタ素子31(32)のインダクタンス値について、各々0.5nH〜1.6nHとなるようにしている。そのため、フィルタのリターンロスが良好となり、外部の整合回路において整合を取りやすくなるので、通過帯域において良好な挿入損失のノッチフィルタを得ることができる。

【0024】

従って、家庭で用いられる特定省電力用の機器(例えばエアコンの電源の切り忘れを携帯電話に電子メールなどで通知する機器や、玩具のラジコン(ラジオコントロールカー)などの機器)で使用される帯域をノッチフィルタの減衰域に充てると共に、ノッチフィルタの通過帯域を携帯電話の通信帯域やデータ通信帯域に充てることにより、前記特定省電力用の機器の影響を抑えることのできる携帯電話などの電子機器用のノッチフィルタを得ることができる。

このような電子機器用のノッチフィルタに本発明のノッチフィルタを適用する場合には、減衰域を869MHzに設定し、通過帯域をこの減衰域よりも高域側例えば900MHz〜3GHz程度に設定しても良い。

【0025】

以下に、本発明のノッチフィルタの他の構成例について挙げる。図9は、2つのSAW共振子11、12のうち一方だけに容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を配置した例を示している。この例では、第1のSAW共振子11に容量素子21及び補助インダクタ素子31を設けている。

【0026】

図10は、図1におけるSAW共振子12と出力ポート6との間に、3つ目のSAW共振子13を直列に配置すると共に、当該SAW共振子13に容量素子23及び第3の補助インダクタ素子33からなる直列回路を並列に設けた例を示している。

【0027】

図11は、本発明をデュアルノッチフィルタに適用した構成例を示している。具体的には、2つのSAW共振子11、12が互いに直列に接続された直列回路61を入力ポート5と出力ポート6との間に互いに並列となるように2箇所に配置すると共に、各々のSAW共振子11、12について個別に容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を各々並列に接続している。この場合においてもSAW共振子11、12との間には、既述のインダクタ素子15が各々並列に接続されている。

【0028】

また、既述の各例では、補助インダクタ素子31、32について、圧電基板41上に配置したが、圧電基板41上に配置することに代えて、パッケージ基板43上に配置しても良いし、あるいは図12に示すように、パッケージ基板43の内部に配置(埋設)しても良い。図12はこのような構成におけるパッケージ基板43の一部を拡大して示しており、図12中71は容量素子21と第1の補助インダクタ素子31との間及び当該第1の補助インダクタ素子31と圧電基板41上の第1のSAW共振子11とを夫々接続するためにパッケージ基板43内に設けられたビアプラグである。

【0029】

図12の補助インダクタ素子31、32の形成方法について、以下に簡単に説明する。即ち、パッケージ基板43は、セラミックス粉末をバインダーによりシート状に成形したシート体43aと、金属粉末及びバインダーを含む配線構造(導電路46やビアプラグ71の一部)を前記シート体43aに平面的に配置した配線シート体43bと、を積層した積層セラミックスとして構成されている。そして、補助インダクタ素子31、32が既述の図1のように配置されるように前記シート体43a及び配線シート体43bを上下方向に組み合わせて積層し、その後焼結することによってパッケージ基板43が得られる。次いで、このパッケージ基板43上に、容量素子21、22、インダクタ素子15及び圧電基板41が配置される。

以上のパッケージ基板43としては、セラミックスにより構成することに代えて、樹脂により構成しても良い。

【0030】

また、容量素子21、22としては、既述の各例では電子部品42として説明したが、電子部品42に代えて、互いに平行に配置された一対の電極膜を用いても良いし、あるいはIDT電極を用いても良い。

更に、並列共振を起こす素子部としては、SAW共振子11、12に代えて、水晶共振子、圧電薄膜共振子、MEMS共振子、誘電体を用いても良い。圧電薄膜共振子としては、例えばFBAR(Film Bulk Acoustic Resonator)やSMR(Solid Mounted Resonator)などが挙げられる。誘電体を素子部として用いる場合には、マイクロストリップラインの両側に誘電体を設けた構成となる。更に前記素子部としては、コイルとコンデンサとを並列に接続した共振回路(LC共振回路)も含まれる。

【符号の説明】

【0031】

5 入力ポート

6 出力ポート

10、11、12、13 SAW共振子

15 インダクタ素子

21、22、23 容量素子

31、32、33 補助インダクタ素子

41 圧電基板

43 パッケージ基板

46 導電路

【技術分野】

【0001】

本発明は、ある周波数帯域に減衰域を設けると共に、この減衰域よりも高周波数側に通過帯域を設けたハイパス型のノッチフィルタ及びこのフィルタを備えた電子機器に関する。

【背景技術】

【0002】

SAW(surface acoustic wave:弾性表面波)を利用したフィルタの一つとして、ある周波数帯域に減衰域を設けると共に、この減衰域よりも高周波数側に通過帯域を設けたハイパス型のノッチフィルタが知られている。このフィルタは、図13に示すように、圧電基板上に互いに直列に接続した複数例えば2つのSAW共振子100を入力ポート101と出力ポート102との間に配置した構成が採られる。図13中103はインダクタ素子である。

【0003】

このフィルタにおいて、前記通過帯域を例えば800MHz以上もの高周波数帯域に設定しようとすると、当該高周波数帯域ではフィルタの挿入損失が劣化してしまう。即ち、このような高周波数帯域では、圧電基板上を伝搬する弾性表面波のうち一部が圧電基板の内部に向かって伝搬するバルク波などに変換されてしまうので、このバルク波の分だけエネルギー損失が起こってしまう。従って、SAW共振子100は、前記高周波数帯域では見かけ上Q値の悪い(小さい)コンデンサとなる。

【0004】

そこで、図14に示すように、SAW共振子100が既述の高周波数帯域において見かけ上Q値の良好な(高い)コンデンサとなるように、前記SAW共振子100に対して容量素子105を並列に接続する手法を採る場合もある。この場合には、通過帯域における挿入損失が改善されるが、前記挿入損失を更に低減させる技術が求められている。

特許文献1には、高域側減衰帯域の減衰極周波数を変更するために、付加インダクタ561及び付加キャパシタ562を直列腕共振器510に対して各々並列に接続したバンドパスフィルタについて記載されているが、既述の課題については検討されていない。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−223147

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明はこのような事情に鑑みてなされたものであり、その目的は、減衰域よりも高周波数帯域側に通過帯域を設定したハイパス型のノッチフィルタにおいて、前記通過帯域における挿入損失を抑えることのできるノッチフィルタ及びこのフィルタを備えた電子機器を提供することにある。

【課題を解決するための手段】

【0007】

本発明のノッチフィルタは、

減衰域よりも高周波数側の900MHz以上の周波数帯域に通過帯域を設けたハイパス型のノッチフィルタにおいて、

入力信号が入力される入力ポートと、

出力信号が取り出される出力ポートと、

前記減衰域を形成するために、前記入力ポート及び前記出力ポートの間に直列に配置され、この減衰域に対応する周波数で各々並列共振を起こす2つのSAW共振子からなる直列回路と、

これらSAW共振子間における接続点とアースとの間に接続されたインダクタ素子と、

前記SAW共振子のうち少なくとも一方のSAW共振子に設けられ、この一方のSAW共振子に対して並列となるように配置された容量素子及び補助インダクタ素子からなる直列回路と、を備え、

前記補助インダクタ素子のインダクタンス値は、前記通過帯域における挿入損失が0.5dB以下となるように構成されていることを特徴とする。

【0008】

前記容量素子及び前記補助インダクタ素子は、前記SAW共振子の各々に設けられていても良い。

前記SAW共振子の各々は、圧電基板上に配置され、

前記インダクタ素子は、前記圧電基板上に引き回された導電路であっても良い。

前記入力ポート及び前記出力ポートが配置される共通の基板を備え、

前記インダクタ素子は、前記基板上あるいは前記基板の内部に配置された導電路であっても良い。

また、本発明の電子機器は、

以上説明したノッチフィルタを備えたことを特徴とする。

【発明の効果】

【0009】

本発明は、ハイパス型のノッチフィルタにおいて、減衰域において各々並列共振を起こす2つのSAW共振子の直列回路を入力ポートと出力ポートとの間に直列に配置すると共に、これらSAW共振子の少なくとも一方のSAW共振子について、容量素子及び補助インダクタ素子からなる直列回路を並列となるように設けている。そして、通過帯域における挿入損失が0.5dB以下となるように補助インダクタ素子のインダクタンス値を設定している。そのため、フィルタのリターンロスが良好となり、外部の整合回路において整合を取りやすくなるので、前記通過帯域において良好な挿入損失のノッチフィルタを得ることができる。

【図面の簡単な説明】

【0010】

【図1】本発明のノッチフィルタの一例を示す回路図である。

【図2】前記フィルタの概観を模式的に示す斜視図である。

【図3】前記フィルタの概観を示す縦断面図である。

【図4】前記フィルタの圧電基板上のSAW共振子などの配置レイアウトを示す平面図である。

【図5】前記フィルタの周波数特性を示す特性図である。

【図6】前記フィルタの周波数特性を示す特性図である。

【図7】前記フィルタの周波数特性を示す特性図である。

【図8】前記フィルタの周波数特性を示す特性図である。

【図9】前記フィルタの他の例を示す電気回路図である。

【図10】前記フィルタの別の例を示す電気回路図である。

【図11】前記フィルタの更に別の例を示す電気回路図である。

【図12】前記フィルタの更にまた別の例の一部を示すパッケージ基板の縦断面図である。

【図13】従来のノッチフィルタを示す電気回路図である。

【図14】従来のノッチフィルタを示す電気回路図である。

【発明を実施するための形態】

【0011】

本発明の実施の形態の一例であるノッチフィルタについて、図1〜図4を参照して説明する。先ず、フィルタの回路構成について説明する。このフィルタは、一部の周波数帯域この例では1GHz±2MHzを阻止域に設定すると共に、この阻止域よりも高域側(高周波数側)の1.1GHz〜3GHzまでを通過帯域としたハイパス型のノッチフィルタである。具体的には、このノッチフィルタは、図1に示すように、2つのSAW(surface acoustic wave:弾性表面波)共振子10からなる素子部を互いに直列に接続すると共に、これらSAW共振子10、10を入力ポート5と出力ポート6との間に直列に配置している。SAW共振子10、10の各々の反共振点(反共振周波数)は、前記阻止域に対応する周波数に設定されている。これらSAW共振子10、10の間には、はしご型回路を構成するためのインダクタ素子15が並列に接続されており、このインダクタ素子15は接地されている。尚、図1ではSAW共振子10について簡略化している。

【0012】

そして、前記2つのSAW共振子10、10のうち入力ポート5側のSAW共振子10及び出力ポート6側のSAW共振子10を夫々第1のSAW共振子11及び第2のSAW共振子12と呼ぶと、第1のSAW共振子11には、第1の容量素子21と第1の補助インダクタ素子31とからなる直列回路が並列に接続されている。即ち、前記直列回路の一端側が入力ポート5と第1のSAW共振子11との間の接続点に接続され、当該直列回路の他端側が2つのSAW共振子11、12間の接続点に接続されている。また、第2のSAW共振子12についても、第1のSAW共振子11と同様に第2の容量素子22と第2の補助インダクタ素子32とからなる直列回路が並列に接続されている。各々の容量素子21、22の容量値は例えば各々2pFに設定されている。また、各々のインダクタ素子31、32のインダクタンス値は、例えば3GHzにおいて各々0.5nH〜1.6nHこの例では1.2nHとなるように設定されている。これら容量素子21、22及び補助インダクタ素子31、32を設けた理由については、後で詳述する。

【0013】

次に、既述の図1の電気回路に対応する各部の構成及びノッチフィルタの概観について説明する。このフィルタは、図2及び図3に示すように、例えば水晶などからなる圧電基板41と、既述の容量素子21、22及びインダクタ素子15に夫々対応する電子部品42と、これら圧電基板41及び電子部品42が配置される共通の例えばアルミナ(Al2O3)などのセラミックスからなるパッケージ基板43と、を備えている。そして、これら電子部品42と圧電基板41(詳しくは圧電基板41の下方側に配置された後述のバンプ47)とは、パッケージ基板43上を引き回された引き回し電極44により、既述の図1の電気回路となるように互いに接続されている。図2及び図3中45は、パッケージ基板43の表面を覆う例えば樹脂などからなる封止材である。尚、図2及び図3では、夫々の電子部品42について、対応する容量素子21、22及びインダクタ素子15の符号を括弧書きで併記している。また、図3は、図2におけるA−A線にてパッケージ基板43を切断した縦断面図を示しており、引き回し電極44については描画を省略している。

【0014】

圧電基板41上には、図4に示すように、既述のSAW共振子11、12が当該圧電基板41の長手方向(X方向)に互いに離間するように配置されている。各々のSAW共振子11、12は、複数本の電極指51及び一対のバスバー52を備えたIDT(インターデジタルトランスデューサ)電極53と、このIDT電極53を弾性表面波(以後「弾性波」と言う)の伝搬方向(Y方向)における一方側及び他方側から挟み込むように各々配置された反射器54、54を備えている。以下において、第1のSAW共振子11側及び第2のSAW共振子12側を夫々「手前側」及び「奥側」と呼ぶ。図4中55は反射器電極指、56は反射器バスバーである。尚、図4は図1における圧電基板41を下方側(パッケージ基板43側)から見た様子を示している。

【0015】

ここで、既述の補助インダクタ素子31、32は、圧電基板41上に引き回された導電路46により構成されている。即ち、弾性波の伝搬方向における一方側及び他方側を夫々右方向及び左方向と呼ぶと、第1のSAW共振子11の左側には、第1の補助インダクタ素子31をなす導電路46が圧電基板41上を手前側から奥側に向かって例えば蛇腹状(メアンダ状)に伸びるように配置されている。また、第2のSAW共振子12の左側には、圧電基板41上を奥側から手前側に向かって同様に蛇腹状に伸びるように配置された導電路46が第2の補助インダクタ素子32として配置されている。これら補助インダクタ素子31、32は、夫々既述のインダクタンス値となるように、導電路46の厚み寸法、幅寸法及び長さ寸法が調整されている。

【0016】

そして、これらSAW共振子11、12及び補助インダクタ素子31、32は、パッケージ基板43上に配置された金属体例えば半田などからなる既述のバンプ47によって、パッケージ基板43上における引き回し電極44あるいはビアプラグ48に電気的に接続されている。具体的には、圧電基板41上には5つのバンプ47が配置されており、これらバンプ47の夫々に「a」〜「e」の添え字を付すと、第1のSAW共振子11の手前側のバスバー52はバンプ47aに接続されている。

【0017】

また、第1の補助インダクタ素子31の手前側の端部は、バンプ47bに接続されている。第1のSAW共振子11の奥側のバスバー52、第2のSAW共振子12の手前側のバスバー52、第1の補助インダクタ素子31の奥側の端部及び第2の補助インダクタ素子32の手前側の端部は、共通のバンプ47cに各々接続されている。第2のSAW共振子12の奥側のバスバー52はバンプ47dに接続され、第2の補助インダクタ素子32の奥側の端部はバンプ47eに接続されている。尚、これらバンプ47a〜47eは、実際にはパッケージ基板43側に設けられていて、圧電基板41を当該パッケージ基板43側に当接させることにより図4の状態となるが、図示を簡略化するために圧電基板41側に配置されているものとして説明している。

【0018】

これらバンプ47a〜47eのうちバンプ47a及びバンプ47dの下方側におけるパッケージ基板43には、当該パッケージ基板43を上下に貫通するように形成された電極であるビアプラグ48、48が各々形成されている。各々のビアプラグ48、48の下面には、電極膜からなる接続用端子部49が各々形成されており、バンプ47aに接続される接続用端子部49と、バンプ47dに接続される接続用端子部49とは、夫々入力ポート5及び出力ポート6をなしている。こうして圧電基板41におけるSAW共振子11、12及びインダクタ素子31、32の配置された面をパッケージ基板43に当接させることにより、バンプ47a〜47eを介して圧電基板41がパッケージ基板43上の引き回し電極44及びビアプラグ48に電気的に接続されると共に固定される。尚、バンプ47cの下方側におけるパッケージ基板43にもビアプラグ48が設けられていて、このビアプラグ48の下面側に配置された接続用端子部49を介してインダクタ素子15が接地されているが、ここでは図示を省略している。また、図4には、パッケージ基板43上に配置されるインダクタ素子15や容量素子21、22についても模式的に圧電基板41の外側に描画している。

【0019】

ここで、SAW共振子11(12)に容量素子21(22)及び補助インダクタ素子31(32)を並列に接続した理由について説明する。既述のように、このノッチフィルタでは通過帯域を1.1GHz以上もの高周波数帯域に設定しているので、このような高周波数帯域ではフィルタの挿入損失が劣化しやすい。即ち、このような高周波数帯域では、圧電基板41上を伝搬する弾性波のうち一部が圧電基板41の内部に向かって伝搬するバルク波などに変換される場合があり、その場合にはバルク波の分だけエネルギー損失が起こってしまう。従って、SAW共振子11(12)は、前記高周波数帯域では見かけ上Q値の悪い(小さい)コンデンサとなる。そのため、各々のSAW共振子11(12)が見かけ上Q値の良好な(高い)コンデンサとなるように、容量素子21(22)を並列に接続している。具体的には、これら容量素子21、22について、各々の容量値が1〜10pFこの例では2pFに設定している。そして、各々のSAW共振子11、12においてリターンロスが良好となり、外部の整合回路において整合を取りやすくするために、これら容量素子21、22に対して直列(SAW共振子11、12に対して並列)となるように、補助インダクタ素子31、32を設けている。この時、以下のシミュレーション結果に示すように、前記通過帯域における挿入損失が0.5dB以下となるように、3GHzにおいてこれら補助インダクタ素子31、32の各々のインダクタンス値が0.5nH〜1.6nHとなるようにしている。

【0020】

このように容量素子21、22に加えて補助インダクタ素子31、32を配置した場合と、補助インダクタ素子31、32を配置せずに容量素子21、22だけを設けた場合(従来、既述の図14の構成)との各々について、ノッチフィルタの特性を評価(シミュレーション)した。図5は、通過帯域の1.1GHzにおける特性を示している。容量素子21、22に加えてインダクタ素子31、32を設けることにより、従来よりも減衰量(挿入損失)が小さく(0.5dB以下に)なっていることが分かる。この時、インダクタンス値が0.5nHから2.0nHに向かって大きくなるにつれて、前記挿入損失が小さくなっている。

【0021】

また、通過帯域の2GHzでは、図6に示すように、図5と同様に容量素子21、22に加えて補助インダクタ素子31、32を設けることにより、従来よりも挿入損失が改善され(0.5dB以下となり)、更にインダクタンス値が大きくなる程挿入損失が小さくなっていた。一方、通過帯域の3GHzでは、図7に示すように、補助インダクタ素子31、32のインダクタンス値が0.5nH〜1.6nHの場合には、従来よりも挿入損失が良好となっていた。従って、1.1GHz〜3GHzに亘る通過帯域を形成し、当該通過帯域において良好な(0.5dB以下の)挿入損失が得られるようにしようとすると、補助インダクタ素子31、32の3GHzにおけるインダクタンス値は、0.5nH〜1.6nHの範囲内に設定する必要のあることが分かる。

【0022】

図8は、1GHz付近に減衰域が形成され、1.1GHz〜3GHzに亘って良好な減衰特性となるように既述の図1のようにノッチフィルタを構成すると共に、補助インダクタ素子31、32の3GHzにおけるインダクタンス値が各々例えば1.2nHとなるように設定したノッチフィルタの特性を示している。図8に「従来」として示した既述の図14の構成のフィルタの特性と比べて、本発明では通過帯域の低域側から高域側に亘って良好な減衰特性となっていることが分かる。従って、このノッチフィルタにおいて入力ポート5に入力された電気信号を出力ポート6から取り出すと、1GHz付近の減衰域において信号が減衰されると共に、当該減衰域よりも高域側において挿入損失の小さく抑えられた特性の信号が得られる。

【0023】

上述の実施の形態によれば、SAW共振子11(12)に対して、容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を並列に接続し、通過帯域における挿入損失が0.5dB以下となるように、補助インダクタ素子31(32)のインダクタンス値を設定している。具体的には、3GHzにおける補助インダクタ素子31(32)のインダクタンス値について、各々0.5nH〜1.6nHとなるようにしている。そのため、フィルタのリターンロスが良好となり、外部の整合回路において整合を取りやすくなるので、通過帯域において良好な挿入損失のノッチフィルタを得ることができる。

【0024】

従って、家庭で用いられる特定省電力用の機器(例えばエアコンの電源の切り忘れを携帯電話に電子メールなどで通知する機器や、玩具のラジコン(ラジオコントロールカー)などの機器)で使用される帯域をノッチフィルタの減衰域に充てると共に、ノッチフィルタの通過帯域を携帯電話の通信帯域やデータ通信帯域に充てることにより、前記特定省電力用の機器の影響を抑えることのできる携帯電話などの電子機器用のノッチフィルタを得ることができる。

このような電子機器用のノッチフィルタに本発明のノッチフィルタを適用する場合には、減衰域を869MHzに設定し、通過帯域をこの減衰域よりも高域側例えば900MHz〜3GHz程度に設定しても良い。

【0025】

以下に、本発明のノッチフィルタの他の構成例について挙げる。図9は、2つのSAW共振子11、12のうち一方だけに容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を配置した例を示している。この例では、第1のSAW共振子11に容量素子21及び補助インダクタ素子31を設けている。

【0026】

図10は、図1におけるSAW共振子12と出力ポート6との間に、3つ目のSAW共振子13を直列に配置すると共に、当該SAW共振子13に容量素子23及び第3の補助インダクタ素子33からなる直列回路を並列に設けた例を示している。

【0027】

図11は、本発明をデュアルノッチフィルタに適用した構成例を示している。具体的には、2つのSAW共振子11、12が互いに直列に接続された直列回路61を入力ポート5と出力ポート6との間に互いに並列となるように2箇所に配置すると共に、各々のSAW共振子11、12について個別に容量素子21(22)及び補助インダクタ素子31(32)からなる直列回路を各々並列に接続している。この場合においてもSAW共振子11、12との間には、既述のインダクタ素子15が各々並列に接続されている。

【0028】

また、既述の各例では、補助インダクタ素子31、32について、圧電基板41上に配置したが、圧電基板41上に配置することに代えて、パッケージ基板43上に配置しても良いし、あるいは図12に示すように、パッケージ基板43の内部に配置(埋設)しても良い。図12はこのような構成におけるパッケージ基板43の一部を拡大して示しており、図12中71は容量素子21と第1の補助インダクタ素子31との間及び当該第1の補助インダクタ素子31と圧電基板41上の第1のSAW共振子11とを夫々接続するためにパッケージ基板43内に設けられたビアプラグである。

【0029】

図12の補助インダクタ素子31、32の形成方法について、以下に簡単に説明する。即ち、パッケージ基板43は、セラミックス粉末をバインダーによりシート状に成形したシート体43aと、金属粉末及びバインダーを含む配線構造(導電路46やビアプラグ71の一部)を前記シート体43aに平面的に配置した配線シート体43bと、を積層した積層セラミックスとして構成されている。そして、補助インダクタ素子31、32が既述の図1のように配置されるように前記シート体43a及び配線シート体43bを上下方向に組み合わせて積層し、その後焼結することによってパッケージ基板43が得られる。次いで、このパッケージ基板43上に、容量素子21、22、インダクタ素子15及び圧電基板41が配置される。

以上のパッケージ基板43としては、セラミックスにより構成することに代えて、樹脂により構成しても良い。

【0030】

また、容量素子21、22としては、既述の各例では電子部品42として説明したが、電子部品42に代えて、互いに平行に配置された一対の電極膜を用いても良いし、あるいはIDT電極を用いても良い。

更に、並列共振を起こす素子部としては、SAW共振子11、12に代えて、水晶共振子、圧電薄膜共振子、MEMS共振子、誘電体を用いても良い。圧電薄膜共振子としては、例えばFBAR(Film Bulk Acoustic Resonator)やSMR(Solid Mounted Resonator)などが挙げられる。誘電体を素子部として用いる場合には、マイクロストリップラインの両側に誘電体を設けた構成となる。更に前記素子部としては、コイルとコンデンサとを並列に接続した共振回路(LC共振回路)も含まれる。

【符号の説明】

【0031】

5 入力ポート

6 出力ポート

10、11、12、13 SAW共振子

15 インダクタ素子

21、22、23 容量素子

31、32、33 補助インダクタ素子

41 圧電基板

43 パッケージ基板

46 導電路

【特許請求の範囲】

【請求項1】

減衰域よりも高周波数側の900MHz以上の周波数帯域に通過帯域を設けたハイパス型のノッチフィルタにおいて、

入力信号が入力される入力ポートと、

出力信号が取り出される出力ポートと、

前記減衰域を形成するために、前記入力ポート及び前記出力ポートの間に直列に配置され、この減衰域に対応する周波数で各々並列共振を起こす2つのSAW共振子からなる直列回路と、

これらSAW共振子間における接続点とアースとの間に接続されたインダクタ素子と、

前記SAW共振子のうち少なくとも一方のSAW共振子に設けられ、この一方のSAW共振子に対して並列となるように配置された容量素子及び補助インダクタ素子からなる直列回路と、を備え、

前記補助インダクタ素子のインダクタンス値は、前記通過帯域における挿入損失が0.5dB以下となるように構成されていることを特徴とするノッチフィルタ。

【請求項2】

前記容量素子及び前記補助インダクタ素子は、前記SAW共振子の各々に設けられていることを特徴とする請求項1に記載のノッチフィルタ。

【請求項3】

前記SAW共振子の各々は、圧電基板上に配置され、

前記インダクタ素子は、前記圧電基板上に引き回された導電路であることを特徴とする請求項1または2に記載のノッチフィルタ。

【請求項4】

前記入力ポート及び前記出力ポートが配置される共通の基板を備え、

前記インダクタ素子は、前記基板上あるいは前記基板の内部に配置された導電路であることを特徴とする請求項1または2に記載のノッチフィルタ。

【請求項5】

請求項1ないし4のいずれか一つに記載のノッチフィルタを備えたことを特徴とする電子機器。

【請求項1】

減衰域よりも高周波数側の900MHz以上の周波数帯域に通過帯域を設けたハイパス型のノッチフィルタにおいて、

入力信号が入力される入力ポートと、

出力信号が取り出される出力ポートと、

前記減衰域を形成するために、前記入力ポート及び前記出力ポートの間に直列に配置され、この減衰域に対応する周波数で各々並列共振を起こす2つのSAW共振子からなる直列回路と、

これらSAW共振子間における接続点とアースとの間に接続されたインダクタ素子と、

前記SAW共振子のうち少なくとも一方のSAW共振子に設けられ、この一方のSAW共振子に対して並列となるように配置された容量素子及び補助インダクタ素子からなる直列回路と、を備え、

前記補助インダクタ素子のインダクタンス値は、前記通過帯域における挿入損失が0.5dB以下となるように構成されていることを特徴とするノッチフィルタ。

【請求項2】

前記容量素子及び前記補助インダクタ素子は、前記SAW共振子の各々に設けられていることを特徴とする請求項1に記載のノッチフィルタ。

【請求項3】

前記SAW共振子の各々は、圧電基板上に配置され、

前記インダクタ素子は、前記圧電基板上に引き回された導電路であることを特徴とする請求項1または2に記載のノッチフィルタ。

【請求項4】

前記入力ポート及び前記出力ポートが配置される共通の基板を備え、

前記インダクタ素子は、前記基板上あるいは前記基板の内部に配置された導電路であることを特徴とする請求項1または2に記載のノッチフィルタ。

【請求項5】

請求項1ないし4のいずれか一つに記載のノッチフィルタを備えたことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2012−257050(P2012−257050A)

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願番号】特願2011−128452(P2011−128452)

【出願日】平成23年6月8日(2011.6.8)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

【公開日】平成24年12月27日(2012.12.27)

【国際特許分類】

【出願日】平成23年6月8日(2011.6.8)

【出願人】(000232483)日本電波工業株式会社 (1,148)

【Fターム(参考)】

[ Back to top ]