ハイブリッドパワーデバイス

【課題】ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスにおいて、共振の発生を抑制しつつ、スイッチング損失を低減できるようにする。

【解決手段】ハイブリッドパワーデバイスを構成するノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とは、各FET2、4のソース及びドレインを互いに接続することによりカスコード接続されており、SiC−JFET2のゲートとSi−MOSFET4のソースはスイッチング速度調整用の抵抗10を介して接続されている。そして、この抵抗10にコンデンサ12を並列接続することにより、ハイブリッドパワーデバイスのスイッチング期間中の前半部分ではスイッチング速度を速くしてスイッチング損失を低減し、後半部分ではスイッチング速度を遅くして発振の発生を防止する。

【解決手段】ハイブリッドパワーデバイスを構成するノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とは、各FET2、4のソース及びドレインを互いに接続することによりカスコード接続されており、SiC−JFET2のゲートとSi−MOSFET4のソースはスイッチング速度調整用の抵抗10を介して接続されている。そして、この抵抗10にコンデンサ12を並列接続することにより、ハイブリッドパワーデバイスのスイッチング期間中の前半部分ではスイッチング速度を速くしてスイッチング損失を低減し、後半部分ではスイッチング速度を遅くして発振の発生を防止する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスに関する。

【背景技術】

【0002】

近年、インバータ、DC−DCコンバータ、スイッチング電源等のパワーエレクトロニクス機器にて使用するのに好適な高耐圧のパワーデバイスとして、SiC(シリコンカーバイト)からなるJFET(接合型電界効果トランジスタ)が注目されている。

【0003】

ところで、SiC−JFETは、ゲート酸化膜がないため、SiC−MOSFETに比べて製造し易いものの、一般的にノーマリオン型であるので、自動車等の信頼性を必要とするパワーエレクトロニクス機器には使い難いという問題があった。

【0004】

このため、SiC−JFETは、Si(シリコン)からなるノーマリオフ型の低耐圧MOSFETとカスコード接続することで、全体としてノーマリオフ型のスイッチング素子として動作する、ハイブリッドパワーデバイスとして構成することが考えられている。

【0005】

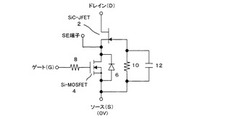

しかし、図8に示すように、ノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とをカスコード接続したハイブリッドパワーデバイスにおいては、製造時に形成される寄生成分(図8に示す容量C1〜C3、インダクタンスL等)により、共振が発生し易いという問題がある。また、低耐圧Si−MOSFETに過渡的に高電圧がかかるという問題もある。

【0006】

そこで、この問題を防止するため、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に抵抗10を挿入することで、スイッチング速度を遅くすることが提案されている(例えば、特許文献1等、参照)。

【0007】

なお、図8において、Si−MOSFET4のドレインソース間に接続されたダイオード6は、Si−MOSFET4の構造上できる寄生ダイオードであり、Si−MOSFET4のゲートに接続された抵抗8は入力抵抗である。

【0008】

また、図8に示すハイブリッドパワーデバイスにおいて、SiC−JFET2、Si−MOSFET4にはnチャネルのものが使用されており、これらをカスコード接続する接続点(SiC−JFET2のソースとSi−MOSFET4のドレインとの接続点)には、センシング用のSE端子が設けられている。

【0009】

そして、このハイブリッドパワーデバイスにおいては、SiC−JFET2のドレインが、ハイブリッドパワーデバイスのドレイン(D)、Si−MOSFET4のソースが、ハイブリッドパワーデバイスのソース(S)、Si−MOSFET4のゲートが、ハイブリッドパワーデバイスのゲート(G)となる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】US 20020153938A1

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、上記提案のハイブリッドパワーデバイスのように、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に抵抗10を挿入した場合、スイッチング速度を遅くして、Si−MOSFET4に過渡的に高電圧が印加されたり、共振が発生したりするのを防止できるが、スイッチング速度の低下によって、ハイブリッドパワーデバイスのターンオン時等に生じるスイッチング損失が増加するという問題があった。

【0012】

つまり、図8に示したハイブリッドパワーデバイスにおいて、例えば、ターンオン時には、図9に示すように、抵抗10を介して、2段階(A、B)で放電を行うことになる。

具体的には、1段目(A)では、ゲート電圧が印加されて、Si−MOSFET4がオンし、SE端子電圧が下がることにより、SiC−JFET2のゲート−ソース間容量C2の放電Q1を行う。また、2段目(B)では、SiC−JFET2のゲート−ドレイン間容量C1の放電Q2を行う。

【0013】

そして、1段目(A)では、スイッチングを高速化して、その期間(時点t1−t2間)を短くすれば、スイッチング損失を低減できる。また、このときの抵抗10の両端電圧(SiC−JFET2のゲート電圧Vg_jfet)は、マイナスに振れるが、できるだけ高い電位(換言すればマイナスの振れ幅が小さい電位)であるほうが、スイッチング速度が高速になり望ましい。

【0014】

一方、2段目(B)では、共振が起こりやすいので、スイッチング速度を遅くするほうが、安定した動作を実現できる。また、このときの抵抗10の両端電圧(SiC−JFET2のゲート電圧Vg_jfet)は、マイナスに振れるが、できるだけ低い電位であるほうが、スイッチング速度が遅くなり、結果的に共振を抑え易い。

【0015】

しかし、上記提案の技術では、単に抵抗10を設けてスイッチング速度を抑えるだけであるので、2段目(B)で共振が発生するのを防止することはできても、1段目(A)でスイッチング損失を増加させてしまうのである。

【0016】

本発明は、こうした問題に鑑みなされたものであり、ノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とをカスコード接続してなるハイブリッドパワーデバイスにおいて、共振の発生を抑制しつつ、スイッチング損失を低減できるようにすることを目的とする。

【課題を解決するための手段】

【0017】

かかる目的を達成するためになされた請求項1に記載のハイブリッドパワーデバイスは、図8に示した従来装置と同様、ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続することにより構成されている。

【0018】

そして、SiC−JFETのゲートには、当該ハイブリッドパワーデバイスのスイッチング期間中にSiC−JFETのゲート電流及びゲート電圧を変化させて、スイッチング期間の前半ではスイッチング速度が速く、スイッチング期間の後半ではスイッチング速度が遅くなるよう、当該ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段が設けられている。

【0019】

このため、本発明のハイブリッドパワーデバイスによれば、図9に示したスイッチング期間の1段目(A)では、スイッチング速度を速くすることで、スイッチング損失を低減し、図9に示したスイッチング期間の2段目(B)では、スイッチング速度を遅くして、共振が発生するのを防止する、といったことができるようになる。

【0020】

ここで、制御手段は、例えば、請求項2に記載のように、SiC−JFETのゲートとSi−MOSFETのソースとの間に設けられたスイッチング速度調整用の抵抗(速度調整抵抗)と、SiC−JFETのゲートに接続されたコンデンサとからなるアナログ回路にて構成することができる。

【0021】

つまり、速度調整抵抗は、図8に示した抵抗10と同じであり、制御手段には、この速度調整抵抗とは別にコンデンサを設けるのである。

そして、このようにすれば、図10(b)に例示するように、当該ハイブリッドパワーデバイスのターンオン時には、まずコンデンサに大電流が流れ、コンデンサに電荷が蓄積されると、速度調整抵抗に電流が流れ、最終的には、コンデンサに蓄積された電荷が速度調整抵抗を介して放電されることになる。

【0022】

つまり、図8に示した従来装置のように速度調整抵抗を設けただけでは、図10(a)に示すように、当該ハイブリッドパワーデバイスのターンオン時に、速度調整抵抗の抵抗値に対応した電流が流れるだけであるが、請求項2に記載のように、制御手段を速度調整抵抗とコンデンサとで構成すれば、スイッチング期間の前半部分でSiC−JFETのゲートに大電流を流して、スイッチング速度を速くし、スイッチング期間の後半部分ではSiC−JFETのゲート電流を減少させ、更にスイッチング終了後もゲート電流を流して、スイッチング速度を遅くすることができる。

【0023】

ここで、上記コンデンサは、請求項3に記載のように、速度調整抵抗に並列に接続するようにしてもよく、或いは、請求項4に記載のように、コンデンサにダイオードと抵抗との並列回路を直列に接続し、その直列回路を、速度調整回路に並列に接続するようにしてもよい。

【0024】

そして、コンデンサに対し、ダイオードと抵抗との並列回路を直列接続した場合には、図9に示したスイッチング期間の1段目(A)では、ダイオードを介してコンデンサに電流を流すことで、スイッチング速度を速くし、図9に示したスイッチング期間の2段目(B)では、コンデンサと抵抗との直列回路にてコンデンサに蓄積された電荷を放電することになるので、請求項3に記載のものに比べて、スイッチング速度を更に遅くし、共振の発生を抑えることができる。

【0025】

またコンデンサは、速度調整抵抗に対し並列接続するのではなく、請求項5に記載のように、コンデンサの一端をSiC−JFETのゲートに接続し、他端を、Si−MOSFETのゲートに接続するようにしてもよい。

【0026】

そして、このようにすれば、SiC−JFETのゲートに、Si−MOSFETのゲートに入力された駆動電圧を直接印加することができるので、Si−MOSFETのオン・オフ動作に対するSiC−JFETの動作遅れを少なくして、スイッチング速度を速くして、Si−MOSFETへの過渡的な電圧印加も防止することができる。

【0027】

なお、請求項3又は請求項5に記載のハイブリッドパワーデバイスのように、コンデンサを速度調整抵抗に並列接続するか、コンデンサを各FETのゲート間に接続する場合には、請求項6に記載のように、コンデンサに対し、速度調整抵抗よりも抵抗値が小さい抵抗を直列に接続するようにしてもよい。

【0028】

そして、このようにすれば、図10(c)に示すように、コンデンサに流れる電流(特にピーク電流)を抵抗とコンデンサとの時定数にて調整することができるようになり、延いては、スイッチング速度の調整を容易に行うことができるようになる。

【図面の簡単な説明】

【0029】

【図1】第1実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図2】第1実施形態のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図3】第2実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図4】第2実施形態のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図5】第3実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図6】第4実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図7】第5実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図8】従来のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図9】従来のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図10】本発明のハイブリッドパワーデバイスにおける電流波形を従来技術と比較して説明する説明図である。

【発明を実施するための形態】

【0030】

以下に本発明の実施形態を図面と共に説明する。

[第1実施形態]

図1に示すように、第1実施形態のハイブリッドパワーデバイスは、ノーマリオン型のSiC−JFET2と、ノーマリオフ型のSi−MOSFET4とを備え、SiC−JFET2のソースとSi−MOSFET4とをカスコード接続したものであり、基本的には、図8に示した従来ものと同様に構成されている。

【0031】

そして、図8に示したものと異なる点は、ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段として、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に挿入された抵抗(速度調整抵抗)10に加えて、この速度調整抵抗10に並列接続されたコンデンサ12とを備えた点であり、他の構成は、図8に示したものと全く同じである。

【0032】

このように構成された本実施形態のハイブリッドパワーデバイスにおいては、速度調整抵抗10に対しコンデンサ12が並列に接続されているので、このコンデンサ12により、スイッチング期間中にスイッチング速度を制御することができる。

【0033】

以下、この制御について説明する。

図2は、本実施形態のハイブリッドパワーデバイスのターンオン時の、ドレイン−ソース間電圧(DS間電圧)、ドレイン電流(DS間電流)、SE端子電圧、コンデンサ12に流れるコンデンサ電流、速度調整抵抗10に流れる速度調整抵抗電流、SiC−JFET2のゲート電圧及びゲート電流を表すタイムチャートである。

【0034】

なお、図2において、コンデンサ電流及び速度調整抵抗電流は、抵抗10或いはコンデンサ12から、ハイブリッドパワーデバイスのソース(S)側に流れる方向を正(+)、これとは逆方向を負(−)として記載されている。

【0035】

図2に示すように、本実施形態のハイブリッドパワーデバイスにおいても、従来のものと同様、2段階で放電を行い、1段目(A)では、SE端子電圧が下がることにより、SiC−JFET2のゲート−ソース間容量放電を行い、2段目(B)では、SiC−JFET2のゲート−ドレイン間容量の放電を行う。

【0036】

そして、1段目(A)の放電時には、コンデンサ12と速度調整抵抗10の両方に電流が流れる。また、初期状態では、コンデンサ12に電荷が溜まっていないので、速度調整抵抗10よりもコンデンサ12側に電流が多く流れるが、徐々にコンデンサ12に電流が流れて電荷が溜まり始めると(換言すればコンデンサ12の電圧が大きくなり始めると)、コンデンサ12に流れる電流が減り、速度調整抵抗10に流れる電流が増加し始める。

【0037】

SiC−JFET2のゲート電流は、『ゲート電流=コンデンサ電流+速度調整抵抗電流』と表すことができ、SiC−JFET2のゲート電流の電荷量は、SiC−JFET2のゲートソース間容量を放電する電荷量(Q1)である。

【0038】

このため、1段目(A)では、コンデンサ12が効果的に機能し、図2の(a)から明らかなように、SiC−JFET2のゲート電圧が下がり難く、スイッチング速度を高速化できる。なお、1段目(A)では、高速化に伴い、SiC−JFET2のゲート電流は増加する(図2(c)参照)。

【0039】

一方、2段目(B)では、コンデンサ12に電荷が溜まっている(換言すればSiC−JFET2のゲート電圧Vg_jfetは「0」ではない)ため、コンデンサ12に電流が流れ難い状態になっている。従って、電流は速度調整抵抗10に多く流れることになり、SiC−JFET2のゲート電圧が低下し易い。そのため、2段目では、コンデンサ12によるスピードアップ機能が弱まり、SiC−JFET2のゲート電圧が下がることから、従来と同様、スイッチング速度を遅くすることができる(図2(b)参照)。

[第2実施形態]

図3に示すように、第2実施形態のハイブリッドパワーデバイスは、コンデンサ12に対し、直列に、ダイオード14と抵抗16とを並列接続した回路を接続したものであり、他の構成は、第1実施形態のハイブリッドパワーデバイスと同一である。なお、ダイオード14は、コンデンサ電流の負(−)方向を順方向として接続されている。また、抵抗16の抵抗値は、速度調整抵抗10の抵抗値よりも小さい値に設定されている。

【0040】

このように構成された本実施形態のハイブリッドパワーデバイスにおいては、図4に示すように、ターンオン時、1段目(A)の前半(時点t1−t1′間)では、主にダイオード14を通じて電流を流し、1段目(A)の後半部分(時点t1′−t2′間)で、コンデンサ12に充電し、その後(時点t2′後)放電を開始する。

【0041】

そして、放電時には、ダイオード14は逆導通しないので、抵抗16の抵抗値を大きめに設定することで電流の流れを妨げることができる。つまり、コンデンサ12に溜まった電荷(換言すればコンデンサ電圧)を保持することができる。

【0042】

従って、2段目(B)では、コンデンサ12に電荷がすでに溜まっているので、電流が流れ難くなり、SiC−JFET2のゲート電流のうち、速度調整抵抗10を使って流れる量が多くなる。このため、本実施形態によれば、第1実施形態に比べ、SiC−JFET2のゲート電圧が低下し、スイッチング速度を弱める効果を高めることができる。

[第3実施形態]

図5に示すように、第3実施形態のハイブリッドパワーデバイスは、第1実施形態に記載のようにコンデンサ12を速度調整抵抗10に並列接続するのではなく、コンデンサ12を、SiC−JFET2のゲートとSi−MOSFET4のゲートとの間に接続したものであり、他の構成は第1実施形態に記載のものと同じである。

【0043】

そして、本実施形態のハイブリッドパワーデバイスによれば、コンデンサ12をSi−MOSFET4の駆動回路に直接接続されることになるので、Si−MOSFET4のオン・オフ動作に対するSiC−JFET2の遅れが少なくなり、スイッチング速度を高めて、Si−MOSFET4の過渡的な電圧変化も抑えることができる。

【0044】

つまり、第1実施形態のハイブリッドパワーデバイスでは、Si−MOSFET4がオン・オフ動作をし、その後にSiC−JFET2が遅れて動作するが、本実施形態では、SiC−JFET2の動作を相対的に速くして、スイッチング速度を高めることができるのである。

[第4実施形態]

図6に示すように、第4実施形態のハイブリッドパワーデバイスは、第1実施形態に記載のコンデンサ12に対し、抵抗18を直列に接続したものであり、他の構成は第1実施形態に記載のものと同じである。

【0045】

そして、このようにコンデンサ12に抵抗18を直列接続すれば、コンデンサ12に流れる電流(特にピーク電流)や時間を抵抗18の抵抗値により調整することができる。

また、共振が改善しない場合は、抵抗18と直列にダイオードを接続し、充電と放電の電流を変えることも可能である。

[第5実施形態]

図7に示すように、第5実施形態のハイブリッドパワーデバイスは、第3実施形態に記載のコンデンサ12に対し、抵抗18を直列に接続したものであり、他の構成は第5実施形態に記載のものと同じである。

【0046】

そして、このようにコンデンサ12に抵抗18を直列接続すれば、第4実施形態と同様に、コンデンサ12に流れる電流(特にピーク電流)や時間を抵抗18の抵抗値により調整することができる。

【0047】

以上、本発明の実施形態について説明したが、本発明は、上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲内にて、種々の態様をとることができる。

【符号の説明】

【0048】

2…SiC−JFET、4…Si−MOSFET、6…ダイオード、8…入力抵抗、10…速度調整抵抗、12…コンデンサ、14…ダイオード、16,18…抵抗。

【技術分野】

【0001】

本発明は、ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスに関する。

【背景技術】

【0002】

近年、インバータ、DC−DCコンバータ、スイッチング電源等のパワーエレクトロニクス機器にて使用するのに好適な高耐圧のパワーデバイスとして、SiC(シリコンカーバイト)からなるJFET(接合型電界効果トランジスタ)が注目されている。

【0003】

ところで、SiC−JFETは、ゲート酸化膜がないため、SiC−MOSFETに比べて製造し易いものの、一般的にノーマリオン型であるので、自動車等の信頼性を必要とするパワーエレクトロニクス機器には使い難いという問題があった。

【0004】

このため、SiC−JFETは、Si(シリコン)からなるノーマリオフ型の低耐圧MOSFETとカスコード接続することで、全体としてノーマリオフ型のスイッチング素子として動作する、ハイブリッドパワーデバイスとして構成することが考えられている。

【0005】

しかし、図8に示すように、ノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とをカスコード接続したハイブリッドパワーデバイスにおいては、製造時に形成される寄生成分(図8に示す容量C1〜C3、インダクタンスL等)により、共振が発生し易いという問題がある。また、低耐圧Si−MOSFETに過渡的に高電圧がかかるという問題もある。

【0006】

そこで、この問題を防止するため、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に抵抗10を挿入することで、スイッチング速度を遅くすることが提案されている(例えば、特許文献1等、参照)。

【0007】

なお、図8において、Si−MOSFET4のドレインソース間に接続されたダイオード6は、Si−MOSFET4の構造上できる寄生ダイオードであり、Si−MOSFET4のゲートに接続された抵抗8は入力抵抗である。

【0008】

また、図8に示すハイブリッドパワーデバイスにおいて、SiC−JFET2、Si−MOSFET4にはnチャネルのものが使用されており、これらをカスコード接続する接続点(SiC−JFET2のソースとSi−MOSFET4のドレインとの接続点)には、センシング用のSE端子が設けられている。

【0009】

そして、このハイブリッドパワーデバイスにおいては、SiC−JFET2のドレインが、ハイブリッドパワーデバイスのドレイン(D)、Si−MOSFET4のソースが、ハイブリッドパワーデバイスのソース(S)、Si−MOSFET4のゲートが、ハイブリッドパワーデバイスのゲート(G)となる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】US 20020153938A1

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかしながら、上記提案のハイブリッドパワーデバイスのように、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に抵抗10を挿入した場合、スイッチング速度を遅くして、Si−MOSFET4に過渡的に高電圧が印加されたり、共振が発生したりするのを防止できるが、スイッチング速度の低下によって、ハイブリッドパワーデバイスのターンオン時等に生じるスイッチング損失が増加するという問題があった。

【0012】

つまり、図8に示したハイブリッドパワーデバイスにおいて、例えば、ターンオン時には、図9に示すように、抵抗10を介して、2段階(A、B)で放電を行うことになる。

具体的には、1段目(A)では、ゲート電圧が印加されて、Si−MOSFET4がオンし、SE端子電圧が下がることにより、SiC−JFET2のゲート−ソース間容量C2の放電Q1を行う。また、2段目(B)では、SiC−JFET2のゲート−ドレイン間容量C1の放電Q2を行う。

【0013】

そして、1段目(A)では、スイッチングを高速化して、その期間(時点t1−t2間)を短くすれば、スイッチング損失を低減できる。また、このときの抵抗10の両端電圧(SiC−JFET2のゲート電圧Vg_jfet)は、マイナスに振れるが、できるだけ高い電位(換言すればマイナスの振れ幅が小さい電位)であるほうが、スイッチング速度が高速になり望ましい。

【0014】

一方、2段目(B)では、共振が起こりやすいので、スイッチング速度を遅くするほうが、安定した動作を実現できる。また、このときの抵抗10の両端電圧(SiC−JFET2のゲート電圧Vg_jfet)は、マイナスに振れるが、できるだけ低い電位であるほうが、スイッチング速度が遅くなり、結果的に共振を抑え易い。

【0015】

しかし、上記提案の技術では、単に抵抗10を設けてスイッチング速度を抑えるだけであるので、2段目(B)で共振が発生するのを防止することはできても、1段目(A)でスイッチング損失を増加させてしまうのである。

【0016】

本発明は、こうした問題に鑑みなされたものであり、ノーマリオン型のSiC−JFET2とノーマリオフ型のSi−MOSFET4とをカスコード接続してなるハイブリッドパワーデバイスにおいて、共振の発生を抑制しつつ、スイッチング損失を低減できるようにすることを目的とする。

【課題を解決するための手段】

【0017】

かかる目的を達成するためになされた請求項1に記載のハイブリッドパワーデバイスは、図8に示した従来装置と同様、ノーマリオン型のSiC−JFETとノーマリオフ型のSi−MOSFETとをカスコード接続することにより構成されている。

【0018】

そして、SiC−JFETのゲートには、当該ハイブリッドパワーデバイスのスイッチング期間中にSiC−JFETのゲート電流及びゲート電圧を変化させて、スイッチング期間の前半ではスイッチング速度が速く、スイッチング期間の後半ではスイッチング速度が遅くなるよう、当該ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段が設けられている。

【0019】

このため、本発明のハイブリッドパワーデバイスによれば、図9に示したスイッチング期間の1段目(A)では、スイッチング速度を速くすることで、スイッチング損失を低減し、図9に示したスイッチング期間の2段目(B)では、スイッチング速度を遅くして、共振が発生するのを防止する、といったことができるようになる。

【0020】

ここで、制御手段は、例えば、請求項2に記載のように、SiC−JFETのゲートとSi−MOSFETのソースとの間に設けられたスイッチング速度調整用の抵抗(速度調整抵抗)と、SiC−JFETのゲートに接続されたコンデンサとからなるアナログ回路にて構成することができる。

【0021】

つまり、速度調整抵抗は、図8に示した抵抗10と同じであり、制御手段には、この速度調整抵抗とは別にコンデンサを設けるのである。

そして、このようにすれば、図10(b)に例示するように、当該ハイブリッドパワーデバイスのターンオン時には、まずコンデンサに大電流が流れ、コンデンサに電荷が蓄積されると、速度調整抵抗に電流が流れ、最終的には、コンデンサに蓄積された電荷が速度調整抵抗を介して放電されることになる。

【0022】

つまり、図8に示した従来装置のように速度調整抵抗を設けただけでは、図10(a)に示すように、当該ハイブリッドパワーデバイスのターンオン時に、速度調整抵抗の抵抗値に対応した電流が流れるだけであるが、請求項2に記載のように、制御手段を速度調整抵抗とコンデンサとで構成すれば、スイッチング期間の前半部分でSiC−JFETのゲートに大電流を流して、スイッチング速度を速くし、スイッチング期間の後半部分ではSiC−JFETのゲート電流を減少させ、更にスイッチング終了後もゲート電流を流して、スイッチング速度を遅くすることができる。

【0023】

ここで、上記コンデンサは、請求項3に記載のように、速度調整抵抗に並列に接続するようにしてもよく、或いは、請求項4に記載のように、コンデンサにダイオードと抵抗との並列回路を直列に接続し、その直列回路を、速度調整回路に並列に接続するようにしてもよい。

【0024】

そして、コンデンサに対し、ダイオードと抵抗との並列回路を直列接続した場合には、図9に示したスイッチング期間の1段目(A)では、ダイオードを介してコンデンサに電流を流すことで、スイッチング速度を速くし、図9に示したスイッチング期間の2段目(B)では、コンデンサと抵抗との直列回路にてコンデンサに蓄積された電荷を放電することになるので、請求項3に記載のものに比べて、スイッチング速度を更に遅くし、共振の発生を抑えることができる。

【0025】

またコンデンサは、速度調整抵抗に対し並列接続するのではなく、請求項5に記載のように、コンデンサの一端をSiC−JFETのゲートに接続し、他端を、Si−MOSFETのゲートに接続するようにしてもよい。

【0026】

そして、このようにすれば、SiC−JFETのゲートに、Si−MOSFETのゲートに入力された駆動電圧を直接印加することができるので、Si−MOSFETのオン・オフ動作に対するSiC−JFETの動作遅れを少なくして、スイッチング速度を速くして、Si−MOSFETへの過渡的な電圧印加も防止することができる。

【0027】

なお、請求項3又は請求項5に記載のハイブリッドパワーデバイスのように、コンデンサを速度調整抵抗に並列接続するか、コンデンサを各FETのゲート間に接続する場合には、請求項6に記載のように、コンデンサに対し、速度調整抵抗よりも抵抗値が小さい抵抗を直列に接続するようにしてもよい。

【0028】

そして、このようにすれば、図10(c)に示すように、コンデンサに流れる電流(特にピーク電流)を抵抗とコンデンサとの時定数にて調整することができるようになり、延いては、スイッチング速度の調整を容易に行うことができるようになる。

【図面の簡単な説明】

【0029】

【図1】第1実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図2】第1実施形態のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図3】第2実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図4】第2実施形態のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図5】第3実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図6】第4実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図7】第5実施形態のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図8】従来のハイブリッドパワーデバイスの構成を表す電気回路図である。

【図9】従来のハイブリッドパワーデバイスの動作を表すタイムチャートである。

【図10】本発明のハイブリッドパワーデバイスにおける電流波形を従来技術と比較して説明する説明図である。

【発明を実施するための形態】

【0030】

以下に本発明の実施形態を図面と共に説明する。

[第1実施形態]

図1に示すように、第1実施形態のハイブリッドパワーデバイスは、ノーマリオン型のSiC−JFET2と、ノーマリオフ型のSi−MOSFET4とを備え、SiC−JFET2のソースとSi−MOSFET4とをカスコード接続したものであり、基本的には、図8に示した従来ものと同様に構成されている。

【0031】

そして、図8に示したものと異なる点は、ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段として、SiC−JFET2のゲートとSi−MOSFET4のソースとの間に挿入された抵抗(速度調整抵抗)10に加えて、この速度調整抵抗10に並列接続されたコンデンサ12とを備えた点であり、他の構成は、図8に示したものと全く同じである。

【0032】

このように構成された本実施形態のハイブリッドパワーデバイスにおいては、速度調整抵抗10に対しコンデンサ12が並列に接続されているので、このコンデンサ12により、スイッチング期間中にスイッチング速度を制御することができる。

【0033】

以下、この制御について説明する。

図2は、本実施形態のハイブリッドパワーデバイスのターンオン時の、ドレイン−ソース間電圧(DS間電圧)、ドレイン電流(DS間電流)、SE端子電圧、コンデンサ12に流れるコンデンサ電流、速度調整抵抗10に流れる速度調整抵抗電流、SiC−JFET2のゲート電圧及びゲート電流を表すタイムチャートである。

【0034】

なお、図2において、コンデンサ電流及び速度調整抵抗電流は、抵抗10或いはコンデンサ12から、ハイブリッドパワーデバイスのソース(S)側に流れる方向を正(+)、これとは逆方向を負(−)として記載されている。

【0035】

図2に示すように、本実施形態のハイブリッドパワーデバイスにおいても、従来のものと同様、2段階で放電を行い、1段目(A)では、SE端子電圧が下がることにより、SiC−JFET2のゲート−ソース間容量放電を行い、2段目(B)では、SiC−JFET2のゲート−ドレイン間容量の放電を行う。

【0036】

そして、1段目(A)の放電時には、コンデンサ12と速度調整抵抗10の両方に電流が流れる。また、初期状態では、コンデンサ12に電荷が溜まっていないので、速度調整抵抗10よりもコンデンサ12側に電流が多く流れるが、徐々にコンデンサ12に電流が流れて電荷が溜まり始めると(換言すればコンデンサ12の電圧が大きくなり始めると)、コンデンサ12に流れる電流が減り、速度調整抵抗10に流れる電流が増加し始める。

【0037】

SiC−JFET2のゲート電流は、『ゲート電流=コンデンサ電流+速度調整抵抗電流』と表すことができ、SiC−JFET2のゲート電流の電荷量は、SiC−JFET2のゲートソース間容量を放電する電荷量(Q1)である。

【0038】

このため、1段目(A)では、コンデンサ12が効果的に機能し、図2の(a)から明らかなように、SiC−JFET2のゲート電圧が下がり難く、スイッチング速度を高速化できる。なお、1段目(A)では、高速化に伴い、SiC−JFET2のゲート電流は増加する(図2(c)参照)。

【0039】

一方、2段目(B)では、コンデンサ12に電荷が溜まっている(換言すればSiC−JFET2のゲート電圧Vg_jfetは「0」ではない)ため、コンデンサ12に電流が流れ難い状態になっている。従って、電流は速度調整抵抗10に多く流れることになり、SiC−JFET2のゲート電圧が低下し易い。そのため、2段目では、コンデンサ12によるスピードアップ機能が弱まり、SiC−JFET2のゲート電圧が下がることから、従来と同様、スイッチング速度を遅くすることができる(図2(b)参照)。

[第2実施形態]

図3に示すように、第2実施形態のハイブリッドパワーデバイスは、コンデンサ12に対し、直列に、ダイオード14と抵抗16とを並列接続した回路を接続したものであり、他の構成は、第1実施形態のハイブリッドパワーデバイスと同一である。なお、ダイオード14は、コンデンサ電流の負(−)方向を順方向として接続されている。また、抵抗16の抵抗値は、速度調整抵抗10の抵抗値よりも小さい値に設定されている。

【0040】

このように構成された本実施形態のハイブリッドパワーデバイスにおいては、図4に示すように、ターンオン時、1段目(A)の前半(時点t1−t1′間)では、主にダイオード14を通じて電流を流し、1段目(A)の後半部分(時点t1′−t2′間)で、コンデンサ12に充電し、その後(時点t2′後)放電を開始する。

【0041】

そして、放電時には、ダイオード14は逆導通しないので、抵抗16の抵抗値を大きめに設定することで電流の流れを妨げることができる。つまり、コンデンサ12に溜まった電荷(換言すればコンデンサ電圧)を保持することができる。

【0042】

従って、2段目(B)では、コンデンサ12に電荷がすでに溜まっているので、電流が流れ難くなり、SiC−JFET2のゲート電流のうち、速度調整抵抗10を使って流れる量が多くなる。このため、本実施形態によれば、第1実施形態に比べ、SiC−JFET2のゲート電圧が低下し、スイッチング速度を弱める効果を高めることができる。

[第3実施形態]

図5に示すように、第3実施形態のハイブリッドパワーデバイスは、第1実施形態に記載のようにコンデンサ12を速度調整抵抗10に並列接続するのではなく、コンデンサ12を、SiC−JFET2のゲートとSi−MOSFET4のゲートとの間に接続したものであり、他の構成は第1実施形態に記載のものと同じである。

【0043】

そして、本実施形態のハイブリッドパワーデバイスによれば、コンデンサ12をSi−MOSFET4の駆動回路に直接接続されることになるので、Si−MOSFET4のオン・オフ動作に対するSiC−JFET2の遅れが少なくなり、スイッチング速度を高めて、Si−MOSFET4の過渡的な電圧変化も抑えることができる。

【0044】

つまり、第1実施形態のハイブリッドパワーデバイスでは、Si−MOSFET4がオン・オフ動作をし、その後にSiC−JFET2が遅れて動作するが、本実施形態では、SiC−JFET2の動作を相対的に速くして、スイッチング速度を高めることができるのである。

[第4実施形態]

図6に示すように、第4実施形態のハイブリッドパワーデバイスは、第1実施形態に記載のコンデンサ12に対し、抵抗18を直列に接続したものであり、他の構成は第1実施形態に記載のものと同じである。

【0045】

そして、このようにコンデンサ12に抵抗18を直列接続すれば、コンデンサ12に流れる電流(特にピーク電流)や時間を抵抗18の抵抗値により調整することができる。

また、共振が改善しない場合は、抵抗18と直列にダイオードを接続し、充電と放電の電流を変えることも可能である。

[第5実施形態]

図7に示すように、第5実施形態のハイブリッドパワーデバイスは、第3実施形態に記載のコンデンサ12に対し、抵抗18を直列に接続したものであり、他の構成は第5実施形態に記載のものと同じである。

【0046】

そして、このようにコンデンサ12に抵抗18を直列接続すれば、第4実施形態と同様に、コンデンサ12に流れる電流(特にピーク電流)や時間を抵抗18の抵抗値により調整することができる。

【0047】

以上、本発明の実施形態について説明したが、本発明は、上記実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲内にて、種々の態様をとることができる。

【符号の説明】

【0048】

2…SiC−JFET、4…Si−MOSFET、6…ダイオード、8…入力抵抗、10…速度調整抵抗、12…コンデンサ、14…ダイオード、16,18…抵抗。

【特許請求の範囲】

【請求項1】

ノーマリオン型のSiC−JFETと、ノーマリオフ型のSi−MOSFETとを備え、前記SiC−JFETのソースと前記Si−MOSFETのドレインとを接続することにより、前記SiC−JFETと前記Si−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスであって、

前記SiC−JFETのゲートに接続され、当該ハイブリッドパワーデバイスのスイッチング期間中に前記SiC−JFETのゲート電流及びゲート電圧を変化させて、前記スイッチング期間の前半ではスイッチング速度が速く、前記スイッチング期間の後半ではスイッチング速度が遅くなるよう、当該ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段、

を設けたことを特徴とするハイブリッドパワーデバイス。

【請求項2】

前記制御手段は、

前記SiC−JFETのゲートと前記Si−MOSFETのソースとの間に設けられ、前記スイッチング速度を調整するための速度調整抵抗と、

前記SiC−JFETのゲートに接続されたコンデンサとからなることを特徴とする請求項1に記載のハイブリッドパワーデバイス。

【請求項3】

前記コンデンサは、前記速度調整抵抗に並列に接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項4】

前記コンデンサには、ダイオードと抵抗との並列回路が直列に接続されており、

これらコンデンサと前記並列回路との直列回路は、前記速度調整回路に並列に接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項5】

前記コンデンサは、一端が前記SiC−JFETのゲートに接続され、他端が前記Si−MOSFETのゲートに接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項6】

前記コンデンサには、前記速度調整抵抗よりも抵抗値が小さい抵抗が、直列に接続されていることを特徴とする請求項3又は請求項5に記載のハイブリッドパワーデバイス。

【請求項1】

ノーマリオン型のSiC−JFETと、ノーマリオフ型のSi−MOSFETとを備え、前記SiC−JFETのソースと前記Si−MOSFETのドレインとを接続することにより、前記SiC−JFETと前記Si−MOSFETとをカスコード接続してなるハイブリッドパワーデバイスであって、

前記SiC−JFETのゲートに接続され、当該ハイブリッドパワーデバイスのスイッチング期間中に前記SiC−JFETのゲート電流及びゲート電圧を変化させて、前記スイッチング期間の前半ではスイッチング速度が速く、前記スイッチング期間の後半ではスイッチング速度が遅くなるよう、当該ハイブリッドパワーデバイスのスイッチング速度を制御する制御手段、

を設けたことを特徴とするハイブリッドパワーデバイス。

【請求項2】

前記制御手段は、

前記SiC−JFETのゲートと前記Si−MOSFETのソースとの間に設けられ、前記スイッチング速度を調整するための速度調整抵抗と、

前記SiC−JFETのゲートに接続されたコンデンサとからなることを特徴とする請求項1に記載のハイブリッドパワーデバイス。

【請求項3】

前記コンデンサは、前記速度調整抵抗に並列に接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項4】

前記コンデンサには、ダイオードと抵抗との並列回路が直列に接続されており、

これらコンデンサと前記並列回路との直列回路は、前記速度調整回路に並列に接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項5】

前記コンデンサは、一端が前記SiC−JFETのゲートに接続され、他端が前記Si−MOSFETのゲートに接続されていることを特徴とする請求項2に記載のハイブリッドパワーデバイス。

【請求項6】

前記コンデンサには、前記速度調整抵抗よりも抵抗値が小さい抵抗が、直列に接続されていることを特徴とする請求項3又は請求項5に記載のハイブリッドパワーデバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2011−166673(P2011−166673A)

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願番号】特願2010−30221(P2010−30221)

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]