バイアス回路およびそれを有するアンプ回路

【課題】増幅トランジスタのトランスコンダクタンスgmの変動を抑制する。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,バイアス回路およびそれを有するアンプ回路に関する。

【背景技術】

【0002】

アンプ回路は,トランジスタなどの増幅素子とそれに接続される負荷素子とを有する。増幅素子としては,例えば,MOSトランジスタが,負荷素子としては,例えば,抵抗やインダクタなどが用いられる。

【0003】

ソース接地型のMOSトランジスタは,ソースが接地され,ゲートに入力信号が入力され,ドレインから出力信号が出力される。入力信号によるゲート電圧に応じてトランジスタのドレイン電流が変化し,そのドレイン電流は,トランジスタのドレイン電流・ゲート電圧特性(以下Id-Vg特性)の傾き(トランスコンダクタンスgm,相互コンダクタンスgm)に応じて入力信号を増幅した電流になる。さらに,ドレインに生成される出力電圧は,トランジスタのドレイン電流に負荷素子のインピーダンスを乗算した電圧である。したがって,トランスコンダクタンスをgm,負荷素子の抵抗値をRLとすると,アンプ回路の利得は,−gmRLになる。

【0004】

トランジスタのトランスコンダクタンスgmは,製造プロセスのバラツキ,温度変化,電源電圧変化により変化する。つまり,製造プロセスバラツキ,温度変化,電源電圧変化により,トランジスタのId-Vg特性が変化し,それに伴いその特性の傾きであるトランスコンダクタンスgmも変化する。このようなトランスコンダクタンスgmの変化は,アンプ回路の利得を変化させるので,好ましくない。

【0005】

利得のバラツキを抑制するために,トランスコンダクタンスgmを一定に保つように増幅素子であるトランジスタのゲートバイアス電圧を変化させるバイアス回路が提案されている。たとえば,以下の特許文献がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−147800号公報

【特許文献2】WO2008/050375

【特許文献3】特開平7−288437号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら,従来のバイアス回路は,MOSトランジスタのドレイン・ソース間電圧の変化に伴ってドレイン電流が変化することを考慮していない。従来の微細化されていないサイズのMOSトランジスタは,ドレイン・ソース間電圧の変化に対応するドレイン電流の変化は微小であるため,ドレイン・ソース間電圧の変化に伴うドレイン電流の変化を無視するバイアス回路でも,アンプ回路の増幅トランジスタのトランスコンダクタンスgmの変動を十分抑制することができた。

【0008】

しかし,近年における高速動作に対応したトランジスタは,チャネル長がより一層短くなる傾向になる。チャネル長が短くなるにしたがって,ドレイン・ソース間電圧の変動に対するドレイン電流の変動幅が大きくなる。そのため,従来のバイアス回路では,微細化されチャネル長が短くなった増幅トランジスタのトランスコンダクタンスgmの変動を十分に抑制することは困難である。

【0009】

そこで,本発明の目的は,アンプ回路内の増幅用トランジスタのトランスコンダクタンスの変動を抑制するバイアス回路と,それを有するアンプ回路とを提供することにある。

【課題を解決するための手段】

【0010】

バイアス回路の第1の側面は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

【発明の効果】

【0011】

第1の側面によれば,アンプ回路内の増幅用トランジスタのトランスコンダクタンスの変動を抑制することができる。

【図面の簡単な説明】

【0012】

【図1】アンプ回路の回路図である。

【図2】増幅トランジスタのゲート電圧・ドレイン電流特性を示す図である。

【図3】微細化トランジスタのId−Vg特性とgm−Vg特性を示す図である

【図4】従来のアンプ回路を示す回路図である。

【図5】図4の場合の27種類の条件に対するトランジスタのトランスコンダクタンスgmの変動を示す図である。

【図6】図4の場合の27種類の条件に対する利得の変動を示す図である。

【図7】27種類の条件を示す図である。

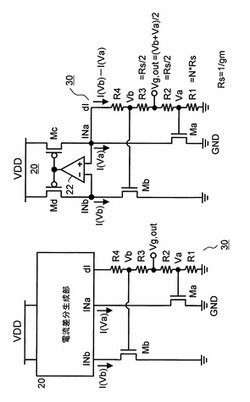

【図8】第1の実施の形態におけるバイアス回路の回路図である。

【図9】第1の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。

【図10】MOSトランジスタのId-Vg特性を示すグラフ図である。

【図11】図8のバイアス回路により生成される電圧Va,Vbとドレイン電流I(Va),I(Vb)との関係を示すグラフ図である。

【図12】トランジスタのId-Vg特性が,低い閾値電圧Vthを有する場合のバイアス回路の動作を示すグラフ図である。

【図13】トランジスタのId-Vg特性がドレイン電流が増大する特性になった場合のバイアス回路の動作を示すグラフ図である。

【図14】図9のアンプ回路の一例を示す回路図である。

【図15】第2の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。

【図16】本実施の形態におけるアンプ回路の増幅トランジスタのトランスコンダクタンスgmを示す図である。

【図17】本実施の形態におけるアンプ回路の利得を示す図である。

【発明を実施するための形態】

【0013】

図1は,アンプ回路の回路図である。アンプ回路は,ソースがグランドGNDなどの基準電圧に接続され,ゲートに入力信号Vinとバイアス電圧Vbiasとが供給されたNMOSトランジスタM0と,トランジスタM0のドレインと電源電圧VDDとの間に設けられた負荷抵抗素子RLと,直流のバイアス電圧Vbiasを生成するバイアス回路BIASとを有する。高周波の入力信号VinはカップリングキャパシタCinを介してゲートに供給される。つまり,入力信号Vinの交流成分だけがゲートに供給される。また,バイアス電圧Vbiasは高抵抗の給電抵抗Rbを介してゲートに供給される。給電抵抗Rbは高い抵抗値を有するので,ゲートからバイアス回路BIASへの電流は微少である。これにより,ゲート電圧は,直流のバイアス電圧Vbiasを中心とし,入力信号Vinの交流成分を有する信号になる。

【0014】

ソース接地のトランジスタM0は,ゲート電圧に応じたドレイン電流を生成し,ドレインに接続された出力端子に出力信号Voutが出力される。出力信号Voutは,ドレイン電流と負荷抵抗素子RLとの積に対応する振幅電圧を有する。

【0015】

図2は,増幅トランジスタのドレイン電流・ゲート電圧特性(Id−Vg特性)を示す図である。ゲート電圧Vgが閾値電圧Vthを超えるとドレイン電流Idが発生し,特性曲線10に示されるとおり,ドレイン電流Idは,ゲート電圧Vgの閾値電圧Vthを超えるオーバードライブ電圧(Vg−Vth)の二乗に比例して増加する。

【0016】

入力信号Vinの交流成分が直流のバイアス電圧Vbiasに重畳され,この電圧変化は,バイアス電圧VbiasにおけるId-Vg特性曲線10の傾きgmに応じて増幅されたドレイン電流Idの変化に変換される。このId-Vg特性曲線10の傾きがトランスコンダクタンスgmである。そして,生成されたドレイン電流Idを負荷抵抗素子RLの抵抗値に乗じた電圧振幅を有する出力信号Voutがドレインと負荷抵抗素子RLの接続ノードである出力端子に生成される。この出力信号Voutは入力信号Vinの逆相信号である。

【0017】

上記図2の説明から,アンプ回路の利得は,−gmRLであることが理解できる。そして,プロセスバラツキ,温度変化,電源電圧変化などによりゲート電圧・ドレイン電流特性が変動すると,トランジスタのトランスコンダクタンスgmが変動し,利得−gmRLの変動を招くことが理解できる。

【0018】

図3は,微細化トランジスタのId−Vg特性とgm−Vg特性を示す図である。この特性は,例えば90nm世代の1.2V電源の微細化トランジスタの特性である。図3のId−Vg特性には,プロセスバラツキなどで高速側(Fast),低速側(Slow),ティピカル(Typical)の特性を持つトランジスタそれぞれについて,さらに,4種類のドレイン電圧Vd(0.4,0.6,0.8,1.2V)に対する特性,合計で3×4=12の特性が示されている。高速側にばらついたトランジスタの特性(Fast)は,閾値電圧が低くドレイン電流Idが大きい。一方,低速側にばらついたトランジスタの特性(Slow)は,閾値電圧が高くドレイン電流Idが小さい。そして,ティピカルなトランジスタの特性(Typical)は,閾値電圧もドレイン電流も高速側と低速側の間の特性である。

【0019】

さらに,Id−Vg特性は,ドレイン電圧Vdが異なるとそれに応じて異なる。微細化された短チャネル長のトランジスタのドレイン電流は,飽和領域でも一定ではなく,ドレイン・ソース間電圧の増大に応じて増大することが知られている。このドレイン電流の増加の程度はチャネル長に反比例する。

【0020】

トランスコンダクタンスgmは,図2に示したとおりId−Vg特性である2次曲線の傾きである。したがって,gm−Vg特性はId−Vg特性を微分したものである。高速側(Fast)のほうが低いゲート電圧Vgでトランスコンダクタンスgmが立ち上がることが示されている。また,図示されていないが,高速側(Fast),低速側(Slow),ティピカル(Typical)のいずれにおいても,ドレイン電圧Vdが高いほど,トランスコンダクタンスgmが大きくなっている。このgm−Vg特性に示されるとおり,MOSトランジスタのトランスコンダクタンスgmを一定にするためには,プロセスバラツキ等の変動とドレイン電圧Vdの変動とに応じて,ゲート電圧Vgを変化させることが必要であることが理解できる。

【0021】

図4は,従来のアンプ回路を示す回路図である。図4には,ゲートバイアス電圧Vbiasを生成するバイアス回路BIASと,負荷抵抗RLがドレインに接続された増幅トランジスタM0とが示されている。バイアス電圧Vbiasは給電抵抗Rbを介して増幅トランジスタM0のゲートに供給され,入力信号VinはカップリングキャパシタCinを介してゲートに供給される。

【0022】

バイアス回路BIASは,トランジスタサイズW/L(Wはチャネル幅,Lはチャネル長)の比がK:1のトランジスタM1,M2と,トランジスタM1のソースとグランド間に接続された抵抗Rsと,両トランジスタM1,M2のドレインと電源電圧VDDとの間にそれぞれ設けられた電流ミラー回路10とを有する。電流ミラー回路10により両トランジスタM1,M2のドレイン電流は等しくなる。つまりIM1=IM2である。

【0023】

そして,以下に示すとおり,トランジスタM2のトランスコンダクタンスgmが一定に保たれるようなバイアス電圧Vbiasを生成する。そして,トランジスタM2,M0が共にソース接地型のトランジスタであるので,トランジスタM2のgmが一定であれば,同じバイアス電圧Vbiasがゲートに供給されている増幅用トランジスタM0のgmも一定であることを前提にしている。

【0024】

トランジスタM1,M2に流れる電流IM1,IM2は,つぎのとおりである

【0025】

【数1】

【0026】

【数2】

【0027】

【数3】

【0028】

【数4】

【0029】

【数5】

【0030】

ここで,μは移動度,Coxは単位面積当たりのゲートキャパシタ,WはトランジスタM2のゲート幅,KWはトランジスタM1のゲート幅,Lは両トランジスタM1,M2のゲート長,VxはトランジスタM1と抵抗Rsとの間のノードの電圧(トランジスタM1のソース電圧),Vthはトランジスタの閾値電圧である。

【0031】

数式(3.4)から数式(3.1)と数式(3.3)の右辺は等しいので,次の通りである。

【0032】

【数6】

【0033】

そして,数式(3.6)の両辺の平方根をとり,√Kで除算して整理すると,ソース電圧Vxは次の通りである。

【0034】

【数7】

【0035】

さらに,数式(3.4)から数式(3.2)と数式(3.3)の右辺も等しいので,

【0036】

【数8】

【0037】

数式(3.7)の電圧Vxを数式(3.8)に代入して(Vg-Vth)について整理すると,

【0038】

【数9】

【0039】

数式(3.9)を数式(3.3)に代入すると,

【0040】

【数10】

【0041】

数式(3.4)からIM1=IM2であるので,数式(3.10)を数式(3.5)に代入すると以下のとおりgmが得られる。

【0042】

【数11】

【0043】

つまり,トランジスタM2のトランスコンダクタンスgmは,一定の値である。

【0044】

しかしながら,図4のバイアス回路には,次の問題点がある。

(1)トランジスタのドレイン電流がドレイン・ソース間電圧Vdsに大きく依存することが考慮されていない。

(2)(1)のドレイン電流のドレイン・ソース間電圧Vds依存性があるにもかかわらず,トランジスタM1のソースとグランドとの間に抵抗Rsが設けられ,両トランジスタM1,M2のドレイン・ソース間電圧が異なる。そのためバイアス電圧Vbiasに対する両トランジスタM1,M2のトランスコンダクタンスgmは異なることになるが,上記の演算式はgmが等しいと見なしている。

(3)(1)のドレイン電流のドレイン・ソース間電圧Vds依存性があるにもかかわらず,増幅用トランジスタM0とバイアス回路のトランジスタM1,M2のドレイン電圧がそれぞれ独立しているので,トランジスタM2について所望のgmが得られるバイアス電圧Vbiasを生成しても,増幅用トランジスタM0について同じ所望のgmが得られる保証はない。

【0045】

上記の問題点(1)は,後述するドレイン電流の計算式に示されるとおり,正確なドレイン電流を算出するためには,数式(3.1)(3.3)に,(1+λVds)(λはチャネル長Lに反比例する定数)を乗算する必要があることを意味する。上記の数式(3.1)(3.3)はλ=0とした近似式である。しかし,微細化された短チャネルのトランジスタの場合は,λが大きくなり,ドレイン・ソース間電圧Vdsに依存してドレイン電流が変動する。そのため,図4の回路では,増幅用トランジスタM0のトランスコンダクタンスgmを所望の一定値に制御することができない。

【0046】

したがって,上記の3つの問題点は,トランジスタM0,M1,M2が短チャネルになるほど,そして電源電圧が低電圧になるほど顕著になり,増幅トランジスタM0を所望のgmに制御するバイアス電圧Vbiasの生成が困難になる。

【0047】

図5は,図4の場合の27種類の条件に対するトランジスタのトランスコンダクタンスgmの変動を示す図である。また,図6は,図4の場合の27種類の条件に対する利得の変動を示す図である。そして,図7は,27種類の条件を示す図である。27種類の条件は,Fast, Typical, Slowの3つのトランジスタ条件,3つの温度条件,そして3種類の電源電圧条件の組み合わせである。

【0048】

つまり,トランスコンダクタンスgmは,トランジスタ条件がFastなほど大きく,温度が低いほど大きく,電源電圧が高いほど大きくなる方向にばらついている。

【0049】

[第1の実施の形態]

図8は,第1の実施の形態におけるバイアス回路の回路図である。左側が概略回路図,右側が概略回路図の電流差分生成部を具体的に示す詳細回路図である。

【0050】

図8の左側に示したバイアス回路は,第1のドレイン電流I(Va)を生成する第1のNMOSトランジスタMaと,第2のドレイン電流I(Vb)を生成する第2のNMOSトランジスタMbとを有する。これらのトランジスタのゲート幅,チャネル長は,例えば同じとする。

【0051】

さらに,バイアス回路は,直列に接続された複数の抵抗素子R1-R4を有し,それら複数の抵抗素子に第2のドレイン電流I(Vb)と第1のドレイン電流I(Va)の差分電流dI(=I(Vb)-I(Va))が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧Va, Vb, Vg,outを生成する抵抗回路30を有する。そして,抵抗回路の第1のノードの第1の電圧Vaが第1のトランジスタMaのゲートに印加され,第2のノードの第2の電圧Vbが第2のトランジスタMbのゲートに印加され,第1,第2のノードと異なる第3のノードから第3の電圧Vg,outがバイアス電圧として出力される。このバイアス電圧Vg,outは,ソース接地の増幅トランジスタ(図8には図示せず)のゲートに給電抵抗を介して供給される。

【0052】

電流差分生成部20は,両トランジスタMa,Mbのドレインと電源電圧VDDとの間に設けられ,電流差分生成部の入力端子INb,INaに流れる両トランジスタMb,Maのドレイン電流I(Vb)とI(Va)の差分電流を出力端子dIに生成する回路である。そして,その出力端子dIの差分電流が抵抗回路30に流れる。

【0053】

図8の右側に示した詳細回路図には,この電流差分生成部20の回路例が示されている。電流差分生成部20は,両トランジスタMa,Mbのドレインに接続される入力端子INa,INbの電位の差動電圧を増幅するオペレーションアンプ22と,入力端子INa,INbと電源電圧VDDとの間にそれぞれ設けられたPMOSトランジスタMc,Mdとを有し,オペレーションアンプ22の出力電圧がPMOSトランジスタMc,Mdのゲートに印加される。これにより,トランジスタMc,Mdには等しい電流が生成され,また,入力端子INa,INbの電圧は等しくなるよう制御される。そして,出力端子dIから差分電流I(Vb)-I(Va)が抵抗回路30の直列接続された抵抗群R1-R4に流れるように構成される。

【0054】

抵抗回路30は,抵抗R1-R4がグランドと電流出力端子dIとの間に直列に接続され,差分電流dI(=I(Vb)-I(Va))が供給される。さらに,抵抗R2,R3の合計抵抗値Rsが,所望のトランスコンダクタンスgmの逆数(Rs=1/gm)と等しくなるように設定される。また,抵抗R2,R3は,例えば抵抗値Rsの1/2の抵抗値Rs/2を有する。そして,抵抗R2,R3の接続ノードから出力電圧Vg,outがバイアス電圧として出力される。抵抗R1は,設定抵抗RsのN倍(Nは正の任意の数)に設定され,また,抵抗R4は,任意の抵抗値を有する。

【0055】

上記の抵抗群R1,R2とR3,R4の抵抗比は任意の比率に変更することができる。ただし,R2とR3は等しい抵抗値を有することが望ましい。また,抵抗R4は,例えば抵抗値を0にすることもできる。

【0056】

図9は,第1の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。アンプ回路は,ゲートに入力される入力信号Vinを増幅し出力信号Voutを出力する増幅トランジスタを有するアンプ40と,それに並列に設けられたレプリカアンプ50と,レプリカアンプ50の出力電圧とバイアス回路内のトランジスタMaのドレイン電圧(入力端子INaの電圧)とを入力するオペレーションアンプ24とを有する。そして,オペレーションアンプ24の出力電圧VFをフィードバックし,その出力電圧VFで抵抗R4の抵抗を可変制御して,トランジスタMaのドレイン電圧とレプリカアンプ50のドレイン電圧とが等しくなるようにする。

【0057】

アンプ40とレプリカアンプ50は,同様の回路構成を有し,ソース接地のNMOSトランジスタと,それのドレインと電源電圧との間に設けた負荷回路とを有する。レプリカアンプ50の回路は,アンプ40の回路の増幅トランジスタや負荷回路より少ない電流を消費するように構成されるが,レプリカアンプ50内のトランジスタとアンプ40内のトランジスタとは同様の動作を行い,ドレイン電圧は互いに等しい。

【0058】

したがって,バイアス回路内のトランジスタMaのドレイン電圧とレプリカアンプ内のドレイン電圧とを等しくするように制御することで,間接的にアンプ40内のドレイン電圧もバイアス回路内のドレイン電圧と等しくすることができる。

【0059】

図9のようなレプリカアンプ50とオペレーションアンプ24の構成により,バイアス回路内のトランジスタMaのドレイン電圧と,アンプ40内の増幅トランジスタ(図示せず)のドレイン電圧(アンプ40の出力電圧Vout)とを等しくして,バイアス回路が生成したバイアス電圧Vg,outによりアンプ40内の増幅トランジスタのトランスコンダクタンスgmが所望の値に制御されるようにしている。

【0060】

以下,図8のバイアス回路と,図9のアンプ回路の動作について説明する。

【0061】

トランジスタMa,Mbは共にソースが基準電圧であるグランドGNDに接続され,オペレーションアンプ22により両トランジスタMa,Mbのドレイン電圧である入力端子INa,INbの電圧は等しくなるように制御される。したがって,両トランジスタMa,Mbのドレイン・ソース間電圧は等しい。一方,トランジスタMaのゲートには抵抗R1,R2の接続ノードの電圧Vaが印加され,トランジスタMbのゲートには抵抗R3,R4の接続ノードの電圧Vbが印加される。両電圧Va,VbはVa<Vbの関係にあるので,ゲート電圧・ドレイン電流の特性により,両トランジスタのドレイン電流I(Va),I(Vb)もI(Va)<I(Vb)になる。

【0062】

一方,オペレーションアンプ22の出力が共にゲートに印加されるトランジスタMc,Mdのドレイン電流は等しくなる。したがって,トランジスタMcにはトランジスタMdと同じ電流が流れ,トランジスタMdとMbは同じドレイン電流I(Vb)であるので,入力端子INaから抵抗回路30に流れる電流は,トランジスタMa,Mbのドレイン電流の差分電流I(Vb)-I(Va)である。

【0063】

そして,両トランジスタMa,Mbのゲートに印加される電圧Va,Vbは,所望とするトランスコンダクタンスgmの逆数に等しい抵抗Rs(=1/gm)に差分電流I(Vb)-I(Va)を乗じた電圧差を有し,出力されるバイアス電圧Vg,outは,電圧Va,Vbの中間電圧になる。

【0064】

つまり,図8のバイアス回路によれば,トランジスタMa,Mbのドレイン電圧が変動しても,また,トランジスタのId-Vg特性がFast,Slow,Typicalのいずれに変動しても,また温度や電源電圧が変動しても,抵抗回路30内の電圧Va,Vbと差分電流I(Vb)-I(Va)との間には,次の関係が維持される。

Vb-Va=Rs(I(Vb)-I(Va))

ここで,Rs=1/gmであるので,上記式を変形して,次の関係が導かれる。

gm=(I(Vb)-I(Va))/(Vb-Va) (4.1)

図10は,MOSトランジスタのId-Vg特性を示すグラフ図である。アンプ40内の増幅トランジスタのゲートにバイアス電圧Vg,outを印加すると,Id-Vg特性のゲート電圧Vg,outにおける傾きがトランスコンダクタンスgmになる。したがって,バイアス回路は,この傾きgmが変動しないバイアス電圧Vg,outを生成すれば良いことになる。

【0065】

図11は,図8のバイアス回路により生成される電圧Va,Vbとドレイン電流I(Va),I(Vb)との関係を示すグラフ図である。図11にもMOSトランジスタのId-Vg特性が示されている。そして,図8のバイアス回路は,前述の数式(4.1)の関係を常に満たすように動作する。従って,図11の3つの頂点(Va,I(Va)),(Vb,I(Vb)),(Vb,I(Va))からなる三角形TRの斜辺の傾きは,常に数式(4.1)となる。この三角形TRの斜辺の傾きは,Id-Vg特性がプロセスバラツキ,温度変動,電源電圧変動,そしてトランジスタのドレイン・ソース間電圧の変動によっても,抵抗Rsの逆数1/Rs=gmに維持される。このgmは,所望とするトランスコンダクタンスである。

【0066】

一方,Id-Vg特性によれば,ドレイン電流Idは,ゲート電圧Vgの閾値電圧Vthを超えるオーバードライブ電圧(Vg-Vth)の二乗に比例する。この二次曲線の特性から,ゲート電圧Va,Vbの中点(Va+Vb)/2での二次曲線の傾きは,数式(4.1)に示した2頂点(Va,I(Va)),(Vb,I(Vb))間の傾きと常に等しくなることは数学的に証明されている。

【0067】

その結果,電圧Va,Vbの中間電圧(Va+Vb)/2をゲートバイアス電圧Vg,outとして増幅トランジスタのゲートに供給することで,増幅トランジスタのトランスコンダクタンスは常に所望の値である1/Rs=gmに維持される。

【0068】

図11のグラフ図から理解されるとおり,抵抗R1の抵抗値NRsの倍数Nは,Id-Vg特性の閾値電圧Vthと,三角形TRの位置に応じて,適切な値が選択可能である。同じ斜面の傾きを有する三角形TRがId-Vg特性と一致する解は無数にある。しかし,この数Nを固定することで,Id-Vg特性内において三角形TRがどのような大きさでどのような位置に発生するかが決まる。発明者が検討したところ,数Nは8〜10程度が望ましい。

【0069】

図12は,トランジスタのId-Vg特性が,低い閾値電圧Vthを有する場合のバイアス回路の動作を示すグラフ図である。図12のId-Vg特性の閾値電圧Vthは,図11の閾値電圧Vthよりも低くなっている。ただし,バイアス回路内の抵抗回路30の抵抗R1:(R2+R3)=N:1の関係を変えることなく,三角形TRが,そのサイズが縮小されて,Id-Vg特性上に形成されている。つまり,電圧Va,Vbは小さくなり,その差電圧Vb-Vaも小さくなっている。ただし,三角形TRの斜辺の傾きは所望のトランスコンダクタンスgm(1/Rs)に維持されている。

【0070】

図13は,トランジスタのId-Vg特性がドレイン電流が増大する特性になった場合のバイアス回路の動作を示すグラフ図である。この場合でも,バイアス回路の動作により三角形TRの斜辺の傾きが所望のトランスコンダクタンスgmになる。つまり,Id-Vg特性がId-Vg(1)からId-Vg(2)に変動した場合,特性Id-Vg(1)の場合の三角形TR(1)は,差分電流(I(Vb)-I(Va))が低下し,トランジスタMa,Mbのゲートの電圧Va,Vbが低下し,ドレイン電流I(Vb),I(Va)が低下した新たな三角形TR(2)になる。これにより,増幅トランジスタのゲートのバイアス電圧Vg,outも低下し,そのドレイン電流Idも下がり,ドレイン電圧Vdは上昇すると考えられる。ただし,三角形TR(2)により増幅トランジスタのトランスコンダクタンスgmは一定に保たれる。

【0071】

図14は,図9のアンプ回路の一例を示す回路図である。図14の例では,アンプ40がソース接地のNMOSトランジスタである増幅トランジスタM0と,そのドレインと電源電圧VDDとの間に設けられた負荷抵抗RLとを有し,バイアス電圧が給電抵抗Rbを介して増幅トランジスタM0のゲートに接続されるとともに,入力信号VinがカップリングキャパシタCinを介して増幅トランジスタM0のゲートに接続され,増幅トランジスタM0と負荷抵抗RLとの接続ノードであるドレイン端子がアンプ40の出力信号Voutである。

【0072】

そして,レプリカアンプ50は,アンプ40の増幅トランジスタM0と同様に,ソース接地されたNMOSトランジスタMrと,それと電源電圧VDDとの間に設けられた負荷抵抗Rrとを有する。レプリカアンプ50のトランジスタMrのトランジスタサイズ(ゲート幅)は,増幅トランジスタM0のk倍(但し,レプリカ比k,k<1)と小さく,その分,レプリカアンプ50の負荷抵抗Rrは,増幅トランジスタM0の負荷抵抗RLの1/k倍(1/k>1)と大きく,それにより,レプリカアンプ50のドレイン電流は,アンプ40のドレイン電流のk倍(k<1)と小さくなっている。ただし,同じゲートバイアス電圧が供給されれば,両トランジスタMr,M0のドレイン電圧は等しくなる。

【0073】

また,バイアス回路内の可変抵抗R4は,CMOSトランジスタMe,Mfを並列に接続したトランスファーゲート回路であり,トランジスタMaのドレイン電圧とレプリカトランジスタMrのドレイン電圧との差分電圧を増幅するオペレーションアンプ24の出力電圧VFと,その出力電圧VFをトランジスタM10と負荷抵抗R10を有するインバータで反転され反転電圧VFxとが,PMOSトランジスタMeとNMOSトランジスタMfのゲートにそれぞれ印加されている。

【0074】

いま仮に,レプリカアンプ50のドレイン電圧が上昇したとすると,オペレーションアンプ24の出力電圧VFが増大し,反転電圧VFxが低下し,可変抵抗R4の抵抗が上昇し,トランジスタMaのドレイン端子INaの電圧も上昇する。レプリカアンプ50のドレイン電圧が低下したときは,上記の逆の動作によりトランジスタMaのドレイン電圧は低下する。その結果,レプリカアンプのドレイン電圧とバイアス回路内のトランジスタMaのドレイン電圧とが等しくなるように制御される。

【0075】

そして,増幅トランジスタM0のドレイン電圧とレプリカトランジスタMrのドレイン電圧とは同じ方向に変動するので,結局,増幅トランジスタM0のドレイン電圧は,バイアス回路内のトランジスタMa,Mbのドレイン電圧と等しくなる。

【0076】

このように,バイアス回路内のトランジスタMa,Mbと,アンプ40内の増幅トランジスタM0と,レプリカアンプ50内のレプリカトランジスタMrとは,全て,ソースが基準電圧であるグランドGNDに接続され,ドレイン電圧は等しく制御される。そして,バイアス回路の動作により,トランジスタMa,MbのId-Vg特性において所望のトランスコンダクタンスgmを生成するバイアス電圧Vg,outが,増幅トランジスタM0のゲートに供給される。その結果,増幅トランジスタM0のトランスコンダクタンスは,所望の値に維持される。

【0077】

再度,第1の実施の形態におけるバイアス回路の必要な条件を整理すると以下のとおりである。

条件α:(I(Vb)-I(Va))/(Vb-Va)=gm(1/Rs=gm)

条件β:N(Vb-Va)=Va

条件αは,抵抗R2,R3により成り立ち,条件βは,抵抗R1,R2,R3により成り立つ。

【0078】

条件αとβが満たされることで,図11,12,13で説明したとおり,トランジスタのId-Vg特性がプロセスバラツキ,温度変動,電源電圧変動等により変動しても,3つの頂点(Va,I(Va)),(Vb,I(Vb)),(Vb,I(Va))からなる三角形TRの斜辺の傾きは常に理想的なトランスコンダクタンスgmになる。

【0079】

一方,バイアス回路内のトランジスタMaのドレイン電圧Vdは,次の式になる。

Vd=(I(Vb)-I(Va))×(N×Rs+Rs/2+Rs/2+R4)

そして,抵抗R4の抵抗値を変更しても,上記の条件α,βは満たされる。そこで,図14のように抵抗R4の抵抗値を可変制御して,バイアス回路のトランジスタMaと増幅トランジスタM0のドレイン電圧が等しくなるように制御している。これにより,トランジスタMa,Mbと増幅トランジスタM0のドレイン電圧とドレイン・ソース間電圧は全て等しく制御される。また,これらのトランジスタMa,Mb,M0のサイズを簡単のために等しいとすると,これらのトランジスタのId-Vg特性は,同じように変動する。

【0080】

そこで,バイアス回路の抵抗R2,R3間の接続ノードに生成される電圧Va,Vbの中間電圧(Va+Vb)/2を,バイアス電圧Vg,outとして,増幅トランジスタM0のゲートに印加すれば,増幅トランジスタM0のId-Vg特性におけるゲート電圧(Va+Vb)/2に対する傾きも理想的なトランスコンダクタンスgmに制御される。

【0081】

このように,第1の実施の形態におけるバイアス回路とそれを有するアンプ回路は,前述した従来の問題点(1)(2)(3)の全てを解決している。

【0082】

図14のアンプ回路において,トランジスタMa,Mb,M0のドレイン電圧Vdsを求める数式を,以下に示す。

トランジスタMa,Mbでは,各ドレイン電流は,次の通り。

【0083】

【数12】

【0084】

抵抗回路では,次の通り。

【0085】

【数13】

【0086】

そして,増幅トランジスタM0では,ドレイン電流とドレイン・ソース間電圧は次の通り。

【0087】

【数14】

【0088】

ここで,β=μCox(W/L),μは移動度,Coxはゲート容量,Wはゲート幅,Lはゲート長またはチャネル長,λはチャネル長に反比例する係数,RVARは可変抵抗R4の抵抗値,Rrはレプリカアンプの負荷抵抗値である。

【0089】

上記の式を解くことで,各トランジスタMa,Mb,M0のドレイン・ソース間電圧Vdsを物理パラメータにより表すことができる。

【0090】

上記の数12に示されるとおり,トランジスタMb,MaのId-Vg特性のドレイン電流は,ゲート電圧Vb,Vaの閾値電圧Vthを超えるオーバードライブ電圧(Vb-Vth),(Va-Vth)の二乗に(1+λVds)を乗算してそれぞれ求められる。従来のバイアス回路では,数式(3.1)(3.3)に示されるとおり,ドレイン・ソース間電圧Vdsに依存してドレイン電流Idが変動することが考慮されていないのに対して,本実施の形態ではそれが考慮されている。

【0091】

再度,図13のようにId-Vg特性が変化した場合の増幅トランジスタM0のドレイン電流I,トランスコンダクタンスgm,ドレイン・ソース間電圧Vdsについて説明する。増幅トランジスタM0のドレイン電流I,トランスコンダクタンスgm,ドレイン・ソース間電圧Vdsは,以下の数式のとおりである。

【0092】

【数15】

【0093】

そして,例えば,トランジスタ特性のβが108/100倍に変動したとする。その場合,バイアス回路は,トランスコンダクタンスgmを一定値に保つように動作し,例えば,((Va+Vb)/2-Vth)が10/12倍に,(1+λVds)が10/9倍に変動し,gmは108/100×10/12×10/9=1となり,変動が抑制される。この時に,増幅トランジスタのドレイン電流Iは,108/100×(10/12)2×10/9=10/12倍に減少し,負荷抵抗RLによる電圧降下が小さくなり,ドレイン電圧Vdsは上昇する。つまり,結論は前述の図13の説明と同じである。

【0094】

[第2の実施の形態]

図15は,第2の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。図15のバイアス回路BIASは,図9と同様の回路構成である。一方,図15の例では,レプリカアンプが設けられていない。ただし,図15のアンプ40は,ソース接地の増幅トランジスタM0と,そのトランジスタのドレインと電源電圧VDD1との間のインダクタンス素子LLを有する負荷回路とを有する。負荷回路は,上記のインダクタンス素子LLに加えて,抵抗素子RL,キャパシタ素子CLも並列に有していても良い。負荷回路がインダクタンス素子LLを有しているので,ドレインと電源電圧VDD1とは直流的に短絡されていると見なすことができ,ドレインの直流電圧は電源電圧VDD1と等しい。そして,ドレイン端子には,電源電圧VDD1の電位を中心にする増幅された交流信号が出力信号Voutとして生成される。

【0095】

そこで,図15のバイアス回路BIASは,アンプ40の電源電圧VDD1をオペレーションアンプ24に入力し,電源電圧VDD1とバイアス回路内のトランジスタMaのドレイン電圧とが等しくなるようにフィードバック回路を構成している。例えば,電源電圧VDD1の電圧が上昇すると,オペレーションアンプ24の出力電圧VFが上昇し,可変抵抗R4の抵抗値が高くなり,トランジスタMaのドレイン電圧も上昇して電源電圧VDD1と等しくなる。電源電圧VDD1の電圧が低下すると,上記と逆の動作によりトランジスタMaのドレイン電圧も低下し等しくなる。そして,出力信号Voutが生成される増幅トランジスタM0のドレイン端子の直流電圧は,電源電圧VDD1と同じ電位であるので,増幅トランジスタM0のドレイン電圧は,トランジスタMaのドレイン電圧と等しくなる。

【0096】

ただし,バイアス回路内のトランジスタMaのドレイン電圧がアンプ40の電源電圧VDD1と等しくなるので,バイアス回路BIAS内の電源電圧VDD2は,電源電圧VDD1より高い電圧にすることが必要になる。例えば,アンプ40の電源電圧VDD1を1.2Vにすると,バイアス回路の電源電圧VDD2は2.5Vにするのが望ましい。ただし,トランジスタの耐圧の制限から,バイアス回路BIAS内のトランジスタは,トランジスタMa,Mbを除いては電源電圧2.5V用のトランジスタにするのが望ましい。トランジスタMa,Mbは,アンプ40内の増幅トランジスタM0と同じ電源電圧1.2V用のサイズが小さいトランジスタにする。これにより,これらのトランジスタのId-Vg特性は同等になり,バイアス回路で生成したバイアス電圧Vg,outを増幅トランジスタM0のゲートに供給することで,所望のトランスコンダクタンスgmにすることができる。

【0097】

また,オペレーションアンプ22,24も高い電位の電源電圧VDD2とし,そのトランジスタは2.5V用の耐圧が高いトランジスタにすることが望ましい。

【0098】

図16,図17は,本実施の形態におけるアンプ回路の増幅トランジスタのトランスコンダクタンスgmと利得を示す図である。図16,17には,図5,6に示した27種類のバラツキ条件に対するトランスコンダクタンスgmと利得を示す白丸に,第1または第2の実施の形態のアンプ回路における増幅トランジスタのトランスコンダクタンスgmと利得を示す黒丸を追加して示している。これらの図からわかるとおり,27種類のバラツキの条件に対して,トランスコンダクタンスgmと利得の変動は,図5,6の白丸より大きく抑制されている。

【0099】

以上の通り,本実施の形態のバイアス回路と,バイアス回路を有するアンプ回路によれば,増幅トランジスタのトランスコンダクタンスgmのバラツキを抑制し,アンプ回路の利得のバラツキを抑制することができる。

【0100】

以上の実施の形態をまとめると,次の付記のとおりである。

【0101】

(付記1)

第1のドレイン電流を生成する第1のトランジスタと,

第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力されるバイアス回路。

【0102】

(付記2)

付記1において,

さらに,前記差電流を生成する差電流生成回路を有し,

前記第1,第2のトランジスタのソースは,第1の電圧に接続され,

前記第3のノードは前記第1および第2のノードの間にあり,前記第3の電圧は前記第1,第2の電圧の中間電圧であり,且つ,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定されているバイアス回路。

【0103】

(付記3)

付記2において,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

さらに,前記第1または第2のトランジスタのドレイン電圧を,前記バイアス電圧がゲートに供給される増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するバイアス回路。

【0104】

(付記4)

付記3において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が前記増幅トランジスタのドレイン電流より小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するバイアス回路。

【0105】

(付記5)

付記3において,

前記差電流生成回路は,電源電圧と前記第1および第2のトランジスタのドレインとの間にそれぞれ設けられた第1および第2の電流源トランジスタと,前記第1および第2のトランジスタのドレイン電圧の差電圧に応じた第2の出力電圧を生成し前記第1および第2の電流源トランジスタのゲートに供給するオペレーションアンプとを有するバイアス回路。

【0106】

(付記6)

ソースが基準電圧に接続され,ゲートに入力信号とバイアス電圧が供給され,電源電圧に接続された負荷回路がドレインに接続された増幅トランジスタと,

前記バイアス電圧を生成し,前記増幅トランジスタのゲートに前記バイアス電圧を供給するバイアス回路とを有し,

前記バイアス回路は,

ソースが前記基準電圧に接続され,第1のドレイン電流を生成する第1のトランジスタと,

ソースが前記基準電圧に接続され,第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノード間にある第3のノードの第3の電圧を,前記バイアス電圧として出力し,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定され,

さらに,前記第1,第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するアンプ回路。

【0107】

(付記7)

付記6において,

前記バイアス回路は,前記差電流を生成する差電流生成回路を有し,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするアンプ回路。

【0108】

(付記8)

付記7において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するアンプ回路。

【符号の説明】

【0109】

Ma,Mb:第1,第2のトランジスタ

30:抵抗回路

20:電流差分生成回路

【技術分野】

【0001】

本発明は,バイアス回路およびそれを有するアンプ回路に関する。

【背景技術】

【0002】

アンプ回路は,トランジスタなどの増幅素子とそれに接続される負荷素子とを有する。増幅素子としては,例えば,MOSトランジスタが,負荷素子としては,例えば,抵抗やインダクタなどが用いられる。

【0003】

ソース接地型のMOSトランジスタは,ソースが接地され,ゲートに入力信号が入力され,ドレインから出力信号が出力される。入力信号によるゲート電圧に応じてトランジスタのドレイン電流が変化し,そのドレイン電流は,トランジスタのドレイン電流・ゲート電圧特性(以下Id-Vg特性)の傾き(トランスコンダクタンスgm,相互コンダクタンスgm)に応じて入力信号を増幅した電流になる。さらに,ドレインに生成される出力電圧は,トランジスタのドレイン電流に負荷素子のインピーダンスを乗算した電圧である。したがって,トランスコンダクタンスをgm,負荷素子の抵抗値をRLとすると,アンプ回路の利得は,−gmRLになる。

【0004】

トランジスタのトランスコンダクタンスgmは,製造プロセスのバラツキ,温度変化,電源電圧変化により変化する。つまり,製造プロセスバラツキ,温度変化,電源電圧変化により,トランジスタのId-Vg特性が変化し,それに伴いその特性の傾きであるトランスコンダクタンスgmも変化する。このようなトランスコンダクタンスgmの変化は,アンプ回路の利得を変化させるので,好ましくない。

【0005】

利得のバラツキを抑制するために,トランスコンダクタンスgmを一定に保つように増幅素子であるトランジスタのゲートバイアス電圧を変化させるバイアス回路が提案されている。たとえば,以下の特許文献がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2009−147800号公報

【特許文献2】WO2008/050375

【特許文献3】特開平7−288437号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら,従来のバイアス回路は,MOSトランジスタのドレイン・ソース間電圧の変化に伴ってドレイン電流が変化することを考慮していない。従来の微細化されていないサイズのMOSトランジスタは,ドレイン・ソース間電圧の変化に対応するドレイン電流の変化は微小であるため,ドレイン・ソース間電圧の変化に伴うドレイン電流の変化を無視するバイアス回路でも,アンプ回路の増幅トランジスタのトランスコンダクタンスgmの変動を十分抑制することができた。

【0008】

しかし,近年における高速動作に対応したトランジスタは,チャネル長がより一層短くなる傾向になる。チャネル長が短くなるにしたがって,ドレイン・ソース間電圧の変動に対するドレイン電流の変動幅が大きくなる。そのため,従来のバイアス回路では,微細化されチャネル長が短くなった増幅トランジスタのトランスコンダクタンスgmの変動を十分に抑制することは困難である。

【0009】

そこで,本発明の目的は,アンプ回路内の増幅用トランジスタのトランスコンダクタンスの変動を抑制するバイアス回路と,それを有するアンプ回路とを提供することにある。

【課題を解決するための手段】

【0010】

バイアス回路の第1の側面は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

【発明の効果】

【0011】

第1の側面によれば,アンプ回路内の増幅用トランジスタのトランスコンダクタンスの変動を抑制することができる。

【図面の簡単な説明】

【0012】

【図1】アンプ回路の回路図である。

【図2】増幅トランジスタのゲート電圧・ドレイン電流特性を示す図である。

【図3】微細化トランジスタのId−Vg特性とgm−Vg特性を示す図である

【図4】従来のアンプ回路を示す回路図である。

【図5】図4の場合の27種類の条件に対するトランジスタのトランスコンダクタンスgmの変動を示す図である。

【図6】図4の場合の27種類の条件に対する利得の変動を示す図である。

【図7】27種類の条件を示す図である。

【図8】第1の実施の形態におけるバイアス回路の回路図である。

【図9】第1の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。

【図10】MOSトランジスタのId-Vg特性を示すグラフ図である。

【図11】図8のバイアス回路により生成される電圧Va,Vbとドレイン電流I(Va),I(Vb)との関係を示すグラフ図である。

【図12】トランジスタのId-Vg特性が,低い閾値電圧Vthを有する場合のバイアス回路の動作を示すグラフ図である。

【図13】トランジスタのId-Vg特性がドレイン電流が増大する特性になった場合のバイアス回路の動作を示すグラフ図である。

【図14】図9のアンプ回路の一例を示す回路図である。

【図15】第2の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。

【図16】本実施の形態におけるアンプ回路の増幅トランジスタのトランスコンダクタンスgmを示す図である。

【図17】本実施の形態におけるアンプ回路の利得を示す図である。

【発明を実施するための形態】

【0013】

図1は,アンプ回路の回路図である。アンプ回路は,ソースがグランドGNDなどの基準電圧に接続され,ゲートに入力信号Vinとバイアス電圧Vbiasとが供給されたNMOSトランジスタM0と,トランジスタM0のドレインと電源電圧VDDとの間に設けられた負荷抵抗素子RLと,直流のバイアス電圧Vbiasを生成するバイアス回路BIASとを有する。高周波の入力信号VinはカップリングキャパシタCinを介してゲートに供給される。つまり,入力信号Vinの交流成分だけがゲートに供給される。また,バイアス電圧Vbiasは高抵抗の給電抵抗Rbを介してゲートに供給される。給電抵抗Rbは高い抵抗値を有するので,ゲートからバイアス回路BIASへの電流は微少である。これにより,ゲート電圧は,直流のバイアス電圧Vbiasを中心とし,入力信号Vinの交流成分を有する信号になる。

【0014】

ソース接地のトランジスタM0は,ゲート電圧に応じたドレイン電流を生成し,ドレインに接続された出力端子に出力信号Voutが出力される。出力信号Voutは,ドレイン電流と負荷抵抗素子RLとの積に対応する振幅電圧を有する。

【0015】

図2は,増幅トランジスタのドレイン電流・ゲート電圧特性(Id−Vg特性)を示す図である。ゲート電圧Vgが閾値電圧Vthを超えるとドレイン電流Idが発生し,特性曲線10に示されるとおり,ドレイン電流Idは,ゲート電圧Vgの閾値電圧Vthを超えるオーバードライブ電圧(Vg−Vth)の二乗に比例して増加する。

【0016】

入力信号Vinの交流成分が直流のバイアス電圧Vbiasに重畳され,この電圧変化は,バイアス電圧VbiasにおけるId-Vg特性曲線10の傾きgmに応じて増幅されたドレイン電流Idの変化に変換される。このId-Vg特性曲線10の傾きがトランスコンダクタンスgmである。そして,生成されたドレイン電流Idを負荷抵抗素子RLの抵抗値に乗じた電圧振幅を有する出力信号Voutがドレインと負荷抵抗素子RLの接続ノードである出力端子に生成される。この出力信号Voutは入力信号Vinの逆相信号である。

【0017】

上記図2の説明から,アンプ回路の利得は,−gmRLであることが理解できる。そして,プロセスバラツキ,温度変化,電源電圧変化などによりゲート電圧・ドレイン電流特性が変動すると,トランジスタのトランスコンダクタンスgmが変動し,利得−gmRLの変動を招くことが理解できる。

【0018】

図3は,微細化トランジスタのId−Vg特性とgm−Vg特性を示す図である。この特性は,例えば90nm世代の1.2V電源の微細化トランジスタの特性である。図3のId−Vg特性には,プロセスバラツキなどで高速側(Fast),低速側(Slow),ティピカル(Typical)の特性を持つトランジスタそれぞれについて,さらに,4種類のドレイン電圧Vd(0.4,0.6,0.8,1.2V)に対する特性,合計で3×4=12の特性が示されている。高速側にばらついたトランジスタの特性(Fast)は,閾値電圧が低くドレイン電流Idが大きい。一方,低速側にばらついたトランジスタの特性(Slow)は,閾値電圧が高くドレイン電流Idが小さい。そして,ティピカルなトランジスタの特性(Typical)は,閾値電圧もドレイン電流も高速側と低速側の間の特性である。

【0019】

さらに,Id−Vg特性は,ドレイン電圧Vdが異なるとそれに応じて異なる。微細化された短チャネル長のトランジスタのドレイン電流は,飽和領域でも一定ではなく,ドレイン・ソース間電圧の増大に応じて増大することが知られている。このドレイン電流の増加の程度はチャネル長に反比例する。

【0020】

トランスコンダクタンスgmは,図2に示したとおりId−Vg特性である2次曲線の傾きである。したがって,gm−Vg特性はId−Vg特性を微分したものである。高速側(Fast)のほうが低いゲート電圧Vgでトランスコンダクタンスgmが立ち上がることが示されている。また,図示されていないが,高速側(Fast),低速側(Slow),ティピカル(Typical)のいずれにおいても,ドレイン電圧Vdが高いほど,トランスコンダクタンスgmが大きくなっている。このgm−Vg特性に示されるとおり,MOSトランジスタのトランスコンダクタンスgmを一定にするためには,プロセスバラツキ等の変動とドレイン電圧Vdの変動とに応じて,ゲート電圧Vgを変化させることが必要であることが理解できる。

【0021】

図4は,従来のアンプ回路を示す回路図である。図4には,ゲートバイアス電圧Vbiasを生成するバイアス回路BIASと,負荷抵抗RLがドレインに接続された増幅トランジスタM0とが示されている。バイアス電圧Vbiasは給電抵抗Rbを介して増幅トランジスタM0のゲートに供給され,入力信号VinはカップリングキャパシタCinを介してゲートに供給される。

【0022】

バイアス回路BIASは,トランジスタサイズW/L(Wはチャネル幅,Lはチャネル長)の比がK:1のトランジスタM1,M2と,トランジスタM1のソースとグランド間に接続された抵抗Rsと,両トランジスタM1,M2のドレインと電源電圧VDDとの間にそれぞれ設けられた電流ミラー回路10とを有する。電流ミラー回路10により両トランジスタM1,M2のドレイン電流は等しくなる。つまりIM1=IM2である。

【0023】

そして,以下に示すとおり,トランジスタM2のトランスコンダクタンスgmが一定に保たれるようなバイアス電圧Vbiasを生成する。そして,トランジスタM2,M0が共にソース接地型のトランジスタであるので,トランジスタM2のgmが一定であれば,同じバイアス電圧Vbiasがゲートに供給されている増幅用トランジスタM0のgmも一定であることを前提にしている。

【0024】

トランジスタM1,M2に流れる電流IM1,IM2は,つぎのとおりである

【0025】

【数1】

【0026】

【数2】

【0027】

【数3】

【0028】

【数4】

【0029】

【数5】

【0030】

ここで,μは移動度,Coxは単位面積当たりのゲートキャパシタ,WはトランジスタM2のゲート幅,KWはトランジスタM1のゲート幅,Lは両トランジスタM1,M2のゲート長,VxはトランジスタM1と抵抗Rsとの間のノードの電圧(トランジスタM1のソース電圧),Vthはトランジスタの閾値電圧である。

【0031】

数式(3.4)から数式(3.1)と数式(3.3)の右辺は等しいので,次の通りである。

【0032】

【数6】

【0033】

そして,数式(3.6)の両辺の平方根をとり,√Kで除算して整理すると,ソース電圧Vxは次の通りである。

【0034】

【数7】

【0035】

さらに,数式(3.4)から数式(3.2)と数式(3.3)の右辺も等しいので,

【0036】

【数8】

【0037】

数式(3.7)の電圧Vxを数式(3.8)に代入して(Vg-Vth)について整理すると,

【0038】

【数9】

【0039】

数式(3.9)を数式(3.3)に代入すると,

【0040】

【数10】

【0041】

数式(3.4)からIM1=IM2であるので,数式(3.10)を数式(3.5)に代入すると以下のとおりgmが得られる。

【0042】

【数11】

【0043】

つまり,トランジスタM2のトランスコンダクタンスgmは,一定の値である。

【0044】

しかしながら,図4のバイアス回路には,次の問題点がある。

(1)トランジスタのドレイン電流がドレイン・ソース間電圧Vdsに大きく依存することが考慮されていない。

(2)(1)のドレイン電流のドレイン・ソース間電圧Vds依存性があるにもかかわらず,トランジスタM1のソースとグランドとの間に抵抗Rsが設けられ,両トランジスタM1,M2のドレイン・ソース間電圧が異なる。そのためバイアス電圧Vbiasに対する両トランジスタM1,M2のトランスコンダクタンスgmは異なることになるが,上記の演算式はgmが等しいと見なしている。

(3)(1)のドレイン電流のドレイン・ソース間電圧Vds依存性があるにもかかわらず,増幅用トランジスタM0とバイアス回路のトランジスタM1,M2のドレイン電圧がそれぞれ独立しているので,トランジスタM2について所望のgmが得られるバイアス電圧Vbiasを生成しても,増幅用トランジスタM0について同じ所望のgmが得られる保証はない。

【0045】

上記の問題点(1)は,後述するドレイン電流の計算式に示されるとおり,正確なドレイン電流を算出するためには,数式(3.1)(3.3)に,(1+λVds)(λはチャネル長Lに反比例する定数)を乗算する必要があることを意味する。上記の数式(3.1)(3.3)はλ=0とした近似式である。しかし,微細化された短チャネルのトランジスタの場合は,λが大きくなり,ドレイン・ソース間電圧Vdsに依存してドレイン電流が変動する。そのため,図4の回路では,増幅用トランジスタM0のトランスコンダクタンスgmを所望の一定値に制御することができない。

【0046】

したがって,上記の3つの問題点は,トランジスタM0,M1,M2が短チャネルになるほど,そして電源電圧が低電圧になるほど顕著になり,増幅トランジスタM0を所望のgmに制御するバイアス電圧Vbiasの生成が困難になる。

【0047】

図5は,図4の場合の27種類の条件に対するトランジスタのトランスコンダクタンスgmの変動を示す図である。また,図6は,図4の場合の27種類の条件に対する利得の変動を示す図である。そして,図7は,27種類の条件を示す図である。27種類の条件は,Fast, Typical, Slowの3つのトランジスタ条件,3つの温度条件,そして3種類の電源電圧条件の組み合わせである。

【0048】

つまり,トランスコンダクタンスgmは,トランジスタ条件がFastなほど大きく,温度が低いほど大きく,電源電圧が高いほど大きくなる方向にばらついている。

【0049】

[第1の実施の形態]

図8は,第1の実施の形態におけるバイアス回路の回路図である。左側が概略回路図,右側が概略回路図の電流差分生成部を具体的に示す詳細回路図である。

【0050】

図8の左側に示したバイアス回路は,第1のドレイン電流I(Va)を生成する第1のNMOSトランジスタMaと,第2のドレイン電流I(Vb)を生成する第2のNMOSトランジスタMbとを有する。これらのトランジスタのゲート幅,チャネル長は,例えば同じとする。

【0051】

さらに,バイアス回路は,直列に接続された複数の抵抗素子R1-R4を有し,それら複数の抵抗素子に第2のドレイン電流I(Vb)と第1のドレイン電流I(Va)の差分電流dI(=I(Vb)-I(Va))が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧Va, Vb, Vg,outを生成する抵抗回路30を有する。そして,抵抗回路の第1のノードの第1の電圧Vaが第1のトランジスタMaのゲートに印加され,第2のノードの第2の電圧Vbが第2のトランジスタMbのゲートに印加され,第1,第2のノードと異なる第3のノードから第3の電圧Vg,outがバイアス電圧として出力される。このバイアス電圧Vg,outは,ソース接地の増幅トランジスタ(図8には図示せず)のゲートに給電抵抗を介して供給される。

【0052】

電流差分生成部20は,両トランジスタMa,Mbのドレインと電源電圧VDDとの間に設けられ,電流差分生成部の入力端子INb,INaに流れる両トランジスタMb,Maのドレイン電流I(Vb)とI(Va)の差分電流を出力端子dIに生成する回路である。そして,その出力端子dIの差分電流が抵抗回路30に流れる。

【0053】

図8の右側に示した詳細回路図には,この電流差分生成部20の回路例が示されている。電流差分生成部20は,両トランジスタMa,Mbのドレインに接続される入力端子INa,INbの電位の差動電圧を増幅するオペレーションアンプ22と,入力端子INa,INbと電源電圧VDDとの間にそれぞれ設けられたPMOSトランジスタMc,Mdとを有し,オペレーションアンプ22の出力電圧がPMOSトランジスタMc,Mdのゲートに印加される。これにより,トランジスタMc,Mdには等しい電流が生成され,また,入力端子INa,INbの電圧は等しくなるよう制御される。そして,出力端子dIから差分電流I(Vb)-I(Va)が抵抗回路30の直列接続された抵抗群R1-R4に流れるように構成される。

【0054】

抵抗回路30は,抵抗R1-R4がグランドと電流出力端子dIとの間に直列に接続され,差分電流dI(=I(Vb)-I(Va))が供給される。さらに,抵抗R2,R3の合計抵抗値Rsが,所望のトランスコンダクタンスgmの逆数(Rs=1/gm)と等しくなるように設定される。また,抵抗R2,R3は,例えば抵抗値Rsの1/2の抵抗値Rs/2を有する。そして,抵抗R2,R3の接続ノードから出力電圧Vg,outがバイアス電圧として出力される。抵抗R1は,設定抵抗RsのN倍(Nは正の任意の数)に設定され,また,抵抗R4は,任意の抵抗値を有する。

【0055】

上記の抵抗群R1,R2とR3,R4の抵抗比は任意の比率に変更することができる。ただし,R2とR3は等しい抵抗値を有することが望ましい。また,抵抗R4は,例えば抵抗値を0にすることもできる。

【0056】

図9は,第1の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。アンプ回路は,ゲートに入力される入力信号Vinを増幅し出力信号Voutを出力する増幅トランジスタを有するアンプ40と,それに並列に設けられたレプリカアンプ50と,レプリカアンプ50の出力電圧とバイアス回路内のトランジスタMaのドレイン電圧(入力端子INaの電圧)とを入力するオペレーションアンプ24とを有する。そして,オペレーションアンプ24の出力電圧VFをフィードバックし,その出力電圧VFで抵抗R4の抵抗を可変制御して,トランジスタMaのドレイン電圧とレプリカアンプ50のドレイン電圧とが等しくなるようにする。

【0057】

アンプ40とレプリカアンプ50は,同様の回路構成を有し,ソース接地のNMOSトランジスタと,それのドレインと電源電圧との間に設けた負荷回路とを有する。レプリカアンプ50の回路は,アンプ40の回路の増幅トランジスタや負荷回路より少ない電流を消費するように構成されるが,レプリカアンプ50内のトランジスタとアンプ40内のトランジスタとは同様の動作を行い,ドレイン電圧は互いに等しい。

【0058】

したがって,バイアス回路内のトランジスタMaのドレイン電圧とレプリカアンプ内のドレイン電圧とを等しくするように制御することで,間接的にアンプ40内のドレイン電圧もバイアス回路内のドレイン電圧と等しくすることができる。

【0059】

図9のようなレプリカアンプ50とオペレーションアンプ24の構成により,バイアス回路内のトランジスタMaのドレイン電圧と,アンプ40内の増幅トランジスタ(図示せず)のドレイン電圧(アンプ40の出力電圧Vout)とを等しくして,バイアス回路が生成したバイアス電圧Vg,outによりアンプ40内の増幅トランジスタのトランスコンダクタンスgmが所望の値に制御されるようにしている。

【0060】

以下,図8のバイアス回路と,図9のアンプ回路の動作について説明する。

【0061】

トランジスタMa,Mbは共にソースが基準電圧であるグランドGNDに接続され,オペレーションアンプ22により両トランジスタMa,Mbのドレイン電圧である入力端子INa,INbの電圧は等しくなるように制御される。したがって,両トランジスタMa,Mbのドレイン・ソース間電圧は等しい。一方,トランジスタMaのゲートには抵抗R1,R2の接続ノードの電圧Vaが印加され,トランジスタMbのゲートには抵抗R3,R4の接続ノードの電圧Vbが印加される。両電圧Va,VbはVa<Vbの関係にあるので,ゲート電圧・ドレイン電流の特性により,両トランジスタのドレイン電流I(Va),I(Vb)もI(Va)<I(Vb)になる。

【0062】

一方,オペレーションアンプ22の出力が共にゲートに印加されるトランジスタMc,Mdのドレイン電流は等しくなる。したがって,トランジスタMcにはトランジスタMdと同じ電流が流れ,トランジスタMdとMbは同じドレイン電流I(Vb)であるので,入力端子INaから抵抗回路30に流れる電流は,トランジスタMa,Mbのドレイン電流の差分電流I(Vb)-I(Va)である。

【0063】

そして,両トランジスタMa,Mbのゲートに印加される電圧Va,Vbは,所望とするトランスコンダクタンスgmの逆数に等しい抵抗Rs(=1/gm)に差分電流I(Vb)-I(Va)を乗じた電圧差を有し,出力されるバイアス電圧Vg,outは,電圧Va,Vbの中間電圧になる。

【0064】

つまり,図8のバイアス回路によれば,トランジスタMa,Mbのドレイン電圧が変動しても,また,トランジスタのId-Vg特性がFast,Slow,Typicalのいずれに変動しても,また温度や電源電圧が変動しても,抵抗回路30内の電圧Va,Vbと差分電流I(Vb)-I(Va)との間には,次の関係が維持される。

Vb-Va=Rs(I(Vb)-I(Va))

ここで,Rs=1/gmであるので,上記式を変形して,次の関係が導かれる。

gm=(I(Vb)-I(Va))/(Vb-Va) (4.1)

図10は,MOSトランジスタのId-Vg特性を示すグラフ図である。アンプ40内の増幅トランジスタのゲートにバイアス電圧Vg,outを印加すると,Id-Vg特性のゲート電圧Vg,outにおける傾きがトランスコンダクタンスgmになる。したがって,バイアス回路は,この傾きgmが変動しないバイアス電圧Vg,outを生成すれば良いことになる。

【0065】

図11は,図8のバイアス回路により生成される電圧Va,Vbとドレイン電流I(Va),I(Vb)との関係を示すグラフ図である。図11にもMOSトランジスタのId-Vg特性が示されている。そして,図8のバイアス回路は,前述の数式(4.1)の関係を常に満たすように動作する。従って,図11の3つの頂点(Va,I(Va)),(Vb,I(Vb)),(Vb,I(Va))からなる三角形TRの斜辺の傾きは,常に数式(4.1)となる。この三角形TRの斜辺の傾きは,Id-Vg特性がプロセスバラツキ,温度変動,電源電圧変動,そしてトランジスタのドレイン・ソース間電圧の変動によっても,抵抗Rsの逆数1/Rs=gmに維持される。このgmは,所望とするトランスコンダクタンスである。

【0066】

一方,Id-Vg特性によれば,ドレイン電流Idは,ゲート電圧Vgの閾値電圧Vthを超えるオーバードライブ電圧(Vg-Vth)の二乗に比例する。この二次曲線の特性から,ゲート電圧Va,Vbの中点(Va+Vb)/2での二次曲線の傾きは,数式(4.1)に示した2頂点(Va,I(Va)),(Vb,I(Vb))間の傾きと常に等しくなることは数学的に証明されている。

【0067】

その結果,電圧Va,Vbの中間電圧(Va+Vb)/2をゲートバイアス電圧Vg,outとして増幅トランジスタのゲートに供給することで,増幅トランジスタのトランスコンダクタンスは常に所望の値である1/Rs=gmに維持される。

【0068】

図11のグラフ図から理解されるとおり,抵抗R1の抵抗値NRsの倍数Nは,Id-Vg特性の閾値電圧Vthと,三角形TRの位置に応じて,適切な値が選択可能である。同じ斜面の傾きを有する三角形TRがId-Vg特性と一致する解は無数にある。しかし,この数Nを固定することで,Id-Vg特性内において三角形TRがどのような大きさでどのような位置に発生するかが決まる。発明者が検討したところ,数Nは8〜10程度が望ましい。

【0069】

図12は,トランジスタのId-Vg特性が,低い閾値電圧Vthを有する場合のバイアス回路の動作を示すグラフ図である。図12のId-Vg特性の閾値電圧Vthは,図11の閾値電圧Vthよりも低くなっている。ただし,バイアス回路内の抵抗回路30の抵抗R1:(R2+R3)=N:1の関係を変えることなく,三角形TRが,そのサイズが縮小されて,Id-Vg特性上に形成されている。つまり,電圧Va,Vbは小さくなり,その差電圧Vb-Vaも小さくなっている。ただし,三角形TRの斜辺の傾きは所望のトランスコンダクタンスgm(1/Rs)に維持されている。

【0070】

図13は,トランジスタのId-Vg特性がドレイン電流が増大する特性になった場合のバイアス回路の動作を示すグラフ図である。この場合でも,バイアス回路の動作により三角形TRの斜辺の傾きが所望のトランスコンダクタンスgmになる。つまり,Id-Vg特性がId-Vg(1)からId-Vg(2)に変動した場合,特性Id-Vg(1)の場合の三角形TR(1)は,差分電流(I(Vb)-I(Va))が低下し,トランジスタMa,Mbのゲートの電圧Va,Vbが低下し,ドレイン電流I(Vb),I(Va)が低下した新たな三角形TR(2)になる。これにより,増幅トランジスタのゲートのバイアス電圧Vg,outも低下し,そのドレイン電流Idも下がり,ドレイン電圧Vdは上昇すると考えられる。ただし,三角形TR(2)により増幅トランジスタのトランスコンダクタンスgmは一定に保たれる。

【0071】

図14は,図9のアンプ回路の一例を示す回路図である。図14の例では,アンプ40がソース接地のNMOSトランジスタである増幅トランジスタM0と,そのドレインと電源電圧VDDとの間に設けられた負荷抵抗RLとを有し,バイアス電圧が給電抵抗Rbを介して増幅トランジスタM0のゲートに接続されるとともに,入力信号VinがカップリングキャパシタCinを介して増幅トランジスタM0のゲートに接続され,増幅トランジスタM0と負荷抵抗RLとの接続ノードであるドレイン端子がアンプ40の出力信号Voutである。

【0072】

そして,レプリカアンプ50は,アンプ40の増幅トランジスタM0と同様に,ソース接地されたNMOSトランジスタMrと,それと電源電圧VDDとの間に設けられた負荷抵抗Rrとを有する。レプリカアンプ50のトランジスタMrのトランジスタサイズ(ゲート幅)は,増幅トランジスタM0のk倍(但し,レプリカ比k,k<1)と小さく,その分,レプリカアンプ50の負荷抵抗Rrは,増幅トランジスタM0の負荷抵抗RLの1/k倍(1/k>1)と大きく,それにより,レプリカアンプ50のドレイン電流は,アンプ40のドレイン電流のk倍(k<1)と小さくなっている。ただし,同じゲートバイアス電圧が供給されれば,両トランジスタMr,M0のドレイン電圧は等しくなる。

【0073】

また,バイアス回路内の可変抵抗R4は,CMOSトランジスタMe,Mfを並列に接続したトランスファーゲート回路であり,トランジスタMaのドレイン電圧とレプリカトランジスタMrのドレイン電圧との差分電圧を増幅するオペレーションアンプ24の出力電圧VFと,その出力電圧VFをトランジスタM10と負荷抵抗R10を有するインバータで反転され反転電圧VFxとが,PMOSトランジスタMeとNMOSトランジスタMfのゲートにそれぞれ印加されている。

【0074】

いま仮に,レプリカアンプ50のドレイン電圧が上昇したとすると,オペレーションアンプ24の出力電圧VFが増大し,反転電圧VFxが低下し,可変抵抗R4の抵抗が上昇し,トランジスタMaのドレイン端子INaの電圧も上昇する。レプリカアンプ50のドレイン電圧が低下したときは,上記の逆の動作によりトランジスタMaのドレイン電圧は低下する。その結果,レプリカアンプのドレイン電圧とバイアス回路内のトランジスタMaのドレイン電圧とが等しくなるように制御される。

【0075】

そして,増幅トランジスタM0のドレイン電圧とレプリカトランジスタMrのドレイン電圧とは同じ方向に変動するので,結局,増幅トランジスタM0のドレイン電圧は,バイアス回路内のトランジスタMa,Mbのドレイン電圧と等しくなる。

【0076】

このように,バイアス回路内のトランジスタMa,Mbと,アンプ40内の増幅トランジスタM0と,レプリカアンプ50内のレプリカトランジスタMrとは,全て,ソースが基準電圧であるグランドGNDに接続され,ドレイン電圧は等しく制御される。そして,バイアス回路の動作により,トランジスタMa,MbのId-Vg特性において所望のトランスコンダクタンスgmを生成するバイアス電圧Vg,outが,増幅トランジスタM0のゲートに供給される。その結果,増幅トランジスタM0のトランスコンダクタンスは,所望の値に維持される。

【0077】

再度,第1の実施の形態におけるバイアス回路の必要な条件を整理すると以下のとおりである。

条件α:(I(Vb)-I(Va))/(Vb-Va)=gm(1/Rs=gm)

条件β:N(Vb-Va)=Va

条件αは,抵抗R2,R3により成り立ち,条件βは,抵抗R1,R2,R3により成り立つ。

【0078】

条件αとβが満たされることで,図11,12,13で説明したとおり,トランジスタのId-Vg特性がプロセスバラツキ,温度変動,電源電圧変動等により変動しても,3つの頂点(Va,I(Va)),(Vb,I(Vb)),(Vb,I(Va))からなる三角形TRの斜辺の傾きは常に理想的なトランスコンダクタンスgmになる。

【0079】

一方,バイアス回路内のトランジスタMaのドレイン電圧Vdは,次の式になる。

Vd=(I(Vb)-I(Va))×(N×Rs+Rs/2+Rs/2+R4)

そして,抵抗R4の抵抗値を変更しても,上記の条件α,βは満たされる。そこで,図14のように抵抗R4の抵抗値を可変制御して,バイアス回路のトランジスタMaと増幅トランジスタM0のドレイン電圧が等しくなるように制御している。これにより,トランジスタMa,Mbと増幅トランジスタM0のドレイン電圧とドレイン・ソース間電圧は全て等しく制御される。また,これらのトランジスタMa,Mb,M0のサイズを簡単のために等しいとすると,これらのトランジスタのId-Vg特性は,同じように変動する。

【0080】

そこで,バイアス回路の抵抗R2,R3間の接続ノードに生成される電圧Va,Vbの中間電圧(Va+Vb)/2を,バイアス電圧Vg,outとして,増幅トランジスタM0のゲートに印加すれば,増幅トランジスタM0のId-Vg特性におけるゲート電圧(Va+Vb)/2に対する傾きも理想的なトランスコンダクタンスgmに制御される。

【0081】

このように,第1の実施の形態におけるバイアス回路とそれを有するアンプ回路は,前述した従来の問題点(1)(2)(3)の全てを解決している。

【0082】

図14のアンプ回路において,トランジスタMa,Mb,M0のドレイン電圧Vdsを求める数式を,以下に示す。

トランジスタMa,Mbでは,各ドレイン電流は,次の通り。

【0083】

【数12】

【0084】

抵抗回路では,次の通り。

【0085】

【数13】

【0086】

そして,増幅トランジスタM0では,ドレイン電流とドレイン・ソース間電圧は次の通り。

【0087】

【数14】

【0088】

ここで,β=μCox(W/L),μは移動度,Coxはゲート容量,Wはゲート幅,Lはゲート長またはチャネル長,λはチャネル長に反比例する係数,RVARは可変抵抗R4の抵抗値,Rrはレプリカアンプの負荷抵抗値である。

【0089】

上記の式を解くことで,各トランジスタMa,Mb,M0のドレイン・ソース間電圧Vdsを物理パラメータにより表すことができる。

【0090】

上記の数12に示されるとおり,トランジスタMb,MaのId-Vg特性のドレイン電流は,ゲート電圧Vb,Vaの閾値電圧Vthを超えるオーバードライブ電圧(Vb-Vth),(Va-Vth)の二乗に(1+λVds)を乗算してそれぞれ求められる。従来のバイアス回路では,数式(3.1)(3.3)に示されるとおり,ドレイン・ソース間電圧Vdsに依存してドレイン電流Idが変動することが考慮されていないのに対して,本実施の形態ではそれが考慮されている。

【0091】

再度,図13のようにId-Vg特性が変化した場合の増幅トランジスタM0のドレイン電流I,トランスコンダクタンスgm,ドレイン・ソース間電圧Vdsについて説明する。増幅トランジスタM0のドレイン電流I,トランスコンダクタンスgm,ドレイン・ソース間電圧Vdsは,以下の数式のとおりである。

【0092】

【数15】

【0093】

そして,例えば,トランジスタ特性のβが108/100倍に変動したとする。その場合,バイアス回路は,トランスコンダクタンスgmを一定値に保つように動作し,例えば,((Va+Vb)/2-Vth)が10/12倍に,(1+λVds)が10/9倍に変動し,gmは108/100×10/12×10/9=1となり,変動が抑制される。この時に,増幅トランジスタのドレイン電流Iは,108/100×(10/12)2×10/9=10/12倍に減少し,負荷抵抗RLによる電圧降下が小さくなり,ドレイン電圧Vdsは上昇する。つまり,結論は前述の図13の説明と同じである。

【0094】

[第2の実施の形態]

図15は,第2の実施の形態におけるバイアス回路を有するアンプ回路の回路図である。図15のバイアス回路BIASは,図9と同様の回路構成である。一方,図15の例では,レプリカアンプが設けられていない。ただし,図15のアンプ40は,ソース接地の増幅トランジスタM0と,そのトランジスタのドレインと電源電圧VDD1との間のインダクタンス素子LLを有する負荷回路とを有する。負荷回路は,上記のインダクタンス素子LLに加えて,抵抗素子RL,キャパシタ素子CLも並列に有していても良い。負荷回路がインダクタンス素子LLを有しているので,ドレインと電源電圧VDD1とは直流的に短絡されていると見なすことができ,ドレインの直流電圧は電源電圧VDD1と等しい。そして,ドレイン端子には,電源電圧VDD1の電位を中心にする増幅された交流信号が出力信号Voutとして生成される。

【0095】

そこで,図15のバイアス回路BIASは,アンプ40の電源電圧VDD1をオペレーションアンプ24に入力し,電源電圧VDD1とバイアス回路内のトランジスタMaのドレイン電圧とが等しくなるようにフィードバック回路を構成している。例えば,電源電圧VDD1の電圧が上昇すると,オペレーションアンプ24の出力電圧VFが上昇し,可変抵抗R4の抵抗値が高くなり,トランジスタMaのドレイン電圧も上昇して電源電圧VDD1と等しくなる。電源電圧VDD1の電圧が低下すると,上記と逆の動作によりトランジスタMaのドレイン電圧も低下し等しくなる。そして,出力信号Voutが生成される増幅トランジスタM0のドレイン端子の直流電圧は,電源電圧VDD1と同じ電位であるので,増幅トランジスタM0のドレイン電圧は,トランジスタMaのドレイン電圧と等しくなる。

【0096】

ただし,バイアス回路内のトランジスタMaのドレイン電圧がアンプ40の電源電圧VDD1と等しくなるので,バイアス回路BIAS内の電源電圧VDD2は,電源電圧VDD1より高い電圧にすることが必要になる。例えば,アンプ40の電源電圧VDD1を1.2Vにすると,バイアス回路の電源電圧VDD2は2.5Vにするのが望ましい。ただし,トランジスタの耐圧の制限から,バイアス回路BIAS内のトランジスタは,トランジスタMa,Mbを除いては電源電圧2.5V用のトランジスタにするのが望ましい。トランジスタMa,Mbは,アンプ40内の増幅トランジスタM0と同じ電源電圧1.2V用のサイズが小さいトランジスタにする。これにより,これらのトランジスタのId-Vg特性は同等になり,バイアス回路で生成したバイアス電圧Vg,outを増幅トランジスタM0のゲートに供給することで,所望のトランスコンダクタンスgmにすることができる。

【0097】

また,オペレーションアンプ22,24も高い電位の電源電圧VDD2とし,そのトランジスタは2.5V用の耐圧が高いトランジスタにすることが望ましい。

【0098】

図16,図17は,本実施の形態におけるアンプ回路の増幅トランジスタのトランスコンダクタンスgmと利得を示す図である。図16,17には,図5,6に示した27種類のバラツキ条件に対するトランスコンダクタンスgmと利得を示す白丸に,第1または第2の実施の形態のアンプ回路における増幅トランジスタのトランスコンダクタンスgmと利得を示す黒丸を追加して示している。これらの図からわかるとおり,27種類のバラツキの条件に対して,トランスコンダクタンスgmと利得の変動は,図5,6の白丸より大きく抑制されている。

【0099】

以上の通り,本実施の形態のバイアス回路と,バイアス回路を有するアンプ回路によれば,増幅トランジスタのトランスコンダクタンスgmのバラツキを抑制し,アンプ回路の利得のバラツキを抑制することができる。

【0100】

以上の実施の形態をまとめると,次の付記のとおりである。

【0101】

(付記1)

第1のドレイン電流を生成する第1のトランジスタと,

第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力されるバイアス回路。

【0102】

(付記2)

付記1において,

さらに,前記差電流を生成する差電流生成回路を有し,

前記第1,第2のトランジスタのソースは,第1の電圧に接続され,

前記第3のノードは前記第1および第2のノードの間にあり,前記第3の電圧は前記第1,第2の電圧の中間電圧であり,且つ,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定されているバイアス回路。

【0103】

(付記3)

付記2において,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

さらに,前記第1または第2のトランジスタのドレイン電圧を,前記バイアス電圧がゲートに供給される増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するバイアス回路。

【0104】

(付記4)

付記3において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が前記増幅トランジスタのドレイン電流より小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するバイアス回路。

【0105】

(付記5)

付記3において,

前記差電流生成回路は,電源電圧と前記第1および第2のトランジスタのドレインとの間にそれぞれ設けられた第1および第2の電流源トランジスタと,前記第1および第2のトランジスタのドレイン電圧の差電圧に応じた第2の出力電圧を生成し前記第1および第2の電流源トランジスタのゲートに供給するオペレーションアンプとを有するバイアス回路。

【0106】

(付記6)

ソースが基準電圧に接続され,ゲートに入力信号とバイアス電圧が供給され,電源電圧に接続された負荷回路がドレインに接続された増幅トランジスタと,

前記バイアス電圧を生成し,前記増幅トランジスタのゲートに前記バイアス電圧を供給するバイアス回路とを有し,

前記バイアス回路は,

ソースが前記基準電圧に接続され,第1のドレイン電流を生成する第1のトランジスタと,

ソースが前記基準電圧に接続され,第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノード間にある第3のノードの第3の電圧を,前記バイアス電圧として出力し,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定され,

さらに,前記第1,第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するアンプ回路。

【0107】

(付記7)

付記6において,

前記バイアス回路は,前記差電流を生成する差電流生成回路を有し,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするアンプ回路。

【0108】

(付記8)

付記7において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するアンプ回路。

【符号の説明】

【0109】

Ma,Mb:第1,第2のトランジスタ

30:抵抗回路

20:電流差分生成回路

【特許請求の範囲】

【請求項1】

第1のドレイン電流を生成する第1のトランジスタと,

第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力されるバイアス回路。

【請求項2】

請求項1において,

さらに,前記差電流を生成する差電流生成回路を有し,

前記第1,第2のトランジスタのソースは,第1の電圧に接続され,

前記第3のノードは前記第1および第2のノードの間にあり,前記第3の電圧は前記第1,第2の電圧の中間電圧であり,且つ,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定されているバイアス回路。

【請求項3】

請求項2において,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

さらに,前記第1または第2のトランジスタのドレイン電圧を,前記バイアス電圧がゲートに供給される増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するバイアス回路。

【請求項4】

請求項3において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が前記増幅トランジスタのドレイン電流より小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するバイアス回路。

【請求項5】

請求項3において,

前記差電流生成回路は,電源電圧と前記第1および第2のトランジスタのドレインとの間にそれぞれ設けられた第1および第2の電流源トランジスタと,前記第1および第2のトランジスタのドレイン電圧の差電圧に応じた第2の出力電圧を生成し前記第1および第2の電流源トランジスタのゲートに供給するオペレーションアンプとを有するバイアス回路。

【請求項6】

ソースが基準電圧に接続され,ゲートに入力信号とバイアス電圧が供給され,電源電圧に接続された負荷回路がドレインに接続された増幅トランジスタと,

前記バイアス電圧を生成し,前記増幅トランジスタのゲートに前記バイアス電圧を供給するバイアス回路とを有し,

前記バイアス回路は,

ソースが前記基準電圧に接続され,第1のドレイン電流を生成する第1のトランジスタと,

ソースが前記基準電圧に接続され,第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノード間にある第3のノードの第3の電圧を,前記バイアス電圧として出力し,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定され,

さらに,前記第1,第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するアンプ回路。

【請求項7】

請求項6において,

前記バイアス回路は,前記差電流を生成する差電流生成回路を有し,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするアンプ回路。

【請求項1】

第1のドレイン電流を生成する第1のトランジスタと,

第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力されるバイアス回路。

【請求項2】

請求項1において,

さらに,前記差電流を生成する差電流生成回路を有し,

前記第1,第2のトランジスタのソースは,第1の電圧に接続され,

前記第3のノードは前記第1および第2のノードの間にあり,前記第3の電圧は前記第1,第2の電圧の中間電圧であり,且つ,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定されているバイアス回路。

【請求項3】

請求項2において,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

さらに,前記第1または第2のトランジスタのドレイン電圧を,前記バイアス電圧がゲートに供給される増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するバイアス回路。

【請求項4】

請求項3において,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧と,前記増幅トランジスタのドレイン電圧または前記増幅トランジスタと同じ回路構造を有しドレイン電流が前記増幅トランジスタのドレイン電流より小さいレプリカトランジスタのドレイン電圧との差電圧に応じて出力電圧を生成するオペレーションアンプと,前記第2のノードと前記第1または第2のトランジスタのドレイン端子との間に設けられ前記オペレーションアンプの出力電圧に応じて抵抗値が可変制御される可変抵抗素子とを有するバイアス回路。

【請求項5】

請求項3において,

前記差電流生成回路は,電源電圧と前記第1および第2のトランジスタのドレインとの間にそれぞれ設けられた第1および第2の電流源トランジスタと,前記第1および第2のトランジスタのドレイン電圧の差電圧に応じた第2の出力電圧を生成し前記第1および第2の電流源トランジスタのゲートに供給するオペレーションアンプとを有するバイアス回路。

【請求項6】

ソースが基準電圧に接続され,ゲートに入力信号とバイアス電圧が供給され,電源電圧に接続された負荷回路がドレインに接続された増幅トランジスタと,

前記バイアス電圧を生成し,前記増幅トランジスタのゲートに前記バイアス電圧を供給するバイアス回路とを有し,

前記バイアス回路は,

ソースが前記基準電圧に接続され,第1のドレイン電流を生成する第1のトランジスタと,

ソースが前記基準電圧に接続され,第2のドレイン電流を生成する第2のトランジスタと,

直列に接続された複数の抵抗素子を有し,前記複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,前記複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有し,

前記抵抗回路の第1のノードの第1の電圧が前記第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が前記第2のトランジスタのゲートに印加され,前記第1,第2のノード間にある第3のノードの第3の電圧を,前記バイアス電圧として出力し,前記第1および第2のノード間の抵抗値は所望のトランスコンダクタンスの逆数に設定され,

さらに,前記第1,第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするドレイン電圧制御回路を有するアンプ回路。

【請求項7】

請求項6において,

前記バイアス回路は,前記差電流を生成する差電流生成回路を有し,

前記差電流生成回路は,前記第1,第2のトランジスタのドレイン電圧を等しくするように制御し,

前記ドレイン電圧制御回路は,前記第1または第2のトランジスタのドレイン電圧を前記増幅トランジスタのドレイン電圧と等しくするアンプ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−93733(P2013−93733A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−234411(P2011−234411)

【出願日】平成23年10月25日(2011.10.25)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月25日(2011.10.25)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]