バス回路

【課題】バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供すること。

【解決手段】入力信号と制御信号がそれぞれ入力される複数の入力部と、複数の入力部の出力を互いに接続したバスと、バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部とを備えるバス回路である。バス回路は、バスがフローティング状態となる場合に、出力部のラッチ回路に保持された信号をバスに出力する。

【解決手段】入力信号と制御信号がそれぞれ入力される複数の入力部と、複数の入力部の出力を互いに接続したバスと、バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部とを備えるバス回路である。バス回路は、バスがフローティング状態となる場合に、出力部のラッチ回路に保持された信号をバスに出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はバス回路に関し、特にバスがフローティング状態となるのを防止するバス回路に関する。

【背景技術】

【0002】

スリーステートバッファ(トライステートバッファ)を含む入力部と、バスとを備えるバス回路において、いずれの入力部からもバスに出力されない場合がある。すなわち、すべての入力部からハイインピーダンスが出力されている状態である。このとき、バスは電気的に不安定な状態(フローティング状態)となる。

【0003】

例えば、CMOS回路がバスに接続されている場合、バスのフローティング状態が続くと、CMOS回路に貫通電流が流れる場合がある。すなわち、バスのフローティング状態は、消費電力の増大や、CMOS回路の破壊を招く恐れがある。そのため、すべての入力部からハイインピーダンスが出力されている場合であっても、バスがフローティング状態とならないよう、バスをH状態またはL状態に設定しておく必要がある。

【0004】

特許文献1には、中間電位検出回路を備えるスリーステートバス電位固定回路に関する技術が開示されている。これによると、バス電位固定用に専用のDラッチを設け、直前までバスに載っていたデータをDラッチに保持する。バスがフローティング状態となる場合には保持されたデータをバスに返す。そのため、バスがフローティング状態となるのを回避するのに加え、バス上の電位の変化が最小限となり、消費電力の削減を図ることができる。

【0005】

特許文献2では、バス上にデータ保持回路を設けるバス回路に関する技術について開示されている。これによると、バス上に設けられた信号保持回路でバス出力信号を保持する。バスがフローティング状態となる場合には、保持されたデータによりバス出力信号が保持される。したがって、バスがフローティング状態となるのを回避することができる。

【0006】

特許文献3には、バスにラッチ機能を持たせる技術が開示されている。これによると、ラッチ回路を省略できるためバス回路のハードウェア量が削減し、データ転送の高速化を図ることができる。

【0007】

特許文献4には、プルアップまたはプルダウン抵抗器を用いないバス電位安定化回路に関する技術が開示されている。これによると、複数の回路ユニットのいずれもが選択されない非通信時には固定データ出力部が選択され、主回路ユニットの入力回路に強制的に固定データを入力する。これにより、バスがフローティング状態となるのを回避することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−048407号公報

【特許文献2】特開平05−216818号公報

【特許文献3】特開2008−177712号公報

【特許文献4】特開2002−076876号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1及び特許文献2に開示された技術では、既存の回路とは別にデータ保持回路を設けている。そのため、バス配線容量を増加させてしまい、バスのデータ転送性能の悪化を招くことや、バス回路の面積を増大させてしまうという問題がある。

【0010】

また、図6に関連するバス回路の構成例を示す。この回路において、データ保持回路6はバス50上に設けられている。すなわち、既存の回路とは別にデータ保持回路6を設けている。そのため、バス配線容量を増加させてしまい、バスのデータ転送性能の悪化を招くことや、バス回路の面積を増大させてしまうという問題がある。

【0011】

本発明は、このような問題点を解決するためになされたものであり、バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、入力端子からそれぞれ入力信号が入力され、制御入力端子からそれぞれ制御信号が入力される複数の入力部と、前記複数の入力部の出力を互いに接続したバスと、前記バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部、とを備え、前記バスがフローティング状態である場合に、前記出力部のラッチ回路に保持された信号を前記バスに出力する、バス回路である。

【発明の効果】

【0013】

本発明により、バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供することができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1にかかるバス回路の図である。

【図2】実施の形態1にかかる他のバス回路の図である。

【図3】実施の形態1にかかるタイムチャートの図である。

【図4】実施の形態2にかかるバス回路の図である。

【図5】実施の形態2にかかるラッチ回路の図である。

【図6】関連するバス回路の図である。

【発明を実施するための形態】

【0015】

実施の形態1.

以下、図面を参照して本実施の形態について説明する。

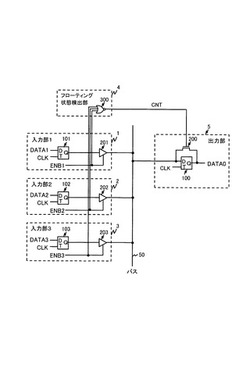

図1は、本実施の形態におけるバス回路の回路図を示したものである。

バス回路は、入力部1、2、3と、バス50と、出力部5を備える。ここで、バス50は、信号の入力元となる入力部1、入力部2、入力部3と、それぞれ接続している。また、バス50は出力部5と接続している。

また図2は、本実施の形態における他のバス回路の回路図を示したものである。このバス回路は図1で示したバス回路に加え、フローティング状態検出部4を備える。また、出力部5においてスイッチ部200を備える。フローティング状態検出部4は、信号の入力元となる入力部1、入力部2、入力部3とそれぞれ接続している。また、フローティング状態検出部4は、信号の出力先となる出力部5と接続している。

【0016】

入力部1は、ラッチ回路101と、ラッチ回路101の出力を入力とし、ENB1を制御信号として入力するスリーステートバッファ201とを備えている。

【0017】

ラッチ回路101は、入力信号DATA1と、クロック信号CLKが入力される。そして、ラッチ回路101は、入力信号DATA1に基づく信号をスリーステートバッファ201に出力する。

典型的には、入力信号DATA1は、任意に定めた"1"または"0"の信号である。また、クロック信号CLKは、一定時間ごとにH状態とL状態が繰り返される信号である。

ラッチ回路101はクロック信号CLKにより、ラッチ回路101において入力信号DATA1をラッチするタイミングや、ラッチ回路101から出力信号を出力するタイミングを制御する。なお、ラッチ回路101はクロック信号CLKがL状態の場合に、入力信号DATA1をラッチするものとする。

【0018】

スリーステートバッファ201は、ラッチ回路101から出力された信号と、制御信号ENB1が入力される。そして、スリーステートバッファ201は、ラッチ回路101から出力された信号に基づいて、バス50にバス信号を出力する。

ここで、スリーステートバッファ201は、典型的には、制御信号ENB1が"1"の場合にはON状態となり、バス出力信号をバス50に出力する。すなわち、制御信号ENB1が"1"の場合に、入力信号DATA1に基づく信号が、バス50に送出される。

また、制御信号ENB1が"0"の場合には、スリーステートバッファ201はOFF状態となり、スリーステートバッファ201は、ハイインピーダンスをバス50に出力する。ハイインピーダンスとは、電気的に"0"でも"1"でもない状態であり、バス50上の信号に影響を与えないように電気的にバスから切り離された状態である。

【0019】

ここで、入力部2及び、入力部3も、入力部1と同様に構成され、入力部1と同様に動作する。但し、入力部の数は限定されない。

【0020】

ここで、各入力部1、2、3のスリーステートバッファ201、202、203の制御信号ENB1、ENB2、ENB3はCLKに同期している。また、スリーステートバッファ201、202、203は排他的に制御されている。すなわち、同時に2つ以上のENBが "1"とならない。したがって、入力部1、入力部2及び入力部3から送出される信号が、バス50上で衝突することはない。

したがって、バス回路の通常動作時は、必ずいずれか1つの入力部が選ばれ、バス50を通過する。すなわち、いずれか1つの入力信号DATAに基づくバス信号がバス50に入力され、バス50はバス信号に基づく電位に設定される。

【0021】

入力部1、入力部2及び入力部3のすべてが電気的にバス50から切り離された場合、制御信号ENB1、ENB2及びENB3が、全て"0"であるディスイネーブル状態となる。すなわち、各入力部1、2、3からの入力信号DATA1、DATA2、DATA3がバス50に出力されない状態であり、このとき、全てのスリーステートバッファからはハイインピーダンスがバス50に出力され、バス50はフローティング状態となる。

【0022】

フローティング状態検出部4は、NOR回路300を備える。NOR回路300は、入力部1からの制御信号ENB1と、入力部2からの制御信号ENB2と入力部3からの制御信号ENB3を入力する。また、NOR回路300は制御信号ENB1、ENB2、ENB3に基づいて出力部制御信号CNTを出力する。

全ての制御信号ENB1、ENB2及びENB3が"0"のディスイネーブル状態となった場合には出力部制御信号CNTは"1"となり、出力部制御信号CNTがフローティング状態検出部4から出力部5に出力される。

【0023】

出力部5は、ラッチ回路100と、スイッチ部200を備える。スイッチ部200は、例えばトランスファーゲート回路である。

ラッチ回路100は、バス回路の通常動作時においてバス50を通過したバス信号と、クロック信号CLKが入力される。そして、ラッチ回路100は、バス信号に基づく出力信号DATA0を出力する。典型的には、ラッチ回路100はバス信号を、クロック信号CLKがH状態の場合にラッチする。

【0024】

例えば、入力部1が選択された場合には、制御信号ENB1は"1"となる。これにより、ラッチ回路101に保持されている入力信号DATA1に基づく信号が、スリーステートバッファ201を介してバス50に送出され、さらに、バス50から出力部5のラッチ回路100に送出される。

なお、選択されなかった入力部2、及び入力部3における制御信号ENB2、ENB3は"0"となり、スリーステートバッファ202、203からバス50にハイインピーダンスが送出される。その結果、入力部2及び入力部3は、電気的にバス50から切り離される。

【0025】

出力部5は、スイッチ部200を介して、ラッチ回路100の出力部と入力部を接続している。

出力部5のスイッチ部200は、出力部制御信号CNTによって制御される。スイッチ部200は、出力部制御信号CNTが"0"の場合に、OFF状態となり閉ざされる。すなわち、スイッチ部200は、いずれかの入力部からバス50にバス信号が入力されている場合には、OFF状態である。

一方、出力部制御信号CNTが"1"の場合にはON状態となり、ラッチ回路100に保持されている信号がバス50上に送られる。ここで、CNTが"1"の場合とは、入力部からバス50にバス信号が入力されていない状態である。この状態では、スイッチ部200がON状態となることにより、ラッチ回路100に保持されている信号がバス50上に送られる。これにより、バス50はラッチ回路100から送出された信号に対応して、直前までの電位状態を維持する。これにより、バス50がフローティング状態となるのは回避される。

【0026】

図3に、本実施形態におけるバス回路の動作のタイムチャートを示す。ここで、図2及び図3を参照して、動作の説明を行う。

【0027】

図3において、時刻T0〜T2の区間は、制御信号ENB1は"1"、制御信号ENB2及びENB3は"0"となっている。したがって、入力部1が選択されており、入力信号DATA1に基づいてラッチ回路101に保持された信号は、スリーステートバッファ201を介し、バス信号としてバス50に入力される。

時刻T0〜T1において、ラッチ回路101に保持された信号は"0"であり、バス50に与えられている信号は"0"となる。また、時刻T1〜T2において、ラッチ回路101に保持された信号は"1"であり、時刻T1のタイミングでバス50に与えられている信号は"0"から"1"に変更される。

【0028】

なお、スリーステートバッファ202及び203において、制御信号ENB2及びENB3が"0"である。このため、スリーステートバッファ202及び203からは、ハイインピーダンスがバス50へ出力されている。すなわち、入力部2及び入力部3はバス50から電気的に切り離された状態である。

【0029】

バス50上の電位は、時刻T2において、スリーステートバッファ201から出力された"1"に対応する電位に設定される。また、信号"1"がラッチ回路100に保持される。

【0030】

時刻T2〜T5の区間では、時刻T2において制御信号ENB1が"1"から"0"に変更される。このとき、ENB2、ENB3も"0"のまま変更されず、全ての制御信号が"0"であるディスイネーブル状態であり、バス50は未使用状態となる。すなわち、バス50がフローティング状態となる。

【0031】

このとき、スリーステートバッファ201、202、203の出力はいずれもハイインピーダンスとなり、NOR回路300の出力部制御信号CNTは"1"となる。したがって、出力部5のスイッチ部200がON状態となり、ラッチ回路100に保持されている信号がバス50に戻される。

その結果、バス50上の電位は"1"に対応する電位に設定され、フローティング状態が回避される。

ここでラッチ回路100に保持され、バス50に戻される"1"は、CNTが"1"となる時刻T2まで、バス50に保持されていた値である。バス50は、この値に対応する電位を維持することにより、その直前までとの電位の変化を抑えることができる。

【0032】

次に時刻T5〜T7の区間における動作を説明する。

時刻T5では、再び制御信号ENB1が"1"となるため、入力信号DATA1に基づきラッチ回路101に保持されている信号"0"が、スリーステートバッファ201を介してバス50に送出される。この信号は、時刻T6においてラッチ回路100に保持される。

【0033】

時刻T6では時刻T2と同様に制御信号ENB1が"1"から"0"に変更される。また、制御信号ENB2及びENB3も"0"のまま変更されていない。したがって、全ての制御信号が"0"であるディスイネーブル状態である。

そのため、スリーステートバッファ201、202、203の出力はいずれもハイインピーダンスとなる。また、フローティング状態検出部4のNOR回路300の出力部制御信号CNTは"1"となる。

CNTが"1"となることにより、出力部5のスイッチ部200がONされ、ラッチ回路100に保持されている信号がバス50に戻される。これにより、時刻T6〜T7におけるバス50のバス信号は"0"となる。ここで、ラッチ回路100に保持されていた値"0"は、CNT="1"となる時刻T6まで、バスに載っていた値である。バス50は、この信号に対応する電位を維持することにより、その直前までとの電位の変化を抑えることができる。

【0034】

本実施形態によれば、すべての入力部からのバス50にバス信号が入力されない場合に、出力部5に保持されている信号をバス50に戻すことにより、バス50がフローティング状態となるのを回避することができる。

【0035】

また、本実施の形態によれば、バス回路の消費電力を削減することができる。これは、バス50がフローティング状態となるのを回避するために与えられる信号は、固定値ではないからである。すなわち、バス50がフローティング状態になる直前の値を使用しており、バス50の電位の変化を最小限に抑えることができるためである。

バス配線容量の増加を抑え、バス回路のデータ転送性能の悪化を防ぐことができる。また、バス回路の面積を削減できる。これは、バス50がフローティング状態となるのを回避するために使用する信号に、既存の回路に保持されている信号を使うことで、バス50に信号保持用の回路を設ける必要がないためである。

【0036】

なお、本実施形態では、バスのビット幅を1ビットとして表わしているが、一般的なデータを扱う場合は、複数ビットのバス構成となる。たとえば8バイトデータを扱う場合には、64ビット分を束ねたデータバス構成となるため上記の効果は大きくなる。更にこのデータバスを、幾つか組み合わせてクロスバを構成する場合には、クロスバの規模に比例して効果も大きくなる。

【0037】

実施の形態2.

次に、他の実施の形態について、図面を参照して詳細に説明する。図4は、本発明の他の実施の形態にかかるバス回路を示したものである。

図4に示すバス回路において、出力部5以外の部分は、基本的に実施の形態1の図2で示した回路と同様である。なお、本実施の形態にかかるバス回路において、出力部5はスイッチ部200を備えない。また、出力部5は、ラッチ回路100の出力部と入力部を接続していない。

ここで、実施の形態1で示した符号と同一の符号は、同一または相当部分を示しており、説明を省略する。

【0038】

図5にラッチ回路100の構造を示す。

図5に示すように、ラッチ回路100は、インバータ回路56、57、59、60、61及びOR回路58を備える。

インバータ回路56は、クロック信号CLKを入力する。また、インバータ回路57は、インバータ回路56の出力信号を入力する。ここで、インバータ回路56の出力信号をCKB、インバータ回路57の出力信号をCKTとする。

インバータ回路61は、クロック信号CLKを入力し、クロック信号CLKを反転させる。インバータ回路61は、反転したクロック信号CLKをOR回路58に出力する。

OR回路58は、出力部制御信号CNTと、インバータ回路61の出力信号を入力する。

インバータ回路59は、OR回路58の出力信号を入力する。また、インバータ回路60は、インバータ回路59の出力信号を入力する。ここで、インバータ回路59の出力信号をCTB、インバータ回路60の出力信号をCTTとする。

【0039】

また、ラッチ回路100は、第1のスイッチ部51と、第2のスイッチ部54と、インバータ回路52、53、55を備える。ここで、第1のスイッチ部51及び第2のスイッチ部54は、例えばトランスファーゲート回路である。

第1のスイッチ部51、インバータ回路53及びインバータ回路55により、信号をラッチする。第1のスイッチ部51は、CKT及びCKBにより制御される。いずれかの入力部1、2、3からバス50にバス信号の入力がある場合には、バス50を介して、ラッチ回路100にバス信号がラッチされる。

【0040】

インバータ回路52は、バス50からの入力に基づく信号を、ラッチ回路100から出力信号DATA0として出力する。インバータ回路52は、ラッチ回路100の入力部と信号をラッチする回路部とを接続しているノードと、出力部との間に設けられている。なお、信号をラッチする回路部とは、第1のスイッチ部51、インバータ回路53及びインバータ回路55を備えた回路部である。

【0041】

第2のスイッチ部54は、一方の端部がバス50と接続されている。また、第2のスイッチ部54は、CTB及びCTTにより制御される。これにより、出力部制御信号CNTが"1"の場合に、これにより、第2のスイッチ部54が常に開かれることとなる。

したがって、バス50がフローティング状態となった場合にラッチ回路100に保持していたデータをバス50に戻すことができ、バス50のフローティング状態を防止することができる。

【0042】

本実施態様によれば、実施の形態1におけるスイッチ部200と、スイッチ部200を介してラッチ回路100の出力部と入力部を接続する回路を設ける必要がなく、バス配線容量を更に削減することができる。

【0043】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0044】

1 入力部

2 入力部

3 入力部

4 フローティング状態検出部

5 出力部

6 データ保持回路

50 バス

51 第1のスイッチ部

52 インバータ回路

53 インバータ回路

54 第2のスイッチ部

55 インバータ回路

56 インバータ回路

57 インバータ回路

58 OR回路

59 インバータ回路

60 インバータ回路

61 インバータ回路

100 ラッチ回路

101 ラッチ回路

102 ラッチ回路

103 ラッチ回路

200 スイッチ部

201 スリーステートバッファ

202 スリーステートバッファ

203 スリーステートバッファ

300 NOR回路

500 スイッチ部

501 インバータ回路

502 インバータ回路

【技術分野】

【0001】

本発明はバス回路に関し、特にバスがフローティング状態となるのを防止するバス回路に関する。

【背景技術】

【0002】

スリーステートバッファ(トライステートバッファ)を含む入力部と、バスとを備えるバス回路において、いずれの入力部からもバスに出力されない場合がある。すなわち、すべての入力部からハイインピーダンスが出力されている状態である。このとき、バスは電気的に不安定な状態(フローティング状態)となる。

【0003】

例えば、CMOS回路がバスに接続されている場合、バスのフローティング状態が続くと、CMOS回路に貫通電流が流れる場合がある。すなわち、バスのフローティング状態は、消費電力の増大や、CMOS回路の破壊を招く恐れがある。そのため、すべての入力部からハイインピーダンスが出力されている場合であっても、バスがフローティング状態とならないよう、バスをH状態またはL状態に設定しておく必要がある。

【0004】

特許文献1には、中間電位検出回路を備えるスリーステートバス電位固定回路に関する技術が開示されている。これによると、バス電位固定用に専用のDラッチを設け、直前までバスに載っていたデータをDラッチに保持する。バスがフローティング状態となる場合には保持されたデータをバスに返す。そのため、バスがフローティング状態となるのを回避するのに加え、バス上の電位の変化が最小限となり、消費電力の削減を図ることができる。

【0005】

特許文献2では、バス上にデータ保持回路を設けるバス回路に関する技術について開示されている。これによると、バス上に設けられた信号保持回路でバス出力信号を保持する。バスがフローティング状態となる場合には、保持されたデータによりバス出力信号が保持される。したがって、バスがフローティング状態となるのを回避することができる。

【0006】

特許文献3には、バスにラッチ機能を持たせる技術が開示されている。これによると、ラッチ回路を省略できるためバス回路のハードウェア量が削減し、データ転送の高速化を図ることができる。

【0007】

特許文献4には、プルアップまたはプルダウン抵抗器を用いないバス電位安定化回路に関する技術が開示されている。これによると、複数の回路ユニットのいずれもが選択されない非通信時には固定データ出力部が選択され、主回路ユニットの入力回路に強制的に固定データを入力する。これにより、バスがフローティング状態となるのを回避することができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−048407号公報

【特許文献2】特開平05−216818号公報

【特許文献3】特開2008−177712号公報

【特許文献4】特開2002−076876号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1及び特許文献2に開示された技術では、既存の回路とは別にデータ保持回路を設けている。そのため、バス配線容量を増加させてしまい、バスのデータ転送性能の悪化を招くことや、バス回路の面積を増大させてしまうという問題がある。

【0010】

また、図6に関連するバス回路の構成例を示す。この回路において、データ保持回路6はバス50上に設けられている。すなわち、既存の回路とは別にデータ保持回路6を設けている。そのため、バス配線容量を増加させてしまい、バスのデータ転送性能の悪化を招くことや、バス回路の面積を増大させてしまうという問題がある。

【0011】

本発明は、このような問題点を解決するためになされたものであり、バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、入力端子からそれぞれ入力信号が入力され、制御入力端子からそれぞれ制御信号が入力される複数の入力部と、前記複数の入力部の出力を互いに接続したバスと、前記バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部、とを備え、前記バスがフローティング状態である場合に、前記出力部のラッチ回路に保持された信号を前記バスに出力する、バス回路である。

【発明の効果】

【0013】

本発明により、バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供することができる。

【図面の簡単な説明】

【0014】

【図1】実施の形態1にかかるバス回路の図である。

【図2】実施の形態1にかかる他のバス回路の図である。

【図3】実施の形態1にかかるタイムチャートの図である。

【図4】実施の形態2にかかるバス回路の図である。

【図5】実施の形態2にかかるラッチ回路の図である。

【図6】関連するバス回路の図である。

【発明を実施するための形態】

【0015】

実施の形態1.

以下、図面を参照して本実施の形態について説明する。

図1は、本実施の形態におけるバス回路の回路図を示したものである。

バス回路は、入力部1、2、3と、バス50と、出力部5を備える。ここで、バス50は、信号の入力元となる入力部1、入力部2、入力部3と、それぞれ接続している。また、バス50は出力部5と接続している。

また図2は、本実施の形態における他のバス回路の回路図を示したものである。このバス回路は図1で示したバス回路に加え、フローティング状態検出部4を備える。また、出力部5においてスイッチ部200を備える。フローティング状態検出部4は、信号の入力元となる入力部1、入力部2、入力部3とそれぞれ接続している。また、フローティング状態検出部4は、信号の出力先となる出力部5と接続している。

【0016】

入力部1は、ラッチ回路101と、ラッチ回路101の出力を入力とし、ENB1を制御信号として入力するスリーステートバッファ201とを備えている。

【0017】

ラッチ回路101は、入力信号DATA1と、クロック信号CLKが入力される。そして、ラッチ回路101は、入力信号DATA1に基づく信号をスリーステートバッファ201に出力する。

典型的には、入力信号DATA1は、任意に定めた"1"または"0"の信号である。また、クロック信号CLKは、一定時間ごとにH状態とL状態が繰り返される信号である。

ラッチ回路101はクロック信号CLKにより、ラッチ回路101において入力信号DATA1をラッチするタイミングや、ラッチ回路101から出力信号を出力するタイミングを制御する。なお、ラッチ回路101はクロック信号CLKがL状態の場合に、入力信号DATA1をラッチするものとする。

【0018】

スリーステートバッファ201は、ラッチ回路101から出力された信号と、制御信号ENB1が入力される。そして、スリーステートバッファ201は、ラッチ回路101から出力された信号に基づいて、バス50にバス信号を出力する。

ここで、スリーステートバッファ201は、典型的には、制御信号ENB1が"1"の場合にはON状態となり、バス出力信号をバス50に出力する。すなわち、制御信号ENB1が"1"の場合に、入力信号DATA1に基づく信号が、バス50に送出される。

また、制御信号ENB1が"0"の場合には、スリーステートバッファ201はOFF状態となり、スリーステートバッファ201は、ハイインピーダンスをバス50に出力する。ハイインピーダンスとは、電気的に"0"でも"1"でもない状態であり、バス50上の信号に影響を与えないように電気的にバスから切り離された状態である。

【0019】

ここで、入力部2及び、入力部3も、入力部1と同様に構成され、入力部1と同様に動作する。但し、入力部の数は限定されない。

【0020】

ここで、各入力部1、2、3のスリーステートバッファ201、202、203の制御信号ENB1、ENB2、ENB3はCLKに同期している。また、スリーステートバッファ201、202、203は排他的に制御されている。すなわち、同時に2つ以上のENBが "1"とならない。したがって、入力部1、入力部2及び入力部3から送出される信号が、バス50上で衝突することはない。

したがって、バス回路の通常動作時は、必ずいずれか1つの入力部が選ばれ、バス50を通過する。すなわち、いずれか1つの入力信号DATAに基づくバス信号がバス50に入力され、バス50はバス信号に基づく電位に設定される。

【0021】

入力部1、入力部2及び入力部3のすべてが電気的にバス50から切り離された場合、制御信号ENB1、ENB2及びENB3が、全て"0"であるディスイネーブル状態となる。すなわち、各入力部1、2、3からの入力信号DATA1、DATA2、DATA3がバス50に出力されない状態であり、このとき、全てのスリーステートバッファからはハイインピーダンスがバス50に出力され、バス50はフローティング状態となる。

【0022】

フローティング状態検出部4は、NOR回路300を備える。NOR回路300は、入力部1からの制御信号ENB1と、入力部2からの制御信号ENB2と入力部3からの制御信号ENB3を入力する。また、NOR回路300は制御信号ENB1、ENB2、ENB3に基づいて出力部制御信号CNTを出力する。

全ての制御信号ENB1、ENB2及びENB3が"0"のディスイネーブル状態となった場合には出力部制御信号CNTは"1"となり、出力部制御信号CNTがフローティング状態検出部4から出力部5に出力される。

【0023】

出力部5は、ラッチ回路100と、スイッチ部200を備える。スイッチ部200は、例えばトランスファーゲート回路である。

ラッチ回路100は、バス回路の通常動作時においてバス50を通過したバス信号と、クロック信号CLKが入力される。そして、ラッチ回路100は、バス信号に基づく出力信号DATA0を出力する。典型的には、ラッチ回路100はバス信号を、クロック信号CLKがH状態の場合にラッチする。

【0024】

例えば、入力部1が選択された場合には、制御信号ENB1は"1"となる。これにより、ラッチ回路101に保持されている入力信号DATA1に基づく信号が、スリーステートバッファ201を介してバス50に送出され、さらに、バス50から出力部5のラッチ回路100に送出される。

なお、選択されなかった入力部2、及び入力部3における制御信号ENB2、ENB3は"0"となり、スリーステートバッファ202、203からバス50にハイインピーダンスが送出される。その結果、入力部2及び入力部3は、電気的にバス50から切り離される。

【0025】

出力部5は、スイッチ部200を介して、ラッチ回路100の出力部と入力部を接続している。

出力部5のスイッチ部200は、出力部制御信号CNTによって制御される。スイッチ部200は、出力部制御信号CNTが"0"の場合に、OFF状態となり閉ざされる。すなわち、スイッチ部200は、いずれかの入力部からバス50にバス信号が入力されている場合には、OFF状態である。

一方、出力部制御信号CNTが"1"の場合にはON状態となり、ラッチ回路100に保持されている信号がバス50上に送られる。ここで、CNTが"1"の場合とは、入力部からバス50にバス信号が入力されていない状態である。この状態では、スイッチ部200がON状態となることにより、ラッチ回路100に保持されている信号がバス50上に送られる。これにより、バス50はラッチ回路100から送出された信号に対応して、直前までの電位状態を維持する。これにより、バス50がフローティング状態となるのは回避される。

【0026】

図3に、本実施形態におけるバス回路の動作のタイムチャートを示す。ここで、図2及び図3を参照して、動作の説明を行う。

【0027】

図3において、時刻T0〜T2の区間は、制御信号ENB1は"1"、制御信号ENB2及びENB3は"0"となっている。したがって、入力部1が選択されており、入力信号DATA1に基づいてラッチ回路101に保持された信号は、スリーステートバッファ201を介し、バス信号としてバス50に入力される。

時刻T0〜T1において、ラッチ回路101に保持された信号は"0"であり、バス50に与えられている信号は"0"となる。また、時刻T1〜T2において、ラッチ回路101に保持された信号は"1"であり、時刻T1のタイミングでバス50に与えられている信号は"0"から"1"に変更される。

【0028】

なお、スリーステートバッファ202及び203において、制御信号ENB2及びENB3が"0"である。このため、スリーステートバッファ202及び203からは、ハイインピーダンスがバス50へ出力されている。すなわち、入力部2及び入力部3はバス50から電気的に切り離された状態である。

【0029】

バス50上の電位は、時刻T2において、スリーステートバッファ201から出力された"1"に対応する電位に設定される。また、信号"1"がラッチ回路100に保持される。

【0030】

時刻T2〜T5の区間では、時刻T2において制御信号ENB1が"1"から"0"に変更される。このとき、ENB2、ENB3も"0"のまま変更されず、全ての制御信号が"0"であるディスイネーブル状態であり、バス50は未使用状態となる。すなわち、バス50がフローティング状態となる。

【0031】

このとき、スリーステートバッファ201、202、203の出力はいずれもハイインピーダンスとなり、NOR回路300の出力部制御信号CNTは"1"となる。したがって、出力部5のスイッチ部200がON状態となり、ラッチ回路100に保持されている信号がバス50に戻される。

その結果、バス50上の電位は"1"に対応する電位に設定され、フローティング状態が回避される。

ここでラッチ回路100に保持され、バス50に戻される"1"は、CNTが"1"となる時刻T2まで、バス50に保持されていた値である。バス50は、この値に対応する電位を維持することにより、その直前までとの電位の変化を抑えることができる。

【0032】

次に時刻T5〜T7の区間における動作を説明する。

時刻T5では、再び制御信号ENB1が"1"となるため、入力信号DATA1に基づきラッチ回路101に保持されている信号"0"が、スリーステートバッファ201を介してバス50に送出される。この信号は、時刻T6においてラッチ回路100に保持される。

【0033】

時刻T6では時刻T2と同様に制御信号ENB1が"1"から"0"に変更される。また、制御信号ENB2及びENB3も"0"のまま変更されていない。したがって、全ての制御信号が"0"であるディスイネーブル状態である。

そのため、スリーステートバッファ201、202、203の出力はいずれもハイインピーダンスとなる。また、フローティング状態検出部4のNOR回路300の出力部制御信号CNTは"1"となる。

CNTが"1"となることにより、出力部5のスイッチ部200がONされ、ラッチ回路100に保持されている信号がバス50に戻される。これにより、時刻T6〜T7におけるバス50のバス信号は"0"となる。ここで、ラッチ回路100に保持されていた値"0"は、CNT="1"となる時刻T6まで、バスに載っていた値である。バス50は、この信号に対応する電位を維持することにより、その直前までとの電位の変化を抑えることができる。

【0034】

本実施形態によれば、すべての入力部からのバス50にバス信号が入力されない場合に、出力部5に保持されている信号をバス50に戻すことにより、バス50がフローティング状態となるのを回避することができる。

【0035】

また、本実施の形態によれば、バス回路の消費電力を削減することができる。これは、バス50がフローティング状態となるのを回避するために与えられる信号は、固定値ではないからである。すなわち、バス50がフローティング状態になる直前の値を使用しており、バス50の電位の変化を最小限に抑えることができるためである。

バス配線容量の増加を抑え、バス回路のデータ転送性能の悪化を防ぐことができる。また、バス回路の面積を削減できる。これは、バス50がフローティング状態となるのを回避するために使用する信号に、既存の回路に保持されている信号を使うことで、バス50に信号保持用の回路を設ける必要がないためである。

【0036】

なお、本実施形態では、バスのビット幅を1ビットとして表わしているが、一般的なデータを扱う場合は、複数ビットのバス構成となる。たとえば8バイトデータを扱う場合には、64ビット分を束ねたデータバス構成となるため上記の効果は大きくなる。更にこのデータバスを、幾つか組み合わせてクロスバを構成する場合には、クロスバの規模に比例して効果も大きくなる。

【0037】

実施の形態2.

次に、他の実施の形態について、図面を参照して詳細に説明する。図4は、本発明の他の実施の形態にかかるバス回路を示したものである。

図4に示すバス回路において、出力部5以外の部分は、基本的に実施の形態1の図2で示した回路と同様である。なお、本実施の形態にかかるバス回路において、出力部5はスイッチ部200を備えない。また、出力部5は、ラッチ回路100の出力部と入力部を接続していない。

ここで、実施の形態1で示した符号と同一の符号は、同一または相当部分を示しており、説明を省略する。

【0038】

図5にラッチ回路100の構造を示す。

図5に示すように、ラッチ回路100は、インバータ回路56、57、59、60、61及びOR回路58を備える。

インバータ回路56は、クロック信号CLKを入力する。また、インバータ回路57は、インバータ回路56の出力信号を入力する。ここで、インバータ回路56の出力信号をCKB、インバータ回路57の出力信号をCKTとする。

インバータ回路61は、クロック信号CLKを入力し、クロック信号CLKを反転させる。インバータ回路61は、反転したクロック信号CLKをOR回路58に出力する。

OR回路58は、出力部制御信号CNTと、インバータ回路61の出力信号を入力する。

インバータ回路59は、OR回路58の出力信号を入力する。また、インバータ回路60は、インバータ回路59の出力信号を入力する。ここで、インバータ回路59の出力信号をCTB、インバータ回路60の出力信号をCTTとする。

【0039】

また、ラッチ回路100は、第1のスイッチ部51と、第2のスイッチ部54と、インバータ回路52、53、55を備える。ここで、第1のスイッチ部51及び第2のスイッチ部54は、例えばトランスファーゲート回路である。

第1のスイッチ部51、インバータ回路53及びインバータ回路55により、信号をラッチする。第1のスイッチ部51は、CKT及びCKBにより制御される。いずれかの入力部1、2、3からバス50にバス信号の入力がある場合には、バス50を介して、ラッチ回路100にバス信号がラッチされる。

【0040】

インバータ回路52は、バス50からの入力に基づく信号を、ラッチ回路100から出力信号DATA0として出力する。インバータ回路52は、ラッチ回路100の入力部と信号をラッチする回路部とを接続しているノードと、出力部との間に設けられている。なお、信号をラッチする回路部とは、第1のスイッチ部51、インバータ回路53及びインバータ回路55を備えた回路部である。

【0041】

第2のスイッチ部54は、一方の端部がバス50と接続されている。また、第2のスイッチ部54は、CTB及びCTTにより制御される。これにより、出力部制御信号CNTが"1"の場合に、これにより、第2のスイッチ部54が常に開かれることとなる。

したがって、バス50がフローティング状態となった場合にラッチ回路100に保持していたデータをバス50に戻すことができ、バス50のフローティング状態を防止することができる。

【0042】

本実施態様によれば、実施の形態1におけるスイッチ部200と、スイッチ部200を介してラッチ回路100の出力部と入力部を接続する回路を設ける必要がなく、バス配線容量を更に削減することができる。

【0043】

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。

【符号の説明】

【0044】

1 入力部

2 入力部

3 入力部

4 フローティング状態検出部

5 出力部

6 データ保持回路

50 バス

51 第1のスイッチ部

52 インバータ回路

53 インバータ回路

54 第2のスイッチ部

55 インバータ回路

56 インバータ回路

57 インバータ回路

58 OR回路

59 インバータ回路

60 インバータ回路

61 インバータ回路

100 ラッチ回路

101 ラッチ回路

102 ラッチ回路

103 ラッチ回路

200 スイッチ部

201 スリーステートバッファ

202 スリーステートバッファ

203 スリーステートバッファ

300 NOR回路

500 スイッチ部

501 インバータ回路

502 インバータ回路

【特許請求の範囲】

【請求項1】

入力信号と制御信号がそれぞれ入力される複数の入力部と、

前記複数の入力部の出力を互いに接続したバスと、

前記バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部、とを備え、

前記バスがフローティング状態である場合に、前記出力部のラッチ回路に保持された信号を前記バスに出力する、

バス回路。

【請求項2】

フローティング状態検出部を更に備え、

前記フローティング状態検出部は、前記複数の入力部の制御入力端子からの制御信号に基づいて、バスがフローティング状態であるか否かを検出し、検出結果に応じて出力部制御信号を出力部に送出する、

請求項1に記載のバス回路。

【請求項3】

前記出力部は前記ラッチ回路の入力部と出力部がスイッチ部を介して接続され、

前記バスの状態に基づいて前記スイッチ部の動作を制御し、ラッチ回路に保持されている信号をバスに送出する、

請求項1又は2に記載のバス回路。

【請求項4】

前記ラッチ回路は、

OR回路と、第1のスイッチ部と、第2のスイッチ部と、を備え、

前記OR回路は、前記フローティング状態検出部から出力部制御信号が入力され、

前記第1のスイッチ部は、前記OR回路の出力信号によって制御され、

前記第2のスイッチ部は、前記OR回路の出力信号によらずに制御される、

請求項2に記載のバス回路。

【請求項1】

入力信号と制御信号がそれぞれ入力される複数の入力部と、

前記複数の入力部の出力を互いに接続したバスと、

前記バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部、とを備え、

前記バスがフローティング状態である場合に、前記出力部のラッチ回路に保持された信号を前記バスに出力する、

バス回路。

【請求項2】

フローティング状態検出部を更に備え、

前記フローティング状態検出部は、前記複数の入力部の制御入力端子からの制御信号に基づいて、バスがフローティング状態であるか否かを検出し、検出結果に応じて出力部制御信号を出力部に送出する、

請求項1に記載のバス回路。

【請求項3】

前記出力部は前記ラッチ回路の入力部と出力部がスイッチ部を介して接続され、

前記バスの状態に基づいて前記スイッチ部の動作を制御し、ラッチ回路に保持されている信号をバスに送出する、

請求項1又は2に記載のバス回路。

【請求項4】

前記ラッチ回路は、

OR回路と、第1のスイッチ部と、第2のスイッチ部と、を備え、

前記OR回路は、前記フローティング状態検出部から出力部制御信号が入力され、

前記第1のスイッチ部は、前記OR回路の出力信号によって制御され、

前記第2のスイッチ部は、前記OR回路の出力信号によらずに制御される、

請求項2に記載のバス回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−97271(P2011−97271A)

【公開日】平成23年5月12日(2011.5.12)

【国際特許分類】

【出願番号】特願2009−247939(P2009−247939)

【出願日】平成21年10月28日(2009.10.28)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成23年5月12日(2011.5.12)

【国際特許分類】

【出願日】平成21年10月28日(2009.10.28)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]