バッファメモリ装置及び通信装置

【課題】 リフレッシュの有無をリアルタイムに判定でき、しかも、優先データを扱うことが可能なパケットバッファ装置を提供する。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

【解決手段】 対象としているパケットバッファ装置は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うものである。そして、メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はバッファメモリ装置及び通信装置に関し、例えば、DRAMを使用したパケットバッファを使用する通信装置に適用し得るものである。

【背景技術】

【0002】

近年、電子装置全般において低消費電力化の要求が高まってきており、通信装置においても例外なく低消費電力化が必要になってきている。他方、一般的な半導体記憶装置であるDRAMは、データを保持するために定期的なリフレッシュ動作が必要であり、DRAMをパケットバッファとして使用した通信装置の消費電力の低減は課題であった。

【0003】

そこで、DRAMに対する低消費電力化の要求を満たすために、パーシャルリフレッシュと呼ばれる技術が提案されている(特許文献1、特許文献2参照)。

【0004】

パーシャルリフレッシュとは、DRAMに含まれる複数のメモリバンクのうち、選択されたメモリバンク若しくは自動判定されたメモリバンクに対してのみリフレッシュ動作を行い、その他のメモリバンクに対してはリフレッシュ動作を停止する技術であり、これにより、未使用バンクメモリへのリフレッシュ動作が省略でき、消費電力を低減することが可能となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−276878号公報

【特許文献2】特開2007−219998号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、リフレッシュを行うメモリバンクを選択する構成(特許文献1参照)では、リフレッシュの有無を例えばファームウェア等でレジスタにて設定する必要がある。他方、DRAMを使用したパケットバッファにおいては、読出しを行ったデータは保持しておく必要がないため、使用バンク、未使用バンクが頻繁に変化する可能性がある。そのため、ファームウェア処理では対応し切れない可能性があり、消費電力の低減効果は必ずしも十分ではない。

【0007】

特許文献2には、リフレッシュするDRAMの領域を自動判定することが記載されている。パケットバッファの書込み及び読出し位置を規定している書込みカウンタと読出しカウンタとを監視し、読出しカウンタのカウント値に基づいて、読出しによって未使用状態となった領域を捉えてリフレッシュすることが記載されている。

【0008】

特許文献2の記載技術は、パケットに優先度が設定されていない場合には有効である。しかしながら、多くの通信システムでは優先パケットの概念を設けている。優先パケットが入力され、パケットバッファに書き込まれた場合には、書き込まれた順序ではなく、優先パケットが一般パケットより優先されてパケットバッファから読み出され、パケットバッファの記憶エリアが歯抜け状態となる。このような歯抜け状態となることもある通信装置では、特許文献2に記載の従来技術を適用することができない。

【0009】

そのため、リフレッシュの有無をリアルタイムに判定できる、しかも、優先データを扱うことが可能なバッファメモリ装置や通信装置が望まれている。

【課題を解決するための手段】

【0010】

第1の本発明は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うバッファメモリ装置において、(1)上記メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、(2)書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

【0011】

第2の本発明は、パケットデータが流れる所定位置にパケットバッファ装置を有する通信装置において、上記パケットバッファ装置として、第1の本発明のバッファメモリ装置を適用したことを特徴とする。

【発明の効果】

【0012】

本発明によれば、リフレッシュの有無をリアルタイムに判定できる、しかも、優先データを扱うことが可能なバッファメモリ装置及び通信装置を提供することができる。

【図面の簡単な説明】

【0013】

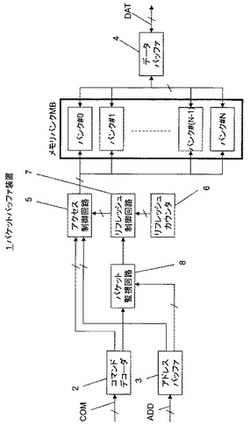

【図1】実施形態に係るパケットバッファ装置の構成を示すブロック図である。

【図2】実施形態に係るパケットバッファ装置におけるパケット監視回路の詳細構成を示すブロック図である。

【発明を実施するための形態】

【0014】

(A)主たる実施形態

以下、本発明によるバッファメモリ装置及び通信装置の一実施形態を、図面を参照しながら説明する。なお、実施形態のバッファメモリ装置はパケットバッファ装置であり、実施形態の通信装置は、そのようなパケットバッファ装置を搭載したものである。

【0015】

(A−1)実施形態の構成

図1は、実施形態に係るパケットバッファ装置の構成を示すブロック図である。

【0016】

図1において、実施形態に係るパケットバッファ装置1は、複数のメモリバンクMB#0〜MB#Nと、コマンドデコーダ2、アドレスバッファ3、データバッファ4、アクセス制御回路5、リフレッシュカウンタ6、リフレッシュ制御回路7及びパケット監視回路8を有する。

【0017】

メモリバンクMB#0〜MB#Nは、1個(又は複数)のDRAMのエリアが分割されて設定されている。各メモリバンクMB#0〜MB#Nはそれぞれ、独立して、コマンドによって書込み又は読出しが可能なものであり、受信したパケットの全体や、受信したパケットから抽出されたデータが、各メモリバンクMB#0〜MB#N内の指定されたエリアにバッファリングされるようになされている。

【0018】

当該パケットバッファ装置1の外部からは、各メモリバンクMB#0〜MB#Nのアクセスのために、コマンドCOM及びアドレスADDが与えられるようになされている。

【0019】

コマンドデコーダ2は、外部から与えられたコマンドCOMから各種制御コマンドを生成し、アクセス制御回路5に与えるものである。

【0020】

アドレスバッファ3は、外部から与えられたアドレスADDをバッファリングするものであり、バッファリングされたアドレスADDは、適宜、アクセス制御回路5に与えられる。

【0021】

データバッファ4は、外部から与えられたパケットデータ(受信したパケットの全体のデータ、若しくは、受信したパケットから抽出されたデータ)DATをバッファリングしたり、いずれかのメモリバンクMB#n(nは0〜Nのいずれか)から読み出されたパケットデータをバッファリングしたりするものである。

【0022】

アクセス制御回路5は、コマンドデコーダ2からの制御コマンド及びアドレスバッファ3からのアドレスに基づき、該当するメモリバンクMB#nに対するアクセスを制御するものである。

【0023】

具体的には、アドレスバッファ3からのアドレス及びコマンドデコーダ2からの制御コマンドにより、アクセス制御回路5によって、該当するメモリバンクMB#nの各メモリセルのロウアドレス線が選択される。さらに、コマンドデコーダ2からの制御コマンドが読出し又は書込み制御の場合には、アドレスバッファ3からのアドレスにより、アクセス制御回路5によって、該当するメモリバンクMB#nの各メモリセルのカラムアドレス線が選択される。これにより、選択されたメモリセルに、データバッファ4にバッファリングされたパケットデータが書き込まれ、若しくは、選択されたメモリセルからパケットデータが読み出されてデータバッファ4にバッファリングされる。

【0024】

リフレッシュカウンタ6は、リフレッシュアドレスを周期的に生成する回路である。リフレッシュカウンタ6は、周期的にインクリメント又はデクリメントしたリフレッシュアドレス(ロウアドレス)を生成する。リフレッシュアドレスは、全てのメモリバンクMB#0〜MB#Nに対して共通のロウアドレス線を指定するものであり、リフレッシュ制御回路7を経由して、アクセス制御回路5に与えられる。アクセス制御回路5では、コマンドデコーダ2及びアドレスバッファ3からの制御との競合処理を実施した上で、該当メモリバンクMB#n内の指定されたロウアドレス線に接続されているメモリセルをリフレッシュする。

【0025】

リフレッシュ制御回路7は、パケット監視回路8からのリフレッシュ許可又はリフレッシュ禁止の信号により、リフレッシュカウンタ6から生成されたロウアドレスをアクセス制御回路5に通知するか又は停止するかの制御を行う。

【0026】

パケット監視回路8は、パケットデータの書込み及び読出しを監視する回路である。パケット監視回路8は、アドレスバッファ3から出力されるアドレスをデコードし、どのメモリバンクに対するアクセスなのかを記憶する。また、パケット監視回路8は、コマンドデコーダ2からの制御コマンドによりメモリバンクへの書込み又は読出しを監視し、別個にカウントする。

【0027】

図2は、パケット監視回路8の詳細構成を示すブロック図であり、パケット監視回路8に接続している周囲の構成要素も併せて示している。

【0028】

図2において、パケット監視回路8は、メモリバンク数のバンク制御回路10#0〜10#Nと、アドレスデコーダ11と、各バンク制御回路10#0〜10#Nに対応して2つずつ設けられた制御許可回路12#0W、12#0R、…、12#NW、12#NRとを有する。バンク制御回路10#0〜10#Nはそれぞれ、書込みカウンタ13#0〜13#N、読出しカウンタ14#0〜14#N及びカウント比較回路15#0〜15#Nを有する。

【0029】

バンク制御回路10#nは、コマンドデコーダ2及びアドレスバッファ3からの信号により制御されるものである。

【0030】

アドレスデコーダ11には、アドレスバッファ3からのアドレスが入力される。アドレスデコーダ11は、各メモリバンクMB#0〜MB#Nへのロウアドレスか否かを判定し、判定の結果で、各メモリバンクMB#0〜MB#Nに対応するバンク制御回路10#0〜10#Nへの制御許可回路12#0W、12#0R、…、12#NW、12#NRのイネーブル、ディセーブルを制御するものである。

【0031】

制御許可回路12#0W〜12#NWは、イネーブルのときに、コマンドデコーダ2から出力された書込み制御信号WCONを通過させ、ディセーブルのときに、書込み制御信号WCONの通過を阻止するものである。制御許可回路12#0R〜12#NRは、イネーブルのときに、コマンドデコーダ2から出力された読出し制御信号RCONを通過させ、ディセーブルのときに、読出し制御信号RCONの通過を阻止するものである。

【0032】

書込みカウンタ13#0〜13#Nは、制御許可回路12#0W〜12#NWを経由して到来した書込み制御信号WCONの数をカウントアップするものである。

【0033】

読出しカウンタ14#0〜14#Nは、制御許可回路12#0R〜12#NRを経由して到来した読出し制御信号RCONの数をカウントアップするものである。

【0034】

カウント比較回路15#0〜15#Nは、書込カウンタ13#0〜13#N及び読出カウンタ14#0〜14#Nのカウント数を比較し、両カウント数が一致している場合にリフレッシュ禁止信号をリフレッシュ制御回路7に出力し、不一致の場合にリフレッシュ許可信号をリフレッシュ回路7に出力するものである。

【0035】

(A−2)実施形態の動作

次に、以上のような構成を有する実施形態のパケットバッファ装置1の動作を説明する。

【0036】

実施形態のパケットバッファ装置1が起動された直後においては、メモリバンクMB#0〜MB#N内には不定情報が格納されており、リフレッシュの必要はない。

【0037】

また、パケット監視回路8内の書込みカウンタ13#0〜13#N及び読出しカウンタ14#0〜14#Nは初期化されており、それぞれカウント数は0のため、カウント比較回路15#0〜15#Nで一致と判定され、全メモリバンクMB#0〜MB#Nについてのリフレッシュ禁止信号がリフレッシュ制御回路7に出力される。

【0038】

リフレッシュカウンタ6が周期的にメモリバンクMB#0〜MB#Nへのロウアドレスを出力するが、リフレッシュ制御回路7により、リフレッシュが禁止されているため、アクセス制御回路5にリフレッシュ用ロウアドレスが出力されず、全メモリバンクMB#0〜MB#Nに対して、リフレッシュ動作が実行されない。

【0039】

通信装置がパケットを受信すると、コマンドデコーダ2、アドレスバッファ3、データバッファ4及びアクセス制御回路5が動作し、アドレスADDで定まるメモリバンクMB#nに対してパケットデータの書込み動作が開始される。

【0040】

書込み動作が開始されると、パケット監視回路8のアドレスデコーダ11はどのメモリバンクMB#nヘのアクセスかを判定し、該当するメモリバンクMB#nに対応するバンク制御回路10#nへの書込み用制御許可回路12#nWをイネーブルにする。これにより、コマンドデコーダ2から出力された書込み制御信号WCONが書込み用制御許可回路12#nWを通過して、バンク制御回路10#n内の書込みカウンタ13#nに与えられ、そのカウントがカウントアップされる。

【0041】

以上のように書込みだけがなされたタイミングで、書込みカウンタ13#nと読出しカウンタ14#nのカウント値をカウント比較回路15#nで比較すると、不一致と判定され、カウント比較回路15#nからリフレッシュ制御回路7へ、該当メモリバンクMB#nへのリフレッシュ許可信号が出力される。

【0042】

リフレッシュカウンタ6が上記メモリバンクMB#nへのロウアドレスを出力したときには、リフレッシュ制御回路7によって、リフレッシュ動作が許可されているため、メモリバンクMB#nに対してのみアクセス制御回路5へリフレッシュ用ロウアドレスが出力され、リフレッシュ動作が実行される。

【0043】

通信装置が次のパケットを受信した場合も、上述と同様な書込み動作が実行され、バンク制御回路10#n内の書込みカウンタ13#nのカウント値がさらにカウントアップする。

【0044】

パケットバッファ装置1からバッファリングされているパケットデータを読み出して通信装置から出力する場合には、コマンドデコーダ2、アドレスバッファ3、データバッファ4及びアクセス制御回路5が動作し、アドレスADDで規定されるメモリバンクMB#nからパケットデータが読み出され、データバッファ4を介して出力される。

【0045】

メモリバンクMB#nはDRAMで構成されているため、パケットデータが読み出されても、読み出されたパケットデータは継続して記憶されている。しかし、パケットバッファとして適用されているため、読出し後に継続して記憶されているパケットデータは保持する必要がなく、メモリバンクMB#n内に別に保持すべきパケットデータが存在しなければリフレッシュは不要である。

【0046】

読出し動作が開始されると、書込み動作と同様に、パケット監視回路8のアドレスデコーダ11はどのメモリバンクMB#nヘのアクセスかを判定し、該当するメモリバンクMB#nに対応するバンク制御回路10#nへの読出し用制御許可回路12#nRをイネーブルにする。これにより、コマンドデコーダ2から出力された読出し制御信号RCONが読出し用制御許可回路12#nRを通過して、バンク制御回路10#n内の読出しカウンタ14#nに与えられ、そのカウント値がカウントアップされる。

【0047】

このような読出し後において、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値がカウント比較回路15#nで比較され、一致と判定されれば、メモリバンクMB#nへのリフレッシュ禁止信号がリフレッシュ制御回路7へ出力される。

【0048】

リフレッシュカウンタ6がメモリバンクMB#nへのロウアドレスを出力しても、リフレッシュ制御回路7においてリフレッシュ動作が禁止されているため、メモリバンクMB#nへのリフレッシュ用ロウアドレスがアクセス制御回路5に出力されず、メモリバンクMB#nのリフレッシュ動作は実行されない。

【0049】

ここで、読出し動作に応じて、読出しカウンタ14#nのカウント値をカウントアップした後において、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値が不一致であると、カウント比較回路15#nからリフレッシュ制御回路7へ、該当メモリバンクMB#nへのリフレッシュ許可信号が出力されるので、リフレッシュカウンタ6がメモリバンクMB#nへのロウアドレスを出力する毎に、メモリバンクMB#nがリフレッシュされる。

【0050】

メモリバンクMB#nへパケットデータを書き込んだ回数と同じ回数だけ読出し動作が実行されたときには、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値が一致し、このとき、リフレッシュ許可信号からリフレッシュ禁止信号へ切り替わり、メモリバンクMB#nのリフレッシュが実行されない状態になる。

【0051】

(A−3)実施形態の効果

上記実施形態によれば、バンクメモリへの書込みデータ数と読出しデータ数との一致、不一致を監視し、不一致の場合に、バンクメモリのリフレッシュを行い、一致した場合に、バンクメモリのリフレッシュを実行しないようにしたので、データ保持が不要なメモリバンクに対してリアルタイムにリフレッシュ動作を停止させることができる。

【0052】

入力パケット間隔が大きくなって入力トラフィックが低下した場合や、入力トラフィックがなくなった場合などでは、書込みデータ数と読出しデータ数とが一致している期間、すなわち、リフレッシュ不要の期間が長くなり、メモリバンクでの電力低減が期待できる。

【0053】

また、上記実施形態によれば、当該パケットバッファ装置が扱うパケットに優先度があり、後で書き込んだ優先パケットのデータをそれより先に書き込んだ他のデータより先に読み出す状況があったとしても、書込みデータ数と読出しデータ数との比較でリフレッシュの有無を決定するので、優先度がない場合と同様に扱うことができる。

【0054】

(B)他の実施形態

上記実施形態のパケットバッファ装置は、通信装置の入力段に設けられるものであっても良く、また、通信装置の出力段に設けられるものであっても良く、通信装置内における設置位置は問われないものである。

【0055】

上記実施形態では、本発明のバッファメモリ装置をパケットバッファ装置に適用したものを示したが、その用途は、パケットバッファ装置に限定されるものではない。すなわち、メモリバンクに一旦格納されるデータの種類はパケットデータに限定されるものではない。

【0056】

また、記憶媒体もDRAMに限定されず、リフレッシュ動作を必要とする記憶媒体を適用しているバッファメモリ装置であれば良い。

【符号の説明】

【0057】

1…パケットバッファ装置、MB#0〜MB#N…メモリバンク、2…コマンドデコーダ、3…アドレスバッファ、4…データバッファ、5…アクセス制御回路、6…リフレッシュカウンタ、7…リフレッシュ制御回路、8…パケット監視回路、10#0〜10#N…バンク制御回路、11…アドレスデコーダ、12#0W〜12#NW、12#0R〜12#NR…制御許可回路、13#0〜13#N…書込みカウンタ、14#0〜14#N…読出しカウンタ、15#0〜15#N…カウント比較回路。

【技術分野】

【0001】

本発明はバッファメモリ装置及び通信装置に関し、例えば、DRAMを使用したパケットバッファを使用する通信装置に適用し得るものである。

【背景技術】

【0002】

近年、電子装置全般において低消費電力化の要求が高まってきており、通信装置においても例外なく低消費電力化が必要になってきている。他方、一般的な半導体記憶装置であるDRAMは、データを保持するために定期的なリフレッシュ動作が必要であり、DRAMをパケットバッファとして使用した通信装置の消費電力の低減は課題であった。

【0003】

そこで、DRAMに対する低消費電力化の要求を満たすために、パーシャルリフレッシュと呼ばれる技術が提案されている(特許文献1、特許文献2参照)。

【0004】

パーシャルリフレッシュとは、DRAMに含まれる複数のメモリバンクのうち、選択されたメモリバンク若しくは自動判定されたメモリバンクに対してのみリフレッシュ動作を行い、その他のメモリバンクに対してはリフレッシュ動作を停止する技術であり、これにより、未使用バンクメモリへのリフレッシュ動作が省略でき、消費電力を低減することが可能となっている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−276878号公報

【特許文献2】特開2007−219998号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、リフレッシュを行うメモリバンクを選択する構成(特許文献1参照)では、リフレッシュの有無を例えばファームウェア等でレジスタにて設定する必要がある。他方、DRAMを使用したパケットバッファにおいては、読出しを行ったデータは保持しておく必要がないため、使用バンク、未使用バンクが頻繁に変化する可能性がある。そのため、ファームウェア処理では対応し切れない可能性があり、消費電力の低減効果は必ずしも十分ではない。

【0007】

特許文献2には、リフレッシュするDRAMの領域を自動判定することが記載されている。パケットバッファの書込み及び読出し位置を規定している書込みカウンタと読出しカウンタとを監視し、読出しカウンタのカウント値に基づいて、読出しによって未使用状態となった領域を捉えてリフレッシュすることが記載されている。

【0008】

特許文献2の記載技術は、パケットに優先度が設定されていない場合には有効である。しかしながら、多くの通信システムでは優先パケットの概念を設けている。優先パケットが入力され、パケットバッファに書き込まれた場合には、書き込まれた順序ではなく、優先パケットが一般パケットより優先されてパケットバッファから読み出され、パケットバッファの記憶エリアが歯抜け状態となる。このような歯抜け状態となることもある通信装置では、特許文献2に記載の従来技術を適用することができない。

【0009】

そのため、リフレッシュの有無をリアルタイムに判定できる、しかも、優先データを扱うことが可能なバッファメモリ装置や通信装置が望まれている。

【課題を解決するための手段】

【0010】

第1の本発明は、メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うバッファメモリ装置において、(1)上記メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、(2)書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段とを備えることを特徴とする。

【0011】

第2の本発明は、パケットデータが流れる所定位置にパケットバッファ装置を有する通信装置において、上記パケットバッファ装置として、第1の本発明のバッファメモリ装置を適用したことを特徴とする。

【発明の効果】

【0012】

本発明によれば、リフレッシュの有無をリアルタイムに判定できる、しかも、優先データを扱うことが可能なバッファメモリ装置及び通信装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】実施形態に係るパケットバッファ装置の構成を示すブロック図である。

【図2】実施形態に係るパケットバッファ装置におけるパケット監視回路の詳細構成を示すブロック図である。

【発明を実施するための形態】

【0014】

(A)主たる実施形態

以下、本発明によるバッファメモリ装置及び通信装置の一実施形態を、図面を参照しながら説明する。なお、実施形態のバッファメモリ装置はパケットバッファ装置であり、実施形態の通信装置は、そのようなパケットバッファ装置を搭載したものである。

【0015】

(A−1)実施形態の構成

図1は、実施形態に係るパケットバッファ装置の構成を示すブロック図である。

【0016】

図1において、実施形態に係るパケットバッファ装置1は、複数のメモリバンクMB#0〜MB#Nと、コマンドデコーダ2、アドレスバッファ3、データバッファ4、アクセス制御回路5、リフレッシュカウンタ6、リフレッシュ制御回路7及びパケット監視回路8を有する。

【0017】

メモリバンクMB#0〜MB#Nは、1個(又は複数)のDRAMのエリアが分割されて設定されている。各メモリバンクMB#0〜MB#Nはそれぞれ、独立して、コマンドによって書込み又は読出しが可能なものであり、受信したパケットの全体や、受信したパケットから抽出されたデータが、各メモリバンクMB#0〜MB#N内の指定されたエリアにバッファリングされるようになされている。

【0018】

当該パケットバッファ装置1の外部からは、各メモリバンクMB#0〜MB#Nのアクセスのために、コマンドCOM及びアドレスADDが与えられるようになされている。

【0019】

コマンドデコーダ2は、外部から与えられたコマンドCOMから各種制御コマンドを生成し、アクセス制御回路5に与えるものである。

【0020】

アドレスバッファ3は、外部から与えられたアドレスADDをバッファリングするものであり、バッファリングされたアドレスADDは、適宜、アクセス制御回路5に与えられる。

【0021】

データバッファ4は、外部から与えられたパケットデータ(受信したパケットの全体のデータ、若しくは、受信したパケットから抽出されたデータ)DATをバッファリングしたり、いずれかのメモリバンクMB#n(nは0〜Nのいずれか)から読み出されたパケットデータをバッファリングしたりするものである。

【0022】

アクセス制御回路5は、コマンドデコーダ2からの制御コマンド及びアドレスバッファ3からのアドレスに基づき、該当するメモリバンクMB#nに対するアクセスを制御するものである。

【0023】

具体的には、アドレスバッファ3からのアドレス及びコマンドデコーダ2からの制御コマンドにより、アクセス制御回路5によって、該当するメモリバンクMB#nの各メモリセルのロウアドレス線が選択される。さらに、コマンドデコーダ2からの制御コマンドが読出し又は書込み制御の場合には、アドレスバッファ3からのアドレスにより、アクセス制御回路5によって、該当するメモリバンクMB#nの各メモリセルのカラムアドレス線が選択される。これにより、選択されたメモリセルに、データバッファ4にバッファリングされたパケットデータが書き込まれ、若しくは、選択されたメモリセルからパケットデータが読み出されてデータバッファ4にバッファリングされる。

【0024】

リフレッシュカウンタ6は、リフレッシュアドレスを周期的に生成する回路である。リフレッシュカウンタ6は、周期的にインクリメント又はデクリメントしたリフレッシュアドレス(ロウアドレス)を生成する。リフレッシュアドレスは、全てのメモリバンクMB#0〜MB#Nに対して共通のロウアドレス線を指定するものであり、リフレッシュ制御回路7を経由して、アクセス制御回路5に与えられる。アクセス制御回路5では、コマンドデコーダ2及びアドレスバッファ3からの制御との競合処理を実施した上で、該当メモリバンクMB#n内の指定されたロウアドレス線に接続されているメモリセルをリフレッシュする。

【0025】

リフレッシュ制御回路7は、パケット監視回路8からのリフレッシュ許可又はリフレッシュ禁止の信号により、リフレッシュカウンタ6から生成されたロウアドレスをアクセス制御回路5に通知するか又は停止するかの制御を行う。

【0026】

パケット監視回路8は、パケットデータの書込み及び読出しを監視する回路である。パケット監視回路8は、アドレスバッファ3から出力されるアドレスをデコードし、どのメモリバンクに対するアクセスなのかを記憶する。また、パケット監視回路8は、コマンドデコーダ2からの制御コマンドによりメモリバンクへの書込み又は読出しを監視し、別個にカウントする。

【0027】

図2は、パケット監視回路8の詳細構成を示すブロック図であり、パケット監視回路8に接続している周囲の構成要素も併せて示している。

【0028】

図2において、パケット監視回路8は、メモリバンク数のバンク制御回路10#0〜10#Nと、アドレスデコーダ11と、各バンク制御回路10#0〜10#Nに対応して2つずつ設けられた制御許可回路12#0W、12#0R、…、12#NW、12#NRとを有する。バンク制御回路10#0〜10#Nはそれぞれ、書込みカウンタ13#0〜13#N、読出しカウンタ14#0〜14#N及びカウント比較回路15#0〜15#Nを有する。

【0029】

バンク制御回路10#nは、コマンドデコーダ2及びアドレスバッファ3からの信号により制御されるものである。

【0030】

アドレスデコーダ11には、アドレスバッファ3からのアドレスが入力される。アドレスデコーダ11は、各メモリバンクMB#0〜MB#Nへのロウアドレスか否かを判定し、判定の結果で、各メモリバンクMB#0〜MB#Nに対応するバンク制御回路10#0〜10#Nへの制御許可回路12#0W、12#0R、…、12#NW、12#NRのイネーブル、ディセーブルを制御するものである。

【0031】

制御許可回路12#0W〜12#NWは、イネーブルのときに、コマンドデコーダ2から出力された書込み制御信号WCONを通過させ、ディセーブルのときに、書込み制御信号WCONの通過を阻止するものである。制御許可回路12#0R〜12#NRは、イネーブルのときに、コマンドデコーダ2から出力された読出し制御信号RCONを通過させ、ディセーブルのときに、読出し制御信号RCONの通過を阻止するものである。

【0032】

書込みカウンタ13#0〜13#Nは、制御許可回路12#0W〜12#NWを経由して到来した書込み制御信号WCONの数をカウントアップするものである。

【0033】

読出しカウンタ14#0〜14#Nは、制御許可回路12#0R〜12#NRを経由して到来した読出し制御信号RCONの数をカウントアップするものである。

【0034】

カウント比較回路15#0〜15#Nは、書込カウンタ13#0〜13#N及び読出カウンタ14#0〜14#Nのカウント数を比較し、両カウント数が一致している場合にリフレッシュ禁止信号をリフレッシュ制御回路7に出力し、不一致の場合にリフレッシュ許可信号をリフレッシュ回路7に出力するものである。

【0035】

(A−2)実施形態の動作

次に、以上のような構成を有する実施形態のパケットバッファ装置1の動作を説明する。

【0036】

実施形態のパケットバッファ装置1が起動された直後においては、メモリバンクMB#0〜MB#N内には不定情報が格納されており、リフレッシュの必要はない。

【0037】

また、パケット監視回路8内の書込みカウンタ13#0〜13#N及び読出しカウンタ14#0〜14#Nは初期化されており、それぞれカウント数は0のため、カウント比較回路15#0〜15#Nで一致と判定され、全メモリバンクMB#0〜MB#Nについてのリフレッシュ禁止信号がリフレッシュ制御回路7に出力される。

【0038】

リフレッシュカウンタ6が周期的にメモリバンクMB#0〜MB#Nへのロウアドレスを出力するが、リフレッシュ制御回路7により、リフレッシュが禁止されているため、アクセス制御回路5にリフレッシュ用ロウアドレスが出力されず、全メモリバンクMB#0〜MB#Nに対して、リフレッシュ動作が実行されない。

【0039】

通信装置がパケットを受信すると、コマンドデコーダ2、アドレスバッファ3、データバッファ4及びアクセス制御回路5が動作し、アドレスADDで定まるメモリバンクMB#nに対してパケットデータの書込み動作が開始される。

【0040】

書込み動作が開始されると、パケット監視回路8のアドレスデコーダ11はどのメモリバンクMB#nヘのアクセスかを判定し、該当するメモリバンクMB#nに対応するバンク制御回路10#nへの書込み用制御許可回路12#nWをイネーブルにする。これにより、コマンドデコーダ2から出力された書込み制御信号WCONが書込み用制御許可回路12#nWを通過して、バンク制御回路10#n内の書込みカウンタ13#nに与えられ、そのカウントがカウントアップされる。

【0041】

以上のように書込みだけがなされたタイミングで、書込みカウンタ13#nと読出しカウンタ14#nのカウント値をカウント比較回路15#nで比較すると、不一致と判定され、カウント比較回路15#nからリフレッシュ制御回路7へ、該当メモリバンクMB#nへのリフレッシュ許可信号が出力される。

【0042】

リフレッシュカウンタ6が上記メモリバンクMB#nへのロウアドレスを出力したときには、リフレッシュ制御回路7によって、リフレッシュ動作が許可されているため、メモリバンクMB#nに対してのみアクセス制御回路5へリフレッシュ用ロウアドレスが出力され、リフレッシュ動作が実行される。

【0043】

通信装置が次のパケットを受信した場合も、上述と同様な書込み動作が実行され、バンク制御回路10#n内の書込みカウンタ13#nのカウント値がさらにカウントアップする。

【0044】

パケットバッファ装置1からバッファリングされているパケットデータを読み出して通信装置から出力する場合には、コマンドデコーダ2、アドレスバッファ3、データバッファ4及びアクセス制御回路5が動作し、アドレスADDで規定されるメモリバンクMB#nからパケットデータが読み出され、データバッファ4を介して出力される。

【0045】

メモリバンクMB#nはDRAMで構成されているため、パケットデータが読み出されても、読み出されたパケットデータは継続して記憶されている。しかし、パケットバッファとして適用されているため、読出し後に継続して記憶されているパケットデータは保持する必要がなく、メモリバンクMB#n内に別に保持すべきパケットデータが存在しなければリフレッシュは不要である。

【0046】

読出し動作が開始されると、書込み動作と同様に、パケット監視回路8のアドレスデコーダ11はどのメモリバンクMB#nヘのアクセスかを判定し、該当するメモリバンクMB#nに対応するバンク制御回路10#nへの読出し用制御許可回路12#nRをイネーブルにする。これにより、コマンドデコーダ2から出力された読出し制御信号RCONが読出し用制御許可回路12#nRを通過して、バンク制御回路10#n内の読出しカウンタ14#nに与えられ、そのカウント値がカウントアップされる。

【0047】

このような読出し後において、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値がカウント比較回路15#nで比較され、一致と判定されれば、メモリバンクMB#nへのリフレッシュ禁止信号がリフレッシュ制御回路7へ出力される。

【0048】

リフレッシュカウンタ6がメモリバンクMB#nへのロウアドレスを出力しても、リフレッシュ制御回路7においてリフレッシュ動作が禁止されているため、メモリバンクMB#nへのリフレッシュ用ロウアドレスがアクセス制御回路5に出力されず、メモリバンクMB#nのリフレッシュ動作は実行されない。

【0049】

ここで、読出し動作に応じて、読出しカウンタ14#nのカウント値をカウントアップした後において、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値が不一致であると、カウント比較回路15#nからリフレッシュ制御回路7へ、該当メモリバンクMB#nへのリフレッシュ許可信号が出力されるので、リフレッシュカウンタ6がメモリバンクMB#nへのロウアドレスを出力する毎に、メモリバンクMB#nがリフレッシュされる。

【0050】

メモリバンクMB#nへパケットデータを書き込んだ回数と同じ回数だけ読出し動作が実行されたときには、書込みカウンタ13#nと読出しカウンタ14#nのカウンタ値が一致し、このとき、リフレッシュ許可信号からリフレッシュ禁止信号へ切り替わり、メモリバンクMB#nのリフレッシュが実行されない状態になる。

【0051】

(A−3)実施形態の効果

上記実施形態によれば、バンクメモリへの書込みデータ数と読出しデータ数との一致、不一致を監視し、不一致の場合に、バンクメモリのリフレッシュを行い、一致した場合に、バンクメモリのリフレッシュを実行しないようにしたので、データ保持が不要なメモリバンクに対してリアルタイムにリフレッシュ動作を停止させることができる。

【0052】

入力パケット間隔が大きくなって入力トラフィックが低下した場合や、入力トラフィックがなくなった場合などでは、書込みデータ数と読出しデータ数とが一致している期間、すなわち、リフレッシュ不要の期間が長くなり、メモリバンクでの電力低減が期待できる。

【0053】

また、上記実施形態によれば、当該パケットバッファ装置が扱うパケットに優先度があり、後で書き込んだ優先パケットのデータをそれより先に書き込んだ他のデータより先に読み出す状況があったとしても、書込みデータ数と読出しデータ数との比較でリフレッシュの有無を決定するので、優先度がない場合と同様に扱うことができる。

【0054】

(B)他の実施形態

上記実施形態のパケットバッファ装置は、通信装置の入力段に設けられるものであっても良く、また、通信装置の出力段に設けられるものであっても良く、通信装置内における設置位置は問われないものである。

【0055】

上記実施形態では、本発明のバッファメモリ装置をパケットバッファ装置に適用したものを示したが、その用途は、パケットバッファ装置に限定されるものではない。すなわち、メモリバンクに一旦格納されるデータの種類はパケットデータに限定されるものではない。

【0056】

また、記憶媒体もDRAMに限定されず、リフレッシュ動作を必要とする記憶媒体を適用しているバッファメモリ装置であれば良い。

【符号の説明】

【0057】

1…パケットバッファ装置、MB#0〜MB#N…メモリバンク、2…コマンドデコーダ、3…アドレスバッファ、4…データバッファ、5…アクセス制御回路、6…リフレッシュカウンタ、7…リフレッシュ制御回路、8…パケット監視回路、10#0〜10#N…バンク制御回路、11…アドレスデコーダ、12#0W〜12#NW、12#0R〜12#NR…制御許可回路、13#0〜13#N…書込みカウンタ、14#0〜14#N…読出しカウンタ、15#0〜15#N…カウント比較回路。

【特許請求の範囲】

【請求項1】

メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うバッファメモリ装置において、

上記メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、

書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段と

を備えることを特徴とするバッファメモリ装置。

【請求項2】

上記メモリブロックに後で書き込んだ優先データをそれより先に書き込んだ他のデータより先に読み出すこともあり得ることを特徴とする請求項1に記載のバッファメモリ装置。

【請求項3】

パケットデータが流れる所定位置にパケットバッファ装置を有する通信装置において、

上記パケットバッファ装置として、請求項1又は2に記載のバッファメモリ装置を適用したことを特徴とする通信装置。

【請求項1】

メモリ空間を複数のブロックに分け、メモリブロック単位で書込みデータのリフレッシュを行うバッファメモリ装置において、

上記メモリブロック毎に、書込みデータ数と読出しデータ数との一致、不一致を判定する一致・不一致判定手段と、

書込みデータ数と読出しデータ数とが一致しているメモリブロックのリフレッシュを禁止し、書込みデータ数と読出しデータ数とが不一致のメモリブロックのリフレッシュを許可するリフレッシュ制御手段と

を備えることを特徴とするバッファメモリ装置。

【請求項2】

上記メモリブロックに後で書き込んだ優先データをそれより先に書き込んだ他のデータより先に読み出すこともあり得ることを特徴とする請求項1に記載のバッファメモリ装置。

【請求項3】

パケットデータが流れる所定位置にパケットバッファ装置を有する通信装置において、

上記パケットバッファ装置として、請求項1又は2に記載のバッファメモリ装置を適用したことを特徴とする通信装置。

【図1】

【図2】

【図2】

【公開番号】特開2013−73644(P2013−73644A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211336(P2011−211336)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(503262509)株式会社オー・エフ・ネットワークス (62)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(503262509)株式会社オー・エフ・ネットワークス (62)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

[ Back to top ]