バランスフィルタ、チップ型バランスフィルタ、及びこれらを備えた電力線通信装置

【課題】小型化可能なバランスフィルタを提供すること。

【解決手段】バランスフィルタは、第1及び第2入力ポートP1,P2を含む平衡入力端子1と、第1及び第2出力ポートP3,P4を含む平衡出力端子2と、前記第1入力ポートP1及び前記第1出力ポートP3の間に接続され、第1コイル素子L21を含む第1第1共振回路31と、前記第2入力ポートP2及び前記第2出力ポートP4の間に接続され、第2コイル素子L22を含む第2共振回路41とを備えている。ここで、前記第1コイル素子L21及び前記第2コイル素子L22は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスM1により互いに結合している。

【解決手段】バランスフィルタは、第1及び第2入力ポートP1,P2を含む平衡入力端子1と、第1及び第2出力ポートP3,P4を含む平衡出力端子2と、前記第1入力ポートP1及び前記第1出力ポートP3の間に接続され、第1コイル素子L21を含む第1第1共振回路31と、前記第2入力ポートP2及び前記第2出力ポートP4の間に接続され、第2コイル素子L22を含む第2共振回路41とを備えている。ここで、前記第1コイル素子L21及び前記第2コイル素子L22は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスM1により互いに結合している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、平衡入力端子・平衡出力端子の間に少なくとも2つの共振回路が接続されたバランスフィルタ及びチップ型バランスフィルタ、並びにこれらを備えた電力線通信装置に関する。

【背景技術】

【0002】

電力線通信(PLC:Power Line Communication)は、電力線を通信回路として利用する技術である。電力線通信では、例えば家庭やオフィスのようなエリア内に張り巡らされた既設の電力線が通信に用いられる。電力線通信技術によれば、新たな通信ケーブルを敷設する必要がなく、上記エリア内に通信ネットワークを手軽に構築することができる。以下、従来の電力線通信装置の一例として、特許文献1に記載されたものについて説明する。

【0003】

従来の電力線通信装置は、特許文献1ではPLCモデムと称され、RF回路やカプラ等を介して電力線に接続される。RF回路は、より具体的に述べると、受信経路上に、電力線からの受信信号に重畳されたノイズを取り除くためのバランスフィルタを有している。

【0004】

従来のバランスフィルタは、図12に示すように、互いに平衡関係にある正相信号及び逆相信号を伝送する一対の線路601,線路602と、該線路601,602に配置されたLC並列共振回路251a3,251a4とを備えている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−232257号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記バランスフィルタの小型化又は積層化を進めようとすると、各LC並列共振回路251a3,251a4(図12参照)が有するコイル素子の配置によっては、各コイル素子から生じる磁界が結合してしまう。このように磁界が結合すると、各コイル素子のインダクタンスが変化するとともに、各コイル素子のQ値が劣化することがある。その結果、バランスフィルタの挿入により大きな損失が生じたり、バランスフィルタの通過特性がなまったりしてしまう。そのため、従来のバランスフィルタには小型化が難しいという問題点があった。特に多段のバランスフィルタの場合、インダクタンスの変化はフィルタ特性に大きな影響を与えるため、性能劣化の原因となる。

【0007】

上記問題点に鑑み、本発明の目的は、小型化可能なバランスフィルタ、チップ型バランスフィルタ、及びこれらを備えた電力線通信装置を提供することである。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明の第1の態様に係るバランスフィルタは、第1及び第2入力ポートを含む平衡入力端子と、第1及び第2出力ポートを含む平衡出力端子と、前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路とを備えている。ここで、前記第1及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している。

【0009】

また、本発明の第2の態様に係るチップ型バランスフィルタでは、複数の磁性体シートを積層してなる磁性体層に、前記第1及び前記第2の共振回路が形成されている。

【0010】

また、本発明の第3の態様に係る電力線通信装置は、前記バランスフィルタ又は前記チップ型バランスフィルタを備えている。

【発明の効果】

【0011】

本発明の各態様によれば、バランスフィルタ、チップ型バランスフィルタ及びこれらを備えた電力線通信装置を小型化することが可能となる。

【図面の簡単な説明】

【0012】

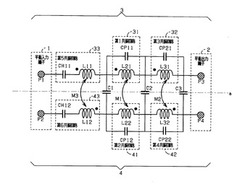

【図1】第1の実施形態に係るバランスフィルタの構成を示す回路図である。

【図2】図1のバランスフィルタ内で形成される各閉磁路を示す模式図である。

【図3】図1のバランスフィルタの素子値及びコイル間の結合係数の一例を示す図である。

【図4】本バランスフィルタの遮断特性及び挿入損失特性の一例を示すグラフである。

【図5】第2の実施形態に係るチップ型バランスフィルタの縦断面図である。

【図6】(A)は、チップ型バランスフィルタの第4非磁性体層の上層側の非磁性体シートの上面図であり、(B)は、同非磁性体層の下層側の非磁性体シートの上面図である。

【図7】(A)〜(E)は、第3磁性体層を構成する各磁性体シート部材を示す上面図である。

【図8】(A)は、第3非磁性体層を構成する非磁性体シートの上面図であり、(B)〜(F)は、第2磁性体層を構成する各磁性体シート層の上面図である。

【図9】(A)は、第2非磁性体層を構成する非磁性体シートの上面図であり、(B)〜(F)は、第1磁性体層を構成する各磁性体シートの上面図である。

【図10】(A)は、チップ型バランスフィルタを構成する第1非磁性体層のシート状部材の上面側を示す図であり、(B)は、同シート状部材の下面側を示す図である。

【図11】第3の実施形態に係る電力線通信装置の構成を示すブロック図である。

【図12】従来のバランスフィルタの構成を示す回路図である。

【発明を実施するための形態】

【0013】

以下、図1〜図4を参照して、第1の実施形態に係るバランスフィルタについて詳説する。図1において、バランスフィルタは、第1及び第2入力ポートP1,P2を有する平衡入力端子1と、第1及び第2出力ポートP3,P4を有する平衡出力端子2とを備えている。本バランスフィルタにおいては、第1入力ポートP1及び第1出力ポートP3の間に第1信号経路3が、また、第2入力ポートP2及び第2出力ポートP4の間に第2信号経路4が形成される。これら第1及び第2信号経路3,4により、差動信号が伝送される平衡伝送線路(差動伝送線路)が構成される。差動信号は、正相信号と、該正相信号に対し180度の位相差を有する逆相信号とからなる。

【0014】

第1信号経路3には第1共振回路31が設けられる。第1共振回路31には、第1コイル素子L21及び第1コンデンサ素子CP11が並列接続される。第2信号経路4には第2共振回路41が設けられる。第2共振回路41には、第2コイル素子L22及び第2コンデンサ素子CP12が並列接続される。各共振回路31,41は、例えばローパスフィルタとして機能する。

【0015】

また、図1に示すように、第1及び第2コイル素子L21,L22は相互インダクタンスM1を介して接続される。また、平衡入力端子1に差動信号が与えられると、各コイル素子L21,L22から磁束が発生する。図2に示すように、この磁束が閉磁路を構成するよう、第1及び第2コイル素子L21,L22は配置される。つまり、両コイル素子L21,L22は互いに逆相で磁界結合している。なお、両コイル素子L21,L22は近接していることが好ましい。

【0016】

上述のとおり、各コイル素子L21,L22からの磁束は閉磁路を構成し、かつ両コイル素子L21,L22は互いに磁気結合している。この構成によれば、両コイル素子L21,L22のインダクタンス値は、2個のコイルが磁気結合等していない場合と比較すると、見かけ上大きくなる。その結果、両コイル素子L21,L22を小型化でき、さらには両コイル素子のQ値の劣化を抑えることができる。このようにQ値の劣化を抑えることで、低挿入損失で急峻な遮断特性を有する小型のバランスフィルタを提供することが可能となる。

【0017】

また、本バランスフィルタでは、図1に示すように、第1信号経路3上で第1共振回路31及び第1出力ポートP3の間に、第3共振回路32が直列接続される。第3共振回路32には、第3コイル素子L31及び第3コンデンサ素子CP21が並列に接続される。また、第2信号経路4上で第2共振回路41及び第2出力ポートP4の間に、第4共振回路42が直列接続される。第4共振回路42には、第4コイル素子L32及び第4コンデンサ素子CP22が並列に接続される。

【0018】

ここで、両コイル素子L31,L32は、両コイル素子L21,L22の場合と同様に、互いに逆相で磁界結合している。なお、両コイル素子L31,L32間の相互インダクタンスはM2である。

【0019】

本バランスフィルタでは、共振回路32,42を共振回路31,41の後段に直列接続することで、2次のローパスフィルタが構成される。これにより、1次のみのものよりも急峻な遮断特性を有するローパスフィルタを実現することが可能となる。なお、本実施形態では2次のローパスフィルタを例示したが、これに限らず、3次以上のローパスフィルタを本バランスフィルタは備えていても構わない。

【0020】

また、本バランスフィルタでは、第1信号経路3上で第1共振回路31及び第1入力ポートP1の間に、第5共振回路33が直列に接続される。第5共振回路33は、第5コンデンサ素子CH11及び第5コイル素子L11を含む直列共振回路である。また、第2信号経路4上で第2共振回路41及び第2入力ポートP2の間に、第6共振回路43が直列に接続される。第6共振回路43は、第6コンデンサ素子CH12及び第6コイル素子L12を含む直列共振回路である。

【0021】

ここで、両コイル素子L11,L12は、両コイル素子L21,L22の場合と同様に、互いに逆相で磁界結合している。なお、両コイル素子L11,L12間の相互インダクタンスはM3である。

【0022】

共振回路33,43により、前記ローパスフィルタの通過帯域における低周波数帯の信号が遮断される。これにより、本バランスフィルタはバンドパスフィルタとして機能することになる。

【0023】

以上の構成のバランスフィルタにおいて、第1及び第2入力ポートP1,P2には正相信号及び逆相信号が入力される。入力正相信号は、共振回路31〜33からなるバンドパスフィルタにより所定の通過帯域に含まれる信号成分のみ抽出され、周波数選択された正相信号が第1出力ポートP3から出力される。また、入力逆相信号は、共振回路41〜43からなるバンドパスフィルタにより上記と実質同一の通過帯域に含まれる信号成分のみ抽出され、周波数選択された逆相信号が第2出力ポートP4から出力される。

【0024】

本実施形態では、第1信号経路3上の各コイル素子L21,L31,L11が実質的に互いに結合しないように、本バランスフィルタは構成される。同様に、第2信号経路4上の各コイル素子L22,L32,L12も相互に結合していない。もし同一信号経路上のコイル同士が結合してしまうと、バランスフィルタが周波数選択性を有さなくなる。例えば図1のコイル素子L21,L31の結合度が極端に高い場合(例えば結合係数kが1の場合)、共振回路31,32からなるフィルタは全域通過フィルタになってしまう。よって、同一信号経路上のコイル素子同士は結合させないようにしている。なお、結合度が低い場合には、バランスフィルタは周波数選択性を有するものの、減衰させたい周波数帯域の減衰量が小さくなってしまう傾向がみられる。

【0025】

また、第1信号経路3と第2信号経路4とは複数のコンデンサ素子により容量結合される。図1の例では、共振回路31,41の入力端同士が第7コンデンサ素子C1で接続される。また、共振回路31,41の出力端同士が第8コンデンサ素子C2で、さらに、共振回路32,42の出力端同士が第9コンデンサ素子C3により接続される。また、共振回路31,41の素子値は互いに実質的に同一である。また、共振回路32,42の素子値も実質的に同一であり、共振回路33,43の素子値も実質的に同一である。したがって、コンデンサ素子C1〜C3にて正相信号及び逆相信号の電位中点(図1の仮想グランドa)が来る。このように、第1信号経路3上の各回路と第2信号経路4上の各回路とは十分な対称性を有することになる。なお、第1信号経路3と第2信号経路4とは、容量結合に限らず、コイル素子を介して結合されても構わない。

【0026】

ここで、図3に示すように、コイル素子L21,L22のインダクタンス値を330nHとし、コイル素子L31,L32については450nHとし、さらにコイル素子L11,L12については550nHとする。また、コンデンサ素子CP11,CP12の容量値を62pFとし、コンデンサ素子CP21,CP22については39pFとし、さらにコンデンサ素子CH11,CH12については980pFとする。また、コンデンサ素子C1,C2,C3の容量値を33pF、18pF及び12pFとする。また、対称関係にある2個のコイル間の結合係数kをそれぞれ0.1とする。

【0027】

上述の素子値の例では、本バランスフィルタ(バンドパスフィルタ)は、図4のような遮断特性を有する。図4において、高域側のカットオフ周波数は、m1で示されるように、概ね3.5dBのゲイン低下点(−3.5dB Compression Point)で概ね30.0MHzである。そして、本バランスフィルタは概ね34.5MHzの周波数成分を44.0dB程度減衰させる(m3を参照)。また、低域側のカットオフ周波数は、m2で示すように、概ね3.7dBのゲイン低下点で概ね2.0MHzである。また、本バランスフィルタは、160.0kHz付近の周波数成分を概ね15.7dB減衰させる(m4を参照)。また、本バランスフィルタの挿入損失については、0〜50MHz帯の広周波数帯域にわたり低損失が実現されている。

【0028】

なお、本バランスフィルタにおいては、2次のローパスフィルタの素子値を調整することで、図4の遮断特性曲線に示されるように、高域側の異なる周波数位置に2個の減衰極が作られている。

【0029】

以上説明した通り、本バランスフィルタでは、まず、第1及び第2コイル素子L21,L22により、閉磁路を構成している。第3及び第4コイル素子L31,L32、さらに、第5及び第6コイル素子L11,L12も同様である。これにより、例えば各コイル素子の巻き数を相対的に減らすことが可能となる。さらに、第1及び第2コイル素子L21,L22は磁気的に結合されている。第3及び第4コイル素子L31,L32、さらに第5及び第6コイル素子L11,L12も同様である。磁気結合により、これらコイル素子が磁気的に結合していない場合と比較して、各コイル素子の見かけ上のインダクタンスを大きくすることができる。上記2つの技術的特徴により、各コイル素子を従来よりも小型化でき、さらにはQ値の劣化も抑えることが可能となる。さらには、低挿入損失で急峻な遮断特性を有しており小型のバランスフィルタを提供することが可能となる。

【0030】

また、本バランスフィルタでは、第1信号経路3上の各コイル素子は実質的に相互に結合しておらず、第2信号経路4上の各コイル素子も実質的に結合していない。これによって、例えば正相信号成分が第7コンデンサ素子C1を超えて第2共振回路41の第2コイル素子L22に入力されないため、逆相信号に位相変化が生じず、その結果、正相信号と逆相信号の位相差180度を確実に維持できるようになる。

【0031】

(第2の実施形態)

次に、図5〜図10を参照して、第2の実施形態に係るチップ型バランスフィルタについて詳説する。本チップ型バランスフィルタは、第1の実施形態のバランスフィルタを表面実装型部品としたものである。それゆえ、図5〜図10のチップ型バランスフィルタにおいて、図1〜図4に示したバランスフィルタの構成に相当するものについては、それぞれの説明を省略する。

【0032】

図5に示すように、チップ型バランスフィルタは、略直方体形状の積層体チップ50を備える。積層体チップ50においては、下面側から上面側に向けて第1非磁性体層51、第1磁性体層52、第2非磁性体層53、第2磁性体層54、第3非磁性体層55、第3磁性体層56及び第4非磁性体層57がこの順番で積層される。各非磁性体層51,53,55,57は、相対的に低い透磁率(例えばμ=1)のフェライト等からなるシート状部材からなる。それに対し、各磁性体層52,54,56は、各前記非磁性体層の透磁率より高い透磁率(例えばμ=100)を有するフェライト等からなるシート状部材を複数枚積層して構成される。磁性体層52,54,56を非磁性体層51,53,55,57で挟むことにより、各磁性体層内に形成されたコイル素子は、他の磁性体層内に形成されたコイル素子との間で磁界結合が発生しにくくなる。これは、磁性体層内に形成されたコイル素子によって発生した磁路がその磁性体層内で閉磁路となるためである。なお、以下の説明では、各非磁性体層を構成するシート状部材を、非磁性体シートと称し、各磁性体層を構成するシート状部材を、磁性体シートと称する。また、図5には各磁性体層及び各非磁性体層も断面を示しているが、図示の都合上、これらにはハッチングをつけていない。

【0033】

まず、最下層となる第1非磁性体層51は、図5及び図10に示すように、非磁性体シート51aを有する。ここで、図10(A)は非磁性体シート51aの上面を、また、図10(B)は非磁性体シート51aの下面を示している。この下面(つまり、積層体チップ50の背面)には、プリント配線板等に実装可能にするため、金属導体からなる入力ポートP1,P2及び出力ポートP3,P4が形成される(図10(B)を参照)。さらに、非磁性体シート51aには、図10(A),(B)に示すように、複数のビアが形成される。具体的には、第1入力ポートP1を導通するように1つのビアが形成され、同様に、第2入力ポートP2、第1及び第2出力ポートP3,P4を導通するよう、1つずつビアが形成される。なお、例示的に、図10(A)では、1つのビアに参照符号51bを付している。

【0034】

次に、最上層の第4非磁性体層57について説明する。第4非磁性体層57は、図6(A),(B)に示すように2枚の非磁性体シート57a,57bを有する。非磁性体シート57aは上側に積層され、非磁性体シート57bは下側に積層される。非磁性体シート57aの上面には、図6(A)においてハッチング部分で示すように金属導体性のランドが形成される。各ランドには第1の実施形態で述べたコンデンサ素子(それぞれを点線で図示)が実装される。さらに、非磁性体シート57aには、各ランドと導通するビアが形成される。また、非磁性体シート57bには、図6(B)に示すように、金属導体性のパターン配線と、複数のビアが形成される。なお、例示的に、図6(A)では、1つのランドに参照符号57cを付しており、図6(B)では、1つのパターン配線に参照符号57dを、また、1つのビアに参照符号57eを付している。

【0035】

なお、図5に示すように、コンデンサ素子CH11,CH12の入力端子電極が前述の入力ポートP1,P2と電気的に接続するように、各層51〜57には適宜ビア及びランドが形成される。

【0036】

次に、3,4層目となる第3非磁性体層55及び第2磁性体層54(図5参照)について説明する。まず、図8(A)に示すように、第3非磁性体層55は、複数のビアが形成された非磁性体シート55aを有する。この非磁性体シート55aは、磁性体層54,56の磁気シールド層として、コイル素子L11,L12とコイル素子L31,L32との間の磁界結合を抑えるように働く。なお、図8(A)では便宜上、1つのビアに参照符号55bを付している。

【0037】

また、図8(B)〜(F)に示すように、第2磁性体層54は、コイル素子L11,L12が形成される磁性体シート54a〜54eを有する。コイル素子L11,L12は内部電極L11a〜L11e,L12a〜L12eを有する。これら内部電極L11a〜L11e,L12a〜L12eは、各磁性体シート54a〜54eの下面に形成される。内部電極L11a〜L11eは、反時計回りの螺旋形状を有するコイル素子L11を形成するように、ビアにより電気的に接続される。また、コイル素子L12が時計回りの螺旋形状を有するように、内部電極L12a〜L12eはビアにより電気的に接続される。

【0038】

また、コイル素子L11は、磁性体シート54e側の入力端子電極INにてコンデンサ素子CH11の出力端子電極OUT(図6(A)参照)と接続される。コイル素子L12は、磁性体シート54a側の入力端子電極INにてコンデンサ素子CH12の出力端子電極OUT(図6(A)参照)と接続される。

【0039】

次に、5,6層目となる第2非磁性体層53及び第1磁性体層52(図5参照)について説明する。まず、第2非磁性体層53は、図9(A)に示すように、複数のビアが形成された非磁性体シート53aを有する。この非磁性体シート53aは、磁性体層52,54の磁気シールド層として、コイル素子L11,L12とコイル素子L21,L22との間の磁界結合を抑えるように働く。なお、図9(A)では1つのビアに参照符号53bを付している。

【0040】

図9(B)〜(F)に示すように、第1磁性体層52は、コイル素子L21,L22が形成される磁性体シート52a〜52eを有する。各磁性体シート52a〜52eの下面には、コイル素子L21を構成する内部電極L21a〜L21eと、コイル素子L22を構成する内部電極L22a〜L22eとが形成される。反時計回りの螺旋形状を有するコイル素子L21が形成されるよう、内部電極L21a〜L21eは接続される。また、時計回りの螺旋形状を有するコイル素子L22が形成されるよう、内部電極L22a〜L22eは接続される。

【0041】

また、コイル素子L21は、磁性体シート52e側の入力端子電極INにて、コイル素子L11の出力端子電極OUT(図8(B)参照)、コンデンサ素子C1,CP11の各出力端子電極OUT(図6(A)参照)と接続される。コイル素子L22は、磁性体シート52a側の入力端子電極INにてコイル素子L12の出力端子電極OUT(図8(F)参照)、コンデンサ素子C1,CP12の各出力端子電極OUT(図6(A)参照)と接続される。

【0042】

次に、上から2層目の第3磁性体層56(図5参照)について説明する。図7(A)〜(E)に示すように、第3磁性体層56は、磁性体シート56a〜56eを有する。各磁性体シート56a〜56eの下面には、コイル素子L31を構成する内部電極L31a〜L31eと、コイル素子L32を構成する内部電極L32a〜L32eとが形成される。反時計回りの螺旋形状を有するコイル素子L31が形成されるよう、内部電極L31a〜L31eは接続される。また、時計回りの螺旋形状を有するコイル素子L32が形成されるよう、内部電極L32a〜L32eは接続される。

【0043】

コイル素子L31は、磁性体シート56e側の入力端子電極INにて、コイル素子L21の出力端子電極OUT(図9(B)参照)、コンデンサ素子CP11の出力端子電極OUT(図6(A)参照)、コンデンサ素子CP21の入力端子電極IN及びコンデンサ素子C2の一方の端子電極と接続される。また、コイル素子L31は、磁性体シート56a側の出力電極OUTにて、コンデンサ素子CP21の出力端子電極OUT(図6(A)参照)、コンデンサ素子C2の他方の端子電極、及び第1出力ポートP3と接続される。

【0044】

コイル素子L32は、磁性体シート56e側の入力端子電極INにて、コイル素子L22の出力端子電極OUT(図9(B)参照)、コンデンサ素子CP12の出力端子電極OUT(図6(A)参照)、コンデンサ素子CP22の入力端子電極IN及びコンデンサ素子C2の一方の端子電極と接続される。また、コイル素子L32は、磁性体シート56e側の出力電極OUTにて、コンデンサ素子CP22の出力端子電極OUT(図6(A)参照)、コンデンサ素子C2の他方の端子電極、及び第2出力ポートP4と接続される。

【0045】

上述した各コイル素子L11,L12を各巻回軸の方向から平面視したとき、それぞれの開口が隣接するよう、各コイル素子L11,L12は第2磁性体層54内に配置されている。これにより、コイル素子L11,L12を通過する磁束が閉磁路を形成するようになる。ここで、各コイル素子L11,L12の場合と同様、各コイル素子L21,L22の開口が隣接するよう、各コイル素子L21,L22は第1磁性体層52内に形成される。また、各コイル素子L31,L32も、同様の手法で第3磁性体層56内に形成される。したがって、各コイル素子L31,L32を通過する磁束、及び各コイル素子L31,L32を通過する磁束はそれぞれ閉磁路を形成する。

【0046】

また、各磁性体層は、上下に配置された2つの非磁性体層の間に形成されている。例えば、第1磁性体層52は、第1非磁性体層51及び第2磁性体層53の間に形成されている。また、図5からも明らかなように、積層体チップ50を上方から平面視した場合、コイル素子L11はコイル素子L21と異なる領域に形成されている。言い換えると、コイル素子L11,L21は、平面視で互いにオーバーラップしないように磁性体層54,52に形成される。このように、各磁性体層を非磁性体層で挟むこと、または閉磁路を形成するような回路構成とすることと併せて、各段のコイル素子を平面視したときに互いに重ならないように形成することで、異なる磁性体層内にある各段のコイル素子間の磁気結合をさらに小さく抑えることができる。コイル素子L21,L22も、コイル素子L11,L21と同様に形成される。また、コイル素子L21,L22は、平面視でコイル素子L31,L32と異なる領域、互いにオーバーラップしないように磁性体層52,56に形成される。以上のようにして、本チップ型バランスフィルタでは、コイル素子L11,L21及びL31が、また、コイル素子L12,L22及びL32は実質的に互いに結合しないように構成されている。

【0047】

(第3の実施形態)

次に、図11を参照して第3の実施形態に係る電力線通信装置について詳説する。図11において、電力線通信装置は、大略的には、PLC通信ブロック60と、カプラ(トランス)70と、電源回路80とを備えている。

【0048】

PLC通信ブロック60は、信号処理回路61及びRF回路62を含んでいる。信号処理回路61は、伝送信号に変復調を行うベースバンドIC(以下、BBICという)、及びメモリ回路としてのSDRAM,FROMを有する。RF回路62は、図示しないDA変換回路、AD変換回路及び可変増幅回路等を有するアナログフロントエンドIC(以下AFEという)、アッテネータ(以下ATTという)、バンドパスフィルタ(以下BPFという)63、パワーアンプ(以下PAという)、ローパスフィルタ(以下LPFという)、DC/DCコンバータ(以下、DC/DCという)を含んでいる。

【0049】

カプラ70及び電源回路80は、コンセントを介して電力線90と接続されている。この電源回路80は、スイッチング電源等で構成されており、DC/DCを介して、AFEやBBIC等の必要な回路に電力を供給する。

【0050】

カプラ70は、電力線90とRF回路62とを接続しており、コイルトランス及び結合コンデンサ等で構成される。

【0051】

以上の構成を有する電力線通信装置は、例えば以下のように動作する。イーサネット(登録商標)を介して入力されたデータは、BBICに送られ、デジタル信号処理を施すことにより、デジタル送信データが生成される。生成されたデジタル送信データは、AFEによりアナログ信号に変換され、LPF、PA及びカプラ70を介して電力線90に出力される。

【0052】

一方、電力線90からの受信信号は、カプラ70及びATTを介してBPFにて処理された後、AFEに入力される。AFEにおいて、入力信号に対し例えばゲイン調整等やデジタル信号への変換が行われ、こうして得られたデジタル信号はBBICに送られる。BBICにおいては、入力デジタル信号に対しデジタル信号処理が施され、デジタルデータが再生される。こうして得られたデジタルデータは、イーサネット(登録商標)を介して出力される。

【0053】

ここで、上記のRF回路62は、バンドパスフィルタ63を備えている。このバンドパスフィルタ63は、第1の実施形態で説明したバランスフィルタ、又は第2の実施形態で説明したチップ型バランスフィルタで構成される。

【0054】

なお、前述したとおり、第1の実施形態で説明したバランスフィルタ、又は第2の実施形態で説明したチップ型バランスフィルタはローパスフィルタを構成しても良い。このようなローパスフィルタとして機能するバランスフィルタ又はチップ型バランスフィルタを、RF回路62のデータ通信の送信系統に備わるローパスフィルタとして用いても構わない。

【産業上の利用可能性】

【0055】

本発明は、典型的には、小型化可能なバランスフィルタ、チップ型バランスフィルタ、及びこれらを備えた電力線通信装置に好適である。他にも、本発明は、USB(Universal Serial Bus)やHDMI(High−Definition Multimedia Interface)のような、平衡伝送線路(差動伝送線路)を用いたインターフェイスにも適用可能である。

【符号の説明】

【0056】

1 平衡入力端子

P1 第1入力ポート

P2 第2入力ポート

2 平衡出力端子

P3 第1出力ポート

P4 第2出力ポート

31 第1共振回路

L21 第1コイル素子

CP11 第1コンデンサ素子

41 第2共振回路

L22 第2コイル素子

CP12 第2コンデンサ素子

【技術分野】

【0001】

本発明は、平衡入力端子・平衡出力端子の間に少なくとも2つの共振回路が接続されたバランスフィルタ及びチップ型バランスフィルタ、並びにこれらを備えた電力線通信装置に関する。

【背景技術】

【0002】

電力線通信(PLC:Power Line Communication)は、電力線を通信回路として利用する技術である。電力線通信では、例えば家庭やオフィスのようなエリア内に張り巡らされた既設の電力線が通信に用いられる。電力線通信技術によれば、新たな通信ケーブルを敷設する必要がなく、上記エリア内に通信ネットワークを手軽に構築することができる。以下、従来の電力線通信装置の一例として、特許文献1に記載されたものについて説明する。

【0003】

従来の電力線通信装置は、特許文献1ではPLCモデムと称され、RF回路やカプラ等を介して電力線に接続される。RF回路は、より具体的に述べると、受信経路上に、電力線からの受信信号に重畳されたノイズを取り除くためのバランスフィルタを有している。

【0004】

従来のバランスフィルタは、図12に示すように、互いに平衡関係にある正相信号及び逆相信号を伝送する一対の線路601,線路602と、該線路601,602に配置されたLC並列共振回路251a3,251a4とを備えている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−232257号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記バランスフィルタの小型化又は積層化を進めようとすると、各LC並列共振回路251a3,251a4(図12参照)が有するコイル素子の配置によっては、各コイル素子から生じる磁界が結合してしまう。このように磁界が結合すると、各コイル素子のインダクタンスが変化するとともに、各コイル素子のQ値が劣化することがある。その結果、バランスフィルタの挿入により大きな損失が生じたり、バランスフィルタの通過特性がなまったりしてしまう。そのため、従来のバランスフィルタには小型化が難しいという問題点があった。特に多段のバランスフィルタの場合、インダクタンスの変化はフィルタ特性に大きな影響を与えるため、性能劣化の原因となる。

【0007】

上記問題点に鑑み、本発明の目的は、小型化可能なバランスフィルタ、チップ型バランスフィルタ、及びこれらを備えた電力線通信装置を提供することである。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明の第1の態様に係るバランスフィルタは、第1及び第2入力ポートを含む平衡入力端子と、第1及び第2出力ポートを含む平衡出力端子と、前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路とを備えている。ここで、前記第1及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している。

【0009】

また、本発明の第2の態様に係るチップ型バランスフィルタでは、複数の磁性体シートを積層してなる磁性体層に、前記第1及び前記第2の共振回路が形成されている。

【0010】

また、本発明の第3の態様に係る電力線通信装置は、前記バランスフィルタ又は前記チップ型バランスフィルタを備えている。

【発明の効果】

【0011】

本発明の各態様によれば、バランスフィルタ、チップ型バランスフィルタ及びこれらを備えた電力線通信装置を小型化することが可能となる。

【図面の簡単な説明】

【0012】

【図1】第1の実施形態に係るバランスフィルタの構成を示す回路図である。

【図2】図1のバランスフィルタ内で形成される各閉磁路を示す模式図である。

【図3】図1のバランスフィルタの素子値及びコイル間の結合係数の一例を示す図である。

【図4】本バランスフィルタの遮断特性及び挿入損失特性の一例を示すグラフである。

【図5】第2の実施形態に係るチップ型バランスフィルタの縦断面図である。

【図6】(A)は、チップ型バランスフィルタの第4非磁性体層の上層側の非磁性体シートの上面図であり、(B)は、同非磁性体層の下層側の非磁性体シートの上面図である。

【図7】(A)〜(E)は、第3磁性体層を構成する各磁性体シート部材を示す上面図である。

【図8】(A)は、第3非磁性体層を構成する非磁性体シートの上面図であり、(B)〜(F)は、第2磁性体層を構成する各磁性体シート層の上面図である。

【図9】(A)は、第2非磁性体層を構成する非磁性体シートの上面図であり、(B)〜(F)は、第1磁性体層を構成する各磁性体シートの上面図である。

【図10】(A)は、チップ型バランスフィルタを構成する第1非磁性体層のシート状部材の上面側を示す図であり、(B)は、同シート状部材の下面側を示す図である。

【図11】第3の実施形態に係る電力線通信装置の構成を示すブロック図である。

【図12】従来のバランスフィルタの構成を示す回路図である。

【発明を実施するための形態】

【0013】

以下、図1〜図4を参照して、第1の実施形態に係るバランスフィルタについて詳説する。図1において、バランスフィルタは、第1及び第2入力ポートP1,P2を有する平衡入力端子1と、第1及び第2出力ポートP3,P4を有する平衡出力端子2とを備えている。本バランスフィルタにおいては、第1入力ポートP1及び第1出力ポートP3の間に第1信号経路3が、また、第2入力ポートP2及び第2出力ポートP4の間に第2信号経路4が形成される。これら第1及び第2信号経路3,4により、差動信号が伝送される平衡伝送線路(差動伝送線路)が構成される。差動信号は、正相信号と、該正相信号に対し180度の位相差を有する逆相信号とからなる。

【0014】

第1信号経路3には第1共振回路31が設けられる。第1共振回路31には、第1コイル素子L21及び第1コンデンサ素子CP11が並列接続される。第2信号経路4には第2共振回路41が設けられる。第2共振回路41には、第2コイル素子L22及び第2コンデンサ素子CP12が並列接続される。各共振回路31,41は、例えばローパスフィルタとして機能する。

【0015】

また、図1に示すように、第1及び第2コイル素子L21,L22は相互インダクタンスM1を介して接続される。また、平衡入力端子1に差動信号が与えられると、各コイル素子L21,L22から磁束が発生する。図2に示すように、この磁束が閉磁路を構成するよう、第1及び第2コイル素子L21,L22は配置される。つまり、両コイル素子L21,L22は互いに逆相で磁界結合している。なお、両コイル素子L21,L22は近接していることが好ましい。

【0016】

上述のとおり、各コイル素子L21,L22からの磁束は閉磁路を構成し、かつ両コイル素子L21,L22は互いに磁気結合している。この構成によれば、両コイル素子L21,L22のインダクタンス値は、2個のコイルが磁気結合等していない場合と比較すると、見かけ上大きくなる。その結果、両コイル素子L21,L22を小型化でき、さらには両コイル素子のQ値の劣化を抑えることができる。このようにQ値の劣化を抑えることで、低挿入損失で急峻な遮断特性を有する小型のバランスフィルタを提供することが可能となる。

【0017】

また、本バランスフィルタでは、図1に示すように、第1信号経路3上で第1共振回路31及び第1出力ポートP3の間に、第3共振回路32が直列接続される。第3共振回路32には、第3コイル素子L31及び第3コンデンサ素子CP21が並列に接続される。また、第2信号経路4上で第2共振回路41及び第2出力ポートP4の間に、第4共振回路42が直列接続される。第4共振回路42には、第4コイル素子L32及び第4コンデンサ素子CP22が並列に接続される。

【0018】

ここで、両コイル素子L31,L32は、両コイル素子L21,L22の場合と同様に、互いに逆相で磁界結合している。なお、両コイル素子L31,L32間の相互インダクタンスはM2である。

【0019】

本バランスフィルタでは、共振回路32,42を共振回路31,41の後段に直列接続することで、2次のローパスフィルタが構成される。これにより、1次のみのものよりも急峻な遮断特性を有するローパスフィルタを実現することが可能となる。なお、本実施形態では2次のローパスフィルタを例示したが、これに限らず、3次以上のローパスフィルタを本バランスフィルタは備えていても構わない。

【0020】

また、本バランスフィルタでは、第1信号経路3上で第1共振回路31及び第1入力ポートP1の間に、第5共振回路33が直列に接続される。第5共振回路33は、第5コンデンサ素子CH11及び第5コイル素子L11を含む直列共振回路である。また、第2信号経路4上で第2共振回路41及び第2入力ポートP2の間に、第6共振回路43が直列に接続される。第6共振回路43は、第6コンデンサ素子CH12及び第6コイル素子L12を含む直列共振回路である。

【0021】

ここで、両コイル素子L11,L12は、両コイル素子L21,L22の場合と同様に、互いに逆相で磁界結合している。なお、両コイル素子L11,L12間の相互インダクタンスはM3である。

【0022】

共振回路33,43により、前記ローパスフィルタの通過帯域における低周波数帯の信号が遮断される。これにより、本バランスフィルタはバンドパスフィルタとして機能することになる。

【0023】

以上の構成のバランスフィルタにおいて、第1及び第2入力ポートP1,P2には正相信号及び逆相信号が入力される。入力正相信号は、共振回路31〜33からなるバンドパスフィルタにより所定の通過帯域に含まれる信号成分のみ抽出され、周波数選択された正相信号が第1出力ポートP3から出力される。また、入力逆相信号は、共振回路41〜43からなるバンドパスフィルタにより上記と実質同一の通過帯域に含まれる信号成分のみ抽出され、周波数選択された逆相信号が第2出力ポートP4から出力される。

【0024】

本実施形態では、第1信号経路3上の各コイル素子L21,L31,L11が実質的に互いに結合しないように、本バランスフィルタは構成される。同様に、第2信号経路4上の各コイル素子L22,L32,L12も相互に結合していない。もし同一信号経路上のコイル同士が結合してしまうと、バランスフィルタが周波数選択性を有さなくなる。例えば図1のコイル素子L21,L31の結合度が極端に高い場合(例えば結合係数kが1の場合)、共振回路31,32からなるフィルタは全域通過フィルタになってしまう。よって、同一信号経路上のコイル素子同士は結合させないようにしている。なお、結合度が低い場合には、バランスフィルタは周波数選択性を有するものの、減衰させたい周波数帯域の減衰量が小さくなってしまう傾向がみられる。

【0025】

また、第1信号経路3と第2信号経路4とは複数のコンデンサ素子により容量結合される。図1の例では、共振回路31,41の入力端同士が第7コンデンサ素子C1で接続される。また、共振回路31,41の出力端同士が第8コンデンサ素子C2で、さらに、共振回路32,42の出力端同士が第9コンデンサ素子C3により接続される。また、共振回路31,41の素子値は互いに実質的に同一である。また、共振回路32,42の素子値も実質的に同一であり、共振回路33,43の素子値も実質的に同一である。したがって、コンデンサ素子C1〜C3にて正相信号及び逆相信号の電位中点(図1の仮想グランドa)が来る。このように、第1信号経路3上の各回路と第2信号経路4上の各回路とは十分な対称性を有することになる。なお、第1信号経路3と第2信号経路4とは、容量結合に限らず、コイル素子を介して結合されても構わない。

【0026】

ここで、図3に示すように、コイル素子L21,L22のインダクタンス値を330nHとし、コイル素子L31,L32については450nHとし、さらにコイル素子L11,L12については550nHとする。また、コンデンサ素子CP11,CP12の容量値を62pFとし、コンデンサ素子CP21,CP22については39pFとし、さらにコンデンサ素子CH11,CH12については980pFとする。また、コンデンサ素子C1,C2,C3の容量値を33pF、18pF及び12pFとする。また、対称関係にある2個のコイル間の結合係数kをそれぞれ0.1とする。

【0027】

上述の素子値の例では、本バランスフィルタ(バンドパスフィルタ)は、図4のような遮断特性を有する。図4において、高域側のカットオフ周波数は、m1で示されるように、概ね3.5dBのゲイン低下点(−3.5dB Compression Point)で概ね30.0MHzである。そして、本バランスフィルタは概ね34.5MHzの周波数成分を44.0dB程度減衰させる(m3を参照)。また、低域側のカットオフ周波数は、m2で示すように、概ね3.7dBのゲイン低下点で概ね2.0MHzである。また、本バランスフィルタは、160.0kHz付近の周波数成分を概ね15.7dB減衰させる(m4を参照)。また、本バランスフィルタの挿入損失については、0〜50MHz帯の広周波数帯域にわたり低損失が実現されている。

【0028】

なお、本バランスフィルタにおいては、2次のローパスフィルタの素子値を調整することで、図4の遮断特性曲線に示されるように、高域側の異なる周波数位置に2個の減衰極が作られている。

【0029】

以上説明した通り、本バランスフィルタでは、まず、第1及び第2コイル素子L21,L22により、閉磁路を構成している。第3及び第4コイル素子L31,L32、さらに、第5及び第6コイル素子L11,L12も同様である。これにより、例えば各コイル素子の巻き数を相対的に減らすことが可能となる。さらに、第1及び第2コイル素子L21,L22は磁気的に結合されている。第3及び第4コイル素子L31,L32、さらに第5及び第6コイル素子L11,L12も同様である。磁気結合により、これらコイル素子が磁気的に結合していない場合と比較して、各コイル素子の見かけ上のインダクタンスを大きくすることができる。上記2つの技術的特徴により、各コイル素子を従来よりも小型化でき、さらにはQ値の劣化も抑えることが可能となる。さらには、低挿入損失で急峻な遮断特性を有しており小型のバランスフィルタを提供することが可能となる。

【0030】

また、本バランスフィルタでは、第1信号経路3上の各コイル素子は実質的に相互に結合しておらず、第2信号経路4上の各コイル素子も実質的に結合していない。これによって、例えば正相信号成分が第7コンデンサ素子C1を超えて第2共振回路41の第2コイル素子L22に入力されないため、逆相信号に位相変化が生じず、その結果、正相信号と逆相信号の位相差180度を確実に維持できるようになる。

【0031】

(第2の実施形態)

次に、図5〜図10を参照して、第2の実施形態に係るチップ型バランスフィルタについて詳説する。本チップ型バランスフィルタは、第1の実施形態のバランスフィルタを表面実装型部品としたものである。それゆえ、図5〜図10のチップ型バランスフィルタにおいて、図1〜図4に示したバランスフィルタの構成に相当するものについては、それぞれの説明を省略する。

【0032】

図5に示すように、チップ型バランスフィルタは、略直方体形状の積層体チップ50を備える。積層体チップ50においては、下面側から上面側に向けて第1非磁性体層51、第1磁性体層52、第2非磁性体層53、第2磁性体層54、第3非磁性体層55、第3磁性体層56及び第4非磁性体層57がこの順番で積層される。各非磁性体層51,53,55,57は、相対的に低い透磁率(例えばμ=1)のフェライト等からなるシート状部材からなる。それに対し、各磁性体層52,54,56は、各前記非磁性体層の透磁率より高い透磁率(例えばμ=100)を有するフェライト等からなるシート状部材を複数枚積層して構成される。磁性体層52,54,56を非磁性体層51,53,55,57で挟むことにより、各磁性体層内に形成されたコイル素子は、他の磁性体層内に形成されたコイル素子との間で磁界結合が発生しにくくなる。これは、磁性体層内に形成されたコイル素子によって発生した磁路がその磁性体層内で閉磁路となるためである。なお、以下の説明では、各非磁性体層を構成するシート状部材を、非磁性体シートと称し、各磁性体層を構成するシート状部材を、磁性体シートと称する。また、図5には各磁性体層及び各非磁性体層も断面を示しているが、図示の都合上、これらにはハッチングをつけていない。

【0033】

まず、最下層となる第1非磁性体層51は、図5及び図10に示すように、非磁性体シート51aを有する。ここで、図10(A)は非磁性体シート51aの上面を、また、図10(B)は非磁性体シート51aの下面を示している。この下面(つまり、積層体チップ50の背面)には、プリント配線板等に実装可能にするため、金属導体からなる入力ポートP1,P2及び出力ポートP3,P4が形成される(図10(B)を参照)。さらに、非磁性体シート51aには、図10(A),(B)に示すように、複数のビアが形成される。具体的には、第1入力ポートP1を導通するように1つのビアが形成され、同様に、第2入力ポートP2、第1及び第2出力ポートP3,P4を導通するよう、1つずつビアが形成される。なお、例示的に、図10(A)では、1つのビアに参照符号51bを付している。

【0034】

次に、最上層の第4非磁性体層57について説明する。第4非磁性体層57は、図6(A),(B)に示すように2枚の非磁性体シート57a,57bを有する。非磁性体シート57aは上側に積層され、非磁性体シート57bは下側に積層される。非磁性体シート57aの上面には、図6(A)においてハッチング部分で示すように金属導体性のランドが形成される。各ランドには第1の実施形態で述べたコンデンサ素子(それぞれを点線で図示)が実装される。さらに、非磁性体シート57aには、各ランドと導通するビアが形成される。また、非磁性体シート57bには、図6(B)に示すように、金属導体性のパターン配線と、複数のビアが形成される。なお、例示的に、図6(A)では、1つのランドに参照符号57cを付しており、図6(B)では、1つのパターン配線に参照符号57dを、また、1つのビアに参照符号57eを付している。

【0035】

なお、図5に示すように、コンデンサ素子CH11,CH12の入力端子電極が前述の入力ポートP1,P2と電気的に接続するように、各層51〜57には適宜ビア及びランドが形成される。

【0036】

次に、3,4層目となる第3非磁性体層55及び第2磁性体層54(図5参照)について説明する。まず、図8(A)に示すように、第3非磁性体層55は、複数のビアが形成された非磁性体シート55aを有する。この非磁性体シート55aは、磁性体層54,56の磁気シールド層として、コイル素子L11,L12とコイル素子L31,L32との間の磁界結合を抑えるように働く。なお、図8(A)では便宜上、1つのビアに参照符号55bを付している。

【0037】

また、図8(B)〜(F)に示すように、第2磁性体層54は、コイル素子L11,L12が形成される磁性体シート54a〜54eを有する。コイル素子L11,L12は内部電極L11a〜L11e,L12a〜L12eを有する。これら内部電極L11a〜L11e,L12a〜L12eは、各磁性体シート54a〜54eの下面に形成される。内部電極L11a〜L11eは、反時計回りの螺旋形状を有するコイル素子L11を形成するように、ビアにより電気的に接続される。また、コイル素子L12が時計回りの螺旋形状を有するように、内部電極L12a〜L12eはビアにより電気的に接続される。

【0038】

また、コイル素子L11は、磁性体シート54e側の入力端子電極INにてコンデンサ素子CH11の出力端子電極OUT(図6(A)参照)と接続される。コイル素子L12は、磁性体シート54a側の入力端子電極INにてコンデンサ素子CH12の出力端子電極OUT(図6(A)参照)と接続される。

【0039】

次に、5,6層目となる第2非磁性体層53及び第1磁性体層52(図5参照)について説明する。まず、第2非磁性体層53は、図9(A)に示すように、複数のビアが形成された非磁性体シート53aを有する。この非磁性体シート53aは、磁性体層52,54の磁気シールド層として、コイル素子L11,L12とコイル素子L21,L22との間の磁界結合を抑えるように働く。なお、図9(A)では1つのビアに参照符号53bを付している。

【0040】

図9(B)〜(F)に示すように、第1磁性体層52は、コイル素子L21,L22が形成される磁性体シート52a〜52eを有する。各磁性体シート52a〜52eの下面には、コイル素子L21を構成する内部電極L21a〜L21eと、コイル素子L22を構成する内部電極L22a〜L22eとが形成される。反時計回りの螺旋形状を有するコイル素子L21が形成されるよう、内部電極L21a〜L21eは接続される。また、時計回りの螺旋形状を有するコイル素子L22が形成されるよう、内部電極L22a〜L22eは接続される。

【0041】

また、コイル素子L21は、磁性体シート52e側の入力端子電極INにて、コイル素子L11の出力端子電極OUT(図8(B)参照)、コンデンサ素子C1,CP11の各出力端子電極OUT(図6(A)参照)と接続される。コイル素子L22は、磁性体シート52a側の入力端子電極INにてコイル素子L12の出力端子電極OUT(図8(F)参照)、コンデンサ素子C1,CP12の各出力端子電極OUT(図6(A)参照)と接続される。

【0042】

次に、上から2層目の第3磁性体層56(図5参照)について説明する。図7(A)〜(E)に示すように、第3磁性体層56は、磁性体シート56a〜56eを有する。各磁性体シート56a〜56eの下面には、コイル素子L31を構成する内部電極L31a〜L31eと、コイル素子L32を構成する内部電極L32a〜L32eとが形成される。反時計回りの螺旋形状を有するコイル素子L31が形成されるよう、内部電極L31a〜L31eは接続される。また、時計回りの螺旋形状を有するコイル素子L32が形成されるよう、内部電極L32a〜L32eは接続される。

【0043】

コイル素子L31は、磁性体シート56e側の入力端子電極INにて、コイル素子L21の出力端子電極OUT(図9(B)参照)、コンデンサ素子CP11の出力端子電極OUT(図6(A)参照)、コンデンサ素子CP21の入力端子電極IN及びコンデンサ素子C2の一方の端子電極と接続される。また、コイル素子L31は、磁性体シート56a側の出力電極OUTにて、コンデンサ素子CP21の出力端子電極OUT(図6(A)参照)、コンデンサ素子C2の他方の端子電極、及び第1出力ポートP3と接続される。

【0044】

コイル素子L32は、磁性体シート56e側の入力端子電極INにて、コイル素子L22の出力端子電極OUT(図9(B)参照)、コンデンサ素子CP12の出力端子電極OUT(図6(A)参照)、コンデンサ素子CP22の入力端子電極IN及びコンデンサ素子C2の一方の端子電極と接続される。また、コイル素子L32は、磁性体シート56e側の出力電極OUTにて、コンデンサ素子CP22の出力端子電極OUT(図6(A)参照)、コンデンサ素子C2の他方の端子電極、及び第2出力ポートP4と接続される。

【0045】

上述した各コイル素子L11,L12を各巻回軸の方向から平面視したとき、それぞれの開口が隣接するよう、各コイル素子L11,L12は第2磁性体層54内に配置されている。これにより、コイル素子L11,L12を通過する磁束が閉磁路を形成するようになる。ここで、各コイル素子L11,L12の場合と同様、各コイル素子L21,L22の開口が隣接するよう、各コイル素子L21,L22は第1磁性体層52内に形成される。また、各コイル素子L31,L32も、同様の手法で第3磁性体層56内に形成される。したがって、各コイル素子L31,L32を通過する磁束、及び各コイル素子L31,L32を通過する磁束はそれぞれ閉磁路を形成する。

【0046】

また、各磁性体層は、上下に配置された2つの非磁性体層の間に形成されている。例えば、第1磁性体層52は、第1非磁性体層51及び第2磁性体層53の間に形成されている。また、図5からも明らかなように、積層体チップ50を上方から平面視した場合、コイル素子L11はコイル素子L21と異なる領域に形成されている。言い換えると、コイル素子L11,L21は、平面視で互いにオーバーラップしないように磁性体層54,52に形成される。このように、各磁性体層を非磁性体層で挟むこと、または閉磁路を形成するような回路構成とすることと併せて、各段のコイル素子を平面視したときに互いに重ならないように形成することで、異なる磁性体層内にある各段のコイル素子間の磁気結合をさらに小さく抑えることができる。コイル素子L21,L22も、コイル素子L11,L21と同様に形成される。また、コイル素子L21,L22は、平面視でコイル素子L31,L32と異なる領域、互いにオーバーラップしないように磁性体層52,56に形成される。以上のようにして、本チップ型バランスフィルタでは、コイル素子L11,L21及びL31が、また、コイル素子L12,L22及びL32は実質的に互いに結合しないように構成されている。

【0047】

(第3の実施形態)

次に、図11を参照して第3の実施形態に係る電力線通信装置について詳説する。図11において、電力線通信装置は、大略的には、PLC通信ブロック60と、カプラ(トランス)70と、電源回路80とを備えている。

【0048】

PLC通信ブロック60は、信号処理回路61及びRF回路62を含んでいる。信号処理回路61は、伝送信号に変復調を行うベースバンドIC(以下、BBICという)、及びメモリ回路としてのSDRAM,FROMを有する。RF回路62は、図示しないDA変換回路、AD変換回路及び可変増幅回路等を有するアナログフロントエンドIC(以下AFEという)、アッテネータ(以下ATTという)、バンドパスフィルタ(以下BPFという)63、パワーアンプ(以下PAという)、ローパスフィルタ(以下LPFという)、DC/DCコンバータ(以下、DC/DCという)を含んでいる。

【0049】

カプラ70及び電源回路80は、コンセントを介して電力線90と接続されている。この電源回路80は、スイッチング電源等で構成されており、DC/DCを介して、AFEやBBIC等の必要な回路に電力を供給する。

【0050】

カプラ70は、電力線90とRF回路62とを接続しており、コイルトランス及び結合コンデンサ等で構成される。

【0051】

以上の構成を有する電力線通信装置は、例えば以下のように動作する。イーサネット(登録商標)を介して入力されたデータは、BBICに送られ、デジタル信号処理を施すことにより、デジタル送信データが生成される。生成されたデジタル送信データは、AFEによりアナログ信号に変換され、LPF、PA及びカプラ70を介して電力線90に出力される。

【0052】

一方、電力線90からの受信信号は、カプラ70及びATTを介してBPFにて処理された後、AFEに入力される。AFEにおいて、入力信号に対し例えばゲイン調整等やデジタル信号への変換が行われ、こうして得られたデジタル信号はBBICに送られる。BBICにおいては、入力デジタル信号に対しデジタル信号処理が施され、デジタルデータが再生される。こうして得られたデジタルデータは、イーサネット(登録商標)を介して出力される。

【0053】

ここで、上記のRF回路62は、バンドパスフィルタ63を備えている。このバンドパスフィルタ63は、第1の実施形態で説明したバランスフィルタ、又は第2の実施形態で説明したチップ型バランスフィルタで構成される。

【0054】

なお、前述したとおり、第1の実施形態で説明したバランスフィルタ、又は第2の実施形態で説明したチップ型バランスフィルタはローパスフィルタを構成しても良い。このようなローパスフィルタとして機能するバランスフィルタ又はチップ型バランスフィルタを、RF回路62のデータ通信の送信系統に備わるローパスフィルタとして用いても構わない。

【産業上の利用可能性】

【0055】

本発明は、典型的には、小型化可能なバランスフィルタ、チップ型バランスフィルタ、及びこれらを備えた電力線通信装置に好適である。他にも、本発明は、USB(Universal Serial Bus)やHDMI(High−Definition Multimedia Interface)のような、平衡伝送線路(差動伝送線路)を用いたインターフェイスにも適用可能である。

【符号の説明】

【0056】

1 平衡入力端子

P1 第1入力ポート

P2 第2入力ポート

2 平衡出力端子

P3 第1出力ポート

P4 第2出力ポート

31 第1共振回路

L21 第1コイル素子

CP11 第1コンデンサ素子

41 第2共振回路

L22 第2コイル素子

CP12 第2コンデンサ素子

【特許請求の範囲】

【請求項1】

第1及び第2入力ポートを含む平衡入力端子と、

第1及び第2出力ポートを含む平衡出力端子と、

前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、

前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路と、を備え、

前記第1コイル素子及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している、

バランスフィルタ。

【請求項2】

前記第1共振回路は、前記第1コイル素子と、該第1コイル素子に並列接続される第1コンデンサ素子とからなる並列共振回路であり、

前記第2共振回路は、前記第2コイル素子と、該第2コイル素子に並列接続される第2コンデンサ素子とからなる並列共振回路である、

請求項1に記載のバランスフィルタ。

【請求項3】

前記バランスフィルタは、さらに、

前記第3コイル素子と、該第3コイル素子に並列接続される第3コンデンサ素子とからなる第3共振回路と、

前記第4コイル素子と、該第4コイル素子に並列接続される第4コンデンサ素子とからなる第4共振回路と、を備え、

前記第3共振回路は前記第1共振回路の後段に直列接続され、前記第4共振回路は前記第2共振回路の後段に直列接続される、

請求項1又は2に記載のバランスフィルタ。

【請求項4】

前記バランスフィルタは、さらに、

前記第5コイル素子と、該第5コイル素子に直列接続される第5コンデンサ素子とからなる第5共振回路と、

前記第6コイル素子と、該第6コイル素子に並列接続される第6コンデンサ素子とからなる第6共振回路と、を備える、

請求項1〜3のいずれかに記載のバランスフィルタ。

【請求項5】

第1及び第2入力ポートを含む平衡入力端子と、

第1及び第2出力ポートを含む平衡出力端子と、

前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、

前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路と、

複数の磁性体シートを積層してなり、前記第1共振回路及び前記第2共振回路が形成される第1磁性体層と、を備え、

前記第1コイル素子及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している、

チップ型バランスフィルタ。

【請求項6】

前記第1及び前記第2コイル素子の巻回軸方向から平面視したとき、前記第1及び前記第2コイル素子の開口が互いに隣接するように、前記第1及び前記第2コイル素子は前記第1磁性体層に形成される、

請求項5に記載のチップ型バランスフィルタ。

【請求項7】

前記チップ型バランスフィルタは、さらに、

前記第3コイル素子を含み、前記第1共振回路の後段に直列接続される第3共振回路と、

前記第4コイル素子を含み、前記第2共振回路の後段に直列接続される第4共振回路と、

複数の磁性体シートを積層してなり、前記第3共振回路及び前記第4共振回路が形成される第2磁性体層と、

前記第1磁性体層と前記第2磁性体層との間に形成される非磁性体層と、を備える、

請求項5又は6に記載のチップ型バランスフィルタ。

【請求項8】

前記第3及び前記第4コイル素子の巻回軸方向から平面視したとき、前記第3及び前記第4コイル素子の開口が互いに隣接するように、前記第3及び前記第4コイル素子は前記第2磁性体層に形成される、

請求項7に記載のチップ型バランスフィルタ。

【請求項9】

前記第1〜第4コイル素子の各巻回軸方向から平面視したとき、前記第1及び前記第3コイル素子は互いに異なる領域に形成され、前記第2及び前記第4コイル素子は互いに異なる領域に形成される、

請求項7又は8に記載のチップ型バランスフィルタ。

【請求項10】

請求項1〜4のいずれかに記載のバランスフィルタ、又は請求項5〜9のいずれかに記載のチップ型バランスフィルタを備える、

電力線通信装置。

【請求項1】

第1及び第2入力ポートを含む平衡入力端子と、

第1及び第2出力ポートを含む平衡出力端子と、

前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、

前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路と、を備え、

前記第1コイル素子及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している、

バランスフィルタ。

【請求項2】

前記第1共振回路は、前記第1コイル素子と、該第1コイル素子に並列接続される第1コンデンサ素子とからなる並列共振回路であり、

前記第2共振回路は、前記第2コイル素子と、該第2コイル素子に並列接続される第2コンデンサ素子とからなる並列共振回路である、

請求項1に記載のバランスフィルタ。

【請求項3】

前記バランスフィルタは、さらに、

前記第3コイル素子と、該第3コイル素子に並列接続される第3コンデンサ素子とからなる第3共振回路と、

前記第4コイル素子と、該第4コイル素子に並列接続される第4コンデンサ素子とからなる第4共振回路と、を備え、

前記第3共振回路は前記第1共振回路の後段に直列接続され、前記第4共振回路は前記第2共振回路の後段に直列接続される、

請求項1又は2に記載のバランスフィルタ。

【請求項4】

前記バランスフィルタは、さらに、

前記第5コイル素子と、該第5コイル素子に直列接続される第5コンデンサ素子とからなる第5共振回路と、

前記第6コイル素子と、該第6コイル素子に並列接続される第6コンデンサ素子とからなる第6共振回路と、を備える、

請求項1〜3のいずれかに記載のバランスフィルタ。

【請求項5】

第1及び第2入力ポートを含む平衡入力端子と、

第1及び第2出力ポートを含む平衡出力端子と、

前記第1入力ポート及び前記第1出力ポートの間に接続され、第1コイル素子を含む第1共振回路と、

前記第2入力ポート及び前記第2出力ポートの間に接続され、第2コイル素子を含む第2共振回路と、

複数の磁性体シートを積層してなり、前記第1共振回路及び前記第2共振回路が形成される第1磁性体層と、を備え、

前記第1コイル素子及び前記第2コイル素子は、それぞれから生じる磁束が閉磁路を構成するよう配置され、かつ相互インダクタンスにより互いに結合している、

チップ型バランスフィルタ。

【請求項6】

前記第1及び前記第2コイル素子の巻回軸方向から平面視したとき、前記第1及び前記第2コイル素子の開口が互いに隣接するように、前記第1及び前記第2コイル素子は前記第1磁性体層に形成される、

請求項5に記載のチップ型バランスフィルタ。

【請求項7】

前記チップ型バランスフィルタは、さらに、

前記第3コイル素子を含み、前記第1共振回路の後段に直列接続される第3共振回路と、

前記第4コイル素子を含み、前記第2共振回路の後段に直列接続される第4共振回路と、

複数の磁性体シートを積層してなり、前記第3共振回路及び前記第4共振回路が形成される第2磁性体層と、

前記第1磁性体層と前記第2磁性体層との間に形成される非磁性体層と、を備える、

請求項5又は6に記載のチップ型バランスフィルタ。

【請求項8】

前記第3及び前記第4コイル素子の巻回軸方向から平面視したとき、前記第3及び前記第4コイル素子の開口が互いに隣接するように、前記第3及び前記第4コイル素子は前記第2磁性体層に形成される、

請求項7に記載のチップ型バランスフィルタ。

【請求項9】

前記第1〜第4コイル素子の各巻回軸方向から平面視したとき、前記第1及び前記第3コイル素子は互いに異なる領域に形成され、前記第2及び前記第4コイル素子は互いに異なる領域に形成される、

請求項7又は8に記載のチップ型バランスフィルタ。

【請求項10】

請求項1〜4のいずれかに記載のバランスフィルタ、又は請求項5〜9のいずれかに記載のチップ型バランスフィルタを備える、

電力線通信装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−48321(P2013−48321A)

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願番号】特願2011−185604(P2011−185604)

【出願日】平成23年8月29日(2011.8.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年3月7日(2013.3.7)

【国際特許分類】

【出願日】平成23年8月29日(2011.8.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]