バーコードセット及びバーコード読取装置

【課題】同一物品間において各物品を識別するためにバーコードを利用する際に、各物品に付されたバーコード間で、見た目の統一性を図ると共に、肉眼でのバーコードの内容の認識が困難なバーコードを提供することである。

【解決手段】 各トレーディングカード17のデータビット43の全長に応じて、適切な長さのダミービット49を付加し、又は、付加しない。ダミービット49によって、全種類のバーコード21の全長を揃えている。

【解決手段】 各トレーディングカード17のデータビット43の全長に応じて、適切な長さのダミービット49を付加し、又は、付加しない。ダミービット49によって、全種類のバーコード21の全長を揃えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、各々が割り当てられた同一物品に付される複数の異なるバーコードからなるバーコードセット、それらのバーコードを読み取るためのバーコード読取装置、及びそれらの関連技術に関する。

【背景技術】

【0002】

特許文献1には、特定の形状を有する絵柄の内部にバーコードを設け、さらに、バーコードの前後に意味のないバーを付加することによって、より絵柄をそれらしく見せ、バーコードのデザイン性を高めるという発明が開示されている。

【0003】

特許文献1の従来技術では、バーコードのマージン(読取のために必要な余白)の外側にダミーバーを配置するか(つまり、ダミーバーがバーコードの一部を構成しない)、ダミーバーの色をバーコード読取装置に認識不可能な色にするなど、ダミーバーが、バーコード読取装置によって読み取られないように工夫されている。こうすることで、実体的な情報を表しているバーのみがバーコード読取装置によって読み取られるので、実体的な情報の正確な読取が担保される。

【0004】

【特許文献1】特開平9−212611

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、通常、バーコードは、ある商品群を他の商品群と識別するために使用される。つまり、同一商品には同一のバーコードが付される。従って、同一商品間で異なるバーコードが付されることはない。従って、特許文献1では、このような通常のバーコードに、ダミーバーを付加することを意図していると考えられる。このため、絵柄並びにその内部のダミーバー及びバーコードは、同一商品間では同一となる。つまり、特許文献1では、同一商品間において、全てのダミーバー及び全てのバーは同一である。

【0006】

ところが、同一物品間において各物品を識別するためにバーコードを使用することもある。この場合、当然、付されるバーコードは、物品間で異なってくる。つまり、バーコードの全長が、物品間で異なってくるのである。これでは、見た目も好ましくない。また、用途によっては、肉眼によってバーコードの内容を認識でき難いほうが好ましい場合もある。しかし、バーコードの全長が物品間で異なることは、肉眼によるバーコードの内容の認識を手助けすることになる。

【0007】

そこで、本発明の目的は、同一物品間において各物品を識別するためにバーコードを利用する際に、各物品に付されたバーコード間で、見た目の統一性を図ると共に、肉眼でのバーコードの内容の認識が困難なバーコードセット及びその関連技術を提供することである。

【課題を解決するための手段】

【0008】

本発明の第1の観点によると、バーコードセットは、各々が割り当てられた同一物品に付される複数の異なるバーコードからなり、前記バーコードの各々は、実体的な情報を表すデータビットと、前記実体的な情報を表さないダミービットと、を含み、前記バーコードの全長が所定長を基準に所定範囲に属するように、前記データビットに前記ダミービットが付加され、前記データビットは、スペースとバーとの組み合わせからなり、前記ダミービットは、スペースとダミーバーとの組み合わせからなる。

【0009】

この構成によれば、同一物品間において各物品を識別するためにバーコードを利用する際に、各物品間でデータビットの全長が異なる場合でも、ダミービットを付加することによって、バーコード間で全長を揃えることができる。その結果、各物品に付されたバーコード間で見た目の統一性を図ることができる。また、肉眼でのバーコードの内容の認識を困難にすることができる。

【0010】

ここで、所定範囲は0を含む。所定範囲が0の場合、全てのバーコードの全長が所定長となる。もちろん、所定範囲は、負から正の範囲であってもよいし、負の範囲でもよいし、正の範囲でもよい。

【0011】

また、データビットは、広義の意味に用いられ、少なくとも実体的な情報を含み、スタートビット、ストップビット、及びチェックサム等の、ダミービット以外の他の情報を含む広い概念である。

【0012】

上記バーコードセットにおいて、前記データビットは、合計幅が第1の所定幅からなる前記スペース及び前記バーから構成される第1の単位データビット、合計幅が前記第1の所定幅より大きい第2の所定幅からなる前記スペース及び前記バーから構成される第2の単位データビット、又はそれらの組み合わせからなり、前記第1の単位データビットは、論理0あるいは論理1のいずれかを示し、前記第2の単位データビットは、前記第1の単位データビットが示す論理と逆の論理を示す。

【0013】

この構成によれば、広狭2つの単位データビットを用いてデータビットを構成するので、バーコード間でデータビットの広狭が発生し又は目立ち易くなり、それ故、ダミービットを付加することの上記意義がより大きくなる。最も極端な例は、あるデータビットが全て第1の単位データビットからなり、別のデータビットが全て第2の単位データビットからなる場合であり、この場合は、データビットの全長の差が最も大きい。

【0014】

このバーコードセットにおいて、前記ダミービットは、単数又は複数の単位ダミービットからなり、前記単位ダミービットは、合計幅が第3の所定幅からなる前記スペース及び前記ダミーバーから構成され、前記第3の所定幅は、前記第1の所定幅及び前記第2の所定幅と異なる。

【0015】

この構成によれば、単位ダミービットの幅が、第1の単位データビットの幅及び第2の単位データビットの幅と異なるので、バーコードの見た目のバリエーションを増やすことができる。

【0016】

上記バーコードセットにおいて、前記ダミービットに代えて、図画、文字、数字及び/又は記号を前記データビットに付加することもできる。この構成によれば、より装飾的効果を高めることができる。

【0017】

上記バーコードセットにおいて、前記バーコードが付される前記物品は、トレーディングカードである。

【0018】

一般に、トレーディングカードは、それに付された図柄が重要な要素であり、その図柄がコレクターの収集意欲を喚起する要因の1つでもある。従って、ダミービットを付加して、トレーディングカード間でバーコードの全長を揃え、見た目を良くする意義は大きい。

【0019】

本発明の第2の観点によると、バーコード読取装置は、上記バーコードセットを構成する前記各バーコードを読み取るバーコード読取装置であって、前記バーコードをスキャンし、そのバーコードに応じた電気信号を出力するスキャン手段と、前記バーコードに応じた前記電気信号を解析して、前記バーコードが表す情報を取得する解析手段と、前記バーコードが表す前記情報から前記ダミービットが表す情報を抽出して、抽出した前記ダミービットが表す前記情報に基づいてエラーチェックを行うエラーチェック手段と、を備える。

【0020】

この構成によれば、ダミービットを装飾目的だけでなく、エラーチェックのためにも利用できる。言わば、一石二鳥である。

【0021】

上記バーコード読取装置は、前記バーコードに含まれる前記ダミービットのビット数の情報とそのバーコードの前記データビットが表す前記実体的な情報とを関連付けたテーブルをさらに備え、前記エラーチェック手段は、スキャンされた前記ダミービットのビット数を計数し、その計数値及びスキャンされた前記データビットの前記実体的な情報と、前記テーブルに格納された前記ダミービットのビット数の前記情報及び前記データビットが表す前記実体的な情報と、に基づいて、エラーの有無を判定する。この構成によれば、テーブルを持つだけで、簡易にエラーチェックを行うことができる。

【0022】

上記バーコード読取装置において、前記エラーチェック手段は、予め設定された情報に基づいて、前記バーコードが表す前記情報から前記ダミービットが表す前記情報を抽出する。

【0023】

例えば、前記予め設定された情報は、前記データビットのビット数の情報である。バーコードの情報には、データビットの情報及びダミービットの情報が含まれるところ、この構成によれば、データビットのビット数が分かるので、データビットとダミービットとの境界を容易に認識でき、それ故、容易にダミービットの情報を抽出できる。

【0024】

上記バーコード読取装置において、前記エラーチェック手段は、前記データビットに含まれるチェックサムの情報に基づいてエラーチェックを行う。この構成によれば、ダミービットによるエラーチェックに加えて、チェックサムによるエラーチェックも行われるので、得られたデータの信頼性の向上をより図ることができる。

【発明を実施するための最良の形態】

【0025】

以下、本発明の実施の形態について、図面を参照しながら説明する。なお、図中、同一又は相当部分については同一の参照符号を付してその説明を援用する。また、本実施の形態において、0bは二進数を表す。

【0026】

図1は、本発明の実施の形態によるゲームシステムの全体構成を示す図である。図1に示すように、このゲームシステムは、1P(第1プレイヤ)用のゲーム機1A、2P(第2プレイヤ)用のゲーム機1B、テレビジョンモニタ3、及び複数枚のトレーディングカード17を含む。本実施の形態では、このシステムによって、サッカーゲームを行う例を挙げる。

【0027】

ゲーム機1Aとゲーム機1Bとは、ケーブル6によって接続される。ゲーム機1Aは、A/Vケーブル5により、テレビジョンモニタ3に接続される。また、図示していないが、ゲーム機1Aには、ACアダプタ又は電池により、電源電圧が供給される。そして、ゲーム機1Aは、ケーブル6を通して、ゲーム機1Bへ電源電圧を供給する。

【0028】

第1プレイヤ及び第2プレイヤは、それぞれゲーム機1A及び1Bの入力ボタン12〜16(後述)を操作して、テレビジョンモニタ3上の自分のチームの選手キャラクタを動かし、相手チームと対戦する。この場合、当初、選手キャラクタごとに異なる能力のデフォルト値が設定される。この場合の能力とは、選手キャラクタが有するサッカープレイにおけるポテンシャルのことであり、例えば、ロングキック速度、ロングキック威力、シュート能力、ヘディングの高さ、及びドリブル速度等である。ただし、各選手キャラクタの能力は、対応するトレーディングカード17に付されたバーコード21(後述)を読み取ることによって変更可能である。

【0029】

次に、ゲームシステムを構成する各要素について詳しく説明する。

【0030】

図2(a)は、図1のトレーディングカード17の表の面を示す図であり、図2(b)は、図1のトレーディングカード17の裏の面を示す図である。図2(a)に示すように、トレーディングカード17の表には、サッカー選手の写真が印刷される。一方、図2(b)に示すように、トレーディングカード17の裏には、一方の長辺に沿って、帯状のバーコード領域38が設けられ、この領域38に、短辺に平行な黒色のバーと白色のスペースとの組み合わせからなるバーコード21が印刷される。バーコード領域38以外の領域には、サッカー選手のプロフィールが印刷される。

【0031】

より具体的には、トレーディングカード17の裏の面のバーコード領域38において、バーコード21の先頭のバーは、一方の短辺から距離LSの位置に印刷される。そして、バーコード21の最後尾のバーは、先頭のバーから距離LBの位置に印刷される。つまり、トレーディングカード17の長辺に沿った長さLBは、バーコード21の全長である。最後尾のバーから、他方の短辺までは、距離LEである。

【0032】

バーコード21のスキャンは、先頭のバーから最後尾のバーへ向かって実行される。従って、先頭のバーに近い、バーコード領域38のエッジ(図中下側の短辺の一部)を、入力エッジ80と呼ぶことにする。

【0033】

本実施の形態では、実体的な情報の内容が異なるバーコード21が印刷された124種類のトレーディングカード17を用意する。この場合、1人のサッカー選手に対して、4種類のトレーディングカード17が用意される。従って、上記のように、トレーディングカード17によって、テレビジョンモニタ3に表示される選手キャラクタの能力を設定できるので、一体の選手キャラクタの能力は、デフォルトを含めると、異なる5つの能力のいずれかに設定できる。

【0034】

図3(a)は、ゲーム機1Aの斜視図であり、図3(b)は、ゲーム機1Aの平面図であり、図3(c)は、図3(b)のA−A線によるゲーム機1Aの断面図である。

【0035】

図3(a)及び図3(b)を参照して、ゲーム機1Aの上面には、プレイヤがサッカーゲームの進行(主として選手キャラクタ)をコントロールするための入力ボタン12〜16が設けられる。また、ゲーム機1Aには、入力ボタン14の外側に、溝部8が形成される。この溝部8は、トレーディングカード17のバーコード21をスキャンするためのスキャン装置の一部を構成し、平面視において、直線状となっている。ただし、溝部8の入口側60は、入力ボタン14側の壁面64に対向する壁面が、平面視において、外側に広がっている。

【0036】

図3(c)を参照して、溝部8の壁面64には、入口側60の端部と出口側62の端部との中間位置にスリット70が形成される。このスリット70の高さは、バーコード21の一本のバーの長さより小さく設定され、スリット70の幅は、バーコード21の一本のバーの幅より小さく設定される。

【0037】

壁面64の後ろ側であって、かつ、スリット70の後ろ側には、スリット70の長手方向に(つまり、バーコード21のバーの長手方向に)、スキャン装置の他の一部を構成する赤外発光ダイオード72及びフォトトランジスタ74が配置される。溝部8の深さは、バーコード21の一本のバーの長さより深くなるように形成される。ここで、バーの長さとは、トレーディングカード17の短辺に沿った長さのことを指し、バーの幅とは、トレーディングカード17の長辺に沿った長さのことを指す。

【0038】

プレイヤは、トレーディングカード17のバーコード21を、溝部8の壁面64と対面するように向けて、トレーディングカード17の入力エッジ80を、溝部8の入口側60から差し込み、トレーディングカード17のバーコード領域38側の長辺を、溝部8の平坦な底部61に沿ってスライドさせ、出口側62から抜き出す。

【0039】

そうすると、赤外発光ダイオード72からの赤外光は、バーコード21に照射され、そして、バーコード21に反射されて、フォトトランジスタ74に入射する。この場合、バーコード21の白色のスペースは、黒色のバーよりも、より強く赤外光を反射するので、白色のスペースが反射した赤外光がフォトトランジスタ74に入射する場合が、黒色のバーが反射した赤外光がフォトトランジスタ74に入射する場合よりも、フォトトランジスタ74の出力レベルは大きくなる。従って、上記のようにトレーディングカード17を溝部8に沿ってスライドさせることにより、フォトトランジスタ74からは、バーコード21のパターンに応じたパルス信号が出力される。ゲーム機1Aは、このパルス信号を解析して、バーコード21の情報を読み取り、選手キャラクタに反映させる。

【0040】

図4は、ゲーム機1Aの電気的構成を説明するブロック図である。図4に示すように、ゲーム機1Aは、プロセッサ23、検知ユニット25、操作スイッチ28、ROM(read only memory)27、及びバス26を含む。

【0041】

検知ユニット25は、上述の赤外発光ダイオード72及びフォトトランジスタ74を含み、さらに、フォトトランジスタ74の出力信号を増幅・反転・整形して出力するアンプ(図示せず)を含む。従って、フォトトランジスタ74の出力信号を反転した信号がプロセッサ23に入力される。つまり、検知ユニット25からプロセッサ23に入力されるパルス信号の高いレベルは、黒色のバーに対応し、低いレベルは、白色のスペースに対応する。ただし、検知ユニット25は、必ずしも反転出力する必要はなく、反転せずに出力してもよい。

【0042】

上記のように、フォトトランジスタ74の出力信号は、トレーディングカード17のバーコード21のパターンに応じたパルス信号なので、プロセッサ23は、検知ユニット25からのパルス信号を解析して、バーコード21の情報を読み取り、選手キャラクタに反映させる。

【0043】

操作スイッチ28は、上記の入力ボタン12〜16を含む。プロセッサ23は、これらからのオン/オフ信号を受けて、第1プレイヤの選手キャラクタを動かしたり、その他のゲームの進行を制御する。

【0044】

ところで、図1のゲーム機1Bは、ゲーム機1Aと同様の構成を有する。従って、ゲーム機1Bは、ゲーム機1Aの入力ボタン12〜16と同様の入力ボタン12〜16を有する。ただし、ゲーム機1Bには、プロセッサ23、バス26、ROM27、及び検知ユニット25は搭載されず、溝部8も形成されない。

【0045】

従って、図4に示すように、ゲーム機1Bの入力ボタン12〜16のオン/オフ信号は、ケーブル6により、ゲーム機1Aに伝送され、プロセッサ23は、これらからのオン/オフ信号を受けて、第2プレイヤの選手キャラクタを動かしたり、その他のゲームの進行を制御する。

【0046】

また、プロセッサ23は、バス26を通じて、ROM27にアクセスできる。従って、プロセッサ23は、ROM27に格納されたプログラムを実行でき、また、ROM27に格納されたデータをリードして処理することができる。このROM27に、後述のフローチャートで示される各処理を行うプログラム、画像データ、及び音声データ等が予め格納される。

【0047】

つまり、プロセッサ23は、ROM27に格納されたプログラムを実行し、ゲーム機1A及び1Bの入力ボタン12〜16のオン/オフ信号に基づいて、各種演算、グラフィック処理、及びサウンド処理を実行して、ROM27に格納された画像データ及び音声データからビデオ信号VD及びオーディオ信号AUを生成する。プロセッサ23が生成したビデオ信号VDおよびオーディオ信号AUは、A/Vケーブル5を介して、テレビジョンモニタ3に与えられ、応じて、テレビジョンモニタ3に映像が表示され、そのスピーカ(図示せず)から音声が出力される。

【0048】

図5は、図4のプロセッサ23の電気的構成を示すブロック図である。図5に示すように、このプロセッサ23は、中央演算処理装置(CPU:central processing unit)101、グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、DMA(direct memory access)コントローラ109、第1バスアービタ113、第2バスアービタ114、バックアップコントロール回路115、メインメモリ117、タイマ回路119、A/Dコンバータ(ADC:analog to digital converter)120、入出力制御回路121、外部メモリインタフェース回路123、クロックドライバ129、PLL(phase−locked loop)回路127、低電圧検出回路125、第1バス131、及び第2バス133を含む。

【0049】

本実施の形態では、メインメモリ117及びROM27を区別して説明する必要がないときは、「メモリMEM」と表記する。

【0050】

CPU101は、メモリMEMに格納されたプログラムに従い、各種演算やシステム全体の制御を行う。CPU101は、第1バス131及び第2バス133のバスマスタであり、それぞれのバスに接続された資源にアクセスが可能である。

【0051】

グラフィックプロセッサ103は、第1バス131及び第2バス133のバスマスタであり、メモリMEMに格納されたデータを基に、グラフィックデータを合成し、さらにこれを基にテレビジョンモニタ3に合わせたビデオ信号VDを生成して出力する。ここで、グラフィックデータは、バックグラウンドスクリーンとスプライトとビットマップスクリーンとから合成される。また、グラフィックプロセッサ103は、第1バス131を通じて、CPU101により制御され、また、CPU101に対して、割込み要求信号INRQを発生する機能を有する。

【0052】

ピクセルプロッタ105は、第1バス131を通じて、CPU101により制御され、CPU101から与えられたピクセルデータの描画を実行する。この場合、ピクセル単位での描画が可能である。ここで言うピクセルデータは、1ピクセルの表示色をMビット(Mは1以上の整数)で表したデータである。また、ピクセルプロッタ105は、キャッシュシステムにより、高速な描画と効率的なバス(第1バス131及び第2バス133)の使用を実現している。さらに、ピクセルプロッタ105は、第1バス131及び第2バス133のバスマスタであり、キャッシュ(図示せず)からメモリMEMへのライト及びメモリMEMからキャッシュへのライトを自律的に行うことができる。

【0053】

サウンドプロセッサ107は、第1バス131及び第2バス133のバスマスタであり、メモリMEMに格納されたデータを基に、サウンドデータを合成し、さらにこれを基にオーディオ信号AUを生成して出力する。サウンドデータは、基本の音色となるPCM(パルスコードモジュレーション)データに対し、ピッチ変換及び振幅変調を行い合成される。振幅変調では、CPU101によって指示されるボリューム制御の他に、楽器の波形を再現するためのエンベロープ制御の機能が用意される。また、サウンドプロセッサ107は、第1バス131を通じて、CPU101により制御され、また、CPU101に対して、割込み要求信号INRQを発生する機能を有する。

【0054】

DMAコントローラ109は、外部バス26に接続されたROM27から、メインメモリ117へのデータ転送を司る。また、DMAコントローラ109は、データ転送の完了を通知するために、CPU101に対する割込み要求信号INRQを発生する機能を有する。さらに、DMAコントローラ109は、第1バス131及び第2バス133のバスマスタであり、また、第1バス131を通じてCPU101により制御される。

【0055】

メインメモリ117は、マスクROM、SRAM、及び、DRAMのうち、必要なものを備える。本実施の形態では、メインメモリ117をSRAMで構成する。

【0056】

バックアップコントロール回路115は、後述の低電圧検出回路125が低電圧を検知した場合に、メインメモリ117を非活性化する。そして、メインメモリ117には、バッテリ141から電源電圧が供給される。従って、電源電圧Vcc0及びVcc1の供給が停止された場合でも、SRAMたるメインメモリ117のデータが保持される。

【0057】

第1バスアービタ113は、第1バス131の各バスマスタからの第1バス使用要求信号を受け付け、調停を行って、バスサイクル毎に1つのバスマスタに対して第1バス使用許可信号を発行する。各バスマスタは、第1バス使用許可信号を受領することによって第1バス131の使用が許可される。ここで、第1バス使用要求信号及び第1バス使用許可信号は、図5では、第1バス調停信号FABとして示されている。

【0058】

第2バスアービタ114は、第2バス133の各バスマスタからの第2バス使用要求信号を受け付け、調停を行って、要求されたバイト数に対応する1または複数のバスサイクル毎に1つのバスマスタに第2バス使用許可信号を発行する。各バスマスタは、第2バス使用許可信号を受領することによって第2バス133の使用が許可される。ここで、第2バス使用要求信号及び第2バス使用許可信号は、図5では、第2バス調停信号SABとして示されている。

【0059】

タイマ回路119は、設定された時間間隔に基づき、CPU101に対する割込み要求信号INRQを発生する機能を有する。時間間隔等の設定は、第1バス131を介してCPU101によって行われる。

【0060】

ADC120は、アナログ入力信号をデジタル信号に変換する。このデジタル信号は、第1バス131を介してCPU101によってリードされる。また、ADC120は、CPU101に対して、割込み要求信号INRQを発生する機能を有する。なお、外部からのアナログ信号は、例えば、6つのアナログポートAIN0〜5(図示せず)を介して、ADC120へ入力される。

【0061】

入出力制御回路121は、外部入出力装置や外部の半導体素子との通信等を、入出力信号を介して行う。入出力信号は、第1バス131を介して、CPU101からリード/ライトされる。また、入出力制御回路121は、CPU101に対して、割込み要求信号INRQを発生する機能を有する。なお、入出力信号は、例えば、プログラマブルな入出力ポートIO0〜IO23(図示せず)を介して入出力される。

【0062】

本実施の形態では、CPU101は、ゲーム機1A及び1Bの入力ボタン12〜16からのオン/オフ信号を、入出力制御回路を介して取得する。

【0063】

低電圧検出回路125は、電源電圧Vcc0及びVcc1を監視し、いずれかの電源電圧がそれぞれについて定められた電圧以下になったときに、PLL回路127等のリセット信号LPW、その他のシステム全体のリセット信号RESを発行する。ここで、電源電圧Vcc0は、例えば、+2.5Vであり、主にプロセッサ23内のデジタル回路に供給される。また、電源電圧Vcc1は、例えば、+3.3Vであり、主にプロセッサ23内のアナログ回路及びI/O部に供給される。

【0064】

PLL回路127は、水晶振動子137より得られる正弦波信号を逓倍した高周波クロック信号ckを生成する。

【0065】

クロックドライバ129は、PLL回路127より受け取った高周波クロック信号ckを、十分な信号強度へ増幅して、内部クロックCKとして、各ブロックへ供給する。

【0066】

外部メモリインタフェース回路123は、第2バス133を外部バス26に接続するための機能を有する。

【0067】

図5のプロセッサ23におけるデータの転送経路を説明する。例えば、バスマスタたるCPU101が、バススレイブとして第1バス131に接続されている他の機能ブロック(グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、DMAコントローラ109、第1バスアービタ113、および第2バスアービタ114等)を制御する場合は、これら機能ブロックの制御レジスタ等へのライトデータは、第1バスアービタ113へ与えられ、調停後に、第1バス131から、各機能ブロックに与えられ、一方、これら機能ブロックの制御レジスタ等からのリードデータは、調停後に、第1バス131及び第1バスアービタ113を介して、CPU101に与えられる。但し、グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、およびDMAコントローラ109は、第1バス131のバスマスタとして、第1バスアービタ113へバス使用要求を行う機能を備える。

【0068】

バスマスタが、メインメモリ117に対してアクセスする場合は、ライトデータは、第1バスアービタ113に与えられ、調停後に、第1バス131から、メインメモリ117に与えられ、一方、リードデータは、調停後に、第1バス131及び第1バスアービタ113を介して、バスマスタに与えられる。

【0069】

また、バスマスタが、ROM27に対してアクセスする場合は、ライトデータは、第2バスアービタ114に与えられ、調停後に、第2バス133から、外部メモリインタフェース回路123及び外部バス26を介して、ROM27に与えられ、一方、リードデータは、調停後に、外部バス26、外部メモリインタフェース回路123、第2バス133及び第2バスアービタ114を介して、バスマスタに与えられる。

【0070】

次に、本実施の形態のバーコード21について詳しく説明する。

【0071】

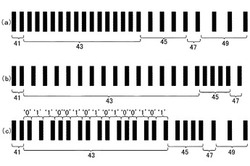

図6(a)〜図6(c)は、バーコード21の例示図である。図6(a)及び図6(c)を参照して、これらのバーコード21は、バーコード21の先頭を示すスタートビット41、トレーディングカード17の識別情報(ID)を含むデータビット43、エラーチェックのためのチェックサム45、チェックサム45の終了を示すストップビット47、及び全種類のバーコード21の全長を揃えるためのダミービット49からなる。また、図6(b)を参照して、このバーコード21は、スタートビット41、データビット43、チェックサム45、及びストップビット47からなる。このように、データビット43の全長によっては、ダミービット49が存在しないバーコード21もある。

【0072】

図6(a)〜図6(c)を参照して、データビット43は、15ビットの情報を表す。後で図示するが、1ビットは、「0」を示す単位データビット35あるいは「1」を示す単位データビット36からなる。データビット43の第0ビットから第7ビットが、トレーディングカード17のIDを表し、第8ビットから第14ビットは、PK(ペナルティキック)対戦で使用するPKパラメータを表す。ROM27には、トレーディングカード17のIDと選手キャラクタの能力値とを関連付けた能力テーブルが用意される。従って、プロセッサ23は、トレーディングカード17のIDをインデックスとして、この能力テーブルを参照して、選手キャラクタの能力値を取得する。このように、バーコード21には、能力値そのものを含ませず、IDを含ませることで、バーコード21の情報量を少なくしている。

【0073】

チェックサム45は、データビット43に含まれる「0」の数を4ビットで表している。1ビットは、単位データビット35あるいは単位データビット36からなる。

【0074】

ダミービット49は、全種類のバーコード21の全長を揃えるために、ストップビット47の後に付される。なぜなら、図6(a)〜図6(c)から明らかなように、データビット43の全長は、それが表す情報の内容によって異なってくるからである。後で図示するが、ダミービット49は、幅が同じ1以上の単位ダミービット50からなる。従って、データビット43の全長に応じて、何個の単位ダミービット50を付加するのか、あるいは、ダミービット49を付加しないのか、が決定される。本実施の形態では、最大3個の単位ダミービット50を付加する。

【0075】

ダミービット49を付加することにより、全種類のバーコード21の全長が揃えられるが、完全に一致するわけではなく、概ね一致する。例えば、所定のバーコード21の全長を基準に、所定範囲内に収まるように単位ダミービット50を付加する。

【0076】

もし、ダミービット49を付加しないならば、トレーディングカード17間で、バーコード21の全長が大きく異なるため、見た目が好ましくない。そこで、ダミービット49を付加して、バーコード21の外観の均整を図る。このように、ダミービット49は、装飾的な機能を有する。

【0077】

一方、ダミービット49は、エラーチェックのためにも使用される。ROM27には、このエラーチェックに使用するためのテーブルが格納されている。

【0078】

図7は、ダミービット49を利用したエラーチェックの際に使用されるテーブルの例示図である。図7を参照して、このテーブルは、トレーディングカード17のID、つまり、データビット43の第0ビット〜第7ビットと、トレーディングカード17の単位ダミービット50の数と、を関連付けたものである。

【0079】

プロセッサ23は、このテーブルを参照して、スキャンの結果得られたバーコード21のデータビット43が示すトレーディングカード17のIDに関連付けられた単位ダミービット50の数を取得する。そして、プロセッサ23は、スキャンの結果得られたバーコード21の単位ダミービット50の数と、テーブルから取得した単位ダミービット50の数と、を比較して、スキャンエラーか否かを判定する。プロセッサ23は、両者が不一致の場合はエラーと認識する。このように、本実施の形態では、チェックサム45及びダミービット49を用いて、二重のエラーチェックを行っている。このため、エラーデータが処理に反映されることを極力防止できる。

【0080】

ここで、バーコード21のうち、ダミービット49を除く部分、即ち、スタートビット41、データビット43、チェックサム45、及びストップビット47を、広義のデータビットと位置づける。従って、データビット43は、狭義のデータビットである。

【0081】

図8(a)は、バーコード21のスタートビット41の説明図である。図8(a)を参照して、スタートビット41は、それぞれ幅が「w」の黒色バー33、白色スペース31、及び黒色バー33をスキャンの方向に並べて構成される。プロセッサ23は、このスタートビット41を検知することで、バーコード21の先頭を認識できる。白色スペース31及びその後の黒色バー33の組は、「0」(つまり論理0)を表す。

【0082】

図8(b)は、バーコード21のストップビット47の説明図である。図8(b)を参照して、ストップビット47は、幅が「2w」の白色スペース32及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。ストップビット47は、「1」(つまり論理1)を表す。プロセッサ23は、このストップビット47を検知することで、チェックサム45の終了を認識できる。

【0083】

図8(c)は、バーコード21の単位ダミービット50の説明図である。図8(c)を参照して、単位ダミービット50は、幅が「3w」の白色スペース34及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。1以上の単位ダミービット50により、ダミービット49が構成される。単位ダミービット50は、「1」(つまり論理1)を表す。

【0084】

図8(d)は、バーコード21の単位データビット35の説明図である。図8(d)を参照して、単位データビット35は、幅が「w」の白色スペース31及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。単位データビット35は、「0」(つまり論理0)を表す。

【0085】

図8(e)は、バーコード21の単位データビット36の説明図である。図8(e)を参照して、単位データビット36は、幅が「2w」の白色スペース32及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。単位データビット35は、「1」(つまり論理1)を表す。

【0086】

合計15個の単位データビット35及び/又は36によりデータビット43が構成され、合計4個の単位データビット35及び/又は36によりチェックサムが構成される。

【0087】

図6(a)〜図6(c)に戻って、図6(a)のデータビット43は、「0b000000000000000」を、図6(b)のデータビット43は、「0b111111111111111」を、図6(c)のデータビット43は、「0b011001010100101」を、それぞれ表す。

【0088】

このように、「0」を示す単位データビット35が多いバーコード21ほど、その全長が短くなり、「1」を示す単位データビット36が多いバーコード21ほど、その全長が長くなる。従って、図6(a)のバーコード21は、3個の単位ダミービット50を含み、図6(b)のバーコード21は、単位ダミービット50を含まず、図6(c)のバーコード21は、2個の単位ダミービット50を含む。このように、単位ダミービット50を付加する数によって、バーコード21の長さを統一して、見た目を整えている。

【0089】

次に、バーコード21の解析方法の基本原理を説明する。

【0090】

図9(a)及び図9(b)は、バーコード21の解析方法の基本原理の説明図である。プレイヤが、図9(a)のトレーディングカード17をゲーム機1Aの溝部8に沿ってスライドさせると、検知ユニット25のフォトトランジスタ74は、信号を反転する上記したアンプ(図示せず)を介して、図9(b)に示す信号71を出力する。なお、この例では、トレーディングカード17をスライドさせる速度が一定であるとしている。

【0091】

より詳細には、次の通りである。ゲーム機1Aの溝部8にトレーディングカード17がない状態では、赤外発光ダイオード72からの赤外光は、溝部8の壁面64に対面する壁面に照射されるため、反射赤外光は弱く、それ故、フォトトランジスタ74の出力信号のレベルは低くなる。ところが、検知ユニット25は、フォトトランジスタ74の出力信号を反転して出力するので、この状態では、検知ユニット25の出力信号のレベルは高くなる(ハイレベル)。

【0092】

そして、プレイヤがトレーディングカード17を溝部8に沿ってスライドさせると、まず、トレーディングカード17の入力エッジ80から長さLS(図2(b)参照)までは、白色の領域が続くので、この領域に照射され、反射される赤外光は強く、それ故、フォトトランジスタ74の出力信号のレベルは高くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは低い(ローレベル)。

【0093】

次に、スタートビット41の最初の黒色バーに、赤外光が照射されるため、反射赤外光は弱く、それ故、フォトトランジスタ74の出力信号のレベルは低くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは高い(ハイレベル)。

【0094】

次に、スタートビット41の最初の白色スペースに、赤外光が照射されるため、反射赤外光は強く、それ故、フォトトランジスタ74の出力信号のレベルは高くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは低い(ローレベル)。

【0095】

以下同様に、黒色バーに赤外光が照射されたときは、検知ユニット25の出力信号71は高いレベル(ハイレベル)となり、白色スペースに赤外光が照射されたときは、検知ユニット25の出力信号71は低いレベル(ローレベル)となる。

【0096】

本実施の形態では、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジを順次検出する。これは、プロセッサ23が、黒色バーの後端エッジ(図中右側のエッジ(長辺))を順次検出することを意味する。そして、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジから次の立ち下がりエッジまでの時間を計測する。これは、プロセッサ23が、黒色バーの後端エッジから次の黒色バーの後端エッジまでの長さを計測することに相当する。

【0097】

単位データビット35(幅2w)は、単位データビット36(幅3w)より小さい。従って、黒色バーの後端エッジから、その次の単位データビット35を構成する黒色バーの後端エッジまでの長さ2wは、黒色バーの後端エッジから、その次の単位データビット36を構成する黒色バーの後端エッジまでの長さ3wより短い。

【0098】

言い換えると、黒色バーの後端エッジに相当する出力信号71の立ち下がりエッジから、その次の単位データビット35を構成する黒色バーの後端エッジに相当する出力信号71の立下りエッジまでの時間T0は、黒色バーの後端エッジに相当する出力信号71の立ち下がりエッジから、その次の単位データビット36を構成する黒色バーの後端エッジに相当する出力信号71の立下りエッジまでの時間T1より短い。

【0099】

よって、プロセッサ23は、検知ユニット25の出力信号の立ち下がりエッジから次の立ち下がりエッジまでの時間を計測し、その長短を判定することにより、単位データビット35と単位データビット36とを判別する。

【0100】

ところが、トレーディングカード17をスライドさせるのはプレイヤ、つまり、人間であるため、ゲーム機1Aのスリット70を通過するときの黒色バーの速度は、それぞれのバーで異なってくる。また、プレイヤによっても、トレーディングカード17をスライドさせるときの速度は異なってくる。これらの点を考慮し、本実施の形態では、後述のフローチャートに示すようにして、単位データビット35と単位データビット36とを判別している。

【0101】

さて、本実施の形態では、スキャンモード、ゲームモード、及びPKモードが用意される。スキャンモードは、トレーディングカード17のバーコード21をスキャンするモードである。ゲームモードは、第1プレイヤと第2プレイヤとがそれぞれの選手キャラクタを操作して、サッカーゲームの対戦を行うモードである。PKモードは、第1プレイヤと第2プレイヤとがそれぞれのトレーディングカード17を使用して、PKの対戦を行うモードである。

【0102】

以下では、第1プレイヤあるいは第2プレイヤが、入力ボタン12〜16を操作して、スキャンモードを選択した場合の処理を説明する。

【0103】

図10は、図4のプロセッサ23によるスキャンモードでの処理の流れを示すフローチャートである。図10を参照して、ステップS1にて、プロセッサ23は、システムの初期設定を実行する。この処理で、図10の処理及び後述する図11〜図13の処理で使用される全ての変数及びカウンタが初期化(0を代入)されるとともに、全てのフラグがオフ(クリア)される。ただし、後述するプレイヤ特定フラグは第1プレイヤを示す値にセットされる。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。

【0104】

ステップS2にて、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジを検出するためのエッジトリガをイネーブルにする。これにより、図5の入出力制御回路121は、出力信号71の立ち下がりエッジを検出した時に、割込み要求信号INRQをCPU101に発行する。以下、この時の込み要求信号INRQをエッジトリガと呼ぶ。

【0105】

ここで、ステップS3以降の説明の前に、割込み処理について説明する。この割込み処理は、エッジトリガによる割込み又はタイマ回路119による割込みが発生した時に、プロセッサ23により実行される。

【0106】

図11は、図4のプロセッサ23の割込み処理の流れを示すフローチャートである。図11を参照して、ステップS30にて、プロセッサ23は、割り込みが、エッジトリガに基づくものか、あるいは、タイマ回路119に基づくものか、を判断し、エッジトリガに基づく割込みの場合はステップS31に進み、タイマ回路119に基づく割り込みの場合ステップS48に進む。

【0107】

エッジトリガに基づく割込みの場合、ステップS31にて、プロセッサ23は、バーコード21を読み込み中であることを示すリード中フラグをオンにする。なぜなら、エッジトリガが発生したということは、トレーディングカード17の入力エッジ又はバーコード21の黒色バーの後端エッジが検出されたことを意味するので、バーコード21の読み取り中ということになるからである。

【0108】

ステップS32にて、プロセッサ23は、検知ユニット25の出力信号71の立下りエッジの検出回数を計数するカウンタCEが「0」か否かを判断する。カウンタCEが「0」の場合は、その時のエッジトリガは、トレーディングカード17の入力エッジ80が検出されたことに基づくものであるので、ステップS33に進む。一方、カウンタCEが「0」以外の場合は、その時のエッジトリガは、バーコード21の黒色バーの後端エッジが検出されたことに基づくものであるので、ステップS35に進む。

【0109】

入力エッジ80が検出された場合、ステップS33にて、プロセッサ23は、タイマ回路119による割込みをセットし、メインルーチンにリターンする。この場合、割込み発生の間隔は、例えば、0.5秒にセットされる。

【0110】

入力エッジ80が検出された後、0.5秒以内に、スタートビット41の最初の黒色バーの後端エッジが検出されない場合は、トレーディングカード17が溝部8に挿入されたにも拘らず、停止しているとみなして、読み取りエラーと判断するためである。なお、ここで設定する0.5秒は、あくまでも例示であり、図2(b)の長さLSに応じて、適宜変更される。

【0111】

ステップS34にて、プロセッサ23は、カウンタCEを1つインクリメントして、メインルーチンにリターンする。

【0112】

ステップS32で、カウンタCEが「0」以外であると判断されると、ステップS35にて、プロセッサ23は、カウンタCEが「1」か否かを判断する。カウンタCEが「1」の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーの後端エッジが検出されたことに基づくものであるので、ステップS45に進む。一方、カウンタCEが2以上の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーに後続する一連の黒色バーのいずれかの後端エッジが検出されたことに基づくものであるので、ステップS36に進む。

【0113】

スタートビット41の最初の黒色バーの後端エッジが検出された場合、ステップS45にて、プロセッサ23は、タイマ回路119による割込みをセットする。この場合、割込み発生の周波数は、例えば、625kHzにセットされる。この割り込みは、検知ユニット25の出力信号71立下りエッジと次の立ち下がりエッジとの間隔を計測するためのものである。

【0114】

ステップS46にて、プロセッサ23は、カウンタCEを1つインクリメントして、メインルーチンにリターンする。

【0115】

ステップS35でカウンタCEが2以上の場合は、ステップS36にて、プロセッサ23は、カウンタCEを1つインクリメントする。ステップS37にて、プロセッサ23は、カウンタCEが「26」か否かを判断する。カウンタCEが「26」の場合は、その時のエッジトリガは、3個の単位ダミービット50が付加されたバーコード21の最後尾の黒色バー、つまり、3つ目の単位ダミービット50の黒色バーの後端エッジが検出されたことに基づくものであるので、バーコード21の読み取り処理を終了すべくステップS38に進む。一方、カウンタCEが3以上26未満の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーに後続する一連の黒色バーのいずれかの後端エッジが検出されたことに基づくものであるので、ステップS42に進む。

【0116】

3つ目の単位ダミービット50の黒色バーの後端エッジが検出された場合、ステップS38にて、プロセッサ23は、バーコード21の読み込み処理が終了したことを示すリード終了フラグをオンにする。ステップS39にて、プロセッサ23は、リード中フラグをオフにする。ステップS40にて、プロセッサ23は、エッジトリガをディセーブルにする。ステップS41にて、プロセッサ23は、タイマ回路119による割込みを解除する。

【0117】

ステップS42では、プロセッサ23は、カウンタTCの値を配列Aの要素A[k]として格納する。カウンタTCの値は、検知ユニット25の出力信号71の立下りエッジから次の立下りエッジまでの時間に相当する。ステップS43にて、プロセッサ23は、カウンタTCに「0」を代入する。ステップS44にて、プロセッサ23は、配列Aの要素番号を表す変数kを1つインクリメントして、メインルーチンにリターンする。

【0118】

ちなみに、ステップS42において、変数kが「0」(初期値)の場合は、CE=3であるので、その時のカウンタTCの値は、スタートビット41の最初の黒色バーの後端エッジに対応する出力信号71の立ち下がりエッジから、その次の立下りエッジまでの時間を示す。この場合のカウンタTCの値は、配列Aの要素A[0]として格納される。従って、スタートビット41の最初の黒色バーの後端エッジから、スタートビット41の最後尾の黒色バーの後端エッジまでの距離に相当する時間が、配列Aの要素A[0]として格納される。もちろん、要素A[0]として格納されるカウンタTCの値は、その時のトレーディングカード17のスライド速度に依存して変動する。上記のように、プレイヤによるトレーディングカード17のスライド速度は一定ではないので、プロセッサ23は、要素A[0]として格納されたカウンタTCの値を基準に、単位データビット35と単位データビット36とを判別する。この点は、後述する。

【0119】

プロセッサ23は、ステップS30でタイマ回路119による割り込みであると判断した場合は、ステップS48にて、カウンタCEが「1」か否かを判断する。カウンタCEが「1」のときに発生するタイマ回路119による割り込みは、ステップS33に基づくものである。従って、この場合、バーコード21のスタートビット41の最初の黒色バーの後端エッジが未だ検出されていない。このため、カウンタCEが「1」の場合、読み取りエラーと判断すべく、ステップS49に進む。一方、カウンタCEが2以上のときに発生するタイマ回路119による割り込みは、ステップS45に基づくものである。従って、出力信号71の立ち下がりエッジ間の時間を計測すべく、ステップS51に進む。

【0120】

ステップS49では、プロセッサ23は、バーコード21のスキャンにエラーが発生したことを示すエラーフラグをオンにする。そして、ステップS50にて、プロセッサ23は、リード中フラグをオフにして、ステップS55に進む。

【0121】

一方、ステップS51では、プロセッサ23は、カウンタTCを1つインクリメントする。ステップS52にて、プロセッサ23は、カウンタTCの値が35ミリ秒に相当するか否かを判断し、35ミリ秒に相当しない場合は、メインルーチンにリターンする。プロセッサ23は、カウンタTCの値が35ミリ秒に相当する場合は、読み取り処理を終了すべく、ステップS53に進む。カウンタTCの値が35ミリ秒ということは、出力信号71の立下りエッジが検出されてから35ミリ秒が経過したが、次の立ち下がりエッジが検出されていないことを意味する。つまり、35ミリ秒の間、出力信号71の立ち下がりエッジが発生していないことになる。そこで、このような場合は、読み取りを終了することにしたのである。ステップS53では、プロセッサ23は、リード終了フラグをオンにする。そして、ステップS54にて、プロセッサ23は、リード中フラグをオフにする。

【0122】

ステップS55では、プロセッサ23は、エッジトリガをディセーブルにする。ステップS56にて、プロセッサ23は、タイマ回路119による割込みを解除して、メインルーチンにリターンする。

【0123】

図10に戻って、ステップS3では、プロセッサ23は、バーコード21のスキャンにエラーが発生したことを示すエラーフラグを参照して、オンの場合はステップS15に進み、オフの場合はステップS4に進む。

【0124】

ステップS15では、プロセッサ23は、バーコード21をスキャンするための再設定を行う。具体的には、プロセッサ23は、図10及び図11の処理並びに後述する図12及び図13の処理で使用される全ての変数及びカウンタを初期化(0を代入)するとともに、全てのフラグをオフ(クリア)にする。ただし、後述するプレイヤ特定フラグの値は維持される。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。さらに、プロセッサ23は、ステップS2と同様にエッジトリガをイネーブルにする。ステップS16にて、プロセッサ23は、エラーである旨のテレビジョンモニタ3への表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0125】

ステップS3でエラーでない場合、ステップS4にて、プロセッサ23は、バーコード21の読み取りが終了したことを示すリード終了フラグを参照して、オフの場合はステップS12に進み、オンの場合はステップS5に進む。

【0126】

ステップS12では、プロセッサ23は、バーコード21を読み込み中であることを示すリード中フラグを参照して、オンの場合はステップS13に進み、オフの場合はステップS14に進む。ステップS13では、プロセッサ23は、リード中である旨のテレビジョンモニタ3への表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。一方、ステップS14では、プロセッサ23は、待機中である旨の表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0127】

ステップS4でリード終了の場合、ステップS5にて、プロセッサ23は、読み込んだバーコード21のデータ(つまり、配列A)を解析する。

【0128】

図12は、図10のステップS5のデータ解析処理の流れを示すフローチャートである。図12を参照して、ステップS70にて、プロセッサ23は、検知ユニット25の出力信号71の立下りエッジの検出回数を計数するカウンタCEが22以下か否かを判断する。カウンタCEが22以下の場合は、ストップビット47が検出されていないので、読み取りエラーとすべく、プロセッサ23は、図10のステップS15に進む。カウンタCEが22を超えている場合は、ストップビット47は検出されているので、データ解析を行うべく、プロセッサ23は、ステップS71に進む。

【0129】

ステップS71にて、プロセッサ23は、配列Aの要素番号を示す変数nが「0」か否かを判断する。変数nが「0」のときの配列Aの要素A[0]は、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wに相当する時間である。つまり、要素A[0]はスタートビット41に関する情報であり、実体的な情報ではない。そこで、この場合、プロセッサ23は、ステップS73に進む。ステップS73では、プロセッサ23は、「0」を配列Dの要素D[0]として格納し、ステップS74に進む。なぜなら、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wは、「0」を示す単位データビット35の幅2wと同一であるため、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wに相当する時間を、「0」と判定するための基準とするためである。

【0130】

ステップS71で変数nが1以上のときは、ステップS74にて、プロセッサ23は、変数nを1つインクリメントする。ステップS75にて、プロセッサ23は、配列Dの要素D[n−1]が「0」か否かを判断し、「0」の場合はステップS76に進み、「0」でない場合、つまり、「1」の場合ステップS80に進む。

【0131】

ステップS76では、プロセッサ23は、配列Aの要素A[n−1]に1.25を乗じて、閾値Th0とする。つまり、1つ前の単位データビットが「0」を示す単位データビット35である場合、その単位データビット35の幅2wに相当する時間である要素A[n−1]に1.25を乗じて、閾値Th0とする。1つ前が、スタートビット41の場合も同様に、スタートビット41の最初の黒色バーの後端エッジから最後尾の黒色バーの後端エッジまでの長さ2wに相当する時間である要素A[0]に1.25を乗じて、閾値Th0とする。

【0132】

そして、ステップS77にて、プロセッサ23は、配列Aの要素A[n]が閾値Th0より小さいか否かを判断し、小さい場合は今回の単位データビットが「0」を示す単位データビット35であるとし、ステップS79に進む。ステップS79では、プロセッサ23は、「0」を配列Dの要素D[n]として格納する。一方、プロセッサ23は、配列Aの要素A[n]が閾値Th0より小さくない場合は今回の単位データビットが「1」を示す単位データビット36であるとし、ステップS78に進む。ステップS78では、プロセッサ23は、「1」を配列Dの要素D[n]として格納する。

【0133】

ステップS75で配列Dの要素D[n−1]が「1」の場合、ステップS80にて、プロセッサ23は、配列Aの要素A[n−1]に0.75を乗じて、閾値Th1とする。つまり、1つ前の単位データビットが「1」を示す単位データビット36である場合、その単位データビット36の幅3wに相当する時間である要素A[n−1]に0.75を乗じて、閾値Th1とする。

【0134】

そして、ステップS81にて、プロセッサ23は、配列Aの要素A[n]が閾値Th1より大きいか否かを判断し、大きい場合は今回の単位データビットが「1」を示す単位データビット36であるとし、ステップS82に進む。ステップS82では、プロセッサ23は、「1」を配列Dの要素D[n]として格納する。一方、プロセッサ23は、配列Aの要素A[n]が閾値Th1より大きくない場合は今回の単位データビットが「0」を示す単位データビット35であるとし、ステップS83に進む。ステップS83では、プロセッサ23は、「0」を配列Dの要素D[n]として格納する。

【0135】

ステップS84では、プロセッサ23は、変数nが値(CE−3)に等しいか否かを判断し、「NO」の場合ステップS71に戻り、「YES」の場合メインルーチンにリターンする。n=CE−3は、バーコード21の最後尾の黒色バーまで、対応するデータが配列Dに格納されたことを意味する。

【0136】

ここで、ステップS76では、要素A[n−1]に1.25を乗じている。理由は次の通りである。前回と今回の単位データビットが単位データビット35の場合において、トレーディングカード17のスライド速度が減速した場合、もし、要素A[n−1]をそのまま閾値Th0とするならば、単位データビット35の長さに相当する要素A[n]が閾値Th0より大きいと判断され、単位データビット35が「1」として要素D[n]に格納されてしまう。この誤認識を回避するために、プラス25%のマージンを持たせたのである。なお、どのくらいのマージンを持たせるかは、プラス25%に限らず、経験的に定めることができる。ちなみに、トレーディングカード17のスライド速度が加速した場合は、上記のケースでは、問題なく単位データビット35が「0」と認識される。

【0137】

また、ステップS80では、要素A[n−1]に0.75を乗じている。理由は次の通りである。前回と今回の単位データビットが単位データビット36の場合において、トレーディングカード17のスライド速度が加速した場合、もし、要素A[n−1]をそのまま閾値Th1とするならば、単位データビット36の長さに相当する要素A[n]が閾値Th1より小さいと判断され、単位データビット36が「0」として要素D[n]に格納されてしまう。この誤認識を回避するために、マイナス25%のマージンを持たせたのである。なお、どのくらいのマージンを持たせるかは、マイナス25%に限らず、経験的に定めることができる。ちなみに、トレーディングカード17のスライド速度が減速した場合は、上記のケースでは、問題なく単位データビット36が「1」と認識される。

【0138】

図10に戻って、ステップS6では、プロセッサ23は、スタートビット41及びストップビット47に基づいてエラーチェックを行う。具体的には、プロセッサ23は、配列Dから、スタートビット41が示すデータを格納している要素D[0]及びストップビット47が示すデータを格納している要素D[20]を取得する。そして、プロセッサ23は、要素D[0]が「1」及び/又は要素D[20]が「0」の場合は、エラーと判断して、ステップS15に進み、それ以外は、つまり、要素D[0]が「0」かつ要素D[20]が「1」の場合はステップS7に進む。

【0139】

ステップS7にて、プロセッサ23は、チェックサム45に基づいてエラーチェックを行う。具体的には、プロセッサ23は、データビット43に対応する配列Dの要素D[1]〜D[15]に含まれる「0」の数と、要素D[16]〜D[19]であるチェックサム45が示す「0」の数と、を比較して、両者が一致しない場合は、エラーと判断して、ステップS15に進み、それ以外はステップS8に進む。

【0140】

ステップS8では、プロセッサ23は、ダミービット49に基づいてエラーチェックを行う。

【0141】

図13は、図10のステップS8のダミービット49によるエラーチェック処理の流れを示すフローチャートである。図13を参照して、ステップS100にて、プロセッサ23は、変数iに「20」を代入する。ステップS101にて、プロセッサ23は、変数iを1つインクリメントする。

【0142】

ステップS102にて、プロセッサ23は、配列Dの要素D[i]が「1」か否かを判断する。プロセッサ23は、要素D[i]が「1」の場合は、単位ダミービット50が存在すると判断して、ステップS103に進む。ステップS103では、単位ダミービット50の数を計数するカウンタjを1つインクリメントし、ステップS104に進む。一方、プロセッサ23は、要素D[i]が「0」の場合は、ステップS102からステップS104に直接進む。

【0143】

ステップS104にて、プロセッサ23は、変数iがCE−3に等しいか否かを判断し、等しい場合は、ステップS105に進み、それ以外はステップS101に戻る。このようにして、読み込んだバーコード21に含まれる単位ダミービット50の数を計数する。

【0144】

ステップS105にて、プロセッサ23は、図7のテーブルを参照して、カウンタjの値の正当性をチェックする。

【0145】

つまり、プロセッサ23は、ステップS5のデータ解析の結果得られたトレーディングカード17のID(つまり、要素D[1]〜D[8])をインデックスとして、テーブルを参照し、そのIDに関連付けられた単位ダミービット50の数を示す情報を取得する。そして、プロセッサ23は、ステップS5のデータ解析の結果に基づく単位ダミービット50の数を示すカウンタjの値と、テーブルから取得した単位ダミービット50の数の情報と、を比較する。ステップS106にて、プロセッサ23は、両者が不一致の場合は、エラーと判断して、図10のステップS15に進み、両者が一致する場合はスキャンが成功したと判断して、メインルーチンにリターンする。

【0146】

図10に戻って、ステップS9にて、プロセッサ23は、スキャンしたトレーディングカード17が示す選手キャラクタの能力値を設定する。具体的には、プロセッサ23は、スキャンしたトレーディングカード17のID(つまり、要素D[1]〜D[8])をインデックスとして、上記した能力テーブルを参照して、そのIDに関連付けられた能力値を取得し、選手キャラクタの能力値を再設定する。

【0147】

この場合、プロセッサ23は、プレイヤ特定フラグが第1プレイヤを示している場合は、第1プレイヤの選手キャラクタに対して能力値を再設定する。一方、プロセッサ23は、プレイヤ特定フラグが第2プレイヤを示している場合は、第2プレイヤの選手キャラクタに対して能力値を再設定する。プロセッサ23は、選手キャラクタの能力値を再設定した後に、プレイヤ特定フラグの値を異なるプレイヤを示す値にセットする。このようにして、第1プレイヤの選手キャラクタに対する能力設定と第2プレイヤに対する能力設定とが交互に行われる。

【0148】

ステップS10では、プロセッサ23は、バーコード21をスキャンするための再設定を行う。具体的には、プロセッサ23は、図10〜図13の処理で使用される全ての変数及びカウンタを初期化(0を代入)するとともに、全てのフラグをオフ(クリア)にする。ただし、プレイヤ特定フラグの値は維持される。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。さらに、プロセッサ23は、ステップS2と同様にエッジトリガをイネーブルにする。ステップS11にて、プロセッサ23は、テレビジョンモニタ3に次のプレイヤのトレーディングカード17のスキャンができる旨の表示をすべく、画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0149】

ステップS17にて、プロセッサは、ビデオ同期信号による割り込みが発生した場合はステップS18に進み、それ以外は同じステップS17に進む。ビデオ同期信号による割り込みが発生すると、プロセッサ23は、ステップS18にて、ステップS11,S13,S14又はS16でセットされた画像情報に基づいて、テレビジョンモニタ3の画面(ビデオフレーム)を更新すると共に、ステップS19にて、音声処理を実行し、音楽や効果音を出力する。そして、プロセッサ23は、ステップS3に戻る。

【0150】

ここで、PKモードについて簡単に説明する。このモードでは、プレイヤが自分のトレーディングカード17をゲーム機1Aにスキャンさせる。そして、ゲーム機1Aは、バーコード21のデータビット43の第8〜第14ビットの情報をPK対戦に利用する。データビット43の第8〜第14ビットの情報は、そのトレーディングカード17に対応する選手キャラクタのPKに関する能力値を示している。従って、ゲーム機1Aは、その能力値に基づいて、PKの成功及び失敗を決定する。

【0151】

さて、以上のように、本実施の形態では、絵柄が異なるトレーディングカード17間において各トレーディングカード17を識別するためにバーコード21を利用している。そして、各トレーディングカード17のデータビット43の全長に応じて、適切な長さのダミービット49を付加し、又は、付加しない。このように、ダミービットによって、全種類のバーコード21の全長を揃えている。その結果、各トレーディングカード17に付されたバーコード21間で見た目の統一性を図ることができる。また、肉眼でのバーコード21の内容の認識を困難にすることができる。

【0152】

特に、本実施の形態では、広狭2つの単位データビット35及び36を用いてデータビット43を構成するので、バーコード21間でデータビット43の広狭が発生し、しかも、目立ち易い。それ故、ダミービット49を付加することの上記意義がより大きくなる。最も極端な例は、あるデータビット43が全て単位データビット35からなり、別のデータビット43が全て単位データビット36からなる場合であり、この場合は、双方の全長の差が最も大きい。

【0153】

一般に、トレーディングカードは、それに付された絵柄が重要な要素であり、その絵柄がコレクターの収集意欲を喚起する要因の1つでもある。従って、ダミービット49を付加して、トレーディングカード17間でバーコード21の全長を揃え、見た目を良くする意義は大きい。

【0154】

また、本実施の形態では、単位ダミービット50の幅4wは、単位データビット35の幅2w及び単位データビット36の幅3wと異なる。このため、バーコード21の見た目のバリエーションを増やすことができる。特に、本実施の形態では、広狭2つの単位データビット35及び36を用いてデータビット43を構成するので、もし、単位ダミービット50の幅が、これらのうちのどれかと同じならば、見た目のバリエーションが少なくなる。

【0155】

さらに、本実施の形態では、単位ダミービット50の幅4wは、ストップビット47の幅3wより大きい。このため、ストップビット47の直後の単位ダミービット50の誤認識を極力防止できる。

【0156】

さらに、バーコード21の情報には、データビット43の情報及びダミービット49の情報が含まれるところ、本実施の形態では、広義のデータビット(スタートビット41、データビット43、チェックサム45、及びストップビット47)のビット数(21)の情報が予め設定されている(ステップS100及びS101)。従って、プロセッサ23は、データビット43の情報とダミービット49の情報との境界を容易に認識でき、それ故、配列Dから容易にダミービット49の情報を抽出できる(ステップS102)。

【0157】

さらに、本実施の形態では、チェックサム45に基づくエラーチェック加えて、ダミービット49基づくエラーチェックをも行っている。このように、ダミービット49を装飾目的だけでなく、エラーチェックのためにも利用している。その結果、得られたデータの信頼性が向上する。

【0158】

なお、本発明は、上記の実施の形態に限られるものではなく、その要旨を逸脱しない範囲で、種々の態様において実施することが可能であり、例えば、以下のような変形も可能である。

【0159】

(1)ダミービット49に代えて、図画、文字、数字及び/又は記号をデータビット(広義)に付加することもできる。これによって、より装飾的効果を高めることができる。

【0160】

(2)上記では、2種類の単位データビット35及び36を用いて、データを二進法により表現した。ただし、3種類以上の単位データビット35及び36を用いてデータを表現してもよい。また、単位データビット35及び36は、それぞれ1つのバーと1つのスペースとの組み合わせにより構成したが、これに限定されず、複数のバー及び複数のスペースにより、1つの単位データビットを構成することもできる。つまり、本発明は、バーコードの構造にほとんど依存しない。

【0161】

(3)上記では、バーコード21を光学的に走査して、得られた信号71の立下りエッジを検知して、単位データビット35及び36等の幅を測定し、その幅の長短によって「0」か「1」かを判別した。ただし、そのような解析方法に限らず、立ち上がりエッジを検知してもよいし、双方を検知してもよいし、また、磁気的な走査方法であったり、バーコード21全体を撮像して、得られた映像を処理する方法であってもよい。つまり、本発明は、走査方法にはほとんど依存しない。

【0162】

(4)上記では、単位データビット35及び36等の幅を計測して、0か1かを判定している。従って、同じ種類の単位データビット間で、スペースの幅とバーの幅との合計幅が同じならば、スペース及びバーの幅をそれぞれ任意に設定できる。この点、単位ダミービットについても同様である。

【0163】

(5)上記では、ダミービット49をデータビット(広義)の後に付加した。ただし、ダミービット49をデータビット(広義)の前に付加することもできる。

【0164】

(6)上記では、単位ダミービット50を1種類用意した。ただし、複数種類の単位ダミービットを使用することもできる。

【0165】

(7)上記では、1次元バーコードを例に挙げたが、本発明を2次元バーコードに適用することもできる。

【図面の簡単な説明】

【0166】

【図1】本発明の実施の形態によるゲームシステムの全体構成を示す図である。

【図2】(a)図1のトレーディングカード17の表の面を示す図である。(b)図1のトレーディングカード17の裏の面を示す図である。

【図3】(a)図1のゲーム機1Aの斜視図である。(b)図1のゲーム機1Aの平面図である。(c)図3(b)のA−A線によるゲーム機1Aの断面図である。

【図4】図1のゲーム機1Aの電気的構成を示すブロック図である。

【図5】図4のプロセッサ23の電気的構成を示すブロック図である。

【図6】(a)バーコード21の例示図である。(b)バーコード21の他の例示図である。(c)バーコード21のさらに他の例示図である。

【図7】ダミービット49を利用したエラーチェックの際に使用されるテーブルの例示図である。

【図8】(a)バーコード21のスタートビット41の説明図である。(b)バーコード21のストップビット47の説明図である。(c)バーコード21のダミービット49の説明図である。(d)バーコード21の単位データビット35の説明図である。(e)バーコード21の単位データビット36の説明図である。

【図9】バーコード21の解析方法の基本原理の説明図である。

【図10】図4のプロセッサ23によるスキャンモードでの処理の流れを示すフローチャートである。

【図11】図4のプロセッサ23の割込み処理の流れを示すフローチャートである。

【図12】図10のステップS5のデータ解析処理の流れを示すフローチャートである。

【図13】図10のステップS8のダミービット49によるエラーチェック処理の流れを示すフローチャートである。

【符号の説明】

【0167】

1A,1B…ゲーム機、3…テレビジョンモニタ、5…A/Vケーブル、6…ケーブル、17…トレーディングカード、21…バーコード、23…プロセッサ、25…検知ユニット、41…スタートビット、43…データビット、45…チェックサム、47…ストップビット、49…ダミービット。

【技術分野】

【0001】

本発明は、各々が割り当てられた同一物品に付される複数の異なるバーコードからなるバーコードセット、それらのバーコードを読み取るためのバーコード読取装置、及びそれらの関連技術に関する。

【背景技術】

【0002】

特許文献1には、特定の形状を有する絵柄の内部にバーコードを設け、さらに、バーコードの前後に意味のないバーを付加することによって、より絵柄をそれらしく見せ、バーコードのデザイン性を高めるという発明が開示されている。

【0003】

特許文献1の従来技術では、バーコードのマージン(読取のために必要な余白)の外側にダミーバーを配置するか(つまり、ダミーバーがバーコードの一部を構成しない)、ダミーバーの色をバーコード読取装置に認識不可能な色にするなど、ダミーバーが、バーコード読取装置によって読み取られないように工夫されている。こうすることで、実体的な情報を表しているバーのみがバーコード読取装置によって読み取られるので、実体的な情報の正確な読取が担保される。

【0004】

【特許文献1】特開平9−212611

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、通常、バーコードは、ある商品群を他の商品群と識別するために使用される。つまり、同一商品には同一のバーコードが付される。従って、同一商品間で異なるバーコードが付されることはない。従って、特許文献1では、このような通常のバーコードに、ダミーバーを付加することを意図していると考えられる。このため、絵柄並びにその内部のダミーバー及びバーコードは、同一商品間では同一となる。つまり、特許文献1では、同一商品間において、全てのダミーバー及び全てのバーは同一である。

【0006】

ところが、同一物品間において各物品を識別するためにバーコードを使用することもある。この場合、当然、付されるバーコードは、物品間で異なってくる。つまり、バーコードの全長が、物品間で異なってくるのである。これでは、見た目も好ましくない。また、用途によっては、肉眼によってバーコードの内容を認識でき難いほうが好ましい場合もある。しかし、バーコードの全長が物品間で異なることは、肉眼によるバーコードの内容の認識を手助けすることになる。

【0007】

そこで、本発明の目的は、同一物品間において各物品を識別するためにバーコードを利用する際に、各物品に付されたバーコード間で、見た目の統一性を図ると共に、肉眼でのバーコードの内容の認識が困難なバーコードセット及びその関連技術を提供することである。

【課題を解決するための手段】

【0008】

本発明の第1の観点によると、バーコードセットは、各々が割り当てられた同一物品に付される複数の異なるバーコードからなり、前記バーコードの各々は、実体的な情報を表すデータビットと、前記実体的な情報を表さないダミービットと、を含み、前記バーコードの全長が所定長を基準に所定範囲に属するように、前記データビットに前記ダミービットが付加され、前記データビットは、スペースとバーとの組み合わせからなり、前記ダミービットは、スペースとダミーバーとの組み合わせからなる。

【0009】

この構成によれば、同一物品間において各物品を識別するためにバーコードを利用する際に、各物品間でデータビットの全長が異なる場合でも、ダミービットを付加することによって、バーコード間で全長を揃えることができる。その結果、各物品に付されたバーコード間で見た目の統一性を図ることができる。また、肉眼でのバーコードの内容の認識を困難にすることができる。

【0010】

ここで、所定範囲は0を含む。所定範囲が0の場合、全てのバーコードの全長が所定長となる。もちろん、所定範囲は、負から正の範囲であってもよいし、負の範囲でもよいし、正の範囲でもよい。

【0011】

また、データビットは、広義の意味に用いられ、少なくとも実体的な情報を含み、スタートビット、ストップビット、及びチェックサム等の、ダミービット以外の他の情報を含む広い概念である。

【0012】

上記バーコードセットにおいて、前記データビットは、合計幅が第1の所定幅からなる前記スペース及び前記バーから構成される第1の単位データビット、合計幅が前記第1の所定幅より大きい第2の所定幅からなる前記スペース及び前記バーから構成される第2の単位データビット、又はそれらの組み合わせからなり、前記第1の単位データビットは、論理0あるいは論理1のいずれかを示し、前記第2の単位データビットは、前記第1の単位データビットが示す論理と逆の論理を示す。

【0013】

この構成によれば、広狭2つの単位データビットを用いてデータビットを構成するので、バーコード間でデータビットの広狭が発生し又は目立ち易くなり、それ故、ダミービットを付加することの上記意義がより大きくなる。最も極端な例は、あるデータビットが全て第1の単位データビットからなり、別のデータビットが全て第2の単位データビットからなる場合であり、この場合は、データビットの全長の差が最も大きい。

【0014】

このバーコードセットにおいて、前記ダミービットは、単数又は複数の単位ダミービットからなり、前記単位ダミービットは、合計幅が第3の所定幅からなる前記スペース及び前記ダミーバーから構成され、前記第3の所定幅は、前記第1の所定幅及び前記第2の所定幅と異なる。

【0015】

この構成によれば、単位ダミービットの幅が、第1の単位データビットの幅及び第2の単位データビットの幅と異なるので、バーコードの見た目のバリエーションを増やすことができる。

【0016】

上記バーコードセットにおいて、前記ダミービットに代えて、図画、文字、数字及び/又は記号を前記データビットに付加することもできる。この構成によれば、より装飾的効果を高めることができる。

【0017】

上記バーコードセットにおいて、前記バーコードが付される前記物品は、トレーディングカードである。

【0018】

一般に、トレーディングカードは、それに付された図柄が重要な要素であり、その図柄がコレクターの収集意欲を喚起する要因の1つでもある。従って、ダミービットを付加して、トレーディングカード間でバーコードの全長を揃え、見た目を良くする意義は大きい。

【0019】

本発明の第2の観点によると、バーコード読取装置は、上記バーコードセットを構成する前記各バーコードを読み取るバーコード読取装置であって、前記バーコードをスキャンし、そのバーコードに応じた電気信号を出力するスキャン手段と、前記バーコードに応じた前記電気信号を解析して、前記バーコードが表す情報を取得する解析手段と、前記バーコードが表す前記情報から前記ダミービットが表す情報を抽出して、抽出した前記ダミービットが表す前記情報に基づいてエラーチェックを行うエラーチェック手段と、を備える。

【0020】

この構成によれば、ダミービットを装飾目的だけでなく、エラーチェックのためにも利用できる。言わば、一石二鳥である。

【0021】

上記バーコード読取装置は、前記バーコードに含まれる前記ダミービットのビット数の情報とそのバーコードの前記データビットが表す前記実体的な情報とを関連付けたテーブルをさらに備え、前記エラーチェック手段は、スキャンされた前記ダミービットのビット数を計数し、その計数値及びスキャンされた前記データビットの前記実体的な情報と、前記テーブルに格納された前記ダミービットのビット数の前記情報及び前記データビットが表す前記実体的な情報と、に基づいて、エラーの有無を判定する。この構成によれば、テーブルを持つだけで、簡易にエラーチェックを行うことができる。

【0022】

上記バーコード読取装置において、前記エラーチェック手段は、予め設定された情報に基づいて、前記バーコードが表す前記情報から前記ダミービットが表す前記情報を抽出する。

【0023】

例えば、前記予め設定された情報は、前記データビットのビット数の情報である。バーコードの情報には、データビットの情報及びダミービットの情報が含まれるところ、この構成によれば、データビットのビット数が分かるので、データビットとダミービットとの境界を容易に認識でき、それ故、容易にダミービットの情報を抽出できる。

【0024】

上記バーコード読取装置において、前記エラーチェック手段は、前記データビットに含まれるチェックサムの情報に基づいてエラーチェックを行う。この構成によれば、ダミービットによるエラーチェックに加えて、チェックサムによるエラーチェックも行われるので、得られたデータの信頼性の向上をより図ることができる。

【発明を実施するための最良の形態】

【0025】

以下、本発明の実施の形態について、図面を参照しながら説明する。なお、図中、同一又は相当部分については同一の参照符号を付してその説明を援用する。また、本実施の形態において、0bは二進数を表す。

【0026】

図1は、本発明の実施の形態によるゲームシステムの全体構成を示す図である。図1に示すように、このゲームシステムは、1P(第1プレイヤ)用のゲーム機1A、2P(第2プレイヤ)用のゲーム機1B、テレビジョンモニタ3、及び複数枚のトレーディングカード17を含む。本実施の形態では、このシステムによって、サッカーゲームを行う例を挙げる。

【0027】

ゲーム機1Aとゲーム機1Bとは、ケーブル6によって接続される。ゲーム機1Aは、A/Vケーブル5により、テレビジョンモニタ3に接続される。また、図示していないが、ゲーム機1Aには、ACアダプタ又は電池により、電源電圧が供給される。そして、ゲーム機1Aは、ケーブル6を通して、ゲーム機1Bへ電源電圧を供給する。

【0028】

第1プレイヤ及び第2プレイヤは、それぞれゲーム機1A及び1Bの入力ボタン12〜16(後述)を操作して、テレビジョンモニタ3上の自分のチームの選手キャラクタを動かし、相手チームと対戦する。この場合、当初、選手キャラクタごとに異なる能力のデフォルト値が設定される。この場合の能力とは、選手キャラクタが有するサッカープレイにおけるポテンシャルのことであり、例えば、ロングキック速度、ロングキック威力、シュート能力、ヘディングの高さ、及びドリブル速度等である。ただし、各選手キャラクタの能力は、対応するトレーディングカード17に付されたバーコード21(後述)を読み取ることによって変更可能である。

【0029】

次に、ゲームシステムを構成する各要素について詳しく説明する。

【0030】

図2(a)は、図1のトレーディングカード17の表の面を示す図であり、図2(b)は、図1のトレーディングカード17の裏の面を示す図である。図2(a)に示すように、トレーディングカード17の表には、サッカー選手の写真が印刷される。一方、図2(b)に示すように、トレーディングカード17の裏には、一方の長辺に沿って、帯状のバーコード領域38が設けられ、この領域38に、短辺に平行な黒色のバーと白色のスペースとの組み合わせからなるバーコード21が印刷される。バーコード領域38以外の領域には、サッカー選手のプロフィールが印刷される。

【0031】

より具体的には、トレーディングカード17の裏の面のバーコード領域38において、バーコード21の先頭のバーは、一方の短辺から距離LSの位置に印刷される。そして、バーコード21の最後尾のバーは、先頭のバーから距離LBの位置に印刷される。つまり、トレーディングカード17の長辺に沿った長さLBは、バーコード21の全長である。最後尾のバーから、他方の短辺までは、距離LEである。

【0032】

バーコード21のスキャンは、先頭のバーから最後尾のバーへ向かって実行される。従って、先頭のバーに近い、バーコード領域38のエッジ(図中下側の短辺の一部)を、入力エッジ80と呼ぶことにする。

【0033】

本実施の形態では、実体的な情報の内容が異なるバーコード21が印刷された124種類のトレーディングカード17を用意する。この場合、1人のサッカー選手に対して、4種類のトレーディングカード17が用意される。従って、上記のように、トレーディングカード17によって、テレビジョンモニタ3に表示される選手キャラクタの能力を設定できるので、一体の選手キャラクタの能力は、デフォルトを含めると、異なる5つの能力のいずれかに設定できる。

【0034】

図3(a)は、ゲーム機1Aの斜視図であり、図3(b)は、ゲーム機1Aの平面図であり、図3(c)は、図3(b)のA−A線によるゲーム機1Aの断面図である。

【0035】

図3(a)及び図3(b)を参照して、ゲーム機1Aの上面には、プレイヤがサッカーゲームの進行(主として選手キャラクタ)をコントロールするための入力ボタン12〜16が設けられる。また、ゲーム機1Aには、入力ボタン14の外側に、溝部8が形成される。この溝部8は、トレーディングカード17のバーコード21をスキャンするためのスキャン装置の一部を構成し、平面視において、直線状となっている。ただし、溝部8の入口側60は、入力ボタン14側の壁面64に対向する壁面が、平面視において、外側に広がっている。

【0036】

図3(c)を参照して、溝部8の壁面64には、入口側60の端部と出口側62の端部との中間位置にスリット70が形成される。このスリット70の高さは、バーコード21の一本のバーの長さより小さく設定され、スリット70の幅は、バーコード21の一本のバーの幅より小さく設定される。

【0037】

壁面64の後ろ側であって、かつ、スリット70の後ろ側には、スリット70の長手方向に(つまり、バーコード21のバーの長手方向に)、スキャン装置の他の一部を構成する赤外発光ダイオード72及びフォトトランジスタ74が配置される。溝部8の深さは、バーコード21の一本のバーの長さより深くなるように形成される。ここで、バーの長さとは、トレーディングカード17の短辺に沿った長さのことを指し、バーの幅とは、トレーディングカード17の長辺に沿った長さのことを指す。

【0038】

プレイヤは、トレーディングカード17のバーコード21を、溝部8の壁面64と対面するように向けて、トレーディングカード17の入力エッジ80を、溝部8の入口側60から差し込み、トレーディングカード17のバーコード領域38側の長辺を、溝部8の平坦な底部61に沿ってスライドさせ、出口側62から抜き出す。

【0039】

そうすると、赤外発光ダイオード72からの赤外光は、バーコード21に照射され、そして、バーコード21に反射されて、フォトトランジスタ74に入射する。この場合、バーコード21の白色のスペースは、黒色のバーよりも、より強く赤外光を反射するので、白色のスペースが反射した赤外光がフォトトランジスタ74に入射する場合が、黒色のバーが反射した赤外光がフォトトランジスタ74に入射する場合よりも、フォトトランジスタ74の出力レベルは大きくなる。従って、上記のようにトレーディングカード17を溝部8に沿ってスライドさせることにより、フォトトランジスタ74からは、バーコード21のパターンに応じたパルス信号が出力される。ゲーム機1Aは、このパルス信号を解析して、バーコード21の情報を読み取り、選手キャラクタに反映させる。

【0040】

図4は、ゲーム機1Aの電気的構成を説明するブロック図である。図4に示すように、ゲーム機1Aは、プロセッサ23、検知ユニット25、操作スイッチ28、ROM(read only memory)27、及びバス26を含む。

【0041】

検知ユニット25は、上述の赤外発光ダイオード72及びフォトトランジスタ74を含み、さらに、フォトトランジスタ74の出力信号を増幅・反転・整形して出力するアンプ(図示せず)を含む。従って、フォトトランジスタ74の出力信号を反転した信号がプロセッサ23に入力される。つまり、検知ユニット25からプロセッサ23に入力されるパルス信号の高いレベルは、黒色のバーに対応し、低いレベルは、白色のスペースに対応する。ただし、検知ユニット25は、必ずしも反転出力する必要はなく、反転せずに出力してもよい。

【0042】

上記のように、フォトトランジスタ74の出力信号は、トレーディングカード17のバーコード21のパターンに応じたパルス信号なので、プロセッサ23は、検知ユニット25からのパルス信号を解析して、バーコード21の情報を読み取り、選手キャラクタに反映させる。

【0043】

操作スイッチ28は、上記の入力ボタン12〜16を含む。プロセッサ23は、これらからのオン/オフ信号を受けて、第1プレイヤの選手キャラクタを動かしたり、その他のゲームの進行を制御する。

【0044】

ところで、図1のゲーム機1Bは、ゲーム機1Aと同様の構成を有する。従って、ゲーム機1Bは、ゲーム機1Aの入力ボタン12〜16と同様の入力ボタン12〜16を有する。ただし、ゲーム機1Bには、プロセッサ23、バス26、ROM27、及び検知ユニット25は搭載されず、溝部8も形成されない。

【0045】

従って、図4に示すように、ゲーム機1Bの入力ボタン12〜16のオン/オフ信号は、ケーブル6により、ゲーム機1Aに伝送され、プロセッサ23は、これらからのオン/オフ信号を受けて、第2プレイヤの選手キャラクタを動かしたり、その他のゲームの進行を制御する。

【0046】

また、プロセッサ23は、バス26を通じて、ROM27にアクセスできる。従って、プロセッサ23は、ROM27に格納されたプログラムを実行でき、また、ROM27に格納されたデータをリードして処理することができる。このROM27に、後述のフローチャートで示される各処理を行うプログラム、画像データ、及び音声データ等が予め格納される。

【0047】

つまり、プロセッサ23は、ROM27に格納されたプログラムを実行し、ゲーム機1A及び1Bの入力ボタン12〜16のオン/オフ信号に基づいて、各種演算、グラフィック処理、及びサウンド処理を実行して、ROM27に格納された画像データ及び音声データからビデオ信号VD及びオーディオ信号AUを生成する。プロセッサ23が生成したビデオ信号VDおよびオーディオ信号AUは、A/Vケーブル5を介して、テレビジョンモニタ3に与えられ、応じて、テレビジョンモニタ3に映像が表示され、そのスピーカ(図示せず)から音声が出力される。

【0048】

図5は、図4のプロセッサ23の電気的構成を示すブロック図である。図5に示すように、このプロセッサ23は、中央演算処理装置(CPU:central processing unit)101、グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、DMA(direct memory access)コントローラ109、第1バスアービタ113、第2バスアービタ114、バックアップコントロール回路115、メインメモリ117、タイマ回路119、A/Dコンバータ(ADC:analog to digital converter)120、入出力制御回路121、外部メモリインタフェース回路123、クロックドライバ129、PLL(phase−locked loop)回路127、低電圧検出回路125、第1バス131、及び第2バス133を含む。

【0049】

本実施の形態では、メインメモリ117及びROM27を区別して説明する必要がないときは、「メモリMEM」と表記する。

【0050】

CPU101は、メモリMEMに格納されたプログラムに従い、各種演算やシステム全体の制御を行う。CPU101は、第1バス131及び第2バス133のバスマスタであり、それぞれのバスに接続された資源にアクセスが可能である。

【0051】

グラフィックプロセッサ103は、第1バス131及び第2バス133のバスマスタであり、メモリMEMに格納されたデータを基に、グラフィックデータを合成し、さらにこれを基にテレビジョンモニタ3に合わせたビデオ信号VDを生成して出力する。ここで、グラフィックデータは、バックグラウンドスクリーンとスプライトとビットマップスクリーンとから合成される。また、グラフィックプロセッサ103は、第1バス131を通じて、CPU101により制御され、また、CPU101に対して、割込み要求信号INRQを発生する機能を有する。

【0052】

ピクセルプロッタ105は、第1バス131を通じて、CPU101により制御され、CPU101から与えられたピクセルデータの描画を実行する。この場合、ピクセル単位での描画が可能である。ここで言うピクセルデータは、1ピクセルの表示色をMビット(Mは1以上の整数)で表したデータである。また、ピクセルプロッタ105は、キャッシュシステムにより、高速な描画と効率的なバス(第1バス131及び第2バス133)の使用を実現している。さらに、ピクセルプロッタ105は、第1バス131及び第2バス133のバスマスタであり、キャッシュ(図示せず)からメモリMEMへのライト及びメモリMEMからキャッシュへのライトを自律的に行うことができる。

【0053】

サウンドプロセッサ107は、第1バス131及び第2バス133のバスマスタであり、メモリMEMに格納されたデータを基に、サウンドデータを合成し、さらにこれを基にオーディオ信号AUを生成して出力する。サウンドデータは、基本の音色となるPCM(パルスコードモジュレーション)データに対し、ピッチ変換及び振幅変調を行い合成される。振幅変調では、CPU101によって指示されるボリューム制御の他に、楽器の波形を再現するためのエンベロープ制御の機能が用意される。また、サウンドプロセッサ107は、第1バス131を通じて、CPU101により制御され、また、CPU101に対して、割込み要求信号INRQを発生する機能を有する。

【0054】

DMAコントローラ109は、外部バス26に接続されたROM27から、メインメモリ117へのデータ転送を司る。また、DMAコントローラ109は、データ転送の完了を通知するために、CPU101に対する割込み要求信号INRQを発生する機能を有する。さらに、DMAコントローラ109は、第1バス131及び第2バス133のバスマスタであり、また、第1バス131を通じてCPU101により制御される。

【0055】

メインメモリ117は、マスクROM、SRAM、及び、DRAMのうち、必要なものを備える。本実施の形態では、メインメモリ117をSRAMで構成する。

【0056】

バックアップコントロール回路115は、後述の低電圧検出回路125が低電圧を検知した場合に、メインメモリ117を非活性化する。そして、メインメモリ117には、バッテリ141から電源電圧が供給される。従って、電源電圧Vcc0及びVcc1の供給が停止された場合でも、SRAMたるメインメモリ117のデータが保持される。

【0057】

第1バスアービタ113は、第1バス131の各バスマスタからの第1バス使用要求信号を受け付け、調停を行って、バスサイクル毎に1つのバスマスタに対して第1バス使用許可信号を発行する。各バスマスタは、第1バス使用許可信号を受領することによって第1バス131の使用が許可される。ここで、第1バス使用要求信号及び第1バス使用許可信号は、図5では、第1バス調停信号FABとして示されている。

【0058】

第2バスアービタ114は、第2バス133の各バスマスタからの第2バス使用要求信号を受け付け、調停を行って、要求されたバイト数に対応する1または複数のバスサイクル毎に1つのバスマスタに第2バス使用許可信号を発行する。各バスマスタは、第2バス使用許可信号を受領することによって第2バス133の使用が許可される。ここで、第2バス使用要求信号及び第2バス使用許可信号は、図5では、第2バス調停信号SABとして示されている。

【0059】

タイマ回路119は、設定された時間間隔に基づき、CPU101に対する割込み要求信号INRQを発生する機能を有する。時間間隔等の設定は、第1バス131を介してCPU101によって行われる。

【0060】

ADC120は、アナログ入力信号をデジタル信号に変換する。このデジタル信号は、第1バス131を介してCPU101によってリードされる。また、ADC120は、CPU101に対して、割込み要求信号INRQを発生する機能を有する。なお、外部からのアナログ信号は、例えば、6つのアナログポートAIN0〜5(図示せず)を介して、ADC120へ入力される。

【0061】

入出力制御回路121は、外部入出力装置や外部の半導体素子との通信等を、入出力信号を介して行う。入出力信号は、第1バス131を介して、CPU101からリード/ライトされる。また、入出力制御回路121は、CPU101に対して、割込み要求信号INRQを発生する機能を有する。なお、入出力信号は、例えば、プログラマブルな入出力ポートIO0〜IO23(図示せず)を介して入出力される。

【0062】

本実施の形態では、CPU101は、ゲーム機1A及び1Bの入力ボタン12〜16からのオン/オフ信号を、入出力制御回路を介して取得する。

【0063】

低電圧検出回路125は、電源電圧Vcc0及びVcc1を監視し、いずれかの電源電圧がそれぞれについて定められた電圧以下になったときに、PLL回路127等のリセット信号LPW、その他のシステム全体のリセット信号RESを発行する。ここで、電源電圧Vcc0は、例えば、+2.5Vであり、主にプロセッサ23内のデジタル回路に供給される。また、電源電圧Vcc1は、例えば、+3.3Vであり、主にプロセッサ23内のアナログ回路及びI/O部に供給される。

【0064】

PLL回路127は、水晶振動子137より得られる正弦波信号を逓倍した高周波クロック信号ckを生成する。

【0065】

クロックドライバ129は、PLL回路127より受け取った高周波クロック信号ckを、十分な信号強度へ増幅して、内部クロックCKとして、各ブロックへ供給する。

【0066】

外部メモリインタフェース回路123は、第2バス133を外部バス26に接続するための機能を有する。

【0067】

図5のプロセッサ23におけるデータの転送経路を説明する。例えば、バスマスタたるCPU101が、バススレイブとして第1バス131に接続されている他の機能ブロック(グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、DMAコントローラ109、第1バスアービタ113、および第2バスアービタ114等)を制御する場合は、これら機能ブロックの制御レジスタ等へのライトデータは、第1バスアービタ113へ与えられ、調停後に、第1バス131から、各機能ブロックに与えられ、一方、これら機能ブロックの制御レジスタ等からのリードデータは、調停後に、第1バス131及び第1バスアービタ113を介して、CPU101に与えられる。但し、グラフィックプロセッサ103、ピクセルプロッタ105、サウンドプロセッサ107、およびDMAコントローラ109は、第1バス131のバスマスタとして、第1バスアービタ113へバス使用要求を行う機能を備える。

【0068】

バスマスタが、メインメモリ117に対してアクセスする場合は、ライトデータは、第1バスアービタ113に与えられ、調停後に、第1バス131から、メインメモリ117に与えられ、一方、リードデータは、調停後に、第1バス131及び第1バスアービタ113を介して、バスマスタに与えられる。

【0069】

また、バスマスタが、ROM27に対してアクセスする場合は、ライトデータは、第2バスアービタ114に与えられ、調停後に、第2バス133から、外部メモリインタフェース回路123及び外部バス26を介して、ROM27に与えられ、一方、リードデータは、調停後に、外部バス26、外部メモリインタフェース回路123、第2バス133及び第2バスアービタ114を介して、バスマスタに与えられる。

【0070】

次に、本実施の形態のバーコード21について詳しく説明する。

【0071】

図6(a)〜図6(c)は、バーコード21の例示図である。図6(a)及び図6(c)を参照して、これらのバーコード21は、バーコード21の先頭を示すスタートビット41、トレーディングカード17の識別情報(ID)を含むデータビット43、エラーチェックのためのチェックサム45、チェックサム45の終了を示すストップビット47、及び全種類のバーコード21の全長を揃えるためのダミービット49からなる。また、図6(b)を参照して、このバーコード21は、スタートビット41、データビット43、チェックサム45、及びストップビット47からなる。このように、データビット43の全長によっては、ダミービット49が存在しないバーコード21もある。

【0072】

図6(a)〜図6(c)を参照して、データビット43は、15ビットの情報を表す。後で図示するが、1ビットは、「0」を示す単位データビット35あるいは「1」を示す単位データビット36からなる。データビット43の第0ビットから第7ビットが、トレーディングカード17のIDを表し、第8ビットから第14ビットは、PK(ペナルティキック)対戦で使用するPKパラメータを表す。ROM27には、トレーディングカード17のIDと選手キャラクタの能力値とを関連付けた能力テーブルが用意される。従って、プロセッサ23は、トレーディングカード17のIDをインデックスとして、この能力テーブルを参照して、選手キャラクタの能力値を取得する。このように、バーコード21には、能力値そのものを含ませず、IDを含ませることで、バーコード21の情報量を少なくしている。

【0073】

チェックサム45は、データビット43に含まれる「0」の数を4ビットで表している。1ビットは、単位データビット35あるいは単位データビット36からなる。

【0074】

ダミービット49は、全種類のバーコード21の全長を揃えるために、ストップビット47の後に付される。なぜなら、図6(a)〜図6(c)から明らかなように、データビット43の全長は、それが表す情報の内容によって異なってくるからである。後で図示するが、ダミービット49は、幅が同じ1以上の単位ダミービット50からなる。従って、データビット43の全長に応じて、何個の単位ダミービット50を付加するのか、あるいは、ダミービット49を付加しないのか、が決定される。本実施の形態では、最大3個の単位ダミービット50を付加する。

【0075】

ダミービット49を付加することにより、全種類のバーコード21の全長が揃えられるが、完全に一致するわけではなく、概ね一致する。例えば、所定のバーコード21の全長を基準に、所定範囲内に収まるように単位ダミービット50を付加する。

【0076】

もし、ダミービット49を付加しないならば、トレーディングカード17間で、バーコード21の全長が大きく異なるため、見た目が好ましくない。そこで、ダミービット49を付加して、バーコード21の外観の均整を図る。このように、ダミービット49は、装飾的な機能を有する。

【0077】

一方、ダミービット49は、エラーチェックのためにも使用される。ROM27には、このエラーチェックに使用するためのテーブルが格納されている。

【0078】

図7は、ダミービット49を利用したエラーチェックの際に使用されるテーブルの例示図である。図7を参照して、このテーブルは、トレーディングカード17のID、つまり、データビット43の第0ビット〜第7ビットと、トレーディングカード17の単位ダミービット50の数と、を関連付けたものである。

【0079】

プロセッサ23は、このテーブルを参照して、スキャンの結果得られたバーコード21のデータビット43が示すトレーディングカード17のIDに関連付けられた単位ダミービット50の数を取得する。そして、プロセッサ23は、スキャンの結果得られたバーコード21の単位ダミービット50の数と、テーブルから取得した単位ダミービット50の数と、を比較して、スキャンエラーか否かを判定する。プロセッサ23は、両者が不一致の場合はエラーと認識する。このように、本実施の形態では、チェックサム45及びダミービット49を用いて、二重のエラーチェックを行っている。このため、エラーデータが処理に反映されることを極力防止できる。

【0080】

ここで、バーコード21のうち、ダミービット49を除く部分、即ち、スタートビット41、データビット43、チェックサム45、及びストップビット47を、広義のデータビットと位置づける。従って、データビット43は、狭義のデータビットである。

【0081】

図8(a)は、バーコード21のスタートビット41の説明図である。図8(a)を参照して、スタートビット41は、それぞれ幅が「w」の黒色バー33、白色スペース31、及び黒色バー33をスキャンの方向に並べて構成される。プロセッサ23は、このスタートビット41を検知することで、バーコード21の先頭を認識できる。白色スペース31及びその後の黒色バー33の組は、「0」(つまり論理0)を表す。

【0082】

図8(b)は、バーコード21のストップビット47の説明図である。図8(b)を参照して、ストップビット47は、幅が「2w」の白色スペース32及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。ストップビット47は、「1」(つまり論理1)を表す。プロセッサ23は、このストップビット47を検知することで、チェックサム45の終了を認識できる。

【0083】

図8(c)は、バーコード21の単位ダミービット50の説明図である。図8(c)を参照して、単位ダミービット50は、幅が「3w」の白色スペース34及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。1以上の単位ダミービット50により、ダミービット49が構成される。単位ダミービット50は、「1」(つまり論理1)を表す。

【0084】

図8(d)は、バーコード21の単位データビット35の説明図である。図8(d)を参照して、単位データビット35は、幅が「w」の白色スペース31及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。単位データビット35は、「0」(つまり論理0)を表す。

【0085】

図8(e)は、バーコード21の単位データビット36の説明図である。図8(e)を参照して、単位データビット36は、幅が「2w」の白色スペース32及び幅が「w」の黒色バー33をスキャンの方向に並べて構成される。単位データビット35は、「1」(つまり論理1)を表す。

【0086】

合計15個の単位データビット35及び/又は36によりデータビット43が構成され、合計4個の単位データビット35及び/又は36によりチェックサムが構成される。

【0087】

図6(a)〜図6(c)に戻って、図6(a)のデータビット43は、「0b000000000000000」を、図6(b)のデータビット43は、「0b111111111111111」を、図6(c)のデータビット43は、「0b011001010100101」を、それぞれ表す。

【0088】

このように、「0」を示す単位データビット35が多いバーコード21ほど、その全長が短くなり、「1」を示す単位データビット36が多いバーコード21ほど、その全長が長くなる。従って、図6(a)のバーコード21は、3個の単位ダミービット50を含み、図6(b)のバーコード21は、単位ダミービット50を含まず、図6(c)のバーコード21は、2個の単位ダミービット50を含む。このように、単位ダミービット50を付加する数によって、バーコード21の長さを統一して、見た目を整えている。

【0089】

次に、バーコード21の解析方法の基本原理を説明する。

【0090】

図9(a)及び図9(b)は、バーコード21の解析方法の基本原理の説明図である。プレイヤが、図9(a)のトレーディングカード17をゲーム機1Aの溝部8に沿ってスライドさせると、検知ユニット25のフォトトランジスタ74は、信号を反転する上記したアンプ(図示せず)を介して、図9(b)に示す信号71を出力する。なお、この例では、トレーディングカード17をスライドさせる速度が一定であるとしている。

【0091】

より詳細には、次の通りである。ゲーム機1Aの溝部8にトレーディングカード17がない状態では、赤外発光ダイオード72からの赤外光は、溝部8の壁面64に対面する壁面に照射されるため、反射赤外光は弱く、それ故、フォトトランジスタ74の出力信号のレベルは低くなる。ところが、検知ユニット25は、フォトトランジスタ74の出力信号を反転して出力するので、この状態では、検知ユニット25の出力信号のレベルは高くなる(ハイレベル)。

【0092】

そして、プレイヤがトレーディングカード17を溝部8に沿ってスライドさせると、まず、トレーディングカード17の入力エッジ80から長さLS(図2(b)参照)までは、白色の領域が続くので、この領域に照射され、反射される赤外光は強く、それ故、フォトトランジスタ74の出力信号のレベルは高くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは低い(ローレベル)。

【0093】

次に、スタートビット41の最初の黒色バーに、赤外光が照射されるため、反射赤外光は弱く、それ故、フォトトランジスタ74の出力信号のレベルは低くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは高い(ハイレベル)。

【0094】

次に、スタートビット41の最初の白色スペースに、赤外光が照射されるため、反射赤外光は強く、それ故、フォトトランジスタ74の出力信号のレベルは高くなる。ところが、検知ユニット25は、反転出力を行うので、この状態では、出力信号71のレベルは低い(ローレベル)。

【0095】

以下同様に、黒色バーに赤外光が照射されたときは、検知ユニット25の出力信号71は高いレベル(ハイレベル)となり、白色スペースに赤外光が照射されたときは、検知ユニット25の出力信号71は低いレベル(ローレベル)となる。

【0096】

本実施の形態では、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジを順次検出する。これは、プロセッサ23が、黒色バーの後端エッジ(図中右側のエッジ(長辺))を順次検出することを意味する。そして、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジから次の立ち下がりエッジまでの時間を計測する。これは、プロセッサ23が、黒色バーの後端エッジから次の黒色バーの後端エッジまでの長さを計測することに相当する。

【0097】

単位データビット35(幅2w)は、単位データビット36(幅3w)より小さい。従って、黒色バーの後端エッジから、その次の単位データビット35を構成する黒色バーの後端エッジまでの長さ2wは、黒色バーの後端エッジから、その次の単位データビット36を構成する黒色バーの後端エッジまでの長さ3wより短い。

【0098】

言い換えると、黒色バーの後端エッジに相当する出力信号71の立ち下がりエッジから、その次の単位データビット35を構成する黒色バーの後端エッジに相当する出力信号71の立下りエッジまでの時間T0は、黒色バーの後端エッジに相当する出力信号71の立ち下がりエッジから、その次の単位データビット36を構成する黒色バーの後端エッジに相当する出力信号71の立下りエッジまでの時間T1より短い。

【0099】

よって、プロセッサ23は、検知ユニット25の出力信号の立ち下がりエッジから次の立ち下がりエッジまでの時間を計測し、その長短を判定することにより、単位データビット35と単位データビット36とを判別する。

【0100】

ところが、トレーディングカード17をスライドさせるのはプレイヤ、つまり、人間であるため、ゲーム機1Aのスリット70を通過するときの黒色バーの速度は、それぞれのバーで異なってくる。また、プレイヤによっても、トレーディングカード17をスライドさせるときの速度は異なってくる。これらの点を考慮し、本実施の形態では、後述のフローチャートに示すようにして、単位データビット35と単位データビット36とを判別している。

【0101】

さて、本実施の形態では、スキャンモード、ゲームモード、及びPKモードが用意される。スキャンモードは、トレーディングカード17のバーコード21をスキャンするモードである。ゲームモードは、第1プレイヤと第2プレイヤとがそれぞれの選手キャラクタを操作して、サッカーゲームの対戦を行うモードである。PKモードは、第1プレイヤと第2プレイヤとがそれぞれのトレーディングカード17を使用して、PKの対戦を行うモードである。

【0102】

以下では、第1プレイヤあるいは第2プレイヤが、入力ボタン12〜16を操作して、スキャンモードを選択した場合の処理を説明する。

【0103】

図10は、図4のプロセッサ23によるスキャンモードでの処理の流れを示すフローチャートである。図10を参照して、ステップS1にて、プロセッサ23は、システムの初期設定を実行する。この処理で、図10の処理及び後述する図11〜図13の処理で使用される全ての変数及びカウンタが初期化(0を代入)されるとともに、全てのフラグがオフ(クリア)される。ただし、後述するプレイヤ特定フラグは第1プレイヤを示す値にセットされる。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。

【0104】

ステップS2にて、プロセッサ23は、検知ユニット25の出力信号71の立ち下がりエッジを検出するためのエッジトリガをイネーブルにする。これにより、図5の入出力制御回路121は、出力信号71の立ち下がりエッジを検出した時に、割込み要求信号INRQをCPU101に発行する。以下、この時の込み要求信号INRQをエッジトリガと呼ぶ。

【0105】

ここで、ステップS3以降の説明の前に、割込み処理について説明する。この割込み処理は、エッジトリガによる割込み又はタイマ回路119による割込みが発生した時に、プロセッサ23により実行される。

【0106】

図11は、図4のプロセッサ23の割込み処理の流れを示すフローチャートである。図11を参照して、ステップS30にて、プロセッサ23は、割り込みが、エッジトリガに基づくものか、あるいは、タイマ回路119に基づくものか、を判断し、エッジトリガに基づく割込みの場合はステップS31に進み、タイマ回路119に基づく割り込みの場合ステップS48に進む。

【0107】

エッジトリガに基づく割込みの場合、ステップS31にて、プロセッサ23は、バーコード21を読み込み中であることを示すリード中フラグをオンにする。なぜなら、エッジトリガが発生したということは、トレーディングカード17の入力エッジ又はバーコード21の黒色バーの後端エッジが検出されたことを意味するので、バーコード21の読み取り中ということになるからである。

【0108】

ステップS32にて、プロセッサ23は、検知ユニット25の出力信号71の立下りエッジの検出回数を計数するカウンタCEが「0」か否かを判断する。カウンタCEが「0」の場合は、その時のエッジトリガは、トレーディングカード17の入力エッジ80が検出されたことに基づくものであるので、ステップS33に進む。一方、カウンタCEが「0」以外の場合は、その時のエッジトリガは、バーコード21の黒色バーの後端エッジが検出されたことに基づくものであるので、ステップS35に進む。

【0109】

入力エッジ80が検出された場合、ステップS33にて、プロセッサ23は、タイマ回路119による割込みをセットし、メインルーチンにリターンする。この場合、割込み発生の間隔は、例えば、0.5秒にセットされる。

【0110】

入力エッジ80が検出された後、0.5秒以内に、スタートビット41の最初の黒色バーの後端エッジが検出されない場合は、トレーディングカード17が溝部8に挿入されたにも拘らず、停止しているとみなして、読み取りエラーと判断するためである。なお、ここで設定する0.5秒は、あくまでも例示であり、図2(b)の長さLSに応じて、適宜変更される。

【0111】

ステップS34にて、プロセッサ23は、カウンタCEを1つインクリメントして、メインルーチンにリターンする。

【0112】

ステップS32で、カウンタCEが「0」以外であると判断されると、ステップS35にて、プロセッサ23は、カウンタCEが「1」か否かを判断する。カウンタCEが「1」の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーの後端エッジが検出されたことに基づくものであるので、ステップS45に進む。一方、カウンタCEが2以上の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーに後続する一連の黒色バーのいずれかの後端エッジが検出されたことに基づくものであるので、ステップS36に進む。

【0113】

スタートビット41の最初の黒色バーの後端エッジが検出された場合、ステップS45にて、プロセッサ23は、タイマ回路119による割込みをセットする。この場合、割込み発生の周波数は、例えば、625kHzにセットされる。この割り込みは、検知ユニット25の出力信号71立下りエッジと次の立ち下がりエッジとの間隔を計測するためのものである。

【0114】

ステップS46にて、プロセッサ23は、カウンタCEを1つインクリメントして、メインルーチンにリターンする。

【0115】

ステップS35でカウンタCEが2以上の場合は、ステップS36にて、プロセッサ23は、カウンタCEを1つインクリメントする。ステップS37にて、プロセッサ23は、カウンタCEが「26」か否かを判断する。カウンタCEが「26」の場合は、その時のエッジトリガは、3個の単位ダミービット50が付加されたバーコード21の最後尾の黒色バー、つまり、3つ目の単位ダミービット50の黒色バーの後端エッジが検出されたことに基づくものであるので、バーコード21の読み取り処理を終了すべくステップS38に進む。一方、カウンタCEが3以上26未満の場合は、その時のエッジトリガは、スタートビット41の最初の黒色バーに後続する一連の黒色バーのいずれかの後端エッジが検出されたことに基づくものであるので、ステップS42に進む。

【0116】

3つ目の単位ダミービット50の黒色バーの後端エッジが検出された場合、ステップS38にて、プロセッサ23は、バーコード21の読み込み処理が終了したことを示すリード終了フラグをオンにする。ステップS39にて、プロセッサ23は、リード中フラグをオフにする。ステップS40にて、プロセッサ23は、エッジトリガをディセーブルにする。ステップS41にて、プロセッサ23は、タイマ回路119による割込みを解除する。

【0117】

ステップS42では、プロセッサ23は、カウンタTCの値を配列Aの要素A[k]として格納する。カウンタTCの値は、検知ユニット25の出力信号71の立下りエッジから次の立下りエッジまでの時間に相当する。ステップS43にて、プロセッサ23は、カウンタTCに「0」を代入する。ステップS44にて、プロセッサ23は、配列Aの要素番号を表す変数kを1つインクリメントして、メインルーチンにリターンする。

【0118】

ちなみに、ステップS42において、変数kが「0」(初期値)の場合は、CE=3であるので、その時のカウンタTCの値は、スタートビット41の最初の黒色バーの後端エッジに対応する出力信号71の立ち下がりエッジから、その次の立下りエッジまでの時間を示す。この場合のカウンタTCの値は、配列Aの要素A[0]として格納される。従って、スタートビット41の最初の黒色バーの後端エッジから、スタートビット41の最後尾の黒色バーの後端エッジまでの距離に相当する時間が、配列Aの要素A[0]として格納される。もちろん、要素A[0]として格納されるカウンタTCの値は、その時のトレーディングカード17のスライド速度に依存して変動する。上記のように、プレイヤによるトレーディングカード17のスライド速度は一定ではないので、プロセッサ23は、要素A[0]として格納されたカウンタTCの値を基準に、単位データビット35と単位データビット36とを判別する。この点は、後述する。

【0119】

プロセッサ23は、ステップS30でタイマ回路119による割り込みであると判断した場合は、ステップS48にて、カウンタCEが「1」か否かを判断する。カウンタCEが「1」のときに発生するタイマ回路119による割り込みは、ステップS33に基づくものである。従って、この場合、バーコード21のスタートビット41の最初の黒色バーの後端エッジが未だ検出されていない。このため、カウンタCEが「1」の場合、読み取りエラーと判断すべく、ステップS49に進む。一方、カウンタCEが2以上のときに発生するタイマ回路119による割り込みは、ステップS45に基づくものである。従って、出力信号71の立ち下がりエッジ間の時間を計測すべく、ステップS51に進む。

【0120】

ステップS49では、プロセッサ23は、バーコード21のスキャンにエラーが発生したことを示すエラーフラグをオンにする。そして、ステップS50にて、プロセッサ23は、リード中フラグをオフにして、ステップS55に進む。

【0121】

一方、ステップS51では、プロセッサ23は、カウンタTCを1つインクリメントする。ステップS52にて、プロセッサ23は、カウンタTCの値が35ミリ秒に相当するか否かを判断し、35ミリ秒に相当しない場合は、メインルーチンにリターンする。プロセッサ23は、カウンタTCの値が35ミリ秒に相当する場合は、読み取り処理を終了すべく、ステップS53に進む。カウンタTCの値が35ミリ秒ということは、出力信号71の立下りエッジが検出されてから35ミリ秒が経過したが、次の立ち下がりエッジが検出されていないことを意味する。つまり、35ミリ秒の間、出力信号71の立ち下がりエッジが発生していないことになる。そこで、このような場合は、読み取りを終了することにしたのである。ステップS53では、プロセッサ23は、リード終了フラグをオンにする。そして、ステップS54にて、プロセッサ23は、リード中フラグをオフにする。

【0122】

ステップS55では、プロセッサ23は、エッジトリガをディセーブルにする。ステップS56にて、プロセッサ23は、タイマ回路119による割込みを解除して、メインルーチンにリターンする。

【0123】

図10に戻って、ステップS3では、プロセッサ23は、バーコード21のスキャンにエラーが発生したことを示すエラーフラグを参照して、オンの場合はステップS15に進み、オフの場合はステップS4に進む。

【0124】

ステップS15では、プロセッサ23は、バーコード21をスキャンするための再設定を行う。具体的には、プロセッサ23は、図10及び図11の処理並びに後述する図12及び図13の処理で使用される全ての変数及びカウンタを初期化(0を代入)するとともに、全てのフラグをオフ(クリア)にする。ただし、後述するプレイヤ特定フラグの値は維持される。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。さらに、プロセッサ23は、ステップS2と同様にエッジトリガをイネーブルにする。ステップS16にて、プロセッサ23は、エラーである旨のテレビジョンモニタ3への表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0125】

ステップS3でエラーでない場合、ステップS4にて、プロセッサ23は、バーコード21の読み取りが終了したことを示すリード終了フラグを参照して、オフの場合はステップS12に進み、オンの場合はステップS5に進む。

【0126】

ステップS12では、プロセッサ23は、バーコード21を読み込み中であることを示すリード中フラグを参照して、オンの場合はステップS13に進み、オフの場合はステップS14に進む。ステップS13では、プロセッサ23は、リード中である旨のテレビジョンモニタ3への表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。一方、ステップS14では、プロセッサ23は、待機中である旨の表示のための画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0127】

ステップS4でリード終了の場合、ステップS5にて、プロセッサ23は、読み込んだバーコード21のデータ(つまり、配列A)を解析する。

【0128】

図12は、図10のステップS5のデータ解析処理の流れを示すフローチャートである。図12を参照して、ステップS70にて、プロセッサ23は、検知ユニット25の出力信号71の立下りエッジの検出回数を計数するカウンタCEが22以下か否かを判断する。カウンタCEが22以下の場合は、ストップビット47が検出されていないので、読み取りエラーとすべく、プロセッサ23は、図10のステップS15に進む。カウンタCEが22を超えている場合は、ストップビット47は検出されているので、データ解析を行うべく、プロセッサ23は、ステップS71に進む。

【0129】

ステップS71にて、プロセッサ23は、配列Aの要素番号を示す変数nが「0」か否かを判断する。変数nが「0」のときの配列Aの要素A[0]は、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wに相当する時間である。つまり、要素A[0]はスタートビット41に関する情報であり、実体的な情報ではない。そこで、この場合、プロセッサ23は、ステップS73に進む。ステップS73では、プロセッサ23は、「0」を配列Dの要素D[0]として格納し、ステップS74に進む。なぜなら、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wは、「0」を示す単位データビット35の幅2wと同一であるため、スタートビット41の最初の黒色バーの後端エッジから次の黒色バーの後端エッジまでの距離2wに相当する時間を、「0」と判定するための基準とするためである。

【0130】

ステップS71で変数nが1以上のときは、ステップS74にて、プロセッサ23は、変数nを1つインクリメントする。ステップS75にて、プロセッサ23は、配列Dの要素D[n−1]が「0」か否かを判断し、「0」の場合はステップS76に進み、「0」でない場合、つまり、「1」の場合ステップS80に進む。

【0131】

ステップS76では、プロセッサ23は、配列Aの要素A[n−1]に1.25を乗じて、閾値Th0とする。つまり、1つ前の単位データビットが「0」を示す単位データビット35である場合、その単位データビット35の幅2wに相当する時間である要素A[n−1]に1.25を乗じて、閾値Th0とする。1つ前が、スタートビット41の場合も同様に、スタートビット41の最初の黒色バーの後端エッジから最後尾の黒色バーの後端エッジまでの長さ2wに相当する時間である要素A[0]に1.25を乗じて、閾値Th0とする。

【0132】

そして、ステップS77にて、プロセッサ23は、配列Aの要素A[n]が閾値Th0より小さいか否かを判断し、小さい場合は今回の単位データビットが「0」を示す単位データビット35であるとし、ステップS79に進む。ステップS79では、プロセッサ23は、「0」を配列Dの要素D[n]として格納する。一方、プロセッサ23は、配列Aの要素A[n]が閾値Th0より小さくない場合は今回の単位データビットが「1」を示す単位データビット36であるとし、ステップS78に進む。ステップS78では、プロセッサ23は、「1」を配列Dの要素D[n]として格納する。

【0133】

ステップS75で配列Dの要素D[n−1]が「1」の場合、ステップS80にて、プロセッサ23は、配列Aの要素A[n−1]に0.75を乗じて、閾値Th1とする。つまり、1つ前の単位データビットが「1」を示す単位データビット36である場合、その単位データビット36の幅3wに相当する時間である要素A[n−1]に0.75を乗じて、閾値Th1とする。

【0134】

そして、ステップS81にて、プロセッサ23は、配列Aの要素A[n]が閾値Th1より大きいか否かを判断し、大きい場合は今回の単位データビットが「1」を示す単位データビット36であるとし、ステップS82に進む。ステップS82では、プロセッサ23は、「1」を配列Dの要素D[n]として格納する。一方、プロセッサ23は、配列Aの要素A[n]が閾値Th1より大きくない場合は今回の単位データビットが「0」を示す単位データビット35であるとし、ステップS83に進む。ステップS83では、プロセッサ23は、「0」を配列Dの要素D[n]として格納する。

【0135】

ステップS84では、プロセッサ23は、変数nが値(CE−3)に等しいか否かを判断し、「NO」の場合ステップS71に戻り、「YES」の場合メインルーチンにリターンする。n=CE−3は、バーコード21の最後尾の黒色バーまで、対応するデータが配列Dに格納されたことを意味する。

【0136】

ここで、ステップS76では、要素A[n−1]に1.25を乗じている。理由は次の通りである。前回と今回の単位データビットが単位データビット35の場合において、トレーディングカード17のスライド速度が減速した場合、もし、要素A[n−1]をそのまま閾値Th0とするならば、単位データビット35の長さに相当する要素A[n]が閾値Th0より大きいと判断され、単位データビット35が「1」として要素D[n]に格納されてしまう。この誤認識を回避するために、プラス25%のマージンを持たせたのである。なお、どのくらいのマージンを持たせるかは、プラス25%に限らず、経験的に定めることができる。ちなみに、トレーディングカード17のスライド速度が加速した場合は、上記のケースでは、問題なく単位データビット35が「0」と認識される。

【0137】

また、ステップS80では、要素A[n−1]に0.75を乗じている。理由は次の通りである。前回と今回の単位データビットが単位データビット36の場合において、トレーディングカード17のスライド速度が加速した場合、もし、要素A[n−1]をそのまま閾値Th1とするならば、単位データビット36の長さに相当する要素A[n]が閾値Th1より小さいと判断され、単位データビット36が「0」として要素D[n]に格納されてしまう。この誤認識を回避するために、マイナス25%のマージンを持たせたのである。なお、どのくらいのマージンを持たせるかは、マイナス25%に限らず、経験的に定めることができる。ちなみに、トレーディングカード17のスライド速度が減速した場合は、上記のケースでは、問題なく単位データビット36が「1」と認識される。

【0138】

図10に戻って、ステップS6では、プロセッサ23は、スタートビット41及びストップビット47に基づいてエラーチェックを行う。具体的には、プロセッサ23は、配列Dから、スタートビット41が示すデータを格納している要素D[0]及びストップビット47が示すデータを格納している要素D[20]を取得する。そして、プロセッサ23は、要素D[0]が「1」及び/又は要素D[20]が「0」の場合は、エラーと判断して、ステップS15に進み、それ以外は、つまり、要素D[0]が「0」かつ要素D[20]が「1」の場合はステップS7に進む。

【0139】

ステップS7にて、プロセッサ23は、チェックサム45に基づいてエラーチェックを行う。具体的には、プロセッサ23は、データビット43に対応する配列Dの要素D[1]〜D[15]に含まれる「0」の数と、要素D[16]〜D[19]であるチェックサム45が示す「0」の数と、を比較して、両者が一致しない場合は、エラーと判断して、ステップS15に進み、それ以外はステップS8に進む。

【0140】

ステップS8では、プロセッサ23は、ダミービット49に基づいてエラーチェックを行う。

【0141】

図13は、図10のステップS8のダミービット49によるエラーチェック処理の流れを示すフローチャートである。図13を参照して、ステップS100にて、プロセッサ23は、変数iに「20」を代入する。ステップS101にて、プロセッサ23は、変数iを1つインクリメントする。

【0142】

ステップS102にて、プロセッサ23は、配列Dの要素D[i]が「1」か否かを判断する。プロセッサ23は、要素D[i]が「1」の場合は、単位ダミービット50が存在すると判断して、ステップS103に進む。ステップS103では、単位ダミービット50の数を計数するカウンタjを1つインクリメントし、ステップS104に進む。一方、プロセッサ23は、要素D[i]が「0」の場合は、ステップS102からステップS104に直接進む。

【0143】

ステップS104にて、プロセッサ23は、変数iがCE−3に等しいか否かを判断し、等しい場合は、ステップS105に進み、それ以外はステップS101に戻る。このようにして、読み込んだバーコード21に含まれる単位ダミービット50の数を計数する。

【0144】

ステップS105にて、プロセッサ23は、図7のテーブルを参照して、カウンタjの値の正当性をチェックする。

【0145】

つまり、プロセッサ23は、ステップS5のデータ解析の結果得られたトレーディングカード17のID(つまり、要素D[1]〜D[8])をインデックスとして、テーブルを参照し、そのIDに関連付けられた単位ダミービット50の数を示す情報を取得する。そして、プロセッサ23は、ステップS5のデータ解析の結果に基づく単位ダミービット50の数を示すカウンタjの値と、テーブルから取得した単位ダミービット50の数の情報と、を比較する。ステップS106にて、プロセッサ23は、両者が不一致の場合は、エラーと判断して、図10のステップS15に進み、両者が一致する場合はスキャンが成功したと判断して、メインルーチンにリターンする。

【0146】

図10に戻って、ステップS9にて、プロセッサ23は、スキャンしたトレーディングカード17が示す選手キャラクタの能力値を設定する。具体的には、プロセッサ23は、スキャンしたトレーディングカード17のID(つまり、要素D[1]〜D[8])をインデックスとして、上記した能力テーブルを参照して、そのIDに関連付けられた能力値を取得し、選手キャラクタの能力値を再設定する。

【0147】

この場合、プロセッサ23は、プレイヤ特定フラグが第1プレイヤを示している場合は、第1プレイヤの選手キャラクタに対して能力値を再設定する。一方、プロセッサ23は、プレイヤ特定フラグが第2プレイヤを示している場合は、第2プレイヤの選手キャラクタに対して能力値を再設定する。プロセッサ23は、選手キャラクタの能力値を再設定した後に、プレイヤ特定フラグの値を異なるプレイヤを示す値にセットする。このようにして、第1プレイヤの選手キャラクタに対する能力設定と第2プレイヤに対する能力設定とが交互に行われる。

【0148】

ステップS10では、プロセッサ23は、バーコード21をスキャンするための再設定を行う。具体的には、プロセッサ23は、図10〜図13の処理で使用される全ての変数及びカウンタを初期化(0を代入)するとともに、全てのフラグをオフ(クリア)にする。ただし、プレイヤ特定フラグの値は維持される。また、プロセッサ23は、使用する全ての配列の全ての要素を「0」に設定する。さらに、プロセッサ23は、ステップS2と同様にエッジトリガをイネーブルにする。ステップS11にて、プロセッサ23は、テレビジョンモニタ3に次のプレイヤのトレーディングカード17のスキャンができる旨の表示をすべく、画像情報(画像データ格納位置情報及び表示位置情報など)をメインメモリ117に設定する。

【0149】

ステップS17にて、プロセッサは、ビデオ同期信号による割り込みが発生した場合はステップS18に進み、それ以外は同じステップS17に進む。ビデオ同期信号による割り込みが発生すると、プロセッサ23は、ステップS18にて、ステップS11,S13,S14又はS16でセットされた画像情報に基づいて、テレビジョンモニタ3の画面(ビデオフレーム)を更新すると共に、ステップS19にて、音声処理を実行し、音楽や効果音を出力する。そして、プロセッサ23は、ステップS3に戻る。

【0150】

ここで、PKモードについて簡単に説明する。このモードでは、プレイヤが自分のトレーディングカード17をゲーム機1Aにスキャンさせる。そして、ゲーム機1Aは、バーコード21のデータビット43の第8〜第14ビットの情報をPK対戦に利用する。データビット43の第8〜第14ビットの情報は、そのトレーディングカード17に対応する選手キャラクタのPKに関する能力値を示している。従って、ゲーム機1Aは、その能力値に基づいて、PKの成功及び失敗を決定する。

【0151】

さて、以上のように、本実施の形態では、絵柄が異なるトレーディングカード17間において各トレーディングカード17を識別するためにバーコード21を利用している。そして、各トレーディングカード17のデータビット43の全長に応じて、適切な長さのダミービット49を付加し、又は、付加しない。このように、ダミービットによって、全種類のバーコード21の全長を揃えている。その結果、各トレーディングカード17に付されたバーコード21間で見た目の統一性を図ることができる。また、肉眼でのバーコード21の内容の認識を困難にすることができる。

【0152】

特に、本実施の形態では、広狭2つの単位データビット35及び36を用いてデータビット43を構成するので、バーコード21間でデータビット43の広狭が発生し、しかも、目立ち易い。それ故、ダミービット49を付加することの上記意義がより大きくなる。最も極端な例は、あるデータビット43が全て単位データビット35からなり、別のデータビット43が全て単位データビット36からなる場合であり、この場合は、双方の全長の差が最も大きい。

【0153】

一般に、トレーディングカードは、それに付された絵柄が重要な要素であり、その絵柄がコレクターの収集意欲を喚起する要因の1つでもある。従って、ダミービット49を付加して、トレーディングカード17間でバーコード21の全長を揃え、見た目を良くする意義は大きい。

【0154】

また、本実施の形態では、単位ダミービット50の幅4wは、単位データビット35の幅2w及び単位データビット36の幅3wと異なる。このため、バーコード21の見た目のバリエーションを増やすことができる。特に、本実施の形態では、広狭2つの単位データビット35及び36を用いてデータビット43を構成するので、もし、単位ダミービット50の幅が、これらのうちのどれかと同じならば、見た目のバリエーションが少なくなる。

【0155】

さらに、本実施の形態では、単位ダミービット50の幅4wは、ストップビット47の幅3wより大きい。このため、ストップビット47の直後の単位ダミービット50の誤認識を極力防止できる。

【0156】

さらに、バーコード21の情報には、データビット43の情報及びダミービット49の情報が含まれるところ、本実施の形態では、広義のデータビット(スタートビット41、データビット43、チェックサム45、及びストップビット47)のビット数(21)の情報が予め設定されている(ステップS100及びS101)。従って、プロセッサ23は、データビット43の情報とダミービット49の情報との境界を容易に認識でき、それ故、配列Dから容易にダミービット49の情報を抽出できる(ステップS102)。

【0157】

さらに、本実施の形態では、チェックサム45に基づくエラーチェック加えて、ダミービット49基づくエラーチェックをも行っている。このように、ダミービット49を装飾目的だけでなく、エラーチェックのためにも利用している。その結果、得られたデータの信頼性が向上する。

【0158】

なお、本発明は、上記の実施の形態に限られるものではなく、その要旨を逸脱しない範囲で、種々の態様において実施することが可能であり、例えば、以下のような変形も可能である。

【0159】

(1)ダミービット49に代えて、図画、文字、数字及び/又は記号をデータビット(広義)に付加することもできる。これによって、より装飾的効果を高めることができる。

【0160】

(2)上記では、2種類の単位データビット35及び36を用いて、データを二進法により表現した。ただし、3種類以上の単位データビット35及び36を用いてデータを表現してもよい。また、単位データビット35及び36は、それぞれ1つのバーと1つのスペースとの組み合わせにより構成したが、これに限定されず、複数のバー及び複数のスペースにより、1つの単位データビットを構成することもできる。つまり、本発明は、バーコードの構造にほとんど依存しない。

【0161】

(3)上記では、バーコード21を光学的に走査して、得られた信号71の立下りエッジを検知して、単位データビット35及び36等の幅を測定し、その幅の長短によって「0」か「1」かを判別した。ただし、そのような解析方法に限らず、立ち上がりエッジを検知してもよいし、双方を検知してもよいし、また、磁気的な走査方法であったり、バーコード21全体を撮像して、得られた映像を処理する方法であってもよい。つまり、本発明は、走査方法にはほとんど依存しない。

【0162】

(4)上記では、単位データビット35及び36等の幅を計測して、0か1かを判定している。従って、同じ種類の単位データビット間で、スペースの幅とバーの幅との合計幅が同じならば、スペース及びバーの幅をそれぞれ任意に設定できる。この点、単位ダミービットについても同様である。

【0163】

(5)上記では、ダミービット49をデータビット(広義)の後に付加した。ただし、ダミービット49をデータビット(広義)の前に付加することもできる。

【0164】

(6)上記では、単位ダミービット50を1種類用意した。ただし、複数種類の単位ダミービットを使用することもできる。

【0165】

(7)上記では、1次元バーコードを例に挙げたが、本発明を2次元バーコードに適用することもできる。

【図面の簡単な説明】

【0166】

【図1】本発明の実施の形態によるゲームシステムの全体構成を示す図である。

【図2】(a)図1のトレーディングカード17の表の面を示す図である。(b)図1のトレーディングカード17の裏の面を示す図である。

【図3】(a)図1のゲーム機1Aの斜視図である。(b)図1のゲーム機1Aの平面図である。(c)図3(b)のA−A線によるゲーム機1Aの断面図である。

【図4】図1のゲーム機1Aの電気的構成を示すブロック図である。

【図5】図4のプロセッサ23の電気的構成を示すブロック図である。

【図6】(a)バーコード21の例示図である。(b)バーコード21の他の例示図である。(c)バーコード21のさらに他の例示図である。

【図7】ダミービット49を利用したエラーチェックの際に使用されるテーブルの例示図である。

【図8】(a)バーコード21のスタートビット41の説明図である。(b)バーコード21のストップビット47の説明図である。(c)バーコード21のダミービット49の説明図である。(d)バーコード21の単位データビット35の説明図である。(e)バーコード21の単位データビット36の説明図である。

【図9】バーコード21の解析方法の基本原理の説明図である。

【図10】図4のプロセッサ23によるスキャンモードでの処理の流れを示すフローチャートである。

【図11】図4のプロセッサ23の割込み処理の流れを示すフローチャートである。

【図12】図10のステップS5のデータ解析処理の流れを示すフローチャートである。

【図13】図10のステップS8のダミービット49によるエラーチェック処理の流れを示すフローチャートである。

【符号の説明】

【0167】

1A,1B…ゲーム機、3…テレビジョンモニタ、5…A/Vケーブル、6…ケーブル、17…トレーディングカード、21…バーコード、23…プロセッサ、25…検知ユニット、41…スタートビット、43…データビット、45…チェックサム、47…ストップビット、49…ダミービット。

【特許請求の範囲】

【請求項1】

各々が割り当てられた同一物品に付される複数の異なるバーコードからなるバーコードセットであって、

前記バーコードの各々は、

実体的な情報を表すデータビットと、

前記実体的な情報を表さないダミービットと、を含み、

前記バーコードの全長が所定長を基準に所定範囲に属するように、前記データビットに前記ダミービットが付加され、

前記データビットは、スペースとバーとの組み合わせからなり、

前記ダミービットは、スペースとダミーバーとの組み合わせからなる、バーコードセット。

【請求項2】

前記データビットは、合計幅が第1の所定幅からなる前記スペース及び前記バーから構成される第1の単位データビット、合計幅が前記第1の所定幅より大きい第2の所定幅からなる前記スペース及び前記バーから構成される第2の単位データビット、又はそれらの組み合わせからなり、

前記第1の単位データビットは、論理0あるいは論理1のいずれかを示し、前記第2の単位データビットは、前記第1の単位データビットが示す論理と逆の論理を示す、請求項1記載のバーコードセット。

【請求項3】

前記ダミービットは、単数又は複数の単位ダミービットからなり、

前記単位ダミービットは、合計幅が第3の所定幅からなる前記スペース及び前記ダミーバーから構成され、

前記第3の所定幅は、前記第1の所定幅及び前記第2の所定幅と異なる、請求項2記載のバーコードセット。

【請求項4】

前記ダミービットに代えて、図画、文字、数字及び/又は記号を前記データビットに付加する、請求項1記載のバーコードセット。

【請求項5】

前記バーコードが付される前記物品は、トレーディングカードである、請求項1から4記載のバーコードセット。

【請求項6】

請求項1から5記載のバーコードセットを構成する前記各バーコードを読み取るバーコード読取装置であって、

前記バーコードをスキャンし、そのバーコードに応じた電気信号を出力するスキャン手段と、

前記バーコードに応じた前記電気信号を解析して、前記バーコードが表す情報を取得する解析手段と、

前記バーコードが表す前記情報から前記ダミービットが表す情報を抽出して、抽出した前記ダミービットが表す前記情報に基づいてエラーチェックを行うエラーチェック手段と、を備えるバーコード読取装置。

【請求項7】

前記バーコードに含まれる前記ダミービットのビット数の情報とそのバーコードの前記データビットが表す前記実体的な情報とを関連付けたテーブルをさらに備え、

前記エラーチェック手段は、スキャンされた前記ダミービットのビット数を計数し、その計数値及びスキャンされた前記データビットの前記実体的な情報と、前記テーブルに格納された前記ダミービットのビット数の前記情報及び前記データビットが表す前記実体的な情報と、に基づいて、エラーの有無を判定する、請求項6記載のバーコード読取装置。

【請求項8】

前記エラーチェック手段は、予め設定された情報に基づいて、前記バーコードが表す前記情報から前記ダミービットが表す前記情報を抽出する、請求項6又は7記載のバーコード読取装置。

【請求項9】

前記予め設定された情報は、前記データビットのビット数の情報である、請求項8記載のバーコード読取装置。

【請求項10】

前記エラーチェック手段は、前記データビットに含まれるチェックサムの情報に基づいてエラーチェックを行う、請求項6から9記載のバーコード読取装置。

【請求項1】

各々が割り当てられた同一物品に付される複数の異なるバーコードからなるバーコードセットであって、

前記バーコードの各々は、

実体的な情報を表すデータビットと、

前記実体的な情報を表さないダミービットと、を含み、

前記バーコードの全長が所定長を基準に所定範囲に属するように、前記データビットに前記ダミービットが付加され、

前記データビットは、スペースとバーとの組み合わせからなり、

前記ダミービットは、スペースとダミーバーとの組み合わせからなる、バーコードセット。

【請求項2】

前記データビットは、合計幅が第1の所定幅からなる前記スペース及び前記バーから構成される第1の単位データビット、合計幅が前記第1の所定幅より大きい第2の所定幅からなる前記スペース及び前記バーから構成される第2の単位データビット、又はそれらの組み合わせからなり、

前記第1の単位データビットは、論理0あるいは論理1のいずれかを示し、前記第2の単位データビットは、前記第1の単位データビットが示す論理と逆の論理を示す、請求項1記載のバーコードセット。

【請求項3】

前記ダミービットは、単数又は複数の単位ダミービットからなり、

前記単位ダミービットは、合計幅が第3の所定幅からなる前記スペース及び前記ダミーバーから構成され、

前記第3の所定幅は、前記第1の所定幅及び前記第2の所定幅と異なる、請求項2記載のバーコードセット。

【請求項4】

前記ダミービットに代えて、図画、文字、数字及び/又は記号を前記データビットに付加する、請求項1記載のバーコードセット。

【請求項5】

前記バーコードが付される前記物品は、トレーディングカードである、請求項1から4記載のバーコードセット。

【請求項6】

請求項1から5記載のバーコードセットを構成する前記各バーコードを読み取るバーコード読取装置であって、

前記バーコードをスキャンし、そのバーコードに応じた電気信号を出力するスキャン手段と、

前記バーコードに応じた前記電気信号を解析して、前記バーコードが表す情報を取得する解析手段と、

前記バーコードが表す前記情報から前記ダミービットが表す情報を抽出して、抽出した前記ダミービットが表す前記情報に基づいてエラーチェックを行うエラーチェック手段と、を備えるバーコード読取装置。

【請求項7】

前記バーコードに含まれる前記ダミービットのビット数の情報とそのバーコードの前記データビットが表す前記実体的な情報とを関連付けたテーブルをさらに備え、

前記エラーチェック手段は、スキャンされた前記ダミービットのビット数を計数し、その計数値及びスキャンされた前記データビットの前記実体的な情報と、前記テーブルに格納された前記ダミービットのビット数の前記情報及び前記データビットが表す前記実体的な情報と、に基づいて、エラーの有無を判定する、請求項6記載のバーコード読取装置。

【請求項8】

前記エラーチェック手段は、予め設定された情報に基づいて、前記バーコードが表す前記情報から前記ダミービットが表す前記情報を抽出する、請求項6又は7記載のバーコード読取装置。

【請求項9】

前記予め設定された情報は、前記データビットのビット数の情報である、請求項8記載のバーコード読取装置。

【請求項10】

前記エラーチェック手段は、前記データビットに含まれるチェックサムの情報に基づいてエラーチェックを行う、請求項6から9記載のバーコード読取装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2007−265033(P2007−265033A)

【公開日】平成19年10月11日(2007.10.11)

【国際特許分類】

【出願番号】特願2006−89315(P2006−89315)

【出願日】平成18年3月28日(2006.3.28)

【出願人】(396025861)新世代株式会社 (138)

【Fターム(参考)】

【公開日】平成19年10月11日(2007.10.11)

【国際特許分類】

【出願日】平成18年3月28日(2006.3.28)

【出願人】(396025861)新世代株式会社 (138)

【Fターム(参考)】

[ Back to top ]