バーコード・スキャナにおける信号調整方法および装置

【課題】バーコードを表すアナログ信号の利得が、制御ループを使用して制御されるバーコード・スキャナ・プラットフォームを提供する。

【解決手段】MTF検出器310が、アナログ信号の低周波数部分(幅広い諸要素、つまり光学焦点が合っていない諸要素)を表す値、およびアナログ信号の高周波数部分(狭い諸要素、つまり光学焦点が合っている諸要素)を表す第2の値を生成する。プロセッサ308は、第1の値および第2の値、ならびに基準振幅を使用して、利得IE信号を算出する。プロセッサ308は、利得信号をAGC回路304に供給し、回路は、整合JFETを使用して、その利得信号に対する線形応答を供給する。雑音フィルタ312が、第1の値、第2の値、および/またはバーコード・スキャナ・プラットフォーム読み取り率に基づいて有効にされる、または無効にされることが可能である。

【解決手段】MTF検出器310が、アナログ信号の低周波数部分(幅広い諸要素、つまり光学焦点が合っていない諸要素)を表す値、およびアナログ信号の高周波数部分(狭い諸要素、つまり光学焦点が合っている諸要素)を表す第2の値を生成する。プロセッサ308は、第1の値および第2の値、ならびに基準振幅を使用して、利得IE信号を算出する。プロセッサ308は、利得信号をAGC回路304に供給し、回路は、整合JFETを使用して、その利得信号に対する線形応答を供給する。雑音フィルタ312が、第1の値、第2の値、および/またはバーコード・スキャナ・プラットフォーム読み取り率に基づいて有効にされる、または無効にされることが可能である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の諸実施形態は、線形自動利得制御(AGC)装置、変調伝達関数検出器および選択可能な雑音フィルタを有するバーコード・スキャナに関し、特に、バーコード・スキャナにおける信号調整に関する。

【背景技術】

【0002】

バーコードは、消費財を識別することを含む多くの用途を有する。商人は、商品にバーコードを付け、例えば、レジでバーコードを走査して、その特定の商品の価格を明らかにする。図1は、バーコード走査プラットフォーム100の高レベルのブロック図である。プラットフォーム100は、光信号105を発するスキャナ104を使用して走査されるバーコード102を含む。変調された光信号107が、バーコード102から反射され、光検出器−入力段106が、変調された光信号107を、バーコード102を表すアナログ信号108に変換する。信号コンディショナ110が、そのアナログ信号108を処理して、バーコード102を表すデジタル信号112を生成する。

【0003】

例示的なバーコード102は、異なるコントラストと異なる幅の一連のバー120と、スペース122を含む。バー120とスペース122の特定の配置と幅が、コードを形成し、そのコードが復号化されて、プラットフォーム100のユーザに意味のある情報を提供する。

【0004】

図示される実施形態では、バー120はスペース122より暗い。バー120は、スペース122より暗いため、バー120は、スペース122よりも吸収率が高く、反射率が低い。その結果、バー120は、アナログ信号108において負のピークを生じさせ、スペースは、アナログ信号108において正のピークを生じさせる。

【0005】

光信号105は、一般に、バーコードを走査する焦点が合わせられた光学「スポット」であり、スポットのサイズは、バーコード102の読み取りに影響を与える。例えば、光学スポット・サイズが、最小のバー120、または最小のスペース122より小さい場合、光信号105は、光学「焦点」の範囲内にあると言われ、アナログ信号108は、バーコード102のかなり良好な表現である。「焦点が合わせられた」信号の1つの特性は、最も狭いバー120Aと最も狭いスペース122Bに関するアナログ信号108における正のピークと負のピークが、より幅広いバー120Cとより幅広いスペース122Cの場合と同一の振幅であることである。

【0006】

走査レーザ104が、光学焦点から引き離されるにつれ(例えば、バーコード102からより遠く、またはバーコード120により近く)、光学スポット・サイズは、より大きくなる。より大きい光学スポットでは、光信号105のエネルギーが、隣接する複数のバー120と複数のスペース122にわたって分散されて、利用できるエネルギーのすべてを吸収する特定の1つのバー120が無いか、または利用できるエネルギーの全てを反射する特定の1つのスペースが無くなる。その結果、最も狭いバー(例えば、120A、120D)と最も狭いスペース(例えば、122B)に関する負のピークと正のピークが、より幅広いバー120Cや幅広いスペース122Cの場合よりも小さい振幅を有する。

【0007】

バーコード走査プラットフォームと焦点ポイントの1つの特性は、ときとして、狭いバーと狭いスペースに関連するアナログ信号108の部分の振幅が、より幅広いバーとより幅広いスペースに関連するアナログ信号108の部分の振幅とは異なる(例えば、より小さい)ことである。これは、光学スポット・サイズが、最も狭いバーと最も狭いスペースより大きい場合によくある。狭いバーと狭いスペースに関連するアナログ信号108の部分の振幅と、幅広いバーと幅広いスペースに関連するアナログ信号108の部分の振幅との比は、「変調伝達関数」またはMTFと呼ばれ、アナログ信号108の特性を記述するのに使用される。例えば、MTFが、100パーセント(100%)より小さい場合、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるのは困難である可能性がある。

【0008】

バーコード走査プラットフォームの別の特性は、光学スポット・サイズが、非常に小さくなるにつれ(例えば、焦点ポイントで)、光信号105のエネルギーが、バーコード102を担持する材料(例えば、紙繊維、木の削り屑、金属ピット、グレインなど)上により集中することである。繊維、グレイン、ピットなど自体が、光信号105のエネルギーを吸収および/または反射することを始め、「ペーパ・ノイズ」と一般に呼ばれるものを生じさせる。ペーパ・ノイズは、アナログ信号108の信号対雑音比(SNR)を低下させる傾向がある。また、その他の雑音も、プラットフォームに導入される可能性がある。アナログ信号108のSNRが低下すると、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるのが困難であろう。

【0009】

バーコード走査プラットフォームのさらに別の特性は、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるために、一定の振幅を保持しなければならないことである。自動利得制御回路が、従来、振幅を一定に保つのに使用されていた。しかし、多くの既知の自動利得制御技術は複雑な制御式や高価格の回路を要求する。

【発明の概要】

【0010】

本発明は、バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅と等しいほぼ等しいと判定し、雑音フィルタがOFFであると判定し、読み取り率が所定の値未満であると判定し、前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにする論理を有することを特徴とする。

【0011】

また、本発明は、バーコードを表すアナログ信ナログ信号の第1の周波数部分の振幅を表す第1の値を生成するステップと、アナログ信号の第2の周波数部分の振幅を表す第2の値を生成するステップとから構成されることを特徴とする。

【0012】

また、本発明は、バーコードを表すアナログ信号の第1の周波数部分を表す第1の値と、アナログ信号の第2の周波数部分を表す第2の値とを生成する変調伝達関数検出器と、アナログ信号に対する第1の値、第2の値、および/または所定の振幅に基づいて利得信号を算出し、利得信号を利得制御回路に印加し、利得制御回路が、利得信号に対する線形応答である利得をアナログ信号に与えるプロセッサとから構成されることを特徴とする。

【図面の簡単な説明】

【0013】

【図1】バーコード走査プラットフォームの高レベルのブロック図である。

【図2】本発明の実施形態による、バーコードを表すアナログ信号、およびバーコードに対するそれらの信号の関係を示すグラフである。

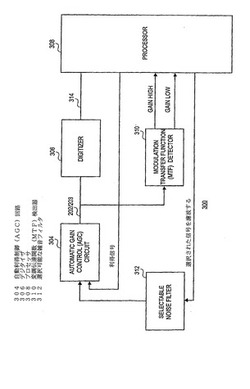

【図3】本発明の実施形態による信号コンディショナの高レベルのブロック図である。

【図4】本発明の実施形態による、図3に示された信号コンディショナを実施するアプローチを示す流れ図である。

【図5】本発明の実施形態による選択可能な雑音フィルタ、および自動利得制御回路の概略図である。

【図6】本発明の実施形態による、図3に示されたMTF検出器の概略図である。

【図7】本発明の実施形態による図3に示された選択可能な雑音フィルタを実施するアプローチを示す流れ図である。

【発明を実施するための形態】

【0014】

図面では、同様の符号が、一般に、同一の要素、機能的に類似した要素、および/または構造的に均等の要素を示す。要素が最初に出現する図面は、符号の左端の数字によって示される。

【0015】

図2は、本発明の実施形態による、バーコード102を表すアナログ信号202、203とそのアナログ信号202、203に関する基準振幅204(例えば、ピーク、ピーク幅)に関連して、バーコード102に対する信号202、203の関係を表すグラフである。図示される実施形態では、アナログ信号202は、負のピーク群220(例えば、220A、220B、220C、220D)と正のピーク群222(例えば、222A、222B、222C)とを含む、変調された信号である。負のピーク群220は、バー120を表し、正のピーク群222は、スペース122を表す。アナログ信号203は、負のピーク群230(例えば、230A、230B、230C、230D)と正のピーク群232(例えば、232A、232B、232C)とを含む、変調された信号である。負のピーク群230は、バー120を表し、正のピーク群232は、スペース122を表す。図示される実施形態では、アナログ信号203は、およそ100パーセント(100%)の変調伝達関数を有し、アナログ信号202は、100パーセント(100%)より低い変調伝達関数を有する。

【0016】

バー120Aは、バー120D(例えば、1×要素幅)と同一の幅であり、バー120B(例えば、2×要素幅)より狭い。バー120D、120Bは、バー120C(3×要素幅)より狭い。スペース122B(例えば、1×要素幅)は、スペース122A(例えば、3×要素幅)とスペース122C(例えば、やはり3×要素幅)より狭い。

【0017】

例示的なアナログ信号203では、ピーク群230とピーク群232のすべてが、基準振幅204とほぼ等しい振幅を有する。ピーク群230とピーク232群のすべては、ほぼ同一の振幅を有する(例えば、変調伝達関数が、100パーセント(100%)にほぼ等しいために)。ピーク群230とピーク群232の一部のピークは、異なる要素サイズ(例えば、1×、2×、3×)からもたらされる、互いに異なる周期(例えば、基本周波数)を有する。

【0018】

図示される実施形態では、アナログ信号203において、ピーク230A、230D、232Bの周期は、ピーク230B、230C、232A、232Cの周期より短い。ピーク230A、230B、230D、232Bの周期はすべて、ピーク230C、232A、232Cの周期より短い。例示的なアナログ信号203は、100パーセント(100%)にほぼ等しい変調伝達関数を有し、したがって、バーコード102要素120、122のサイズの違いに関わらず、さらに、そのため、関連するピークの周期の違いに関わらず、正のピーク群232と負のピーク群230は、ほぼ等しい振幅を有する。

【0019】

例示的なアナログ信号202では、ピーク群220とピーク群222の一部のピークは、基準振幅204とは異なる振幅を有する。ピーク群220とピーク群222の一部のピークは、互いに異なる振幅を有する(例えば、変調伝達関数が、光学スポット焦点および/または電子帯域幅に起因して、100パーセント未満(<100%)であるために)。ピーク群220とピーク群222の一部のピークは、異なる要素サイズ(例えば、1×、2×、3×)からもたらされる、互いに異なる周期(例えば、基準周波数)を有する。

【0020】

例示的なアナログ信号202では、ピーク220A、220D、222Bの周期は、ピーク220Bの周期より短い。ピーク220A、220B、220D、222Bの周期は、ピーク220C、222A、222Cの周期より短い。

【0021】

図3は、本発明の実施形態による信号コンディショナ300の高レベルのブロック図であり、コンディショナ300は、ピーク群230とピーク群232、およびピーク群220とピーク群222の一部のピーク、またはすべてのピークを増幅する、または減衰させる制御ループである。また、信号コンディショナ300は、アナログ信号202/203から雑音を選択的に濾波して除くこともできる。

【0022】

図示される実施形態における信号コンディショナ300は、デジタイザ306に出力が結合された自動利得制御回路(AGC)回路304を含む。デジタイザ306の出力は、プロセッサ308に結合される。変調伝達関数(MTF)検出器310が、アナログ信号202/203の一部分をタップするように結合される。選択可能な雑音フィルタ312が、AGC回路304の入力とプロセッサ308に結合される。

【0023】

AGC回路304は、入力に線形応答を与えることができ、したがって、アナログ信号202/203を増幅する、または減衰させる。本発明の諸実施形態によるAGC回路304の実施は、図4および図5に関連して以下により詳細に説明する。

【0024】

デジタイザ306が、アナログ信号202/203を受信し、その信号202/203を、バーコード102を表すデジタル信号314(例えば、方形波)に変換する。一実施形態では、デジタイザ306の性能は、アナログ信号202/203が、基準振幅204の範囲内にある場合に、最適である。デジタイザ306を実施するのに適した回路は、知られている。

【0025】

MTF検出器310が、アナログ信号202/203の少なくとも1つの低周波数部分のピーク振幅と、アナログ信号202/203の少なくとも1つの高周波数部分のピーク振幅を検出する。MTF検出器310は、Gain Low信号を生成し、この信号は、一実施形態では、アナログ信号202/203における低周波数ピークを表す直流(DC)レベルである。また、MTF検出器は、Gain High信号も生成し、この信号は、一実施形態では、アナログ信号202/203における高周波数ピークを表すDCレベルである。もちろん、Gain Low信号とGain High信号は、アナログ信号202/203における低周波数ピークと高周波数ピークをそれぞれ表す任意の適切な信号でよい。本発明の諸実施形態によるMTF検出器310の実施は、図6に関連して以下により詳細に説明する。

【0026】

選択可能な雑音フィルタ312が、AGC回路304の入力に結合されて、アナログ信号202/203の雑音を減衰させ、かつ/または信号対雑音比(SNR)を向上させることが可能である。本発明の諸実施形態による選択可能な雑音フィルタ312の実施は、図5と図7に関連して以下により詳細に説明する。

【0027】

本発明の諸実施形態では、プロセッサ308は、デジタル信号314を復号化することができ、Gain High信号とGain Low信号を測定して、デジタル値に変換し、デジタル値を測定し、デジタル値を基準振幅204と比較し、アナログ信号202/203が増幅されるべきか、または減衰させられるべきか、またはそのままであるべきかを判定する。本明細書の説明を読んだ後、本発明の諸実施形態によるプロセッサ308をどのように実施するかは、当業者には明白となろう。

【0028】

図4は、本発明の実施形態による信号コンディショナ300によって実施されるプロセス400を示す流れ図である。プロセス400のオペレーションは、本発明の諸実施形態を理解するのに最も役立つ形で順に実行される複数の別々のブロックとして説明される。しかし、それらのオペレーションが説明される順序は、それらのオペレーションが、必然的に順序依存であること、またはオペレーションが、ブロックが提示される順序で実施されるべきことを意味するものと解釈されてはならない。

【0029】

もちろん、プロセス400は、単に例示的なプロセスであり、他のプロセスを使用して、本発明の諸実施形態を実施してもよい。マシン可読命令を担持するマシンアクセス可能な媒体を使用して、マシン(例えば、プロセッサ)がプロセス400を実行するようにさせてもよい。

【0030】

ブロック402で、AGC回路304が、光検出器と入力段106からアナログ信号202/203を受け取り、そのアナログ信号202/203に、基準振幅204に基づいて利得または減衰を与える。一実施形態では、プロセッサ308は、基準振幅204を表す利得信号をAGC回路304に供給し、回路304は、その利得信号を、アナログ信号202/203を増幅するため、または減衰させるための基準として使用する。

【0031】

ブロック404で、MTF検出器310が、アナログ信号202/203の一部分をタップし、アナログ信号202/203の少なくとも1つの低周波数部分のピーク振幅を検出し、アナログ信号202/203の少なくとも1つの高周波数部分のピーク振幅を検出する。

【0032】

ブロック406で、プロセッサ308が、基準振幅204、Gain High信号とGain Low信号に関連するアルゴリズムに基づいて新たな利得信号を選択し、その新たな利得信号をAGC回路304に加える。一実施形態では、プロセッサ308は、Gain High信号が、Gain Low信号および基準振幅204と比べて不釣合いに小さいと判定する。その実施形態では、新たな利得信号によって、アナログ信号202/203を増幅することを行うよう、AGC回路304に通知する。その際、そのような増幅により、Gain Low信号が、基準振幅204を超えるようになるかどうかに関わらない。

【0033】

代替の実施形態では、Gain Low信号は、Gain High信号とほぼ等しいが、アナログ信号202/203は、基準振幅204未満である。その実施形態では、新たな利得信号は、アナログ信号202/203を増幅して、その信号202/203を基準振幅204の範囲内にするよう、AGC回路304に知らせる。もちろん、他の振幅スキームや減衰スキームも可能であり、本明細書の説明を読んだ後、Gain High値、Gain Low値、基準振幅204値の様々な組合せのために、本発明の諸実施形態をどのように実施するかは、当業者には直ちに認識されよう。

【0034】

ブロック408で、AGC回路304が、アナログ信号202/203を増幅する、または減衰させるための基準として新たな利得信号を使用する。

【0035】

図5は、本発明の実施形態によるAGC回路304の概略図である。図示される実施形態では、AGC回路304は、キャパシタC4(0.1μF)、C10(0.1μF)、C15(39pF)、C17(0.1μF)、C21(12pF)、C22(30μF)、C24(580pF)、C30(100pF)、演算増幅器U3A(非反転)、演算増幅器U4(反転)、トランジスタQ4(補償接合電界効果トランジスタ(JFET))、トランジスタQ7(電圧制御抵抗器の役割をする利得JFET)、抵抗器R4(24Ω)、R8(5.1Ω)、R19(24Ω)、R21(10KΩ)、R24(24Ω)、R26(10KΩ)、R28(4.7KΩ)、R32(20KΩ)、R35(100KΩ)、R39(100KΩ)、R41(100KΩ)、R43(100KΩ)、R46(8.2KΩ)、R47(10KΩ)を含む。

【0036】

C21は、雑音をロールオフし、増幅器U3Aに信号安定性を与える高周波数補償フィルタを構成する。C22、R24は、U4とFET Q7に関するバイアス電圧が、相互に作用して、アナログ信号202/203に関する不適切なDC出力オフセットと非対称性をもたらすのを低減させる低周波数DCブロッキング・フィルタを構成する。R19とC10およびR4とC4は、U3Aのための電源(例えば、5ボルト)フィルタである。R26とJFET Q7の等価抵抗により、U3Aの利得が決まる。JFET Q4とQ7は、整合トランジスタである。R41、R43、C24は、メイン利得JFET Q7のためのバイアス素子である。R35、R39、C17は、調整JFET Q4のための同様のバイアス素子である。R21、R28は、Q7によって見られる、Q4に対する同様のインピーダンスを提供する。U4は、Q7、Q4のゲートを駆動し、プロセッサ308からのアナログ信号で制御される。R47、R46、C30は、所望される正確なJFETゲート制御のための利得調整を可能にする。

【0037】

プロセッサ308からの利得信号はU4を制御する。U4は、利得信号をバッファリングして、JFET Q7とJFET Q4を駆動する。JFET Q4は、U4の正のフィードバック・パスにある。プロセッサ308からの利得信号に基づき、U4は、JFET Q7にゲート電圧を出力し、JFET Q7は、JFET Q7の特性曲線に従って応答して、等価抵抗をもたらす。U4は、JFET Q4にもゲート電圧を出力し、JFET Q4も、JFET Q4の特性曲線に従って応答して、調整応答をU4に戻す。

【0038】

JFET Q4は、JFET Q7と同様のインピーダンスによって駆動され、負荷がかけられており、JFET Q4は、U4の調整フィードバック・パスにあるため、AGC回路304からの出力は、非常に広いダイナミック・レンジにわたって線形であることが可能である(これにより、非常に幅広い範囲の読み取り距離、例えば、バーコード102に近い読み取り距離と、バーコード102から遠く離れた読み取り距離とすることができる)。実施するのに、複雑な制御式を要求し、しばしば、予測利得調整を制限する既知の他の回路とは異なり、本発明の諸実施形態に従って実施されるAGC回路304は、安価な整合JFETを使用して、利得信号入力に対する応答を線形化する。その結果、プロセッサ308からの利得信号に対するAGC回路304の応答は、予測され、決定論的である。

【0039】

AGC回路304が、アナログ信号202/203を減衰させることが可能な代替の実施形態では、AGC回路304は、R8のすぐ後に結合されたJFET Q7を含む。その実施形態では、JFET Q7ドレインが、アースに結合され、U3Aのプラス入力に分圧電圧を供給する、R8とJFET Q7の等価抵抗の間における電圧分圧器を形成する。

【0040】

本発明のさらに別の実施形態では、AGC回路304は、1つだけのJFET Q7を含み、この実施形態では、回路304の非線形応答(例えば、応答曲線)がプロセッサ308によってマップされる。マップされた値は、格納され(例えば、ルックアップ・テーブルの中に)、プロセッサ308は、マップされた値を使用して、同一の予測利得調整を生成する。

【0041】

本発明の諸実施形態は、JFETであるQ4とQ7に関連して説明されているが、本発明の諸実施形態は、そのように限定されない。例えば、Q4および/またはQ7は、バイポーラ接合トランジスタ(BJT)、MOSFET、真空管、ガリウム・ヒ素(GaAs)FET、ヘテロ接合バイポーラ接合トランジスタ(HBJT)などを含むが、以上には限定されない、任意の適切な利得素子であることが可能である。本明細書の説明を読んだ後、本発明の他の様々な実施形態におけるQ4とQ7をどのように実施するかは、当業者には明白となろう。

【0042】

図4を再び参照する。ブロック404において、MTF検出器310が、アナログ信号202/203の一部分をタップし、アナログ信号202/203の少なくとも1つの周波数部分(例えば、低周波数)のピーク振幅を検出し、アナログ信号202/203の少なくとも1つの他の周波数部分(例えば、高周波数)のピーク振幅を検出することを思い起こされたい。図6は、本発明の実施形態によるMTF検出器310の概略図である。図示される実施形態では、MTF検出器310は、2つの周波数検出回路602、604を含む。一実施形態では、周波数検出回路602は、およそ2、3百キロヘルツから、およそ5、6百キロヘルツまでのレンジにおけるアナログ信号202/203内の高い方の周波数を検出する。別の実施形態では、周波数検出回路604は、およそ数十キロヘルツから、およそ2、3百キロヘルツまでのレンジにおけるアナログ信号202/203内の低い方の周波数を検出する。

【0043】

もちろん、本発明の諸実施形態は、バーコードを表すアナログ信号内の2つだけの、または以上の特定の2つだけの周波数範囲を検出することに限定されない。例えば、いくつかの異なる周波数範囲が検出され、プロセッサ308に供給されてもよい(例えば、1つの周波数範囲が、別の周波数範囲内にあってもよい)。本明細書の説明を読んだ後、さらなる他の周波数範囲に関して本発明の諸実施形態をどのように実施するかは、当業者には直ちに認識されよう。

【0044】

図示される実施形態では、周波数検出回路604は、キャパシタC37(580pF)、C38(0.1μF)、C39(200pF)、C41(8.2pF)、ダイオードD4、D5、D6、増幅器U7A、トランジスタQ8A、抵抗器R51(10KΩ)、R52(100KΩ)、R53(120KΩ)、R54(330Ω)、R55(1KΩ)、R56(10KΩ)、R57(1KΩ)を含む。タップされたアナログ信号202/203は、C37とD5を介して周波数検出回路604に入る。C37、D5は、アナログ信号202/203をアースに整流する。C37、R51、R55は、周波数検出回路604のための信号負荷分離とローエンド・カットオフ周波数を提供する。U7Aは、アナログ信号202/203を増幅する。U7A、D4、D6の組合せは、周波数検出回路604の帯域幅の範囲内に入る、アナログ信号202/203におけるピーク振幅を検出する。

【0045】

C39とR53は、ホールド時定数を与え、周波数検出回路604の帯域幅の範囲内にあるアナログ信号202/203の諸部分のピーク値に基づく電荷を生じさせる。C39の電荷は、プロセッサ308に送られるGain Low信号である。プロセッサ308は、R54を介してQ8Aのベース上に信号を供給して、C39上の電荷をクリアし、これにより、新たな利得信号が、AGC回路304に送られた後、Gain Low信号をリセットする。

【0046】

図示される実施形態では、周波数検出回路602は、キャパシタC43(68pF)、C45(0.015μF)、C46(200pF)、C47(8.2pF)、ダイオードD7、D8、D9、増幅器U7B、トランジスタQ8B、抵抗器R58(10KΩ)、R59(100Ω)、R60(1KΩ)、R61(200KΩ)、R62(330Ω)、R63(10KΩ)、R64(510Ω)を含む。タップされたアナログ信号202/203は、C43とD7を介して周波数検出回路602に入る。C43とD7は、アナログ信号202/203をアースに整流する。C43、R58、R60は、周波数検出回路602のための信号負荷分離とローエンド・カットオフ周波数を提供する。U7Aは、アナログ信号202/203を増幅する。C45とR59は、周波数検出回路602のためのさらなるローエンド・カットオフ周波数を提供する。U7B、D8、D9の組合せは、周波数検出器回路602の帯域幅の範囲内に入る、アナログ信号202/203におけるピーク振幅を検出する。

【0047】

C46とR61は、ホールド時定数を与え、周波数検出回路602の帯域幅の範囲内にあるアナログ信号202/203の諸部分のピーク値に基づく電荷を生じさせる。C46の電荷は、プロセッサ308に送られるGain High信号である。プロセッサ308は、R62を介してQ8Bのベース上に信号を供給して、C46上の電荷をクリアし、これにより、新たな利得信号が、AGC回路304に送られた後、Gain High信号をリセットする。

【0048】

図7は、本発明の実施形態による選択可能な雑音フィルタ312を実施するためのプロセス700を示す流れ図である。プロセス700のオペレーションは、本発明の諸実施形態を理解するのに最も役立つ形で順に実行される複数の別々のブロックとして説明される。しかし、それらのオペレーションが説明される順序は、それらのオペレーションが、必然的に順序依存であること、またはオペレーションが、ブロックが提示される順序で実施されるべきことを意味するものと解釈されてはならない。

【0049】

もちろん、プロセス700は、単に例示的なプロセスであり、他のプロセスを使用して、本発明の諸実施形態を実施してもよい。マシン可読命令を担持するマシンアクセス可能な媒体を使用して、マシン(例えば、プロセッサ)がプロセス700を実行するようにしてもよい。一実施形態では、ユーザは、プロセス700を手動で実施することができる。

【0050】

ブロック702で、プロセッサ308が、Gain Low信号がGain High信号とほぼ等しいと判定する。

【0051】

ブロック704で、プロセッサ308は、新たな利得信号をAGC回路304に印加し、この利得信号は、基準振幅204の範囲内にアナログ信号202/203を(持って行くように)増幅する/減衰させる/保持するよう、AGC回路304に通知する。

【0052】

ブロック706で、プロセッサ308は、選択可能な雑音フィルタ312が、ONであるか、またはOFFであるかを判定する。

【0053】

選択可能な雑音フィルタ312がOFFである場合、ブロック708で、プロセッサ308は、プラットフォーム100に関する読み取り率が、所定の値未満(例えば、およそ100パーセント未満(<100%))であるかどうかを判定する。本明細書で使用される読み取り率は、試行された読み取りの回数当たりの、アナログ信号202/203の復号化の成功の回数として定義される(例えば、10回の試行された読み取りのうち10回の復号化の成功は、100パーセントの読み取り率である)。読み取り率が、所定の値未満である場合、プロセッサ308は、選択可能な雑音フィルタ312をONにする。

【0054】

ブロック712で、プロセッサ308は、読み取り率が増加したか、または低下したかを判定する。読み取り率が低下した場合、ブロック714で、プロセッサ308は、選択可能な雑音フィルタ312をOFFにする。読み取り率が増加した場合、ブロック716で、プロセッサ308は、選択可能な雑音フィルタ312をONのままとする。

【0055】

ブロック706で、選択可能な雑音フィルタ312がONであるとプロセッサ308が判定した場合、プロセス700は、ブロック712に進んで、読み取り率が増加しているか、または低下しているかを判定する。

【0056】

ブロック708で、読み取り率が所定の値未満ではないとプロセッサ308が判定した場合、プロセスは、ブロック714に進み、プロセッサ308は、選択可能な雑音フィルタ312をOFFのままにする。

【0057】

図5を再び参照すると、選択可能な雑音フィルタ312の概略図が示されている。図示される実施形態では、雑音フィルタ312は、抵抗器R32、R42(1KΩ)、キャパシタC15、金属酸化物半導体電界効果トランジスタ(MOSFET)Q5を含む。R32、R42、C15、MOSFET Q5は、既存の抵抗器R8と組み合わさって機能して、雑音フィルタ312を形成し、フィルタ312は、アナログ信号202/203内の選択されたレンジの周波数が通過することを許す一方で、望ましくないペーパ周波数と雑音周波数が通過するのを阻止する。

【0058】

図示される実施形態では、MOSFET Q5は、信号コンディショナ300内の回路から雑音フィルタ312を選択する、または選択解除するようにプロセッサ308によって制御されるスイッチである。R42は、プルダウン・レジスタである。R8、C15、およびR32により、フィルタの周波数ポイントおよび減衰率が決まる。プロセッサ308からの信号が、MOSFET Q5をONにするのに十分である場合、選択可能な雑音フィルタ312は、フィルタ312の帯域内の雑音を濾波して除く。一実施形態では、選択可能な雑音フィルタ312は、アナログ信号202/203上の雑音240を濾波して除く。

【0059】

代替の実施形態では、Q5は、信号コンディショナ300内の回路から雑音フィルタ312を選択する、または選択解除するようにプロセッサ308によって制御されるJFETスイッチである。その実施形態では、Q5は、雑音フィルタ312の極によって定義されるレンジの周波数にわたる、あるレンジの減衰レベルを提供することができる。

【0060】

本発明の諸実施形態は、特定の周波数と特定の帯域幅を使用して説明されてきたが、本明細書の説明を読んだ後には、異なるフィルタ・カットオフ・ポイントを使用して、本発明の諸実施形態をどのように実施するかが明白となろう。さらに、特定のフィルタ・プロファイルは、能動増幅フィルタ、受動フィルタ、および/またはデジタル処理フィルタなどの、他の技術を使用して実現することができる。

【0061】

本発明の諸実施形態は、ハードウェア、ソフトウェア、またはハードウェアとソフトウェアの組合せを使用して実施されることが可能である。ソフトウェアを使用する実装では、ソフトウェアは、マシンアクセス可能な媒体に格納されてもよい。

【0062】

マシンアクセス可能な媒体には、マシン(例えば、コンピュータ、ネットワーク・デバイス、パーソナル・デジタル・アシスタント、製造ツール、1つまたは複数のプロセッサのセットを有する任意のデバイス、その他)がアクセスすることが可能な形態で情報を提供する(すなわち、格納し、かつ/または伝送する)任意の機構が含まれる。例えば、マシンアクセス可能な媒体には、書き込み可能な媒体と書き込み可能でない媒体(例えば、読取り専用メモリ(ROM)、ランダム・アクセス・メモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ・デバイス、その他)ならびに電気形態、光形態、音響形態、またはその他の形態の伝搬される信号(例えば、搬送波、赤外線信号、デジタル信号、その他)が含まれる。

【0063】

以上の説明では、特定のプロセス、材料、およびデバイスなどの、多数の特定の詳細が、本発明の諸実施形態の徹底的な理解をもたらすように提示された。しかし、本発明の諸実施形態は、それらの特定の詳細の1つまたは複数を伴わずに、または他の方法、コンポーネント、その他を使用して実施されることも可能であることが、当業者には認識されよう。その他、周知の構造、または周知のオペレーションは、以上の説明の理解を不明瞭にするのを回避するため、詳細に図示すること、または説明することはしていない。

【0064】

本明細書全体における「一実施形態」または「実施形態」への言及は、ある実施形態に関連して説明される特定の特徴、構造、プロセス、ブロック、または特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。このため、本明細書全体の様々な箇所における「一実施形態では」または「ある実施形態では」という句の出現は、それらの句がすべて同一の実施形態を指すことを必ずしも意味しない。特定の特徴、構造、または特性は、1つまたは複数の実施形態において任意の適切な形で組み合わせられることが可能である。

【0065】

添付の特許請求の範囲において使用される用語は、本発明の諸実施形態を、明細書および特許請求の範囲において開示される特定の諸実施形態に限定するものと解釈されてはならない。むしろ、本発明の諸実施形態の範囲は、特許請求の範囲の解釈の確立されている諸原則に準じて解釈されるべき、添付の特許請求の範囲によって完全に確定されるべきである。

【符号の説明】

【0066】

102…バーコード、104…走査レーザ、106…光検出器−入力段、110…信号コンディショナ、304…自動利得制御(AGC)回路、306…デジタイザ、308…プロセッサ、310…変調伝達関数(MTF)検出器、312…選択可能な雑音フィルタ。

【技術分野】

【0001】

本発明の諸実施形態は、線形自動利得制御(AGC)装置、変調伝達関数検出器および選択可能な雑音フィルタを有するバーコード・スキャナに関し、特に、バーコード・スキャナにおける信号調整に関する。

【背景技術】

【0002】

バーコードは、消費財を識別することを含む多くの用途を有する。商人は、商品にバーコードを付け、例えば、レジでバーコードを走査して、その特定の商品の価格を明らかにする。図1は、バーコード走査プラットフォーム100の高レベルのブロック図である。プラットフォーム100は、光信号105を発するスキャナ104を使用して走査されるバーコード102を含む。変調された光信号107が、バーコード102から反射され、光検出器−入力段106が、変調された光信号107を、バーコード102を表すアナログ信号108に変換する。信号コンディショナ110が、そのアナログ信号108を処理して、バーコード102を表すデジタル信号112を生成する。

【0003】

例示的なバーコード102は、異なるコントラストと異なる幅の一連のバー120と、スペース122を含む。バー120とスペース122の特定の配置と幅が、コードを形成し、そのコードが復号化されて、プラットフォーム100のユーザに意味のある情報を提供する。

【0004】

図示される実施形態では、バー120はスペース122より暗い。バー120は、スペース122より暗いため、バー120は、スペース122よりも吸収率が高く、反射率が低い。その結果、バー120は、アナログ信号108において負のピークを生じさせ、スペースは、アナログ信号108において正のピークを生じさせる。

【0005】

光信号105は、一般に、バーコードを走査する焦点が合わせられた光学「スポット」であり、スポットのサイズは、バーコード102の読み取りに影響を与える。例えば、光学スポット・サイズが、最小のバー120、または最小のスペース122より小さい場合、光信号105は、光学「焦点」の範囲内にあると言われ、アナログ信号108は、バーコード102のかなり良好な表現である。「焦点が合わせられた」信号の1つの特性は、最も狭いバー120Aと最も狭いスペース122Bに関するアナログ信号108における正のピークと負のピークが、より幅広いバー120Cとより幅広いスペース122Cの場合と同一の振幅であることである。

【0006】

走査レーザ104が、光学焦点から引き離されるにつれ(例えば、バーコード102からより遠く、またはバーコード120により近く)、光学スポット・サイズは、より大きくなる。より大きい光学スポットでは、光信号105のエネルギーが、隣接する複数のバー120と複数のスペース122にわたって分散されて、利用できるエネルギーのすべてを吸収する特定の1つのバー120が無いか、または利用できるエネルギーの全てを反射する特定の1つのスペースが無くなる。その結果、最も狭いバー(例えば、120A、120D)と最も狭いスペース(例えば、122B)に関する負のピークと正のピークが、より幅広いバー120Cや幅広いスペース122Cの場合よりも小さい振幅を有する。

【0007】

バーコード走査プラットフォームと焦点ポイントの1つの特性は、ときとして、狭いバーと狭いスペースに関連するアナログ信号108の部分の振幅が、より幅広いバーとより幅広いスペースに関連するアナログ信号108の部分の振幅とは異なる(例えば、より小さい)ことである。これは、光学スポット・サイズが、最も狭いバーと最も狭いスペースより大きい場合によくある。狭いバーと狭いスペースに関連するアナログ信号108の部分の振幅と、幅広いバーと幅広いスペースに関連するアナログ信号108の部分の振幅との比は、「変調伝達関数」またはMTFと呼ばれ、アナログ信号108の特性を記述するのに使用される。例えば、MTFが、100パーセント(100%)より小さい場合、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるのは困難である可能性がある。

【0008】

バーコード走査プラットフォームの別の特性は、光学スポット・サイズが、非常に小さくなるにつれ(例えば、焦点ポイントで)、光信号105のエネルギーが、バーコード102を担持する材料(例えば、紙繊維、木の削り屑、金属ピット、グレインなど)上により集中することである。繊維、グレイン、ピットなど自体が、光信号105のエネルギーを吸収および/または反射することを始め、「ペーパ・ノイズ」と一般に呼ばれるものを生じさせる。ペーパ・ノイズは、アナログ信号108の信号対雑音比(SNR)を低下させる傾向がある。また、その他の雑音も、プラットフォームに導入される可能性がある。アナログ信号108のSNRが低下すると、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるのが困難であろう。

【0009】

バーコード走査プラットフォームのさらに別の特性は、アナログ信号108が、バーコード102を表すデジタル信号に正確に分解されるために、一定の振幅を保持しなければならないことである。自動利得制御回路が、従来、振幅を一定に保つのに使用されていた。しかし、多くの既知の自動利得制御技術は複雑な制御式や高価格の回路を要求する。

【発明の概要】

【0010】

本発明は、バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅と等しいほぼ等しいと判定し、雑音フィルタがOFFであると判定し、読み取り率が所定の値未満であると判定し、前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにする論理を有することを特徴とする。

【0011】

また、本発明は、バーコードを表すアナログ信ナログ信号の第1の周波数部分の振幅を表す第1の値を生成するステップと、アナログ信号の第2の周波数部分の振幅を表す第2の値を生成するステップとから構成されることを特徴とする。

【0012】

また、本発明は、バーコードを表すアナログ信号の第1の周波数部分を表す第1の値と、アナログ信号の第2の周波数部分を表す第2の値とを生成する変調伝達関数検出器と、アナログ信号に対する第1の値、第2の値、および/または所定の振幅に基づいて利得信号を算出し、利得信号を利得制御回路に印加し、利得制御回路が、利得信号に対する線形応答である利得をアナログ信号に与えるプロセッサとから構成されることを特徴とする。

【図面の簡単な説明】

【0013】

【図1】バーコード走査プラットフォームの高レベルのブロック図である。

【図2】本発明の実施形態による、バーコードを表すアナログ信号、およびバーコードに対するそれらの信号の関係を示すグラフである。

【図3】本発明の実施形態による信号コンディショナの高レベルのブロック図である。

【図4】本発明の実施形態による、図3に示された信号コンディショナを実施するアプローチを示す流れ図である。

【図5】本発明の実施形態による選択可能な雑音フィルタ、および自動利得制御回路の概略図である。

【図6】本発明の実施形態による、図3に示されたMTF検出器の概略図である。

【図7】本発明の実施形態による図3に示された選択可能な雑音フィルタを実施するアプローチを示す流れ図である。

【発明を実施するための形態】

【0014】

図面では、同様の符号が、一般に、同一の要素、機能的に類似した要素、および/または構造的に均等の要素を示す。要素が最初に出現する図面は、符号の左端の数字によって示される。

【0015】

図2は、本発明の実施形態による、バーコード102を表すアナログ信号202、203とそのアナログ信号202、203に関する基準振幅204(例えば、ピーク、ピーク幅)に関連して、バーコード102に対する信号202、203の関係を表すグラフである。図示される実施形態では、アナログ信号202は、負のピーク群220(例えば、220A、220B、220C、220D)と正のピーク群222(例えば、222A、222B、222C)とを含む、変調された信号である。負のピーク群220は、バー120を表し、正のピーク群222は、スペース122を表す。アナログ信号203は、負のピーク群230(例えば、230A、230B、230C、230D)と正のピーク群232(例えば、232A、232B、232C)とを含む、変調された信号である。負のピーク群230は、バー120を表し、正のピーク群232は、スペース122を表す。図示される実施形態では、アナログ信号203は、およそ100パーセント(100%)の変調伝達関数を有し、アナログ信号202は、100パーセント(100%)より低い変調伝達関数を有する。

【0016】

バー120Aは、バー120D(例えば、1×要素幅)と同一の幅であり、バー120B(例えば、2×要素幅)より狭い。バー120D、120Bは、バー120C(3×要素幅)より狭い。スペース122B(例えば、1×要素幅)は、スペース122A(例えば、3×要素幅)とスペース122C(例えば、やはり3×要素幅)より狭い。

【0017】

例示的なアナログ信号203では、ピーク群230とピーク群232のすべてが、基準振幅204とほぼ等しい振幅を有する。ピーク群230とピーク232群のすべては、ほぼ同一の振幅を有する(例えば、変調伝達関数が、100パーセント(100%)にほぼ等しいために)。ピーク群230とピーク群232の一部のピークは、異なる要素サイズ(例えば、1×、2×、3×)からもたらされる、互いに異なる周期(例えば、基本周波数)を有する。

【0018】

図示される実施形態では、アナログ信号203において、ピーク230A、230D、232Bの周期は、ピーク230B、230C、232A、232Cの周期より短い。ピーク230A、230B、230D、232Bの周期はすべて、ピーク230C、232A、232Cの周期より短い。例示的なアナログ信号203は、100パーセント(100%)にほぼ等しい変調伝達関数を有し、したがって、バーコード102要素120、122のサイズの違いに関わらず、さらに、そのため、関連するピークの周期の違いに関わらず、正のピーク群232と負のピーク群230は、ほぼ等しい振幅を有する。

【0019】

例示的なアナログ信号202では、ピーク群220とピーク群222の一部のピークは、基準振幅204とは異なる振幅を有する。ピーク群220とピーク群222の一部のピークは、互いに異なる振幅を有する(例えば、変調伝達関数が、光学スポット焦点および/または電子帯域幅に起因して、100パーセント未満(<100%)であるために)。ピーク群220とピーク群222の一部のピークは、異なる要素サイズ(例えば、1×、2×、3×)からもたらされる、互いに異なる周期(例えば、基準周波数)を有する。

【0020】

例示的なアナログ信号202では、ピーク220A、220D、222Bの周期は、ピーク220Bの周期より短い。ピーク220A、220B、220D、222Bの周期は、ピーク220C、222A、222Cの周期より短い。

【0021】

図3は、本発明の実施形態による信号コンディショナ300の高レベルのブロック図であり、コンディショナ300は、ピーク群230とピーク群232、およびピーク群220とピーク群222の一部のピーク、またはすべてのピークを増幅する、または減衰させる制御ループである。また、信号コンディショナ300は、アナログ信号202/203から雑音を選択的に濾波して除くこともできる。

【0022】

図示される実施形態における信号コンディショナ300は、デジタイザ306に出力が結合された自動利得制御回路(AGC)回路304を含む。デジタイザ306の出力は、プロセッサ308に結合される。変調伝達関数(MTF)検出器310が、アナログ信号202/203の一部分をタップするように結合される。選択可能な雑音フィルタ312が、AGC回路304の入力とプロセッサ308に結合される。

【0023】

AGC回路304は、入力に線形応答を与えることができ、したがって、アナログ信号202/203を増幅する、または減衰させる。本発明の諸実施形態によるAGC回路304の実施は、図4および図5に関連して以下により詳細に説明する。

【0024】

デジタイザ306が、アナログ信号202/203を受信し、その信号202/203を、バーコード102を表すデジタル信号314(例えば、方形波)に変換する。一実施形態では、デジタイザ306の性能は、アナログ信号202/203が、基準振幅204の範囲内にある場合に、最適である。デジタイザ306を実施するのに適した回路は、知られている。

【0025】

MTF検出器310が、アナログ信号202/203の少なくとも1つの低周波数部分のピーク振幅と、アナログ信号202/203の少なくとも1つの高周波数部分のピーク振幅を検出する。MTF検出器310は、Gain Low信号を生成し、この信号は、一実施形態では、アナログ信号202/203における低周波数ピークを表す直流(DC)レベルである。また、MTF検出器は、Gain High信号も生成し、この信号は、一実施形態では、アナログ信号202/203における高周波数ピークを表すDCレベルである。もちろん、Gain Low信号とGain High信号は、アナログ信号202/203における低周波数ピークと高周波数ピークをそれぞれ表す任意の適切な信号でよい。本発明の諸実施形態によるMTF検出器310の実施は、図6に関連して以下により詳細に説明する。

【0026】

選択可能な雑音フィルタ312が、AGC回路304の入力に結合されて、アナログ信号202/203の雑音を減衰させ、かつ/または信号対雑音比(SNR)を向上させることが可能である。本発明の諸実施形態による選択可能な雑音フィルタ312の実施は、図5と図7に関連して以下により詳細に説明する。

【0027】

本発明の諸実施形態では、プロセッサ308は、デジタル信号314を復号化することができ、Gain High信号とGain Low信号を測定して、デジタル値に変換し、デジタル値を測定し、デジタル値を基準振幅204と比較し、アナログ信号202/203が増幅されるべきか、または減衰させられるべきか、またはそのままであるべきかを判定する。本明細書の説明を読んだ後、本発明の諸実施形態によるプロセッサ308をどのように実施するかは、当業者には明白となろう。

【0028】

図4は、本発明の実施形態による信号コンディショナ300によって実施されるプロセス400を示す流れ図である。プロセス400のオペレーションは、本発明の諸実施形態を理解するのに最も役立つ形で順に実行される複数の別々のブロックとして説明される。しかし、それらのオペレーションが説明される順序は、それらのオペレーションが、必然的に順序依存であること、またはオペレーションが、ブロックが提示される順序で実施されるべきことを意味するものと解釈されてはならない。

【0029】

もちろん、プロセス400は、単に例示的なプロセスであり、他のプロセスを使用して、本発明の諸実施形態を実施してもよい。マシン可読命令を担持するマシンアクセス可能な媒体を使用して、マシン(例えば、プロセッサ)がプロセス400を実行するようにさせてもよい。

【0030】

ブロック402で、AGC回路304が、光検出器と入力段106からアナログ信号202/203を受け取り、そのアナログ信号202/203に、基準振幅204に基づいて利得または減衰を与える。一実施形態では、プロセッサ308は、基準振幅204を表す利得信号をAGC回路304に供給し、回路304は、その利得信号を、アナログ信号202/203を増幅するため、または減衰させるための基準として使用する。

【0031】

ブロック404で、MTF検出器310が、アナログ信号202/203の一部分をタップし、アナログ信号202/203の少なくとも1つの低周波数部分のピーク振幅を検出し、アナログ信号202/203の少なくとも1つの高周波数部分のピーク振幅を検出する。

【0032】

ブロック406で、プロセッサ308が、基準振幅204、Gain High信号とGain Low信号に関連するアルゴリズムに基づいて新たな利得信号を選択し、その新たな利得信号をAGC回路304に加える。一実施形態では、プロセッサ308は、Gain High信号が、Gain Low信号および基準振幅204と比べて不釣合いに小さいと判定する。その実施形態では、新たな利得信号によって、アナログ信号202/203を増幅することを行うよう、AGC回路304に通知する。その際、そのような増幅により、Gain Low信号が、基準振幅204を超えるようになるかどうかに関わらない。

【0033】

代替の実施形態では、Gain Low信号は、Gain High信号とほぼ等しいが、アナログ信号202/203は、基準振幅204未満である。その実施形態では、新たな利得信号は、アナログ信号202/203を増幅して、その信号202/203を基準振幅204の範囲内にするよう、AGC回路304に知らせる。もちろん、他の振幅スキームや減衰スキームも可能であり、本明細書の説明を読んだ後、Gain High値、Gain Low値、基準振幅204値の様々な組合せのために、本発明の諸実施形態をどのように実施するかは、当業者には直ちに認識されよう。

【0034】

ブロック408で、AGC回路304が、アナログ信号202/203を増幅する、または減衰させるための基準として新たな利得信号を使用する。

【0035】

図5は、本発明の実施形態によるAGC回路304の概略図である。図示される実施形態では、AGC回路304は、キャパシタC4(0.1μF)、C10(0.1μF)、C15(39pF)、C17(0.1μF)、C21(12pF)、C22(30μF)、C24(580pF)、C30(100pF)、演算増幅器U3A(非反転)、演算増幅器U4(反転)、トランジスタQ4(補償接合電界効果トランジスタ(JFET))、トランジスタQ7(電圧制御抵抗器の役割をする利得JFET)、抵抗器R4(24Ω)、R8(5.1Ω)、R19(24Ω)、R21(10KΩ)、R24(24Ω)、R26(10KΩ)、R28(4.7KΩ)、R32(20KΩ)、R35(100KΩ)、R39(100KΩ)、R41(100KΩ)、R43(100KΩ)、R46(8.2KΩ)、R47(10KΩ)を含む。

【0036】

C21は、雑音をロールオフし、増幅器U3Aに信号安定性を与える高周波数補償フィルタを構成する。C22、R24は、U4とFET Q7に関するバイアス電圧が、相互に作用して、アナログ信号202/203に関する不適切なDC出力オフセットと非対称性をもたらすのを低減させる低周波数DCブロッキング・フィルタを構成する。R19とC10およびR4とC4は、U3Aのための電源(例えば、5ボルト)フィルタである。R26とJFET Q7の等価抵抗により、U3Aの利得が決まる。JFET Q4とQ7は、整合トランジスタである。R41、R43、C24は、メイン利得JFET Q7のためのバイアス素子である。R35、R39、C17は、調整JFET Q4のための同様のバイアス素子である。R21、R28は、Q7によって見られる、Q4に対する同様のインピーダンスを提供する。U4は、Q7、Q4のゲートを駆動し、プロセッサ308からのアナログ信号で制御される。R47、R46、C30は、所望される正確なJFETゲート制御のための利得調整を可能にする。

【0037】

プロセッサ308からの利得信号はU4を制御する。U4は、利得信号をバッファリングして、JFET Q7とJFET Q4を駆動する。JFET Q4は、U4の正のフィードバック・パスにある。プロセッサ308からの利得信号に基づき、U4は、JFET Q7にゲート電圧を出力し、JFET Q7は、JFET Q7の特性曲線に従って応答して、等価抵抗をもたらす。U4は、JFET Q4にもゲート電圧を出力し、JFET Q4も、JFET Q4の特性曲線に従って応答して、調整応答をU4に戻す。

【0038】

JFET Q4は、JFET Q7と同様のインピーダンスによって駆動され、負荷がかけられており、JFET Q4は、U4の調整フィードバック・パスにあるため、AGC回路304からの出力は、非常に広いダイナミック・レンジにわたって線形であることが可能である(これにより、非常に幅広い範囲の読み取り距離、例えば、バーコード102に近い読み取り距離と、バーコード102から遠く離れた読み取り距離とすることができる)。実施するのに、複雑な制御式を要求し、しばしば、予測利得調整を制限する既知の他の回路とは異なり、本発明の諸実施形態に従って実施されるAGC回路304は、安価な整合JFETを使用して、利得信号入力に対する応答を線形化する。その結果、プロセッサ308からの利得信号に対するAGC回路304の応答は、予測され、決定論的である。

【0039】

AGC回路304が、アナログ信号202/203を減衰させることが可能な代替の実施形態では、AGC回路304は、R8のすぐ後に結合されたJFET Q7を含む。その実施形態では、JFET Q7ドレインが、アースに結合され、U3Aのプラス入力に分圧電圧を供給する、R8とJFET Q7の等価抵抗の間における電圧分圧器を形成する。

【0040】

本発明のさらに別の実施形態では、AGC回路304は、1つだけのJFET Q7を含み、この実施形態では、回路304の非線形応答(例えば、応答曲線)がプロセッサ308によってマップされる。マップされた値は、格納され(例えば、ルックアップ・テーブルの中に)、プロセッサ308は、マップされた値を使用して、同一の予測利得調整を生成する。

【0041】

本発明の諸実施形態は、JFETであるQ4とQ7に関連して説明されているが、本発明の諸実施形態は、そのように限定されない。例えば、Q4および/またはQ7は、バイポーラ接合トランジスタ(BJT)、MOSFET、真空管、ガリウム・ヒ素(GaAs)FET、ヘテロ接合バイポーラ接合トランジスタ(HBJT)などを含むが、以上には限定されない、任意の適切な利得素子であることが可能である。本明細書の説明を読んだ後、本発明の他の様々な実施形態におけるQ4とQ7をどのように実施するかは、当業者には明白となろう。

【0042】

図4を再び参照する。ブロック404において、MTF検出器310が、アナログ信号202/203の一部分をタップし、アナログ信号202/203の少なくとも1つの周波数部分(例えば、低周波数)のピーク振幅を検出し、アナログ信号202/203の少なくとも1つの他の周波数部分(例えば、高周波数)のピーク振幅を検出することを思い起こされたい。図6は、本発明の実施形態によるMTF検出器310の概略図である。図示される実施形態では、MTF検出器310は、2つの周波数検出回路602、604を含む。一実施形態では、周波数検出回路602は、およそ2、3百キロヘルツから、およそ5、6百キロヘルツまでのレンジにおけるアナログ信号202/203内の高い方の周波数を検出する。別の実施形態では、周波数検出回路604は、およそ数十キロヘルツから、およそ2、3百キロヘルツまでのレンジにおけるアナログ信号202/203内の低い方の周波数を検出する。

【0043】

もちろん、本発明の諸実施形態は、バーコードを表すアナログ信号内の2つだけの、または以上の特定の2つだけの周波数範囲を検出することに限定されない。例えば、いくつかの異なる周波数範囲が検出され、プロセッサ308に供給されてもよい(例えば、1つの周波数範囲が、別の周波数範囲内にあってもよい)。本明細書の説明を読んだ後、さらなる他の周波数範囲に関して本発明の諸実施形態をどのように実施するかは、当業者には直ちに認識されよう。

【0044】

図示される実施形態では、周波数検出回路604は、キャパシタC37(580pF)、C38(0.1μF)、C39(200pF)、C41(8.2pF)、ダイオードD4、D5、D6、増幅器U7A、トランジスタQ8A、抵抗器R51(10KΩ)、R52(100KΩ)、R53(120KΩ)、R54(330Ω)、R55(1KΩ)、R56(10KΩ)、R57(1KΩ)を含む。タップされたアナログ信号202/203は、C37とD5を介して周波数検出回路604に入る。C37、D5は、アナログ信号202/203をアースに整流する。C37、R51、R55は、周波数検出回路604のための信号負荷分離とローエンド・カットオフ周波数を提供する。U7Aは、アナログ信号202/203を増幅する。U7A、D4、D6の組合せは、周波数検出回路604の帯域幅の範囲内に入る、アナログ信号202/203におけるピーク振幅を検出する。

【0045】

C39とR53は、ホールド時定数を与え、周波数検出回路604の帯域幅の範囲内にあるアナログ信号202/203の諸部分のピーク値に基づく電荷を生じさせる。C39の電荷は、プロセッサ308に送られるGain Low信号である。プロセッサ308は、R54を介してQ8Aのベース上に信号を供給して、C39上の電荷をクリアし、これにより、新たな利得信号が、AGC回路304に送られた後、Gain Low信号をリセットする。

【0046】

図示される実施形態では、周波数検出回路602は、キャパシタC43(68pF)、C45(0.015μF)、C46(200pF)、C47(8.2pF)、ダイオードD7、D8、D9、増幅器U7B、トランジスタQ8B、抵抗器R58(10KΩ)、R59(100Ω)、R60(1KΩ)、R61(200KΩ)、R62(330Ω)、R63(10KΩ)、R64(510Ω)を含む。タップされたアナログ信号202/203は、C43とD7を介して周波数検出回路602に入る。C43とD7は、アナログ信号202/203をアースに整流する。C43、R58、R60は、周波数検出回路602のための信号負荷分離とローエンド・カットオフ周波数を提供する。U7Aは、アナログ信号202/203を増幅する。C45とR59は、周波数検出回路602のためのさらなるローエンド・カットオフ周波数を提供する。U7B、D8、D9の組合せは、周波数検出器回路602の帯域幅の範囲内に入る、アナログ信号202/203におけるピーク振幅を検出する。

【0047】

C46とR61は、ホールド時定数を与え、周波数検出回路602の帯域幅の範囲内にあるアナログ信号202/203の諸部分のピーク値に基づく電荷を生じさせる。C46の電荷は、プロセッサ308に送られるGain High信号である。プロセッサ308は、R62を介してQ8Bのベース上に信号を供給して、C46上の電荷をクリアし、これにより、新たな利得信号が、AGC回路304に送られた後、Gain High信号をリセットする。

【0048】

図7は、本発明の実施形態による選択可能な雑音フィルタ312を実施するためのプロセス700を示す流れ図である。プロセス700のオペレーションは、本発明の諸実施形態を理解するのに最も役立つ形で順に実行される複数の別々のブロックとして説明される。しかし、それらのオペレーションが説明される順序は、それらのオペレーションが、必然的に順序依存であること、またはオペレーションが、ブロックが提示される順序で実施されるべきことを意味するものと解釈されてはならない。

【0049】

もちろん、プロセス700は、単に例示的なプロセスであり、他のプロセスを使用して、本発明の諸実施形態を実施してもよい。マシン可読命令を担持するマシンアクセス可能な媒体を使用して、マシン(例えば、プロセッサ)がプロセス700を実行するようにしてもよい。一実施形態では、ユーザは、プロセス700を手動で実施することができる。

【0050】

ブロック702で、プロセッサ308が、Gain Low信号がGain High信号とほぼ等しいと判定する。

【0051】

ブロック704で、プロセッサ308は、新たな利得信号をAGC回路304に印加し、この利得信号は、基準振幅204の範囲内にアナログ信号202/203を(持って行くように)増幅する/減衰させる/保持するよう、AGC回路304に通知する。

【0052】

ブロック706で、プロセッサ308は、選択可能な雑音フィルタ312が、ONであるか、またはOFFであるかを判定する。

【0053】

選択可能な雑音フィルタ312がOFFである場合、ブロック708で、プロセッサ308は、プラットフォーム100に関する読み取り率が、所定の値未満(例えば、およそ100パーセント未満(<100%))であるかどうかを判定する。本明細書で使用される読み取り率は、試行された読み取りの回数当たりの、アナログ信号202/203の復号化の成功の回数として定義される(例えば、10回の試行された読み取りのうち10回の復号化の成功は、100パーセントの読み取り率である)。読み取り率が、所定の値未満である場合、プロセッサ308は、選択可能な雑音フィルタ312をONにする。

【0054】

ブロック712で、プロセッサ308は、読み取り率が増加したか、または低下したかを判定する。読み取り率が低下した場合、ブロック714で、プロセッサ308は、選択可能な雑音フィルタ312をOFFにする。読み取り率が増加した場合、ブロック716で、プロセッサ308は、選択可能な雑音フィルタ312をONのままとする。

【0055】

ブロック706で、選択可能な雑音フィルタ312がONであるとプロセッサ308が判定した場合、プロセス700は、ブロック712に進んで、読み取り率が増加しているか、または低下しているかを判定する。

【0056】

ブロック708で、読み取り率が所定の値未満ではないとプロセッサ308が判定した場合、プロセスは、ブロック714に進み、プロセッサ308は、選択可能な雑音フィルタ312をOFFのままにする。

【0057】

図5を再び参照すると、選択可能な雑音フィルタ312の概略図が示されている。図示される実施形態では、雑音フィルタ312は、抵抗器R32、R42(1KΩ)、キャパシタC15、金属酸化物半導体電界効果トランジスタ(MOSFET)Q5を含む。R32、R42、C15、MOSFET Q5は、既存の抵抗器R8と組み合わさって機能して、雑音フィルタ312を形成し、フィルタ312は、アナログ信号202/203内の選択されたレンジの周波数が通過することを許す一方で、望ましくないペーパ周波数と雑音周波数が通過するのを阻止する。

【0058】

図示される実施形態では、MOSFET Q5は、信号コンディショナ300内の回路から雑音フィルタ312を選択する、または選択解除するようにプロセッサ308によって制御されるスイッチである。R42は、プルダウン・レジスタである。R8、C15、およびR32により、フィルタの周波数ポイントおよび減衰率が決まる。プロセッサ308からの信号が、MOSFET Q5をONにするのに十分である場合、選択可能な雑音フィルタ312は、フィルタ312の帯域内の雑音を濾波して除く。一実施形態では、選択可能な雑音フィルタ312は、アナログ信号202/203上の雑音240を濾波して除く。

【0059】

代替の実施形態では、Q5は、信号コンディショナ300内の回路から雑音フィルタ312を選択する、または選択解除するようにプロセッサ308によって制御されるJFETスイッチである。その実施形態では、Q5は、雑音フィルタ312の極によって定義されるレンジの周波数にわたる、あるレンジの減衰レベルを提供することができる。

【0060】

本発明の諸実施形態は、特定の周波数と特定の帯域幅を使用して説明されてきたが、本明細書の説明を読んだ後には、異なるフィルタ・カットオフ・ポイントを使用して、本発明の諸実施形態をどのように実施するかが明白となろう。さらに、特定のフィルタ・プロファイルは、能動増幅フィルタ、受動フィルタ、および/またはデジタル処理フィルタなどの、他の技術を使用して実現することができる。

【0061】

本発明の諸実施形態は、ハードウェア、ソフトウェア、またはハードウェアとソフトウェアの組合せを使用して実施されることが可能である。ソフトウェアを使用する実装では、ソフトウェアは、マシンアクセス可能な媒体に格納されてもよい。

【0062】

マシンアクセス可能な媒体には、マシン(例えば、コンピュータ、ネットワーク・デバイス、パーソナル・デジタル・アシスタント、製造ツール、1つまたは複数のプロセッサのセットを有する任意のデバイス、その他)がアクセスすることが可能な形態で情報を提供する(すなわち、格納し、かつ/または伝送する)任意の機構が含まれる。例えば、マシンアクセス可能な媒体には、書き込み可能な媒体と書き込み可能でない媒体(例えば、読取り専用メモリ(ROM)、ランダム・アクセス・メモリ(RAM)、磁気ディスク記憶媒体、光記憶媒体、フラッシュ・メモリ・デバイス、その他)ならびに電気形態、光形態、音響形態、またはその他の形態の伝搬される信号(例えば、搬送波、赤外線信号、デジタル信号、その他)が含まれる。

【0063】

以上の説明では、特定のプロセス、材料、およびデバイスなどの、多数の特定の詳細が、本発明の諸実施形態の徹底的な理解をもたらすように提示された。しかし、本発明の諸実施形態は、それらの特定の詳細の1つまたは複数を伴わずに、または他の方法、コンポーネント、その他を使用して実施されることも可能であることが、当業者には認識されよう。その他、周知の構造、または周知のオペレーションは、以上の説明の理解を不明瞭にするのを回避するため、詳細に図示すること、または説明することはしていない。

【0064】

本明細書全体における「一実施形態」または「実施形態」への言及は、ある実施形態に関連して説明される特定の特徴、構造、プロセス、ブロック、または特性が、本発明の少なくとも1つの実施形態に含まれることを意味する。このため、本明細書全体の様々な箇所における「一実施形態では」または「ある実施形態では」という句の出現は、それらの句がすべて同一の実施形態を指すことを必ずしも意味しない。特定の特徴、構造、または特性は、1つまたは複数の実施形態において任意の適切な形で組み合わせられることが可能である。

【0065】

添付の特許請求の範囲において使用される用語は、本発明の諸実施形態を、明細書および特許請求の範囲において開示される特定の諸実施形態に限定するものと解釈されてはならない。むしろ、本発明の諸実施形態の範囲は、特許請求の範囲の解釈の確立されている諸原則に準じて解釈されるべき、添付の特許請求の範囲によって完全に確定されるべきである。

【符号の説明】

【0066】

102…バーコード、104…走査レーザ、106…光検出器−入力段、110…信号コンディショナ、304…自動利得制御(AGC)回路、306…デジタイザ、308…プロセッサ、310…変調伝達関数(MTF)検出器、312…選択可能な雑音フィルタ。

【特許請求の範囲】

【請求項1】

バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅と等しいほぼ等しいと判定し、雑音フィルタがOFFであると判定し、読み取り率が所定の値未満であると判定し、前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにする論理を有することを特徴とする装置。

【請求項2】

バーコードを表す前記アナログ信号に、前記アナログ信号に関する所定の振幅に基づいて第1の利得を与え、

前記アナログ信号の第1の周波数部分の振幅を測定し、

前記アナログ信号の第2の周波数部分の振幅を測定する

論理を有することを特徴とする請求項1記載の装置。

【請求項3】

第1の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第2の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第1の利得要素と第2の利得要素と、

前記線形応答を前記第1のアナログ信号に与えて、第2のアナログ信号を生成する回路と、

前記第2のアナログ信号の第1の周波数部分の振幅を測定し、前記第2のアナログ信号の第2の周波数部分の振幅を測定する回路と、

から構成されることを特徴とする請求項1または2記載の装置。

【請求項4】

第1の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第2の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第1の利得要素と第2の利得要素と、

前記線形応答を前記第1のアナログ信号に与え、前記第2のアナログ信号を生成する回路と、

から構成されることを特徴とする請求項1または2記載の装置。

【請求項5】

応答を有する利得要素と、

前記利得要素との組合せが、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する前記利得要素応答のマップと、

前記線形応答を前記第1のアナログ信号に与えて、第2のアナログ信号を生成する回路と、

前記第2のアナログ信号の第1の周波数部分の振幅を測定し、前記第2のアナログ信号の第2の周波数部分の振幅を測定する論理と、

から構成されることを特徴とする請求項1記載の装置

【請求項6】

バーコードを表すアナログ信号の第1の周波数部分の振幅を表す第1の値を生成するステップと、

前記アナログ信号の第2の周波数部分の振幅を表す第2の値を生成するステップと、

から構成されることを特徴とする方法。

【請求項7】

バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅とほぼ等しいと判定するために前記第1と第2の値を使用するステップと、

雑音フィルタがOFFであると判定するステップと、

読み取り率が所定の値未満であると判定するステップと、

前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにするステップと、

をさらに有することを特徴とする請求項6記載の方法。

【請求項8】

前記アナログ信号に関する所定の振幅に基づいてバーコードを表すアナログ信号に利得を与えるステップをさらに有することを特徴とする請求項7記載の方法。

【請求項9】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数より低いと判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項10】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数より高いと判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項11】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数の範囲内にあると判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項12】

前記アナログ信号の前記第2の周波数部分の前記振幅は、前記アナログ信号の第1の周波数部分の前記振幅未満であると判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項13】

前記アナログ信号の前記第1の周波数部分の前記振幅に基づいて前記アナログ信号に第2の利得を与えるステップをさらに有することを特徴とする請求項12記載の方法。

【請求項14】

前記アナログ信号の前記第2の周波数部分の前記振幅に基づいて第2の利得を前記アナログ信号に与えるステップをさらに有することを特徴とする請求項12記載の方法。

【請求項15】

前記アナログ信号に関する前記所定の振幅に基づいて前記アナログ信号に第2の利得を与えるステップをさらに有することを特徴とする請求項8記載の方法。

【請求項16】

前記読み取り率が増加したと判定するステップと、

前記増加した読み取り率に応答して前記雑音フィルタをONのままにするステップと、をさらに有することを特徴とする請求項7または8記載の方法。

【請求項17】

前記読み取り率が低下したと判定するステップと、

前記低下した読み取り率に応答して前記雑音フィルタをOFFにするステップと、をさらに有することを特徴とする請求項7または8記載の方法。

【請求項18】

バーコードを表すアナログ信号の第1の周波数部分を表す第1の値と、前記アナログ信号の第2の周波数部分を表す第2の値とを生成する変調伝達関数検出器と、

前記アナログ信号に対する前記第1の値、前記第2の値、および/または所定の振幅に基づいて利得信号を算出し、前記利得信号を利得制御回路に印加し、前記利得制御回路が、前記利得信号に対する線形応答である利得を前記アナログ信号に与えるプロセッサと、から構成されることを特徴とする装置。

【請求項19】

前記アナログ信号内の所定のレンジの周波数を通過させ、前記所定のレンジ外の周波数が通過するのを阻止するフィルタ回路をさらに有することを特徴とする請求項18記載の装置。

【請求項20】

前記アナログ信号をデジタル化する論理をさらに有することを特徴とする請求項18記載の装置。

【請求項1】

バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅と等しいほぼ等しいと判定し、雑音フィルタがOFFであると判定し、読み取り率が所定の値未満であると判定し、前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにする論理を有することを特徴とする装置。

【請求項2】

バーコードを表す前記アナログ信号に、前記アナログ信号に関する所定の振幅に基づいて第1の利得を与え、

前記アナログ信号の第1の周波数部分の振幅を測定し、

前記アナログ信号の第2の周波数部分の振幅を測定する

論理を有することを特徴とする請求項1記載の装置。

【請求項3】

第1の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第2の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第1の利得要素と第2の利得要素と、

前記線形応答を前記第1のアナログ信号に与えて、第2のアナログ信号を生成する回路と、

前記第2のアナログ信号の第1の周波数部分の振幅を測定し、前記第2のアナログ信号の第2の周波数部分の振幅を測定する回路と、

から構成されることを特徴とする請求項1または2記載の装置。

【請求項4】

第1の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第2の利得要素と、

前記第1の利得要素にマッチさせ、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する第1の利得要素と第2の利得要素と、

前記線形応答を前記第1のアナログ信号に与え、前記第2のアナログ信号を生成する回路と、

から構成されることを特徴とする請求項1または2記載の装置。

【請求項5】

応答を有する利得要素と、

前記利得要素との組合せが、バーコードを表す第1のアナログ信号に関する所定の振幅に基づく利得信号に対する線形応答を生成する前記利得要素応答のマップと、

前記線形応答を前記第1のアナログ信号に与えて、第2のアナログ信号を生成する回路と、

前記第2のアナログ信号の第1の周波数部分の振幅を測定し、前記第2のアナログ信号の第2の周波数部分の振幅を測定する論理と、

から構成されることを特徴とする請求項1記載の装置

【請求項6】

バーコードを表すアナログ信号の第1の周波数部分の振幅を表す第1の値を生成するステップと、

前記アナログ信号の第2の周波数部分の振幅を表す第2の値を生成するステップと、

から構成されることを特徴とする方法。

【請求項7】

バーコードを表すアナログ信号の第1の周波数部分の振幅が前記アナログ信号の第2の周波数部分の振幅とほぼ等しいと判定するために前記第1と第2の値を使用するステップと、

雑音フィルタがOFFであると判定するステップと、

読み取り率が所定の値未満であると判定するステップと、

前記読み取り率が前記所定の値未満であることに応答して前記雑音フィルタをONにするステップと、

をさらに有することを特徴とする請求項6記載の方法。

【請求項8】

前記アナログ信号に関する所定の振幅に基づいてバーコードを表すアナログ信号に利得を与えるステップをさらに有することを特徴とする請求項7記載の方法。

【請求項9】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数より低いと判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項10】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数より高いと判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項11】

前記第1の周波数部分内の周波数は、前記第2の周波数部分内の周波数の範囲内にあると判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項12】

前記アナログ信号の前記第2の周波数部分の前記振幅は、前記アナログ信号の第1の周波数部分の前記振幅未満であると判定するステップをさらに有することを特徴とする請求項6,7または8のいずれかに記載の方法。

【請求項13】

前記アナログ信号の前記第1の周波数部分の前記振幅に基づいて前記アナログ信号に第2の利得を与えるステップをさらに有することを特徴とする請求項12記載の方法。

【請求項14】

前記アナログ信号の前記第2の周波数部分の前記振幅に基づいて第2の利得を前記アナログ信号に与えるステップをさらに有することを特徴とする請求項12記載の方法。

【請求項15】

前記アナログ信号に関する前記所定の振幅に基づいて前記アナログ信号に第2の利得を与えるステップをさらに有することを特徴とする請求項8記載の方法。

【請求項16】

前記読み取り率が増加したと判定するステップと、

前記増加した読み取り率に応答して前記雑音フィルタをONのままにするステップと、をさらに有することを特徴とする請求項7または8記載の方法。

【請求項17】

前記読み取り率が低下したと判定するステップと、

前記低下した読み取り率に応答して前記雑音フィルタをOFFにするステップと、をさらに有することを特徴とする請求項7または8記載の方法。

【請求項18】

バーコードを表すアナログ信号の第1の周波数部分を表す第1の値と、前記アナログ信号の第2の周波数部分を表す第2の値とを生成する変調伝達関数検出器と、

前記アナログ信号に対する前記第1の値、前記第2の値、および/または所定の振幅に基づいて利得信号を算出し、前記利得信号を利得制御回路に印加し、前記利得制御回路が、前記利得信号に対する線形応答である利得を前記アナログ信号に与えるプロセッサと、から構成されることを特徴とする装置。

【請求項19】

前記アナログ信号内の所定のレンジの周波数を通過させ、前記所定のレンジ外の周波数が通過するのを阻止するフィルタ回路をさらに有することを特徴とする請求項18記載の装置。

【請求項20】

前記アナログ信号をデジタル化する論理をさらに有することを特徴とする請求項18記載の装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−267293(P2010−267293A)

【公開日】平成22年11月25日(2010.11.25)

【国際特許分類】

【出願番号】特願2010−159473(P2010−159473)

【出願日】平成22年7月14日(2010.7.14)

【分割の表示】特願2007−508380(P2007−508380)の分割

【原出願日】平成17年4月4日(2005.4.4)

【出願人】(502435683)マイクロスキャン・システムズ・インコーポレーテッド (6)

【Fターム(参考)】

【公開日】平成22年11月25日(2010.11.25)

【国際特許分類】

【出願日】平成22年7月14日(2010.7.14)

【分割の表示】特願2007−508380(P2007−508380)の分割

【原出願日】平成17年4月4日(2005.4.4)

【出願人】(502435683)マイクロスキャン・システムズ・インコーポレーテッド (6)

【Fターム(参考)】

[ Back to top ]