バーストクロック発生回路

【課題】バーストクロック信号を安定に生成できるバーストクロック発生回路を提供する。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明はバーストクロック発生回路に関し、特に、複合映像信号に含まれるバースト信号に同期したバーストクロック信号を生成するバーストクロック発生回路に関する。

【背景技術】

【0002】

NTSC(National Television System Committee)方式やPAL(Phase Alternating Line standard)方式の複合映像信号を、ベースバンド信号である輝度信号と色差信号に分離するとき、複合映像信号に含まれるバースト信号に同期したバーストクロック信号を生成する必要がある。

【0003】

従来のバーストクロック発生回路は、制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、バースト信号とバーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、位相検波回路の出力信号を積分し、その積分値に基づいて制御電圧を生成する制御電圧発生回路とを備えている(たとえば、特許文献1,2)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−80026号公報

【特許文献2】特開2000−287220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来のバーストクロック発生回路は、規格に準拠した標準の複合映像信号が入力された場合は特性的に問題なく動作するが、標準でない複合映像信号が入力された場合は、バーストクロック信号を安定に生成することができなかった。標準でない複合映像信号としては、たとえば、フィールド単位でバースト信号の位相が不連続になる複合映像信号や、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号がある。

【0006】

それゆえに、この発明の主たる目的は、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することが可能なバーストクロック発生回路を提供することである。

【課題を解決するための手段】

【0007】

この発明に係るバーストクロック発生回路は、制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号とバーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、位相検波回路の出力信号を積分し、その積分値に基づいて制御電圧を生成する、応答速度の変更が可能な制御電圧発生回路と、複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では制御電圧発生回路の応答速度を0に設定し、各垂直帰線期間のうちの第1の期間を除く第2の期間では制御電圧発生回路の応答速度を第1の速度に設定し、複合映像信号における垂直帰線期間以外の表示期間では制御電圧発生回路の応答速度を第1の速度よりも遅い第2の速度に設定する制御回路とを備えたものである。

【発明の効果】

【0008】

この発明に係るバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では、バースト信号が設けられていないので、制御電圧発生回路の応答速度を0に設定する。また、各垂直帰線期間のうちの第1の期間を除く第2の期間では制御電圧発生回路の応答速度を、表示期間よりも速い第1の速度に設定するので、フィールド単位でバースト信号の位相が不連続になる場合でも、表示期間の開始までに位相誤差をなくすことができる。また、複合映像信号における垂直帰線期間以外の表示期間では制御電圧発生回路の応答速度を第1の速度よりも遅い第2の速度に設定するので、VTRの巻き戻し/早送りやコピーガード信号によってバースト信号が異常になった場合でも、過敏に反応することがない。したがって、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することができる。

【図面の簡単な説明】

【0009】

【図1】この発明の実施の形態1によるバーストクロック発生回路の構成を示すブロック図である。

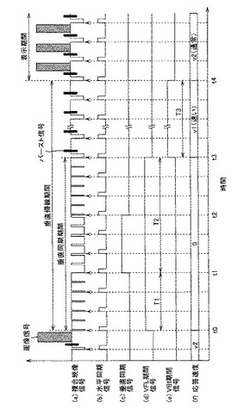

【図2】図1に示したバーストクロック発生回路の動作を例示するタイムチャートである。

【図3】図1に示したバーストクロック発生回路の動作を例示する他のタイムチャートである。

【図4】実施の形態1の比較例を示すブロック図である。

【図5】図4に示したバーストクロック発生回路の問題点を説明するためのタイムチャートである。

【図6】図4に示したバーストクロック発生回路の問題点を説明するための他のタイムチャートである。

【図7】この発明の実施の形態2によるバーストクロック発生回路の構成を示すブロック図である。

【図8】この発明の実施の形態3によるバーストクロック発生回路の構成を示すブロック図である。

【図9】実施の形態3の効果を示すタイムチャートである。

【発明を実施するための形態】

【0010】

[実施の形態1]

本発明の実施の形態1によるバーストクロック発生回路は、図1に示すように、水平同期分離回路1、バースト期間生成回路2、位相検波回路3、位相ロックフィルタ4、電圧制御型発振器(VCO)5、垂直同期分離回路6、信号発生回路7、および制御回路8を備える。このバーストクロック発生回路は、複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号に同期したバーストクロック信号を生成するものである。

【0011】

複合映像信号における各1水平期間には、図2(a)に示すように、水平同期パルス、バースト信号、および画像信号が設けられている。水平同期パルスとバースト信号は、1水平期間のうちの水平帰線期間に設けられている。水平同期パルスは、1水平期間の開始を示す信号である。バースト信号は、カラー信号を正しく復調し再現するための位相の基準となる信号であり、所定周波数の正弦波状の信号である。画像信号は、1ライン分の画像を示す信号である。

【0012】

水平同期分離回路1は、複合映像信号から水平同期パルスを分離して水平同期信号を生成する。水平同期信号は、図2(b)に示すように、各1水平期間の開始時に所定時間だけ「H」レベルにされる。

【0013】

バースト期間生成回路2は、水平同期分離回路1によって生成された水平同期信号に同期して、バースト信号が設けられている期間を示すバースト期間信号を生成する。バースト期間生成回路2は、たとえば、水平同期信号を遅延させた信号のパルス幅を調整してバースト期間信号を生成する。バースト期間信号は、図2(c)に示すように、各1水平期間においてバースト信号が設けられている期間だけ「H」レベルにされる。

【0014】

位相検波回路3は、バースト期間信号が「H」レベルにされている期間において、電圧制御型発振器5で生成されたバーストクロック信号と、複合映像信号に含まれるバースト信号との位相誤差を検出し、検出した位相誤差を示す位相誤差信号を出力する。

【0015】

位相誤差信号は、たとえば、位相誤差に応じたレベルの電流信号である。バーストクロック信号の位相がバースト信号よりも進んでいる場合は、位相誤差信号は負の電流となり、バーストクロック信号の位相がバースト信号よりも遅れている場合は、位相誤差信号は正の電流となる。また、バーストクロック信号とバースト信号の位相差が大きいほど位相誤差信号の電流値が増大し、バーストクロック信号とバースト信号の位相差が小さいほど位相誤差信号の電流値が減少する。

【0016】

位相ロックフィルタ(制御電圧発生回路)4は、積分回路を含み、位相誤差信号を積分し、その積分値に基づいて制御電圧を生成する。電圧制御型発振器5は、制御電圧に応じた周波数のバーストクロック信号を生成する。このバーストクロック信号は、位相検波回路3にフィードバックされる。これにより、バーストクロック信号は、図2(d)に示すように、バースト信号と同じ周波数を有し、バースト信号と位相が一致した正弦波状の信号となる。位相ロックフィルタ4の応答速度は、変更可能になっており、複合映像信号の各1垂直期間において3段階で変更される。

【0017】

すなわち、複合映像信号では、図3(a)に示すように、垂直帰線期間と表示期間が交互に配置されている。表示期間は、複数の水平期間含み、1つの画像を画面に描画するための期間である。垂直帰線期間は、複合映像信号の各1垂直期間の先頭に挿入される。垂直帰線期間は、1つの画像を描画するために上部から下部まで画面を走査した電子銃が、次の画像を描画するために画面の上部に移動するための期間である。たとえば垂直周波数が59.94HzであるNTSC方式の場合、1〜21番の水平期間が垂直帰線期間とされている。垂直帰線期間の信号は画像として表示されることはないので、垂直帰線期間の複合映像信号には、制御用の信号、テスト信号、文字情報、その他のデジタルデータが挿入されている。

【0018】

1〜9番の水平期間は、垂直同期期間とされている。1〜3番の水平期間の各々には、前置等価パルスが挿入されている。4〜6番の水平期間の各々には、垂直同期パルスが挿入されている。7〜9番の水平期間の各々には、後置等価パルスが挿入されている。10〜21番の水平期間の各々には、テスト信号、その他の信号が挿入されている。1〜9番の水平期間ではバースト信号は挿入されず、10〜21番の水平期間の各々にはバースト信号が挿入されている。22番以降の各水平期間では、バースト信号と画像信号が挿入されている。

【0019】

水平同期信号は、図3(b)に示すように、垂直帰線期間でも各1水平期間の開始時に一定時間だけ「H」レベルにされる。垂直同期分離回路6は、4〜6番の水平期間の各々に挿入された垂直同期パルスに同期して垂直同期信号を生成する。垂直同期信号は、図3(c)に示すように、4番の水平期間の開始時に「H」レベルに立ち上げられ、6番の水平期間の終了時に「L」レベルに立ち下げられる。

【0020】

信号発生回路7は、水平同期分離回路1で生成された水平同期信号と垂直同期分離回路6で生成された垂直同期信号とに基づいて、VFL期間信号およびVBI期間信号を生成する。VFL期間信号は、図3(d)に示すように、各垂直帰線期間のうちの垂直同期期間(時刻t0〜t3)だけ「H」レベルにされる信号である。VBI期間信号は、図3(e)に示すように、各垂直帰線期間のうちの垂直同期期間以外の期間(時刻t3〜t4)だけ「H」レベルにされる信号である。

【0021】

垂直同期期間の開始時刻t0から垂直同期信号の立ち上がりエッジ(時刻t1)までの時間T1は、3水平期間分の時間と定められている。また、垂直同期信号の立ち上がりエッジ(時刻t1)から垂直同期期間の終了時刻(時刻t3)までの時間T2は、6水平期間分の時間と定められている。各垂直帰線期間のうちの垂直同期期間以外の期間(時刻t3〜t4)の時間T3は、12水平期間分の時間と定められている。たとえば、VFL期間信号は、垂直同期信号の立ち上がりエッジと、所定時間T1,T2とに基づいて生成される。VBI期間信号は、垂直同期信号の立ち上がりエッジと、所定時間T2,T3とに基づいて生成される。

【0022】

制御回路8は、VFL期間信号およびVBI期間信号に基いて、位相ロックフィルタ4の応答速度を制御する。図3(f)に示すように、VFL期間信号が「H」レベルである期間は、位相ロックフィルタ4の応答速度は0に設定され、位相ロックフィルタ4の出力電圧はVFL期間信号が「H」レベルに立ち上げられる直前のレベルに維持される。

【0023】

また、VBI期間信号が「H」レベルである期間は、位相ロックフィルタ4の応答速度は比較的速い速度v1に設定される。また、VFL期間信号およびVBI期間信号がともに「L」レベルにされる表示期間は、位相ロックフィルタ4の応答速度は比較的遅い通常の速度v2に設定される。たとえば、v1は、v2の約4倍に設定される。位相ロックフィルタ4の応答速度は、たとえば位相ロックフィルタ4の時定数を変更することにより、変更される。

【0024】

本実施の形態1では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では、バースト信号が設けられていないので、位相ロックフィルタ4の応答速度を0に設定する。また、各垂直帰線期間のうちの垂直同期期間以外の期間では、位相ロックフィルタ4の応答速度を通常よりも速い速度v1に設定するので、フィールド単位でバースト信号の位相が不連続になる場合でも、表示期間の開始までに位相誤差をなくすことができる。また、表示期間では、位相ロックフィルタ4の応答速度を通常の速度v2に設定するので、VTRの巻き戻し/早送りやコピーガード信号によってバースト信号が異常になった場合でも、過敏に反応することがない。したがって、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することができる。

【0025】

なお、本実施の形態1では、本願発明が垂直周波数が59.94HzであるNTSC方式の複合映像信号に適用された場合について説明したが、これに限るものではなく、本願発明は他の複合映像信号、たとえば垂直周波数が50HzであるPAL方式の複合映像信号にも適用可能であることは言うまでもない。

【0026】

[比較例]

図4は実施の形態1の比較例を示すブロック図であって、図1と対比される図である。図4を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、垂直同期分離回路6、信号発生回路7、および制御回路8が除去され、位相ロックフィルタ4が位相ロックフィルタ10で置換されている点である。

【0027】

位相ロックフィルタ10は、位相ロックフィルタ4と同様に、位相誤差信号を積分して制御電圧を生成するが、位相ロックフィルタ10の応答速度は通常の速度v2に固定されている。比較例のバーストクロック発生回路は、規格に準拠した標準の複合映像信号が入力された場合は、特性的に問題なく動作する。この場合は図5(a)に示すように、位相ロックフィルタ10で生成された制御電圧VCは、ほぼ一定値に安定する。

【0028】

しかし、バーストクロック発生回路には標準の複合映像信号だけが入力されるとは限らない。たとえば、フィールド単位でバースト信号の位相が不連続になる複合映像信号が入力される場合がある。この場合は図5(b)に示すように、各垂直帰線期間でバースト信号とバーストクロック信号の位相誤差が発生し、制御電圧VCが所定値から外れてしまう。比較例では、位相ロックフィルタ10の応答速度が比較的遅い通常の速度v2に固定されているので、図5(b)に示すように、垂直帰線期間内に制御電圧VCを所定値にすることができない。このため、表示期間でも制御電圧VCが変化し(点線で囲まれた部分)、良好なカラー画像を表示することができない。

【0029】

この問題を解決する方法としては、位相ロックフィルタ10の応答速度を通常よりも速い速度v1に固定する方法が考えられる。この方法によれば、図5(c)に示すように、垂直帰線期間内に制御電圧VCを所定値に到達させることができる。しかし、この方法では、以下の問題がある。

【0030】

バーストクロック発生回路に、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号が入力される場合がある。この場合は図6(a)に示すように、表示期間内においてバースト信号が一定の時間間隔で短時間だけ異常になる。

【0031】

位相ロックフィルタ10の応答速度が通常の速度v2に設定されている場合は、図6(b)に示すように、バースト信号が短時間だけ変動しても制御電圧VCはほどんど変動しない。しかし、位相ロックフィルタ10の応答速度が通常よりも速い速度v1に設定されている場合は、図6(c)に示すように、バースト信号が短時間だけ変動しても制御電圧VCが変動してしまい、良好なカラー画像を表示することができない。

【0032】

つまり、比較例のバーストクロック発生回路では、位相ロックフィルタ10の応答速度が一定値に固定されているので、標準でない複合映像信号が入力された場合はバーストクロック信号を安定に生成することができない。

【0033】

これに対して本実施の形態1では、複合映像信号の期間に応じて位相ロックフィルタ4の応答速度を適値に切換えるので、図5(c)および図6(b)で示すように制御電圧VCを安定に生成することができる。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成することができる。

【0034】

[実施の形態2]

水平同期信号および垂直同期信号の同期が安定していない場合では、各同期信号において本来パルスが存在すべき位置にパルスが存在しない欠落状態や、逆に、各同期信号において本来パルスが存在しない位置にパルスが存在する多発状態が発生する。この場合は、実施の形態1のバーストクロック発生回路ではVFL期間信号およびVBI期間信号が正常に生成されなくなり、比較例よりも性能が劣化してしまう。この実施の形態2では、この問題の解決が図られる。

【0035】

図7は、この発明の実施の形態2によるバーストクロック発生回路の構成を示すブロック図であって、図1と対比される図である。図7を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、同期安定判定回路11が追加されている点である。

【0036】

同期安定判定回路11は、水平同期信号および垂直同期信号の同期が安定している場合は信号φ11を「L」レベルにし、水平同期信号および垂直同期信号の同期が安定していない場合は信号φ11を「H」レベルにする。

【0037】

制御回路8は、信号φ11が「L」レベルである場合は実施の形態1と同様に動作し、信号φ11が「H」レベルである場合は位相ロックフィルタ4の応答速度を通常の速度v2に固定する。

【0038】

この実施の形態2では、水平同期信号および垂直同期信号の同期が安定しない場合は、位相ロックフィルタ4の応答速度を通常の速度v2に固定する。したがって、実施の形態1と同じ効果が得られる他、同期信号の同期が安定しない場合でも従来と同じ性能が得られる。

【0039】

なお、この実施の形態2では、同期安定判定回路11は水平同期信号および垂直同期信号の同期が安定しているか否かを判定したが、水平同期信号の同期が安定しているか否かだけを判定してもよいし、垂直同期信号の同期が安定しているか否かだけを判定してもよい。

【0040】

[実施の形態3]

上述のように、バーストクロック発生回路に、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号が入力された場合は、表示期間内においてバースト信号が一定の時間間隔で短時間だけ異常になる。実施の形態1では、表示期間における位相ロックフィルタ4の応答速度を比較的遅い速度v2に設定して、バースト信号の異常に過敏に反応しないようにした。しかし、位相ロックフィルタ4の応答速度を遅くすると、通常レベルのノイズに対する応答が遅延してしまう。この実施の形態3では、この問題が解決される。

【0041】

図8は、この発明の実施の形態3によるバーストクロック発生回路の構成を示すブロック図であって、図1と対比される図である。図8を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、異常検出回路12が追加されている点である。

【0042】

異常検出回路12は、位相検波回路3と位相ロックフィルタ4との間に設けられ、位相検波回路3からの位相誤差信号のレベル変化が正常範囲内か否かを判別し、正常範囲内である場合は位相誤差信号を通過させ、正常範囲内でない場合(異常な場合)は位相誤差信号の通過を禁止する。位相誤差信号の通過が禁止されると、位相ロックフィルタ4では制御電圧VCの更新が停止される。

【0043】

図9(a)〜(e)は、実施の形態3の効果を示すタイムチャートである。図9(a)に示すように、表示期間においてバースト信号が一定の時間間隔で短時間だけ異常になるものとする。位相誤差信号Ieは、図9(b)に示すように、バースト信号の異常に応答して突発的に異常に変化する。

【0044】

実施の形態1のバーストクロック発生回路では、表示期間における位相ロックフィルタ4の応答速度を比較的速い速度v3(v2<v3≦v1)にすると、図9(c)に示すように、位相誤差信号Ieの突発的な変化に応答して制御電圧VCが変動してしまう。

【0045】

これに対して実施の形態3では、位相誤差信号Ieのうちの突発的な変化分は異常検出回路12によって除去されるので、制御電圧VCが変動しない。このため、安定したバーストクロック信号を得ることができ、良好なカラー画像を表示することができる。

【0046】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0047】

1 水平同期分離回路、2 バースト期間生成回路、3 位相検波回路、4,10 位相ロックフィルタ、5 電圧制御型発振器、6 垂直同期分離回路、7 信号発生回路、8 制御回路、11 同期安定判定回路、12 異常検出回路。

【技術分野】

【0001】

この発明はバーストクロック発生回路に関し、特に、複合映像信号に含まれるバースト信号に同期したバーストクロック信号を生成するバーストクロック発生回路に関する。

【背景技術】

【0002】

NTSC(National Television System Committee)方式やPAL(Phase Alternating Line standard)方式の複合映像信号を、ベースバンド信号である輝度信号と色差信号に分離するとき、複合映像信号に含まれるバースト信号に同期したバーストクロック信号を生成する必要がある。

【0003】

従来のバーストクロック発生回路は、制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、バースト信号とバーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、位相検波回路の出力信号を積分し、その積分値に基づいて制御電圧を生成する制御電圧発生回路とを備えている(たとえば、特許文献1,2)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−80026号公報

【特許文献2】特開2000−287220号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来のバーストクロック発生回路は、規格に準拠した標準の複合映像信号が入力された場合は特性的に問題なく動作するが、標準でない複合映像信号が入力された場合は、バーストクロック信号を安定に生成することができなかった。標準でない複合映像信号としては、たとえば、フィールド単位でバースト信号の位相が不連続になる複合映像信号や、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号がある。

【0006】

それゆえに、この発明の主たる目的は、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することが可能なバーストクロック発生回路を提供することである。

【課題を解決するための手段】

【0007】

この発明に係るバーストクロック発生回路は、制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号とバーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、位相検波回路の出力信号を積分し、その積分値に基づいて制御電圧を生成する、応答速度の変更が可能な制御電圧発生回路と、複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では制御電圧発生回路の応答速度を0に設定し、各垂直帰線期間のうちの第1の期間を除く第2の期間では制御電圧発生回路の応答速度を第1の速度に設定し、複合映像信号における垂直帰線期間以外の表示期間では制御電圧発生回路の応答速度を第1の速度よりも遅い第2の速度に設定する制御回路とを備えたものである。

【発明の効果】

【0008】

この発明に係るバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では、バースト信号が設けられていないので、制御電圧発生回路の応答速度を0に設定する。また、各垂直帰線期間のうちの第1の期間を除く第2の期間では制御電圧発生回路の応答速度を、表示期間よりも速い第1の速度に設定するので、フィールド単位でバースト信号の位相が不連続になる場合でも、表示期間の開始までに位相誤差をなくすことができる。また、複合映像信号における垂直帰線期間以外の表示期間では制御電圧発生回路の応答速度を第1の速度よりも遅い第2の速度に設定するので、VTRの巻き戻し/早送りやコピーガード信号によってバースト信号が異常になった場合でも、過敏に反応することがない。したがって、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することができる。

【図面の簡単な説明】

【0009】

【図1】この発明の実施の形態1によるバーストクロック発生回路の構成を示すブロック図である。

【図2】図1に示したバーストクロック発生回路の動作を例示するタイムチャートである。

【図3】図1に示したバーストクロック発生回路の動作を例示する他のタイムチャートである。

【図4】実施の形態1の比較例を示すブロック図である。

【図5】図4に示したバーストクロック発生回路の問題点を説明するためのタイムチャートである。

【図6】図4に示したバーストクロック発生回路の問題点を説明するための他のタイムチャートである。

【図7】この発明の実施の形態2によるバーストクロック発生回路の構成を示すブロック図である。

【図8】この発明の実施の形態3によるバーストクロック発生回路の構成を示すブロック図である。

【図9】実施の形態3の効果を示すタイムチャートである。

【発明を実施するための形態】

【0010】

[実施の形態1]

本発明の実施の形態1によるバーストクロック発生回路は、図1に示すように、水平同期分離回路1、バースト期間生成回路2、位相検波回路3、位相ロックフィルタ4、電圧制御型発振器(VCO)5、垂直同期分離回路6、信号発生回路7、および制御回路8を備える。このバーストクロック発生回路は、複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号に同期したバーストクロック信号を生成するものである。

【0011】

複合映像信号における各1水平期間には、図2(a)に示すように、水平同期パルス、バースト信号、および画像信号が設けられている。水平同期パルスとバースト信号は、1水平期間のうちの水平帰線期間に設けられている。水平同期パルスは、1水平期間の開始を示す信号である。バースト信号は、カラー信号を正しく復調し再現するための位相の基準となる信号であり、所定周波数の正弦波状の信号である。画像信号は、1ライン分の画像を示す信号である。

【0012】

水平同期分離回路1は、複合映像信号から水平同期パルスを分離して水平同期信号を生成する。水平同期信号は、図2(b)に示すように、各1水平期間の開始時に所定時間だけ「H」レベルにされる。

【0013】

バースト期間生成回路2は、水平同期分離回路1によって生成された水平同期信号に同期して、バースト信号が設けられている期間を示すバースト期間信号を生成する。バースト期間生成回路2は、たとえば、水平同期信号を遅延させた信号のパルス幅を調整してバースト期間信号を生成する。バースト期間信号は、図2(c)に示すように、各1水平期間においてバースト信号が設けられている期間だけ「H」レベルにされる。

【0014】

位相検波回路3は、バースト期間信号が「H」レベルにされている期間において、電圧制御型発振器5で生成されたバーストクロック信号と、複合映像信号に含まれるバースト信号との位相誤差を検出し、検出した位相誤差を示す位相誤差信号を出力する。

【0015】

位相誤差信号は、たとえば、位相誤差に応じたレベルの電流信号である。バーストクロック信号の位相がバースト信号よりも進んでいる場合は、位相誤差信号は負の電流となり、バーストクロック信号の位相がバースト信号よりも遅れている場合は、位相誤差信号は正の電流となる。また、バーストクロック信号とバースト信号の位相差が大きいほど位相誤差信号の電流値が増大し、バーストクロック信号とバースト信号の位相差が小さいほど位相誤差信号の電流値が減少する。

【0016】

位相ロックフィルタ(制御電圧発生回路)4は、積分回路を含み、位相誤差信号を積分し、その積分値に基づいて制御電圧を生成する。電圧制御型発振器5は、制御電圧に応じた周波数のバーストクロック信号を生成する。このバーストクロック信号は、位相検波回路3にフィードバックされる。これにより、バーストクロック信号は、図2(d)に示すように、バースト信号と同じ周波数を有し、バースト信号と位相が一致した正弦波状の信号となる。位相ロックフィルタ4の応答速度は、変更可能になっており、複合映像信号の各1垂直期間において3段階で変更される。

【0017】

すなわち、複合映像信号では、図3(a)に示すように、垂直帰線期間と表示期間が交互に配置されている。表示期間は、複数の水平期間含み、1つの画像を画面に描画するための期間である。垂直帰線期間は、複合映像信号の各1垂直期間の先頭に挿入される。垂直帰線期間は、1つの画像を描画するために上部から下部まで画面を走査した電子銃が、次の画像を描画するために画面の上部に移動するための期間である。たとえば垂直周波数が59.94HzであるNTSC方式の場合、1〜21番の水平期間が垂直帰線期間とされている。垂直帰線期間の信号は画像として表示されることはないので、垂直帰線期間の複合映像信号には、制御用の信号、テスト信号、文字情報、その他のデジタルデータが挿入されている。

【0018】

1〜9番の水平期間は、垂直同期期間とされている。1〜3番の水平期間の各々には、前置等価パルスが挿入されている。4〜6番の水平期間の各々には、垂直同期パルスが挿入されている。7〜9番の水平期間の各々には、後置等価パルスが挿入されている。10〜21番の水平期間の各々には、テスト信号、その他の信号が挿入されている。1〜9番の水平期間ではバースト信号は挿入されず、10〜21番の水平期間の各々にはバースト信号が挿入されている。22番以降の各水平期間では、バースト信号と画像信号が挿入されている。

【0019】

水平同期信号は、図3(b)に示すように、垂直帰線期間でも各1水平期間の開始時に一定時間だけ「H」レベルにされる。垂直同期分離回路6は、4〜6番の水平期間の各々に挿入された垂直同期パルスに同期して垂直同期信号を生成する。垂直同期信号は、図3(c)に示すように、4番の水平期間の開始時に「H」レベルに立ち上げられ、6番の水平期間の終了時に「L」レベルに立ち下げられる。

【0020】

信号発生回路7は、水平同期分離回路1で生成された水平同期信号と垂直同期分離回路6で生成された垂直同期信号とに基づいて、VFL期間信号およびVBI期間信号を生成する。VFL期間信号は、図3(d)に示すように、各垂直帰線期間のうちの垂直同期期間(時刻t0〜t3)だけ「H」レベルにされる信号である。VBI期間信号は、図3(e)に示すように、各垂直帰線期間のうちの垂直同期期間以外の期間(時刻t3〜t4)だけ「H」レベルにされる信号である。

【0021】

垂直同期期間の開始時刻t0から垂直同期信号の立ち上がりエッジ(時刻t1)までの時間T1は、3水平期間分の時間と定められている。また、垂直同期信号の立ち上がりエッジ(時刻t1)から垂直同期期間の終了時刻(時刻t3)までの時間T2は、6水平期間分の時間と定められている。各垂直帰線期間のうちの垂直同期期間以外の期間(時刻t3〜t4)の時間T3は、12水平期間分の時間と定められている。たとえば、VFL期間信号は、垂直同期信号の立ち上がりエッジと、所定時間T1,T2とに基づいて生成される。VBI期間信号は、垂直同期信号の立ち上がりエッジと、所定時間T2,T3とに基づいて生成される。

【0022】

制御回路8は、VFL期間信号およびVBI期間信号に基いて、位相ロックフィルタ4の応答速度を制御する。図3(f)に示すように、VFL期間信号が「H」レベルである期間は、位相ロックフィルタ4の応答速度は0に設定され、位相ロックフィルタ4の出力電圧はVFL期間信号が「H」レベルに立ち上げられる直前のレベルに維持される。

【0023】

また、VBI期間信号が「H」レベルである期間は、位相ロックフィルタ4の応答速度は比較的速い速度v1に設定される。また、VFL期間信号およびVBI期間信号がともに「L」レベルにされる表示期間は、位相ロックフィルタ4の応答速度は比較的遅い通常の速度v2に設定される。たとえば、v1は、v2の約4倍に設定される。位相ロックフィルタ4の応答速度は、たとえば位相ロックフィルタ4の時定数を変更することにより、変更される。

【0024】

本実施の形態1では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では、バースト信号が設けられていないので、位相ロックフィルタ4の応答速度を0に設定する。また、各垂直帰線期間のうちの垂直同期期間以外の期間では、位相ロックフィルタ4の応答速度を通常よりも速い速度v1に設定するので、フィールド単位でバースト信号の位相が不連続になる場合でも、表示期間の開始までに位相誤差をなくすことができる。また、表示期間では、位相ロックフィルタ4の応答速度を通常の速度v2に設定するので、VTRの巻き戻し/早送りやコピーガード信号によってバースト信号が異常になった場合でも、過敏に反応することがない。したがって、標準でない複合映像信号が入力された場合でもバーストクロック信号を安定に生成することができる。

【0025】

なお、本実施の形態1では、本願発明が垂直周波数が59.94HzであるNTSC方式の複合映像信号に適用された場合について説明したが、これに限るものではなく、本願発明は他の複合映像信号、たとえば垂直周波数が50HzであるPAL方式の複合映像信号にも適用可能であることは言うまでもない。

【0026】

[比較例]

図4は実施の形態1の比較例を示すブロック図であって、図1と対比される図である。図4を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、垂直同期分離回路6、信号発生回路7、および制御回路8が除去され、位相ロックフィルタ4が位相ロックフィルタ10で置換されている点である。

【0027】

位相ロックフィルタ10は、位相ロックフィルタ4と同様に、位相誤差信号を積分して制御電圧を生成するが、位相ロックフィルタ10の応答速度は通常の速度v2に固定されている。比較例のバーストクロック発生回路は、規格に準拠した標準の複合映像信号が入力された場合は、特性的に問題なく動作する。この場合は図5(a)に示すように、位相ロックフィルタ10で生成された制御電圧VCは、ほぼ一定値に安定する。

【0028】

しかし、バーストクロック発生回路には標準の複合映像信号だけが入力されるとは限らない。たとえば、フィールド単位でバースト信号の位相が不連続になる複合映像信号が入力される場合がある。この場合は図5(b)に示すように、各垂直帰線期間でバースト信号とバーストクロック信号の位相誤差が発生し、制御電圧VCが所定値から外れてしまう。比較例では、位相ロックフィルタ10の応答速度が比較的遅い通常の速度v2に固定されているので、図5(b)に示すように、垂直帰線期間内に制御電圧VCを所定値にすることができない。このため、表示期間でも制御電圧VCが変化し(点線で囲まれた部分)、良好なカラー画像を表示することができない。

【0029】

この問題を解決する方法としては、位相ロックフィルタ10の応答速度を通常よりも速い速度v1に固定する方法が考えられる。この方法によれば、図5(c)に示すように、垂直帰線期間内に制御電圧VCを所定値に到達させることができる。しかし、この方法では、以下の問題がある。

【0030】

バーストクロック発生回路に、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号が入力される場合がある。この場合は図6(a)に示すように、表示期間内においてバースト信号が一定の時間間隔で短時間だけ異常になる。

【0031】

位相ロックフィルタ10の応答速度が通常の速度v2に設定されている場合は、図6(b)に示すように、バースト信号が短時間だけ変動しても制御電圧VCはほどんど変動しない。しかし、位相ロックフィルタ10の応答速度が通常よりも速い速度v1に設定されている場合は、図6(c)に示すように、バースト信号が短時間だけ変動しても制御電圧VCが変動してしまい、良好なカラー画像を表示することができない。

【0032】

つまり、比較例のバーストクロック発生回路では、位相ロックフィルタ10の応答速度が一定値に固定されているので、標準でない複合映像信号が入力された場合はバーストクロック信号を安定に生成することができない。

【0033】

これに対して本実施の形態1では、複合映像信号の期間に応じて位相ロックフィルタ4の応答速度を適値に切換えるので、図5(c)および図6(b)で示すように制御電圧VCを安定に生成することができる。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成することができる。

【0034】

[実施の形態2]

水平同期信号および垂直同期信号の同期が安定していない場合では、各同期信号において本来パルスが存在すべき位置にパルスが存在しない欠落状態や、逆に、各同期信号において本来パルスが存在しない位置にパルスが存在する多発状態が発生する。この場合は、実施の形態1のバーストクロック発生回路ではVFL期間信号およびVBI期間信号が正常に生成されなくなり、比較例よりも性能が劣化してしまう。この実施の形態2では、この問題の解決が図られる。

【0035】

図7は、この発明の実施の形態2によるバーストクロック発生回路の構成を示すブロック図であって、図1と対比される図である。図7を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、同期安定判定回路11が追加されている点である。

【0036】

同期安定判定回路11は、水平同期信号および垂直同期信号の同期が安定している場合は信号φ11を「L」レベルにし、水平同期信号および垂直同期信号の同期が安定していない場合は信号φ11を「H」レベルにする。

【0037】

制御回路8は、信号φ11が「L」レベルである場合は実施の形態1と同様に動作し、信号φ11が「H」レベルである場合は位相ロックフィルタ4の応答速度を通常の速度v2に固定する。

【0038】

この実施の形態2では、水平同期信号および垂直同期信号の同期が安定しない場合は、位相ロックフィルタ4の応答速度を通常の速度v2に固定する。したがって、実施の形態1と同じ効果が得られる他、同期信号の同期が安定しない場合でも従来と同じ性能が得られる。

【0039】

なお、この実施の形態2では、同期安定判定回路11は水平同期信号および垂直同期信号の同期が安定しているか否かを判定したが、水平同期信号の同期が安定しているか否かだけを判定してもよいし、垂直同期信号の同期が安定しているか否かだけを判定してもよい。

【0040】

[実施の形態3]

上述のように、バーストクロック発生回路に、VTRの巻き戻し/早送りなどによって一定間隔でバースト信号が異常になる複合映像信号や、コピーガード信号が重畳された複合映像信号が入力された場合は、表示期間内においてバースト信号が一定の時間間隔で短時間だけ異常になる。実施の形態1では、表示期間における位相ロックフィルタ4の応答速度を比較的遅い速度v2に設定して、バースト信号の異常に過敏に反応しないようにした。しかし、位相ロックフィルタ4の応答速度を遅くすると、通常レベルのノイズに対する応答が遅延してしまう。この実施の形態3では、この問題が解決される。

【0041】

図8は、この発明の実施の形態3によるバーストクロック発生回路の構成を示すブロック図であって、図1と対比される図である。図8を参照して、このバーストクロック発生回路が図1のバーストクロック発生回路と異なる点は、異常検出回路12が追加されている点である。

【0042】

異常検出回路12は、位相検波回路3と位相ロックフィルタ4との間に設けられ、位相検波回路3からの位相誤差信号のレベル変化が正常範囲内か否かを判別し、正常範囲内である場合は位相誤差信号を通過させ、正常範囲内でない場合(異常な場合)は位相誤差信号の通過を禁止する。位相誤差信号の通過が禁止されると、位相ロックフィルタ4では制御電圧VCの更新が停止される。

【0043】

図9(a)〜(e)は、実施の形態3の効果を示すタイムチャートである。図9(a)に示すように、表示期間においてバースト信号が一定の時間間隔で短時間だけ異常になるものとする。位相誤差信号Ieは、図9(b)に示すように、バースト信号の異常に応答して突発的に異常に変化する。

【0044】

実施の形態1のバーストクロック発生回路では、表示期間における位相ロックフィルタ4の応答速度を比較的速い速度v3(v2<v3≦v1)にすると、図9(c)に示すように、位相誤差信号Ieの突発的な変化に応答して制御電圧VCが変動してしまう。

【0045】

これに対して実施の形態3では、位相誤差信号Ieのうちの突発的な変化分は異常検出回路12によって除去されるので、制御電圧VCが変動しない。このため、安定したバーストクロック信号を得ることができ、良好なカラー画像を表示することができる。

【0046】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0047】

1 水平同期分離回路、2 バースト期間生成回路、3 位相検波回路、4,10 位相ロックフィルタ、5 電圧制御型発振器、6 垂直同期分離回路、7 信号発生回路、8 制御回路、11 同期安定判定回路、12 異常検出回路。

【特許請求の範囲】

【請求項1】

制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、

複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号と前記バーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、

前記位相検波回路の出力信号を積分し、その積分値に基づいて前記制御電圧を生成する、応答速度の変更が可能な制御電圧発生回路と、

前記複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では前記制御電圧発生回路の応答速度を0に設定し、各垂直帰線期間のうちの前記第1の期間を除く第2の期間では前記制御電圧発生回路の応答速度を第1の速度に設定し、前記複合映像信号における垂直帰線期間以外の表示期間では前記制御電圧発生回路の応答速度を前記第1の速度よりも遅い第2の速度に設定する制御回路とを備える、バーストクロック発生回路。

【請求項2】

さらに、前記複合映像信号から水平同期信号を生成する第1の信号発生回路と、

前記水平同期信号から前記バースト期間を示す信号を生成する第2の信号発生回路と、

前記複合映像信号から垂直同期信号を生成する第3の信号発生回路と、

前記水平同期信号と前記垂直同期信号に基いて、前記第1の期間を示す信号と前記第2の期間を示す信号とを生成する第4の信号発生回路とを備え、

前記位相検波回路は、前記バースト期間を示す信号に応答して前記バースト信号と前記バーストクロック信号の位相誤差を検出し、

前記制御回路は、前記第1の期間を示す信号と前記第2の期間を示す信号に応答して、前記制御電圧発生回路の応答速度を0、前記第1の速度、または前記第2の速度に設定する、請求項1に記載のバーストクロック発生回路。

【請求項3】

さらに、前記水平同期信号および前記垂直同期信号のうちの少なくとも一方の同期信号が安定しているか否かを判別する同期安定判定回路を備え、

前記制御回路は、前記同期安定判定回路によって前記少なくとも一方の同期信号が安定していないと判別された場合は、前記制御電圧発生回路の応答速度を前記第2の速度に固定する、請求項2に記載のバーストクロック発生回路。

【請求項4】

さらに、前記位相検波回路と前記制御電圧発生回路の間に設けられ、前記位相誤差を示す信号の変化が正常範囲内か否かを判別し、正常範囲内である場合は前記位相誤差を示す信号を通過させ、正常範囲内でない場合は前記位相誤差を示す信号の通過を禁止する異常検出回路を備える、請求項1から請求項3までのいずれかに記載のバーストクロック発生回路。

【請求項1】

制御電圧に応じた周波数のバーストクロック信号を生成する電圧制御型発振器と、

複合映像信号における各1水平期間のうちのバースト期間に設けられたバースト信号と前記バーストクロック信号との位相誤差を検出し、検出した位相誤差を示す信号を出力する位相検波回路と、

前記位相検波回路の出力信号を積分し、その積分値に基づいて前記制御電圧を生成する、応答速度の変更が可能な制御電圧発生回路と、

前記複合映像信号における各垂直帰線期間のうちの垂直同期期間を含む第1の期間では前記制御電圧発生回路の応答速度を0に設定し、各垂直帰線期間のうちの前記第1の期間を除く第2の期間では前記制御電圧発生回路の応答速度を第1の速度に設定し、前記複合映像信号における垂直帰線期間以外の表示期間では前記制御電圧発生回路の応答速度を前記第1の速度よりも遅い第2の速度に設定する制御回路とを備える、バーストクロック発生回路。

【請求項2】

さらに、前記複合映像信号から水平同期信号を生成する第1の信号発生回路と、

前記水平同期信号から前記バースト期間を示す信号を生成する第2の信号発生回路と、

前記複合映像信号から垂直同期信号を生成する第3の信号発生回路と、

前記水平同期信号と前記垂直同期信号に基いて、前記第1の期間を示す信号と前記第2の期間を示す信号とを生成する第4の信号発生回路とを備え、

前記位相検波回路は、前記バースト期間を示す信号に応答して前記バースト信号と前記バーストクロック信号の位相誤差を検出し、

前記制御回路は、前記第1の期間を示す信号と前記第2の期間を示す信号に応答して、前記制御電圧発生回路の応答速度を0、前記第1の速度、または前記第2の速度に設定する、請求項1に記載のバーストクロック発生回路。

【請求項3】

さらに、前記水平同期信号および前記垂直同期信号のうちの少なくとも一方の同期信号が安定しているか否かを判別する同期安定判定回路を備え、

前記制御回路は、前記同期安定判定回路によって前記少なくとも一方の同期信号が安定していないと判別された場合は、前記制御電圧発生回路の応答速度を前記第2の速度に固定する、請求項2に記載のバーストクロック発生回路。

【請求項4】

さらに、前記位相検波回路と前記制御電圧発生回路の間に設けられ、前記位相誤差を示す信号の変化が正常範囲内か否かを判別し、正常範囲内である場合は前記位相誤差を示す信号を通過させ、正常範囲内でない場合は前記位相誤差を示す信号の通過を禁止する異常検出回路を備える、請求項1から請求項3までのいずれかに記載のバーストクロック発生回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−98635(P2013−98635A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−237472(P2011−237472)

【出願日】平成23年10月28日(2011.10.28)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月28日(2011.10.28)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]