パルスアーク溶接のアーク長制御方法

【課題】消耗電極式パルスアーク溶接において、平均アーク長を短く設定して高速溶接等を行うときのアーク長制御性を向上させる。

【解決手段】本発明は、ピーク電圧及びベース電圧からなる溶接電圧Vwの平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるようにパルス周期を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、ベース期間中に短絡状態Tsになりベース電圧から短絡電圧Vsに変化したときは、この短絡電圧Vsをベース電圧下限値Vbtに制限して上記溶接電圧平均値を算出するアーク長制御方法において、上記ベース電圧下限値Vbtを、短絡期間Tsの時間経過に伴ってより低い値に変化させる。

【解決手段】本発明は、ピーク電圧及びベース電圧からなる溶接電圧Vwの平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるようにパルス周期を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、ベース期間中に短絡状態Tsになりベース電圧から短絡電圧Vsに変化したときは、この短絡電圧Vsをベース電圧下限値Vbtに制限して上記溶接電圧平均値を算出するアーク長制御方法において、上記ベース電圧下限値Vbtを、短絡期間Tsの時間経過に伴ってより低い値に変化させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、短絡期間中の短絡電圧値を制限することによってアーク長制御性を向上させることができるパルスアーク溶接のアーク長制御方法に関するものである。

【背景技術】

【0002】

消耗電極式アーク溶接において、良好な溶接品質を得るためには、溶接中のアーク長を適正値に維持する必要がある。ピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電する消耗電極式パルスアーク溶接においては、溶接電圧平均値が予め定めた電圧設定値と略等しくなるようにパルス周期等を制御してアーク長を適正値に維持するアーク長制御方法が従来から使用されている。以下、この従来技術のパルスアーク溶接のアーク長制御方法について説明する。

【0003】

図4は、パルスアーク溶接の電流・電圧波形図である。同図(A)は消耗電極である溶接ワイヤを通電する溶接電流Iwの時間変化を示し、同図(B)は給電チップ・母材間に印加する溶接電圧Vwの時間変化を示す。以下、同図を参照して説明する。

【0004】

同図(A)に示すように、時刻t1〜t2のピーク期間Tp中は、溶滴移行させるための大電流値のピーク電流Ipが通電し、同図(B)に示すように、アーク長に略比例したピーク電圧Vpが給電チップ・母材間に印加する。続いて,同図(A)に示すように、時刻t2〜t3のベース期間Tb中は、アークを維持しつつ溶滴を成長させないための小電流値のベース電流Ibが通電し、同図(B)に示すように、アーク長に略比例したベース電圧Vbが印加する。以下の説明において、ピーク電圧Vp及びベース電圧Vbは、アーク発生中の電圧値を示し、短絡期間中は短絡電圧と表記して区別する。

【0005】

溶接品質は、ピーク期間Tp及びベース期間Tbからなるパルス周期Tf中の平均アーク長に大きく影響される。したがって、良好な溶接品質を得るためには、平均アーク長を適正値に制御する必要がある。一般的に、瞬時瞬時のアーク長は、ピーク電圧Vp及びベース電圧Vbからなる溶接電圧Vwに略比例する。したがって、平均アーク長は、溶接電圧平均値Vaと略比例することになる。この関係を利用して、溶接電圧平均値Vaを検出し、この検出値が予め定めた電圧設定値Vrと略等しくなるように溶接電圧Vwを制御する。この溶接電圧Vwの制御方法としては、同図に示すように、パルス周期Tf、ピーク期間Tp、ピーク電流Ip又はベース電流Ibの少なくとも1つ以上の値をフィードバック制御によって変化させる方法が従来から慣用されている。

【0006】

上述したように、従来技術では、溶接電圧Vwを検出し、この溶接電圧検出値から溶接電圧平均値Vaを算出してアーク長を制御する。しかしながら、図5で後述するように、パルスアーク溶接では溶滴移行に伴って短時間の短絡が発生することが多い。通常、溶滴移行はピーク期間Tp終了後のベース期間Tb中に行われることが多いために、短絡はベース期間Tb中にほとんど発生する。この短絡期間Ts中の短絡電圧Vsを含めて溶接電圧平均値Vaが算出させるために、溶接電圧平均値Vaと平均アーク長との間に誤差が生じる。このために、アーク長制御性が悪くなるという問題があった。この問題を解決するために、以下に説明する従来技術が提案されている。

【0007】

図5は、短絡が発生したときの従来技術のアーク長制御方法を示す波形図である。同図(A)は溶接電圧Vwの、同図(B)は溶接電圧制限値Vfの、同図(C)はアーク長Laの時間変化を示し、同図(D)〜(F)は各時刻におけるアーク発生部の様子を示す。以下、同図を参照して説明する。

【0008】

同図(A)に示すように、ベース期間中の時刻t4において溶滴が移行する際に、時刻t4〜t5の期間(短絡期間Ts)中短時間の短絡が発生する。この短絡期間Ts中の溶接電圧Vwはベース電圧Vbから短絡電圧Vsに変化する。ベース電圧Vbは15〜25V程度であり、短絡電圧Vsは数V程度である。

【0009】

同図(C)に示すように、アーク長Laは、時刻t1〜t2のピーク期間中は次第に長くなる。これは、同図(D)に示すように、ピーク電流の通電によって溶接ワイヤ1先端が溶融されて溶滴1aが形成されるためである。続く時刻t2〜t3のピーク立下り期間からベース期間にかけての期間中のアーク長Laは、次第に短くなる。これは、溶滴1aの上部にくびれ1bが発生して溶滴1aが下方へ移動するのでアーク長Laが短くなるためである。続く時刻t3〜t4の期間中は、溶滴1aが重力によって急速に落下してくびれ部1bが細く伸びるために、アーク長Laは急速に短くなる。そして、時刻t4において、同図(E)に示すように、くびれ部1bが細く伸びた状態で溶滴1aが母材2と接触して短絡状態となる。時刻t5において溶滴1aが溶融池の表面張力によって移行すると、同図(F)に示すように、アーク3が再発生し、同図(C)に示すように、アーク長Laは長くなる。続く時刻t5〜t6の期間中は、ベース電流が溶接ワイヤ1を溶融しない低い値であるために、ワイヤ先端には溶滴1aは形成されずに溶接ワイヤ1が定速送給されるので、同図(C)に示すように、アーク長Laは次第に短くなる。上述した動作によって時刻t1〜t6のパルス周期中の平均アーク長が適正値になるように制御される。

【0010】

同図(E)に示すように、時刻t4において短絡が発生したときはくびれ部1bが細く伸びた状態にある。ワイヤ先端の溶融部と母材間の距離を実質的なアーク長Lbと定義すると、同図(D)〜(F)に示すように、なだらかに短くなる。この実質的なアーク長Lbは、同図(C)に示すように、時刻t2〜t5にかけてなだらかに低下する。特に、時刻t3〜t4にかけてのアーク長Laの急激な変化は、くびれ部1bが伸びて短絡することに起因しており、溶接品質を決める平均アーク長には実質的なアーク長Lbを使用する方がよい。このために、従来技術では、時刻t4〜t5の短絡期間Ts中の実質的なアーク長Lbを検出するために、同図(B)に示すように、短絡電圧Vsをベース電圧下限値Vbtに制限して溶接電圧制限値Vfを算出している。すなわち、溶接電圧制限値Vfは、同図(A)に示す溶接電圧Vwに対して短絡期間Tsの短絡電圧Vsをベース電圧下限値Vbtに制限し、それ以外の期間の電圧はそのままとしたものである。この溶接電圧制限値Vfを使用して溶接電圧平均値Vaを算出しアーク長制御を行うことによって、同図(C)に示す実質的なアーク長Lbを含む平均アーク長を適正値に維持することができる。

【0011】

上記のベース電圧下限値Vbtは、ベース電圧基準値Vbc及び予め定めた修正値ΔVを入力として、Vbt=Vbc−ΔVによって設定される。修正値ΔVは1〜3V程度であり、溶接ワイヤの材質、ワイヤ送給速度等の溶接条件に応じて適正値に設定する。上記のベース電圧基準値Vbcは、溶接条件に応じて予め定めた値でもよいし、短絡発生直前のベース電圧値でもよい。さらに、ベース電圧基準値Vbcは、所定期間にわたるベース電圧の移動平均値でもよい。(上述した従来技術については特許文献1、2を参照)

【0012】

【特許文献1】特開2003−311409号公報

【特許文献2】特開2005−34853号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

図6は、高速溶接等において平均アーク長を短く設定したときの図5に対応する波形図である。同図(A)〜(F)に示す各信号は図5と同一である。平均アーク長が図5に比べて短いために、同図(A)に示す溶接電圧Vw及び同図(B)に示す溶接電圧制限値Vfの瞬時値は低くなる。また、同図(C)に示すアーク長Laの瞬時値も短くなる。

【0014】

平均アーク長が短くなると、同図(A)に示すように、短絡期間Tsが長くなる傾向にある。この短絡期間Ts中は、同図(B)に示すように、短絡電圧Vsはベース電圧下限値Vbtに制限される。これは、同図(C)に示すように、実質的なアーク長Lbを検出してアーク長制御性を向上させるためであった。

【0015】

平均アーク長の設定が短くなると、瞬時的なアーク長が短くなり、溶滴移行と関係のない短絡が発生してスパッタが多く発生したり溶接状態が不安定になったりしやすい。このために、アーク長をより高精度に制御する必要がある。この1つの方法としてフィードバック制御系の増幅率を高くする方法がある。しかし、この方法では、フィードバック制御系が不安定になりやすいために限界があった。

【0016】

そこで、本発明では、平均アーク長を短く設定したときにアーク長制御性を向上させることができるパルスアーク溶接のアーク長制御方法を提供する。

【課題を解決するための手段】

【0017】

上述した課題を解決するために、第1の発明は、溶接ワイヤにピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電すると共に、前記ピーク期間中のピーク電圧及び前記ベース期間中のベース電圧からなる溶接電圧の平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるように前記パルス周期又は前記ピーク期間又は前記ピーク電流又は前記ベース電流の少なくとも1つ以上を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、

前記ベース期間中に溶接ワイヤと母材とが短絡状態になり前記ベース電圧から短絡電圧に変化したときはこの短絡電圧を前記ベース電圧値よりも所定値だけ低い値であるベース電圧下限値に制限して前記溶接電圧平均値を算出するパルスアーク溶接のアーク長制御方法において、

前記ベース電圧下限値を前記短絡期間の時間経過に伴ってより低い値に変化させる、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0018】

また、第2の発明は、第1の発明記載のベース電圧下限値の変化がステップ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0019】

また、第3の発明は、第1の発明記載のベース電圧下限値の変化がスロ−プ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0020】

また、第4の発明は、第1〜第3の発明のいずれかに記載のベース電圧下限値の変化に最大下限値の制限を設けた、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【発明の効果】

【0021】

本発明によれば、短絡期間Tsの経過時間に伴ってベース電圧下限値Vbtをより低い値にステップ状又はスロープ状に変化させることによって、溶接電圧Vwによるアーク長の検出に短絡期間長さによるアーク長の検出を加味することができる。このために、平均アーク長を短く設定して比較的長い短絡が発生する高速溶接等において、アーク長を高精度に検出することができ、アーク長制御性が向上する。

【発明を実施するための最良の形態】

【0022】

以下、図面を参照して本発明の実施の形態について説明する。

【0023】

[実施の形態1]

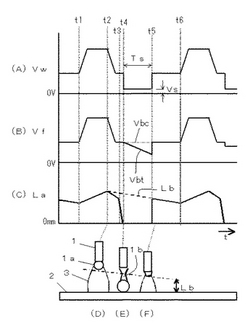

図1は、本発明の実施の形態1に係るパルスアーク溶接のアーク長制御方法を示す波形図である。同図(A)は溶接電圧Vwの、同図(B)は溶接電圧制限値Vfの、同図(C)はアーク長Laの時間変化を示し、同図(D)〜(F)は各時刻におけるアーク発生部の様子を示す。同図は、上述した図6と対応しており、平均アーク長を短く設定した場合である。同図において、時刻t4〜t5の短絡期間Ts以外の期間の動作は、上述した図5及び図6と同一であるので説明は省略する。以下、短絡期間Tsの動作について説明する。

【0024】

実施の形態1では、同図(B)に示すように、短絡期間Ts中の時間経過に伴ってベース電圧下限値Vbtの値を次第に低くする。この低下させる傾斜S[V/ms]は、0.3〜3程度の範囲であり、溶接ワイヤの材質、ワイヤ送給速度等の溶接条件に応じて適正値に設定される。このようにベース電圧下限値Vbtを低下させる理由は、以下のとおりである。すなわち、平均アーク長が低くなると、溶滴移行に伴う短絡期間Tsの時間長さが略比例して長くなる傾向にある。そこで、平均アーク長を溶接電圧平均値によって検出するときに、短絡期間Tsの長さに応じてベース電圧下限値Vbtを低下させれば短絡期間長さと平均アーク長との比例関係の情報を内包させることができる。これにより、平均アーク長をピーク電圧及びベース電圧に加えて短絡期間長さによって高精度に検出することができる。この結果、平均アーク長が短く設定された場合でも、アーク長制御性を向上させることができる。

【0025】

図2は、実施の形態1に係るパルスアーク溶接のアーク長制御方法を実施するための溶接電源のブロック図である。電源主回路PMは、3相200V等の商用電源を入力として、後述する電流誤差増幅信号Eiに従ってインバータ制御、チョッパ制御等の出力制御を行い、溶接電流Iw及び溶接電圧Vwを出力する。溶接ワイヤ1はワイヤ送給装置の送給ロール5の回転によって溶接トーチ4内を通って送給されて、母材2との間でアーク3が発生する。

【0026】

電圧検出回路VDは、溶接電圧Vwを検出して、電圧検出信号Vdを出力する。ベース電圧基準値算出回路VBCは、この電圧検出信号Vdを入力して、所定期間にわたるベース電圧の移動平均値を算出し、ベース電圧基準値信号Vbcとして出力する。このベース電圧基準値信号Vbcは、上述したように、予め定めた値でもよいし、短絡発生直前のベース電圧値でもよい。短絡期間検出回路TSは、上記の電圧検出信号Vdの値によって短絡の発生を検出し短絡期間中Highレベルになる短絡期間信号Tsを出力する。ベース電圧下限値算出回路VBTは、上記のベース電圧基準値信号Vbc及び上記の短絡期間信号Tsを入力として、短絡期間の時間経過に伴ってベース電圧基準値信号Vbcの値からより低い値に変化するベース電圧下限値信号Vbtを出力する。電圧制限値算出回路VFは、上記の電圧検出信号Vd及び上記のベース電圧下限値信号Vbtを入力として、短絡期間中の電圧をベース電圧下限値に制限して、電圧制限値信号Vfを出力する。電圧平均値算出回路VAは、この電圧制限値信号Vfの平均値を算出して、電圧平均値信号Vaを出力する。

【0027】

電圧設定回路VRは、予め定めた電圧設定信号Vrを出力する。電圧誤差増幅回路EVは、この電圧設定信号Vrと上記の電圧平均値信号Vaとの誤差を増幅して、電圧誤差増幅信号Evを出力する。電圧・周波数変換回路V/Fは、この電圧誤差増幅信号Evに比例した周波数のパルス周期信号Tfを出力する。すなわち、電圧設定信号Vrと電圧平均値信号Vaとが略等しくなるように図4で上述したパルス周期Tfが変化する。ピーク期間タイマ回路TPは、上記のパルス周期信号Tfの毎周期の開始時点から予め定めたピーク期間中Highレベルになるピーク期間信号Tpを出力する。すなわち、このピーク期間信号TpがHighレベルのときはピーク期間となり、Lowレベルのときはベース期間となる。

【0028】

ピーク電流設定回路IPRは、予め定めたピーク電流設定信号Iprを出力する。ベース電流設定回路IBRは、予め定めたベース電流設定信号Ibrを出力する。電流制御設定回路ICRは、上記のピーク期間信号TpがHighレベルのときは上記のピーク電流設定信号Iprを電流制御設定信号Icrとして出力し、Lowレベルのときは上記のベース電流設定信号Ibrを電流制御設定信号Icrとして出力する。電流検出回路IDは、溶接電流Iwを検出して、電流検出信号Idを出力する。電流誤差増幅回路EIは、上記の電流制御設定信号Icrと上記の電流検出信号Idとの誤差を増幅して、電流誤差増幅信号Eiを出力する。図2はフィードバック制御によってパルス周期Tfを変化させる場合であるが、上記の電圧誤差増幅信号Evによって、ピーク期間、ピーク電流、ベース電流又はそれらの組合せを変化させてもよい。

【0029】

[実施の形態2]

図3は、短絡期間の時間経過に伴うベース電圧下限値Vbtの変化パターンを示す図である。同図の横軸は短絡期間Tsの開始時点からの経過時間を示し、縦軸はベース電圧下限値Vbtの値を示す。同図に示すように、特性L1はベース電圧基準値Vbcからステップ状に低下させている。この場合、数msごとに数Vずつ低下させる。また、特性L2はスロープ状に低下させており、最大下限値Vbmを設けて、この値よりも低下しないようにしている。この最大下限値Vbmは、4〜15V程度であり、溶接条件に応じて適正値を選択する。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態1に係るパルスアーク溶接のアーク長制御方法を示す波形図である。

【図2】本発明の実施の形態1に係る溶接電源のブロック図である。

【図3】本発明の実施の形態2に係る短絡期間Tsの時間経過に対するベース電圧下限値Vbtの変化パターンを示す図である。

【図4】従来技術における消耗電極式パルスアーク溶接の電流・電圧波形図である。

【図5】従来技術におけるパルスアーク溶接のアーク長制御方法を示す波形図である。

【図6】従来技術の課題を説明するための図5において平均アーク長を短く設定したときの波形図である。

【符号の説明】

【0031】

1 溶接ワイヤ

1a 溶滴

1b くびれ部

2 母材

3 アーク

4 溶接トーチ

5 送給ロール

EI 電流誤差増幅回路

Ei 電流誤差増幅信号

EV 電圧誤差増幅回路

Ev 電圧誤差増幅信号

Ib ベース電流

IBR ベース電流設定回路

Ibr ベース電流設定信号

ICR 電流制御設定回路

Icr 電流制御設定信号

ID 電流検出回路

Id 電流検出信号

Ip ピーク電流

IPR ピーク電流設定回路

Ipr ピーク電流設定信号

Iw 溶接電流

L1 特性

L2 特性

La アーク長

Lb 実質的なアーク長

PM 電源主回路

S 傾斜

Tb ベース期間

Tf パルス周期(信号)

TP ピーク期間タイマ回路

Tp ピーク期間(信号)

TS 短絡期間検出回路

Ts 短絡期間(信号)

V/F 電圧・周波数変換回路

VA 電圧平均値算出回路

Va 溶接電圧平均値/電圧平均値信号

Vb ベース電圧

VBC ベース電圧基準値算出回路

Vbc ベース電圧基準値(信号)

Vbm 最大下限値

VBT ベース電圧下限値算出回路

Vbt ベース電圧下限値(信号)

VD 電圧検出回路

Vd 電圧検出信号

VF 電圧制限値算出回路

Vf 溶接電圧制限値/電圧制限値信号

Vp ピーク電圧

VR 電圧設定回路

Vr 電圧設定(値/信号)

Vs 短絡電圧

Vw 溶接電圧

ΔV 修正値

【技術分野】

【0001】

本発明は、短絡期間中の短絡電圧値を制限することによってアーク長制御性を向上させることができるパルスアーク溶接のアーク長制御方法に関するものである。

【背景技術】

【0002】

消耗電極式アーク溶接において、良好な溶接品質を得るためには、溶接中のアーク長を適正値に維持する必要がある。ピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電する消耗電極式パルスアーク溶接においては、溶接電圧平均値が予め定めた電圧設定値と略等しくなるようにパルス周期等を制御してアーク長を適正値に維持するアーク長制御方法が従来から使用されている。以下、この従来技術のパルスアーク溶接のアーク長制御方法について説明する。

【0003】

図4は、パルスアーク溶接の電流・電圧波形図である。同図(A)は消耗電極である溶接ワイヤを通電する溶接電流Iwの時間変化を示し、同図(B)は給電チップ・母材間に印加する溶接電圧Vwの時間変化を示す。以下、同図を参照して説明する。

【0004】

同図(A)に示すように、時刻t1〜t2のピーク期間Tp中は、溶滴移行させるための大電流値のピーク電流Ipが通電し、同図(B)に示すように、アーク長に略比例したピーク電圧Vpが給電チップ・母材間に印加する。続いて,同図(A)に示すように、時刻t2〜t3のベース期間Tb中は、アークを維持しつつ溶滴を成長させないための小電流値のベース電流Ibが通電し、同図(B)に示すように、アーク長に略比例したベース電圧Vbが印加する。以下の説明において、ピーク電圧Vp及びベース電圧Vbは、アーク発生中の電圧値を示し、短絡期間中は短絡電圧と表記して区別する。

【0005】

溶接品質は、ピーク期間Tp及びベース期間Tbからなるパルス周期Tf中の平均アーク長に大きく影響される。したがって、良好な溶接品質を得るためには、平均アーク長を適正値に制御する必要がある。一般的に、瞬時瞬時のアーク長は、ピーク電圧Vp及びベース電圧Vbからなる溶接電圧Vwに略比例する。したがって、平均アーク長は、溶接電圧平均値Vaと略比例することになる。この関係を利用して、溶接電圧平均値Vaを検出し、この検出値が予め定めた電圧設定値Vrと略等しくなるように溶接電圧Vwを制御する。この溶接電圧Vwの制御方法としては、同図に示すように、パルス周期Tf、ピーク期間Tp、ピーク電流Ip又はベース電流Ibの少なくとも1つ以上の値をフィードバック制御によって変化させる方法が従来から慣用されている。

【0006】

上述したように、従来技術では、溶接電圧Vwを検出し、この溶接電圧検出値から溶接電圧平均値Vaを算出してアーク長を制御する。しかしながら、図5で後述するように、パルスアーク溶接では溶滴移行に伴って短時間の短絡が発生することが多い。通常、溶滴移行はピーク期間Tp終了後のベース期間Tb中に行われることが多いために、短絡はベース期間Tb中にほとんど発生する。この短絡期間Ts中の短絡電圧Vsを含めて溶接電圧平均値Vaが算出させるために、溶接電圧平均値Vaと平均アーク長との間に誤差が生じる。このために、アーク長制御性が悪くなるという問題があった。この問題を解決するために、以下に説明する従来技術が提案されている。

【0007】

図5は、短絡が発生したときの従来技術のアーク長制御方法を示す波形図である。同図(A)は溶接電圧Vwの、同図(B)は溶接電圧制限値Vfの、同図(C)はアーク長Laの時間変化を示し、同図(D)〜(F)は各時刻におけるアーク発生部の様子を示す。以下、同図を参照して説明する。

【0008】

同図(A)に示すように、ベース期間中の時刻t4において溶滴が移行する際に、時刻t4〜t5の期間(短絡期間Ts)中短時間の短絡が発生する。この短絡期間Ts中の溶接電圧Vwはベース電圧Vbから短絡電圧Vsに変化する。ベース電圧Vbは15〜25V程度であり、短絡電圧Vsは数V程度である。

【0009】

同図(C)に示すように、アーク長Laは、時刻t1〜t2のピーク期間中は次第に長くなる。これは、同図(D)に示すように、ピーク電流の通電によって溶接ワイヤ1先端が溶融されて溶滴1aが形成されるためである。続く時刻t2〜t3のピーク立下り期間からベース期間にかけての期間中のアーク長Laは、次第に短くなる。これは、溶滴1aの上部にくびれ1bが発生して溶滴1aが下方へ移動するのでアーク長Laが短くなるためである。続く時刻t3〜t4の期間中は、溶滴1aが重力によって急速に落下してくびれ部1bが細く伸びるために、アーク長Laは急速に短くなる。そして、時刻t4において、同図(E)に示すように、くびれ部1bが細く伸びた状態で溶滴1aが母材2と接触して短絡状態となる。時刻t5において溶滴1aが溶融池の表面張力によって移行すると、同図(F)に示すように、アーク3が再発生し、同図(C)に示すように、アーク長Laは長くなる。続く時刻t5〜t6の期間中は、ベース電流が溶接ワイヤ1を溶融しない低い値であるために、ワイヤ先端には溶滴1aは形成されずに溶接ワイヤ1が定速送給されるので、同図(C)に示すように、アーク長Laは次第に短くなる。上述した動作によって時刻t1〜t6のパルス周期中の平均アーク長が適正値になるように制御される。

【0010】

同図(E)に示すように、時刻t4において短絡が発生したときはくびれ部1bが細く伸びた状態にある。ワイヤ先端の溶融部と母材間の距離を実質的なアーク長Lbと定義すると、同図(D)〜(F)に示すように、なだらかに短くなる。この実質的なアーク長Lbは、同図(C)に示すように、時刻t2〜t5にかけてなだらかに低下する。特に、時刻t3〜t4にかけてのアーク長Laの急激な変化は、くびれ部1bが伸びて短絡することに起因しており、溶接品質を決める平均アーク長には実質的なアーク長Lbを使用する方がよい。このために、従来技術では、時刻t4〜t5の短絡期間Ts中の実質的なアーク長Lbを検出するために、同図(B)に示すように、短絡電圧Vsをベース電圧下限値Vbtに制限して溶接電圧制限値Vfを算出している。すなわち、溶接電圧制限値Vfは、同図(A)に示す溶接電圧Vwに対して短絡期間Tsの短絡電圧Vsをベース電圧下限値Vbtに制限し、それ以外の期間の電圧はそのままとしたものである。この溶接電圧制限値Vfを使用して溶接電圧平均値Vaを算出しアーク長制御を行うことによって、同図(C)に示す実質的なアーク長Lbを含む平均アーク長を適正値に維持することができる。

【0011】

上記のベース電圧下限値Vbtは、ベース電圧基準値Vbc及び予め定めた修正値ΔVを入力として、Vbt=Vbc−ΔVによって設定される。修正値ΔVは1〜3V程度であり、溶接ワイヤの材質、ワイヤ送給速度等の溶接条件に応じて適正値に設定する。上記のベース電圧基準値Vbcは、溶接条件に応じて予め定めた値でもよいし、短絡発生直前のベース電圧値でもよい。さらに、ベース電圧基準値Vbcは、所定期間にわたるベース電圧の移動平均値でもよい。(上述した従来技術については特許文献1、2を参照)

【0012】

【特許文献1】特開2003−311409号公報

【特許文献2】特開2005−34853号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

図6は、高速溶接等において平均アーク長を短く設定したときの図5に対応する波形図である。同図(A)〜(F)に示す各信号は図5と同一である。平均アーク長が図5に比べて短いために、同図(A)に示す溶接電圧Vw及び同図(B)に示す溶接電圧制限値Vfの瞬時値は低くなる。また、同図(C)に示すアーク長Laの瞬時値も短くなる。

【0014】

平均アーク長が短くなると、同図(A)に示すように、短絡期間Tsが長くなる傾向にある。この短絡期間Ts中は、同図(B)に示すように、短絡電圧Vsはベース電圧下限値Vbtに制限される。これは、同図(C)に示すように、実質的なアーク長Lbを検出してアーク長制御性を向上させるためであった。

【0015】

平均アーク長の設定が短くなると、瞬時的なアーク長が短くなり、溶滴移行と関係のない短絡が発生してスパッタが多く発生したり溶接状態が不安定になったりしやすい。このために、アーク長をより高精度に制御する必要がある。この1つの方法としてフィードバック制御系の増幅率を高くする方法がある。しかし、この方法では、フィードバック制御系が不安定になりやすいために限界があった。

【0016】

そこで、本発明では、平均アーク長を短く設定したときにアーク長制御性を向上させることができるパルスアーク溶接のアーク長制御方法を提供する。

【課題を解決するための手段】

【0017】

上述した課題を解決するために、第1の発明は、溶接ワイヤにピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電すると共に、前記ピーク期間中のピーク電圧及び前記ベース期間中のベース電圧からなる溶接電圧の平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるように前記パルス周期又は前記ピーク期間又は前記ピーク電流又は前記ベース電流の少なくとも1つ以上を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、

前記ベース期間中に溶接ワイヤと母材とが短絡状態になり前記ベース電圧から短絡電圧に変化したときはこの短絡電圧を前記ベース電圧値よりも所定値だけ低い値であるベース電圧下限値に制限して前記溶接電圧平均値を算出するパルスアーク溶接のアーク長制御方法において、

前記ベース電圧下限値を前記短絡期間の時間経過に伴ってより低い値に変化させる、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0018】

また、第2の発明は、第1の発明記載のベース電圧下限値の変化がステップ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0019】

また、第3の発明は、第1の発明記載のベース電圧下限値の変化がスロ−プ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【0020】

また、第4の発明は、第1〜第3の発明のいずれかに記載のベース電圧下限値の変化に最大下限値の制限を設けた、ことを特徴とするパルスアーク溶接のアーク長制御方法である。

【発明の効果】

【0021】

本発明によれば、短絡期間Tsの経過時間に伴ってベース電圧下限値Vbtをより低い値にステップ状又はスロープ状に変化させることによって、溶接電圧Vwによるアーク長の検出に短絡期間長さによるアーク長の検出を加味することができる。このために、平均アーク長を短く設定して比較的長い短絡が発生する高速溶接等において、アーク長を高精度に検出することができ、アーク長制御性が向上する。

【発明を実施するための最良の形態】

【0022】

以下、図面を参照して本発明の実施の形態について説明する。

【0023】

[実施の形態1]

図1は、本発明の実施の形態1に係るパルスアーク溶接のアーク長制御方法を示す波形図である。同図(A)は溶接電圧Vwの、同図(B)は溶接電圧制限値Vfの、同図(C)はアーク長Laの時間変化を示し、同図(D)〜(F)は各時刻におけるアーク発生部の様子を示す。同図は、上述した図6と対応しており、平均アーク長を短く設定した場合である。同図において、時刻t4〜t5の短絡期間Ts以外の期間の動作は、上述した図5及び図6と同一であるので説明は省略する。以下、短絡期間Tsの動作について説明する。

【0024】

実施の形態1では、同図(B)に示すように、短絡期間Ts中の時間経過に伴ってベース電圧下限値Vbtの値を次第に低くする。この低下させる傾斜S[V/ms]は、0.3〜3程度の範囲であり、溶接ワイヤの材質、ワイヤ送給速度等の溶接条件に応じて適正値に設定される。このようにベース電圧下限値Vbtを低下させる理由は、以下のとおりである。すなわち、平均アーク長が低くなると、溶滴移行に伴う短絡期間Tsの時間長さが略比例して長くなる傾向にある。そこで、平均アーク長を溶接電圧平均値によって検出するときに、短絡期間Tsの長さに応じてベース電圧下限値Vbtを低下させれば短絡期間長さと平均アーク長との比例関係の情報を内包させることができる。これにより、平均アーク長をピーク電圧及びベース電圧に加えて短絡期間長さによって高精度に検出することができる。この結果、平均アーク長が短く設定された場合でも、アーク長制御性を向上させることができる。

【0025】

図2は、実施の形態1に係るパルスアーク溶接のアーク長制御方法を実施するための溶接電源のブロック図である。電源主回路PMは、3相200V等の商用電源を入力として、後述する電流誤差増幅信号Eiに従ってインバータ制御、チョッパ制御等の出力制御を行い、溶接電流Iw及び溶接電圧Vwを出力する。溶接ワイヤ1はワイヤ送給装置の送給ロール5の回転によって溶接トーチ4内を通って送給されて、母材2との間でアーク3が発生する。

【0026】

電圧検出回路VDは、溶接電圧Vwを検出して、電圧検出信号Vdを出力する。ベース電圧基準値算出回路VBCは、この電圧検出信号Vdを入力して、所定期間にわたるベース電圧の移動平均値を算出し、ベース電圧基準値信号Vbcとして出力する。このベース電圧基準値信号Vbcは、上述したように、予め定めた値でもよいし、短絡発生直前のベース電圧値でもよい。短絡期間検出回路TSは、上記の電圧検出信号Vdの値によって短絡の発生を検出し短絡期間中Highレベルになる短絡期間信号Tsを出力する。ベース電圧下限値算出回路VBTは、上記のベース電圧基準値信号Vbc及び上記の短絡期間信号Tsを入力として、短絡期間の時間経過に伴ってベース電圧基準値信号Vbcの値からより低い値に変化するベース電圧下限値信号Vbtを出力する。電圧制限値算出回路VFは、上記の電圧検出信号Vd及び上記のベース電圧下限値信号Vbtを入力として、短絡期間中の電圧をベース電圧下限値に制限して、電圧制限値信号Vfを出力する。電圧平均値算出回路VAは、この電圧制限値信号Vfの平均値を算出して、電圧平均値信号Vaを出力する。

【0027】

電圧設定回路VRは、予め定めた電圧設定信号Vrを出力する。電圧誤差増幅回路EVは、この電圧設定信号Vrと上記の電圧平均値信号Vaとの誤差を増幅して、電圧誤差増幅信号Evを出力する。電圧・周波数変換回路V/Fは、この電圧誤差増幅信号Evに比例した周波数のパルス周期信号Tfを出力する。すなわち、電圧設定信号Vrと電圧平均値信号Vaとが略等しくなるように図4で上述したパルス周期Tfが変化する。ピーク期間タイマ回路TPは、上記のパルス周期信号Tfの毎周期の開始時点から予め定めたピーク期間中Highレベルになるピーク期間信号Tpを出力する。すなわち、このピーク期間信号TpがHighレベルのときはピーク期間となり、Lowレベルのときはベース期間となる。

【0028】

ピーク電流設定回路IPRは、予め定めたピーク電流設定信号Iprを出力する。ベース電流設定回路IBRは、予め定めたベース電流設定信号Ibrを出力する。電流制御設定回路ICRは、上記のピーク期間信号TpがHighレベルのときは上記のピーク電流設定信号Iprを電流制御設定信号Icrとして出力し、Lowレベルのときは上記のベース電流設定信号Ibrを電流制御設定信号Icrとして出力する。電流検出回路IDは、溶接電流Iwを検出して、電流検出信号Idを出力する。電流誤差増幅回路EIは、上記の電流制御設定信号Icrと上記の電流検出信号Idとの誤差を増幅して、電流誤差増幅信号Eiを出力する。図2はフィードバック制御によってパルス周期Tfを変化させる場合であるが、上記の電圧誤差増幅信号Evによって、ピーク期間、ピーク電流、ベース電流又はそれらの組合せを変化させてもよい。

【0029】

[実施の形態2]

図3は、短絡期間の時間経過に伴うベース電圧下限値Vbtの変化パターンを示す図である。同図の横軸は短絡期間Tsの開始時点からの経過時間を示し、縦軸はベース電圧下限値Vbtの値を示す。同図に示すように、特性L1はベース電圧基準値Vbcからステップ状に低下させている。この場合、数msごとに数Vずつ低下させる。また、特性L2はスロープ状に低下させており、最大下限値Vbmを設けて、この値よりも低下しないようにしている。この最大下限値Vbmは、4〜15V程度であり、溶接条件に応じて適正値を選択する。

【図面の簡単な説明】

【0030】

【図1】本発明の実施の形態1に係るパルスアーク溶接のアーク長制御方法を示す波形図である。

【図2】本発明の実施の形態1に係る溶接電源のブロック図である。

【図3】本発明の実施の形態2に係る短絡期間Tsの時間経過に対するベース電圧下限値Vbtの変化パターンを示す図である。

【図4】従来技術における消耗電極式パルスアーク溶接の電流・電圧波形図である。

【図5】従来技術におけるパルスアーク溶接のアーク長制御方法を示す波形図である。

【図6】従来技術の課題を説明するための図5において平均アーク長を短く設定したときの波形図である。

【符号の説明】

【0031】

1 溶接ワイヤ

1a 溶滴

1b くびれ部

2 母材

3 アーク

4 溶接トーチ

5 送給ロール

EI 電流誤差増幅回路

Ei 電流誤差増幅信号

EV 電圧誤差増幅回路

Ev 電圧誤差増幅信号

Ib ベース電流

IBR ベース電流設定回路

Ibr ベース電流設定信号

ICR 電流制御設定回路

Icr 電流制御設定信号

ID 電流検出回路

Id 電流検出信号

Ip ピーク電流

IPR ピーク電流設定回路

Ipr ピーク電流設定信号

Iw 溶接電流

L1 特性

L2 特性

La アーク長

Lb 実質的なアーク長

PM 電源主回路

S 傾斜

Tb ベース期間

Tf パルス周期(信号)

TP ピーク期間タイマ回路

Tp ピーク期間(信号)

TS 短絡期間検出回路

Ts 短絡期間(信号)

V/F 電圧・周波数変換回路

VA 電圧平均値算出回路

Va 溶接電圧平均値/電圧平均値信号

Vb ベース電圧

VBC ベース電圧基準値算出回路

Vbc ベース電圧基準値(信号)

Vbm 最大下限値

VBT ベース電圧下限値算出回路

Vbt ベース電圧下限値(信号)

VD 電圧検出回路

Vd 電圧検出信号

VF 電圧制限値算出回路

Vf 溶接電圧制限値/電圧制限値信号

Vp ピーク電圧

VR 電圧設定回路

Vr 電圧設定(値/信号)

Vs 短絡電圧

Vw 溶接電圧

ΔV 修正値

【特許請求の範囲】

【請求項1】

溶接ワイヤにピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電すると共に、前記ピーク期間中のピーク電圧及び前記ベース期間中のベース電圧からなる溶接電圧の平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるように前記パルス周期又は前記ピーク期間又は前記ピーク電流又は前記ベース電流の少なくとも1つ以上を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、

前記ベース期間中に溶接ワイヤと母材とが短絡状態になり前記ベース電圧から短絡電圧に変化したときはこの短絡電圧を前記ベース電圧値よりも所定値だけ低い値であるベース電圧下限値に制限して前記溶接電圧平均値を算出するパルスアーク溶接のアーク長制御方法において、

前記ベース電圧下限値を前記短絡期間の時間経過に伴ってより低い値に変化させる、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項2】

請求項1記載のベース電圧下限値の変化がステップ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項3】

請求項1記載のベース電圧下限値の変化がスロ−プ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項4】

請求項1〜3のいずれか1項に記載のベース電圧下限値の変化に最大下限値の制限を設けた、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項1】

溶接ワイヤにピーク期間中のピーク電流の通電とベース期間中のベース電流の通電とを1パルス周期として繰り返して通電すると共に、前記ピーク期間中のピーク電圧及び前記ベース期間中のベース電圧からなる溶接電圧の平均値を算出し,この溶接電圧平均値が予め定めた電圧設定値と略等しくなるように前記パルス周期又は前記ピーク期間又は前記ピーク電流又は前記ベース電流の少なくとも1つ以上を制御してアーク長を適正値に維持するパルスアーク溶接のアーク長制御方法であって、

前記ベース期間中に溶接ワイヤと母材とが短絡状態になり前記ベース電圧から短絡電圧に変化したときはこの短絡電圧を前記ベース電圧値よりも所定値だけ低い値であるベース電圧下限値に制限して前記溶接電圧平均値を算出するパルスアーク溶接のアーク長制御方法において、

前記ベース電圧下限値を前記短絡期間の時間経過に伴ってより低い値に変化させる、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項2】

請求項1記載のベース電圧下限値の変化がステップ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項3】

請求項1記載のベース電圧下限値の変化がスロ−プ状である、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【請求項4】

請求項1〜3のいずれか1項に記載のベース電圧下限値の変化に最大下限値の制限を設けた、ことを特徴とするパルスアーク溶接のアーク長制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−263757(P2006−263757A)

【公開日】平成18年10月5日(2006.10.5)

【国際特許分類】

【出願番号】特願2005−82915(P2005−82915)

【出願日】平成17年3月23日(2005.3.23)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

【公開日】平成18年10月5日(2006.10.5)

【国際特許分類】

【出願日】平成17年3月23日(2005.3.23)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

[ Back to top ]