パルス出力装置

【課題】前回の設定に対応する歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御を可能とするパルス出力ASICを提供する。

【解決手段】出力部133は、出力指示信号S1に応答して、絶対位置指定データとパルス間隔指定データD2とに基づいて、目標位置へと到達するに必要な個数の歩進パルスをパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に出力すると共に、目標位置へと到達するに必要な歩進方向に対応させて、方向信号DSの論理値を変化させる。

【解決手段】出力部133は、出力指示信号S1に応答して、絶対位置指定データとパルス間隔指定データD2とに基づいて、目標位置へと到達するに必要な個数の歩進パルスをパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に出力すると共に、目標位置へと到達するに必要な歩進方向に対応させて、方向信号DSの論理値を変化させる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニット等への組み込みに好適なパルス出力装置に関する。

【背景技術】

【0002】

位置制御ユニットを含むビルディングブロック型PLCの応用例を示す模式図が図5に示されている。この応用例は、CPUユニット11と位置制御ユニット12とを含むビルディングブロック型のPLC1によって、昇降ベース6を有するリフト装置を制御するものである。

【0003】

同図において、位置制御の対象となる昇降ベース6は、上部スプロケット4aと下部スプロケット4bとの間に巻き掛けされたチェーン5と一体に結合され、チェーン5の動きに連れて、垂直に延びる昇降ガイド7に案内されつつ上下に移動可能とされている。

【0004】

下部スプロケット4bは、モータ3の駆動軸と連動するものであり、モータ3はモータ駆動装置2の制御下にあって、正逆回転駆動される。モータ3の回転量乃至回転角度と昇降ベース6の昇降量とは、一定の相関が保たれている。そのため、モータ3の回転量乃至回転角度をモータ駆動装置2を介して制御することで、昇降ベース6の高さ位置をオープンループで制御することができる。

【0005】

モータ駆動装置2は、PLC1に組み込まれた位置制御ユニット12から出力される歩進信号PSと方向信号DSとを受けて、モータ3を指定された回転量乃至回転角度だけ回転させるように動作する。

【0006】

歩進信号PSには、パルス数(N)とパルス間隔(T)とで規定される複数の歩進パルス列(N1とT1とで規定される第1歩進パルス列、N2とT2とで規定される第2歩進パルス列、N3とT3とで規定される第3歩進パルス列、・・・NnとTnとで規定される第n歩進パルス列)が順次直列に含まれている。

【0007】

方向進行DSは二値信号であって、その論理値は、モータ3を時計回り(CW)に回転させたいときには第1の論理値(例えば、“H”)、反時計回り(CCW)に回転させたいときには第2の論理値(例えば、“L”)となるように設定されている。

【0008】

歩進信号PSに含まれる歩進パルス1個当たりのモータ回転量乃至回転角度(歩進量)は、モータ駆動装置2によって一定に維持され、その際における回転速度は、パルス間隔(T)により決定され、また回転方向は方向信号DSの論理値により決定され、総回転量乃至回転角度はパルス数(N)によって決定される。

【0009】

そのため、歩進信号PSに含まれるパルス数(N)及びパルス間隔(T)と、方向信号DSの論理値とを制御することで、モータ3の回転量、回転速度、及び回転方向、換言すれば、昇降ベース6の昇降量、昇降速度、及び昇降方向を正確に制御することができるようになっている。

【0010】

位置制御ユニットの全体構成を示すブロック図が図6に、同ユニットを含むPLC全体の詳細構成図が図7に示されている(例えば、特許文献1参照)。

【0011】

図6に示されるように、位置制御ユニット12は、MPUシステム121とパルス出力ASIC122と、それらを繋ぐ内部バス123とを含んで構成されている。MPUシステム121は、システム全体を統括するMPU121aと、MPU121aにて実行されるべきシステムプログラムを格納するROM121bと、MPU121aがシステムプログラムを実行する際にワークエリア等として使用されるRAM121cとを含んで構成されている。なお、バスインタフェース124は、当該位置制御ユニット12をCPUユニット11へと繋がるユニット間接続バスと接続するためのものである。

【0012】

位置制御ユニットを含むPLC全体の詳細構成図が図7に示されている。同図に示されるように、MPUシステム121は、ROM121bに格納されるシステムプログラムを実行することにより、指令解析処理部P1と、単位変換演算処理部P2と、位置制御演算処理部(パルス単位)P3と、パルス出力指令処理部P4とをファームウエアとして実現するものである。

【0013】

ここで、指令解析処理部P1は、バスインタフェース124を介してCPUユニット11から受け取った制御指令(例えば、制御対象となるリフト装置において、「昇降ベース6を高さHmm上昇せよ」といった内容)を解析するものである。

【0014】

単位変換演算処理部P2と位置制御演算処理部P3とは、両者相俟って、指令解析処理部P1における解析の結果として得られた所定の指令単位系(mm)で表現された目標高さに基づいて、図8(a)に示されるように、現在高さから目標高さに至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、図8(b)に示されるように、所定のパルス単位系(歩進パルスの個数)で表現された一連の移動量データとして時系列的に出力するものである。

【0015】

パルス出力指令処理部P4は、位置制御演算処理部P3から時系列的に出力される一連の移動量データに基づいて、対応する位置制御指令データ(出力指示データ、パルス出力数指定データ、パルス間隔指定データ、方向指定データ等)を生成し、それらのデータをパルス出力ASIC122内の該当するレジスタに書き込むことにより、歩進信号PS及び方向信号DSの出力を指令するものである。

【0016】

従来のパルス出力ASICの2つの例を示す構成図が図9に示されている。同図に示されるように、これらのパルス出力ASIC122(同図(a),(b))は、いずれも、MPU・I/F制御部1221と、出力指示部1222と、出力部1223とを含んで構成されている。

【0017】

MPU・I/F制御部1221は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するものである。出力指示部1222は、MPU・I/F制御部121を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含んでいる。出力部1223は、出力指示部1222のレジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する。

【0018】

出力指示部1222は、前記レジスタとして、出力指示データD0を書き込むための出力指示レジスタ1222aと、パルス出力数指定データD1を書き込むためのパルス出力数指定レジスタ1222bと、パルス間隔指定データD2を書き込むためのパルス間隔指定レジスタ1222cと、方向指定データD3を書き込むための方向指定レジスタ1222dとを含んで構成されている。そして、出力指示データD0が出力指示レジスタ1222aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0019】

出力部1223は、出力指示信号S1の受信タイミングに応答して、パルス出力数指定レジスタ1222bに格納されたパルス出力数指定データD1で指定される数の歩進パルスを、パルス間隔指定レジスタ1222cに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力すると共に、方向指定レジスタ1222dに方向指定データD3が書き込まれるタイミングで、方向指定データで指定される方向に対応させて、方向信号DSの論理値を“H”又は“L”に変化させるように構成されている。

【特許文献1】特開2000−339009号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

ところで、この種のパルス出力ASICを使用した位置制御にあっては、歩進信号PS及び方向信号DSを受け付ける側の装置(例えば、図5に示されるモータ駆動装置2)の入力回路構成に起因して、図11に示されるように、歩進信号PS中の歩進パルスの前方エッジと方向信号DS中の論理値変化タイミングとの間には、所定のセットアップタイムを確保することが必要とされている。このセットアップタイムが確保されないと、歩進信号PS及び方向信号DSを受け付ける装置の側では、歩進方向が反転したことを認識することができずに、誤った方向(反転前の方向)へと制御対象物を歩進(カウント)させてしまう虞がある。

【0021】

従来、セットアップタイムを確保するためには、ソフトウェア的な手法(図9(a)び図10参照)とハードウェア的な手法(図9(b)参照)とが知られている。

【0022】

ソフトウェア的な手法にあっては、図9(a)に示されるように、パルス出力ASICそれ自体には遅延要素を含めることなく、図10に示されるように、MPUシステム121の側でソフトウェア的に遅延時間を作り出すものである。

【0023】

すなわち、図10に示されるように、先ず、パルス出力数指定レジスタ1222b及びパルス間隔指定レジスタ1222cに、それぞれ、パルス出力数指定データD1及びパルス間隔指定データD2を書き込み(ステップ201)、さらに、方向指定レジスタ1222dに方向指定データD3を書き込み(ステップ202)、しかるのち、セットアップ時間の経過するのを待ってから(ステップ203)、出力指示レジスタ1222aに出力指示データD0を書き込む(ステップ204)。

【0024】

こうすることにより、方向指定データD3の書き込みタイミングで方向信号DSの論理値が変化したとしても、出力指示信号S1により歩進パルス列が開始されるタイミングは、それよりもセットアップ時間分遅れることとなるため、歩進信号PS中の歩進クロックの前方エッジと方向信号DS中の変化タイミングとの間には、所定のセットアップタイムが確保される。

【0025】

ハードウェア的な手法にあっては、図9(b)に示されるように、パルス出力ASICそれ自体に、遅延要素として遅延回路1224を介在させることにより、パルス出力ASIC側で遅延時間を作り出すものである。なお、この場合、方向指定レジスタ1222dに方向指定データD3を書き込む処理と出力指示レジスタ1222aに出力指示データD0を書き込む処理とはほぼ同時に行なうことができる。

【0026】

こうすることにより、方向指定データD3の書き込みタイミングで方向信号DSの論理値が変化し、同タイミングで、出力指示信号S1により歩進パルス列が出力開始されたとしても、歩進パルス列の出力開始タイミングは遅延回路1224によって遅れることとなるため、歩進信号PS中の歩進クロックの前方エッジと方向信号DS中の変化タイミングとの間には、所定のセットアップタイムが確保される。

【0027】

上述のソフトウェア的な手法(図9(a)び図10参照)にあっては、方向信号DSの論理値反転のタイミングと歩進パルス列の出力開始タイミングとをソフトウエアにより決定するものであるから、パルス出力ASICのハードウェアそれ自体は同一であったとしても、1)ソフトウェアを変更することで、様々な入力回路仕様を有する駆動装置に対応することができ、コストメリットが大きいこと、2)セットアップタイムを挿入する必要があるか否かの判断をファームウエアが毎サイクル行うようにすれば、セットアップタイムを選択的に挿入することで、駆動装置の側で無駄な待ち時間が発生することを回避することもできること、と言った利点がある。

【0028】

その反面、ソフトウェア的な手法にあっては、セットアップタイムの設定にはファームウエアが介在されるため、1)方向信号DSの出力を指示してから、歩進信号PS中において、歩進パルス列の出力開始を指示するまでの時間が一定とならずにブレが発生すること、2)セットアップタイムの指定を精密に行うことができないこと、と言った欠点がある。

【0029】

上述のハードウェア的な手法(図9(b)参照)にあっては、方向信号DSの論理値反転のタイミングと歩進パルス列の出力開始タイミングとの時間差をハードウェア(遅延回路1224)により決定するものであるから、1)方向信号DS中における論理値反転のタイミングと歩進信号PS中における歩進パルス列の出力開始タイミングとの時間差を正確に一定とすることができること、2)回路設計によってセットアップタイムの設定を精密に行うことができること、と言った利点がある。

【0030】

その反面、ハードウェア的な手法にあっては、セットアップタイムの値は回路的に固定化されてしまうため、1)対象となる駆動装置が変われば、それに合わせて設計をし直さねばならないこと、2)方向信号中の論理値反転の有無に拘わらず、歩進パルス列は一様に遅延回路で遅延されるため、駆動装置の側で無駄な待ち時間が発生して、制御遅れが生ずる虞があること、と言った欠点がある。

【0031】

この発明は、従来のパルス出力ASICにおける上述の問題点に着目してなされたものであり、その目的とするところは、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能なパルス出力装置を提供することにある。

【0032】

この発明の他の目的とするところは、上述の目的に加えて、対象となる駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能なパルス出力装置を提供することにある。

【0033】

この発明の他の目的とするところは、そのようなパルス出力装置を組み込むことにより、高速かつ微細制御を可能としたビルディングブロック型PLCの位置制御ユニットを提供することにある。

【0034】

この発明のさらに他の目的並びに作用効果は、明細書の以下の記述を参照することにより、当業者であれば容易に理解される筈である。

【課題を解決するための手段】

【0035】

上述の[発明が解決しようとする課題]は、以下の構成を有するパルス出力装置乃至位置制御ユニットにより解決することができると考えられる。

【0036】

[基本構成]

すなわち、本発明のパルス出力装置は、先に図5〜図7を参照して説明したように、位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力装置(一般的には、ワイヤードロジックICであるが、場合によっては、FPGAのようなプログラミング可能な素子であってもよい)であって、次の構成を有するものである。

【0037】

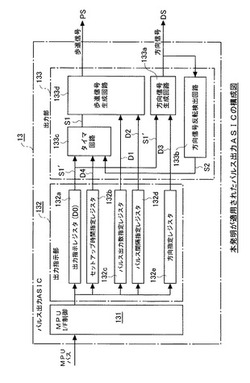

すなわち、このパルス出力装置(13)は、図1に示されるように、MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、MPU・I/F制御部(131)を介して前記MPUシステム(121)側から位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号(PS)と方向信号(DS)とを生成出力する出力部(133)とを有する。

【0038】

出力指示部(132)は、前記位置制御指令データを書き込み可能な複数のレジスタとして、出力指示データを書き込むための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を書き込むためのパルス間隔指定レジスタ(132d)と、目標位置までの相対距離に相当するパルス出力数指定データ(D1)及び目標位置の方向に相当する方向指定データ(D3)を書き込むためのパルス出力数指定レジスタ(132c)及び方向指定レジスタ(132e)、又は目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタ(図示せず)とを含み、かつ出力指示データ(D0)が出力指示レジスタ(132a)に書き込まれたタイミングに応答して、所定の出力指示源信号(S1´)を生成するように構成されている。

【0039】

出力部(133)は、出力指示源信号(S1´)の生成タイミングに応答して、方向指定レジスタ(132e)に格納された方向指定データ(D3)又は絶対位置指定レジスタ(図示せず)に格納された絶対位置指定データと現在位置とから求められた方向指定データで指定される歩進方向に対応する論理値を有する方向信号(DS)を生成する方向信号生成回路(133a)と、方向信号(DS)の反転タイミングに応答して微少幅パルスを出力する方向信号反転検出信号(S2)を生成する方向信号反転検出回路(133b)と、方向信号反転検出信号(S2)の微少幅パルスに応答して、前記出力指示源信号(S1´)を所定のセットアップ時間分だけ遅延させることにより、出力指示信号(S1)を生成するタイマ回路(133c)と、出力指示信号(S1)の生成タイミングに応答して、パルス出力数指定レジスタ(132c)に格納されたパルス出力数指定データ(D1)又は前記絶対位置指定データと現在位置とから求められたパルス出力数指定データにより指定される数の歩進パルスを、パルス間隔指定レジスタ(132d)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で歩進信号(PS)中に生成する歩進信号生成回路(133d)とを有する。

【0040】

[基本構成の作用効果]

このような構成によれば、図4に示されるように、パルス出力数指定レジスタ(132c)、パルス間隔指定レジスタ(132d)に、それぞれ、パルス出力数指定データ(D1)、パルス間隔指定データ(D2)を書き込み(ステップ101)、方向指定レジスタ(132e)に方向指定データ(D3)を書き込み(ステップ102)、最後に、出力指示レジスタ(132a)に出力指示データ(D0)を書き込みさえすれば、方向指示源信号(S1´)は、方向信号(DS)中に論理値反転が生じた場合に限り、タイマ回路(133c)の選択的タイマ機能により遅延されて、出力指示信号(S1)となり、この出力指示信号(S1)に応答して、歩進信号(PS)の生成が行われる。

【0041】

したがって、上述のパルス出力装置(13)によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号(DS)中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【0042】

[変形例1]

出力指示部(132)は、セットアップ時間指定データ(D4)を書き込むためのセットアップ時間指定レジスタ(132b)をさらに含み、出力部(133)のタイマ回路(133c)は、方向信号反転検出信号(S2)の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、所定のセットアップ時間を更新するものであってもよい。

【0043】

[変形例1の作用効果]

このような構成によれば、対象となる駆動装置が変わったとしても、その駆動装置に合わせて、セットアップ時間指定データ(D1)を予めセットアップ時間指定レジスタ(132b)に書き込んでおきさえすれば、出力部(133)のタイマ回路(133c)は、方向信号反転検出信号(S2)の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D1)を読み込むことにより、所定のセットアップ時間を更新するから、駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能となる。

【0044】

[応用例]

上述の基本構成並びに変形例1にかかるパルス出力装置は、ビルディングブロック型PLCの位置制御ユニットに応用することができる。すなわち、この位置制御ユニットは、CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、以下の構成を有するものである。

【0045】

すなわち、この位置制御ユニットは、CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含んでいる。

【0046】

MPUシステム(121)は、前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC122に対して必要な指令を与えるパルス出力指令処理部(P4)とを含んでいる。

【0047】

そして、パルス出力装置としては、基本構成並びに変形例1〜4のいずれかに記載のパルス出力装置(13)が使用されている。

【0048】

[応用例の作用効果]

この位置制御ユニットによれば、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に、本発明のパルス出力装置を介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【発明の効果】

【0049】

本発明のパルス出力装置によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【発明を実施するための最良の形態】

【0050】

以下に、本発明が適用されたパルス出力ASICの好適な実施の一形態を添付図面を参照しながら詳細に説明する。

【0051】

本発明が適用されたパルス出力ASICの構成図が図1に示されている。このパルス出力ASIC13は、先に図5〜図8を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0052】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132と、出力指示部132の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133とを含んで構成される。

【0053】

出力指示部132は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、セットアップ時間指定データD4を書き込むためのセットアップ時間指定レジスタ132bと、パルス出力数指定データD1を書き込むためのパルス出力数指定レジスタ132cと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132dと、方向指定データを書き込むための方向指定レジスタ132eとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示源信号S1´を生成するように構成されている。

【0054】

出力部133は、方向信号生成回路133aと、方向信号反転検出回路133bと、タイマ回路133cと、歩進信号生成回路133dとを含んで構成されている。

【0055】

方向信号生成回路133aは、出力指示源信号S1´の発生タイミングに応答して、方向指定レジスタ132eに書き込まれた方向指定データD3で指定される歩進方向に対応する論理値を有する方向信号DSを出力する。

【0056】

方向信号反転検出回路133bは、方向信号DSの論理値が反転されるタイミングを検出し、その検出タイミングに応答して微少幅パルス信号となる方向信号反転検出信号S2を生成する。

【0057】

タイマ回路133cは、方向信号反転検出信号S2が到来したときに限り、セットアップ時間指定レジスタ132bからセットアップ時間指定データD4を読み出すと共に、その読み出されたセットアップ時間指定データD4によって、セットアップ時間を更新し、その更新されたセットアップ時間だけ、出力指示源信号S1´を遅延させたのち、これを出力指示信号S1として出力する。

【0058】

歩進信号生成回路133dは、出力指示信号S1の生成タイミングに応答して、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD2により指定される数の歩進パルスを、パルス間隔指定レジスタ132dに格納されたパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に生成する。

【0059】

図1に示されるタイマ回路133cの詳細構成図が、図2にロジックシンボルを用いて概略的に示されている。

【0060】

同図において、残時間レジスタ133c−3のD入力には、同レジスタのQ出力を「−1」減算器133c−2にて減算した値(Q出力−1)又はセットアップ時間データD4が、切替器133c−1を介して択一的に入力される。この切替器133c−1は、方向信号反転検出信号S2により切替制御される。

【0061】

方向信号反転検出信号S2を生成する方向信号反転検出回路133bの詳細構成図が図3に示されている。同図に示されるように、同回路133bは、方向信号DSを2系統に分岐すると共に、一方には微少遅延素子133b−1を介在させ、しかるのち、両系統の信号をEORゲート133b−2に供給するきとにより、両者の不一致期間に対応して微少幅パルスとなる方向信号反転検出信号を生成するようにしたものである。

【0062】

残時間レジスタ133c−3のQ出力は、比較器133c−6において、All“0”と比較され、両者が一致すると、比較器133c−6からは、一致信号が出力されることとなる。

【0063】

残時間レジスタ133c−3のE(イネーブル)入力には、ORゲート133c−4を介して、方向信号反転検出信号S2又は上述の一致信号の反転信号が供給される。

【0064】

RSフリップフロップ133c−5のS(セット)入力には、出力指示源信号S1´が入力され、同フリップフロップ133c−5のR(リセット)入力には、上述の一致信号がそのまま入力されている。

【0065】

出力ゲートとして機能するANDゲート133c−7は、RSフリップフロップ133c−5のQ出力で開閉制御され、上述の一致信号を通過させて、出力指示信号S1として出力する。

【0066】

したがって、残時間レジスタ133c−3には、方向信号反転検出信号S2の中の微少幅パルスに応答して、セットアップ時間指定データD4が読み込まれる。こうして読み込まれたセットアップ時間指定データD4は、「−1」減算器133c−2の作用により減算されてゆき、セットアップ時間相当の時間が経過すると、ANDゲート133c−7の一方の入力に一致信号が供給される。

【0067】

ANDゲート133c−7の他方の入力には、RSフリップフロップのQ出力が供給され、このQ出力は、出力指示源信号S1´の立ち上がりでセットされている。そのため、上述の一致信号がANDゲート133c−7を通過することにより、出力指示信号S1が生成される。

【0068】

そして、前述のように、歩進信号生成回路133dは、出力指示信号S1の生成タイミングに応答して、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD2により指定される数の歩進パルスを、パルス間隔指定レジスタ132dに格納されたパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に生成する。

【0069】

そのため、この例によれば、図4に示されるように、パルス出力数指定レジスタ132c、パルス間隔指定レジスタ132dに、それぞれ、パルス出力数指定データD1、パルス間隔指定データD2を書き込み(ステップ101)、方向指定レジスタ132eに方向指定データD3を書き込み(ステップ102)、最後に、出力指示レジスタ132aに出力指示データD0を書き込みさえすれば、方向指示源信号S1´は、方向信号DS中に論理値反転が生じた場合に限り、タイマ回路133cの選択的タイマ機能により遅延されて、出力指示信号S1となり、この出力指示信号S1に応答して、歩進信号PSの生成が行われる。

【0070】

したがって、上述のパルス出力ASIC13によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【0071】

また、出力指示部132は、セットアップ時間指定データD4を書き込むためのセットアップ時間指定レジスタ132bをさらに含み、出力部133のタイマ回路133cは、方向信号反転検出信号S2の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、所定のセットアップ時間を更新する。

【0072】

そのため、対象となる駆動装置が変わったとしても、その駆動装置に合わせて、セットアップ時間指定データD1を予めセットアップ時間指定レジスタ132bに書き込んでおきさえすれば、出力部133のタイマ回路133cは、方向信号反転検出信号S2の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データD1を読み込むことにより、所定のセットアップ時間を更新するから、駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能となる。

【0073】

なお、以上の図示例にあっては、目標位置を指定するための手法として、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD1と方向指定レジスタ132eに格納された方向指定データD3を使用する相対位置指定方式を用いたが、それに代えて、目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタを出力指示部132に設ける一方、出力部133には、絶対位置指定レジスタに格納された絶対位置指定データと現在位置とから方向指定データを求める一方、絶対位置指定データと現在位置とからパルス出力数指定データを求める絶対位置指定方式を採用することもできる。

【0074】

[応用例]

上述の第1乃至第4実施形態にかかるパルス出力ASIC13は、ビルディングブロック型PLC1の位置制御ユニット12に応用することができる。すなわち、この位置制御ユニット12は、図6及び図7に示されるように、CPUユニット11や入出力ユニット等と共に使用されるビルディングブロック型PLC1の1要素ユニットであって、以下の構成を有するものである。

【0075】

すなわち、この位置制御ユニット12は、図6に示されるように、CPUユニット11に繋がる内部バス123に接続が可能なMPUシステム121と、MPUシステム121から位置制御指令データが与えられるパルス出力ASIC13(従来例の122に相当)とを含んでいる。

【0076】

MPUシステム121は、図7に示されるように、CPUユニット11から受け取った制御指令を解析する指令解析処理部P1と、指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部P2,P3と、単位変換機能付きの位置制御演算処理部P2,P3から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC13(122に相当)に対して必要な指令を与えるパルス出力指令処理部P4とを含んでいる。そして、パルス出力ASIC13としては、上述のパルス出力ASIC13のいずれかが採用されている。

【0077】

[応用例の作用効果]

この位置制御ユニットによれば、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に、本発明のパルス出力ASIC介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【産業上の利用可能性】

【0078】

本発明が適用されたパルス出力ASICは、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニットにおいて、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【図面の簡単な説明】

【0079】

【図1】本発明が適用されたパルス出力ASICの構成図である。

【図2】タイマ回路の詳細構成図である。

【図3】方向信号反転検出回路の詳細構成図である。

【図4】本発明が適用されたパルス出力ASIC使用時におけるMPU処理を示すフローチャートである。

【図5】位置制御ユニットを含むPLCの応用例を示す模式図である。

【図6】本発明が適用されたパルス出力ASICを含む位置制御ユニットの全体構成図である。

【図7】位置制御ユニットを含むPLC全体の詳細構成図である。

【図8】位置制御ユニット内のMPU処理の説明図である。

【図9】従来のパルス出力ASICの2つの例を示す構成図である。

【図10】従来の従来のパルス出力ASIC使用時におけるMPU処理を示すフローチャートである。

【図11】パルス出力ASICの出力信号とカウント値(想定現在位置)との関係を示す説明図である。

【符号の説明】

【0080】

1 PLC

2 モータ駆動装置

3 モータ

4a 上部スプロケット

4b 下部スプロケット

5 チェーン

6 昇降ベース

7 昇降ガイド

11 CPUユニット

12 位置制御ユニット

13 パルス出力ASIC(本発明)

121 MPUシステム

121a MPU

121b ROM

121c RAM

122 パルス出力ASIC(従来例)

123 内部バス

124 バスI/F部

131 MPU・I/F制御部

132 出力指示部

132a 出力指示レジスタ

132b セットアップ時間指定レジスタ

132c パルス出力数指定レジスタ

132d パルス間隔指定レジスタ

132e 方向指定レジスタ

133 出力部

133a 方向信号生成回路

133b 方向信号反転検出回路

133c タイマ回路

133d 歩進信号生成回路

P1 指令解析処理部

P2 単位変換処理部

P3 位置制御演算処理部

P4 パルス出力指令処理部

1221 MPU・I/F制御部

1222 出力指示部

1222a 出力指示レジスタ

1222b パルス出力数指定レジスタ

1222c パルス間隔指定レジスタ

1222d 方向指定レジスタ

1223 出力部

1223a 歩進信号生成回路

1223b 方向信号生成回路

1224 遅延回路

S1´ 出力指示源信号

S1 出力指示信号

S2 方向信号反転検出信号

D0 出力指示データ

D1 パルス出力数指定データ

D2 パルス間隔指定データ

D3 方向指定データ

D4 セットアップ時間指定データ

S1 出力指示信号

S1´ 出力指示源信号

S2 方向信号反転検出信号

【技術分野】

【0001】

この発明は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニット等への組み込みに好適なパルス出力装置に関する。

【背景技術】

【0002】

位置制御ユニットを含むビルディングブロック型PLCの応用例を示す模式図が図5に示されている。この応用例は、CPUユニット11と位置制御ユニット12とを含むビルディングブロック型のPLC1によって、昇降ベース6を有するリフト装置を制御するものである。

【0003】

同図において、位置制御の対象となる昇降ベース6は、上部スプロケット4aと下部スプロケット4bとの間に巻き掛けされたチェーン5と一体に結合され、チェーン5の動きに連れて、垂直に延びる昇降ガイド7に案内されつつ上下に移動可能とされている。

【0004】

下部スプロケット4bは、モータ3の駆動軸と連動するものであり、モータ3はモータ駆動装置2の制御下にあって、正逆回転駆動される。モータ3の回転量乃至回転角度と昇降ベース6の昇降量とは、一定の相関が保たれている。そのため、モータ3の回転量乃至回転角度をモータ駆動装置2を介して制御することで、昇降ベース6の高さ位置をオープンループで制御することができる。

【0005】

モータ駆動装置2は、PLC1に組み込まれた位置制御ユニット12から出力される歩進信号PSと方向信号DSとを受けて、モータ3を指定された回転量乃至回転角度だけ回転させるように動作する。

【0006】

歩進信号PSには、パルス数(N)とパルス間隔(T)とで規定される複数の歩進パルス列(N1とT1とで規定される第1歩進パルス列、N2とT2とで規定される第2歩進パルス列、N3とT3とで規定される第3歩進パルス列、・・・NnとTnとで規定される第n歩進パルス列)が順次直列に含まれている。

【0007】

方向進行DSは二値信号であって、その論理値は、モータ3を時計回り(CW)に回転させたいときには第1の論理値(例えば、“H”)、反時計回り(CCW)に回転させたいときには第2の論理値(例えば、“L”)となるように設定されている。

【0008】

歩進信号PSに含まれる歩進パルス1個当たりのモータ回転量乃至回転角度(歩進量)は、モータ駆動装置2によって一定に維持され、その際における回転速度は、パルス間隔(T)により決定され、また回転方向は方向信号DSの論理値により決定され、総回転量乃至回転角度はパルス数(N)によって決定される。

【0009】

そのため、歩進信号PSに含まれるパルス数(N)及びパルス間隔(T)と、方向信号DSの論理値とを制御することで、モータ3の回転量、回転速度、及び回転方向、換言すれば、昇降ベース6の昇降量、昇降速度、及び昇降方向を正確に制御することができるようになっている。

【0010】

位置制御ユニットの全体構成を示すブロック図が図6に、同ユニットを含むPLC全体の詳細構成図が図7に示されている(例えば、特許文献1参照)。

【0011】

図6に示されるように、位置制御ユニット12は、MPUシステム121とパルス出力ASIC122と、それらを繋ぐ内部バス123とを含んで構成されている。MPUシステム121は、システム全体を統括するMPU121aと、MPU121aにて実行されるべきシステムプログラムを格納するROM121bと、MPU121aがシステムプログラムを実行する際にワークエリア等として使用されるRAM121cとを含んで構成されている。なお、バスインタフェース124は、当該位置制御ユニット12をCPUユニット11へと繋がるユニット間接続バスと接続するためのものである。

【0012】

位置制御ユニットを含むPLC全体の詳細構成図が図7に示されている。同図に示されるように、MPUシステム121は、ROM121bに格納されるシステムプログラムを実行することにより、指令解析処理部P1と、単位変換演算処理部P2と、位置制御演算処理部(パルス単位)P3と、パルス出力指令処理部P4とをファームウエアとして実現するものである。

【0013】

ここで、指令解析処理部P1は、バスインタフェース124を介してCPUユニット11から受け取った制御指令(例えば、制御対象となるリフト装置において、「昇降ベース6を高さHmm上昇せよ」といった内容)を解析するものである。

【0014】

単位変換演算処理部P2と位置制御演算処理部P3とは、両者相俟って、指令解析処理部P1における解析の結果として得られた所定の指令単位系(mm)で表現された目標高さに基づいて、図8(a)に示されるように、現在高さから目標高さに至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、図8(b)に示されるように、所定のパルス単位系(歩進パルスの個数)で表現された一連の移動量データとして時系列的に出力するものである。

【0015】

パルス出力指令処理部P4は、位置制御演算処理部P3から時系列的に出力される一連の移動量データに基づいて、対応する位置制御指令データ(出力指示データ、パルス出力数指定データ、パルス間隔指定データ、方向指定データ等)を生成し、それらのデータをパルス出力ASIC122内の該当するレジスタに書き込むことにより、歩進信号PS及び方向信号DSの出力を指令するものである。

【0016】

従来のパルス出力ASICの2つの例を示す構成図が図9に示されている。同図に示されるように、これらのパルス出力ASIC122(同図(a),(b))は、いずれも、MPU・I/F制御部1221と、出力指示部1222と、出力部1223とを含んで構成されている。

【0017】

MPU・I/F制御部1221は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するものである。出力指示部1222は、MPU・I/F制御部121を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含んでいる。出力部1223は、出力指示部1222のレジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する。

【0018】

出力指示部1222は、前記レジスタとして、出力指示データD0を書き込むための出力指示レジスタ1222aと、パルス出力数指定データD1を書き込むためのパルス出力数指定レジスタ1222bと、パルス間隔指定データD2を書き込むためのパルス間隔指定レジスタ1222cと、方向指定データD3を書き込むための方向指定レジスタ1222dとを含んで構成されている。そして、出力指示データD0が出力指示レジスタ1222aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0019】

出力部1223は、出力指示信号S1の受信タイミングに応答して、パルス出力数指定レジスタ1222bに格納されたパルス出力数指定データD1で指定される数の歩進パルスを、パルス間隔指定レジスタ1222cに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力すると共に、方向指定レジスタ1222dに方向指定データD3が書き込まれるタイミングで、方向指定データで指定される方向に対応させて、方向信号DSの論理値を“H”又は“L”に変化させるように構成されている。

【特許文献1】特開2000−339009号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

ところで、この種のパルス出力ASICを使用した位置制御にあっては、歩進信号PS及び方向信号DSを受け付ける側の装置(例えば、図5に示されるモータ駆動装置2)の入力回路構成に起因して、図11に示されるように、歩進信号PS中の歩進パルスの前方エッジと方向信号DS中の論理値変化タイミングとの間には、所定のセットアップタイムを確保することが必要とされている。このセットアップタイムが確保されないと、歩進信号PS及び方向信号DSを受け付ける装置の側では、歩進方向が反転したことを認識することができずに、誤った方向(反転前の方向)へと制御対象物を歩進(カウント)させてしまう虞がある。

【0021】

従来、セットアップタイムを確保するためには、ソフトウェア的な手法(図9(a)び図10参照)とハードウェア的な手法(図9(b)参照)とが知られている。

【0022】

ソフトウェア的な手法にあっては、図9(a)に示されるように、パルス出力ASICそれ自体には遅延要素を含めることなく、図10に示されるように、MPUシステム121の側でソフトウェア的に遅延時間を作り出すものである。

【0023】

すなわち、図10に示されるように、先ず、パルス出力数指定レジスタ1222b及びパルス間隔指定レジスタ1222cに、それぞれ、パルス出力数指定データD1及びパルス間隔指定データD2を書き込み(ステップ201)、さらに、方向指定レジスタ1222dに方向指定データD3を書き込み(ステップ202)、しかるのち、セットアップ時間の経過するのを待ってから(ステップ203)、出力指示レジスタ1222aに出力指示データD0を書き込む(ステップ204)。

【0024】

こうすることにより、方向指定データD3の書き込みタイミングで方向信号DSの論理値が変化したとしても、出力指示信号S1により歩進パルス列が開始されるタイミングは、それよりもセットアップ時間分遅れることとなるため、歩進信号PS中の歩進クロックの前方エッジと方向信号DS中の変化タイミングとの間には、所定のセットアップタイムが確保される。

【0025】

ハードウェア的な手法にあっては、図9(b)に示されるように、パルス出力ASICそれ自体に、遅延要素として遅延回路1224を介在させることにより、パルス出力ASIC側で遅延時間を作り出すものである。なお、この場合、方向指定レジスタ1222dに方向指定データD3を書き込む処理と出力指示レジスタ1222aに出力指示データD0を書き込む処理とはほぼ同時に行なうことができる。

【0026】

こうすることにより、方向指定データD3の書き込みタイミングで方向信号DSの論理値が変化し、同タイミングで、出力指示信号S1により歩進パルス列が出力開始されたとしても、歩進パルス列の出力開始タイミングは遅延回路1224によって遅れることとなるため、歩進信号PS中の歩進クロックの前方エッジと方向信号DS中の変化タイミングとの間には、所定のセットアップタイムが確保される。

【0027】

上述のソフトウェア的な手法(図9(a)び図10参照)にあっては、方向信号DSの論理値反転のタイミングと歩進パルス列の出力開始タイミングとをソフトウエアにより決定するものであるから、パルス出力ASICのハードウェアそれ自体は同一であったとしても、1)ソフトウェアを変更することで、様々な入力回路仕様を有する駆動装置に対応することができ、コストメリットが大きいこと、2)セットアップタイムを挿入する必要があるか否かの判断をファームウエアが毎サイクル行うようにすれば、セットアップタイムを選択的に挿入することで、駆動装置の側で無駄な待ち時間が発生することを回避することもできること、と言った利点がある。

【0028】

その反面、ソフトウェア的な手法にあっては、セットアップタイムの設定にはファームウエアが介在されるため、1)方向信号DSの出力を指示してから、歩進信号PS中において、歩進パルス列の出力開始を指示するまでの時間が一定とならずにブレが発生すること、2)セットアップタイムの指定を精密に行うことができないこと、と言った欠点がある。

【0029】

上述のハードウェア的な手法(図9(b)参照)にあっては、方向信号DSの論理値反転のタイミングと歩進パルス列の出力開始タイミングとの時間差をハードウェア(遅延回路1224)により決定するものであるから、1)方向信号DS中における論理値反転のタイミングと歩進信号PS中における歩進パルス列の出力開始タイミングとの時間差を正確に一定とすることができること、2)回路設計によってセットアップタイムの設定を精密に行うことができること、と言った利点がある。

【0030】

その反面、ハードウェア的な手法にあっては、セットアップタイムの値は回路的に固定化されてしまうため、1)対象となる駆動装置が変われば、それに合わせて設計をし直さねばならないこと、2)方向信号中の論理値反転の有無に拘わらず、歩進パルス列は一様に遅延回路で遅延されるため、駆動装置の側で無駄な待ち時間が発生して、制御遅れが生ずる虞があること、と言った欠点がある。

【0031】

この発明は、従来のパルス出力ASICにおける上述の問題点に着目してなされたものであり、その目的とするところは、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能なパルス出力装置を提供することにある。

【0032】

この発明の他の目的とするところは、上述の目的に加えて、対象となる駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能なパルス出力装置を提供することにある。

【0033】

この発明の他の目的とするところは、そのようなパルス出力装置を組み込むことにより、高速かつ微細制御を可能としたビルディングブロック型PLCの位置制御ユニットを提供することにある。

【0034】

この発明のさらに他の目的並びに作用効果は、明細書の以下の記述を参照することにより、当業者であれば容易に理解される筈である。

【課題を解決するための手段】

【0035】

上述の[発明が解決しようとする課題]は、以下の構成を有するパルス出力装置乃至位置制御ユニットにより解決することができると考えられる。

【0036】

[基本構成]

すなわち、本発明のパルス出力装置は、先に図5〜図7を参照して説明したように、位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力装置(一般的には、ワイヤードロジックICであるが、場合によっては、FPGAのようなプログラミング可能な素子であってもよい)であって、次の構成を有するものである。

【0037】

すなわち、このパルス出力装置(13)は、図1に示されるように、MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、MPU・I/F制御部(131)を介して前記MPUシステム(121)側から位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号(PS)と方向信号(DS)とを生成出力する出力部(133)とを有する。

【0038】

出力指示部(132)は、前記位置制御指令データを書き込み可能な複数のレジスタとして、出力指示データを書き込むための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を書き込むためのパルス間隔指定レジスタ(132d)と、目標位置までの相対距離に相当するパルス出力数指定データ(D1)及び目標位置の方向に相当する方向指定データ(D3)を書き込むためのパルス出力数指定レジスタ(132c)及び方向指定レジスタ(132e)、又は目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタ(図示せず)とを含み、かつ出力指示データ(D0)が出力指示レジスタ(132a)に書き込まれたタイミングに応答して、所定の出力指示源信号(S1´)を生成するように構成されている。

【0039】

出力部(133)は、出力指示源信号(S1´)の生成タイミングに応答して、方向指定レジスタ(132e)に格納された方向指定データ(D3)又は絶対位置指定レジスタ(図示せず)に格納された絶対位置指定データと現在位置とから求められた方向指定データで指定される歩進方向に対応する論理値を有する方向信号(DS)を生成する方向信号生成回路(133a)と、方向信号(DS)の反転タイミングに応答して微少幅パルスを出力する方向信号反転検出信号(S2)を生成する方向信号反転検出回路(133b)と、方向信号反転検出信号(S2)の微少幅パルスに応答して、前記出力指示源信号(S1´)を所定のセットアップ時間分だけ遅延させることにより、出力指示信号(S1)を生成するタイマ回路(133c)と、出力指示信号(S1)の生成タイミングに応答して、パルス出力数指定レジスタ(132c)に格納されたパルス出力数指定データ(D1)又は前記絶対位置指定データと現在位置とから求められたパルス出力数指定データにより指定される数の歩進パルスを、パルス間隔指定レジスタ(132d)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で歩進信号(PS)中に生成する歩進信号生成回路(133d)とを有する。

【0040】

[基本構成の作用効果]

このような構成によれば、図4に示されるように、パルス出力数指定レジスタ(132c)、パルス間隔指定レジスタ(132d)に、それぞれ、パルス出力数指定データ(D1)、パルス間隔指定データ(D2)を書き込み(ステップ101)、方向指定レジスタ(132e)に方向指定データ(D3)を書き込み(ステップ102)、最後に、出力指示レジスタ(132a)に出力指示データ(D0)を書き込みさえすれば、方向指示源信号(S1´)は、方向信号(DS)中に論理値反転が生じた場合に限り、タイマ回路(133c)の選択的タイマ機能により遅延されて、出力指示信号(S1)となり、この出力指示信号(S1)に応答して、歩進信号(PS)の生成が行われる。

【0041】

したがって、上述のパルス出力装置(13)によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号(DS)中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【0042】

[変形例1]

出力指示部(132)は、セットアップ時間指定データ(D4)を書き込むためのセットアップ時間指定レジスタ(132b)をさらに含み、出力部(133)のタイマ回路(133c)は、方向信号反転検出信号(S2)の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、所定のセットアップ時間を更新するものであってもよい。

【0043】

[変形例1の作用効果]

このような構成によれば、対象となる駆動装置が変わったとしても、その駆動装置に合わせて、セットアップ時間指定データ(D1)を予めセットアップ時間指定レジスタ(132b)に書き込んでおきさえすれば、出力部(133)のタイマ回路(133c)は、方向信号反転検出信号(S2)の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D1)を読み込むことにより、所定のセットアップ時間を更新するから、駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能となる。

【0044】

[応用例]

上述の基本構成並びに変形例1にかかるパルス出力装置は、ビルディングブロック型PLCの位置制御ユニットに応用することができる。すなわち、この位置制御ユニットは、CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、以下の構成を有するものである。

【0045】

すなわち、この位置制御ユニットは、CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含んでいる。

【0046】

MPUシステム(121)は、前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC122に対して必要な指令を与えるパルス出力指令処理部(P4)とを含んでいる。

【0047】

そして、パルス出力装置としては、基本構成並びに変形例1〜4のいずれかに記載のパルス出力装置(13)が使用されている。

【0048】

[応用例の作用効果]

この位置制御ユニットによれば、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に、本発明のパルス出力装置を介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【発明の効果】

【0049】

本発明のパルス出力装置によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【発明を実施するための最良の形態】

【0050】

以下に、本発明が適用されたパルス出力ASICの好適な実施の一形態を添付図面を参照しながら詳細に説明する。

【0051】

本発明が適用されたパルス出力ASICの構成図が図1に示されている。このパルス出力ASIC13は、先に図5〜図8を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0052】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132と、出力指示部132の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133とを含んで構成される。

【0053】

出力指示部132は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、セットアップ時間指定データD4を書き込むためのセットアップ時間指定レジスタ132bと、パルス出力数指定データD1を書き込むためのパルス出力数指定レジスタ132cと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132dと、方向指定データを書き込むための方向指定レジスタ132eとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示源信号S1´を生成するように構成されている。

【0054】

出力部133は、方向信号生成回路133aと、方向信号反転検出回路133bと、タイマ回路133cと、歩進信号生成回路133dとを含んで構成されている。

【0055】

方向信号生成回路133aは、出力指示源信号S1´の発生タイミングに応答して、方向指定レジスタ132eに書き込まれた方向指定データD3で指定される歩進方向に対応する論理値を有する方向信号DSを出力する。

【0056】

方向信号反転検出回路133bは、方向信号DSの論理値が反転されるタイミングを検出し、その検出タイミングに応答して微少幅パルス信号となる方向信号反転検出信号S2を生成する。

【0057】

タイマ回路133cは、方向信号反転検出信号S2が到来したときに限り、セットアップ時間指定レジスタ132bからセットアップ時間指定データD4を読み出すと共に、その読み出されたセットアップ時間指定データD4によって、セットアップ時間を更新し、その更新されたセットアップ時間だけ、出力指示源信号S1´を遅延させたのち、これを出力指示信号S1として出力する。

【0058】

歩進信号生成回路133dは、出力指示信号S1の生成タイミングに応答して、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD2により指定される数の歩進パルスを、パルス間隔指定レジスタ132dに格納されたパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に生成する。

【0059】

図1に示されるタイマ回路133cの詳細構成図が、図2にロジックシンボルを用いて概略的に示されている。

【0060】

同図において、残時間レジスタ133c−3のD入力には、同レジスタのQ出力を「−1」減算器133c−2にて減算した値(Q出力−1)又はセットアップ時間データD4が、切替器133c−1を介して択一的に入力される。この切替器133c−1は、方向信号反転検出信号S2により切替制御される。

【0061】

方向信号反転検出信号S2を生成する方向信号反転検出回路133bの詳細構成図が図3に示されている。同図に示されるように、同回路133bは、方向信号DSを2系統に分岐すると共に、一方には微少遅延素子133b−1を介在させ、しかるのち、両系統の信号をEORゲート133b−2に供給するきとにより、両者の不一致期間に対応して微少幅パルスとなる方向信号反転検出信号を生成するようにしたものである。

【0062】

残時間レジスタ133c−3のQ出力は、比較器133c−6において、All“0”と比較され、両者が一致すると、比較器133c−6からは、一致信号が出力されることとなる。

【0063】

残時間レジスタ133c−3のE(イネーブル)入力には、ORゲート133c−4を介して、方向信号反転検出信号S2又は上述の一致信号の反転信号が供給される。

【0064】

RSフリップフロップ133c−5のS(セット)入力には、出力指示源信号S1´が入力され、同フリップフロップ133c−5のR(リセット)入力には、上述の一致信号がそのまま入力されている。

【0065】

出力ゲートとして機能するANDゲート133c−7は、RSフリップフロップ133c−5のQ出力で開閉制御され、上述の一致信号を通過させて、出力指示信号S1として出力する。

【0066】

したがって、残時間レジスタ133c−3には、方向信号反転検出信号S2の中の微少幅パルスに応答して、セットアップ時間指定データD4が読み込まれる。こうして読み込まれたセットアップ時間指定データD4は、「−1」減算器133c−2の作用により減算されてゆき、セットアップ時間相当の時間が経過すると、ANDゲート133c−7の一方の入力に一致信号が供給される。

【0067】

ANDゲート133c−7の他方の入力には、RSフリップフロップのQ出力が供給され、このQ出力は、出力指示源信号S1´の立ち上がりでセットされている。そのため、上述の一致信号がANDゲート133c−7を通過することにより、出力指示信号S1が生成される。

【0068】

そして、前述のように、歩進信号生成回路133dは、出力指示信号S1の生成タイミングに応答して、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD2により指定される数の歩進パルスを、パルス間隔指定レジスタ132dに格納されたパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に生成する。

【0069】

そのため、この例によれば、図4に示されるように、パルス出力数指定レジスタ132c、パルス間隔指定レジスタ132dに、それぞれ、パルス出力数指定データD1、パルス間隔指定データD2を書き込み(ステップ101)、方向指定レジスタ132eに方向指定データD3を書き込み(ステップ102)、最後に、出力指示レジスタ132aに出力指示データD0を書き込みさえすれば、方向指示源信号S1´は、方向信号DS中に論理値反転が生じた場合に限り、タイマ回路133cの選択的タイマ機能により遅延されて、出力指示信号S1となり、この出力指示信号S1に応答して、歩進信号PSの生成が行われる。

【0070】

したがって、上述のパルス出力ASIC13によれば、ファームウエアの側におけるセットアップタイムに関する時間管理を要することなく、方向信号DS中において論理値反転が生じたときに限り、その論理値反転タイミングと歩進パルス列の出力開始タイミングとの間に、正確な値を有するセットアップタイムを設けることが可能となる。

【0071】

また、出力指示部132は、セットアップ時間指定データD4を書き込むためのセットアップ時間指定レジスタ132bをさらに含み、出力部133のタイマ回路133cは、方向信号反転検出信号S2の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、所定のセットアップ時間を更新する。

【0072】

そのため、対象となる駆動装置が変わったとしても、その駆動装置に合わせて、セットアップ時間指定データD1を予めセットアップ時間指定レジスタ132bに書き込んでおきさえすれば、出力部133のタイマ回路133cは、方向信号反転検出信号S2の微少幅パルスに応答して、セットアップ時間指定レジスタに格納されたセットアップ時間指定データD1を読み込むことにより、所定のセットアップ時間を更新するから、駆動装置が変わったとしても、ハードウエア的な構成は維持したままで、所定の設定データを変更するだけで対応することが可能となる。

【0073】

なお、以上の図示例にあっては、目標位置を指定するための手法として、パルス出力数指定レジスタ132cに格納されたパルス出力数指定データD1と方向指定レジスタ132eに格納された方向指定データD3を使用する相対位置指定方式を用いたが、それに代えて、目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタを出力指示部132に設ける一方、出力部133には、絶対位置指定レジスタに格納された絶対位置指定データと現在位置とから方向指定データを求める一方、絶対位置指定データと現在位置とからパルス出力数指定データを求める絶対位置指定方式を採用することもできる。

【0074】

[応用例]

上述の第1乃至第4実施形態にかかるパルス出力ASIC13は、ビルディングブロック型PLC1の位置制御ユニット12に応用することができる。すなわち、この位置制御ユニット12は、図6及び図7に示されるように、CPUユニット11や入出力ユニット等と共に使用されるビルディングブロック型PLC1の1要素ユニットであって、以下の構成を有するものである。

【0075】

すなわち、この位置制御ユニット12は、図6に示されるように、CPUユニット11に繋がる内部バス123に接続が可能なMPUシステム121と、MPUシステム121から位置制御指令データが与えられるパルス出力ASIC13(従来例の122に相当)とを含んでいる。

【0076】

MPUシステム121は、図7に示されるように、CPUユニット11から受け取った制御指令を解析する指令解析処理部P1と、指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部P2,P3と、単位変換機能付きの位置制御演算処理部P2,P3から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC13(122に相当)に対して必要な指令を与えるパルス出力指令処理部P4とを含んでいる。そして、パルス出力ASIC13としては、上述のパルス出力ASIC13のいずれかが採用されている。

【0077】

[応用例の作用効果]

この位置制御ユニットによれば、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に、本発明のパルス出力ASIC介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【産業上の利用可能性】

【0078】

本発明が適用されたパルス出力ASICは、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニットにおいて、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に介在することにより、当該位置制御ユニットにおける制御精度や使い勝手を向上させることが可能となる。

【図面の簡単な説明】

【0079】

【図1】本発明が適用されたパルス出力ASICの構成図である。

【図2】タイマ回路の詳細構成図である。

【図3】方向信号反転検出回路の詳細構成図である。

【図4】本発明が適用されたパルス出力ASIC使用時におけるMPU処理を示すフローチャートである。

【図5】位置制御ユニットを含むPLCの応用例を示す模式図である。

【図6】本発明が適用されたパルス出力ASICを含む位置制御ユニットの全体構成図である。

【図7】位置制御ユニットを含むPLC全体の詳細構成図である。

【図8】位置制御ユニット内のMPU処理の説明図である。

【図9】従来のパルス出力ASICの2つの例を示す構成図である。

【図10】従来の従来のパルス出力ASIC使用時におけるMPU処理を示すフローチャートである。

【図11】パルス出力ASICの出力信号とカウント値(想定現在位置)との関係を示す説明図である。

【符号の説明】

【0080】

1 PLC

2 モータ駆動装置

3 モータ

4a 上部スプロケット

4b 下部スプロケット

5 チェーン

6 昇降ベース

7 昇降ガイド

11 CPUユニット

12 位置制御ユニット

13 パルス出力ASIC(本発明)

121 MPUシステム

121a MPU

121b ROM

121c RAM

122 パルス出力ASIC(従来例)

123 内部バス

124 バスI/F部

131 MPU・I/F制御部

132 出力指示部

132a 出力指示レジスタ

132b セットアップ時間指定レジスタ

132c パルス出力数指定レジスタ

132d パルス間隔指定レジスタ

132e 方向指定レジスタ

133 出力部

133a 方向信号生成回路

133b 方向信号反転検出回路

133c タイマ回路

133d 歩進信号生成回路

P1 指令解析処理部

P2 単位変換処理部

P3 位置制御演算処理部

P4 パルス出力指令処理部

1221 MPU・I/F制御部

1222 出力指示部

1222a 出力指示レジスタ

1222b パルス出力数指定レジスタ

1222c パルス間隔指定レジスタ

1222d 方向指定レジスタ

1223 出力部

1223a 歩進信号生成回路

1223b 方向信号生成回路

1224 遅延回路

S1´ 出力指示源信号

S1 出力指示信号

S2 方向信号反転検出信号

D0 出力指示データ

D1 パルス出力数指定データ

D2 パルス間隔指定データ

D3 方向指定データ

D4 セットアップ時間指定データ

S1 出力指示信号

S1´ 出力指示源信号

S2 方向信号反転検出信号

【特許請求の範囲】

【請求項1】

位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力ASIC(13)であって、

前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、

前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132と、

前記出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有し、

前記出力指示部(132)は、前記位置制御指令データを書き込み可能なレジスタとして、

出力指示データ(D0)を書き込むための出力指示レジスタ(132a)と、

パルス間隔指定データ(D2)を書き込むためのパルス間隔指定レジスタ(132d)と、

目標位置までの相対距離に相当するパルス出力数指定データ(D1)及び目標位置の方向に相当する方向指定データ(D3)を書き込むためのパルス出力数指定レジスタ(132c)及び方向指定レジスタ(132e)、又は目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタとを含み、かつ

前記出力指示データ(D0)が前記出力指示レジスタ(132a)に書き込まれたタイミングに応答して、所定の出力指示源信号(S1´)を生成するように構成されており、

前記出力部(133)は、

前記出力指示源信号(S1´)の生成タイミングに応答して、前記方向指定レジスタ(132e)に格納された方向指定データ(D3)又は前記絶対位置指定レジスタに格納された絶対位置指定データと現在位置とから求められた方向指定データで指定される歩進方向に対応する論理値を有する方向信号(DS)を生成する方向信号生成回路(133a)と、

前記方向信号(DS)の反転タイミングに応答して微少幅パルスを出力する方向信号反転検出信号(S2)を生成する方向信号反転検出回路(133b)と、

前記方向信号反転検出信号(S2)の微少幅パルスに応答して、前記出力指示源信号(S1´)を所定のセットアップ時間分だけ遅延させることにより、出力指示信号(S1)を生成するタイマ回路(133c)と、

前記出力指示信号(S1)の生成タイミングに応答して、前記パルス出力数指定レジスタ(132c)に格納されたパルス出力数指定データ(D1)又は前記絶対位置指定データと現在位置とから求められたパルス出力数指定データにより指定される数の歩進パルスを、前記パルス間隔指定レジスタ(132d)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に生成する歩進信号生成回路(133d)とを有する、ことを特徴とするパルス出力装置。

【請求項2】

前記出力指示部(132)は、セットアップ時間指定データ(D4)を書き込むためのセットアップ時間指定レジスタ(132b)をさらに含み、

前記出力部(133)のタイマ回路(133c)は、前記方向信号反転検出信号(S2)の微少幅パルスに応答して、前記セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、前記所定のセットアップ時間を更新する、ことを特徴とする請求項1に記載のパルス出力装置。

【請求項3】

CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、

前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含み、

前記MPUシステム(121)は、

前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、

前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、

前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対に基づいて、パルス出力ASIC122に対して必要な位置制御指令データを与えるパルス出力指令処理部(P4)とを含み、

前記パルス出力ASICとしては、請求項1又は2に記載のパルス出力装置が使用されている、ことを特徴とするPLCの位置制御ユニット。

【請求項1】

位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力ASIC(13)であって、

前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、

前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132と、

前記出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有し、

前記出力指示部(132)は、前記位置制御指令データを書き込み可能なレジスタとして、

出力指示データ(D0)を書き込むための出力指示レジスタ(132a)と、

パルス間隔指定データ(D2)を書き込むためのパルス間隔指定レジスタ(132d)と、

目標位置までの相対距離に相当するパルス出力数指定データ(D1)及び目標位置の方向に相当する方向指定データ(D3)を書き込むためのパルス出力数指定レジスタ(132c)及び方向指定レジスタ(132e)、又は目標位置をその絶対位置で表す絶対位置指定データを書き込むための絶対位置指定レジスタとを含み、かつ

前記出力指示データ(D0)が前記出力指示レジスタ(132a)に書き込まれたタイミングに応答して、所定の出力指示源信号(S1´)を生成するように構成されており、

前記出力部(133)は、

前記出力指示源信号(S1´)の生成タイミングに応答して、前記方向指定レジスタ(132e)に格納された方向指定データ(D3)又は前記絶対位置指定レジスタに格納された絶対位置指定データと現在位置とから求められた方向指定データで指定される歩進方向に対応する論理値を有する方向信号(DS)を生成する方向信号生成回路(133a)と、

前記方向信号(DS)の反転タイミングに応答して微少幅パルスを出力する方向信号反転検出信号(S2)を生成する方向信号反転検出回路(133b)と、

前記方向信号反転検出信号(S2)の微少幅パルスに応答して、前記出力指示源信号(S1´)を所定のセットアップ時間分だけ遅延させることにより、出力指示信号(S1)を生成するタイマ回路(133c)と、

前記出力指示信号(S1)の生成タイミングに応答して、前記パルス出力数指定レジスタ(132c)に格納されたパルス出力数指定データ(D1)又は前記絶対位置指定データと現在位置とから求められたパルス出力数指定データにより指定される数の歩進パルスを、前記パルス間隔指定レジスタ(132d)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に生成する歩進信号生成回路(133d)とを有する、ことを特徴とするパルス出力装置。

【請求項2】

前記出力指示部(132)は、セットアップ時間指定データ(D4)を書き込むためのセットアップ時間指定レジスタ(132b)をさらに含み、

前記出力部(133)のタイマ回路(133c)は、前記方向信号反転検出信号(S2)の微少幅パルスに応答して、前記セットアップ時間指定レジスタに格納されたセットアップ時間指定データ(D4)を読み込むことにより、前記所定のセットアップ時間を更新する、ことを特徴とする請求項1に記載のパルス出力装置。

【請求項3】

CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、

前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含み、

前記MPUシステム(121)は、

前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、

前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、

前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対に基づいて、パルス出力ASIC122に対して必要な位置制御指令データを与えるパルス出力指令処理部(P4)とを含み、

前記パルス出力ASICとしては、請求項1又は2に記載のパルス出力装置が使用されている、ことを特徴とするPLCの位置制御ユニット。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2010−140314(P2010−140314A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−316899(P2008−316899)

【出願日】平成20年12月12日(2008.12.12)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月12日(2008.12.12)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

[ Back to top ]