パルス出力装置

【課題】前回の設定に対応する歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御を可能とするパルス出力装置を提供する。

【解決手段】出力部133−1は、出力指示信号S1に応答して、絶対位置指定データD4とパルス間隔指定データD2とに基づいて、目標位置へと到達するに必要な個数の歩進パルスをパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に出力すると共に、目標位置へと到達するに必要な歩進方向に対応させて、方向信号DSの論理値を変化させる。

【解決手段】出力部133−1は、出力指示信号S1に応答して、絶対位置指定データD4とパルス間隔指定データD2とに基づいて、目標位置へと到達するに必要な個数の歩進パルスをパルス間隔指定データD2で指定されるパルス間隔で歩進信号PS中に出力すると共に、目標位置へと到達するに必要な歩進方向に対応させて、方向信号DSの論理値を変化させる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニット等への組み込みに好適なパルス出力装置に関する。

【背景技術】

【0002】

位置制御ユニットを含むビルディングブロック型PLCの応用例を示す模式図が図11に示されている。この応用例は、CPUユニット11と位置制御ユニット12とを含むビルディングブロック型のPLC1によって、昇降ベース6を有するリフト装置を制御するものである。

【0003】

同図において、位置制御の対象となる昇降ベース6は、上部スプロケット4aと下部スプロケット4bとの間に巻き掛けされたチェーン5と一体に結合され、チェーン5の動きに連れて、垂直に延びる昇降ガイド7に案内されつつ上下に移動可能とされている。

【0004】

下部スプロケット4bは、モータ3の駆動軸と連動するものであり、モータ3はモータ駆動装置2の制御下にあって、正逆回転駆動される。モータ3の回転量乃至回転角度と昇降ベース6の昇降量とは、一定の相関が保たれている。そのため、モータ3の回転量乃至回転角度をモータ駆動装置2を介して制御することで、昇降ベース6の高さ位置をオープンループで制御することができる。

【0005】

モータ駆動装置2は、PLC1に組み込まれた位置制御ユニット12から出力される歩進信号PSと方向信号DSとを受けて、モータ3を指定された回転量乃至回転角度だけ回転させるように動作する。

【0006】

歩進信号PSには、パルス数(N)とパルス間隔(T)とで規定される複数の歩進パルス列(N1とT1とで規定される第1歩進パルス列、N2とT2とで規定される第2歩進パルス列、N3とT3とで規定される第3歩進パルス列、・・・NnとTnとで規定される第n歩進パルス列)が順次直列に含まれている。

【0007】

方向進行DSは二値信号であって、その論理値は、モータ3を時計回り(CW)に回転させたいときには第1の論理値(例えば、“H”)、反時計回り(CCW)に回転させたいときには第2の論理値(例えば、“L”)となるように設定されている。

【0008】

歩進信号PSに含まれる歩進パルス1個当たりのモータ回転量乃至回転角度は、モータ駆動装置2によって一定に維持され、その際における回転速度は、パルス間隔(T)により決定され、また回転方向は方向信号DSの論理値により決定され、総回転量乃至回転角度はパルス数(N)によって決定される。

【0009】

そのため、歩進信号PSに含まれるパルス数(N)及びパルス間隔(T)と、方向信号DSの論理値とを制御することで、モータ3の回転量、回転速度、及び回転方向、換言すれば、昇降ベース6の昇降量、昇降速度、及び昇降方向を正確に制御することができるようになっている。

【0010】

位置制御ユニットの全体構成を示すブロック図が図12に、同ユニットを含むPLC全体の詳細構成図が図13に示されている(例えば、特許文献1参照)。

【0011】

図12に示されるように、位置制御ユニット12は、MPUシステム121とパルス出力ASIC122と、それらを繋ぐ内部バス123とを含んで構成されている。MPUシステム121は、システム全体を統括するMPU121aと、MPU121aにて実行されるべきシステムプログラムを格納するROM121bと、MPU121aがシステムプログラムを実行する際にワークエリア等として使用されるRAM121cとを含んで構成されている。なお、バスインタフェース124は、当該位置制御ユニット12をCPUユニット11へと繋がるユニット間接続バスと接続するためのものである。

【0012】

位置制御ユニットを含むPLC全体の詳細構成図が図13に示されている。同図に示されるように、MPUシステム121は、ROM121bに格納されるシステムプログラムを実行することにより、指令解析処理部P1と、単位変換演算処理部P2と、位置制御演算処理部(パルス単位)P3と、パルス出力指令処理部P4とをファームウエアとして実現するものである。

【0013】

ここで、指令解析処理部P1は、バスインタフェース124を介してCPUユニット11から受け取った制御指令(例えば、制御対象となるリフト装置において、「昇降ベース6を高さHmm上昇せよ」といった内容)を解析するものである。

【0014】

単位変換演算処理部P2と位置制御演算処理部P3とは、両者相俟って、指令解析処理部P1における解析の結果として得られた所定の指令単位系(mm)で表現された目標高さに基づいて、図14(a)に示されるように、現在高さから目標高さに至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、図14(b)に示されるように、所定のパルス単位系(歩進パルスの個数)で表現された一連の移動量データとして時系列的に出力するものである。

【0015】

パルス出力指令処理部P4は、位置制御演算処理部P3から時系列的に出力される一連の移動量データに基づいて、対応する位置制御指令データ(出力指示データ、パルス出力数指定データ、パルス間隔指定データ、方向指定データ等)を生成し、それらのデータをパルス出力装置を構成するパルス出力ASIC122内の該当するレジスタに書き込むことにより、歩進信号PS及び方向信号DSの出力を指令するものである。

【0016】

従来のパルス出力ASICの構成図が図15に示されている。同図に示されるように、このパルス出力ASIC122は、MPU・I/F制御部1221と、出力指示部1222と、出力部1223とを含んで構成されている。

【0017】

MPU・I/F制御部1221は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するものである。出力指示部1222は、MPU・I/F制御部121を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含んでいる。出力部1223は、出力指示部1222のレジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する。

【0018】

出力指示部1222は、前記レジスタとして、出力指示データD0(図示せず)を格納するための出力指示レジスタ1222aと、パルス出力数指定データD1を格納するためのパルス出力数指定レジスタ1222bと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ1222cと、方向指定データD3を格納するための方向指定レジスタ1222dとを含んで構成されている。そして、出力指示部1222は、出力指示データD0が出力指示レジスタ1222aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0019】

出力部1223は、出力指示信号S1の受信タイミングに応答して、パルス出力数指定レジスタ1222bに格納されたパルス出力数指定データD1で指定される数の歩進パルスを、パルス間隔指定レジスタ1222cに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力すると共に、方向指定レジスタ1222dに格納される方向指定データD3で指定される方向に対応させて、方向信号DSの論理値を変化させるように構成されている。

【0020】

加えて、出力部1223の内部には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じた方向へとカウントすることにより、現在値データを生成するカウント機能が組み込まれており、こうして生成された現在位置データは、MPU・I/F制御部1221を介して、MPUシステム121側から読み出し可能とされている。

【特許文献1】特開2000−339009号公報

【発明の開示】

【発明が解決しようとする課題】

【0021】

ところで、パルス出力指令処理部P4(図13参照)は、その前段に位置する位置制御演算処理部P3から時系列的に与えられる移動量データ列(図14(b)参照)に基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC122に対して必要な指令を与える。

【0022】

その際における従来のMPU処理(パルス出力指令処理部P4の機能を実現するための処理に相当)を示すフローチャートが図16に示されている。

【0023】

同図に示されるように、このMPU処理にあっては、先ず、ステップ101として、MPU・I/F処理部1221を介して、出力部1223から「現在位置」を読み出し、続くステップ102として、読み出された「現在位置」と既知の「目標位置」との差の絶対値から「パルス出力数」を求める。

【0024】

次に、ステップ103として、「現在位置」と「目標位置」との大小判定を行い、「目標位置≧現在位置」のときには「CW方向指定」として、「目標位置<現在位置」のときには「CCW方向指定」として、「歩進方向」を求める。

【0025】

次に、ステップ104として、MPU・I/F処理部1221を介して、パルス出力数指定レジスタ1222b、パルス間隔指定レジスタ1222c、方向指定レジスタ1222dに、上で求められた「パルス出力数」、既知の速度に対応する「パルス間隔」、上で求められた「歩進方向」をそれぞれ書き込む。

【0026】

最後に、ステップ105として、MPU・I/F処理部1221を介して、出力指示レジスタ1222aに、出力指示データを格納することにより、出力指示信号S1を発生させる。

【0027】

しかしながら、このような従来のMPU処理にあっては、出力指示部1222に対するデータ書き込み処理(ステップ104,105)に先立って、各種の前処理(ステップ101,102,103)が必要であることから、前回の目標位置に対応する歩進パルスの出力中に、次回の目標位置に対応する新たな設定を行おうとすると、歩進パルスの出力周波数が高周波(例えば、1MHz程度)になると、MPUの処理速度との関係により、前回の設定に対応する歩進パルスの出力終了よりもかなり(例えば、歩進パルス2個分程度)早めに、次回の設定を完了させねばならず、位置制御上の応答性に制約を与え、高速かつ微細制御に支障を来す虞があると言う問題点があった(図17参照)。

【0028】

この発明は、上述の問題点に着目してなされたものであり、その目的とするところは、出力指示部に対するデータ書き込み処理に先立つ前処理をできるかぎり不要としてMPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、前回の設定に対応する歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御を可能とするパルス出力ASICを提供することにある。

【0029】

この発明のさらに他の目的とするところは、そのようなパルス出力ASICを組み込むことにより、高速かつ微細制御を可能としたビルディングブロック型PLCの位置制御ユニットを提供することにある。

【0030】

この発明のさらに他の目的並びに作用効果は、明細書の下記の記述を参照することにより、当業者であれば容易に理解される筈である。

【課題を解決するための手段】

【0031】

上述の[発明が解決しようとする課題]は、以下の構成を有するパルス出力ASIC乃至位置制御ユニットにより解決することができると考えられる。

【0032】

[基本構成]

すなわち、本発明のパルス出力装置(13)は、位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するものである。より具体的には、例えば、パルス出力ASIC(一般的には、ワイヤードロジックICであるが、場合によっては、FPGAのようなプログラミング可能な素子であってもよい)として構成することができる。

【0033】

すなわち、このパルス出力装置は、図1、図3、図5、図7に示されるように、前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、前記出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有する。

【0034】

前記出力指示部(132)は、前記レジスタとして、出力指示データ(D0)を格納するための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を格納するためのパルス間隔指定レジスタ(132b)と、目標位置をその絶対位置で表す絶対位置指定データ(D4)を格納するための絶対位置指定レジスタ(132c)とを含み、かつ前記出力指示データ(D0)が前記出力指示レジスタに書き込まれたタイミングに応答して、所定の出力指示信号(S1)を生成するように構成(132−1)されている。

【0035】

前記出力部(133)は、前記出力指示信号(S1)に応答して、前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)と前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)とに基づいて、前記絶対位置指定データ(D4)で指定される目標位置へと到達するに必要な個数の歩進パルスを前記パルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に出力すると共に、前記目標位置へと到達するに必要な歩進方向に対応させて、前記方向信号(DS)の論理値を変化させるように構成(133−1)されている。

【0036】

[基本構成の作用効果]

このような構成によれば、出力指示部(132−1)の各レジスタ(132a,132b,132c)に書き込まれるべきデータ(D0,D2,D4)は、いずれも既知のものであるから、出力指示部(132−1)の各レジスタ(132a,132b,132c)に対するデータ書き込み処理に先立つ前処理は殆ど不要となり、図8に示されるように、MPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【0037】

[変形例1]

前記出力部(133)は、図3に示される出力部(133−2)のように、前記歩進信号(PS)を生成するための歩進信号生成回路(133a´)と、前記方向信号(DS)を生成するための方向信号生成回路(133b)と、前記歩進信号(PS)中における歩進パルスの出力を停止するための出力停止指示信号(S2)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c´)とを含んでいてもよい。

【0038】

前記絶対位置制御回路(133c´)は、図4に示されるように、前記歩進信号(PS)に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c´−1)と、前記現在位置レジスタ(133c´−1)に格納された現在位置データと前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)との比較に基づいて出力停止指示信号(S2)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−2)とを有し、こうして生成された出力停止指示信号(S2)と方向指定データ(D3)とを出力するように構成されていてもよい。

【0039】

前記歩進信号生成回路(133a´)は、図3に示されるように、前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c´)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されていてもよい。

【0040】

前記方向信号生成回路(133b)は、図3に示されるように、前記絶対位置制御回路(133c´)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0041】

[変形例1の作用効果]

このような構成によれば、基本構成による作用効果に加えて、図4に示されるように、演算回路(1334−2)においては、移動量を計算する機能が不要となり、その分だけ、回路構成が簡素化される利点がある。

【0042】

[変形例2]

出力指示部(132)は、図7に示される出力指示部(132−3)のように、前記レジスタとして、さらに、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ(132f)と、パルス出力数指定データ(D1)を格納するためのパルス出力数指定レジスタ(132g)と、方向指定データを格納するための方向指定レジスタ(132h)とを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号(S4)を生成するように構成されていてもよい。

【0043】

前記相対/絶対・切替信号(S4)が相対位置指定モードを示すときには、前記出力部(133)は、図7に示される出力部(133−4)のように構成することができ、その場合には、前記歩進信号生成回路(133a)は、前記歩進信号生成回路(133a″)のように、前記出力指示信号(S1)のタイミングに応答して、パルス出力数指定レジスタ(132g)に格納されたパルス出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されていてもよい。

【0044】

前記方向信号生成回路(133b)についても、方向信号生成回路(133b´)のように、前記方向指定レジスタ(132h)に格納された方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0045】

前記相対/絶対・切替信号(S4)が絶対位置指定モードを示すときには、前記出力部(133)は、図7に示される出力部(133−4)のように構成することができ、その場合には、前記歩進信号生成回路(133a)は、前記歩進信号生成回路(133a″)のように、前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c″)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されていてもよい。

【0046】

前記方向信号生成回路(133b)は、図7に示される方向信号生成回路(133b´)のように、前記絶対位置制御回路(133c″)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。このとき、絶対位置制御回路(133c″)から出力される方向指定データ(D3)は、言うまでもないが、前記歩進信号(PS)に含まれる歩進パルスを前記方向信号(DS)の論理値に応じて加減算することにより得られた現在位置データと前記絶対位置指定データ(D4)との差の極性から生成されたものであって、方向指定レジスタ132hに格納されたものではない。

【0047】

[変形例2の作用効果]

このような構成によれば、基本構成による作用効果に加えて、相対/絶対切替レジスタ132fに「相対モード」に相当するデータを書き込みさえすれば、従前通りに、「パルス間隔」、「パルス出力数」、及び「歩進方向」を直接に指定することで、所望の信号形態を有する歩進信号PSと方向信号DSとを発生させることができる一方、相対/絶対切替レジスタ132fに「絶対モード」に相当するデータを書き込みさえすれば、「パルス間隔」と「目標位置(絶対位置)」とを指定するだけで、自動的に最適な信号形態を有する歩進信号PSと方向信号DSとを発生させることができ、用途に応じて最適な使い方が可能となる。

【0048】

[変形例3]

前記出力部133は、図1に示される出力部(133−1)のように、前記歩進信号(PS)を生成するための歩進信号生成回路(133a)と、前記方向信号(DS)を生成するための方向信号生成回路(133b)と、目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データ(D1)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c)とを含んでいてもよい。

【0049】

前記絶対位置制御回路(133c)は、図2に示されるように、前記歩進信号に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c−1)と、前記現在位置レジスタ(133c−1)に格納された現在位置データと前記絶対位置指定レジスタに格納された絶対位置指定データ(D4)との差の絶対値から出力数指定データ(D1)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−1)とを有し、こうして生成された出力数指定データ(D1)と方向指定データ(D3)とを前記出力指示信号(S1)に同期して出力するように構成されていてもよい。

【0050】

前記歩進信号生成回路(133a)は、前記出力指示信号(S1)のタイミングに応答して、前記絶対位置制御回路(133c)から出力される出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されていてもよい。

【0051】

前記方向信号生成回路(133b)は、前記絶対位置制御回路(133c)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0052】

[変形例3の作用効果]

このような構成によれば、基本構成による作用効果に加えて、図15に示される従来から使用されている歩進信号生成回路(1223a)が使用できると言う利点がある。

【0053】

[変形例4]

上述の基本構成及び変形例1〜3のいずれかにおいて、前記出力指示部(132)は、図5に示される出力指示部(132−2)のように、前記レジスタとして、さらに、プリセット指定データを格納するためのプリセット指定レジスタ(132d)と、プリセット値指定データを格納するためのプリセット値指定レジスタ(132e)とを含み、かつ前記プリセット指定データが前記プリセット指定レジスタ(132d)に格納されるタイミングに応答して、所定のプリセット指定信号(S3)を生成するように構成されていてもよい。

【0054】

前記絶対位置制御回路(133c)は、図5に示される絶対位置制御回路(133c″)のように、前記プリセット指定信号(S3)に応答して、前記プリセット値指定レジスタ(132e)に格納されたプリセット値指定データで指定されるプリセット値を前記現在位置レジスタ(133c″−1)にプリセットするように構成されていてもよい。

【0055】

[変形例4の作用効果]

このような構成によれば、現在位置を定義するための一次元座標の基準点を自由に決めることができる利点がある。

【0056】

[応用例]

上述の基本構成並びに変形例1〜4にかかるパルス出力装置は、ビルディングブロック型PLCの位置制御ユニットに応用することができる。すなわち、この位置制御ユニットは、CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、以下の構成を有するものである。

【0057】

すなわち、この位置制御ユニットは、前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力装置(122)とを含んでいる。

【0058】

前記MPUシステム(121)は、前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力装置122に対して必要な指令を与えるパルス出力指令処理部(P4)とを含んでいる。

【0059】

そして、前記パルス出力装置としては、基本構成並びに変形例1〜4のいずれかに記載のパルス出力装置が使用されている。

【0060】

[応用例の作用効果]

この位置制御ユニットによれば、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能であるため、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【発明の効果】

【0061】

本発明のパルス出力装置によれば、出力指示部(132)の各レジスタ(132a,132b,132c)に書き込まれるべきデータ(D0,D2,D4)は、いずれも既知のものであるから、出力指示部(132−1)の各レジスタ(132a,132b,132c)に対するデータ書き込み処理に先立つ前処理は殆ど不要となり、図8に示されるように、MPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【発明を実施するための最良の形態】

【0062】

以下に、本発明に係るパルス出力装置の好適な実施の一形態を添付図面を参照しながら詳細に説明する。なお、以下の実施形態は、本発明に係るパルス出力装置をASIC(Application Specific IC)として実現したものである。

【0063】

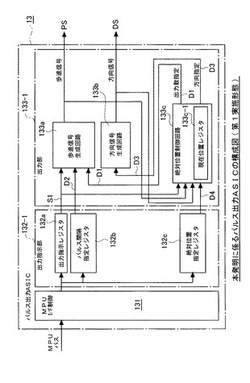

[第1実施形態]

本発明に係るパルス出力装置であるパルス出力ASICの構成図(第1実施形態)が図1に示されている。このパルス出力ASIC13は、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0064】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−1と、出力指示部132−1の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−1とを含んで構成される。

【0065】

出力指示部132−1は、前記レジスタとして、出力指示データD0(図示せず)を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0066】

出力部133−1は、歩進信号PSを生成するための歩進信号生成回路133aと、方向信号DSを生成するための方向信号生成回路133bと、目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データD1と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133cとを含んでいる。

【0067】

図1に示される絶対位置制御回路133cの詳細構成図が、図2にロジックシンボルを用いて概略的に示されている。

【0068】

図2において、現在位置レジスタ133c−1のデータ入力Dには、自己の「Q出力値+1」又は「Q出力値−1」が切替器1333を介して択一的に入力されており、またクロック入力CKには、歩進信号PSが供給され、さらに切替器1333の切替動作は方向信号DSにより制御されている。そのため、現在値レジスタ133c−1には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じて加減算することにより得られた現在位置データが格納される。

【0069】

演算回路1334−1は、現在位置レジスタ133c−1に格納された現在位置データと絶対位置指定レジスタに格納された目標位置に相当する絶対位置指定データD4との差の絶対値から出力数指定データD1を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成する。

【0070】

現在位置及び指定位置が与えられた場合におけるリングカウント動作の説明図が図10に示されている。同図に示されるように、この演算回路1334−1においては、リングカウント動作を想定すると、現在位置<指定位置の場合には歩進方向は時計回り(CW方向)かつ移動量は(指定位置−現在位置)とされるのに対して、現在位置>指定位置の場合には歩進方向は反時計回り(CCW方向)かつ移動量は(現在位置−指定位置)とされ、また現在位置=指定位置の場合には歩進方向は現状維持、移動量は0とされる。

【0071】

こうして生成された出力数指定データD1は、出力指示信号S1の発生タイミングに同期してレジスタ1335にラッチされるから、出力数指定データD1と方向指定データD3とは、出力指示信号S1に同期して外部へと出力されることとなる。

【0072】

歩進信号生成回路133aは、出力指示信号S1の受信タイミングに応答して、絶対位置制御回路133cから出力される出力数指定データD1で指定される個数の歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力する。

【0073】

方向信号生成回路133bは、絶対位置制御回路133cから出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0074】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力数指定データD1及び方向指定データD3は、絶対位置制御回路133cの作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ201)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0075】

このとき、出力指示部132−1の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−1の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0076】

本発明者等の実験によれば、図9に示されるように、歩進パルスの出力中に目標値を「4」に設定したい場合、高周波(例えば、1MHz)出力中であっても、マージン必要なく制御が実装できることが確認された。

【0077】

[第2実施形態]

本発明に係るパルス出力ASICの構成図(第2実施形態)が図3に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0078】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−1と、出力指示部132−1の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−2とを含んで構成される。

【0079】

出力指示部132−1は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0080】

出力部133−2は、歩進信号PSを生成するための歩進信号生成回路133a´と、方向信号DSを生成するための方向信号生成回路133bと、歩進信号PS中における歩進パルスの出力を停止するための出力停止指示信号S2と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133c´とを含んで構成される。

【0081】

図3に示される絶対位置制御回路133c´の詳細構成図が、図4にロジックシンボルを用いて概略的に示されている。

【0082】

図4において、現在位置レジスタ133c´−1のデータ入力Dには、自己の「Q出力値+1」又は「Q出力値−1」が切替器1333を介して択一的に入力されており、またクロック入力CKには歩進信号PSが供給され、さらに切替器1333の切替動作は方向信号DSにより制御されている。そのため、現在値レジスタ133c´−1には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じて加減算することにより得られた現在位置データが格納される。

【0083】

演算回路1334−2は、現在位置レジスタ133c´−1に格納された現在位置データと絶対位置指定レジスタ132cに格納された絶対位置指定データD4との比較に基づいて出力停止指示源信号(現在位置=指定位置の場合、“H”)S2´を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成し、こうして生成された出力停止指示源信号S2´と方向指定データD3とを出力するように構成されている。なお、このとき、出力停止指示源信号S2´の“L”から“H”へのエッジは、微分回路1336を介して微少幅“H”パルスである出力停止指示信号S2に変換される。

【0084】

図3に戻って、歩進信号生成回路133a´は、出力指示信号S1の発生タイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c´から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されている。

【0085】

方向信号生成回路133bは、絶対位置制御回路133c´から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0086】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力停止指示信号S2及び方向指定データD3は、絶対位置制御回路133c´の作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ202)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0087】

このとき、出力指示部132−1の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−1の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0088】

しかも、この第2実施形態にあっては、絶対位置制御回路には、移動量を計算する機能が不要となり、その分だけ、回路構成が簡素化される利点がある。

【0089】

[第3実施形態]

本発明に係るパルス出力ASICの構成図(第3実施形態)が図5に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0090】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−2と、出力指示部132−2の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−3とを含んで構成される。

【0091】

出力指示部132−2は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0092】

加えて、出力指示部132−2には、プリセット指示データを格納するためのプリセット指示レジスタ132dと、プリセット値指定データD5を格納するためのプリセット値指定レジスタ132eとが含まれており、かつプリセット指示データがプリセット指示レジスタに書き込まれるタイミングに応答して、所定のプリセット指示信号S3を生成するように構成されている。

【0093】

出力部133−3は、歩進信号PSを生成するための歩進信号生成回路133a´と、方向信号DSを生成するための方向信号生成回路133bと、歩進信号PS中における歩進パルスの出力を停止するための出力停止指示信号S2と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133c″とを含んで構成される。

【0094】

図5に示される絶対位置制御回路133c″の詳細構成図が、図6にロジックシンボルを用いて概略的に示されている。

【0095】

図6において、現在位置レジスタ133c″−1のデータ入力Dには、プリセット値指定データD5と切替器1333の出力とが、切替器1337を介して択一的に入力される。切替器1333の出力側には、方向信号DSの論理値に応じて、現在位置レジスタ133c″−1の「Q出力値+1」又は「Q出力値−1」が択一的に出力される。切替器1337の切替動作は、出力指示信号S1とプリセット指示信号S3との論理積を生成するANDゲート1338の出力で制御される。現在位置レジスタ133c″−1のクロック入力CKには、ANDゲート1338の出力と歩進信号PSの出力との論理和を生成するORゲートの出力が供給される。

【0096】

そのため、現在位置レジスタ133c″−1には、プリセット指示信号S3の発生タイミングに応答して、任意のプリセット値が現在位置として読み込まれると共に、こうして読み込まれた現在位置は、歩進信号PSに含まれる歩進パルスと方向信号DSの論理値に応じて加減算されて更新される。

【0097】

演算回路1334−2は、現在位置レジスタ133c″−1に格納された現在位置データと絶対位置指定レジスタ132cに格納された絶対位置指定データD4との比較に基づいて出力停止指示源信号(現在位置=指定位置の場合、“H”)S2´を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成し、こうして生成された出力停止指示源信号S2´と方向指定データD3とを出力するように構成されている。なお、このとき、出力停止指示源信号S2´の“L”から“H”へのエッジは、微分回路1336を介して微少幅“H”パルスである出力停止指示信号S2に変換される。

【0098】

図5に戻って、歩進信号生成回路133cは、出力指示信号S1の発生タイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c″から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されている。

【0099】

方向信号生成回路133bは、絶対位置制御回路133c″から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0100】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力停止指示信号S2及び方向指定データD3は、絶対位置制御回路133c″の作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ201)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0101】

このとき、出力指示部132−2の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−2の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0102】

しかも、この第3実施形態にあっては、プリセット指示レジスタ132dとプリセット値指定レジスタ132eとを適宜に操作することで、現在位置を定義するための一次元座標の基準点を自由に決めることができる利点がある。

【0103】

[第4実施形態]

本発明に係るパルス出力ASICの構成図(第4実施形態)が図7に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0104】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−3と、出力指示部132−3の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−4とを含んで構成される。

【0105】

出力指示部132−3は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0106】

また、出力指示部132−3には、プリセット指示データを格納するためのプリセット指示レジスタ132dと、プリセット値指定データD5を格納するためのプリセット値指定レジスタ132eとが含まれており、かつプリセット指示データがプリセット指示レジスタに書き込まれるタイミングに応答して、所定のプリセット指示信号S3を生成するように構成されている。

【0107】

さらに、出力指示部132−3は、前記レジスタとして、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ132fと、パルス出力数指定データD1を格納するためのパルス出力数指定レジスタ132gと、方向指定データD3を格納するための方向指定レジスタ132hとを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号S4を生成するように構成されている。

【0108】

そして、相対/絶対・切替信号S4が相対位置指定モードを示すときには、出力部133−4において、歩進信号生成回路133a″は、出力指示信号S1のタイミングに応答して、パルス出力数指定レジスタ132gに格納されたパルス出力数指定データD1で指定される個数の歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力するように構成されており、同時に、方向信号生成回路133b´は、方向指定レジスタ132hに格納された方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0109】

相対/絶対・切替信号S4が絶対位置指定モードを示すときには、出力部134−4において、歩進信号生成回路133a″は、出力指示信号S1のタイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c″から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されており、同時に、方向信号生成回路133b´は、絶対位置制御回路133c″から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0110】

[第4実施形態の作用効果]

以上の構成によれば、第3実施形態の構成による作用効果に加えて、相対/絶対切替レジスタ132fに「相対モード」に相当するデータを書き込みさえすれば、従前通りに、「パルス間隔」、「パルス出力数」、及び「歩進方向」を直接に指定することで、所望の信号形態を有する歩進信号PSと方向信号DSとを発生させることができる一方、相対/絶対切替レジスタ132fに「絶対モード」に相当するデータを書き込みさえすれば、「パルス間隔」と「目標位置(絶対位置)」とを指定するだけで、自動的に最適な信号形態を有する歩進信号PSと方向信号DSとを発生させることができ、用途に応じて最適な使い方が可能となる。

【0111】

[応用例]

上述の第1乃至第4実施形態にかかるパルス出力ASIC13は、ビルディングブロック型PLC1の位置制御ユニット12に応用することができる。すなわち、この位置制御ユニット12は、図11に示されるように、CPUユニット11や入出力ユニット等と共に使用されるビルディングブロック型PLC1の1要素ユニットであって、以下の構成を有するものである。

【0112】

すなわち、この位置制御ユニット12は、図12に示されるように、CPUユニット11に繋がる内部バス123に接続が可能なMPUシステム121と、MPUシステム121から位置制御指令データが与えられるパルス出力ASIC13(従来例の122に相当)とを含んでいる。

【0113】

MPUシステム121は、図13に示されるように、CPUユニット11から受け取った制御指令を解析する指令解析処理部P1と、指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部P2,P3と、単位変換機能付きの位置制御演算処理部P2,P3から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC13(122に相当)に対して必要な指令を与えるパルス出力指令処理部P4とを含んでいる。そして、パルス出力ASIC13としては、上述の第1乃至第4実施形態にかかるパルス出力ASIC13のいずれかが採用されている。

【0114】

[応用例の作用効果]

この位置制御ユニットによれば、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能であるため、位置制御上の応答性を向上させ、高速かつ正確な微細制御が可能となる。

【産業上の利用可能性】

【0115】

本発明のパルス出力装置(実施形態ではパルス出力ASIC)は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニットにおいて、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に介在することにより、当該位置制御ユニットにおける位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【図面の簡単な説明】

【0116】

【図1】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第1実施形態)である。

【図2】図1に示される絶対位置制御回路の詳細構成図である。

【図3】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第2実施形態)である。

【図4】図3に示される絶対位置制御回路の詳細構成図である。

【図5】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第3実施形態)である。

【図6】図5に示される絶対位置制御回路の詳細構成図である。

【図7】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第4実施形態)である。

【図8】本発明のMPU処理を示すフローチャートである。

【図9】本発明に係るパルス出力装置の一例であるパルス出力ASIC使用時におけるパルス出力波形、現在値、及び指定値変更のタイミングの説明図である。

【図10】現在位置及び指定位置が与えられた場合に於けるリングカウント動作の説明図である。

【図11】位置制御ユニットを含むPLCの応用例を示す模式図である。

【図12】位置制御ユニットの全体構成を示すブロック図である。

【図13】PLCの詳細構成図である。

【図14】位置制御ユニット内のMPU処理の説明図である。

【図15】従来のパルス出力装置の一例であるパルス出力ASICの構成図である。

【図16】従来のMPU処理を示すフローチャートである。

【図17】従来のパルス出力装置の一例であるパルス出力ASIC使用時におけるパルス出力波形、現在値、及び指令値変更のタイミングの説明図である。

【符号の説明】

【0117】

1 PLC

2 モータ駆動装置

3 モータ

4a 上部スプロケット

4b 下部スプロケット

5 チェーン

6 昇降ベース

7 昇降ガイド

11 CPUユニット

12 位置制御ユニット

13 パルス出力ASIC(本発明)

121 MPUシステム

121a MPU

121b ROM

121c RAM

122 パルス出力ASIC(従来例)

123 内部バス

124 バスI/F部

131 MPU・I/F制御部

132−1〜3 出力指示部

132a 出力指示レジスタ

132b パルス間隔指定レジスタ

132c 絶対位置指定レジスタ

132d プリセット指示レジスタ

132e プリセット値指定レジスタ

132f 相対/絶対・切替レジスタ

132g パルス出力数指定レジスタ

132h 方向指定レジスタ

133−1〜4 出力部

133a,133a´,133a″ 歩進信号生成回路

133b,133b´ 方向信号生成回路

133c,133c´,133c″ 絶対位置制御回路

133c−1,133c´−1,133c″−1 現在位置レジスタ

P1 指令解析処理部

P2 単位変換処理部

P3 位置制御演算処理部

P4 パルス出力指令処理部

1221 MPU・I/F制御部

1222 出力指示部

1222a 出力指示レジスタ

1222b パルス出力数指定レジスタ

1222c パルス間隔指定レジスタ

1222d 方向指定レジスタ

S1 出力指示信号

S2 出力停止指示信号

S3 プリセット指示信号

S4 相対/絶対・切替信号

D1 パルス出力数指定データ

D2 パルス間隔指定データ

D3 方向指定データ

D4 絶対位置指定データ

D5 プリセット値指定データ

【技術分野】

【0001】

この発明は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニット等への組み込みに好適なパルス出力装置に関する。

【背景技術】

【0002】

位置制御ユニットを含むビルディングブロック型PLCの応用例を示す模式図が図11に示されている。この応用例は、CPUユニット11と位置制御ユニット12とを含むビルディングブロック型のPLC1によって、昇降ベース6を有するリフト装置を制御するものである。

【0003】

同図において、位置制御の対象となる昇降ベース6は、上部スプロケット4aと下部スプロケット4bとの間に巻き掛けされたチェーン5と一体に結合され、チェーン5の動きに連れて、垂直に延びる昇降ガイド7に案内されつつ上下に移動可能とされている。

【0004】

下部スプロケット4bは、モータ3の駆動軸と連動するものであり、モータ3はモータ駆動装置2の制御下にあって、正逆回転駆動される。モータ3の回転量乃至回転角度と昇降ベース6の昇降量とは、一定の相関が保たれている。そのため、モータ3の回転量乃至回転角度をモータ駆動装置2を介して制御することで、昇降ベース6の高さ位置をオープンループで制御することができる。

【0005】

モータ駆動装置2は、PLC1に組み込まれた位置制御ユニット12から出力される歩進信号PSと方向信号DSとを受けて、モータ3を指定された回転量乃至回転角度だけ回転させるように動作する。

【0006】

歩進信号PSには、パルス数(N)とパルス間隔(T)とで規定される複数の歩進パルス列(N1とT1とで規定される第1歩進パルス列、N2とT2とで規定される第2歩進パルス列、N3とT3とで規定される第3歩進パルス列、・・・NnとTnとで規定される第n歩進パルス列)が順次直列に含まれている。

【0007】

方向進行DSは二値信号であって、その論理値は、モータ3を時計回り(CW)に回転させたいときには第1の論理値(例えば、“H”)、反時計回り(CCW)に回転させたいときには第2の論理値(例えば、“L”)となるように設定されている。

【0008】

歩進信号PSに含まれる歩進パルス1個当たりのモータ回転量乃至回転角度は、モータ駆動装置2によって一定に維持され、その際における回転速度は、パルス間隔(T)により決定され、また回転方向は方向信号DSの論理値により決定され、総回転量乃至回転角度はパルス数(N)によって決定される。

【0009】

そのため、歩進信号PSに含まれるパルス数(N)及びパルス間隔(T)と、方向信号DSの論理値とを制御することで、モータ3の回転量、回転速度、及び回転方向、換言すれば、昇降ベース6の昇降量、昇降速度、及び昇降方向を正確に制御することができるようになっている。

【0010】

位置制御ユニットの全体構成を示すブロック図が図12に、同ユニットを含むPLC全体の詳細構成図が図13に示されている(例えば、特許文献1参照)。

【0011】

図12に示されるように、位置制御ユニット12は、MPUシステム121とパルス出力ASIC122と、それらを繋ぐ内部バス123とを含んで構成されている。MPUシステム121は、システム全体を統括するMPU121aと、MPU121aにて実行されるべきシステムプログラムを格納するROM121bと、MPU121aがシステムプログラムを実行する際にワークエリア等として使用されるRAM121cとを含んで構成されている。なお、バスインタフェース124は、当該位置制御ユニット12をCPUユニット11へと繋がるユニット間接続バスと接続するためのものである。

【0012】

位置制御ユニットを含むPLC全体の詳細構成図が図13に示されている。同図に示されるように、MPUシステム121は、ROM121bに格納されるシステムプログラムを実行することにより、指令解析処理部P1と、単位変換演算処理部P2と、位置制御演算処理部(パルス単位)P3と、パルス出力指令処理部P4とをファームウエアとして実現するものである。

【0013】

ここで、指令解析処理部P1は、バスインタフェース124を介してCPUユニット11から受け取った制御指令(例えば、制御対象となるリフト装置において、「昇降ベース6を高さHmm上昇せよ」といった内容)を解析するものである。

【0014】

単位変換演算処理部P2と位置制御演算処理部P3とは、両者相俟って、指令解析処理部P1における解析の結果として得られた所定の指令単位系(mm)で表現された目標高さに基づいて、図14(a)に示されるように、現在高さから目標高さに至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、図14(b)に示されるように、所定のパルス単位系(歩進パルスの個数)で表現された一連の移動量データとして時系列的に出力するものである。

【0015】

パルス出力指令処理部P4は、位置制御演算処理部P3から時系列的に出力される一連の移動量データに基づいて、対応する位置制御指令データ(出力指示データ、パルス出力数指定データ、パルス間隔指定データ、方向指定データ等)を生成し、それらのデータをパルス出力装置を構成するパルス出力ASIC122内の該当するレジスタに書き込むことにより、歩進信号PS及び方向信号DSの出力を指令するものである。

【0016】

従来のパルス出力ASICの構成図が図15に示されている。同図に示されるように、このパルス出力ASIC122は、MPU・I/F制御部1221と、出力指示部1222と、出力部1223とを含んで構成されている。

【0017】

MPU・I/F制御部1221は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するものである。出力指示部1222は、MPU・I/F制御部121を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含んでいる。出力部1223は、出力指示部1222のレジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する。

【0018】

出力指示部1222は、前記レジスタとして、出力指示データD0(図示せず)を格納するための出力指示レジスタ1222aと、パルス出力数指定データD1を格納するためのパルス出力数指定レジスタ1222bと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ1222cと、方向指定データD3を格納するための方向指定レジスタ1222dとを含んで構成されている。そして、出力指示部1222は、出力指示データD0が出力指示レジスタ1222aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0019】

出力部1223は、出力指示信号S1の受信タイミングに応答して、パルス出力数指定レジスタ1222bに格納されたパルス出力数指定データD1で指定される数の歩進パルスを、パルス間隔指定レジスタ1222cに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力すると共に、方向指定レジスタ1222dに格納される方向指定データD3で指定される方向に対応させて、方向信号DSの論理値を変化させるように構成されている。

【0020】

加えて、出力部1223の内部には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じた方向へとカウントすることにより、現在値データを生成するカウント機能が組み込まれており、こうして生成された現在位置データは、MPU・I/F制御部1221を介して、MPUシステム121側から読み出し可能とされている。

【特許文献1】特開2000−339009号公報

【発明の開示】

【発明が解決しようとする課題】

【0021】

ところで、パルス出力指令処理部P4(図13参照)は、その前段に位置する位置制御演算処理部P3から時系列的に与えられる移動量データ列(図14(b)参照)に基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC122に対して必要な指令を与える。

【0022】

その際における従来のMPU処理(パルス出力指令処理部P4の機能を実現するための処理に相当)を示すフローチャートが図16に示されている。

【0023】

同図に示されるように、このMPU処理にあっては、先ず、ステップ101として、MPU・I/F処理部1221を介して、出力部1223から「現在位置」を読み出し、続くステップ102として、読み出された「現在位置」と既知の「目標位置」との差の絶対値から「パルス出力数」を求める。

【0024】

次に、ステップ103として、「現在位置」と「目標位置」との大小判定を行い、「目標位置≧現在位置」のときには「CW方向指定」として、「目標位置<現在位置」のときには「CCW方向指定」として、「歩進方向」を求める。

【0025】

次に、ステップ104として、MPU・I/F処理部1221を介して、パルス出力数指定レジスタ1222b、パルス間隔指定レジスタ1222c、方向指定レジスタ1222dに、上で求められた「パルス出力数」、既知の速度に対応する「パルス間隔」、上で求められた「歩進方向」をそれぞれ書き込む。

【0026】

最後に、ステップ105として、MPU・I/F処理部1221を介して、出力指示レジスタ1222aに、出力指示データを格納することにより、出力指示信号S1を発生させる。

【0027】

しかしながら、このような従来のMPU処理にあっては、出力指示部1222に対するデータ書き込み処理(ステップ104,105)に先立って、各種の前処理(ステップ101,102,103)が必要であることから、前回の目標位置に対応する歩進パルスの出力中に、次回の目標位置に対応する新たな設定を行おうとすると、歩進パルスの出力周波数が高周波(例えば、1MHz程度)になると、MPUの処理速度との関係により、前回の設定に対応する歩進パルスの出力終了よりもかなり(例えば、歩進パルス2個分程度)早めに、次回の設定を完了させねばならず、位置制御上の応答性に制約を与え、高速かつ微細制御に支障を来す虞があると言う問題点があった(図17参照)。

【0028】

この発明は、上述の問題点に着目してなされたものであり、その目的とするところは、出力指示部に対するデータ書き込み処理に先立つ前処理をできるかぎり不要としてMPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、前回の設定に対応する歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御を可能とするパルス出力ASICを提供することにある。

【0029】

この発明のさらに他の目的とするところは、そのようなパルス出力ASICを組み込むことにより、高速かつ微細制御を可能としたビルディングブロック型PLCの位置制御ユニットを提供することにある。

【0030】

この発明のさらに他の目的並びに作用効果は、明細書の下記の記述を参照することにより、当業者であれば容易に理解される筈である。

【課題を解決するための手段】

【0031】

上述の[発明が解決しようとする課題]は、以下の構成を有するパルス出力ASIC乃至位置制御ユニットにより解決することができると考えられる。

【0032】

[基本構成]

すなわち、本発明のパルス出力装置(13)は、位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するものである。より具体的には、例えば、パルス出力ASIC(一般的には、ワイヤードロジックICであるが、場合によっては、FPGAのようなプログラミング可能な素子であってもよい)として構成することができる。

【0033】

すなわち、このパルス出力装置は、図1、図3、図5、図7に示されるように、前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、前記出力指示部(132)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有する。

【0034】

前記出力指示部(132)は、前記レジスタとして、出力指示データ(D0)を格納するための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を格納するためのパルス間隔指定レジスタ(132b)と、目標位置をその絶対位置で表す絶対位置指定データ(D4)を格納するための絶対位置指定レジスタ(132c)とを含み、かつ前記出力指示データ(D0)が前記出力指示レジスタに書き込まれたタイミングに応答して、所定の出力指示信号(S1)を生成するように構成(132−1)されている。

【0035】

前記出力部(133)は、前記出力指示信号(S1)に応答して、前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)と前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)とに基づいて、前記絶対位置指定データ(D4)で指定される目標位置へと到達するに必要な個数の歩進パルスを前記パルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に出力すると共に、前記目標位置へと到達するに必要な歩進方向に対応させて、前記方向信号(DS)の論理値を変化させるように構成(133−1)されている。

【0036】

[基本構成の作用効果]

このような構成によれば、出力指示部(132−1)の各レジスタ(132a,132b,132c)に書き込まれるべきデータ(D0,D2,D4)は、いずれも既知のものであるから、出力指示部(132−1)の各レジスタ(132a,132b,132c)に対するデータ書き込み処理に先立つ前処理は殆ど不要となり、図8に示されるように、MPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【0037】

[変形例1]

前記出力部(133)は、図3に示される出力部(133−2)のように、前記歩進信号(PS)を生成するための歩進信号生成回路(133a´)と、前記方向信号(DS)を生成するための方向信号生成回路(133b)と、前記歩進信号(PS)中における歩進パルスの出力を停止するための出力停止指示信号(S2)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c´)とを含んでいてもよい。

【0038】

前記絶対位置制御回路(133c´)は、図4に示されるように、前記歩進信号(PS)に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c´−1)と、前記現在位置レジスタ(133c´−1)に格納された現在位置データと前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)との比較に基づいて出力停止指示信号(S2)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−2)とを有し、こうして生成された出力停止指示信号(S2)と方向指定データ(D3)とを出力するように構成されていてもよい。

【0039】

前記歩進信号生成回路(133a´)は、図3に示されるように、前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c´)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されていてもよい。

【0040】

前記方向信号生成回路(133b)は、図3に示されるように、前記絶対位置制御回路(133c´)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0041】

[変形例1の作用効果]

このような構成によれば、基本構成による作用効果に加えて、図4に示されるように、演算回路(1334−2)においては、移動量を計算する機能が不要となり、その分だけ、回路構成が簡素化される利点がある。

【0042】

[変形例2]

出力指示部(132)は、図7に示される出力指示部(132−3)のように、前記レジスタとして、さらに、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ(132f)と、パルス出力数指定データ(D1)を格納するためのパルス出力数指定レジスタ(132g)と、方向指定データを格納するための方向指定レジスタ(132h)とを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号(S4)を生成するように構成されていてもよい。

【0043】

前記相対/絶対・切替信号(S4)が相対位置指定モードを示すときには、前記出力部(133)は、図7に示される出力部(133−4)のように構成することができ、その場合には、前記歩進信号生成回路(133a)は、前記歩進信号生成回路(133a″)のように、前記出力指示信号(S1)のタイミングに応答して、パルス出力数指定レジスタ(132g)に格納されたパルス出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されていてもよい。

【0044】

前記方向信号生成回路(133b)についても、方向信号生成回路(133b´)のように、前記方向指定レジスタ(132h)に格納された方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0045】

前記相対/絶対・切替信号(S4)が絶対位置指定モードを示すときには、前記出力部(133)は、図7に示される出力部(133−4)のように構成することができ、その場合には、前記歩進信号生成回路(133a)は、前記歩進信号生成回路(133a″)のように、前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c″)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されていてもよい。

【0046】

前記方向信号生成回路(133b)は、図7に示される方向信号生成回路(133b´)のように、前記絶対位置制御回路(133c″)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。このとき、絶対位置制御回路(133c″)から出力される方向指定データ(D3)は、言うまでもないが、前記歩進信号(PS)に含まれる歩進パルスを前記方向信号(DS)の論理値に応じて加減算することにより得られた現在位置データと前記絶対位置指定データ(D4)との差の極性から生成されたものであって、方向指定レジスタ132hに格納されたものではない。

【0047】

[変形例2の作用効果]

このような構成によれば、基本構成による作用効果に加えて、相対/絶対切替レジスタ132fに「相対モード」に相当するデータを書き込みさえすれば、従前通りに、「パルス間隔」、「パルス出力数」、及び「歩進方向」を直接に指定することで、所望の信号形態を有する歩進信号PSと方向信号DSとを発生させることができる一方、相対/絶対切替レジスタ132fに「絶対モード」に相当するデータを書き込みさえすれば、「パルス間隔」と「目標位置(絶対位置)」とを指定するだけで、自動的に最適な信号形態を有する歩進信号PSと方向信号DSとを発生させることができ、用途に応じて最適な使い方が可能となる。

【0048】

[変形例3]

前記出力部133は、図1に示される出力部(133−1)のように、前記歩進信号(PS)を生成するための歩進信号生成回路(133a)と、前記方向信号(DS)を生成するための方向信号生成回路(133b)と、目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データ(D1)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c)とを含んでいてもよい。

【0049】

前記絶対位置制御回路(133c)は、図2に示されるように、前記歩進信号に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c−1)と、前記現在位置レジスタ(133c−1)に格納された現在位置データと前記絶対位置指定レジスタに格納された絶対位置指定データ(D4)との差の絶対値から出力数指定データ(D1)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−1)とを有し、こうして生成された出力数指定データ(D1)と方向指定データ(D3)とを前記出力指示信号(S1)に同期して出力するように構成されていてもよい。

【0050】

前記歩進信号生成回路(133a)は、前記出力指示信号(S1)のタイミングに応答して、前記絶対位置制御回路(133c)から出力される出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されていてもよい。

【0051】

前記方向信号生成回路(133b)は、前記絶対位置制御回路(133c)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されていてもよい。

【0052】

[変形例3の作用効果]

このような構成によれば、基本構成による作用効果に加えて、図15に示される従来から使用されている歩進信号生成回路(1223a)が使用できると言う利点がある。

【0053】

[変形例4]

上述の基本構成及び変形例1〜3のいずれかにおいて、前記出力指示部(132)は、図5に示される出力指示部(132−2)のように、前記レジスタとして、さらに、プリセット指定データを格納するためのプリセット指定レジスタ(132d)と、プリセット値指定データを格納するためのプリセット値指定レジスタ(132e)とを含み、かつ前記プリセット指定データが前記プリセット指定レジスタ(132d)に格納されるタイミングに応答して、所定のプリセット指定信号(S3)を生成するように構成されていてもよい。

【0054】

前記絶対位置制御回路(133c)は、図5に示される絶対位置制御回路(133c″)のように、前記プリセット指定信号(S3)に応答して、前記プリセット値指定レジスタ(132e)に格納されたプリセット値指定データで指定されるプリセット値を前記現在位置レジスタ(133c″−1)にプリセットするように構成されていてもよい。

【0055】

[変形例4の作用効果]

このような構成によれば、現在位置を定義するための一次元座標の基準点を自由に決めることができる利点がある。

【0056】

[応用例]

上述の基本構成並びに変形例1〜4にかかるパルス出力装置は、ビルディングブロック型PLCの位置制御ユニットに応用することができる。すなわち、この位置制御ユニットは、CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、以下の構成を有するものである。

【0057】

すなわち、この位置制御ユニットは、前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力装置(122)とを含んでいる。

【0058】

前記MPUシステム(121)は、前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力装置122に対して必要な指令を与えるパルス出力指令処理部(P4)とを含んでいる。

【0059】

そして、前記パルス出力装置としては、基本構成並びに変形例1〜4のいずれかに記載のパルス出力装置が使用されている。

【0060】

[応用例の作用効果]

この位置制御ユニットによれば、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能であるため、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【発明の効果】

【0061】

本発明のパルス出力装置によれば、出力指示部(132)の各レジスタ(132a,132b,132c)に書き込まれるべきデータ(D0,D2,D4)は、いずれも既知のものであるから、出力指示部(132−1)の各レジスタ(132a,132b,132c)に対するデータ書き込み処理に先立つ前処理は殆ど不要となり、図8に示されるように、MPUの負荷を軽減することにより、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能として、位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【発明を実施するための最良の形態】

【0062】

以下に、本発明に係るパルス出力装置の好適な実施の一形態を添付図面を参照しながら詳細に説明する。なお、以下の実施形態は、本発明に係るパルス出力装置をASIC(Application Specific IC)として実現したものである。

【0063】

[第1実施形態]

本発明に係るパルス出力装置であるパルス出力ASICの構成図(第1実施形態)が図1に示されている。このパルス出力ASIC13は、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0064】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−1と、出力指示部132−1の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−1とを含んで構成される。

【0065】

出力指示部132−1は、前記レジスタとして、出力指示データD0(図示せず)を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0066】

出力部133−1は、歩進信号PSを生成するための歩進信号生成回路133aと、方向信号DSを生成するための方向信号生成回路133bと、目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データD1と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133cとを含んでいる。

【0067】

図1に示される絶対位置制御回路133cの詳細構成図が、図2にロジックシンボルを用いて概略的に示されている。

【0068】

図2において、現在位置レジスタ133c−1のデータ入力Dには、自己の「Q出力値+1」又は「Q出力値−1」が切替器1333を介して択一的に入力されており、またクロック入力CKには、歩進信号PSが供給され、さらに切替器1333の切替動作は方向信号DSにより制御されている。そのため、現在値レジスタ133c−1には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じて加減算することにより得られた現在位置データが格納される。

【0069】

演算回路1334−1は、現在位置レジスタ133c−1に格納された現在位置データと絶対位置指定レジスタに格納された目標位置に相当する絶対位置指定データD4との差の絶対値から出力数指定データD1を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成する。

【0070】

現在位置及び指定位置が与えられた場合におけるリングカウント動作の説明図が図10に示されている。同図に示されるように、この演算回路1334−1においては、リングカウント動作を想定すると、現在位置<指定位置の場合には歩進方向は時計回り(CW方向)かつ移動量は(指定位置−現在位置)とされるのに対して、現在位置>指定位置の場合には歩進方向は反時計回り(CCW方向)かつ移動量は(現在位置−指定位置)とされ、また現在位置=指定位置の場合には歩進方向は現状維持、移動量は0とされる。

【0071】

こうして生成された出力数指定データD1は、出力指示信号S1の発生タイミングに同期してレジスタ1335にラッチされるから、出力数指定データD1と方向指定データD3とは、出力指示信号S1に同期して外部へと出力されることとなる。

【0072】

歩進信号生成回路133aは、出力指示信号S1の受信タイミングに応答して、絶対位置制御回路133cから出力される出力数指定データD1で指定される個数の歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力する。

【0073】

方向信号生成回路133bは、絶対位置制御回路133cから出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0074】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力数指定データD1及び方向指定データD3は、絶対位置制御回路133cの作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ201)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0075】

このとき、出力指示部132−1の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−1の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0076】

本発明者等の実験によれば、図9に示されるように、歩進パルスの出力中に目標値を「4」に設定したい場合、高周波(例えば、1MHz)出力中であっても、マージン必要なく制御が実装できることが確認された。

【0077】

[第2実施形態]

本発明に係るパルス出力ASICの構成図(第2実施形態)が図3に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0078】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−1と、出力指示部132−1の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−2とを含んで構成される。

【0079】

出力指示部132−1は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0080】

出力部133−2は、歩進信号PSを生成するための歩進信号生成回路133a´と、方向信号DSを生成するための方向信号生成回路133bと、歩進信号PS中における歩進パルスの出力を停止するための出力停止指示信号S2と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133c´とを含んで構成される。

【0081】

図3に示される絶対位置制御回路133c´の詳細構成図が、図4にロジックシンボルを用いて概略的に示されている。

【0082】

図4において、現在位置レジスタ133c´−1のデータ入力Dには、自己の「Q出力値+1」又は「Q出力値−1」が切替器1333を介して択一的に入力されており、またクロック入力CKには歩進信号PSが供給され、さらに切替器1333の切替動作は方向信号DSにより制御されている。そのため、現在値レジスタ133c´−1には、歩進信号PSに含まれる歩進パルスを方向信号DSの論理値に応じて加減算することにより得られた現在位置データが格納される。

【0083】

演算回路1334−2は、現在位置レジスタ133c´−1に格納された現在位置データと絶対位置指定レジスタ132cに格納された絶対位置指定データD4との比較に基づいて出力停止指示源信号(現在位置=指定位置の場合、“H”)S2´を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成し、こうして生成された出力停止指示源信号S2´と方向指定データD3とを出力するように構成されている。なお、このとき、出力停止指示源信号S2´の“L”から“H”へのエッジは、微分回路1336を介して微少幅“H”パルスである出力停止指示信号S2に変換される。

【0084】

図3に戻って、歩進信号生成回路133a´は、出力指示信号S1の発生タイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c´から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されている。

【0085】

方向信号生成回路133bは、絶対位置制御回路133c´から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0086】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力停止指示信号S2及び方向指定データD3は、絶対位置制御回路133c´の作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ202)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0087】

このとき、出力指示部132−1の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−1の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0088】

しかも、この第2実施形態にあっては、絶対位置制御回路には、移動量を計算する機能が不要となり、その分だけ、回路構成が簡素化される利点がある。

【0089】

[第3実施形態]

本発明に係るパルス出力ASICの構成図(第3実施形態)が図5に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0090】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−2と、出力指示部132−2の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−3とを含んで構成される。

【0091】

出力指示部132−2は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0092】

加えて、出力指示部132−2には、プリセット指示データを格納するためのプリセット指示レジスタ132dと、プリセット値指定データD5を格納するためのプリセット値指定レジスタ132eとが含まれており、かつプリセット指示データがプリセット指示レジスタに書き込まれるタイミングに応答して、所定のプリセット指示信号S3を生成するように構成されている。

【0093】

出力部133−3は、歩進信号PSを生成するための歩進信号生成回路133a´と、方向信号DSを生成するための方向信号生成回路133bと、歩進信号PS中における歩進パルスの出力を停止するための出力停止指示信号S2と目標位置に到達するに必要な歩進方向を表す方向指定データD3とを生成するため絶対位置制御回路133c″とを含んで構成される。

【0094】

図5に示される絶対位置制御回路133c″の詳細構成図が、図6にロジックシンボルを用いて概略的に示されている。

【0095】

図6において、現在位置レジスタ133c″−1のデータ入力Dには、プリセット値指定データD5と切替器1333の出力とが、切替器1337を介して択一的に入力される。切替器1333の出力側には、方向信号DSの論理値に応じて、現在位置レジスタ133c″−1の「Q出力値+1」又は「Q出力値−1」が択一的に出力される。切替器1337の切替動作は、出力指示信号S1とプリセット指示信号S3との論理積を生成するANDゲート1338の出力で制御される。現在位置レジスタ133c″−1のクロック入力CKには、ANDゲート1338の出力と歩進信号PSの出力との論理和を生成するORゲートの出力が供給される。

【0096】

そのため、現在位置レジスタ133c″−1には、プリセット指示信号S3の発生タイミングに応答して、任意のプリセット値が現在位置として読み込まれると共に、こうして読み込まれた現在位置は、歩進信号PSに含まれる歩進パルスと方向信号DSの論理値に応じて加減算されて更新される。

【0097】

演算回路1334−2は、現在位置レジスタ133c″−1に格納された現在位置データと絶対位置指定レジスタ132cに格納された絶対位置指定データD4との比較に基づいて出力停止指示源信号(現在位置=指定位置の場合、“H”)S2´を生成すると共に、現在位置データと絶対位置指定データD4との差の極性から判定される歩進方向を示す方向指定データD3を生成し、こうして生成された出力停止指示源信号S2´と方向指定データD3とを出力するように構成されている。なお、このとき、出力停止指示源信号S2´の“L”から“H”へのエッジは、微分回路1336を介して微少幅“H”パルスである出力停止指示信号S2に変換される。

【0098】

図5に戻って、歩進信号生成回路133cは、出力指示信号S1の発生タイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c″から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されている。

【0099】

方向信号生成回路133bは、絶対位置制御回路133c″から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0100】

以上の構成によれば、歩進信号PS及び方向信号DSの生成に必要とされる出力停止指示信号S2及び方向指定データD3は、絶対位置制御回路133c″の作用により自動的に作り出されることとなるため、MPUシステム121の側では、図8に示されるように、パルス間隔指定レジスタ132b、絶対位置指定レジスタ132cに、パルス間隔指定データD2、目標位置に相当する絶対位置指定データD4を書き込んだのち(ステップ201)、出力指示レジスタ132aに出力指示データD0を書き込むだけで(ステップ201)、目標位置に所定速度で接近するに要する歩進信号PS及び方向信号DSを発生させることができる。

【0101】

このとき、出力指示部132−2の各レジスタ132a,132b,132cに書き込まれるべきデータD0,D2,D4は、いずれも既知のものであるから、出力指示部132−2の各レジスタ132a,132b,132cに対するデータ書き込み処理に先立つ前処理は殆ど不要となって、その分だけMPUの負荷を軽減することができ、前回の目標位置に対応する歩進パルスの出力中であっても、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定が可能となり、位置制御上の応答性を向上させ、高速かつ微細な制御が可能となるのである。

【0102】

しかも、この第3実施形態にあっては、プリセット指示レジスタ132dとプリセット値指定レジスタ132eとを適宜に操作することで、現在位置を定義するための一次元座標の基準点を自由に決めることができる利点がある。

【0103】

[第4実施形態]

本発明に係るパルス出力ASICの構成図(第4実施形態)が図7に示されている。このパルス出力ASIC13も、先に図11〜図14を参照して説明したように、位置制御指令データを生成するMPUシステム121と、一連の歩進用パルス列を含む歩進信号PSと歩進方向に対応する論理値を有する方向信号DSとに基づいてモータ等の駆動源を指定された方向へと歩進するモータ駆動装置2との間に介在され、MPUシステム121から与えられる位置制御指令データに基づいて、それに対応する歩進信号PSと方向信号DSとを生成出力するものである。

【0104】

同パルス出力ASIC13は、MPUシステム121に繋がるMPUバス123に接続されて、MPUシステム121との間におけるインタフェースとして機能するMPU・I/F制御部131と、MPU・I/F制御部131を介してMPUシステム121側から位置制御指令データを書き込み可能なレジスタを含む出力指示部132−3と、出力指示部132−3の前記レジスタに書き込まれた位置制御指令データに基づいて歩進信号PSと方向信号DSとを生成出力する出力部133−4とを含んで構成される。

【0105】

出力指示部132−3は、前記レジスタとして、出力指示データD0を格納するための出力指示レジスタ132aと、パルス間隔指定データD2を格納するためのパルス間隔指定レジスタ132bと、目標位置をその絶対位置で表す絶対位置指定データD4を格納するための絶対位置指定レジスタ132cとを含み、かつ出力指示データD0が出力指示レジスタ132aに書き込まれたタイミングに応答して、所定の出力指示信号S1を生成するように構成されている。

【0106】

また、出力指示部132−3には、プリセット指示データを格納するためのプリセット指示レジスタ132dと、プリセット値指定データD5を格納するためのプリセット値指定レジスタ132eとが含まれており、かつプリセット指示データがプリセット指示レジスタに書き込まれるタイミングに応答して、所定のプリセット指示信号S3を生成するように構成されている。

【0107】

さらに、出力指示部132−3は、前記レジスタとして、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ132fと、パルス出力数指定データD1を格納するためのパルス出力数指定レジスタ132gと、方向指定データD3を格納するための方向指定レジスタ132hとを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号S4を生成するように構成されている。

【0108】

そして、相対/絶対・切替信号S4が相対位置指定モードを示すときには、出力部133−4において、歩進信号生成回路133a″は、出力指示信号S1のタイミングに応答して、パルス出力数指定レジスタ132gに格納されたパルス出力数指定データD1で指定される個数の歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力するように構成されており、同時に、方向信号生成回路133b´は、方向指定レジスタ132hに格納された方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0109】

相対/絶対・切替信号S4が絶対位置指定モードを示すときには、出力部134−4において、歩進信号生成回路133a″は、出力指示信号S1のタイミングに応答して、歩進パルスを、パルス間隔指定レジスタ132bに格納されたパルス間隔指定データD2で指定されるパルス間隔で、歩進信号PS中に出力開始すると共に、絶対位置制御回路133c″から出力される出力停止指示信号S2に応答して、歩進パルスの出力を停止するように構成されており、同時に、方向信号生成回路133b´は、絶対位置制御回路133c″から出力される方向指定データD3で示される方向に対応する論理値を有する方向信号DSを出力するように構成されている。

【0110】

[第4実施形態の作用効果]

以上の構成によれば、第3実施形態の構成による作用効果に加えて、相対/絶対切替レジスタ132fに「相対モード」に相当するデータを書き込みさえすれば、従前通りに、「パルス間隔」、「パルス出力数」、及び「歩進方向」を直接に指定することで、所望の信号形態を有する歩進信号PSと方向信号DSとを発生させることができる一方、相対/絶対切替レジスタ132fに「絶対モード」に相当するデータを書き込みさえすれば、「パルス間隔」と「目標位置(絶対位置)」とを指定するだけで、自動的に最適な信号形態を有する歩進信号PSと方向信号DSとを発生させることができ、用途に応じて最適な使い方が可能となる。

【0111】

[応用例]

上述の第1乃至第4実施形態にかかるパルス出力ASIC13は、ビルディングブロック型PLC1の位置制御ユニット12に応用することができる。すなわち、この位置制御ユニット12は、図11に示されるように、CPUユニット11や入出力ユニット等と共に使用されるビルディングブロック型PLC1の1要素ユニットであって、以下の構成を有するものである。

【0112】

すなわち、この位置制御ユニット12は、図12に示されるように、CPUユニット11に繋がる内部バス123に接続が可能なMPUシステム121と、MPUシステム121から位置制御指令データが与えられるパルス出力ASIC13(従来例の122に相当)とを含んでいる。

【0113】

MPUシステム121は、図13に示されるように、CPUユニット11から受け取った制御指令を解析する指令解析処理部P1と、指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部P2,P3と、単位変換機能付きの位置制御演算処理部P2,P3から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力ASIC13(122に相当)に対して必要な指令を与えるパルス出力指令処理部P4とを含んでいる。そして、パルス出力ASIC13としては、上述の第1乃至第4実施形態にかかるパルス出力ASIC13のいずれかが採用されている。

【0114】

[応用例の作用効果]

この位置制御ユニットによれば、歩進パルスの出力終了寸前まで、次回の目標位置に対応する新たな設定を可能であるため、位置制御上の応答性を向上させ、高速かつ正確な微細制御が可能となる。

【産業上の利用可能性】

【0115】

本発明のパルス出力装置(実施形態ではパルス出力ASIC)は、例えば、ビルディングブロック型PLCの一要素ユニットである位置制御ユニットにおいて、位置制御指令データを生成するMPUシステムと、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置との間に介在することにより、当該位置制御ユニットにおける位置制御上の応答性を向上させ、高速かつ微細制御が可能となる。

【図面の簡単な説明】

【0116】

【図1】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第1実施形態)である。

【図2】図1に示される絶対位置制御回路の詳細構成図である。

【図3】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第2実施形態)である。

【図4】図3に示される絶対位置制御回路の詳細構成図である。

【図5】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第3実施形態)である。

【図6】図5に示される絶対位置制御回路の詳細構成図である。

【図7】本発明に係るパルス出力装置の一例であるパルス出力ASICの構成図(第4実施形態)である。

【図8】本発明のMPU処理を示すフローチャートである。

【図9】本発明に係るパルス出力装置の一例であるパルス出力ASIC使用時におけるパルス出力波形、現在値、及び指定値変更のタイミングの説明図である。

【図10】現在位置及び指定位置が与えられた場合に於けるリングカウント動作の説明図である。

【図11】位置制御ユニットを含むPLCの応用例を示す模式図である。

【図12】位置制御ユニットの全体構成を示すブロック図である。

【図13】PLCの詳細構成図である。

【図14】位置制御ユニット内のMPU処理の説明図である。

【図15】従来のパルス出力装置の一例であるパルス出力ASICの構成図である。

【図16】従来のMPU処理を示すフローチャートである。

【図17】従来のパルス出力装置の一例であるパルス出力ASIC使用時におけるパルス出力波形、現在値、及び指令値変更のタイミングの説明図である。

【符号の説明】

【0117】

1 PLC

2 モータ駆動装置

3 モータ

4a 上部スプロケット

4b 下部スプロケット

5 チェーン

6 昇降ベース

7 昇降ガイド

11 CPUユニット

12 位置制御ユニット

13 パルス出力ASIC(本発明)

121 MPUシステム

121a MPU

121b ROM

121c RAM

122 パルス出力ASIC(従来例)

123 内部バス

124 バスI/F部

131 MPU・I/F制御部

132−1〜3 出力指示部

132a 出力指示レジスタ

132b パルス間隔指定レジスタ

132c 絶対位置指定レジスタ

132d プリセット指示レジスタ

132e プリセット値指定レジスタ

132f 相対/絶対・切替レジスタ

132g パルス出力数指定レジスタ

132h 方向指定レジスタ

133−1〜4 出力部

133a,133a´,133a″ 歩進信号生成回路

133b,133b´ 方向信号生成回路

133c,133c´,133c″ 絶対位置制御回路

133c−1,133c´−1,133c″−1 現在位置レジスタ

P1 指令解析処理部

P2 単位変換処理部

P3 位置制御演算処理部

P4 パルス出力指令処理部

1221 MPU・I/F制御部

1222 出力指示部

1222a 出力指示レジスタ

1222b パルス出力数指定レジスタ

1222c パルス間隔指定レジスタ

1222d 方向指定レジスタ

S1 出力指示信号

S2 出力停止指示信号

S3 プリセット指示信号

S4 相対/絶対・切替信号

D1 パルス出力数指定データ

D2 パルス間隔指定データ

D3 方向指定データ

D4 絶対位置指定データ

D5 プリセット値指定データ

【特許請求の範囲】

【請求項1】

位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力装置(13)であって、

前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、

前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、

前記出力指示部(132−1)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有し、

前記出力指示部(132)は、

前記レジスタとして、出力指示データを格納するための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を格納するためのパルス間隔指定レジスタ(132b)と、目標位置をその絶対位置で表す絶対位置指定データ(D4)を格納するための絶対位置指定レジスタ(132c)とを含み、かつ前記出力指示データが前記出力指示レジスタに書き込まれたタイミングに応答して、所定の出力指示信号(S1)を生成するように構成(132−1)されており、

前記出力部(133)は、

前記出力指示信号(S1)に応答して、前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)と前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)とに基づいて、前記絶対位置指定データ(D4)で指定される目標位置へと到達するに必要な個数の歩進パルスを前記パルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に出力すると共に、前記目標位置へと到達するに必要な歩進方向に対応させて、前記方向信号(DS)の論理値を変化させるように構成(133−1)されている、ことを特徴とするパルス出力装置。

【請求項2】

前記出力部(133)は、

前記歩進信号(PS)を生成するための歩進信号生成回路(133a´)と、

前記方向信号(DS)を生成するための方向信号生成回路(133b)と、

前記歩進信号(PS)中における歩進パルスの出力を停止するための出力停止指示信号(S2)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c´)とを含み(133−2)、

前記絶対位置制御回路(133c´)は、

前記歩進信号(PS)に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c´−1)と、

前記現在位置レジスタ(133c´−1)に格納された現在位置データと前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)との比較に基づいて出力停止指示信号(S2)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−2)とを有し、

こうして生成された出力停止指示信号(S2)と方向指定データ(D3)とを出力するように構成されており、

前記歩進信号生成回路(133a´)は、

前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c´)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c´)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されている、ことを特徴とする請求項1に記載のパルス出力装置(13)。

【請求項3】

前記出力指示部(132)は、

前記レジスタとして、さらに、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ(132f)と、パルス出力数指定データ(D1)を格納するためのパルス出力数指定レジスタ(132g)と、方向指定データを格納するための方向指定レジスタ(132h)とを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号(S4)を生成するように構成(132−3)されており、

前記相対/絶対・切替信号(S4)が相対位置指定モードを示すときには、

前記出力部(133)において、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、パルス出力数指定レジスタ(132g)に格納されたパルス出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成(133a″)されており、かつ

前記方向信号生成回路(133b)は、

前記方向指定レジスタ(132h)に格納された方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成(133b´)されており、

前記相対/絶対・切替信号(S4)が絶対位置指定モードを示すときには、

前記出力部(133)において、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c″)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成(133a″)されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c″)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成(133b´)されている、ことを特徴とする請求項2に記載のパルス出力装置。

【請求項4】

前記出力部(133)は、

前記歩進信号(PS)を生成するための歩進信号生成回路(133a)と、

前記方向信号(DS)を生成するための方向信号生成回路(133b)と、

目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データ(D1)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c)とを含み、

前記絶対位置制御回路(133c)は、

前記歩進信号に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c−1)と、

前記現在位置レジスタ(133c−1)に格納された現在位置データと前記絶対位置指定レジスタに格納された絶対位置指定データ(D4)との差の絶対値から出力数指定データ(D1)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−1)とを有し、

こうして生成された出力数指定データ(D1)と方向指定データ(D3)とを前記出力指示信号(S1)に同期して出力するように構成されており、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、前記絶対位置制御回路(133c)から出力される出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されている、ことを特徴とする請求項1に記載のパルス出力装置。

【請求項5】

前記出力指示部(132)は、

前記レジスタとして、さらに、プリセット指定データを格納するためのプリセット指定レジスタ(132d)と、プリセット値指定データを格納するためのプリセット値指定レジスタ(132e)とを含み、かつ前記プリセット指定データが前記プリセット指定レジスタ(132d)に格納されるタイミングに応答して、所定のプリセット指定信号(S3)を生成するように構成(132−2)されており、

前記絶対位置制御回路(133c)は、

前記プリセット指定信号(S3)に応答して、前記プリセット値指定レジスタ(132e)に格納されたプリセット値指定データで指定されるプリセット値を前記現在位置レジスタ(133c″−1)にプリセットするように構成(133c″)されている、ことを特徴とする請求項2〜4のいずれかに記載のパルス出力装置。

【請求項6】

CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、

前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含み、

前記MPUシステム(121)は、

前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、

前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、

前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力装置(122)に対して必要な指令を与えるパルス出力指令処理部(P4)とを含み、

前記パルス出力装置としては、請求項1〜5のいずれかに記載のパルス出力装置が使用されている、ことを特徴とするPLCの位置制御ユニット。

【請求項1】

位置制御指令データを生成するMPUシステム(121)と、一連の歩進用パルス列を含む歩進信号(PS)と歩進方向に対応する論理値を有する方向信号(DS)とに基づいてモータ等の駆動源を指定された方向へと歩進する駆動装置(2)との間に介在され、前記MPUシステム(121)から与えられる位置制御指令データに基づいて、それに対応する前記歩進信号(PS)と前記方向信号(DS)とを生成出力するパルス出力装置(13)であって、

前記MPUシステム(121)に繋がるMPUバス(123)に接続されて、MPUシステム(121)との間におけるインタフェースとして機能するMPU・I/F制御部(131)と、

前記MPU・I/F制御部(131)を介して前記MPUシステム(121)側から前記位置制御指令データを書き込み可能なレジスタを含む出力指示部(132)と、

前記出力指示部(132−1)の前記レジスタに書き込まれた位置制御指令データに基づいて前記歩進信号(PS)と前記方向信号(DS)とを生成出力する出力部(133)とを有し、

前記出力指示部(132)は、

前記レジスタとして、出力指示データを格納するための出力指示レジスタ(132a)と、パルス間隔指定データ(D2)を格納するためのパルス間隔指定レジスタ(132b)と、目標位置をその絶対位置で表す絶対位置指定データ(D4)を格納するための絶対位置指定レジスタ(132c)とを含み、かつ前記出力指示データが前記出力指示レジスタに書き込まれたタイミングに応答して、所定の出力指示信号(S1)を生成するように構成(132−1)されており、

前記出力部(133)は、

前記出力指示信号(S1)に応答して、前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)と前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)とに基づいて、前記絶対位置指定データ(D4)で指定される目標位置へと到達するに必要な個数の歩進パルスを前記パルス間隔指定データ(D2)で指定されるパルス間隔で前記歩進信号(PS)中に出力すると共に、前記目標位置へと到達するに必要な歩進方向に対応させて、前記方向信号(DS)の論理値を変化させるように構成(133−1)されている、ことを特徴とするパルス出力装置。

【請求項2】

前記出力部(133)は、

前記歩進信号(PS)を生成するための歩進信号生成回路(133a´)と、

前記方向信号(DS)を生成するための方向信号生成回路(133b)と、

前記歩進信号(PS)中における歩進パルスの出力を停止するための出力停止指示信号(S2)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c´)とを含み(133−2)、

前記絶対位置制御回路(133c´)は、

前記歩進信号(PS)に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c´−1)と、

前記現在位置レジスタ(133c´−1)に格納された現在位置データと前記絶対位置指定レジスタ(132c)に格納された絶対位置指定データ(D4)との比較に基づいて出力停止指示信号(S2)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−2)とを有し、

こうして生成された出力停止指示信号(S2)と方向指定データ(D3)とを出力するように構成されており、

前記歩進信号生成回路(133a´)は、

前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c´)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c´)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されている、ことを特徴とする請求項1に記載のパルス出力装置(13)。

【請求項3】

前記出力指示部(132)は、

前記レジスタとして、さらに、位置指定モードを相対位置指定モードと絶対位置指定モードとに切り替えるための相対/絶対・切替データを格納するための相対/絶対・切替レジスタ(132f)と、パルス出力数指定データ(D1)を格納するためのパルス出力数指定レジスタ(132g)と、方向指定データを格納するための方向指定レジスタ(132h)とを含み、かつ前記相対/絶対・切替レジスタ(132f)に書き込まれた前記相対/絶対・切替データに基づいて、所定の相対/絶対・切替信号(S4)を生成するように構成(132−3)されており、

前記相対/絶対・切替信号(S4)が相対位置指定モードを示すときには、

前記出力部(133)において、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、パルス出力数指定レジスタ(132g)に格納されたパルス出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成(133a″)されており、かつ

前記方向信号生成回路(133b)は、

前記方向指定レジスタ(132h)に格納された方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成(133b´)されており、

前記相対/絶対・切替信号(S4)が絶対位置指定モードを示すときには、

前記出力部(133)において、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、前記歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力開始すると共に、前記絶対位置制御回路(133c″)から出力される出力停止指示信号(S2)に応答して、前記歩進パルスの出力を停止するように構成(133a″)されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c″)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成(133b´)されている、ことを特徴とする請求項2に記載のパルス出力装置。

【請求項4】

前記出力部(133)は、

前記歩進信号(PS)を生成するための歩進信号生成回路(133a)と、

前記方向信号(DS)を生成するための方向信号生成回路(133b)と、

目標位置に到達するに必要な歩進パルスの個数を表す出力数指定データ(D1)と目標位置に到達するに必要な歩進方向を表す方向指定データ(D3)とを生成するため絶対位置制御回路(133c)とを含み、

前記絶対位置制御回路(133c)は、

前記歩進信号に含まれる歩進パルスを前記方向信号の論理値に応じて加減算することにより得られた現在位置データを格納するための現在位置レジスタ(133c−1)と、

前記現在位置レジスタ(133c−1)に格納された現在位置データと前記絶対位置指定レジスタに格納された絶対位置指定データ(D4)との差の絶対値から出力数指定データ(D1)を生成すると共に、前記現在位置データと前記絶対位置指定データ(D4)との差の極性から判定される歩進方向を示す方向指定データ(D3)を生成する演算回路(1334−1)とを有し、

こうして生成された出力数指定データ(D1)と方向指定データ(D3)とを前記出力指示信号(S1)に同期して出力するように構成されており、

前記歩進信号生成回路(133a)は、

前記出力指示信号(S1)のタイミングに応答して、前記絶対位置制御回路(133c)から出力される出力数指定データ(D1)で指定される個数の歩進パルスを、前記パルス間隔指定レジスタ(132b)に格納されたパルス間隔指定データ(D2)で指定されるパルス間隔で、前記歩進信号(PS)中に出力するように構成されており、

前記方向信号生成回路(133b)は、

前記絶対位置制御回路(133c)から出力される方向指定データ(D3)で示される方向に対応する論理値を有する方向信号(DS)を出力するように構成されている、ことを特徴とする請求項1に記載のパルス出力装置。

【請求項5】

前記出力指示部(132)は、

前記レジスタとして、さらに、プリセット指定データを格納するためのプリセット指定レジスタ(132d)と、プリセット値指定データを格納するためのプリセット値指定レジスタ(132e)とを含み、かつ前記プリセット指定データが前記プリセット指定レジスタ(132d)に格納されるタイミングに応答して、所定のプリセット指定信号(S3)を生成するように構成(132−2)されており、

前記絶対位置制御回路(133c)は、

前記プリセット指定信号(S3)に応答して、前記プリセット値指定レジスタ(132e)に格納されたプリセット値指定データで指定されるプリセット値を前記現在位置レジスタ(133c″−1)にプリセットするように構成(133c″)されている、ことを特徴とする請求項2〜4のいずれかに記載のパルス出力装置。

【請求項6】

CPUユニット(11)や入出力ユニット等と共に使用されるビルディングブロック型PLC(12)の1要素ユニットであって、

前記CPUユニット(11)に繋がる内部バス(123)に接続が可能なMPUシステム(121)と、前記MPUシステム(121)から位置制御指令データが与えられるパルス出力ASIC(122)とを含み、

前記MPUシステム(121)は、

前記CPUユニットから受け取った制御指令を解析する指令解析処理部(P1)と、

前記指令解析処理部における解析の結果として得られた所定の指令単位系で表現された目標位置に基づいて、現在位置から目標位置に至る速度プロファイルの各時分割瞬時値に相当する一連の速度を算出し、所定のパルス単位系で表現された一連の移動量データとして時系列的に出力する単位変換機能付きの位置制御演算処理部(P2,P3)と、

前記単位変換機能付きの位置制御演算処理部(P2,P3)から時系列的に出力される一連の移動量データのそれぞれに基づいて、当面の目標位置データと速度データとを対として次々と決定し、それらの決定された各データ対(目標位置データと速度データ)に基づいて、パルス出力装置(122)に対して必要な指令を与えるパルス出力指令処理部(P4)とを含み、

前記パルス出力装置としては、請求項1〜5のいずれかに記載のパルス出力装置が使用されている、ことを特徴とするPLCの位置制御ユニット。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2010−140341(P2010−140341A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−317164(P2008−317164)

【出願日】平成20年12月12日(2008.12.12)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月12日(2008.12.12)

【出願人】(000002945)オムロン株式会社 (3,542)

【Fターム(参考)】

[ Back to top ]