パルス幅変調回路及びそれを用いたスイッチングアンプ

【課題】パルス幅変調回路の簡素化、省スペース化、低コスト化を図る。

【解決手段】パルス幅変調回路1は、第1,第2コンデンサC1,C2にオーディオ信号eSの電圧に比例した電流による充電動作と定電流による放電動作を互いに逆動作と成る関係で行わせることによりパスル幅変調信号PWMoutを生成する。第1,第2コンデンサC1,C2の充電動作を制御するためのスイッチ回路と差動増幅回路及び充電電流生成回路からなる充電電流を生成する回路構成とを同一構成とし、差動増幅回路を共用する構成とする。また、第1,第2コンデンサC1,C2の放電動作を制御するためのスイッチ回路と放電用定電流回路を同一構成とする。更にこれらの電源を±Vの2種類の電源で構成する。これにより、部品の共通化、部品数の低減を可能になる。

【解決手段】パルス幅変調回路1は、第1,第2コンデンサC1,C2にオーディオ信号eSの電圧に比例した電流による充電動作と定電流による放電動作を互いに逆動作と成る関係で行わせることによりパスル幅変調信号PWMoutを生成する。第1,第2コンデンサC1,C2の充電動作を制御するためのスイッチ回路と差動増幅回路及び充電電流生成回路からなる充電電流を生成する回路構成とを同一構成とし、差動増幅回路を共用する構成とする。また、第1,第2コンデンサC1,C2の放電動作を制御するためのスイッチ回路と放電用定電流回路を同一構成とする。更にこれらの電源を±Vの2種類の電源で構成する。これにより、部品の共通化、部品数の低減を可能になる。

【発明の詳細な説明】

【技術分野】

【0001】

本願発明は、例えばオーディオ信号をパルス幅変調(PWM)してその変調信号を出力するパルス幅変調回路及びそれを用いたスイッチングアンプに関するものである。

【背景技術】

【0002】

従来、オーディオアンプに用いられるスイッチングアンプでは、例えば入力信号としてのオーディオ信号をパルス幅変調し、その変調信号を出力するパルス幅変調回路が用いられているものが提案されている。このスイッチングアンプでは、パルス幅変調回路から出力される変調信号に基づいて所定の電源電圧がスイッチングされ、スイッチングされた出力信号が例えばローパスフィルタを通して負荷(例えばスピーカ)に出力される。

【0003】

図8は、従来のスイッチングアンプの一例を示す構成図である。このスイッチングアンプは、オーディオ信号発生源AUに接続されたパルス幅変調回路1と、スイッチング回路2と、ローパスフィルタ回路3と、正負の電源電圧+EB,−EBを供給する第1電源4及び第2電源5とを備えている。ローパスフィルタ回路3には、負荷RLとしてのスピーカが接続されている。

【0004】

パルス幅変調回路1では、オーディオ信号発生源AUから出力された入力信号としてのオーディオ信号eSをパルス幅変調することにより変調信号PWMoutが生成される。スイッチング回路2では、変調信号PWMoutと逆位相の変調信号PWMout’が生成される。

【0005】

スイッチング回路2では正の電源電圧+EBを供給する第1電源4と負の電源電圧−EBを供給する第2電源5との間にスイッチ素子SW−Aとスイッチ素子SW−Bの直列回路が接続されている。スイッチング回路2では、変調信号PWMout及び変調信号PWMout'に基づいて、スイッチ素子SW−A,SW−Bのオン・オフ動作を制御することにより電源電圧+EB,−EBが交互にローパスフィルタ回路3に出力される。この出力は、コイルL0及びコンデンサC0のL型回路からなるローパスフィルタ回路3によって高周波成分が除去され、ローパスフィルタ回路3の出力(増幅されたオーディオ信号)は、負荷RL(スピーカ)に供給されることにより音声として出力される。

【0006】

例えば、特許文献1には、オーディオ信号eSに基づいてPWM変調信号を生成するパルス幅変調回路が提案されている。このパルス幅変調回路では、以下の原理に基づいてPWM変調信号が生成される。

(1)オーディオ信号eS(電圧信号)のレベルを所定の周期Tでサンプリングする。

(2)サンプリングした電圧値を電流値に変換し、その電流値でT/2の期間(充電期間)だけコンデンサを充電する。

(3)T/2の充電期間の充電動作後に、一定の電流値でT/2の時間だけコンデンサの蓄積電荷を放電する。

(4)このコンデンサの放電時間をハイレベル期間とするパルスを生成する。この場合、コンデンサの充電電圧が高いときには、放電動作を行なう期間(T/2の放電期間)内における放電時間(蓄積電荷を放出する時間)は長くなり、パルス幅が長くなる。一方、コンデンサの充電電圧が低いときには、放電期間内における放電時間は短くなり、パルス幅が短くなる。

(5)上記の充放電動作は、2つのコンデンサについて行なうようにし、これらの充放電動作をT/2の時間だけずらすことによりそれぞれのパルス信号を生成し、両者を合成してPWM変調信号を生成する。

【0007】

図9は、特許文献1に提案されているパルス幅変調回路を機能ブロックで示した図である。

【0008】

パルス幅変調回路1は、同図に示すように、クロック生成回路100と、電圧−電流変換回路101と、第1及び第2コンデンサC1,C2と、スイッチ回路102と、放電用定電流回路103と、第1及び第2パルス生成回路104,105と、パルス合成回路106とによって構成されている。スイッチ回路102は、それぞれ2つずつのスイッチを有する第1及び第2スイッチ部102a,102bによって構成されている。

【0009】

電圧−電流変換回路101は、オーディオ信号発生源AU(図8参照)から供給されるオーディオ信号eS(電圧信号)を当該オーディオ信号eSの振幅に電流値が比例する電流信号に変換する。クロック生成回路100は、周期Tでデューティ比50%のパルス信号からなる第1制御信号φ1と、第1制御信号φ1とはハイレベルとローレベルが逆になっている第2制御信号φ2を生成する。第1スイッチ部102a内の一方のスイッチ(電圧−電流変換回路101に接続されたスイッチ)のオン・オフ動作は第1制御信号φ1によって制御され、第2スイッチ部102b内の一方のスイッチ(電圧−電流変換回路101に接続されたスイッチ)のオン・オフ動作は第2制御信号φ2によって制御される。

【0010】

第1スイッチ部102a内の一方のスイッチがオンになると、第1コンデンサC1が電圧−電流変換回路101から出力される電流信号によって充電され、第2スイッチ部102b内の一方のスイッチがオンになると、第2コンデンサC2が電圧−電流変換回路101から出力される電流信号によって充電される。

【0011】

第1パルス生成回路104は、第1コンデンサC1が放電開始時のレベルから所定の基準レベルに変化するまでの放電時間をパルス幅とするパルス信号rsout1と、第1スイッチ部102a内の他方のスイッチ(放電用定電流回路103に接続されたスイッチ)のオン・オフ動作を制御する第3制御信号φ3とを生成する。第2パルス生成回路105は、第2コンデンサC2が放電開始時のレベルから上記の基準レベルに変化するまでの放電時間をパルス幅とするパルス信号rsout2と、第2スイッチ部102b内の他方のスイッチ(放電用定電流回路103に接続されたスイッチ)のオン・オフ動作を制御する第4制御信号φ4とを生成する。

【0012】

第3制御信号φ3は、第1制御信号φ1のローレベル期間内にハイレベル期間が生じるパルス信号である。第1スイッチ部102a内の他方のスイッチがオンになると、第1コンデンサC1に蓄積された電荷が放電用定電流回路103によって一定の電流で放電される。第4制御信号φ4は、第2制御信号φ2のローレベル期間内にハイレベル期間が生じるパルス信号である。第2スイッチ部102b内の他方のスイッチがオンになると、第2コンデンサC2に蓄積された電荷が放電用定電流回路103によって一定の電流で放電される。

【0013】

従って、第1コンデンサC1は、第1制御信号φ1のハイレベル期間(T/2)に充電され、それに続くローレベル期間(T/2)内で第3制御信号φ3がハイレベルとなる期間に蓄積電荷が放電される。同様に、第2コンデンサC2は、第2制御信号φ2のハイレベル期間(T/2)に充電され、それに続くローレベル期間(T/2)内で第4制御信号φ4がハイレベルとなる期間に蓄積電荷が放電される。

【0014】

第1制御信号φ1と第2制御信号φ2は互いにハイレベル期間とローレベル期間が逆になっており、第1コンデンサC1の充電期間が第2コンデンサC2の放電期間となり、第1コンデンサC1の放電期間が第2コンデンサC2の充電期間となるので、第1コンデンサC1と第2コンデンサC2は交互に充電動作と放電動作とが行なわれる。

【0015】

パルス生成回路104から出力されるパルス信号rsout1とパルス生成回路105から出力されるパルス信号rsout2はパルス合成回路106で合成される。パルス生成回路104から出力されるパルス信号rsout1は、周期Tで第1コンデンサC1が蓄積電荷を放電する時間だけハイレベルとなる信号であり、パルス生成回路105から出力されるパルス信号rsout2は、パルス生成回路104から出力されるパルス信号rsout1に対してT/2だけずれた、周期Tで第2コンデンサC2が蓄積電荷を放電する時間だけハイレベルとなる信号である。従って、パルス合成回路106では、T/2でパルス生成回路104から出力されるパルス信号rsout1とパルス生成回路105から出力されるパルス信号rsout2を交互に合成した信号(変調信号PWMoutに相当)が出力される。

【0016】

上記構成において、第1コンデンサC1及び第2コンデンサC2の充放電動作を制御するスイッチ部102a,102bは、各コンデンサC1,C2に対してそれぞれ必要となる。その一方、電圧−電流変換回路101及び放電用定電流回路103は、第1及び第2コンデンサC1,C2がT/2だけずれて充放電されるので、電圧−電流変換回路101及び放電用定電流回路103は共用される。

【0017】

図9に示すブロック構成図は、PWM変調信号の生成原理上、必要かつ十分なブロックの構成を可及的に簡素化して示しているが、図9に示すブロック構成に基づいてPWM変調回路を実現するための具体回路を表すと、例えば図10に示すような回路になる。

【0018】

なお、図10においては、オーディオ信号eSが入力されるオペアンプ101aと、その出力に接続されたpnp型のトランジスタ101bと、そのベース端子に接続された定電圧ダイオード101c等の部分が電圧−電流変換回路101に対応する。また、2つのアナログスイッチICで構成される部分がスイッチ回路102に対応し、アナログスイッチのスイッチSW3,SW4に接続されたnpn型のトランジスタ103a、及びそのベース端子に接続された定電圧ダイオード103b等の部分が放電用定電流回路103に対応している。

【0019】

図10に示す具体回路では、回路構成が複雑になり、回路スペースや製造コスト等の点で種々の問題が生じ易いという不都合がある。例えば、図10に示す具体回路では、以下の点で問題が生じる。

【0020】

(1)電圧−電流変換回路101を共通化するために、オペアンプを用いた回路構成とすることで、電圧−電流変換回路101を構成する部品点数が多くなる。

(2)アナログスイッチICを用いることにより、スイッチ回路102の回路スペースの効率化は可能になるが、製造コストが増加する。

(3)電圧−電流変換回路101、スイッチ回路102、及び放電用定電流回路103をそれぞれブロック単位で構成し、それらを接続する構成であるので、各回路の電源電圧が異なり、複数種類の電源(図10では、+14.6v,−14.6v,+3v,−3vの4種類)が必要になる分、回路が複雑になる。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2008−206128号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

本願発明は、上記した事情のもとで考え出されたものであって、2つのパルス信号を生成するための同一構成のパルス生成回路をそれぞれ設け、各パルス生成回路を構成する電圧−電流変換回路、スイッチ回路及び放電用の定電流回路を簡素化することにより、上記した回路スペースや製造コスト等の低減することのできるパルス幅変調回路及びそれを適用したスイッチングアンプを提供することを、その課題とする。

【課題を解決するための手段】

【0023】

本願発明の第1の側面によって提供されるパルス幅変調回路は、所定の周期を有する基準クロックを生成し、その基準クロックのオン期間に充電動作を行なわせるための第1の制御信号と前記基準クロックのオフ期間に充電動作を行なわせるための第2の制御信号とを生成する充電制御信号生成部と、前記第1の制御信号により充電動作が行なわれたオン期間に続くオフ期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第3の制御信号と前記第2の制御信号により充電動作が行なわれたオフ期間に続くオン期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第4の制御信号とを生成する放電制御信号生成部と、前記第1及び第3の制御信号に基づき、入力信号のレベルに基づいて生成される充電電流により第1のコンデンサを充電する充電動作とその第1のコンデンサの蓄積電荷を一定の放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第1のコンデンサが放電開始時のレベルから前記所定の基準レベルに変化するまでの放電時間をパルス幅とする第1のパルス信号を生成する第1のパルス信号生成部と、前記第2及び第4の制御信号に基づき、前記充電電流により第2のコンデンサを充電する充電動作とその第2のコンデンサの蓄積電荷を前記放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第2のコンデンサが放電開始時のレベルから前記基準レベルに変化するまでの放電時間をパルス幅とする第2のパルス信号を生成する第2のパルス信号生成部と、前記第1のパルス信号生成部で生成される第1のパルス信号と前記第2のパルス信号生成部で生成される第2のパルス信号とを合成し、前記所定の周期を有し、各パルスのパルス幅が前記入力信号のレベルに応じて変化するパルス幅変調信号を出力するパルス信号合成部と、を備えたパルス幅変調回路であって、前記第1のパルス信号生成部は、前記入力信号の電圧を増幅する差動増幅回路と、前記差動増幅回路の一対の電源端子間に接続され、前記第1のコンデンサの充放電動作を制御する第1の制御回路と、前記第1のコンデンサの両端電圧に基づいて前記第1のパルス信号を生成する第1のパルス信号生成回路と、を備え、前記第1の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第1の充電電流生成回路とこの第1の充電電流生成回路で生成される充電電流による前記第1のコンデンサの充電動作を前記第1の制御信号により制御する第1のスイッチ回路との第1の直列回路と、前記放電電流として一定の電流を生成する第1の定電流回路とこの第1の定電流回路で生成される放電電流による前記第1のコンデンサの放電動作を前記第3の制御信号により制御する第2のスイッチ回路との第2の直列回路とを直列に接続し、その接続点に前記第1のコンデンサを接続した回路で構成され、前記第2のパルス信号生成部は、前記差動増幅回路を前記第1のパルス信号生成部と共有し、前記差動増幅回路の一対の電源端子間に接続され、前記第2のコンデンサの充放電動作を制御する第2の制御回路と、前記第2のコンデンサの両端電圧に基づいて前記第2のパルス信号を生成する第2のパルス信号生成回路と、を備え、前記第2の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第2の充電電流生成回路とこの第2の充電電流生成回路で生成される充電電流による前記第2のコンデンサの充電動作を前記第2の制御信号により制御する第3のスイッチ回路との第3の直列回路と、前記放電電流として一定の電流を生成する第2の定電流回路とこの第2の定電流回路で生成される放電電流による前記第2のコンデンサの放電動作を前記第4の制御信号により制御する第4のスイッチ回路との第4の直列回路とを直列に接続し、その接続点に前記第2のコンデンサを接続した回路で構成されている、ことを特徴としている(請求項1)。

【0024】

本願発明のパルス幅変調回路において、前記差動増幅回路は、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路が接続された回路で構成され、前記第1の定電流回路と前記第2の定電流回路は、前記定電流回路と同一の回路構成を有し、前記定電圧源を当該定電流回路と共用しているとよい(請求項2)。

【0025】

本願発明のパルス幅変調回路において、前記第1ないし第4のスイッチ回路は、半導体スイッチング素子からなり、前記第1及び第2の充電電流生成回路は、1個のトランジスタを用いた電圧−電流変換回路で構成されているとよい(請求項3)。

【0026】

この構成によれば、第1のパルス信号生成部に含まれる第1のコンデンサの充放電動作を制御する第1の制御回路と第2のパルス信号生成部に含まれる第2のコンデンサの充放電動作を制御する第2の制御回路を、充電電流生成回路とこの充電電流生成回路で生成される充電電流によるコンデンサの充電動作を充電用の制御信号によって制御するスイッチ回路との直列回路と、放電電流として一定の電流を生成する定電流回路とこの定電流回路で生成される放電電流によるコンデンサの放電動作を放電用の制御信号により制御するスイッチ回路との直列回路と直列に接続し、その接続点にコンデンサを接続するという同一の回路構成で構成し、両制御回路を共通化した差動増幅回路の一対の電源端子間に並列に接続する構成としたので、第1及び第2の制御回路に含まれる第1,第2の充電電流生成回路、充電制御用の第1,第2のスイッチ回路、放電用の第1,第2の定電流回路及び放電制御用の第3,第4のスイッチ回路をそれぞれトランジスタ等の半導体素子を用いた簡単な回路によって実現することができ、パルス幅変調回路の具体回路の簡単化を図ることができる。

【0027】

例えば、差動増幅回路を、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路を接続した回路とし、第1ないし第4のスイッチ回路を半導体スイッチ素子で構成し、第1及び第2の充電電流生成回路を1個のトランジスタを用いた電圧−電流変換回路で構成し、第1の定電流回路と第2の定電流回路を差動増幅回路に含まれる定電流回路と同一の回路構成にするとともに、当該定電流回路の定電圧源を共用する構成とすることにより、第1及び第2の制御回路を少ない部品点数で構成できるとともに、低価格の部品を使用することができる。これにより、パルス幅変調回路の具体回路の簡単化と製造コストの低減を図ることができる。

【0028】

また、第1及び第2の制御回路の駆動電源を差動増幅回路の駆動電源と共通化するとともに、第1の定電流回路と第2の定電流回路の定電圧源を差動増幅回路に含まれる定電流回路の定電圧源と共用することにより電源電圧の種類を少なくすることができ、パルス幅変調回路の電源も簡素化することができる。

【0029】

本願発明の第2の側面によって提供されるスイッチングアンプは、本願発明の第1の側面によって提供されるパルス幅変調回路と、所定の電源電圧を出力する電圧源と、前記パルス幅変調回路から出力される変調信号に基づいて、前記電圧源から供給される所定の電源電圧をスイッチングするスイッチング回路と、を備えたことを特徴としている(請求項4)。

【0030】

この構成によれば、このスイッチングアンプは、本願発明の第1の側面によって提供されるパルス幅変調回路を備えているので、第1の側面によって提供されるパルス幅変調回路と同様の作用効果を奏する。

【0031】

本発明のその他の特徴及び利点は、添付図面を参照して以下に行なう詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0032】

【図1】本願発明に係るパルス幅変調回路の一実施例を示すブロック回路図である。

【図2】パルス幅変調回路に含まれる充放電動作に関する回路の詳細回路図である。

【図3】オーディオ信号が無信号の場合のパルス幅変調回路の各信号の波形を示す図である。

【図4】パルス生成回路及びパルス合成回路の具体回路を示す図である。

【図5】パルス幅変調回路におけるパルス幅変調動作を説明するための図である。

【図6】従来のパルス幅変調回路において、第1制御信号のハイレベルと第2制御信号のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【図7】本願発明に係るパルス幅変調回路において、第1制御信号のハイレベルと第2制御信号のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【図8】従来のパルス幅変調回路が適用されるスイッチングアンプを示す構成図である。

【図9】従来のパルス幅変調回路を示すブロック構成図である。

【図10】従来のパルス幅変調回路を示す詳細回路図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施の形態につき、図面を参照して具体的に説明する。

【0034】

本願発明に係るパルス幅変調(PWM)回路が適用されるスイッチングアンプは、背景技術の欄で説明した図8に示すスイッチングアンプと同様である。よって、ここでは、その説明を省略する。

【0035】

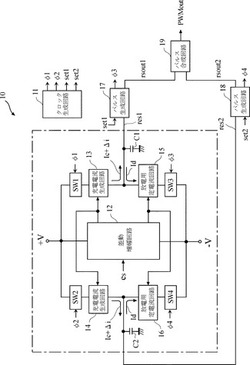

図1は、パルス幅変調回路10のブロック構成図である。図2は、パルス幅変調回路10に含まれる充放電動作に関する回路(図1の一点鎖線で囲まれた回路参照)の詳細回路図である。パルス幅変調回路10は、図1に示すように、クロック生成回路11と、差動増幅回路12と、第1及び第2充電電流生成回路13,14と、第1ないし第4スイッチSW1〜SW4と、第1及び第2コンデンサC1,C2と、第1及び第2放電用定電流回路15,16と、第1及び第2パルス生成回路17,18と、パルス合成回路19とによって構成されている。

【0036】

なお、以下の説明では、このパルス幅変調回路10の動作を示す図3のタイミングチャートを随時参照する。

【0037】

クロック生成回路11は、基準クロック信号MCLK(図3(a)参照)を生成し、その基準クロック信号MCLKから第1制御信号φ1と第2制御信号φ2を生成する。基準クロック信号MCLKは、デューティ比がほぼ50%のクロック信号であり、第1及び第2制御信号φ1,φ2の基準信号となるものである。第1及び第2制御信号φ1,φ2は、第1及び第2コンデンサC1,C2に充電動作を行なわせるために第1及び第2スイッチSW1,SW2のオン、オフ動作を制御する信号である。第2制御信号φ2は、第1制御信号φ1に対して逆位相の関係を有する。クロック生成回路11は、第1制御信号φ1を第1スイッチSW1に出力し、第2制御信号φ2を第2スイッチSW2に出力する。

【0038】

また、クロック生成回路11は、第1及び第2制御信号φ1,φ2から第1及び第2セット信号set1,set2を生成する。第1セット信号set1は、図3(d)に示すように、第1制御信号φのハイレベルからローレベルに反転する際の立下りエッジを検出した信号であり、第2セット信号set2は、図3(e)に示すように、第2制御信号φのハイレベルからローレベルに反転する際の立下りエッジを検出した信号である。第1セット信号set1は、R−Sラッチ回路によって構成される第1パルス生成回路17にセット信号として入力され、第2セット信号set2は、R−Sラッチ回路によって構成される第2パルス生成回路18にセット信号として入力される。

【0039】

差動増幅回路12は、オーディオ信号発生源AU(図8参照)からパルス幅変調回路10に供給されるオーディオ信号eSの接地レベル(0ボルト)を基準とした振幅を増幅して出力する回路である。差動増幅回路12は、2つのトランジスタのエミッタを相互に接続し、両トランジスタのコレクタをそれぞれ抵抗を介して正の電源(電源電圧+V)に接続する一方、両トランジスタのエミッタを定電流回路を介して負の電源(電源電圧−V)に接続した周知の差動増幅回路である。差動増幅回路12では、一方のトランジスタのベースにオーディオ信号eSを入力し、他方のトランジスタのベースを接地することによって両トランジスタのコレクタの間にオーディオ信号eSの0ボルト(接地レベル)を基準とした差電圧(オーディオ信号eSの振幅)を増幅した電圧が出力される。この差電圧は、第1及び第2充電電流生成回路13,14に出力される。

【0040】

第1及び第2充電電流生成回路13,14は、差動増幅回路12から出力される電圧をその電圧の変化に比例して変化する電流に変換する回路である。第1充電電流生成回路13と第2充電電流生成回路14は同一の回路構成である。第1充電電流生成回路13は、第1コンデンサC1に接続されており、電圧−電流変換した電流を第1コンデンサC1に供給することで第1コンデンサC1を充電する。従って、第1充電電流生成回路13は、第1コンデンサC1を充電するための充電電流を生成する。一方、第2充電電流生成回路14は、第2コンデンサC2に接続されており、電圧−電流変換した電流を第2コンデンサC2に供給することで第2コンデンサC2を充電する。従って、第2充電電流生成回路14は、第2コンデンサC2を充電するための充電電流を生成する。

【0041】

第1及び第2充電電流生成回路13,14における変換コンダクタンスをGmとすると、オーディオ信号eSが第1及び第2充電電流生成回路13,14で変換される電流Δiは、Δi=Gm・eSで表すことができる。また、第1及び第2充電電流生成回路13,14におけるバイアス電流をIcとすると、第1及び第2コンデンサC1,C2の充電電流は、Ic+Gm・eS=Ic+Δiで表すことができる。

【0042】

第1スイッチSW1は、第1充電電流生成回路13に電源電圧+Vを供給するか否か、すなわち、第1充電電流生成回路13を動作させて第1コンデンサC1を充電するか否かを制御する回路であり、第2スイッチSW2は、第2充電電流生成回路14に電源電圧+Vを供給するか否か、すなわち、第2充電電流生成回路14を動作させて第2コンデンサC2を充電するか否かを制御する回路である。第1スイッチSW1と第2スイッチW2は同一の回路構成である。第1及び第2スイッチSW1,SW2は、クロック生成回路11から出力される第1及び第2制御信号φ1,φ2に基づいてオン、オフ動作される。第1スイッチSW1は、第1制御信号φ1がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。また、第2スイッチSW2は、第2制御信号φ2がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。

【0043】

第1放電用定電流回路15は、充電電流(Ic+Δi)で充電された第1コンデンサC1の蓄積電荷を放電させるための回路であり、第2放電用定電流回路15は、充電電流(Ic+Δi)で充電された第2コンデンサC2の蓄積電荷を放電させるための回路である。第1放電用定電流回路15は、第1コンデンサC1に接続されており、一定の放電電流Idで第1コンデンサC1に蓄積された電荷を引き込むことにより、第1コンデンサC1の蓄積電荷を放電させる。一方、第2放電用定電流回路16は、第2コンデンサC2に接続されており、一定の放電電流Idによって第2コンデンサC2に蓄積された電荷を引き込むことにより、第2コンデンサC2の蓄積電荷を放電させる。

【0044】

第3スイッチSW3は、第1放電用定電流回路15に電源電圧−Vを供給するか否か、すなわち、第1放電用定電流回路15を動作させて第1コンデンサC1を放電するか否かを制御する回路であり、第4スイッチSW4は、第2放電用定電流回路16に電源電圧−Vを供給するか否か、すなわち、第2放電用定電流回路16を動作させて第2コンデンサC2を放電するか否かを制御する回路である。第3スイッチSW3と第4スイッチW4は同一の回路構成である。第3及び第4スイッチSW3,SW4は、第1及び第2パルス生成回路17,18からそれぞれ出力される第3及び第4制御信号φ3,φ4に基づいてオン、オフ動作される。第3スイッチSW3は、第3制御信号φ3がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。また、第4スイッチSW4は、第4制御信号φ4がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。

【0045】

第1及び第2コンデンサC1,C2は、オーディオ信号eSの振幅を時間に変換するための素子である。オーディオ信号eSの振幅は、第1及び第2コンデンサC1,C2をオーディオ信号eSの振幅に比例した充電電流(Ic+Δi)で一定時間(基準クロック信号MCLKの周期Tの1/2の時間)だけ充電した後その蓄積電荷を一定の放電電流Idで放電し、その放電時間をパルス幅とするパルスを生成することによって時間に変換される。

【0046】

第1パルス生成回路17は、第1コンデンサC1の両端電圧が放電開始時の電圧レベルから所定の基準レベルVthに変化するまでの放電時間をパルス幅とする第1パルス信号rsout1(図3(j)参照)と、第3スイッチSW3のオン・オフ動作を制御する第3制御信号φ3(図3(f)参照)を生成する回路である。なお、本実施形態では、後述するように第1パルス生成回路17及び第2パルス生成回路18はNAND回路を用いたR−Sラッチ回路で構成されるので、基準レベルVthはNAND回路のスレシホールドレベルとなる。

【0047】

第1パルス信号rsout1は、パルス合成回路19に出力され、第3制御信号φ3は第3スイッチSW3に出力される。第1パルス生成回路18は、第2コンデンサC2の両端電圧が放電開始時の電圧レベルから上記の基準レベルVthに変化するまでの放電時間をパルス幅とする第2パルス信号rsout2(図3(k)参照)と、第4スイッチSW4のオン・オフ動作を制御する第4制御信号φ4(図3(g)参照)を生成する回路である。第2パルス信号rsout2は、パルス合成回路19に出力され、第4制御信号φ4は第4スイッチSW4に出力される。

【0048】

パルス合成回路19は、第1及び第2パルス生成回路17,18から出力される第1及び第2パルス信号rsout1,rsout2を合成し、PWM変調信号PWMout(図3(l)参照)として出力する回路である。

【0049】

次に、図2を参照して充放電動作に関する回路(図1の一点鎖線で囲まれた回路参照)の詳細について説明する。なお、図1と同一機能を果たす回路には同一の符号を付している。

【0050】

差動増幅回路12は、npn型の第1トランジスタQ1のエミッタとnpn型の第1トランジスタQ2のエミッタをそれぞれ抵抗R3と抵抗R4を介して定電流回路に接続し、第1トランジスタQ1のコレクタと第2トランジスタQ2のコレクタをそれぞれ抵抗R1と抵抗R2を介して正の電源(電源電圧+V)に接続した周知の差動増幅回路である。

【0051】

第1トランジスタQ1のベースには、カップリングコンデンサCaを介してオーディオ信号eSが入力され、第2トランジスタQ2のベースは、接地(0ボルトレベル)されている。

【0052】

定電流回路は、npn型の第3トランジスタQ3のエミッタを抵抗R6を介して負の電源(電源電圧−V)に接続し、ベースを抵抗R11を介して正の電源(電源電圧+V)に接続するとともにベースと負の電源の間にツェナーダイオード(定電圧ダイオード)D1を接続した周知の定電流回路である。第3トランジスタQ3のコレクタは、抵抗R3と抵抗R4に接続されている。この回路では、第3トランジスタQ3のベース電圧がツェナーダイオードD1のツェナ電圧Vzになるので、第3トランジスタQ3のコレクタには(Vz−Vbe)/R6(Vbeは第3トランジスタQ3のベース−エミッタ間の電圧)の定電流Idが流れる。

【0053】

第1充電電流生成回路13と第2充電電流生成回路14は、pnp型トランジスタのエミッタに電流制限用の抵抗を接続した回路で構成され、第1スイッチSW1と第2スイッチSW2は、pnp型トランジスタで構成されている。第1スイッチSW1と第1充電電流生成回路13は直列に接続され、第2スイッチSW2と第2充電電流生成回路14は直列に接続されている。また、第1スイッチSW1と第2スイッチSW2のエミッタは共に正の電源(電源電圧+V)に接続され、第1充電電流生成回路13を構成する第4トランジスタQ4と第2充電電流生成回路14を構成する第5トランジスタQ5のコレクタはそれぞれ第1コンデンサC1と第2コンデンサに接続されている。

【0054】

第4トランジスタQ4と第5のトランジスタQ5のベースには差動増幅回路12内の第1トランジスタQ1のコレクタが接続され、差動増幅回路12からオーディオ信号esの接地レベルを基準とした振幅が入力される。また、第1スイッチSW1と第2スイッチSW2のベースにはクロック生成回路11からそれぞれ第1制御信号φ1と第2制御信号φ2が入力される。

【0055】

第1放電用定電流回路15と第2放電用定電流回路16は、差動増幅回路12内の定電流回路と同一の回路で構成され、第3スイッチSW3と第4スイッチSW4は、npn型トランジスタで構成されている。第1放電用定電流回路15と第3スイッチSW3は直列に接続され、第2放電用定電流回路16と第4スイッチSW4は直列に接続されている。第1放電用定電流回路15と第2放電用定電流回路16は、npn型トランジスタ、エミッタ抵抗及びツェナーダイオードを用いた定電流回路であるが、第1及び第2放電用定電流回路15,16のnpn型トランジスタのベース電圧を与えるツェナーダイオードは、差動増幅回路12内の定電流回路のツェナーダイオードD1が共用されている。

【0056】

従って、第1放電用定電流回路15を構成する第6トランジスタQ6のコレクタは第1コンデンサC1に接続され、第6トランジスタQ6のエミッタは抵抗R9を介して第3スイッチSW3のコレクタに接続されている。また、第2放電用定電流回路16を構成する第7トランジスタQ7のコレクタは第2コンデンサに接続され、第7トランジスタQ7のエミッタは抵抗R10を介して第4スイッチSW4のコレクタに接続されている。そして、第6トランジスタQ6及び第7トランジスタQ7のベースは、ツェナーダイオードD1のカソードに接続されている。

【0057】

また、第3スイッチSW3及び第4スイッチSW4のエミッタは負の電源(電源電圧−V)に接続され、第3スイッチSW3のベースには第1パルス生成回路17から出力される第3制御信号φ3が入力され、第4スイッチSW4のベースには第2パルス生成回路18から出力される第4制御信号φ4が入力される。

【0058】

図2の回路では、第1制御信号φ1がローレベルになると、第1スイッチSW1がオンになり、第1充電電流生成回路13に正の電源(+V)が接続され、第1充電電流生成回路13内の第4トランジスタQ4が動作する。第4トランジスタQ4のベースには差動増幅回路12から接地レベルに対するオーディオ信号eSの差電圧、すなわち、オーディオ信号eSの振幅値が入力されるので、第4トランジスタQ4のコレクタにはオーディオ信号eの振幅値に比例した充電電流(Ic+Δi)が流れ、第1コンデンサC1が第1制御信号φ1のローレベルの期間にこの充電電流(Ic+Δi)によって充電される(図3(b),(h)のT1,T3期間の波形参照)。

【0059】

同様に、第2制御信号φ2がローレベルになると、第2スイッチSW2がオンになり、第2充電電流生成回路14に正の電源(+V)が接続され、第2充電電流生成回路14内の第5トランジスタQ5が動作する。第4トランジスタQ4のベースにも差動増幅回路12から接地レベルに対するオーディオ信号eSの差電圧が入力されるので、第5トランジスタQ5のコレクタにはオーディオ信号eの振幅値に比例した充電電流(Ic+Δi)が流れ、第2コンデンサC2が第2制御信号φ2のローレベルの期間にこの充電電流(Ic+Δi)によって充電される(図3(c),(i)のT2,T4期間の波形参照)。

【0060】

また、第3制御信号φ3がハイレベルになると、第3スイッチSW3がオンになり、第1放電用定電流回路15に負の電源(−V)が接続され、第1放電用定電流回路15内の第6トランジスタQ6が一定の電流Idを引き込む動作を行なう。これにより、第1コンデンサC1の蓄積電荷が定電流Idで放電される(図3(f),(h)のT2,T4期間の波形参照)。

【0061】

同様に、第4制御信号φ4がハイレベルになると、第4スイッチSW4がオンになり、第2放電用定電流回路16に負の電源(−V)が接続され、第2放電用定電流回路16内の第7トランジスタQ7が一定の電流Idを引き込む動作を行なう。これにより、第2コンデンサC2の蓄積電荷が定電流Idで放電される(図3(g),(i)のT1,T3期間の波形参照)。

【0062】

第1パルス生成回路17は、図4に示すように、2個のNAND回路を用いた周知のR−Sラッチ回路で構成されている。第1パルス生成回路17の第2NAND回路N2の入力端子はS(set)信号の入力端子であり、第1NAND回路N1の入力端子はR(reset)信号の入力端子である。また、第1NAND回路N1の出力端子は/Q信号の出力端子であり、第2NAND回路N2の出力端子はQ信号の出力端子である。

【0063】

そして、第1パルス生成回路17の第1NAND回路N1の入力端子には第1コンデンサC1の両端電圧が第1リセット信号res1として入力され、第2NAND回路N2の入力端子にはクロック生成回路11から出力される第1セット信号set1が入力される。また、第1NAND回路N1の出力端子から出力されるパルス信号はPWM変調信号PWMoutを生成するための第1パルス信号rsout1としてパルス合成回路19に入力され、第2NAND回路N2の出力端子から出力されるパルス信号は第3制御信号φ3として第3スイッチSW3のベースに入力される。

【0064】

図4に示すR−Sラッチ回路では、(S,R)=(ハイ,ロー)で(Q,/Q)=(ハイ,ロー)の論理となり、(S,R)=(ロー,ハイ)で(Q,/Q)=(ロー,ハイ)の論理となる。図3(d),(h)に示されるように、第1制御信号φ1が立ち下がるタイミングで第1セット信号set1は一瞬ローレベルになり、第1コンデンサC1の両端電圧(第1リセット信号res1)はハイレベルとなるので、第1パルス信号rsout1はローレベルとなり、第3制御信号φ3はハイレベルとなる(図3(f)(j)参照)。第3制御信号φ3がハイレベルになると、第1コンデンサC1の放電が開始されるが、第1コンデンサC1の両端電圧が第1NAND回路N1のスレシホールドレベルVthより高い間は第1パルス信号rsout1がローレベルに保持され、スレシホールドレベルVthに達すると、第1セット信号set1はハイレベルになり、第1リセット信号res1はローレベルとなるので、そのタイミングで第1パルス信号rsout1はハイレベルとなり、第3制御信号φ3はローレベルとなる(図3(f)(j)参照)。

【0065】

第2パルス生成回路18も第1パルス生成回路17と同様に、2個のNAND回路を用いた周知のR−Sラッチ回路で構成されている。図4に示すように、第2パルス生成回路18の第3NAND回路N3の入力端子には第2コンデンサC2の両端電圧が第2リセット信号res2として入力され、第4NAND回路N4の入力端子にはクロック生成回路11から出力される第2セット信号set2が入力される。また、第3NAND回路N3の出力端子から出力されるパルス信号はPWM変調信号PWMoutを生成するための第2パルス信号rsout2としてパルス合成回路19に入力され、第4NAND回路N4の出力端子から出力されるパルス信号は第4制御信号φ4として第4スイッチSW3のベースに入力される。

【0066】

図3(e),(i)に示されるように、第2制御信号φ2が立ち下がるタイミングで第2セット信号set2は一瞬ローレベルになり、第2コンデンサC2の両端電圧(第1リセット信号res1)はハイレベルとなるので、第2パルス信号rsout2はローレベルとなり、第4制御信号φ4はハイレベルとなる(図3(g)(k)参照)。第4制御信号φ4がハイレベルになると、第2コンデンサC2の放電が開始されるが、第2コンデンサC2の両端電圧が第3NAND回路N3のスレシホールドレベルVthより高い間は第2パルス信号rsout2がローレベルに保持され、スレシホールドレベルVthに達すると、第2セット信号set2はハイレベルになり、第2リセット信号res2はローレベルとなるので、そのタイミングで第2パルス信号rsout2はハイレベルとなり、第4制御信号φ4はローレベルとなる(図3(g)(k)参照)。

【0067】

パルス合成回路19は、図4に示すように、第5NAND回路N5によって構成され、第1パルス生成回路17から出力される第1パルス信号rsout1と、第2パルス生成回路18から出力される第2パルス信号rsout2との否定論理積を演算することによりパルス幅変調信号PWMoutを生成する(図3(l)参照)。

【0068】

次に、パルス幅変調回路10におけるパルス幅変調動作について、図5を用いて簡単に説明する。なお、第1コンデンサC1と第2コンデンサC2で同様のパルス幅変調動作が行なわれるので、ここでは第1コンデンサC1におけるパルス幅変調動作について説明する。

【0069】

第1制御信号φ1がハイレベルになると、第1スイッチSW1がオンになり、第1充電電流生成回路13が充電電流(Ic+Δi)の生成動作を行なう。第1制御信号φ1がハイレベルの期間では第3制御信号φ3がローレベルであるので、第3スイッチSW3がオフ状態となっており(図3(b)(f)参照)、第1放電用定電流回路15は動作していない。従って、第1コンデンサC1には第1充電電流生成回路13で生成された充電電流(Ic+Δi)のみが流れ込み、これにより第1コンデンサC1が充電される。この充電動作は、第1制御信号φ1がオンになっている期間(図5ではT1の期間)に行なわれる。

【0070】

期間T1における第1コンデンサC1の両端電圧(図2のA点の電圧)は、基準電圧Vthから充電電流(Ic+G・eS)の大きさに比例した傾きで上昇する。充電電流(Ic+G・eS)はオーディオ信号eSの正負の方向及び振幅の大きさに依存し、eS>0で振幅|eS|が大きいほど、期間T1の終了時の充電電圧は高くなり、eS<0で振幅|eS|が大きいほど、期間T1の終了時の充電電圧は低くなる。なお、図5では、期間T1はオーディオ信号eSの振幅変動に対して非常に短く、期間T1ではオーディオ信号eSの振幅変動は殆どなく一定であるとして第1コンデンサC1の充電電圧をほぼ直線的に上昇させている。

【0071】

図5の電圧波形S0は、eS=0のとき(オーディオ信号eSが無信号のとき)の波形を示し、電圧波形S1は、eS>0のときの波形を示し、電圧波形S2は、eS<0のときの波形を示している。

【0072】

第1コンデンサC1の容量を「C」、期間T1の終了時の第1コンデンサC1の充電電圧を「Vj」とすると、期間T1における第1コンデンサC1の充電動作においては、(Ic+G・eS)×T1=C×(Vj−Vth)の関係が成立する。この関係式より、Vj=G・eS×T1/C+Ic×T1/C+Vthとなるので、A=G×T1/C、B=Ic×T1/C+Vthとして整理すると、Vj=A×eS+Bとなる。図5によれば、eS=0ではVj=V0であるから、B=V0となるので、第1コンデンサC1の充電電圧VjはVj=A×eS+V0を表される。すなわち、第1コンデンサC1の充電電圧VjはV0を中心にeS>0ではオーディオ信号eSの振幅|eS|に比例して増大し、eS<0ではオーディオ信号eSの振幅|eS|に比例して減少する。

【0073】

第1制御信号φ1がローレベルになると同時に第3制御信号φ3がハイレベルになると、第1スイッチSW1がオフなると同時に第3スイッチSW3がオンになり、第1充電電流生成回路13が動作を停止し、第1放電用定電流回路15が定電流Idの引き込み動作を行なう。従って、第1コンデンサC1に蓄積された電荷が定電流Idで第1放電用定電流回路15に引き込まれ、これにより第1コンデンサC1の蓄積電荷が放電される。この放電動作は、第1コンデンサC1の電圧が基準電圧Vthに低下するまで行なわれる。

【0074】

第1コンデンサC1の電圧が基準電圧Vthに低下すると、第3制御信号φ3がローレベルに反転し、第3スイッチSW3がオフになるので、第1放電用定電流回路15の定電流Idによる引き込み動作が停止する。すなわち、第1コンデンサC1の電圧が基準電圧Vthに低下してから次に第1制御信号φ1がハイレベルになるまでの期間は、第1コンデンサC1に充電電流も放電電流も流れない状態となる。従って、第1コンデンサC1の電圧は第1制御信号φ1がハイレベルになるまで基準電圧Vthに保持される(図5の時間t1k,t0k,t2k参照)。

【0075】

第1コンデンサC1の充電電圧を「Vj」、放電時間を「Th」とすると、Id×Th=C×(Vj−Vth)の関係が成立するから、Th=C×Vj/id−Vth/Idより、放電時間Thは、充電電圧Vjに比例する。すなわち、充電電圧Vjが高いほど、放電時間Thは長くなる。図5において、時間t1は、オーディオ信号eS>0のときの放電時間を示し、時間t0は、オーディオ信号eS=0のときの放電時間を示し、時間t2は、オーディオ信号eS<0のときの放電時間を示し、t2<t0<t1の関係になっている。

【0076】

そして、充電電圧Vjの高さは、オーディオ信号eSの振幅|eS|に比例するから、放電時間Thもオーディオ信号eSの振幅|eS|に比例することになる。すなわち、第1コンデンサC1の放電時間Thは、オーディオ信号eSの振幅|eS|により変調された時間を示す。上記のパルス幅変調動作は、第2コンデンサC2についても同様である。

【0077】

本実施形態に係るパルス幅変調回路10では、図3に示すように、基準クロック信号MCLKの周期Tのハイレベル期間で第2コンデンサC2によりオーディオ信号eSをパルス幅変調したパルスを生成し、それに続くローレベル期間で第1コンデンサC1によりオーディオ信号eSをパルス幅変調したパルスを生成するので、両パルスをパルス合成回路19で合成することにより基準クロック信号MCLKの周期Tを有するパルス幅変調信号PWMoutを生成している。

【0078】

次に、パルス幅変調回路10の動作を図3に示すタイミングチャートを参照して説明する。図3は、オーディオ信号eSが無信号の場合(Gm・eS=0)を示している。図3では、基準クロック信号MCLKが最初にハイレベルになる期間から2周期分のハイレベルとローレベルの期間に対してそれぞれ第1期間T1、第2期間T2、第3期間T3、第4期間T4と言うことにする。

【0079】

第1期間T1では、クロック生成回路11からの第1制御信号φ1がハイレベル(第2制御信号φ2がローレベル)であるので(図3(b)参照)、第1スイッチSW1がオン状態(第2スイッチSW2はオフ状態)となり、第1コンデンサC1に第1充電電流生成回路13が接続される。従って、第1期間T1では第1充電電流生成回路13から第1コンデンサC1に充電電流(Ic+Δi)が流れ込み、これにより第1コンデンサC1が充電される(図3(h)参照)。この充電動作は、第1期間T1が終了するまで行なわれる。

【0080】

第1期間T1が終了し、第1制御信号φ1がハイレベルからローレベルに反転すると、第1スイッチSW1がオフ状態になる。第1スイッチSW1のオフ状態は第2期間T2の間、継続する。クロック生成回路11では、第1制御信号φ1の反転時の立下りを検出し、第1パルス生成回路17に瞬間的にローレベルに変化する第1セット信号set1を出力する(図3(d)の最初のローレベル変化参照)。

【0081】

第1パルス生成回路17では、第2期間T2の開始時に第1セット信号set1(ローレベル)が入力されると、第2NAND回路N2の出力がローレベルからハイレベルに反転する(図3(f)参照)。第2NAND回路N2の出力は、第3制御信号φ3として第3スイッチSW3に入力されるので、第3スイッチSW3がオン状態となり、第1コンデンサC1に第1放電用定電流回路15が接続され、これにより、第1コンデンサC1は定電流Idで放電される(図3(h)参照)。

【0082】

また、第1パルス生成回路17では、第2期間T2の開始時に第1セット信号set1(ローレベル)が入力されると、第1NAND回路N1の出力をハイレベルからローレベルに反転する(図3(j)参照)。第1NAND回路N1の出力は、第1パルス信号rsout1としてパルス合成回路19に入力される。

【0083】

パルス合成回路19に第1NAND回路N1のローレベル出力が入力された時にはパルス合成回路19の第5NAND回路N5に第2パルス生成回路18から入力される第2パルス信号rsout2はハイレベルのため、パルス合成回路19からは第1パルス信号rsout1のレベルを反転したパルス(ハイレベルのパルス)が出力される(図3(l)の2つ目のパルス参照)。

【0084】

第2期間T2においては、第1コンデンサC1が定電流Idで放電されるので、第1コンデンサC1の両端電圧が低下する。第1パルス生成回路17では第1コンデンサC1の両端電圧が第1NAND回路N1に入力されているが、第1コンデンサC1の両端電圧が基準電圧Vthに低下すると、その時の電圧がローレベルの第1リセット信号res1として第1パルス生成回路17に入力されることになる。第1パルス生成回路17に第1リセット信号res1が入力されると、第1パルス信号rsout1は、ローレベルからハイレベルに反転する(図3(j)参照)。

【0085】

一方、第2期間T2では、クロック生成回路11からの第2制御信号φ2がハイレベル(第1制御信号φ1がローレベル)であるので(図3(c)参照)、第2スイッチSW2がオン状態(第1スイッチSW1はオフ状態)となり、第2コンデンサC2に第2充電電流生成回路14が接続される。従って、第2期間T2では第2充電電流生成回路14から第2コンデンサC2に充電電流(Ic+Δi)が流れ込み、これにより第2コンデンサC2が充電される(図3(i)参照)。この充電動作は、第2期間T2が終了するまで行なわれる。

【0086】

第2期間T2が終了し、第2制御信号φ2がハイレベルからローレベルに反転すると、第2スイッチSW2がオフ状態になる。第2スイッチSW2のオフ状態は第3期間T3の間、継続する。クロック生成回路11では、第2制御信号φ2の反転時の立下りを検出し、第2パルス生成回路18に瞬間的にローレベルに変化する第2セット信号set2を出力する(図3(e)参照)。

【0087】

第2パルス生成回路18では、第3期間T3の開始時に第2セット信号set2(ローレベル)が入力されると、第4NAND回路N4の出力がローレベルからハイレベルに反転する(図3(g)参照)。第4NAND回路N4の出力は、第4制御信号φ4として第4スイッチSW4に入力されるので、第4スイッチSW4がオン状態となり、第2コンデンサC2に第2放電用定電流回路16が接続され、これにより、第2コンデンサC2は定電流Idで放電される(図3(i)参照)。

【0088】

また、第2パルス生成回路18では、第3期間T3の開始時に第2セット信号set2(ローレベル)が入力されると、第3NAND回路N3の出力をハイレベルからローレベルに反転する(図3(k)参照)。第3NAND回路N3の出力は、第2パルス信号rsout2としてパルス合成回路19に入力される。

【0089】

パルス合成回路19に第3NAND回路N3のローレベル出力が入力された時にはパルス合成回路19の第5NAND回路N5に第1パルス生成回路17から入力される第1パルス信号rsout1はハイレベルのため、パルス合成回路19からは第2パルス信号rsout2のレベルを反転したパルス(ハイレベルのパルス)が出力される(図3(l)の3つ目のパルス参照)。

【0090】

以下、第3期間以降では第1期間T1及び第2期間T2と同様の動作が繰返される。従って、パルス合成回路19からは基準クロック信号MCLKの半周期毎に第1パルス信号rsout1と第2パルス信号rout2のレベルを反転したパルスが交互に出力される。

【0091】

上記のように、パルス幅変調回路10では、図1に示すように、第1コンデンサC1の充電動作を制御する回路と第2コンデンサC2の充電動作を制御する回路を同一の回路構成(スイッチ回路と充電電流生成回路の直列回路)にするとともに、第1コンデンサC1の放電動作を制御する回路と第2コンデンサC2の放電動作を制御する回路を同一の回路構成(スイッチ回路と放電用定電流回路の直列回路)としているので、図2に示すように、充電動作を制御する第1スイッチSW1及び第2スイッチSW2を同一のトランジスタで実現することができるとともに、放電動作を制御する第3スイッチSW3及び第4スイッチSW4を同一のトランジスタで実現することができる。

【0092】

また、第1充電電流生成回路13及び第2充電電流生成回路14を、差動増幅回路12を共通化し、その差動増幅回路12にトランジスタを用いた同一回路構成の電圧−電流変換回路を接続することよって実現することができる。更に、第1放電用定電流回路15及び第2放電用定電流回路16をトランジスタとツェナーダイオードを用いた同一回路構成の定電流回路で実現することができる。

【0093】

しかも、この定電流回路は差動増幅回路12内の定電流回路と同一の回路構成とすることができるので、差動増幅回路12内のツェナーダイオードD1を第1放電用定電流回路15及び第2放電用定電流回路16のツェナーダイオードに共用することができる。更に、パルス幅変調回路10の駆動電源は正の電源(+V)と負の電源(−V)の2種類で良いので、電源回路も簡単にすることができる。

【0094】

従って、パルス幅変調回路10を少ない部品点数で実現でき、回路の簡素化、小型化を図ることができる。また、低価格のトランジスタやツェナーダイオード等の半導体素子を用いてパルス幅変調回路10を実現できるので、製造コストの低減を図ることができる。

【0095】

また、従来のパルス幅変調回路1では、図9に示すように、第1スイッチ部102a内の第1制御信号φ1で制御されるスイッチと第2スイッチ部102b内の第2制御信号φ2で制御されるスイッチが第1コンデンサC1と第2コンデンサC2の間で直列に接続される構成であるので、両スイッチが同時にオン状態になると、電圧−電流変換回路101に第1コンデンサC1と第2コンデンサC2が並列に接続され、第1コンデンサC1の充電動作と第2の充電動作が適正に行なわれないという不都合が生じる。

【0096】

特に、図10に示す具体回路では、第1スイッチ部102a及び第2スイッチ部102b内の4つのスイッチを、双方向特性を有するアナログスイッチICで構成しているので、第1制御信号φ1の立下りタイミングと第2制御信号φ2の立上りタイミングの間にデッドタイムがなければ、第1スイッチ部102a内の第1制御信号φ1で制御されるアナログスイッチと第2スイッチ部102b内の第2制御信号φ2で制御されるアナログスイッチが同時にオン状態になる虞があり、そのような状態が生じた場合はパルス幅変調回路1からは異常なPWM変調信号PWMoutが出力されることになるが、本実施形態に係るパルス幅変調回路10では、このような不都合が乗じることはない。以下、この効果について説明する。

【0097】

図6は、従来のパルス幅変調回路1において、第1制御信号φ1のハイレベルと第2制御信号φ2のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【0098】

図6の「φ1」と「φ2」の波形は、図9の第1スイッチ部102aと第2スイッチ部102bに入力される第1制御信号φ1と第2制御信号φ2の波形である。また、「C1」と「C2」の波形は、図9の第1パルス生成回路104と第2パルス生成回路105に入力される電圧波形であり、「rsout1」、「rsout2」、「PWMout」の波形は、それぞれ図9の第1パルス生成回路104、第2パルス生成回路105、パルス合成回路106から出力される電圧波形である。

【0099】

同図に示すように、第2制御信号φ2は、第2制御信号φ2の立上りタイミングが第1制御信号φ1の立下りタイミング対して微小時間tdだけ早くなるように設定されており、第1制御信号φ1の立下りタイミングより微小時間tdだけ前の期間で第1制御信号φ1と第2制御信号φ2が共にハイレベルになっている(図6(a),(b)参照)。

【0100】

第1期間T1において、第1制御信号φ1がハイレベルに立ち上ってから第2制御信号φ1がハイレベルに立ち上る直前までの期間は、電圧−電流変換回路101に第1コンデンサC1のみが接続され、第1コンデンサC1は電圧−電流変換回路101からの充電電流(Ic+Δi)によって充電されるので、第1コンデンサC1の両端電圧はほぼ直線的に上昇する。しかし、第2制御信号φ2がハイレベルに立ち上ると、第1コンデンサC1に第2コンデンサC2が並列に接続されるので、第1コンデンサC1の両端電圧は不連続に急減することになる。

【0101】

第2制御信号φ2の立上りタイミングにおける第1コンデンサC1の充電電圧を「Vj」とすると、その時点では第2コンデンサC2の蓄積電荷はゼロで、両端電圧は「Vth」であるから、第1コンデンサC1に第2コンデンサC2が並列に接続されると、合成容量が2倍になるので、第1コンデンサC1及び第2コンデンサC2の両端電圧は、(Vj+Vth)/2となる。図6に示すように、第1コンデンサC1の充電電圧Vjと第1コンデンサC1の充電電圧Vthの差電圧を「Cv」とすると、Vj=Vth+Cvより(Vj+Vth)/2=Vth+Cv/2となる。すなわち、第2制御信号φ2の立上りタイミングで、第1コンデンサC1の両端電圧は充電電圧Vjから第2コンデンサC2との差電圧Cvの1/2だけ急減し、第2コンデンサC2の両端電圧は電圧Vthから第1コンデンサC1との差電圧Cvの1/2だけ急増する(図6(c)(d)参照)。

【0102】

そして、第1制御信号φ1の立下がりタイミングでは、電圧−電流変換回路101に第1コンデンサC1と第2コンデンサC2が並列接続されている状態が第2コンデンサC2のみの接続状態になるので、第2コンデンサC2は電圧(Vth+Cv/2)から充電されることになる。一方、第1コンデンサC1は、第1制御信号φ1の立下がりタイミングで第3制御信号φ3がハイレベルとなり、放電用定電流回路103が接続されるので、電圧(Vth+Cv/2)から放電されることになる。

【0103】

この結果、第1コンデンサC1は、正常時は充電電圧(Vth+Cv)から放電が行なわれるところ、充電電圧(Vth+Cv/2)から電圧Vthまで放電が行なわれるので、その放電時間は正常時の放電時間よりも短くなる(図6(c),(e)参照)。一方、第2コンデンサC1は、正常時は電圧Vthから充電が行なわれるところ、電圧(Vth+Cv/2)から基準クロック信号MCLKの周期Tの1/2だけ充電されるので、その充電電圧は正常時の充電電圧よりも高くなる。従って、充電期間の放電期間では放電時間が正常時の放電時間よりも長くなる(図6(d),(f)参照)。この結果、第1コンデンサC1を用いて変調されるパルス幅と第2コンデンサC2を用いて変調されるパルス幅とに著しいアンバランスが生じ、図6(g)に示すように、PWM変調信号PWMoutの波形は異常な波形となる。

【0104】

従来のパルス幅変調回路1では、上記の不都合を解消するために、図9に示したクロック生成回路100の後段に必ずデッドタイム生成回路を設け、第1制御信号φ1がハイレベルからローレベルに立ち下がるタイミングから所定時間だけ遅れて第2制御信号φ2がローレベルからハイレベルに立ち上がるようにデッドタイムを設ける必要がある。

【0105】

これ対し、本実施形態に係るパルス幅変調回路10は、図2に示したように、第1スイッチSW1と第1コンデンサC1との間に第1充電電流生成回路13が介在し、第2スイッチSW2と第2コンデンサC2との間に第2充電電流生成回路14が介在するので、第1スイッチSW1と第2スイッチSW2が同時にオン状態になったとしても、従来のパルス幅変調回路1のように第1コンデンサC1と第2コンデンサC2が同一の充電電流生成回路に並列に接続されることはない。

【0106】

すなわち、本実施形態に係るパルス幅変調回路10では、第1コンデンサC1は、第2スイッチSW2のオン・オフ動作に関係なく、第1スイッチSW1がオンになると、第1充電電流生成回路13に接続されて当該第1充電電流生成回路13からの充電電流によって充電され、第2コンデンサC2は、第1スイッチSW1のオン・オフ動作に関係なく、第2スイッチSW2がオンになると、第2充電電流生成回路14に接続されて当該第2充電電流生成回路14からの充電電流によって充電される。

【0107】

図7は、本実施形態に係るパルス幅変調回路10において、第1制御信号φ1のハイレベルと第2制御信号φ2のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【0108】

図7の第1制御信号φ1と第2制御信号φ2の波形は図6の第1制御信号φ1と第2制御信号φ2の波形と同一である。

【0109】

第1期間T1において、第1制御信号φ1がハイレベルに立ち上ってから第2制御信号φ1がハイレベルに立ち上る直前までの期間は、第1コンデンサC1に第1充電電流生成回路13が接続され、第1コンデンサC1は当該第1充電電流生成回路13から出力される充電電流(Ic+Δi)によって充電されるので、第1コンデンサC1の両端電圧はほぼ直線的に上昇する。また、第2制御信号φ2がハイレベルに立ち上っても、第1コンデンサC1には第2コンデンサC2が並列に接続されることはないので、第1コンデンサC1の両端電圧は第1制御信号φ1の立下がりタイミング、すわなち、第1期間T1の終了まで上昇することになる。

【0110】

従って、第2期間T2においては、第1コンデンサC1に第1放電用定電流回路15が接続され、第1コンデンサC1は当該第1放電用定電流回路15から出力される定電流Idによって放電される。

【0111】

一方、第2コンデンサC2は、第1期間T1の終了間際の第2制御信号φ2がハイレベルに立ち上るタイミングから次の立下りタイミングまでの期間、第2充電電流生成回路14が接続され、当該第2充電電流生成回路14から出力される充電電流(Ic+Δi)によって充電されるので、第2コンデンサC2の両端電圧もほぼ直線的に上昇する。また、その期間中には第1制御信号φ1がハイレベルに立ち上ることはないので、第2コンデンサC2の両端電圧は第2制御信号φ2が立ち下がるタイミングまで上昇し、その電圧が第2期間T2の終了まで保持される。そして、第3期間T3の開始間際に第2コンデンサC2に第2放電用定電流回路16が接続され、第2コンデンサC2は当該第2放電用定電流回路16から出力される定電流Idによって放電される。

【0112】

上記のように、第1コンデンサC1の充放電動作と第2コンデンサC2の充放電動作は互いに独立した動作となるので、両コンデンサC1,C2の充電動作と放電動作とにアンバランスが生じることはなく、図7(e)〜(g)に示すように、PWM変調信号PWMoutの波形は正常な波形となる。

【0113】

従って、本実施形態に係るパルス幅変調回路10では、従来のパルス幅変調回路1のようにデッドタイム生成回路を設ける必要はないので、その分、回路の簡素化、回路スペースを削減化及び部品コストの低減化を図ることができる。

【0114】

もちろん、この発明の範囲は上述した実施の形態に限定されるものではなく、上記実施形態に示した回路構成は一例であり、同等の機能を有するものであれば、種々の回路を適用することができる。例えば、上記した実施形態では、第1及び第2コンデンサC1,C2を一旦プラス方向に充電し、その後マイナス方向に放電するようにしたが、これに代えて、第1及び第2コンデンサC1,C2を一旦マイナス方向に充電し、その後プラス方向に放電するようにして、パルス幅変調信号PWMoutを生成するようにしてもよい。

【0115】

また、第1ないし第4スイッチSW1〜SW4は、バイポーラトランジスタに限られず、FETなどの他の種類の半導体スイッチング素子を使用することができる。

【0116】

また、第1コンデンサC1と第1パルス生成回路17との間、または第2コンデンサC2と第2パルス生成回路18との間には、例えばオペアンプからなる比較回路が設けられてもよい。この比較回路により、第1コンデンサC1の一端における電圧が基準電圧に達することを正確に検出することができる。

【符号の説明】

【0117】

1,10 パルス幅変調回路

2 スイッチング回路

3 ローパスフィルタ回路

4 第1電源

5 第2電源

11 クロック生成回路

12 差動増幅回路

13 第1充電電流生成回路

14 第2充電電流生成回路

15 第1放電用定電流回路

16 第2放電用定電流回路

17 第1パルス生成回路

18 第2パルス生成回路

19 パルス合成回路

AU オーディオ発生源

C1 第1コンデンサ

C2 第2コンデンサ

eS オーディオ信号

SW1 第1スイッチ

SW2 第2スイッチ

SW3 第3スイッチ

SW4 第4スイッチ

T1 第1期間

T2 第2期間

T3 第3期間

T4 第3期間

φ1 第1制御信号

φ2 第2制御信号

φ3 第3制御信号

φ4 第4制御信号

【技術分野】

【0001】

本願発明は、例えばオーディオ信号をパルス幅変調(PWM)してその変調信号を出力するパルス幅変調回路及びそれを用いたスイッチングアンプに関するものである。

【背景技術】

【0002】

従来、オーディオアンプに用いられるスイッチングアンプでは、例えば入力信号としてのオーディオ信号をパルス幅変調し、その変調信号を出力するパルス幅変調回路が用いられているものが提案されている。このスイッチングアンプでは、パルス幅変調回路から出力される変調信号に基づいて所定の電源電圧がスイッチングされ、スイッチングされた出力信号が例えばローパスフィルタを通して負荷(例えばスピーカ)に出力される。

【0003】

図8は、従来のスイッチングアンプの一例を示す構成図である。このスイッチングアンプは、オーディオ信号発生源AUに接続されたパルス幅変調回路1と、スイッチング回路2と、ローパスフィルタ回路3と、正負の電源電圧+EB,−EBを供給する第1電源4及び第2電源5とを備えている。ローパスフィルタ回路3には、負荷RLとしてのスピーカが接続されている。

【0004】

パルス幅変調回路1では、オーディオ信号発生源AUから出力された入力信号としてのオーディオ信号eSをパルス幅変調することにより変調信号PWMoutが生成される。スイッチング回路2では、変調信号PWMoutと逆位相の変調信号PWMout’が生成される。

【0005】

スイッチング回路2では正の電源電圧+EBを供給する第1電源4と負の電源電圧−EBを供給する第2電源5との間にスイッチ素子SW−Aとスイッチ素子SW−Bの直列回路が接続されている。スイッチング回路2では、変調信号PWMout及び変調信号PWMout'に基づいて、スイッチ素子SW−A,SW−Bのオン・オフ動作を制御することにより電源電圧+EB,−EBが交互にローパスフィルタ回路3に出力される。この出力は、コイルL0及びコンデンサC0のL型回路からなるローパスフィルタ回路3によって高周波成分が除去され、ローパスフィルタ回路3の出力(増幅されたオーディオ信号)は、負荷RL(スピーカ)に供給されることにより音声として出力される。

【0006】

例えば、特許文献1には、オーディオ信号eSに基づいてPWM変調信号を生成するパルス幅変調回路が提案されている。このパルス幅変調回路では、以下の原理に基づいてPWM変調信号が生成される。

(1)オーディオ信号eS(電圧信号)のレベルを所定の周期Tでサンプリングする。

(2)サンプリングした電圧値を電流値に変換し、その電流値でT/2の期間(充電期間)だけコンデンサを充電する。

(3)T/2の充電期間の充電動作後に、一定の電流値でT/2の時間だけコンデンサの蓄積電荷を放電する。

(4)このコンデンサの放電時間をハイレベル期間とするパルスを生成する。この場合、コンデンサの充電電圧が高いときには、放電動作を行なう期間(T/2の放電期間)内における放電時間(蓄積電荷を放出する時間)は長くなり、パルス幅が長くなる。一方、コンデンサの充電電圧が低いときには、放電期間内における放電時間は短くなり、パルス幅が短くなる。

(5)上記の充放電動作は、2つのコンデンサについて行なうようにし、これらの充放電動作をT/2の時間だけずらすことによりそれぞれのパルス信号を生成し、両者を合成してPWM変調信号を生成する。

【0007】

図9は、特許文献1に提案されているパルス幅変調回路を機能ブロックで示した図である。

【0008】

パルス幅変調回路1は、同図に示すように、クロック生成回路100と、電圧−電流変換回路101と、第1及び第2コンデンサC1,C2と、スイッチ回路102と、放電用定電流回路103と、第1及び第2パルス生成回路104,105と、パルス合成回路106とによって構成されている。スイッチ回路102は、それぞれ2つずつのスイッチを有する第1及び第2スイッチ部102a,102bによって構成されている。

【0009】

電圧−電流変換回路101は、オーディオ信号発生源AU(図8参照)から供給されるオーディオ信号eS(電圧信号)を当該オーディオ信号eSの振幅に電流値が比例する電流信号に変換する。クロック生成回路100は、周期Tでデューティ比50%のパルス信号からなる第1制御信号φ1と、第1制御信号φ1とはハイレベルとローレベルが逆になっている第2制御信号φ2を生成する。第1スイッチ部102a内の一方のスイッチ(電圧−電流変換回路101に接続されたスイッチ)のオン・オフ動作は第1制御信号φ1によって制御され、第2スイッチ部102b内の一方のスイッチ(電圧−電流変換回路101に接続されたスイッチ)のオン・オフ動作は第2制御信号φ2によって制御される。

【0010】

第1スイッチ部102a内の一方のスイッチがオンになると、第1コンデンサC1が電圧−電流変換回路101から出力される電流信号によって充電され、第2スイッチ部102b内の一方のスイッチがオンになると、第2コンデンサC2が電圧−電流変換回路101から出力される電流信号によって充電される。

【0011】

第1パルス生成回路104は、第1コンデンサC1が放電開始時のレベルから所定の基準レベルに変化するまでの放電時間をパルス幅とするパルス信号rsout1と、第1スイッチ部102a内の他方のスイッチ(放電用定電流回路103に接続されたスイッチ)のオン・オフ動作を制御する第3制御信号φ3とを生成する。第2パルス生成回路105は、第2コンデンサC2が放電開始時のレベルから上記の基準レベルに変化するまでの放電時間をパルス幅とするパルス信号rsout2と、第2スイッチ部102b内の他方のスイッチ(放電用定電流回路103に接続されたスイッチ)のオン・オフ動作を制御する第4制御信号φ4とを生成する。

【0012】

第3制御信号φ3は、第1制御信号φ1のローレベル期間内にハイレベル期間が生じるパルス信号である。第1スイッチ部102a内の他方のスイッチがオンになると、第1コンデンサC1に蓄積された電荷が放電用定電流回路103によって一定の電流で放電される。第4制御信号φ4は、第2制御信号φ2のローレベル期間内にハイレベル期間が生じるパルス信号である。第2スイッチ部102b内の他方のスイッチがオンになると、第2コンデンサC2に蓄積された電荷が放電用定電流回路103によって一定の電流で放電される。

【0013】

従って、第1コンデンサC1は、第1制御信号φ1のハイレベル期間(T/2)に充電され、それに続くローレベル期間(T/2)内で第3制御信号φ3がハイレベルとなる期間に蓄積電荷が放電される。同様に、第2コンデンサC2は、第2制御信号φ2のハイレベル期間(T/2)に充電され、それに続くローレベル期間(T/2)内で第4制御信号φ4がハイレベルとなる期間に蓄積電荷が放電される。

【0014】

第1制御信号φ1と第2制御信号φ2は互いにハイレベル期間とローレベル期間が逆になっており、第1コンデンサC1の充電期間が第2コンデンサC2の放電期間となり、第1コンデンサC1の放電期間が第2コンデンサC2の充電期間となるので、第1コンデンサC1と第2コンデンサC2は交互に充電動作と放電動作とが行なわれる。

【0015】

パルス生成回路104から出力されるパルス信号rsout1とパルス生成回路105から出力されるパルス信号rsout2はパルス合成回路106で合成される。パルス生成回路104から出力されるパルス信号rsout1は、周期Tで第1コンデンサC1が蓄積電荷を放電する時間だけハイレベルとなる信号であり、パルス生成回路105から出力されるパルス信号rsout2は、パルス生成回路104から出力されるパルス信号rsout1に対してT/2だけずれた、周期Tで第2コンデンサC2が蓄積電荷を放電する時間だけハイレベルとなる信号である。従って、パルス合成回路106では、T/2でパルス生成回路104から出力されるパルス信号rsout1とパルス生成回路105から出力されるパルス信号rsout2を交互に合成した信号(変調信号PWMoutに相当)が出力される。

【0016】

上記構成において、第1コンデンサC1及び第2コンデンサC2の充放電動作を制御するスイッチ部102a,102bは、各コンデンサC1,C2に対してそれぞれ必要となる。その一方、電圧−電流変換回路101及び放電用定電流回路103は、第1及び第2コンデンサC1,C2がT/2だけずれて充放電されるので、電圧−電流変換回路101及び放電用定電流回路103は共用される。

【0017】

図9に示すブロック構成図は、PWM変調信号の生成原理上、必要かつ十分なブロックの構成を可及的に簡素化して示しているが、図9に示すブロック構成に基づいてPWM変調回路を実現するための具体回路を表すと、例えば図10に示すような回路になる。

【0018】

なお、図10においては、オーディオ信号eSが入力されるオペアンプ101aと、その出力に接続されたpnp型のトランジスタ101bと、そのベース端子に接続された定電圧ダイオード101c等の部分が電圧−電流変換回路101に対応する。また、2つのアナログスイッチICで構成される部分がスイッチ回路102に対応し、アナログスイッチのスイッチSW3,SW4に接続されたnpn型のトランジスタ103a、及びそのベース端子に接続された定電圧ダイオード103b等の部分が放電用定電流回路103に対応している。

【0019】

図10に示す具体回路では、回路構成が複雑になり、回路スペースや製造コスト等の点で種々の問題が生じ易いという不都合がある。例えば、図10に示す具体回路では、以下の点で問題が生じる。

【0020】

(1)電圧−電流変換回路101を共通化するために、オペアンプを用いた回路構成とすることで、電圧−電流変換回路101を構成する部品点数が多くなる。

(2)アナログスイッチICを用いることにより、スイッチ回路102の回路スペースの効率化は可能になるが、製造コストが増加する。

(3)電圧−電流変換回路101、スイッチ回路102、及び放電用定電流回路103をそれぞれブロック単位で構成し、それらを接続する構成であるので、各回路の電源電圧が異なり、複数種類の電源(図10では、+14.6v,−14.6v,+3v,−3vの4種類)が必要になる分、回路が複雑になる。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】特開2008−206128号公報

【発明の概要】

【発明が解決しようとする課題】

【0022】

本願発明は、上記した事情のもとで考え出されたものであって、2つのパルス信号を生成するための同一構成のパルス生成回路をそれぞれ設け、各パルス生成回路を構成する電圧−電流変換回路、スイッチ回路及び放電用の定電流回路を簡素化することにより、上記した回路スペースや製造コスト等の低減することのできるパルス幅変調回路及びそれを適用したスイッチングアンプを提供することを、その課題とする。

【課題を解決するための手段】

【0023】

本願発明の第1の側面によって提供されるパルス幅変調回路は、所定の周期を有する基準クロックを生成し、その基準クロックのオン期間に充電動作を行なわせるための第1の制御信号と前記基準クロックのオフ期間に充電動作を行なわせるための第2の制御信号とを生成する充電制御信号生成部と、前記第1の制御信号により充電動作が行なわれたオン期間に続くオフ期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第3の制御信号と前記第2の制御信号により充電動作が行なわれたオフ期間に続くオン期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第4の制御信号とを生成する放電制御信号生成部と、前記第1及び第3の制御信号に基づき、入力信号のレベルに基づいて生成される充電電流により第1のコンデンサを充電する充電動作とその第1のコンデンサの蓄積電荷を一定の放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第1のコンデンサが放電開始時のレベルから前記所定の基準レベルに変化するまでの放電時間をパルス幅とする第1のパルス信号を生成する第1のパルス信号生成部と、前記第2及び第4の制御信号に基づき、前記充電電流により第2のコンデンサを充電する充電動作とその第2のコンデンサの蓄積電荷を前記放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第2のコンデンサが放電開始時のレベルから前記基準レベルに変化するまでの放電時間をパルス幅とする第2のパルス信号を生成する第2のパルス信号生成部と、前記第1のパルス信号生成部で生成される第1のパルス信号と前記第2のパルス信号生成部で生成される第2のパルス信号とを合成し、前記所定の周期を有し、各パルスのパルス幅が前記入力信号のレベルに応じて変化するパルス幅変調信号を出力するパルス信号合成部と、を備えたパルス幅変調回路であって、前記第1のパルス信号生成部は、前記入力信号の電圧を増幅する差動増幅回路と、前記差動増幅回路の一対の電源端子間に接続され、前記第1のコンデンサの充放電動作を制御する第1の制御回路と、前記第1のコンデンサの両端電圧に基づいて前記第1のパルス信号を生成する第1のパルス信号生成回路と、を備え、前記第1の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第1の充電電流生成回路とこの第1の充電電流生成回路で生成される充電電流による前記第1のコンデンサの充電動作を前記第1の制御信号により制御する第1のスイッチ回路との第1の直列回路と、前記放電電流として一定の電流を生成する第1の定電流回路とこの第1の定電流回路で生成される放電電流による前記第1のコンデンサの放電動作を前記第3の制御信号により制御する第2のスイッチ回路との第2の直列回路とを直列に接続し、その接続点に前記第1のコンデンサを接続した回路で構成され、前記第2のパルス信号生成部は、前記差動増幅回路を前記第1のパルス信号生成部と共有し、前記差動増幅回路の一対の電源端子間に接続され、前記第2のコンデンサの充放電動作を制御する第2の制御回路と、前記第2のコンデンサの両端電圧に基づいて前記第2のパルス信号を生成する第2のパルス信号生成回路と、を備え、前記第2の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第2の充電電流生成回路とこの第2の充電電流生成回路で生成される充電電流による前記第2のコンデンサの充電動作を前記第2の制御信号により制御する第3のスイッチ回路との第3の直列回路と、前記放電電流として一定の電流を生成する第2の定電流回路とこの第2の定電流回路で生成される放電電流による前記第2のコンデンサの放電動作を前記第4の制御信号により制御する第4のスイッチ回路との第4の直列回路とを直列に接続し、その接続点に前記第2のコンデンサを接続した回路で構成されている、ことを特徴としている(請求項1)。

【0024】

本願発明のパルス幅変調回路において、前記差動増幅回路は、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路が接続された回路で構成され、前記第1の定電流回路と前記第2の定電流回路は、前記定電流回路と同一の回路構成を有し、前記定電圧源を当該定電流回路と共用しているとよい(請求項2)。

【0025】

本願発明のパルス幅変調回路において、前記第1ないし第4のスイッチ回路は、半導体スイッチング素子からなり、前記第1及び第2の充電電流生成回路は、1個のトランジスタを用いた電圧−電流変換回路で構成されているとよい(請求項3)。

【0026】

この構成によれば、第1のパルス信号生成部に含まれる第1のコンデンサの充放電動作を制御する第1の制御回路と第2のパルス信号生成部に含まれる第2のコンデンサの充放電動作を制御する第2の制御回路を、充電電流生成回路とこの充電電流生成回路で生成される充電電流によるコンデンサの充電動作を充電用の制御信号によって制御するスイッチ回路との直列回路と、放電電流として一定の電流を生成する定電流回路とこの定電流回路で生成される放電電流によるコンデンサの放電動作を放電用の制御信号により制御するスイッチ回路との直列回路と直列に接続し、その接続点にコンデンサを接続するという同一の回路構成で構成し、両制御回路を共通化した差動増幅回路の一対の電源端子間に並列に接続する構成としたので、第1及び第2の制御回路に含まれる第1,第2の充電電流生成回路、充電制御用の第1,第2のスイッチ回路、放電用の第1,第2の定電流回路及び放電制御用の第3,第4のスイッチ回路をそれぞれトランジスタ等の半導体素子を用いた簡単な回路によって実現することができ、パルス幅変調回路の具体回路の簡単化を図ることができる。

【0027】

例えば、差動増幅回路を、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路を接続した回路とし、第1ないし第4のスイッチ回路を半導体スイッチ素子で構成し、第1及び第2の充電電流生成回路を1個のトランジスタを用いた電圧−電流変換回路で構成し、第1の定電流回路と第2の定電流回路を差動増幅回路に含まれる定電流回路と同一の回路構成にするとともに、当該定電流回路の定電圧源を共用する構成とすることにより、第1及び第2の制御回路を少ない部品点数で構成できるとともに、低価格の部品を使用することができる。これにより、パルス幅変調回路の具体回路の簡単化と製造コストの低減を図ることができる。

【0028】

また、第1及び第2の制御回路の駆動電源を差動増幅回路の駆動電源と共通化するとともに、第1の定電流回路と第2の定電流回路の定電圧源を差動増幅回路に含まれる定電流回路の定電圧源と共用することにより電源電圧の種類を少なくすることができ、パルス幅変調回路の電源も簡素化することができる。

【0029】

本願発明の第2の側面によって提供されるスイッチングアンプは、本願発明の第1の側面によって提供されるパルス幅変調回路と、所定の電源電圧を出力する電圧源と、前記パルス幅変調回路から出力される変調信号に基づいて、前記電圧源から供給される所定の電源電圧をスイッチングするスイッチング回路と、を備えたことを特徴としている(請求項4)。

【0030】

この構成によれば、このスイッチングアンプは、本願発明の第1の側面によって提供されるパルス幅変調回路を備えているので、第1の側面によって提供されるパルス幅変調回路と同様の作用効果を奏する。

【0031】

本発明のその他の特徴及び利点は、添付図面を参照して以下に行なう詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0032】

【図1】本願発明に係るパルス幅変調回路の一実施例を示すブロック回路図である。

【図2】パルス幅変調回路に含まれる充放電動作に関する回路の詳細回路図である。

【図3】オーディオ信号が無信号の場合のパルス幅変調回路の各信号の波形を示す図である。

【図4】パルス生成回路及びパルス合成回路の具体回路を示す図である。

【図5】パルス幅変調回路におけるパルス幅変調動作を説明するための図である。

【図6】従来のパルス幅変調回路において、第1制御信号のハイレベルと第2制御信号のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【図7】本願発明に係るパルス幅変調回路において、第1制御信号のハイレベルと第2制御信号のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【図8】従来のパルス幅変調回路が適用されるスイッチングアンプを示す構成図である。

【図9】従来のパルス幅変調回路を示すブロック構成図である。

【図10】従来のパルス幅変調回路を示す詳細回路図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施の形態につき、図面を参照して具体的に説明する。

【0034】

本願発明に係るパルス幅変調(PWM)回路が適用されるスイッチングアンプは、背景技術の欄で説明した図8に示すスイッチングアンプと同様である。よって、ここでは、その説明を省略する。

【0035】

図1は、パルス幅変調回路10のブロック構成図である。図2は、パルス幅変調回路10に含まれる充放電動作に関する回路(図1の一点鎖線で囲まれた回路参照)の詳細回路図である。パルス幅変調回路10は、図1に示すように、クロック生成回路11と、差動増幅回路12と、第1及び第2充電電流生成回路13,14と、第1ないし第4スイッチSW1〜SW4と、第1及び第2コンデンサC1,C2と、第1及び第2放電用定電流回路15,16と、第1及び第2パルス生成回路17,18と、パルス合成回路19とによって構成されている。

【0036】

なお、以下の説明では、このパルス幅変調回路10の動作を示す図3のタイミングチャートを随時参照する。

【0037】

クロック生成回路11は、基準クロック信号MCLK(図3(a)参照)を生成し、その基準クロック信号MCLKから第1制御信号φ1と第2制御信号φ2を生成する。基準クロック信号MCLKは、デューティ比がほぼ50%のクロック信号であり、第1及び第2制御信号φ1,φ2の基準信号となるものである。第1及び第2制御信号φ1,φ2は、第1及び第2コンデンサC1,C2に充電動作を行なわせるために第1及び第2スイッチSW1,SW2のオン、オフ動作を制御する信号である。第2制御信号φ2は、第1制御信号φ1に対して逆位相の関係を有する。クロック生成回路11は、第1制御信号φ1を第1スイッチSW1に出力し、第2制御信号φ2を第2スイッチSW2に出力する。

【0038】

また、クロック生成回路11は、第1及び第2制御信号φ1,φ2から第1及び第2セット信号set1,set2を生成する。第1セット信号set1は、図3(d)に示すように、第1制御信号φのハイレベルからローレベルに反転する際の立下りエッジを検出した信号であり、第2セット信号set2は、図3(e)に示すように、第2制御信号φのハイレベルからローレベルに反転する際の立下りエッジを検出した信号である。第1セット信号set1は、R−Sラッチ回路によって構成される第1パルス生成回路17にセット信号として入力され、第2セット信号set2は、R−Sラッチ回路によって構成される第2パルス生成回路18にセット信号として入力される。

【0039】

差動増幅回路12は、オーディオ信号発生源AU(図8参照)からパルス幅変調回路10に供給されるオーディオ信号eSの接地レベル(0ボルト)を基準とした振幅を増幅して出力する回路である。差動増幅回路12は、2つのトランジスタのエミッタを相互に接続し、両トランジスタのコレクタをそれぞれ抵抗を介して正の電源(電源電圧+V)に接続する一方、両トランジスタのエミッタを定電流回路を介して負の電源(電源電圧−V)に接続した周知の差動増幅回路である。差動増幅回路12では、一方のトランジスタのベースにオーディオ信号eSを入力し、他方のトランジスタのベースを接地することによって両トランジスタのコレクタの間にオーディオ信号eSの0ボルト(接地レベル)を基準とした差電圧(オーディオ信号eSの振幅)を増幅した電圧が出力される。この差電圧は、第1及び第2充電電流生成回路13,14に出力される。

【0040】

第1及び第2充電電流生成回路13,14は、差動増幅回路12から出力される電圧をその電圧の変化に比例して変化する電流に変換する回路である。第1充電電流生成回路13と第2充電電流生成回路14は同一の回路構成である。第1充電電流生成回路13は、第1コンデンサC1に接続されており、電圧−電流変換した電流を第1コンデンサC1に供給することで第1コンデンサC1を充電する。従って、第1充電電流生成回路13は、第1コンデンサC1を充電するための充電電流を生成する。一方、第2充電電流生成回路14は、第2コンデンサC2に接続されており、電圧−電流変換した電流を第2コンデンサC2に供給することで第2コンデンサC2を充電する。従って、第2充電電流生成回路14は、第2コンデンサC2を充電するための充電電流を生成する。

【0041】

第1及び第2充電電流生成回路13,14における変換コンダクタンスをGmとすると、オーディオ信号eSが第1及び第2充電電流生成回路13,14で変換される電流Δiは、Δi=Gm・eSで表すことができる。また、第1及び第2充電電流生成回路13,14におけるバイアス電流をIcとすると、第1及び第2コンデンサC1,C2の充電電流は、Ic+Gm・eS=Ic+Δiで表すことができる。

【0042】

第1スイッチSW1は、第1充電電流生成回路13に電源電圧+Vを供給するか否か、すなわち、第1充電電流生成回路13を動作させて第1コンデンサC1を充電するか否かを制御する回路であり、第2スイッチSW2は、第2充電電流生成回路14に電源電圧+Vを供給するか否か、すなわち、第2充電電流生成回路14を動作させて第2コンデンサC2を充電するか否かを制御する回路である。第1スイッチSW1と第2スイッチW2は同一の回路構成である。第1及び第2スイッチSW1,SW2は、クロック生成回路11から出力される第1及び第2制御信号φ1,φ2に基づいてオン、オフ動作される。第1スイッチSW1は、第1制御信号φ1がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。また、第2スイッチSW2は、第2制御信号φ2がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。

【0043】

第1放電用定電流回路15は、充電電流(Ic+Δi)で充電された第1コンデンサC1の蓄積電荷を放電させるための回路であり、第2放電用定電流回路15は、充電電流(Ic+Δi)で充電された第2コンデンサC2の蓄積電荷を放電させるための回路である。第1放電用定電流回路15は、第1コンデンサC1に接続されており、一定の放電電流Idで第1コンデンサC1に蓄積された電荷を引き込むことにより、第1コンデンサC1の蓄積電荷を放電させる。一方、第2放電用定電流回路16は、第2コンデンサC2に接続されており、一定の放電電流Idによって第2コンデンサC2に蓄積された電荷を引き込むことにより、第2コンデンサC2の蓄積電荷を放電させる。

【0044】

第3スイッチSW3は、第1放電用定電流回路15に電源電圧−Vを供給するか否か、すなわち、第1放電用定電流回路15を動作させて第1コンデンサC1を放電するか否かを制御する回路であり、第4スイッチSW4は、第2放電用定電流回路16に電源電圧−Vを供給するか否か、すなわち、第2放電用定電流回路16を動作させて第2コンデンサC2を放電するか否かを制御する回路である。第3スイッチSW3と第4スイッチW4は同一の回路構成である。第3及び第4スイッチSW3,SW4は、第1及び第2パルス生成回路17,18からそれぞれ出力される第3及び第4制御信号φ3,φ4に基づいてオン、オフ動作される。第3スイッチSW3は、第3制御信号φ3がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。また、第4スイッチSW4は、第4制御信号φ4がハイレベルの状態でオン動作し、ローレベルの状態でオフ動作する。

【0045】

第1及び第2コンデンサC1,C2は、オーディオ信号eSの振幅を時間に変換するための素子である。オーディオ信号eSの振幅は、第1及び第2コンデンサC1,C2をオーディオ信号eSの振幅に比例した充電電流(Ic+Δi)で一定時間(基準クロック信号MCLKの周期Tの1/2の時間)だけ充電した後その蓄積電荷を一定の放電電流Idで放電し、その放電時間をパルス幅とするパルスを生成することによって時間に変換される。

【0046】

第1パルス生成回路17は、第1コンデンサC1の両端電圧が放電開始時の電圧レベルから所定の基準レベルVthに変化するまでの放電時間をパルス幅とする第1パルス信号rsout1(図3(j)参照)と、第3スイッチSW3のオン・オフ動作を制御する第3制御信号φ3(図3(f)参照)を生成する回路である。なお、本実施形態では、後述するように第1パルス生成回路17及び第2パルス生成回路18はNAND回路を用いたR−Sラッチ回路で構成されるので、基準レベルVthはNAND回路のスレシホールドレベルとなる。

【0047】

第1パルス信号rsout1は、パルス合成回路19に出力され、第3制御信号φ3は第3スイッチSW3に出力される。第1パルス生成回路18は、第2コンデンサC2の両端電圧が放電開始時の電圧レベルから上記の基準レベルVthに変化するまでの放電時間をパルス幅とする第2パルス信号rsout2(図3(k)参照)と、第4スイッチSW4のオン・オフ動作を制御する第4制御信号φ4(図3(g)参照)を生成する回路である。第2パルス信号rsout2は、パルス合成回路19に出力され、第4制御信号φ4は第4スイッチSW4に出力される。

【0048】

パルス合成回路19は、第1及び第2パルス生成回路17,18から出力される第1及び第2パルス信号rsout1,rsout2を合成し、PWM変調信号PWMout(図3(l)参照)として出力する回路である。

【0049】

次に、図2を参照して充放電動作に関する回路(図1の一点鎖線で囲まれた回路参照)の詳細について説明する。なお、図1と同一機能を果たす回路には同一の符号を付している。

【0050】

差動増幅回路12は、npn型の第1トランジスタQ1のエミッタとnpn型の第1トランジスタQ2のエミッタをそれぞれ抵抗R3と抵抗R4を介して定電流回路に接続し、第1トランジスタQ1のコレクタと第2トランジスタQ2のコレクタをそれぞれ抵抗R1と抵抗R2を介して正の電源(電源電圧+V)に接続した周知の差動増幅回路である。

【0051】

第1トランジスタQ1のベースには、カップリングコンデンサCaを介してオーディオ信号eSが入力され、第2トランジスタQ2のベースは、接地(0ボルトレベル)されている。

【0052】

定電流回路は、npn型の第3トランジスタQ3のエミッタを抵抗R6を介して負の電源(電源電圧−V)に接続し、ベースを抵抗R11を介して正の電源(電源電圧+V)に接続するとともにベースと負の電源の間にツェナーダイオード(定電圧ダイオード)D1を接続した周知の定電流回路である。第3トランジスタQ3のコレクタは、抵抗R3と抵抗R4に接続されている。この回路では、第3トランジスタQ3のベース電圧がツェナーダイオードD1のツェナ電圧Vzになるので、第3トランジスタQ3のコレクタには(Vz−Vbe)/R6(Vbeは第3トランジスタQ3のベース−エミッタ間の電圧)の定電流Idが流れる。

【0053】

第1充電電流生成回路13と第2充電電流生成回路14は、pnp型トランジスタのエミッタに電流制限用の抵抗を接続した回路で構成され、第1スイッチSW1と第2スイッチSW2は、pnp型トランジスタで構成されている。第1スイッチSW1と第1充電電流生成回路13は直列に接続され、第2スイッチSW2と第2充電電流生成回路14は直列に接続されている。また、第1スイッチSW1と第2スイッチSW2のエミッタは共に正の電源(電源電圧+V)に接続され、第1充電電流生成回路13を構成する第4トランジスタQ4と第2充電電流生成回路14を構成する第5トランジスタQ5のコレクタはそれぞれ第1コンデンサC1と第2コンデンサに接続されている。

【0054】

第4トランジスタQ4と第5のトランジスタQ5のベースには差動増幅回路12内の第1トランジスタQ1のコレクタが接続され、差動増幅回路12からオーディオ信号esの接地レベルを基準とした振幅が入力される。また、第1スイッチSW1と第2スイッチSW2のベースにはクロック生成回路11からそれぞれ第1制御信号φ1と第2制御信号φ2が入力される。

【0055】

第1放電用定電流回路15と第2放電用定電流回路16は、差動増幅回路12内の定電流回路と同一の回路で構成され、第3スイッチSW3と第4スイッチSW4は、npn型トランジスタで構成されている。第1放電用定電流回路15と第3スイッチSW3は直列に接続され、第2放電用定電流回路16と第4スイッチSW4は直列に接続されている。第1放電用定電流回路15と第2放電用定電流回路16は、npn型トランジスタ、エミッタ抵抗及びツェナーダイオードを用いた定電流回路であるが、第1及び第2放電用定電流回路15,16のnpn型トランジスタのベース電圧を与えるツェナーダイオードは、差動増幅回路12内の定電流回路のツェナーダイオードD1が共用されている。

【0056】

従って、第1放電用定電流回路15を構成する第6トランジスタQ6のコレクタは第1コンデンサC1に接続され、第6トランジスタQ6のエミッタは抵抗R9を介して第3スイッチSW3のコレクタに接続されている。また、第2放電用定電流回路16を構成する第7トランジスタQ7のコレクタは第2コンデンサに接続され、第7トランジスタQ7のエミッタは抵抗R10を介して第4スイッチSW4のコレクタに接続されている。そして、第6トランジスタQ6及び第7トランジスタQ7のベースは、ツェナーダイオードD1のカソードに接続されている。

【0057】

また、第3スイッチSW3及び第4スイッチSW4のエミッタは負の電源(電源電圧−V)に接続され、第3スイッチSW3のベースには第1パルス生成回路17から出力される第3制御信号φ3が入力され、第4スイッチSW4のベースには第2パルス生成回路18から出力される第4制御信号φ4が入力される。

【0058】

図2の回路では、第1制御信号φ1がローレベルになると、第1スイッチSW1がオンになり、第1充電電流生成回路13に正の電源(+V)が接続され、第1充電電流生成回路13内の第4トランジスタQ4が動作する。第4トランジスタQ4のベースには差動増幅回路12から接地レベルに対するオーディオ信号eSの差電圧、すなわち、オーディオ信号eSの振幅値が入力されるので、第4トランジスタQ4のコレクタにはオーディオ信号eの振幅値に比例した充電電流(Ic+Δi)が流れ、第1コンデンサC1が第1制御信号φ1のローレベルの期間にこの充電電流(Ic+Δi)によって充電される(図3(b),(h)のT1,T3期間の波形参照)。

【0059】

同様に、第2制御信号φ2がローレベルになると、第2スイッチSW2がオンになり、第2充電電流生成回路14に正の電源(+V)が接続され、第2充電電流生成回路14内の第5トランジスタQ5が動作する。第4トランジスタQ4のベースにも差動増幅回路12から接地レベルに対するオーディオ信号eSの差電圧が入力されるので、第5トランジスタQ5のコレクタにはオーディオ信号eの振幅値に比例した充電電流(Ic+Δi)が流れ、第2コンデンサC2が第2制御信号φ2のローレベルの期間にこの充電電流(Ic+Δi)によって充電される(図3(c),(i)のT2,T4期間の波形参照)。

【0060】

また、第3制御信号φ3がハイレベルになると、第3スイッチSW3がオンになり、第1放電用定電流回路15に負の電源(−V)が接続され、第1放電用定電流回路15内の第6トランジスタQ6が一定の電流Idを引き込む動作を行なう。これにより、第1コンデンサC1の蓄積電荷が定電流Idで放電される(図3(f),(h)のT2,T4期間の波形参照)。

【0061】

同様に、第4制御信号φ4がハイレベルになると、第4スイッチSW4がオンになり、第2放電用定電流回路16に負の電源(−V)が接続され、第2放電用定電流回路16内の第7トランジスタQ7が一定の電流Idを引き込む動作を行なう。これにより、第2コンデンサC2の蓄積電荷が定電流Idで放電される(図3(g),(i)のT1,T3期間の波形参照)。

【0062】

第1パルス生成回路17は、図4に示すように、2個のNAND回路を用いた周知のR−Sラッチ回路で構成されている。第1パルス生成回路17の第2NAND回路N2の入力端子はS(set)信号の入力端子であり、第1NAND回路N1の入力端子はR(reset)信号の入力端子である。また、第1NAND回路N1の出力端子は/Q信号の出力端子であり、第2NAND回路N2の出力端子はQ信号の出力端子である。

【0063】

そして、第1パルス生成回路17の第1NAND回路N1の入力端子には第1コンデンサC1の両端電圧が第1リセット信号res1として入力され、第2NAND回路N2の入力端子にはクロック生成回路11から出力される第1セット信号set1が入力される。また、第1NAND回路N1の出力端子から出力されるパルス信号はPWM変調信号PWMoutを生成するための第1パルス信号rsout1としてパルス合成回路19に入力され、第2NAND回路N2の出力端子から出力されるパルス信号は第3制御信号φ3として第3スイッチSW3のベースに入力される。

【0064】

図4に示すR−Sラッチ回路では、(S,R)=(ハイ,ロー)で(Q,/Q)=(ハイ,ロー)の論理となり、(S,R)=(ロー,ハイ)で(Q,/Q)=(ロー,ハイ)の論理となる。図3(d),(h)に示されるように、第1制御信号φ1が立ち下がるタイミングで第1セット信号set1は一瞬ローレベルになり、第1コンデンサC1の両端電圧(第1リセット信号res1)はハイレベルとなるので、第1パルス信号rsout1はローレベルとなり、第3制御信号φ3はハイレベルとなる(図3(f)(j)参照)。第3制御信号φ3がハイレベルになると、第1コンデンサC1の放電が開始されるが、第1コンデンサC1の両端電圧が第1NAND回路N1のスレシホールドレベルVthより高い間は第1パルス信号rsout1がローレベルに保持され、スレシホールドレベルVthに達すると、第1セット信号set1はハイレベルになり、第1リセット信号res1はローレベルとなるので、そのタイミングで第1パルス信号rsout1はハイレベルとなり、第3制御信号φ3はローレベルとなる(図3(f)(j)参照)。

【0065】

第2パルス生成回路18も第1パルス生成回路17と同様に、2個のNAND回路を用いた周知のR−Sラッチ回路で構成されている。図4に示すように、第2パルス生成回路18の第3NAND回路N3の入力端子には第2コンデンサC2の両端電圧が第2リセット信号res2として入力され、第4NAND回路N4の入力端子にはクロック生成回路11から出力される第2セット信号set2が入力される。また、第3NAND回路N3の出力端子から出力されるパルス信号はPWM変調信号PWMoutを生成するための第2パルス信号rsout2としてパルス合成回路19に入力され、第4NAND回路N4の出力端子から出力されるパルス信号は第4制御信号φ4として第4スイッチSW3のベースに入力される。

【0066】

図3(e),(i)に示されるように、第2制御信号φ2が立ち下がるタイミングで第2セット信号set2は一瞬ローレベルになり、第2コンデンサC2の両端電圧(第1リセット信号res1)はハイレベルとなるので、第2パルス信号rsout2はローレベルとなり、第4制御信号φ4はハイレベルとなる(図3(g)(k)参照)。第4制御信号φ4がハイレベルになると、第2コンデンサC2の放電が開始されるが、第2コンデンサC2の両端電圧が第3NAND回路N3のスレシホールドレベルVthより高い間は第2パルス信号rsout2がローレベルに保持され、スレシホールドレベルVthに達すると、第2セット信号set2はハイレベルになり、第2リセット信号res2はローレベルとなるので、そのタイミングで第2パルス信号rsout2はハイレベルとなり、第4制御信号φ4はローレベルとなる(図3(g)(k)参照)。

【0067】

パルス合成回路19は、図4に示すように、第5NAND回路N5によって構成され、第1パルス生成回路17から出力される第1パルス信号rsout1と、第2パルス生成回路18から出力される第2パルス信号rsout2との否定論理積を演算することによりパルス幅変調信号PWMoutを生成する(図3(l)参照)。

【0068】

次に、パルス幅変調回路10におけるパルス幅変調動作について、図5を用いて簡単に説明する。なお、第1コンデンサC1と第2コンデンサC2で同様のパルス幅変調動作が行なわれるので、ここでは第1コンデンサC1におけるパルス幅変調動作について説明する。

【0069】

第1制御信号φ1がハイレベルになると、第1スイッチSW1がオンになり、第1充電電流生成回路13が充電電流(Ic+Δi)の生成動作を行なう。第1制御信号φ1がハイレベルの期間では第3制御信号φ3がローレベルであるので、第3スイッチSW3がオフ状態となっており(図3(b)(f)参照)、第1放電用定電流回路15は動作していない。従って、第1コンデンサC1には第1充電電流生成回路13で生成された充電電流(Ic+Δi)のみが流れ込み、これにより第1コンデンサC1が充電される。この充電動作は、第1制御信号φ1がオンになっている期間(図5ではT1の期間)に行なわれる。

【0070】

期間T1における第1コンデンサC1の両端電圧(図2のA点の電圧)は、基準電圧Vthから充電電流(Ic+G・eS)の大きさに比例した傾きで上昇する。充電電流(Ic+G・eS)はオーディオ信号eSの正負の方向及び振幅の大きさに依存し、eS>0で振幅|eS|が大きいほど、期間T1の終了時の充電電圧は高くなり、eS<0で振幅|eS|が大きいほど、期間T1の終了時の充電電圧は低くなる。なお、図5では、期間T1はオーディオ信号eSの振幅変動に対して非常に短く、期間T1ではオーディオ信号eSの振幅変動は殆どなく一定であるとして第1コンデンサC1の充電電圧をほぼ直線的に上昇させている。

【0071】

図5の電圧波形S0は、eS=0のとき(オーディオ信号eSが無信号のとき)の波形を示し、電圧波形S1は、eS>0のときの波形を示し、電圧波形S2は、eS<0のときの波形を示している。

【0072】

第1コンデンサC1の容量を「C」、期間T1の終了時の第1コンデンサC1の充電電圧を「Vj」とすると、期間T1における第1コンデンサC1の充電動作においては、(Ic+G・eS)×T1=C×(Vj−Vth)の関係が成立する。この関係式より、Vj=G・eS×T1/C+Ic×T1/C+Vthとなるので、A=G×T1/C、B=Ic×T1/C+Vthとして整理すると、Vj=A×eS+Bとなる。図5によれば、eS=0ではVj=V0であるから、B=V0となるので、第1コンデンサC1の充電電圧VjはVj=A×eS+V0を表される。すなわち、第1コンデンサC1の充電電圧VjはV0を中心にeS>0ではオーディオ信号eSの振幅|eS|に比例して増大し、eS<0ではオーディオ信号eSの振幅|eS|に比例して減少する。

【0073】

第1制御信号φ1がローレベルになると同時に第3制御信号φ3がハイレベルになると、第1スイッチSW1がオフなると同時に第3スイッチSW3がオンになり、第1充電電流生成回路13が動作を停止し、第1放電用定電流回路15が定電流Idの引き込み動作を行なう。従って、第1コンデンサC1に蓄積された電荷が定電流Idで第1放電用定電流回路15に引き込まれ、これにより第1コンデンサC1の蓄積電荷が放電される。この放電動作は、第1コンデンサC1の電圧が基準電圧Vthに低下するまで行なわれる。

【0074】

第1コンデンサC1の電圧が基準電圧Vthに低下すると、第3制御信号φ3がローレベルに反転し、第3スイッチSW3がオフになるので、第1放電用定電流回路15の定電流Idによる引き込み動作が停止する。すなわち、第1コンデンサC1の電圧が基準電圧Vthに低下してから次に第1制御信号φ1がハイレベルになるまでの期間は、第1コンデンサC1に充電電流も放電電流も流れない状態となる。従って、第1コンデンサC1の電圧は第1制御信号φ1がハイレベルになるまで基準電圧Vthに保持される(図5の時間t1k,t0k,t2k参照)。

【0075】

第1コンデンサC1の充電電圧を「Vj」、放電時間を「Th」とすると、Id×Th=C×(Vj−Vth)の関係が成立するから、Th=C×Vj/id−Vth/Idより、放電時間Thは、充電電圧Vjに比例する。すなわち、充電電圧Vjが高いほど、放電時間Thは長くなる。図5において、時間t1は、オーディオ信号eS>0のときの放電時間を示し、時間t0は、オーディオ信号eS=0のときの放電時間を示し、時間t2は、オーディオ信号eS<0のときの放電時間を示し、t2<t0<t1の関係になっている。

【0076】

そして、充電電圧Vjの高さは、オーディオ信号eSの振幅|eS|に比例するから、放電時間Thもオーディオ信号eSの振幅|eS|に比例することになる。すなわち、第1コンデンサC1の放電時間Thは、オーディオ信号eSの振幅|eS|により変調された時間を示す。上記のパルス幅変調動作は、第2コンデンサC2についても同様である。

【0077】

本実施形態に係るパルス幅変調回路10では、図3に示すように、基準クロック信号MCLKの周期Tのハイレベル期間で第2コンデンサC2によりオーディオ信号eSをパルス幅変調したパルスを生成し、それに続くローレベル期間で第1コンデンサC1によりオーディオ信号eSをパルス幅変調したパルスを生成するので、両パルスをパルス合成回路19で合成することにより基準クロック信号MCLKの周期Tを有するパルス幅変調信号PWMoutを生成している。

【0078】

次に、パルス幅変調回路10の動作を図3に示すタイミングチャートを参照して説明する。図3は、オーディオ信号eSが無信号の場合(Gm・eS=0)を示している。図3では、基準クロック信号MCLKが最初にハイレベルになる期間から2周期分のハイレベルとローレベルの期間に対してそれぞれ第1期間T1、第2期間T2、第3期間T3、第4期間T4と言うことにする。

【0079】

第1期間T1では、クロック生成回路11からの第1制御信号φ1がハイレベル(第2制御信号φ2がローレベル)であるので(図3(b)参照)、第1スイッチSW1がオン状態(第2スイッチSW2はオフ状態)となり、第1コンデンサC1に第1充電電流生成回路13が接続される。従って、第1期間T1では第1充電電流生成回路13から第1コンデンサC1に充電電流(Ic+Δi)が流れ込み、これにより第1コンデンサC1が充電される(図3(h)参照)。この充電動作は、第1期間T1が終了するまで行なわれる。

【0080】

第1期間T1が終了し、第1制御信号φ1がハイレベルからローレベルに反転すると、第1スイッチSW1がオフ状態になる。第1スイッチSW1のオフ状態は第2期間T2の間、継続する。クロック生成回路11では、第1制御信号φ1の反転時の立下りを検出し、第1パルス生成回路17に瞬間的にローレベルに変化する第1セット信号set1を出力する(図3(d)の最初のローレベル変化参照)。

【0081】

第1パルス生成回路17では、第2期間T2の開始時に第1セット信号set1(ローレベル)が入力されると、第2NAND回路N2の出力がローレベルからハイレベルに反転する(図3(f)参照)。第2NAND回路N2の出力は、第3制御信号φ3として第3スイッチSW3に入力されるので、第3スイッチSW3がオン状態となり、第1コンデンサC1に第1放電用定電流回路15が接続され、これにより、第1コンデンサC1は定電流Idで放電される(図3(h)参照)。

【0082】

また、第1パルス生成回路17では、第2期間T2の開始時に第1セット信号set1(ローレベル)が入力されると、第1NAND回路N1の出力をハイレベルからローレベルに反転する(図3(j)参照)。第1NAND回路N1の出力は、第1パルス信号rsout1としてパルス合成回路19に入力される。

【0083】

パルス合成回路19に第1NAND回路N1のローレベル出力が入力された時にはパルス合成回路19の第5NAND回路N5に第2パルス生成回路18から入力される第2パルス信号rsout2はハイレベルのため、パルス合成回路19からは第1パルス信号rsout1のレベルを反転したパルス(ハイレベルのパルス)が出力される(図3(l)の2つ目のパルス参照)。

【0084】

第2期間T2においては、第1コンデンサC1が定電流Idで放電されるので、第1コンデンサC1の両端電圧が低下する。第1パルス生成回路17では第1コンデンサC1の両端電圧が第1NAND回路N1に入力されているが、第1コンデンサC1の両端電圧が基準電圧Vthに低下すると、その時の電圧がローレベルの第1リセット信号res1として第1パルス生成回路17に入力されることになる。第1パルス生成回路17に第1リセット信号res1が入力されると、第1パルス信号rsout1は、ローレベルからハイレベルに反転する(図3(j)参照)。

【0085】

一方、第2期間T2では、クロック生成回路11からの第2制御信号φ2がハイレベル(第1制御信号φ1がローレベル)であるので(図3(c)参照)、第2スイッチSW2がオン状態(第1スイッチSW1はオフ状態)となり、第2コンデンサC2に第2充電電流生成回路14が接続される。従って、第2期間T2では第2充電電流生成回路14から第2コンデンサC2に充電電流(Ic+Δi)が流れ込み、これにより第2コンデンサC2が充電される(図3(i)参照)。この充電動作は、第2期間T2が終了するまで行なわれる。

【0086】

第2期間T2が終了し、第2制御信号φ2がハイレベルからローレベルに反転すると、第2スイッチSW2がオフ状態になる。第2スイッチSW2のオフ状態は第3期間T3の間、継続する。クロック生成回路11では、第2制御信号φ2の反転時の立下りを検出し、第2パルス生成回路18に瞬間的にローレベルに変化する第2セット信号set2を出力する(図3(e)参照)。

【0087】

第2パルス生成回路18では、第3期間T3の開始時に第2セット信号set2(ローレベル)が入力されると、第4NAND回路N4の出力がローレベルからハイレベルに反転する(図3(g)参照)。第4NAND回路N4の出力は、第4制御信号φ4として第4スイッチSW4に入力されるので、第4スイッチSW4がオン状態となり、第2コンデンサC2に第2放電用定電流回路16が接続され、これにより、第2コンデンサC2は定電流Idで放電される(図3(i)参照)。

【0088】

また、第2パルス生成回路18では、第3期間T3の開始時に第2セット信号set2(ローレベル)が入力されると、第3NAND回路N3の出力をハイレベルからローレベルに反転する(図3(k)参照)。第3NAND回路N3の出力は、第2パルス信号rsout2としてパルス合成回路19に入力される。

【0089】

パルス合成回路19に第3NAND回路N3のローレベル出力が入力された時にはパルス合成回路19の第5NAND回路N5に第1パルス生成回路17から入力される第1パルス信号rsout1はハイレベルのため、パルス合成回路19からは第2パルス信号rsout2のレベルを反転したパルス(ハイレベルのパルス)が出力される(図3(l)の3つ目のパルス参照)。

【0090】

以下、第3期間以降では第1期間T1及び第2期間T2と同様の動作が繰返される。従って、パルス合成回路19からは基準クロック信号MCLKの半周期毎に第1パルス信号rsout1と第2パルス信号rout2のレベルを反転したパルスが交互に出力される。

【0091】

上記のように、パルス幅変調回路10では、図1に示すように、第1コンデンサC1の充電動作を制御する回路と第2コンデンサC2の充電動作を制御する回路を同一の回路構成(スイッチ回路と充電電流生成回路の直列回路)にするとともに、第1コンデンサC1の放電動作を制御する回路と第2コンデンサC2の放電動作を制御する回路を同一の回路構成(スイッチ回路と放電用定電流回路の直列回路)としているので、図2に示すように、充電動作を制御する第1スイッチSW1及び第2スイッチSW2を同一のトランジスタで実現することができるとともに、放電動作を制御する第3スイッチSW3及び第4スイッチSW4を同一のトランジスタで実現することができる。

【0092】

また、第1充電電流生成回路13及び第2充電電流生成回路14を、差動増幅回路12を共通化し、その差動増幅回路12にトランジスタを用いた同一回路構成の電圧−電流変換回路を接続することよって実現することができる。更に、第1放電用定電流回路15及び第2放電用定電流回路16をトランジスタとツェナーダイオードを用いた同一回路構成の定電流回路で実現することができる。

【0093】

しかも、この定電流回路は差動増幅回路12内の定電流回路と同一の回路構成とすることができるので、差動増幅回路12内のツェナーダイオードD1を第1放電用定電流回路15及び第2放電用定電流回路16のツェナーダイオードに共用することができる。更に、パルス幅変調回路10の駆動電源は正の電源(+V)と負の電源(−V)の2種類で良いので、電源回路も簡単にすることができる。

【0094】

従って、パルス幅変調回路10を少ない部品点数で実現でき、回路の簡素化、小型化を図ることができる。また、低価格のトランジスタやツェナーダイオード等の半導体素子を用いてパルス幅変調回路10を実現できるので、製造コストの低減を図ることができる。

【0095】

また、従来のパルス幅変調回路1では、図9に示すように、第1スイッチ部102a内の第1制御信号φ1で制御されるスイッチと第2スイッチ部102b内の第2制御信号φ2で制御されるスイッチが第1コンデンサC1と第2コンデンサC2の間で直列に接続される構成であるので、両スイッチが同時にオン状態になると、電圧−電流変換回路101に第1コンデンサC1と第2コンデンサC2が並列に接続され、第1コンデンサC1の充電動作と第2の充電動作が適正に行なわれないという不都合が生じる。

【0096】

特に、図10に示す具体回路では、第1スイッチ部102a及び第2スイッチ部102b内の4つのスイッチを、双方向特性を有するアナログスイッチICで構成しているので、第1制御信号φ1の立下りタイミングと第2制御信号φ2の立上りタイミングの間にデッドタイムがなければ、第1スイッチ部102a内の第1制御信号φ1で制御されるアナログスイッチと第2スイッチ部102b内の第2制御信号φ2で制御されるアナログスイッチが同時にオン状態になる虞があり、そのような状態が生じた場合はパルス幅変調回路1からは異常なPWM変調信号PWMoutが出力されることになるが、本実施形態に係るパルス幅変調回路10では、このような不都合が乗じることはない。以下、この効果について説明する。

【0097】

図6は、従来のパルス幅変調回路1において、第1制御信号φ1のハイレベルと第2制御信号φ2のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【0098】

図6の「φ1」と「φ2」の波形は、図9の第1スイッチ部102aと第2スイッチ部102bに入力される第1制御信号φ1と第2制御信号φ2の波形である。また、「C1」と「C2」の波形は、図9の第1パルス生成回路104と第2パルス生成回路105に入力される電圧波形であり、「rsout1」、「rsout2」、「PWMout」の波形は、それぞれ図9の第1パルス生成回路104、第2パルス生成回路105、パルス合成回路106から出力される電圧波形である。

【0099】

同図に示すように、第2制御信号φ2は、第2制御信号φ2の立上りタイミングが第1制御信号φ1の立下りタイミング対して微小時間tdだけ早くなるように設定されており、第1制御信号φ1の立下りタイミングより微小時間tdだけ前の期間で第1制御信号φ1と第2制御信号φ2が共にハイレベルになっている(図6(a),(b)参照)。

【0100】

第1期間T1において、第1制御信号φ1がハイレベルに立ち上ってから第2制御信号φ1がハイレベルに立ち上る直前までの期間は、電圧−電流変換回路101に第1コンデンサC1のみが接続され、第1コンデンサC1は電圧−電流変換回路101からの充電電流(Ic+Δi)によって充電されるので、第1コンデンサC1の両端電圧はほぼ直線的に上昇する。しかし、第2制御信号φ2がハイレベルに立ち上ると、第1コンデンサC1に第2コンデンサC2が並列に接続されるので、第1コンデンサC1の両端電圧は不連続に急減することになる。

【0101】

第2制御信号φ2の立上りタイミングにおける第1コンデンサC1の充電電圧を「Vj」とすると、その時点では第2コンデンサC2の蓄積電荷はゼロで、両端電圧は「Vth」であるから、第1コンデンサC1に第2コンデンサC2が並列に接続されると、合成容量が2倍になるので、第1コンデンサC1及び第2コンデンサC2の両端電圧は、(Vj+Vth)/2となる。図6に示すように、第1コンデンサC1の充電電圧Vjと第1コンデンサC1の充電電圧Vthの差電圧を「Cv」とすると、Vj=Vth+Cvより(Vj+Vth)/2=Vth+Cv/2となる。すなわち、第2制御信号φ2の立上りタイミングで、第1コンデンサC1の両端電圧は充電電圧Vjから第2コンデンサC2との差電圧Cvの1/2だけ急減し、第2コンデンサC2の両端電圧は電圧Vthから第1コンデンサC1との差電圧Cvの1/2だけ急増する(図6(c)(d)参照)。

【0102】

そして、第1制御信号φ1の立下がりタイミングでは、電圧−電流変換回路101に第1コンデンサC1と第2コンデンサC2が並列接続されている状態が第2コンデンサC2のみの接続状態になるので、第2コンデンサC2は電圧(Vth+Cv/2)から充電されることになる。一方、第1コンデンサC1は、第1制御信号φ1の立下がりタイミングで第3制御信号φ3がハイレベルとなり、放電用定電流回路103が接続されるので、電圧(Vth+Cv/2)から放電されることになる。

【0103】

この結果、第1コンデンサC1は、正常時は充電電圧(Vth+Cv)から放電が行なわれるところ、充電電圧(Vth+Cv/2)から電圧Vthまで放電が行なわれるので、その放電時間は正常時の放電時間よりも短くなる(図6(c),(e)参照)。一方、第2コンデンサC1は、正常時は電圧Vthから充電が行なわれるところ、電圧(Vth+Cv/2)から基準クロック信号MCLKの周期Tの1/2だけ充電されるので、その充電電圧は正常時の充電電圧よりも高くなる。従って、充電期間の放電期間では放電時間が正常時の放電時間よりも長くなる(図6(d),(f)参照)。この結果、第1コンデンサC1を用いて変調されるパルス幅と第2コンデンサC2を用いて変調されるパルス幅とに著しいアンバランスが生じ、図6(g)に示すように、PWM変調信号PWMoutの波形は異常な波形となる。

【0104】

従来のパルス幅変調回路1では、上記の不都合を解消するために、図9に示したクロック生成回路100の後段に必ずデッドタイム生成回路を設け、第1制御信号φ1がハイレベルからローレベルに立ち下がるタイミングから所定時間だけ遅れて第2制御信号φ2がローレベルからハイレベルに立ち上がるようにデッドタイムを設ける必要がある。

【0105】

これ対し、本実施形態に係るパルス幅変調回路10は、図2に示したように、第1スイッチSW1と第1コンデンサC1との間に第1充電電流生成回路13が介在し、第2スイッチSW2と第2コンデンサC2との間に第2充電電流生成回路14が介在するので、第1スイッチSW1と第2スイッチSW2が同時にオン状態になったとしても、従来のパルス幅変調回路1のように第1コンデンサC1と第2コンデンサC2が同一の充電電流生成回路に並列に接続されることはない。

【0106】

すなわち、本実施形態に係るパルス幅変調回路10では、第1コンデンサC1は、第2スイッチSW2のオン・オフ動作に関係なく、第1スイッチSW1がオンになると、第1充電電流生成回路13に接続されて当該第1充電電流生成回路13からの充電電流によって充電され、第2コンデンサC2は、第1スイッチSW1のオン・オフ動作に関係なく、第2スイッチSW2がオンになると、第2充電電流生成回路14に接続されて当該第2充電電流生成回路14からの充電電流によって充電される。

【0107】

図7は、本実施形態に係るパルス幅変調回路10において、第1制御信号φ1のハイレベルと第2制御信号φ2のハイレベルが重複したときのパルス幅変調動作を示すタイムチャートである。

【0108】

図7の第1制御信号φ1と第2制御信号φ2の波形は図6の第1制御信号φ1と第2制御信号φ2の波形と同一である。

【0109】

第1期間T1において、第1制御信号φ1がハイレベルに立ち上ってから第2制御信号φ1がハイレベルに立ち上る直前までの期間は、第1コンデンサC1に第1充電電流生成回路13が接続され、第1コンデンサC1は当該第1充電電流生成回路13から出力される充電電流(Ic+Δi)によって充電されるので、第1コンデンサC1の両端電圧はほぼ直線的に上昇する。また、第2制御信号φ2がハイレベルに立ち上っても、第1コンデンサC1には第2コンデンサC2が並列に接続されることはないので、第1コンデンサC1の両端電圧は第1制御信号φ1の立下がりタイミング、すわなち、第1期間T1の終了まで上昇することになる。

【0110】

従って、第2期間T2においては、第1コンデンサC1に第1放電用定電流回路15が接続され、第1コンデンサC1は当該第1放電用定電流回路15から出力される定電流Idによって放電される。

【0111】

一方、第2コンデンサC2は、第1期間T1の終了間際の第2制御信号φ2がハイレベルに立ち上るタイミングから次の立下りタイミングまでの期間、第2充電電流生成回路14が接続され、当該第2充電電流生成回路14から出力される充電電流(Ic+Δi)によって充電されるので、第2コンデンサC2の両端電圧もほぼ直線的に上昇する。また、その期間中には第1制御信号φ1がハイレベルに立ち上ることはないので、第2コンデンサC2の両端電圧は第2制御信号φ2が立ち下がるタイミングまで上昇し、その電圧が第2期間T2の終了まで保持される。そして、第3期間T3の開始間際に第2コンデンサC2に第2放電用定電流回路16が接続され、第2コンデンサC2は当該第2放電用定電流回路16から出力される定電流Idによって放電される。

【0112】

上記のように、第1コンデンサC1の充放電動作と第2コンデンサC2の充放電動作は互いに独立した動作となるので、両コンデンサC1,C2の充電動作と放電動作とにアンバランスが生じることはなく、図7(e)〜(g)に示すように、PWM変調信号PWMoutの波形は正常な波形となる。

【0113】

従って、本実施形態に係るパルス幅変調回路10では、従来のパルス幅変調回路1のようにデッドタイム生成回路を設ける必要はないので、その分、回路の簡素化、回路スペースを削減化及び部品コストの低減化を図ることができる。

【0114】

もちろん、この発明の範囲は上述した実施の形態に限定されるものではなく、上記実施形態に示した回路構成は一例であり、同等の機能を有するものであれば、種々の回路を適用することができる。例えば、上記した実施形態では、第1及び第2コンデンサC1,C2を一旦プラス方向に充電し、その後マイナス方向に放電するようにしたが、これに代えて、第1及び第2コンデンサC1,C2を一旦マイナス方向に充電し、その後プラス方向に放電するようにして、パルス幅変調信号PWMoutを生成するようにしてもよい。

【0115】

また、第1ないし第4スイッチSW1〜SW4は、バイポーラトランジスタに限られず、FETなどの他の種類の半導体スイッチング素子を使用することができる。

【0116】

また、第1コンデンサC1と第1パルス生成回路17との間、または第2コンデンサC2と第2パルス生成回路18との間には、例えばオペアンプからなる比較回路が設けられてもよい。この比較回路により、第1コンデンサC1の一端における電圧が基準電圧に達することを正確に検出することができる。

【符号の説明】

【0117】

1,10 パルス幅変調回路

2 スイッチング回路

3 ローパスフィルタ回路

4 第1電源

5 第2電源

11 クロック生成回路

12 差動増幅回路

13 第1充電電流生成回路

14 第2充電電流生成回路

15 第1放電用定電流回路

16 第2放電用定電流回路

17 第1パルス生成回路

18 第2パルス生成回路

19 パルス合成回路

AU オーディオ発生源

C1 第1コンデンサ

C2 第2コンデンサ

eS オーディオ信号

SW1 第1スイッチ

SW2 第2スイッチ

SW3 第3スイッチ

SW4 第4スイッチ

T1 第1期間

T2 第2期間

T3 第3期間

T4 第3期間

φ1 第1制御信号

φ2 第2制御信号

φ3 第3制御信号

φ4 第4制御信号

【特許請求の範囲】

【請求項1】

所定の周期を有する基準クロックを生成し、その基準クロックのオン期間に充電動作を行なわせるための第1の制御信号と前記基準クロックのオフ期間に充電動作を行なわせるための第2の制御信号とを生成する充電制御信号生成部と、

前記第1の制御信号により充電動作が行なわれたオン期間に続くオフ期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第3の制御信号と前記第2の制御信号により充電動作が行なわれたオフ期間に続くオン期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第4の制御信号とを生成する放電制御信号生成部と、

前記第1及び第3の制御信号に基づき、入力信号のレベルに基づいて生成される充電電流により第1のコンデンサを充電する充電動作とその第1のコンデンサの蓄積電荷を一定の放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第1のコンデンサが放電開始時のレベルから前記所定の基準レベルに変化するまでの放電時間をパルス幅とする第1のパルス信号を生成する第1のパルス信号生成部と、

前記第2及び第4の制御信号に基づき、前記充電電流により第2のコンデンサを充電する充電動作とその第2のコンデンサの蓄積電荷を前記放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第2のコンデンサが放電開始時のレベルから前記基準レベルに変化するまでの放電時間をパルス幅とする第2のパルス信号を生成する第2のパルス信号生成部と、

前記第1のパルス信号生成部で生成される第1のパルス信号と前記第2のパルス信号生成部で生成される第2のパルス信号とを合成し、前記所定の周期を有し、各パルスのパルス幅が前記入力信号のレベルに応じて変化するパルス幅変調信号を出力するパルス信号合成部と、

を備えたパルス幅変調回路であって、

前記第1のパルス信号生成部は、

前記入力信号の電圧を増幅する差動増幅回路と、

前記差動増幅回路の一対の電源端子間に接続され、前記第1のコンデンサの充放電動作を制御する第1の制御回路と、

前記第1のコンデンサの両端電圧に基づいて前記第1のパルス信号を生成する第1のパルス信号生成回路と、を備え、

前記第1の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第1の充電電流生成回路とこの第1の充電電流生成回路で生成される充電電流による前記第1のコンデンサの充電動作を前記第1の制御信号により制御する第1のスイッチ回路との第1の直列回路と、前記放電電流として一定の電流を生成する第1の定電流回路とこの第1の定電流回路で生成される放電電流による前記第1のコンデンサの放電動作を前記第3の制御信号により制御する第2のスイッチ回路との第2の直列回路とを直列に接続し、その接続点に前記第1のコンデンサを接続した回路で構成され、

前記第2のパルス信号生成部は、

前記差動増幅回路を前記第1のパルス信号生成部と共有し、

前記差動増幅回路の一対の電源端子間に接続され、前記第2のコンデンサの充放電動作を制御する第2の制御回路と、

前記第2のコンデンサの両端電圧に基づいて前記第2のパルス信号を生成する第2のパルス信号生成回路と、を備え、

前記第2の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第2の充電電流生成回路とこの第2の充電電流生成回路で生成される充電電流による前記第2のコンデンサの充電動作を前記第2の制御信号により制御する第3のスイッチ回路との第3の直列回路と、前記放電電流として一定の電流を生成する第2の定電流回路とこの第2の定電流回路で生成される放電電流による前記第2のコンデンサの放電動作を前記第4の制御信号により制御する第4のスイッチ回路との第4の直列回路とを直列に接続し、その接続点に前記第2のコンデンサを接続した回路で構成されている、ことを特徴とする、パルス幅変調回路。

【請求項2】

前記差動増幅回路は、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路が接続された回路で構成され、

前記第1の定電流回路と前記第2の定電流回路は、前記定電流回路と同一の回路構成を有し、前記定電圧源を当該定電流回路と共用している、

ことを特徴とする、請求項1に記載のパルス幅変調回路。

【請求項3】

前記第1ないし第4のスイッチ回路は、半導体スイッチング素子からなり、

前記第1及び第2の充電電流生成回路は、1個のトランジスタを用いた電圧−電流変換回路で構成されている、

ことを特徴とする、請求項2に記載のパルス幅変調回路。

【請求項4】

請求項1ないし3に記載のパルス幅変調回路と、

所定の電源電圧を出力する電圧源と、

前記パルス幅変調回路から出力されるパルス幅変調信号に基づいて、前記電圧源から供給される所定の電源電圧をスイッチングするスイッチング回路と、

を備えたことを特徴とする、スイッチングアンプ。

【請求項1】

所定の周期を有する基準クロックを生成し、その基準クロックのオン期間に充電動作を行なわせるための第1の制御信号と前記基準クロックのオフ期間に充電動作を行なわせるための第2の制御信号とを生成する充電制御信号生成部と、

前記第1の制御信号により充電動作が行なわれたオン期間に続くオフ期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第3の制御信号と前記第2の制御信号により充電動作が行なわれたオフ期間に続くオン期間にその充電動作で蓄積された電荷の放電動作を行なわせるための第4の制御信号とを生成する放電制御信号生成部と、

前記第1及び第3の制御信号に基づき、入力信号のレベルに基づいて生成される充電電流により第1のコンデンサを充電する充電動作とその第1のコンデンサの蓄積電荷を一定の放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第1のコンデンサが放電開始時のレベルから前記所定の基準レベルに変化するまでの放電時間をパルス幅とする第1のパルス信号を生成する第1のパルス信号生成部と、

前記第2及び第4の制御信号に基づき、前記充電電流により第2のコンデンサを充電する充電動作とその第2のコンデンサの蓄積電荷を前記放電電流で放電する放電動作とを前記基準クロックの半周期毎に交互に行ない、前記放電動作をしている各期間に前記第2のコンデンサが放電開始時のレベルから前記基準レベルに変化するまでの放電時間をパルス幅とする第2のパルス信号を生成する第2のパルス信号生成部と、

前記第1のパルス信号生成部で生成される第1のパルス信号と前記第2のパルス信号生成部で生成される第2のパルス信号とを合成し、前記所定の周期を有し、各パルスのパルス幅が前記入力信号のレベルに応じて変化するパルス幅変調信号を出力するパルス信号合成部と、

を備えたパルス幅変調回路であって、

前記第1のパルス信号生成部は、

前記入力信号の電圧を増幅する差動増幅回路と、

前記差動増幅回路の一対の電源端子間に接続され、前記第1のコンデンサの充放電動作を制御する第1の制御回路と、

前記第1のコンデンサの両端電圧に基づいて前記第1のパルス信号を生成する第1のパルス信号生成回路と、を備え、

前記第1の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第1の充電電流生成回路とこの第1の充電電流生成回路で生成される充電電流による前記第1のコンデンサの充電動作を前記第1の制御信号により制御する第1のスイッチ回路との第1の直列回路と、前記放電電流として一定の電流を生成する第1の定電流回路とこの第1の定電流回路で生成される放電電流による前記第1のコンデンサの放電動作を前記第3の制御信号により制御する第2のスイッチ回路との第2の直列回路とを直列に接続し、その接続点に前記第1のコンデンサを接続した回路で構成され、

前記第2のパルス信号生成部は、

前記差動増幅回路を前記第1のパルス信号生成部と共有し、

前記差動増幅回路の一対の電源端子間に接続され、前記第2のコンデンサの充放電動作を制御する第2の制御回路と、

前記第2のコンデンサの両端電圧に基づいて前記第2のパルス信号を生成する第2のパルス信号生成回路と、を備え、

前記第2の制御回路は、前記差動増幅回路から出力される電圧に応じた電流を前記充電電流として生成する第2の充電電流生成回路とこの第2の充電電流生成回路で生成される充電電流による前記第2のコンデンサの充電動作を前記第2の制御信号により制御する第3のスイッチ回路との第3の直列回路と、前記放電電流として一定の電流を生成する第2の定電流回路とこの第2の定電流回路で生成される放電電流による前記第2のコンデンサの放電動作を前記第4の制御信号により制御する第4のスイッチ回路との第4の直列回路とを直列に接続し、その接続点に前記第2のコンデンサを接続した回路で構成されている、ことを特徴とする、パルス幅変調回路。

【請求項2】

前記差動増幅回路は、2つのトランジスタのエミッタを相互に接続し、その接続点にベース・エミッタ間に定電圧源が接続されたトランジスタ回路からなる定電流回路が接続された回路で構成され、

前記第1の定電流回路と前記第2の定電流回路は、前記定電流回路と同一の回路構成を有し、前記定電圧源を当該定電流回路と共用している、

ことを特徴とする、請求項1に記載のパルス幅変調回路。

【請求項3】

前記第1ないし第4のスイッチ回路は、半導体スイッチング素子からなり、

前記第1及び第2の充電電流生成回路は、1個のトランジスタを用いた電圧−電流変換回路で構成されている、

ことを特徴とする、請求項2に記載のパルス幅変調回路。

【請求項4】

請求項1ないし3に記載のパルス幅変調回路と、

所定の電源電圧を出力する電圧源と、

前記パルス幅変調回路から出力されるパルス幅変調信号に基づいて、前記電圧源から供給される所定の電源電圧をスイッチングするスイッチング回路と、

を備えたことを特徴とする、スイッチングアンプ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−273326(P2010−273326A)

【公開日】平成22年12月2日(2010.12.2)

【国際特許分類】

【出願番号】特願2010−60434(P2010−60434)

【出願日】平成22年3月17日(2010.3.17)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

【公開日】平成22年12月2日(2010.12.2)

【国際特許分類】

【出願日】平成22年3月17日(2010.3.17)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

[ Back to top ]