パワースイッチング素子の駆動回路

【課題】電圧制御形のパワースイッチング素子Swの電力損失の抑制とサージの抑制との両立を図ることが困難なこと。

【解決手段】パワースイッチング素子Swのゲートは、充電用抵抗体34、並びに充電用バイポーラトランジスタ32及び充電用MOSトランジスタ40を介して、電源30の正極に接続されている。パワースイッチング素子Swをオン状態へと切り替える際には、まず充電用バイポーラトランジスタ32をオン操作することで、パワースイッチング素子Swのゲートに正の電荷を充電する。そして、パワースイッチング素子Swがオン状態となった後に、充電用MOSトランジスタ40をオン操作する。

【解決手段】パワースイッチング素子Swのゲートは、充電用抵抗体34、並びに充電用バイポーラトランジスタ32及び充電用MOSトランジスタ40を介して、電源30の正極に接続されている。パワースイッチング素子Swをオン状態へと切り替える際には、まず充電用バイポーラトランジスタ32をオン操作することで、パワースイッチング素子Swのゲートに正の電荷を充電する。そして、パワースイッチング素子Swがオン状態となった後に、充電用MOSトランジスタ40をオン操作する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電圧制御形のパワースイッチング素子を駆動するパワースイッチング素子の駆動回路に関する。

【背景技術】

【0002】

3相モータの各相を直流電源の正極側及び負極側に接続する一対のパワースイッチング素子の直列接続体を備えるインバータが周知である。ここで、一対のパワースイッチング素子のそれぞれには、フリーホイールダイオードが逆並列に接続されている。これら一対のパワースイッチング素子のうちの一方に接続されるフリーホイールダイオードに順方向電流が流れる状況下、他方のパワースイッチング素子をオン操作すると、フリーホイールダイオードには、そのカソード側からアノード側へとリカバリ電流が流れる。リカバリ電流は、増加した後、減少しやがてゼロとなるものであるが、減少を開始するに際して、フリーホイールダイオードの両端にサージ電圧が重畳する。そして、このサージ電圧は、パワースイッチング素子の入出力端子間の電圧降下量が大きいほど小さくなる。

【0003】

そこで従来、例えば下記特許文献1に見られるように、パワースイッチング素子としての絶縁ゲートバイポーラトランジスタ(IGBT)のゲートに正の電荷を充電するための高電位側のバイポーラトランジスタ及びIGBTのゲートから正の電荷を放電するための低電位側のバイポーラトランジスタの直列接続体を備え、これら一対のバイポーラトランジスタのベースに、CR回路を介してIGBTの駆動信号を印加するものも提案されている。これにより、上記一対のバイポーラトランジスタをエミッタフォロワとして用いることで、エミッタの出力電圧をCR回路の時定数に応じて調節することができる。これにより、ゲートの充電速度を調節することができ、ひいてはサージを好適に抑制することができる。

【0004】

なお、この種の駆動回路としては、他にも例えば下記特許文献2に記載されているものがある。

【特許文献1】特開平5−161343号公報

【特許文献1】特開2000−295838号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、高電位側のバイポーラトランジスタの出力端子(エミッタ)の電圧は、その入力端子(コレクタ)の電圧に対して低下する。このため、例えばMOS型電界効果トランジスタを用いる場合と比較して、IGBTのゲートに印加可能な電圧が小さくなる。そして、ゲートに印加可能な電圧が小さい場合には、IGBTがオン状態である際のIGBTの入力端子及び出力端子間の電圧降下量が増大し、ひいては電力損失が大きくなる。このため、IGBTとして、熱的に十分に余裕のある素子を選択することが要求される。更に、バイポーラトランジスタの出力電圧は、温度に応じて変化し易いため、出力電圧が温度に応じて低下する場合には、IGBTの損失が更に大きくなり、ひいてはIGBTとして更に熱的に余裕がある素子を選択することが要求されることとなる。

【0006】

ここで、IGBTのゲートをゲート抵抗を介して高電位側のバイポーラトランジスタに接続する代わりに、ゲート抵抗を介してMOS型電界効果トランジスタに接続する場合には、IGBTのゲートに印加可能な電圧を増大させることはできるものの、スイッチング状態の切り替えに伴うサージの抑制とスイッチング状態の切り替え時の電力損失の低減との両立を図ることが困難となることが懸念される。すなわち、MOS型の電界効果トランジスタとIGBTのゲートとの間のゲート抵抗を増大させると、スイッチング状態の切替速度が小さくなるため、サージを抑制することはできるものの、切り替え時の電力損失が増大する。これに対し、MOS型の電界効果トランジスタとIGBTのゲートとの間のゲート抵抗を低減すると、スイッチング状態の切替速度が大きくなるため、切り替え時の電力損失は低減できるものの、サージが増大する。

【0007】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のパワースイッチング素子の電力損失の抑制とサージの抑制との好適な両立を図ることのできるパワースイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0008】

以下、上記課題を解決するための手段、及びその作用効果について記載する。

【0009】

請求項1記載の発明は、電圧制御形のパワースイッチング素子を駆動する駆動回路において、前記パワースイッチング素子の導通制御端子に正の電荷を充電するための電源と前記導通制御端子との間を電気的に開閉する充電用開閉手段として、電流制御形のスイッチング素子と、電圧制御形のスイッチング素子とを備えることを特徴とする。

【0010】

上記発明では、電流制御形のスイッチング素子を備えることで、電圧制御形のスイッチング素子のみを用いる場合と比較して、パワースイッチング素子の導通制御端子の充電態様の設定の自由度が増し、ひいては、サージを好適に抑制することができる設定が可能となる。更に、電圧制御形のスイッチング素子を備えることで、電流制御形のスイッチング素子のみを用いる場合と比較して、パワースイッチング素子の導通制御端子の電圧を上昇させることもできる。このため、上記発明は、電圧制御形のパワースイッチング素子の電力損失の抑制とサージの抑制との好適な両立を図ることができる。

【0011】

請求項2記載の発明は、請求項1記載の発明において、前記電流制御形のスイッチング素子は、NPN型のバイポーラトランジスタであることを特徴とする。

【0012】

請求項3記載の発明は、請求項2記載の発明において、前記導通制御端子への前記電荷の充電期間のうちの充電開始から所定期間内における前記NPN型バイポーラトランジスタの出力電圧の上昇速度を緩和する緩和手段を備えることを特徴とする。

【0013】

パワースイッチング素子にダイオードが直列接続される場合、導通制御端子の充電期間の中間において、ダイオードにリカバリ電流が流れ、これによりサージが生じる。一方、導通制御端子の充電速度を抑制することで、サージを抑制することができることが知られている。上記発明では、この点に鑑み、緩和手段を備えることで、サージを好適に抑制することができる。

【0014】

請求項4記載の発明は、請求項3記載の発明において、前記緩和手段は、前記パワースイッチング素子の操作信号の変化を遅延させる遅延回路を備え、該遅延回路の出力電圧を前記NPN型バイポーラトランジスタのベースに印加する手段であることを特徴とする。

【0015】

上記発明では、遅延回路を備えることで、緩和手段を適切に構成することができる。

【0016】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記パワースイッチング素子の導通制御端子に正の電荷を充電すべく前記充電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧(前記パワースイッチング素子をオン状態とするための閾値電圧)以上となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする。

【0017】

上記発明では、電圧制御形のスイッチング素子を、パワースイッチング素子がオン状態となるタイミング以降において導通制御端子に印加する電圧を確保する用途として用いることができる。

【0018】

請求項6記載の発明は、請求項2〜5のいずれか1項に記載の発明において、前記パワースイッチング素子の導通制御端子から前記正の電荷を放電させるべく前記導通制御端子と前記正の電荷の放電経路の下流側との間を電気的に開閉する放電用開閉手段として、PNP型のバイポーラトランジスタを備えることを特徴とする。

【0019】

上記発明では、充電用開閉手段と放電用開閉手段とがそれぞれ、NPN型バイポーラトランジスタとPNP型バイポーラトランジスタとを備えるために、これらの一方に対してオン状態に切り替える指令を与えて且つ他方に対してオフ状態に切り替える指令を与える際、デッドタイムを生成する処理を削除することができる。

【0020】

請求項7記載の発明は、請求項6記載の発明において、前記放電用開閉手段として、電圧制御形のスイッチング素子を更に備えることを特徴とする。

【0021】

請求項8記載の発明は、請求項7記載の発明において、前記パワースイッチング素子の導通制御端子から正の電荷を放電すべく前記放電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧(前記パワースイッチング素子をオフ状態とするための閾値電圧)以下となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする。

【0022】

請求項9記載の発明は、請求項1〜8のいずれか1項に記載の発明において、前記パワースイッチング素子には、ダイオードが直列接続されてなることを特徴とする。

【発明を実施するための最良の形態】

【0023】

(第1の実施形態)

以下、本発明にかかるパワースイッチング素子の駆動回路をハイブリッド車の電力変換回路の駆動回路に適用した一実施形態について、図面を参照しつつ説明する。

【0024】

図1に、本実施形態のシステム構成を示す。図示されるように、車載回転機としてのモータジェネレータ10は、インバータIVを介して高圧バッテリ12に接続されている。インバータIVは、高電位側のパワースイッチング素子Swp及び低電位側のパワースイッチング素子Swnの直列接続体が3つ並列接続されて構成されている。そして、これら各直列接続体の接続点が、モータジェネレータ10の各相にそれぞれ接続されている。これら高電位側のパワースイッチング素子Swp及び低電位側のパワースイッチング素子Swnのそれぞれの入出力端子間(コレクタ及びエミッタ間)には、高電位側のフリーホイールダイオードFDp及び低電位側のフリーホイールダイオードFDnのカソード及びアノードが接続されている。

【0025】

上記インバータIVを構成するパワースイッチング素子Swp,Swnの導通制御端子(ゲート)には、いずれも駆動回路DCが接続されている。これにより、パワースイッチング素子Swp,Swnは、駆動回路DC及びインターフェース14を介して、低圧バッテリ16を電源とするマイクロコンピュータ(マイコン20)にて駆動される。ここで、インターフェース14は、インバータIVやコンバータCVを備える高圧システムと、マイコン20を備える低圧システムとを絶縁するフォトカプラ等の絶縁手段を備えて構成されるものである。マイコン20は、図示しない各種センサの検出値等に基づき、インバータIVのU相、V相、及びW相のそれぞれについての、パワースイッチング素子Swpを操作する操作信号gup,gvp,gwpと、パワースイッチング素子Swnを操作する操作信号gun,gvn,gwnとを生成し出力する。これにより、スイッチング素子Swp,Swnは、駆動回路DCを介してマイコン20により操作される。なお、各相の高電位側の操作信号gup,gvp,gwpのそれぞれと、低電位側の操作信号gun,gvn,gwnのそれぞれとは、高電位側のスイッチング素子Swpと低電位側のスイッチング素子Swnとを互いに相補的に駆動するものとしてもよい。すなわち、いずれか一方の操作信号がオン状態とするための信号である期間、他方の操作信号がオフ状態とするための信号となるようにしてもよい。

【0026】

上記パワースイッチング素子Swp,Swnは、いずれも、入力端子及び出力端子が一義に定義されており、出力端子から入力端子への電流の流通を阻止するスイッチング素子である。詳しくは、これらは、絶縁ゲートバイポーラトランジスタ(IGBT)にて構成されている。このため、高電位側のパワースイッチング素子Swpに電流が流れ得る状況下にあっては、これをオフ状態とすることで、低電位側のパワースイッチング素子Swnに電流が流れず、これに逆並列に接続されるフリーホイールダイオードFDnに電流が流れる。また、低電位側のパワースイッチング素子Swnに電流が流れ得る状況下にあっては、これをオフ状態とすることで、高電位側のパワースイッチング素子Swpに電流が流れず、これに逆並列に接続されるフリーホイールダイオードFDpに電流が流れる。そしてこの場合、上記パワースイッチング素子Swp(Swn)が再度オン操作される際には、フリーホイールダイオードFDn(FDp)にリカバリ電流が流れる。そして、このリカバリ電流は、パワースイッチング素子Swp,Swnをオン操作する際のサージ電圧の原因となる。以下、これについて図2を用いて更に説明する。

【0027】

図2には、高電位側のパワースイッチング素子Swpに電流が流れ得る状況を例示している。こうした状況下、図2(a)に示すように、高電位側のパワースイッチング素子Swpがオフ状態であるなら、コレクタ電流icはゼロであり、低電位側のフリーホイールダイオードFDnに順方向の電流idが流れる。この際、フリーホイールダイオードFDnの両端の電圧Vfdは略ゼロであるため、高電位側のパワースイッチング素子Swpのエミッタ及びコレクタ間の電圧Vceは、高圧バッテリ12の電圧Vdc程度となっている。

【0028】

ここで、時刻t1において、高電位側のパワースイッチング素子Swpがオン操作されると、図2(b)に示されるように、コレクタ電流icが漸増する。これに伴いフリーホイールダイオードFDnを流れる電流idは、漸減してやがてゼロとなる。このとき、コレクタ及びエミッタ間の電圧Vceは、コレクタ電流icの電流変化率とインバータIVの配線に存在するインダクタ成分(図中、配線インダクタLpと模式的に表記)の積を電源電圧Vdcから減算した値となる。

【0029】

フリーホイールダイオードFDnを流れる電流がゼロとなると、フリーホイールダイオードFDnのキャリア蓄積効果により、逆方向の電流であるリカバリ電流が流れ始める。このとき、高電位側のスイッチング素子Swpのコレクタ及びエミッタ間には、モータジェネレータ10との間で授受される電流(負荷電流)に加えて、リカバリ電流が流れることとなる。そしてその後、フリーホイールダイオードFDnの接合部のキャリアが減少し、リカバリ電流は漸増から漸減に転じ、やがてゼロとなる。ここで、リカバリ電流が漸増から漸減に転じる際には、リカバリ電流の電流変化率とインバータIVの配線に存在するインダクタ成分によって生じる電圧成分によってサージ電圧が生じる。

【0030】

図3に、上記サージ電圧の抑制効果を有する本実施形態にかかる駆動回路DCの回路構成を示す。なお、以下では、パワースイッチング素子Swp,Swnをパワースイッチング素子Swにて総括表記し、フリーホイールダイオードFDp,FDnをフリーホイールダイオードFDにて総括表記する。また、上記操作信号gup,gvp,gwp,gun,gvn,gwnを、操作信号gにて総括表記する。

【0031】

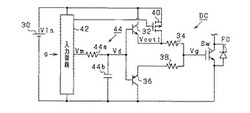

図示されるように、駆動回路DCにおいては、電圧Vinの電源30の正極に、NPN型のバイポーラトランジスタである充電用バイポーラトランジスタ32のコレクタが接続され、そのエミッタには、充電用抵抗体34を介してパワースイッチング素子Swのゲートが接続されている。また、電源30の負極に、PNP型のバイポーラトランジスタである放電用バイポーラトランジスタ36のコレクタが接続され、そのエミッタには、放電用抵抗体38を介してパワースイッチング素子Swのゲートが接続されている。更に、上記充電用バイポーラトランジスタ32のコレクタ及びエミッタ間には、PチャネルMOS型電界効果トランジスタからなる充電用MOSトランジスタ40が並列接続されている。

【0032】

一方、入力回路42は、上記操作信号gを入力とし、これに応じて充電用バイポーラトランジスタ32や、放電用バイポーラトランジスタ36、充電用MOSトランジスタ40を操作する回路である。ここで、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36との操作は、入力回路42は、操作信号gを所定に電圧変換した信号を遅延回路44に出力することで行われる。すなわち、入力回路42は、電源30の電圧Vinが印加される一対のバイポーラトランジスタ又はMOS型電界効果トランジスタ等からなるバッファ回路を備え、バッファ回路を介して操作信号gに応じた信号を遅延回路44に出力する。

【0033】

上記遅延回路44は、線形素子としての抵抗体44aとコンデンサ44bとを備えるCR回路である。抵抗体44aとコンデンサ44bとの接続点の電圧は、遅延回路44の出力信号(遅延電圧Vd)として、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36とのそれぞれのベースに印加される。この遅延回路44は、主に、充電用バイポーラトランジスタ32のエミッタの出力電圧Vout1の上昇速度を、操作信号gの上昇速度に対して緩和するために設けられたものである。すなわち、充電用バイポーラトランジスタ32は、エミッタフォロワ回路を構成しているため、エミッタからの出力電圧Vout1は、ベースに印加される電圧(遅延電圧Vd)となる(より正確には、これからベース及びエミッタ間の電圧降下量Vbeだけ低い値となる)。

【0034】

上記入力回路42は、更に、操作信号gによって、パワースイッチング素子Swをオフ状態からオン状態へと切り替える旨指示されてから所定期間経過することで充電用MOSトランジスタ40をオン状態とする機能を有する。これにより、パワースイッチング素子Swのゲートの充電終了後には、ゲートの電圧を電源30の電圧Vinに保持することができる。

【0035】

図4に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。詳しくは、図4(a)に、操作信号gの推移を示し、図4(b)に、入力回路42の出力信号の電圧(駆動電圧Vm)の推移を示し、図4(c)に、遅延回路44の出力信号の電圧(遅延電圧Vd)の推移を示し、図4(d)に、充電用バイポーラトランジスタ32の出力電圧Vout1の推移を示す。更に、図4(e)に、パワースイッチング素子Swのゲートの充電電流の推移を示し、図4(f)に、パワースイッチング素子Swのゲート電圧Vgの推移を示し、図4(g)に、充電用MOSトランジスタ32の状態の推移を示す。

【0036】

図示されるように、操作信号gが立ち上がることで駆動電圧Vmも立ち上がるものの、遅延電圧Vdの上昇速度は、駆動電圧Vmの上昇速度よりも緩やかとなる。このため、出力電圧Vout1の上昇速度も、操作信号gや駆動電圧Vmの立ち上がり速度と比較して緩やかなものとなる。したがって、ゲート電圧Vgの上昇速度は、上記遅延回路44を備えない場合と比較して緩やかなものとなる。

【0037】

上記出力電圧Vout1は緩やかに上昇した後、一定値となるものである。本実施形態では、パワースイッチング素子Swのオン状態への切り替わりに起因してこれに直列接続されるフリーホイールダイオードFDにリカバリ電流が流れる期間が、緩やかに上昇する期間に包含されるように、予め遅延回路44の時定数を設定する。これにより、リカバリ電流に起因するサージの抑制を図ることができる。

【0038】

一方、ゲートの充電電流は、出力電圧Vout1とゲート電圧Vgとの差圧に応じて流れるものである。ただし、この充電電流は、充電用抵抗体34によって制御可能である。このため、充電用抵抗体34を比較的低抵抗とすることで、出力電圧Vout1が略定常値となった後のゲートの充電速度を高速化することができる。このため、パワースイッチング素子Swがオフ状態からオン状態へと切り替わるまでに要する時間を短縮することができ、ひいてはスイッチング状態の切り替えに伴う電力損失を低減することができる。

【0039】

上記操作信号gによってパワースイッチング素子Swをオン状態に切り替える旨指示されてから所定期間T経過すると、上記充電用MOSトランジスタ40をオン操作とする。ここで、所定期間Tは、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電が略完了するタイミングに設定される。これにより、パワースイッチング素子Swがオン状態とされた後には、ゲート電圧Vgを電源30の電圧Vinに持ち上げ保持することができる。

【0040】

このように、本実施形態では、遅延回路44の出力電圧をエミッタフォロワを介してパワースイッチング素子Swのゲートに印加するようにしたことで、遅延回路44の時定数によって、サージを抑制すべくゲートの充電処理態様を調節することができる。このようにバイポーラトランジスタを用いてサージ対策を施すことで、あたかも充電用抵抗体34の抵抗値をゲートの充電期間において可変とするかのような充電制御が可能となる。このため、充電用抵抗体34のみによってサージ対策をする場合と比較して、スイッチング状態の切り替えに伴う電力損失の増大を抑制しつつもサージ対策をより好適に行うことができる。

【0041】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0042】

(1)パワースイッチング素子Swの導通制御端子(ゲート)に正の電荷を充電するための電源30とゲートとの間を電気的に開閉する充電用開閉手段として、充電用バイポーラトランジスタ32と、充電用MOSトランジスタ40とを備えた。これにより、パワースイッチング素子Swの電力損失の抑制とサージの抑制との好適な両立を図ることができる。

【0043】

(2)充電用バイポーラトランジスタ32をエミッタフォロワとして用いて且つ、そのベースに遅延回路44の出力電圧(遅延電圧Vd)を印加した。これにより、パワースイッチング素子Swのゲートの充電期間初期の充電速度を緩和することができ、ひいてはサージを好適に抑制することができる。

【0044】

(3)充電用バイポーラトランジスタ32をオン状態とすることでパワースイッチング素子Swのゲート電圧がパワースイッチング素子Swをオン状態とするための閾値電圧以上となるタイミング以降において充電用MOSトランジスタ40をオン状態とした。これにより、サージ対策を抑制する処理を確実に行うことや、充電用MOSトランジスタ40と放電用バイポーラトランジスタ36との間に貫通電流が流れることを回避することができる。

【0045】

(4)パワースイッチング素子Swのゲートから正の電荷を放電させるためのスイッチング素子として、放電用バイポーラトランジスタ36を備えた。これにより、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36との双方が同時にオン状態となる貫通状態が生じることを制御上簡易に回避しつつ、操作信号gに基づきパワースイッチング素子Swのゲートの充放電処理を行うことができる。

【0046】

(第2の実施形態)

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0047】

図5に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図5において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0048】

本実施形態では、充電用バイポーラトランジスタ32の出力電圧Vout1をモニタし、これが閾値電圧以上となることで、充電用MOSトランジスタ40をオン操作する。そして、この閾値電圧を、電源30の電圧Vinよりも充電用バイポーラトランジスタ32のベース及びエミッタ間の電圧降下量Vbe程度低い値に設定する。これにより、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電処理中に、充電用MOSトランジスタ40をオン操作することができる。

【0049】

(第3の実施形態)

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0050】

図6に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図6において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0051】

本実施形態では、パワースイッチング素子Swのゲート電圧Vgをモニタし、これが閾値電圧以上となることで、充電用MOSトランジスタ40をオン操作する。そして、この閾値電圧を、電源30の電圧Vinよりも充電用バイポーラトランジスタ32のベース及びエミッタ間の電圧降下量Vbe程度低い値に設定する。これによっても、先の第1の実施形態のように、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電の完了後に、充電用MOSトランジスタ40をオン操作することができる。

【0052】

(第4の実施形態)

以下、第4の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0053】

図7に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。なお、図7(a)〜図7(g)は、先の図4(a)〜図4(g)に対応している。

【0054】

図示されるように、本実施形態によっても、上記操作信号gによってパワースイッチング素子Swをオン状態に切り替える旨指示されてから所定期間T経過すると、上記充電用MOSトランジスタ40をオン操作する。ただし本実施形態では、所定期間Tを、パワースイッチング素子Swがオン状態への移行を開始するタイミング以降であって極力早期のタイミングに設定する。詳しくは、パワースイッチング素子Swのゲート電圧がミラー期間の電圧となるタイミングであって且つパワースイッチング素子Swに直列接続されるフリーホイールダイオードFDのリカバリ電流がゼロとなるタイミングに設定される。これにより、リカバリ電流がゼロとなった後には、パワースイッチング素子Swのゲート電圧を電源30の電圧Vinまで迅速に持ち上げることができる。

【0055】

(第5の実施形態)

以下、第5の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0056】

図8に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図8において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0057】

図示されるように、本実施形態では、放電用バイポーラトランジスタ36のコレクタ及びエミッタ間に、NチャネルのMOS型電界効果トランジスタとしての放電用MOSトランジスタ50が並列接続されている。

【0058】

図9に、本実施形態にかかるパワースイッチング素子Swのオフ状態への切り替え処理態様を示す。詳しくは、図9(a)に、操作信号gの推移を示し、図9(b)に、放電用バイポーラトランジスタ36のエミッタ電圧(出力電圧Vout1)の推移を示し、図9(c)に、パワースイッチング素子Swのゲート電圧の推移を示し、図9(d)に、放電用MOSトランジスタ50の状態の推移を示す。

【0059】

図示されるように、本実施形態では、操作信号gによって、パワースイッチング素子Swをオフ状態に切り替える旨指示されると、まず放電用バイポーラトランジスタ36がオン操作されることで、パワースイッチング素子Swのゲートから正の電荷を放電させる。そして、上記指示されるタイミングから所定期間Tが経過することで、放電用MOSトランジスタ50がオン操作されることで、パワースイッチング素子Swのゲート電圧Vgを、電源30の負極電位まで引き下げて保持する。ここで、所定期間Tは、放電用バイポーラトランジスタ36によるパワースイッチング素子Swのゲートの放電処理が完了するのに要する所要時間程度に設定される。

【0060】

(第6の実施形態)

以下、第6の実施形態について、先の第5の実施形態との相違点を中心に図面を参照しつつ説明する。

【0061】

図10に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図10において、先の図8に示した部材に対応する部材については、便宜上同一の符号を付している。

【0062】

本実施形態では、放電用バイポーラトランジスタ36の出力電圧Vout2をモニタし、これが閾値電圧以下となることで、放電用MOSトランジスタ50をオン操作する。そして、この閾値電圧を、放電用バイポーラトランジスタ36のベース及びエミッタ間の電圧降下量Vbe程度に設定する。これにより、パワースイッチング素子Swのゲートの放電処理の途中で、放電用MOSトランジスタ50をオン操作することができる。

【0063】

(第7の実施形態)

以下、第7の実施形態について、先の第5の実施形態との相違点を中心に図面を参照しつつ説明する。

【0064】

図11に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図11において、先の図10に示した部材に対応する部材については、便宜上同一の符号を付している。

【0065】

本実施形態では、パワースイッチング素子Swのゲート電圧Vgをモニタし、これが閾値電圧以下となることで、放電用MOSトランジスタ50をオン操作する。そして、この閾値電圧を、放電用バイポーラトランジスタ36のベース及びエミッタ間の電圧降下量Vbe程度に設定する。これによっても、先の第5の実施形態のように、放電用バイポーラトランジスタ36によるパワースイッチング素子Swのゲートの放電の完了後に、放電用MOSトランジスタ50をオン操作することができる。

【0066】

(第8の実施形態)

以下、第8の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0067】

図12に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。なお、図12(a)〜図12(d)は、先の図9(a)〜図9(d)に対応している。

【0068】

図示されるように、本実施形態によっても、上記操作信号gによってパワースイッチング素子Swをオフ状態に切り替える旨指示されてから所定期間T経過すると、上記放電用MOSトランジスタ50をオン操作する。ただし本実施形態では、所定期間Tを、パワースイッチング素子Swがオフ状態への移行を開始するタイミング以降であって極力早期のタイミングに設定する。詳しくは、パワースイッチング素子Swのゲート電圧がミラー期間の電圧にある間のタイミングに設定する。これにより、パワースイッチング素子Swの放電速度を上昇させることができる。このため、遅延回路44を設けたことによるゲート電圧の低下速度の低下を、放電用抵抗体38との協働によって好適に補償することができる。更に、放電速度を所望に制御する自由度を向上させることもできるため、ゲート電圧の低下速度を所望に制御することも可能となる。

【0069】

(その他の実施形態)

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0070】

・先の第1の実施形態に対する第3の実施形態の変更点によって、先の第4の実施形態を変更してもよい。

【0071】

・先の第5の実施形態に対する第7の実施形態の変更点によって、先の第8の実施形態を変更してもよい。

【0072】

・遅延回路44としては、CR回路に限らない。例えば、抵抗体44aと並列に、コンデンサ44b側から入力回路42側に進む方向を順方向とするダイオードを備えてもよい。この場合、パワースイッチング素子Swをオフ状態に切り替えるに際して、放電用バイポーラトランジスタ36の出力電圧の低下速度を増大させることができる。また例えば、LCR回路であってもよい。

【0073】

・パワースイッチング素子Swのゲートへの正の電荷の充電初期における充電用バイポーラトランジスタ32の出力電圧Vout1の上昇速度を、操作信号gの論理反転速度に対して緩和する緩和手段としては、遅延回路に限らない。例えば、パワースイッチング素子Swの電力損失の低減とサージ電圧の抑制との優先度合いに基づき、充電用バイポーラトランジスタ32のベース電流を可変設定するものであってもよい。この場合であっても、充電用MOSトランジスタ40に代えて、充電用バイポーラトランジスタ32を用いてパワースイッチング素子Swのオン状態への切り替えを行うことで、サージの抑制や電力損失の低減等の要求に適切に応じることができる。しかもこの際、充電用MOSトランジスタ40を併用することで、パワースイッチング素子Swのゲート電圧を、充電用バイポーラトランジスタ32のみを用いた場合と比較して上昇させることができる。

【0074】

・駆動回路DCとしては、放電用バイポーラトランジスタ36を備えるものに限らない。例えば放電用バイポーラトランジスタ36を備えることなく、放電用MOSトランジスタ50によって放電処理を行うようにしてもよい。

【0075】

・駆動回路DCとしては、パワースイッチング素子Swのオフ時のゲート電圧を略ゼロ(出力端子電位と同電位)とするものに限らず、負(出力端子電位よりも低電位)とするものであってもよい。これを実現する上では、放電用MOSトランジスタ50を設けることが特に有効である。

【0076】

・放電用MOSトランジスタ50をオン操作するタイミングは、上記各実施形態にて例示したタイミングに限らない。例えば、充電用MOSトランジスタ40と放電用MOSトランジスタ50とに貫通電流が流れることがないとの条件下における極力早期のタイミングであってもよい。

【0077】

・上記各実施形態では、充電用抵抗体34と放電用抵抗体38とを別部材としたがこれに限らず、これらを同一の部材としてもよい。

【0078】

・充電用の電圧制御形のスイッチング素子としては、MOS型電界効果トランジスタに限らない。例えば、MIS型電界効果トランジスタ等、任意の電界効果トランジスタであってもよい。

【0079】

・パワースイッチング素子としては、IGBTに限らず、例えばパワーMOS型電界効果トランジスタであってもよい。

【0080】

・パワースイッチング素子にて構成される電力変換回路としては、インバータIVに限らない。例えば車載インバータIVと高圧バッテリ12との間に昇圧回路を備えるものにあっては、この昇圧回路であってもよい。また、高圧バッテリ12の電圧を降圧して低圧バッテリ16に供給する降圧コンバータであってもよい。これらであっても、パワースイッチング素子とフリーホイールダイオードとが直列接続された構成を有するなら、フリーホイールダイオードのリカバリ電流に起因したサージを抑制する設計を容易とする観点からは、充電用開閉手段として電流制御形のスイッチング素子を用いることが望ましいため、本発明の適用は有効である。

【図面の簡単な説明】

【0081】

【図1】第1の実施形態にかかるシステム構成図。

【図2】リカバリ電流に起因するサージの生成を説明するための図。

【図3】上記実施形態にかかる駆動回路の回路構成を示す回路図。

【図4】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図5】第2の実施形態にかかる駆動回路の回路構成を示す回路図。

【図6】第3の実施形態にかかる駆動回路の回路構成を示す回路図。

【図7】第4の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図8】第5の実施形態にかかる駆動回路の回路構成を示す回路図。

【図9】同実施形態にかかるパワースイッチング素子のオフ操作態様を示すタイムチャート。

【図10】第6の実施形態にかかる駆動回路の回路構成を示す回路図。

【図11】第7の実施形態にかかる駆動回路の回路構成を示す回路図。

【図12】第8の実施形態にかかるパワースイッチング素子のオフ操作態様を示すタイムチャート。

【符号の説明】

【0082】

32…充電用バイポーラトランジスタ、36…放電用バイポーラトランジスタ、40…充電用MOSトランジスタ、44…遅延回路、50…放電用MOSトランジスタ、Sw…パワースイッチング素子、FD…フリーホイールダイオード。

【技術分野】

【0001】

本発明は、電圧制御形のパワースイッチング素子を駆動するパワースイッチング素子の駆動回路に関する。

【背景技術】

【0002】

3相モータの各相を直流電源の正極側及び負極側に接続する一対のパワースイッチング素子の直列接続体を備えるインバータが周知である。ここで、一対のパワースイッチング素子のそれぞれには、フリーホイールダイオードが逆並列に接続されている。これら一対のパワースイッチング素子のうちの一方に接続されるフリーホイールダイオードに順方向電流が流れる状況下、他方のパワースイッチング素子をオン操作すると、フリーホイールダイオードには、そのカソード側からアノード側へとリカバリ電流が流れる。リカバリ電流は、増加した後、減少しやがてゼロとなるものであるが、減少を開始するに際して、フリーホイールダイオードの両端にサージ電圧が重畳する。そして、このサージ電圧は、パワースイッチング素子の入出力端子間の電圧降下量が大きいほど小さくなる。

【0003】

そこで従来、例えば下記特許文献1に見られるように、パワースイッチング素子としての絶縁ゲートバイポーラトランジスタ(IGBT)のゲートに正の電荷を充電するための高電位側のバイポーラトランジスタ及びIGBTのゲートから正の電荷を放電するための低電位側のバイポーラトランジスタの直列接続体を備え、これら一対のバイポーラトランジスタのベースに、CR回路を介してIGBTの駆動信号を印加するものも提案されている。これにより、上記一対のバイポーラトランジスタをエミッタフォロワとして用いることで、エミッタの出力電圧をCR回路の時定数に応じて調節することができる。これにより、ゲートの充電速度を調節することができ、ひいてはサージを好適に抑制することができる。

【0004】

なお、この種の駆動回路としては、他にも例えば下記特許文献2に記載されているものがある。

【特許文献1】特開平5−161343号公報

【特許文献1】特開2000−295838号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、高電位側のバイポーラトランジスタの出力端子(エミッタ)の電圧は、その入力端子(コレクタ)の電圧に対して低下する。このため、例えばMOS型電界効果トランジスタを用いる場合と比較して、IGBTのゲートに印加可能な電圧が小さくなる。そして、ゲートに印加可能な電圧が小さい場合には、IGBTがオン状態である際のIGBTの入力端子及び出力端子間の電圧降下量が増大し、ひいては電力損失が大きくなる。このため、IGBTとして、熱的に十分に余裕のある素子を選択することが要求される。更に、バイポーラトランジスタの出力電圧は、温度に応じて変化し易いため、出力電圧が温度に応じて低下する場合には、IGBTの損失が更に大きくなり、ひいてはIGBTとして更に熱的に余裕がある素子を選択することが要求されることとなる。

【0006】

ここで、IGBTのゲートをゲート抵抗を介して高電位側のバイポーラトランジスタに接続する代わりに、ゲート抵抗を介してMOS型電界効果トランジスタに接続する場合には、IGBTのゲートに印加可能な電圧を増大させることはできるものの、スイッチング状態の切り替えに伴うサージの抑制とスイッチング状態の切り替え時の電力損失の低減との両立を図ることが困難となることが懸念される。すなわち、MOS型の電界効果トランジスタとIGBTのゲートとの間のゲート抵抗を増大させると、スイッチング状態の切替速度が小さくなるため、サージを抑制することはできるものの、切り替え時の電力損失が増大する。これに対し、MOS型の電界効果トランジスタとIGBTのゲートとの間のゲート抵抗を低減すると、スイッチング状態の切替速度が大きくなるため、切り替え時の電力損失は低減できるものの、サージが増大する。

【0007】

本発明は、上記課題を解決するためになされたものであり、その目的は、電圧制御形のパワースイッチング素子の電力損失の抑制とサージの抑制との好適な両立を図ることのできるパワースイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0008】

以下、上記課題を解決するための手段、及びその作用効果について記載する。

【0009】

請求項1記載の発明は、電圧制御形のパワースイッチング素子を駆動する駆動回路において、前記パワースイッチング素子の導通制御端子に正の電荷を充電するための電源と前記導通制御端子との間を電気的に開閉する充電用開閉手段として、電流制御形のスイッチング素子と、電圧制御形のスイッチング素子とを備えることを特徴とする。

【0010】

上記発明では、電流制御形のスイッチング素子を備えることで、電圧制御形のスイッチング素子のみを用いる場合と比較して、パワースイッチング素子の導通制御端子の充電態様の設定の自由度が増し、ひいては、サージを好適に抑制することができる設定が可能となる。更に、電圧制御形のスイッチング素子を備えることで、電流制御形のスイッチング素子のみを用いる場合と比較して、パワースイッチング素子の導通制御端子の電圧を上昇させることもできる。このため、上記発明は、電圧制御形のパワースイッチング素子の電力損失の抑制とサージの抑制との好適な両立を図ることができる。

【0011】

請求項2記載の発明は、請求項1記載の発明において、前記電流制御形のスイッチング素子は、NPN型のバイポーラトランジスタであることを特徴とする。

【0012】

請求項3記載の発明は、請求項2記載の発明において、前記導通制御端子への前記電荷の充電期間のうちの充電開始から所定期間内における前記NPN型バイポーラトランジスタの出力電圧の上昇速度を緩和する緩和手段を備えることを特徴とする。

【0013】

パワースイッチング素子にダイオードが直列接続される場合、導通制御端子の充電期間の中間において、ダイオードにリカバリ電流が流れ、これによりサージが生じる。一方、導通制御端子の充電速度を抑制することで、サージを抑制することができることが知られている。上記発明では、この点に鑑み、緩和手段を備えることで、サージを好適に抑制することができる。

【0014】

請求項4記載の発明は、請求項3記載の発明において、前記緩和手段は、前記パワースイッチング素子の操作信号の変化を遅延させる遅延回路を備え、該遅延回路の出力電圧を前記NPN型バイポーラトランジスタのベースに印加する手段であることを特徴とする。

【0015】

上記発明では、遅延回路を備えることで、緩和手段を適切に構成することができる。

【0016】

請求項5記載の発明は、請求項1〜4のいずれか1項に記載の発明において、前記パワースイッチング素子の導通制御端子に正の電荷を充電すべく前記充電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧(前記パワースイッチング素子をオン状態とするための閾値電圧)以上となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする。

【0017】

上記発明では、電圧制御形のスイッチング素子を、パワースイッチング素子がオン状態となるタイミング以降において導通制御端子に印加する電圧を確保する用途として用いることができる。

【0018】

請求項6記載の発明は、請求項2〜5のいずれか1項に記載の発明において、前記パワースイッチング素子の導通制御端子から前記正の電荷を放電させるべく前記導通制御端子と前記正の電荷の放電経路の下流側との間を電気的に開閉する放電用開閉手段として、PNP型のバイポーラトランジスタを備えることを特徴とする。

【0019】

上記発明では、充電用開閉手段と放電用開閉手段とがそれぞれ、NPN型バイポーラトランジスタとPNP型バイポーラトランジスタとを備えるために、これらの一方に対してオン状態に切り替える指令を与えて且つ他方に対してオフ状態に切り替える指令を与える際、デッドタイムを生成する処理を削除することができる。

【0020】

請求項7記載の発明は、請求項6記載の発明において、前記放電用開閉手段として、電圧制御形のスイッチング素子を更に備えることを特徴とする。

【0021】

請求項8記載の発明は、請求項7記載の発明において、前記パワースイッチング素子の導通制御端子から正の電荷を放電すべく前記放電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧(前記パワースイッチング素子をオフ状態とするための閾値電圧)以下となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする。

【0022】

請求項9記載の発明は、請求項1〜8のいずれか1項に記載の発明において、前記パワースイッチング素子には、ダイオードが直列接続されてなることを特徴とする。

【発明を実施するための最良の形態】

【0023】

(第1の実施形態)

以下、本発明にかかるパワースイッチング素子の駆動回路をハイブリッド車の電力変換回路の駆動回路に適用した一実施形態について、図面を参照しつつ説明する。

【0024】

図1に、本実施形態のシステム構成を示す。図示されるように、車載回転機としてのモータジェネレータ10は、インバータIVを介して高圧バッテリ12に接続されている。インバータIVは、高電位側のパワースイッチング素子Swp及び低電位側のパワースイッチング素子Swnの直列接続体が3つ並列接続されて構成されている。そして、これら各直列接続体の接続点が、モータジェネレータ10の各相にそれぞれ接続されている。これら高電位側のパワースイッチング素子Swp及び低電位側のパワースイッチング素子Swnのそれぞれの入出力端子間(コレクタ及びエミッタ間)には、高電位側のフリーホイールダイオードFDp及び低電位側のフリーホイールダイオードFDnのカソード及びアノードが接続されている。

【0025】

上記インバータIVを構成するパワースイッチング素子Swp,Swnの導通制御端子(ゲート)には、いずれも駆動回路DCが接続されている。これにより、パワースイッチング素子Swp,Swnは、駆動回路DC及びインターフェース14を介して、低圧バッテリ16を電源とするマイクロコンピュータ(マイコン20)にて駆動される。ここで、インターフェース14は、インバータIVやコンバータCVを備える高圧システムと、マイコン20を備える低圧システムとを絶縁するフォトカプラ等の絶縁手段を備えて構成されるものである。マイコン20は、図示しない各種センサの検出値等に基づき、インバータIVのU相、V相、及びW相のそれぞれについての、パワースイッチング素子Swpを操作する操作信号gup,gvp,gwpと、パワースイッチング素子Swnを操作する操作信号gun,gvn,gwnとを生成し出力する。これにより、スイッチング素子Swp,Swnは、駆動回路DCを介してマイコン20により操作される。なお、各相の高電位側の操作信号gup,gvp,gwpのそれぞれと、低電位側の操作信号gun,gvn,gwnのそれぞれとは、高電位側のスイッチング素子Swpと低電位側のスイッチング素子Swnとを互いに相補的に駆動するものとしてもよい。すなわち、いずれか一方の操作信号がオン状態とするための信号である期間、他方の操作信号がオフ状態とするための信号となるようにしてもよい。

【0026】

上記パワースイッチング素子Swp,Swnは、いずれも、入力端子及び出力端子が一義に定義されており、出力端子から入力端子への電流の流通を阻止するスイッチング素子である。詳しくは、これらは、絶縁ゲートバイポーラトランジスタ(IGBT)にて構成されている。このため、高電位側のパワースイッチング素子Swpに電流が流れ得る状況下にあっては、これをオフ状態とすることで、低電位側のパワースイッチング素子Swnに電流が流れず、これに逆並列に接続されるフリーホイールダイオードFDnに電流が流れる。また、低電位側のパワースイッチング素子Swnに電流が流れ得る状況下にあっては、これをオフ状態とすることで、高電位側のパワースイッチング素子Swpに電流が流れず、これに逆並列に接続されるフリーホイールダイオードFDpに電流が流れる。そしてこの場合、上記パワースイッチング素子Swp(Swn)が再度オン操作される際には、フリーホイールダイオードFDn(FDp)にリカバリ電流が流れる。そして、このリカバリ電流は、パワースイッチング素子Swp,Swnをオン操作する際のサージ電圧の原因となる。以下、これについて図2を用いて更に説明する。

【0027】

図2には、高電位側のパワースイッチング素子Swpに電流が流れ得る状況を例示している。こうした状況下、図2(a)に示すように、高電位側のパワースイッチング素子Swpがオフ状態であるなら、コレクタ電流icはゼロであり、低電位側のフリーホイールダイオードFDnに順方向の電流idが流れる。この際、フリーホイールダイオードFDnの両端の電圧Vfdは略ゼロであるため、高電位側のパワースイッチング素子Swpのエミッタ及びコレクタ間の電圧Vceは、高圧バッテリ12の電圧Vdc程度となっている。

【0028】

ここで、時刻t1において、高電位側のパワースイッチング素子Swpがオン操作されると、図2(b)に示されるように、コレクタ電流icが漸増する。これに伴いフリーホイールダイオードFDnを流れる電流idは、漸減してやがてゼロとなる。このとき、コレクタ及びエミッタ間の電圧Vceは、コレクタ電流icの電流変化率とインバータIVの配線に存在するインダクタ成分(図中、配線インダクタLpと模式的に表記)の積を電源電圧Vdcから減算した値となる。

【0029】

フリーホイールダイオードFDnを流れる電流がゼロとなると、フリーホイールダイオードFDnのキャリア蓄積効果により、逆方向の電流であるリカバリ電流が流れ始める。このとき、高電位側のスイッチング素子Swpのコレクタ及びエミッタ間には、モータジェネレータ10との間で授受される電流(負荷電流)に加えて、リカバリ電流が流れることとなる。そしてその後、フリーホイールダイオードFDnの接合部のキャリアが減少し、リカバリ電流は漸増から漸減に転じ、やがてゼロとなる。ここで、リカバリ電流が漸増から漸減に転じる際には、リカバリ電流の電流変化率とインバータIVの配線に存在するインダクタ成分によって生じる電圧成分によってサージ電圧が生じる。

【0030】

図3に、上記サージ電圧の抑制効果を有する本実施形態にかかる駆動回路DCの回路構成を示す。なお、以下では、パワースイッチング素子Swp,Swnをパワースイッチング素子Swにて総括表記し、フリーホイールダイオードFDp,FDnをフリーホイールダイオードFDにて総括表記する。また、上記操作信号gup,gvp,gwp,gun,gvn,gwnを、操作信号gにて総括表記する。

【0031】

図示されるように、駆動回路DCにおいては、電圧Vinの電源30の正極に、NPN型のバイポーラトランジスタである充電用バイポーラトランジスタ32のコレクタが接続され、そのエミッタには、充電用抵抗体34を介してパワースイッチング素子Swのゲートが接続されている。また、電源30の負極に、PNP型のバイポーラトランジスタである放電用バイポーラトランジスタ36のコレクタが接続され、そのエミッタには、放電用抵抗体38を介してパワースイッチング素子Swのゲートが接続されている。更に、上記充電用バイポーラトランジスタ32のコレクタ及びエミッタ間には、PチャネルMOS型電界効果トランジスタからなる充電用MOSトランジスタ40が並列接続されている。

【0032】

一方、入力回路42は、上記操作信号gを入力とし、これに応じて充電用バイポーラトランジスタ32や、放電用バイポーラトランジスタ36、充電用MOSトランジスタ40を操作する回路である。ここで、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36との操作は、入力回路42は、操作信号gを所定に電圧変換した信号を遅延回路44に出力することで行われる。すなわち、入力回路42は、電源30の電圧Vinが印加される一対のバイポーラトランジスタ又はMOS型電界効果トランジスタ等からなるバッファ回路を備え、バッファ回路を介して操作信号gに応じた信号を遅延回路44に出力する。

【0033】

上記遅延回路44は、線形素子としての抵抗体44aとコンデンサ44bとを備えるCR回路である。抵抗体44aとコンデンサ44bとの接続点の電圧は、遅延回路44の出力信号(遅延電圧Vd)として、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36とのそれぞれのベースに印加される。この遅延回路44は、主に、充電用バイポーラトランジスタ32のエミッタの出力電圧Vout1の上昇速度を、操作信号gの上昇速度に対して緩和するために設けられたものである。すなわち、充電用バイポーラトランジスタ32は、エミッタフォロワ回路を構成しているため、エミッタからの出力電圧Vout1は、ベースに印加される電圧(遅延電圧Vd)となる(より正確には、これからベース及びエミッタ間の電圧降下量Vbeだけ低い値となる)。

【0034】

上記入力回路42は、更に、操作信号gによって、パワースイッチング素子Swをオフ状態からオン状態へと切り替える旨指示されてから所定期間経過することで充電用MOSトランジスタ40をオン状態とする機能を有する。これにより、パワースイッチング素子Swのゲートの充電終了後には、ゲートの電圧を電源30の電圧Vinに保持することができる。

【0035】

図4に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。詳しくは、図4(a)に、操作信号gの推移を示し、図4(b)に、入力回路42の出力信号の電圧(駆動電圧Vm)の推移を示し、図4(c)に、遅延回路44の出力信号の電圧(遅延電圧Vd)の推移を示し、図4(d)に、充電用バイポーラトランジスタ32の出力電圧Vout1の推移を示す。更に、図4(e)に、パワースイッチング素子Swのゲートの充電電流の推移を示し、図4(f)に、パワースイッチング素子Swのゲート電圧Vgの推移を示し、図4(g)に、充電用MOSトランジスタ32の状態の推移を示す。

【0036】

図示されるように、操作信号gが立ち上がることで駆動電圧Vmも立ち上がるものの、遅延電圧Vdの上昇速度は、駆動電圧Vmの上昇速度よりも緩やかとなる。このため、出力電圧Vout1の上昇速度も、操作信号gや駆動電圧Vmの立ち上がり速度と比較して緩やかなものとなる。したがって、ゲート電圧Vgの上昇速度は、上記遅延回路44を備えない場合と比較して緩やかなものとなる。

【0037】

上記出力電圧Vout1は緩やかに上昇した後、一定値となるものである。本実施形態では、パワースイッチング素子Swのオン状態への切り替わりに起因してこれに直列接続されるフリーホイールダイオードFDにリカバリ電流が流れる期間が、緩やかに上昇する期間に包含されるように、予め遅延回路44の時定数を設定する。これにより、リカバリ電流に起因するサージの抑制を図ることができる。

【0038】

一方、ゲートの充電電流は、出力電圧Vout1とゲート電圧Vgとの差圧に応じて流れるものである。ただし、この充電電流は、充電用抵抗体34によって制御可能である。このため、充電用抵抗体34を比較的低抵抗とすることで、出力電圧Vout1が略定常値となった後のゲートの充電速度を高速化することができる。このため、パワースイッチング素子Swがオフ状態からオン状態へと切り替わるまでに要する時間を短縮することができ、ひいてはスイッチング状態の切り替えに伴う電力損失を低減することができる。

【0039】

上記操作信号gによってパワースイッチング素子Swをオン状態に切り替える旨指示されてから所定期間T経過すると、上記充電用MOSトランジスタ40をオン操作とする。ここで、所定期間Tは、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電が略完了するタイミングに設定される。これにより、パワースイッチング素子Swがオン状態とされた後には、ゲート電圧Vgを電源30の電圧Vinに持ち上げ保持することができる。

【0040】

このように、本実施形態では、遅延回路44の出力電圧をエミッタフォロワを介してパワースイッチング素子Swのゲートに印加するようにしたことで、遅延回路44の時定数によって、サージを抑制すべくゲートの充電処理態様を調節することができる。このようにバイポーラトランジスタを用いてサージ対策を施すことで、あたかも充電用抵抗体34の抵抗値をゲートの充電期間において可変とするかのような充電制御が可能となる。このため、充電用抵抗体34のみによってサージ対策をする場合と比較して、スイッチング状態の切り替えに伴う電力損失の増大を抑制しつつもサージ対策をより好適に行うことができる。

【0041】

以上詳述した本実施形態によれば、以下の効果が得られるようになる。

【0042】

(1)パワースイッチング素子Swの導通制御端子(ゲート)に正の電荷を充電するための電源30とゲートとの間を電気的に開閉する充電用開閉手段として、充電用バイポーラトランジスタ32と、充電用MOSトランジスタ40とを備えた。これにより、パワースイッチング素子Swの電力損失の抑制とサージの抑制との好適な両立を図ることができる。

【0043】

(2)充電用バイポーラトランジスタ32をエミッタフォロワとして用いて且つ、そのベースに遅延回路44の出力電圧(遅延電圧Vd)を印加した。これにより、パワースイッチング素子Swのゲートの充電期間初期の充電速度を緩和することができ、ひいてはサージを好適に抑制することができる。

【0044】

(3)充電用バイポーラトランジスタ32をオン状態とすることでパワースイッチング素子Swのゲート電圧がパワースイッチング素子Swをオン状態とするための閾値電圧以上となるタイミング以降において充電用MOSトランジスタ40をオン状態とした。これにより、サージ対策を抑制する処理を確実に行うことや、充電用MOSトランジスタ40と放電用バイポーラトランジスタ36との間に貫通電流が流れることを回避することができる。

【0045】

(4)パワースイッチング素子Swのゲートから正の電荷を放電させるためのスイッチング素子として、放電用バイポーラトランジスタ36を備えた。これにより、充電用バイポーラトランジスタ32と放電用バイポーラトランジスタ36との双方が同時にオン状態となる貫通状態が生じることを制御上簡易に回避しつつ、操作信号gに基づきパワースイッチング素子Swのゲートの充放電処理を行うことができる。

【0046】

(第2の実施形態)

以下、第2の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0047】

図5に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図5において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0048】

本実施形態では、充電用バイポーラトランジスタ32の出力電圧Vout1をモニタし、これが閾値電圧以上となることで、充電用MOSトランジスタ40をオン操作する。そして、この閾値電圧を、電源30の電圧Vinよりも充電用バイポーラトランジスタ32のベース及びエミッタ間の電圧降下量Vbe程度低い値に設定する。これにより、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電処理中に、充電用MOSトランジスタ40をオン操作することができる。

【0049】

(第3の実施形態)

以下、第3の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0050】

図6に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図6において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0051】

本実施形態では、パワースイッチング素子Swのゲート電圧Vgをモニタし、これが閾値電圧以上となることで、充電用MOSトランジスタ40をオン操作する。そして、この閾値電圧を、電源30の電圧Vinよりも充電用バイポーラトランジスタ32のベース及びエミッタ間の電圧降下量Vbe程度低い値に設定する。これによっても、先の第1の実施形態のように、充電用バイポーラトランジスタ32によるパワースイッチング素子Swのゲートの充電の完了後に、充電用MOSトランジスタ40をオン操作することができる。

【0052】

(第4の実施形態)

以下、第4の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0053】

図7に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。なお、図7(a)〜図7(g)は、先の図4(a)〜図4(g)に対応している。

【0054】

図示されるように、本実施形態によっても、上記操作信号gによってパワースイッチング素子Swをオン状態に切り替える旨指示されてから所定期間T経過すると、上記充電用MOSトランジスタ40をオン操作する。ただし本実施形態では、所定期間Tを、パワースイッチング素子Swがオン状態への移行を開始するタイミング以降であって極力早期のタイミングに設定する。詳しくは、パワースイッチング素子Swのゲート電圧がミラー期間の電圧となるタイミングであって且つパワースイッチング素子Swに直列接続されるフリーホイールダイオードFDのリカバリ電流がゼロとなるタイミングに設定される。これにより、リカバリ電流がゼロとなった後には、パワースイッチング素子Swのゲート電圧を電源30の電圧Vinまで迅速に持ち上げることができる。

【0055】

(第5の実施形態)

以下、第5の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0056】

図8に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図8において、先の図3に示した部材に対応する部材については、便宜上同一の符号を付している。

【0057】

図示されるように、本実施形態では、放電用バイポーラトランジスタ36のコレクタ及びエミッタ間に、NチャネルのMOS型電界効果トランジスタとしての放電用MOSトランジスタ50が並列接続されている。

【0058】

図9に、本実施形態にかかるパワースイッチング素子Swのオフ状態への切り替え処理態様を示す。詳しくは、図9(a)に、操作信号gの推移を示し、図9(b)に、放電用バイポーラトランジスタ36のエミッタ電圧(出力電圧Vout1)の推移を示し、図9(c)に、パワースイッチング素子Swのゲート電圧の推移を示し、図9(d)に、放電用MOSトランジスタ50の状態の推移を示す。

【0059】

図示されるように、本実施形態では、操作信号gによって、パワースイッチング素子Swをオフ状態に切り替える旨指示されると、まず放電用バイポーラトランジスタ36がオン操作されることで、パワースイッチング素子Swのゲートから正の電荷を放電させる。そして、上記指示されるタイミングから所定期間Tが経過することで、放電用MOSトランジスタ50がオン操作されることで、パワースイッチング素子Swのゲート電圧Vgを、電源30の負極電位まで引き下げて保持する。ここで、所定期間Tは、放電用バイポーラトランジスタ36によるパワースイッチング素子Swのゲートの放電処理が完了するのに要する所要時間程度に設定される。

【0060】

(第6の実施形態)

以下、第6の実施形態について、先の第5の実施形態との相違点を中心に図面を参照しつつ説明する。

【0061】

図10に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図10において、先の図8に示した部材に対応する部材については、便宜上同一の符号を付している。

【0062】

本実施形態では、放電用バイポーラトランジスタ36の出力電圧Vout2をモニタし、これが閾値電圧以下となることで、放電用MOSトランジスタ50をオン操作する。そして、この閾値電圧を、放電用バイポーラトランジスタ36のベース及びエミッタ間の電圧降下量Vbe程度に設定する。これにより、パワースイッチング素子Swのゲートの放電処理の途中で、放電用MOSトランジスタ50をオン操作することができる。

【0063】

(第7の実施形態)

以下、第7の実施形態について、先の第5の実施形態との相違点を中心に図面を参照しつつ説明する。

【0064】

図11に、本実施形態にかかる駆動回路DCの回路構成を示す。なお、図11において、先の図10に示した部材に対応する部材については、便宜上同一の符号を付している。

【0065】

本実施形態では、パワースイッチング素子Swのゲート電圧Vgをモニタし、これが閾値電圧以下となることで、放電用MOSトランジスタ50をオン操作する。そして、この閾値電圧を、放電用バイポーラトランジスタ36のベース及びエミッタ間の電圧降下量Vbe程度に設定する。これによっても、先の第5の実施形態のように、放電用バイポーラトランジスタ36によるパワースイッチング素子Swのゲートの放電の完了後に、放電用MOSトランジスタ50をオン操作することができる。

【0066】

(第8の実施形態)

以下、第8の実施形態について、先の第1の実施形態との相違点を中心に図面を参照しつつ説明する。

【0067】

図12に、本実施形態にかかるパワースイッチング素子Swのオン状態への切り替え処理態様を示す。なお、図12(a)〜図12(d)は、先の図9(a)〜図9(d)に対応している。

【0068】

図示されるように、本実施形態によっても、上記操作信号gによってパワースイッチング素子Swをオフ状態に切り替える旨指示されてから所定期間T経過すると、上記放電用MOSトランジスタ50をオン操作する。ただし本実施形態では、所定期間Tを、パワースイッチング素子Swがオフ状態への移行を開始するタイミング以降であって極力早期のタイミングに設定する。詳しくは、パワースイッチング素子Swのゲート電圧がミラー期間の電圧にある間のタイミングに設定する。これにより、パワースイッチング素子Swの放電速度を上昇させることができる。このため、遅延回路44を設けたことによるゲート電圧の低下速度の低下を、放電用抵抗体38との協働によって好適に補償することができる。更に、放電速度を所望に制御する自由度を向上させることもできるため、ゲート電圧の低下速度を所望に制御することも可能となる。

【0069】

(その他の実施形態)

なお、上記各実施形態は、以下のように変更して実施してもよい。

【0070】

・先の第1の実施形態に対する第3の実施形態の変更点によって、先の第4の実施形態を変更してもよい。

【0071】

・先の第5の実施形態に対する第7の実施形態の変更点によって、先の第8の実施形態を変更してもよい。

【0072】

・遅延回路44としては、CR回路に限らない。例えば、抵抗体44aと並列に、コンデンサ44b側から入力回路42側に進む方向を順方向とするダイオードを備えてもよい。この場合、パワースイッチング素子Swをオフ状態に切り替えるに際して、放電用バイポーラトランジスタ36の出力電圧の低下速度を増大させることができる。また例えば、LCR回路であってもよい。

【0073】

・パワースイッチング素子Swのゲートへの正の電荷の充電初期における充電用バイポーラトランジスタ32の出力電圧Vout1の上昇速度を、操作信号gの論理反転速度に対して緩和する緩和手段としては、遅延回路に限らない。例えば、パワースイッチング素子Swの電力損失の低減とサージ電圧の抑制との優先度合いに基づき、充電用バイポーラトランジスタ32のベース電流を可変設定するものであってもよい。この場合であっても、充電用MOSトランジスタ40に代えて、充電用バイポーラトランジスタ32を用いてパワースイッチング素子Swのオン状態への切り替えを行うことで、サージの抑制や電力損失の低減等の要求に適切に応じることができる。しかもこの際、充電用MOSトランジスタ40を併用することで、パワースイッチング素子Swのゲート電圧を、充電用バイポーラトランジスタ32のみを用いた場合と比較して上昇させることができる。

【0074】

・駆動回路DCとしては、放電用バイポーラトランジスタ36を備えるものに限らない。例えば放電用バイポーラトランジスタ36を備えることなく、放電用MOSトランジスタ50によって放電処理を行うようにしてもよい。

【0075】

・駆動回路DCとしては、パワースイッチング素子Swのオフ時のゲート電圧を略ゼロ(出力端子電位と同電位)とするものに限らず、負(出力端子電位よりも低電位)とするものであってもよい。これを実現する上では、放電用MOSトランジスタ50を設けることが特に有効である。

【0076】

・放電用MOSトランジスタ50をオン操作するタイミングは、上記各実施形態にて例示したタイミングに限らない。例えば、充電用MOSトランジスタ40と放電用MOSトランジスタ50とに貫通電流が流れることがないとの条件下における極力早期のタイミングであってもよい。

【0077】

・上記各実施形態では、充電用抵抗体34と放電用抵抗体38とを別部材としたがこれに限らず、これらを同一の部材としてもよい。

【0078】

・充電用の電圧制御形のスイッチング素子としては、MOS型電界効果トランジスタに限らない。例えば、MIS型電界効果トランジスタ等、任意の電界効果トランジスタであってもよい。

【0079】

・パワースイッチング素子としては、IGBTに限らず、例えばパワーMOS型電界効果トランジスタであってもよい。

【0080】

・パワースイッチング素子にて構成される電力変換回路としては、インバータIVに限らない。例えば車載インバータIVと高圧バッテリ12との間に昇圧回路を備えるものにあっては、この昇圧回路であってもよい。また、高圧バッテリ12の電圧を降圧して低圧バッテリ16に供給する降圧コンバータであってもよい。これらであっても、パワースイッチング素子とフリーホイールダイオードとが直列接続された構成を有するなら、フリーホイールダイオードのリカバリ電流に起因したサージを抑制する設計を容易とする観点からは、充電用開閉手段として電流制御形のスイッチング素子を用いることが望ましいため、本発明の適用は有効である。

【図面の簡単な説明】

【0081】

【図1】第1の実施形態にかかるシステム構成図。

【図2】リカバリ電流に起因するサージの生成を説明するための図。

【図3】上記実施形態にかかる駆動回路の回路構成を示す回路図。

【図4】同実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図5】第2の実施形態にかかる駆動回路の回路構成を示す回路図。

【図6】第3の実施形態にかかる駆動回路の回路構成を示す回路図。

【図7】第4の実施形態にかかるパワースイッチング素子のオン操作態様を示すタイムチャート。

【図8】第5の実施形態にかかる駆動回路の回路構成を示す回路図。

【図9】同実施形態にかかるパワースイッチング素子のオフ操作態様を示すタイムチャート。

【図10】第6の実施形態にかかる駆動回路の回路構成を示す回路図。

【図11】第7の実施形態にかかる駆動回路の回路構成を示す回路図。

【図12】第8の実施形態にかかるパワースイッチング素子のオフ操作態様を示すタイムチャート。

【符号の説明】

【0082】

32…充電用バイポーラトランジスタ、36…放電用バイポーラトランジスタ、40…充電用MOSトランジスタ、44…遅延回路、50…放電用MOSトランジスタ、Sw…パワースイッチング素子、FD…フリーホイールダイオード。

【特許請求の範囲】

【請求項1】

電圧制御形のパワースイッチング素子を駆動する駆動回路において、

前記パワースイッチング素子の導通制御端子に正の電荷を充電するための電源と前記導通制御端子との間を電気的に開閉する充電用開閉手段として、電流制御形のスイッチング素子と、電圧制御形のスイッチング素子とを備えることを特徴とするパワースイッチング素子の駆動回路。

【請求項2】

前記電流制御形のスイッチング素子は、NPN型のバイポーラトランジスタであることを特徴とする請求項1記載のパワースイッチング素子の駆動回路。

【請求項3】

前記導通制御端子への前記電荷の充電期間のうちの充電開始から所定期間内における前記NPN型バイポーラトランジスタの出力電圧の上昇速度を緩和する緩和手段を備えることを特徴とする請求項2記載のパワースイッチング素子の駆動回路。

【請求項4】

前記緩和手段は、前記パワースイッチング素子の操作信号の変化を遅延させる遅延回路を備え、該遅延回路の出力電圧を前記NPN型バイポーラトランジスタのベースに印加する手段であることを特徴とする請求項3記載のパワースイッチング素子の駆動回路。

【請求項5】

前記パワースイッチング素子の導通制御端子に正の電荷を充電すべく前記充電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧以上となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする請求項1〜4のいずれか1項に記載のパワースイッチング素子の駆動回路。

【請求項6】

前記パワースイッチング素子の導通制御端子から前記正の電荷を放電させるべく前記導通制御端子と前記正の電荷の放電経路の下流側との間を電気的に開閉する放電用開閉手段として、PNP型のバイポーラトランジスタを備えることを特徴とする請求項2〜5のいずれか1項に記載のパワースイッチング素子の駆動回路。

【請求項7】

前記放電用開閉手段として、電圧制御形のスイッチング素子を更に備えることを特徴とする請求項6記載のパワースイッチング素子の駆動回路。

【請求項8】

前記パワースイッチング素子の導通制御端子から正の電荷を放電すべく前記放電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧以下となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする請求項7記載のパワースイッチング素子の駆動回路。

【請求項9】

前記パワースイッチング素子には、ダイオードが直列接続されてなることを特徴とする請求項1〜8のいずれか1項に記載のパワースイッチング素子の駆動回路。

【請求項1】

電圧制御形のパワースイッチング素子を駆動する駆動回路において、

前記パワースイッチング素子の導通制御端子に正の電荷を充電するための電源と前記導通制御端子との間を電気的に開閉する充電用開閉手段として、電流制御形のスイッチング素子と、電圧制御形のスイッチング素子とを備えることを特徴とするパワースイッチング素子の駆動回路。

【請求項2】

前記電流制御形のスイッチング素子は、NPN型のバイポーラトランジスタであることを特徴とする請求項1記載のパワースイッチング素子の駆動回路。

【請求項3】

前記導通制御端子への前記電荷の充電期間のうちの充電開始から所定期間内における前記NPN型バイポーラトランジスタの出力電圧の上昇速度を緩和する緩和手段を備えることを特徴とする請求項2記載のパワースイッチング素子の駆動回路。

【請求項4】

前記緩和手段は、前記パワースイッチング素子の操作信号の変化を遅延させる遅延回路を備え、該遅延回路の出力電圧を前記NPN型バイポーラトランジスタのベースに印加する手段であることを特徴とする請求項3記載のパワースイッチング素子の駆動回路。

【請求項5】

前記パワースイッチング素子の導通制御端子に正の電荷を充電すべく前記充電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧以上となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする請求項1〜4のいずれか1項に記載のパワースイッチング素子の駆動回路。

【請求項6】

前記パワースイッチング素子の導通制御端子から前記正の電荷を放電させるべく前記導通制御端子と前記正の電荷の放電経路の下流側との間を電気的に開閉する放電用開閉手段として、PNP型のバイポーラトランジスタを備えることを特徴とする請求項2〜5のいずれか1項に記載のパワースイッチング素子の駆動回路。

【請求項7】

前記放電用開閉手段として、電圧制御形のスイッチング素子を更に備えることを特徴とする請求項6記載のパワースイッチング素子の駆動回路。

【請求項8】

前記パワースイッチング素子の導通制御端子から正の電荷を放電すべく前記放電用開閉手段を閉状態とする処理は、前記電流制御形のスイッチング素子をオン状態とした後、前記パワースイッチング素子の導通制御端子の電圧が閾値電圧以下となるタイミング以降において前記電圧制御形のスイッチング素子をオン状態とする処理であることを特徴とする請求項7記載のパワースイッチング素子の駆動回路。

【請求項9】

前記パワースイッチング素子には、ダイオードが直列接続されてなることを特徴とする請求項1〜8のいずれか1項に記載のパワースイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2010−93885(P2010−93885A)

【公開日】平成22年4月22日(2010.4.22)

【国際特許分類】

【出願番号】特願2008−259344(P2008−259344)

【出願日】平成20年10月6日(2008.10.6)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成22年4月22日(2010.4.22)

【国際特許分類】

【出願日】平成20年10月6日(2008.10.6)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]