ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

【発明の詳細な説明】

【技術分野】

【0001】

ヒューズ、半導体装置、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体装置は、冗長回路などの設定や、抵抗値などの調整のために、トリミング回路を有している。トリミング回路は、印加する電圧や電流によって導通状態から非導通状態となる、つまり溶断する素子(ヒューズ:Fuse)を含む。このようなトリミング回路の場合、溶断箇所の絶縁距離を十分に確保することが難しく、時間経過によって切断箇所が接続状態に変化する場合がある。このため、別のトリミング回路は、書き込み電圧によって非導通状態から導通状態となる素子(アンチヒューズ:anti−fuse)を含む(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特表2007−536744号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところが、非導通状態から導通状態となる素子は、絶縁膜を挟む2つの導体間に、絶縁膜を破壊する高電圧を印加する必要がある。このようなトリミング回路を含む半導体装置には、高電圧に対応する素子や制御回路が必要となる。このような素子や制御回路は、半導体装置のサイズの増大を招く。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、第1の導電体と、前記第1の導電体の上方にある絶縁膜と、前記絶縁膜の上方にある第2の導電体と、前記第2の導電体の上方にあり、引っ張り応力を有するカバー膜と、前記第1の導電体に接続する第1のプラグと、前記第2の導電体に接続する第2のプラグ及び第3のプラグを有する。

【発明の効果】

【0006】

本発明の一観点によれば、高電圧が不要で安定した状態を得ることができる。

【図面の簡単な説明】

【0007】

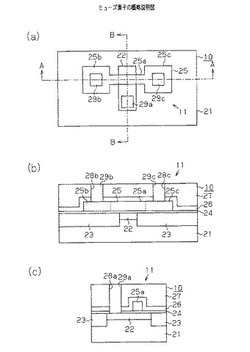

【図1】(a)はヒューズ素子の概略平面図、(b)はA−A線断面図、(c)はB−B線断面図である。

【図2】(a),(b)は動作説明図である。

【図3】(a),(b)は動作説明図である。

【図4】トリミング回路の回路図である。

【図5】半導体装置の概略平面図である。

【図6】半導体装置の概略断面図である。

【図7】(a)〜(e)は製造工程の説明図である。

【図8】(a)〜(d)は製造工程の説明図である。

【図9】別のヒューズ素子の(a)概略平面図、(b)断面図である。

【図10】別の半導体装置の概略断面図である。

【図11】(a)〜(f)は製造工程の説明図である。

【図12】(a)〜(e)は製造工程の説明図である。

【発明を実施するための形態】

【0008】

以下、一実施形態を添付図面に従って説明する。尚、添付図面は、構造の概略を説明するためのものであり、実際の大きさを表していない。

図1(a)に示すように、半導体装置10にはヒューズ素子11が形成されている。ヒューズ素子11は、概略的に、拡散領域22と、半導体基板21の厚さ方向(図1(a)において図面の表裏方向)において拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。拡散領域22は、第1の導電体の一例であり、導電体25は第2の導電体の一例である。

【0009】

図1(b)に示すように、半導体装置10の半導体基板21には、例えばN+型の拡散領域22が形成されている。拡散領域22は、平面視長方形状に形成されている。拡散領域22の幅は、例えば1.5μm(マイクロメートル)である。

【0010】

半導体基板21には素子分離領域23が形成されている。この素子分離領域23は、拡散領域22を、半導体基板21に形成された他の素子(図示略)と電気的に分離する。素子分離領域23は、例えば、LOCOS(local oxidation of silicon)やSTI(shallow trench isolation)により形成される。

【0011】

拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24は,例えばシリコン酸化膜(SiO2)である。この絶縁膜24の膜厚は、例えば18nm(ナノメートル)である。

【0012】

絶縁膜24上には、導電体25が形成されている。導電体25は、例えば多結晶シリコン(ポリシリコン:polycrystalline silicon)膜である。導電体25は、所定の方向(図1(b)において左右方向)に沿って延びる長方形状に形成された接続部25aと、接続部25aの両端に矩形状に形成された端子部25b,25cとを有している。接続部25aは例えば、長さが2μm、幅は1.2μm、厚さは400nmである。

【0013】

導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。カバー膜26は、例えばシリコン窒化膜(SiN,Si3N4)である。シリコン窒化膜は、高い引っ張り応力を持つ。例えば、膜厚30nmのシリコン窒化膜(SiN)は、1GPa(ギガパスカル)のテンシル(tensile)応力を持つ。

【0014】

カバー膜26上には層間絶縁膜27が形成されている。層間絶縁膜27は、例えばシリコン酸化膜である。層間絶縁膜27の上面は、平坦状に形成され、図示しない上層の配線を形成し易くしている。図1(c)に示すように、層間絶縁膜27には上面から拡散領域22まで延びるコンタクトホール28aが形成されている。コンタクトホール28a内には、拡散領域22と接続されるプラグ29aが形成されている。同様に、図1(b)に示すように、層間絶縁膜27には上面から導電体25の端子部25b,25cまで延びるコンタクトホール28b,28cが形成されている。コンタクトホール28b,28c内には、導電体25の端子部25b,25cとそれぞれ接続されるプラグ29b,29cが形成されている。プラグ29a〜29cは、例えばタングステン(W)である。

【0015】

上記のように形成されたヒューズ素子11において、導電体25に接続されるプラグ29b,29c間に、プログラムのための電流Ipが供給される。この電流は、100mA(ミリアンペア)〜400mAである。導電体25の接続部25aは、電流Ipにより、例えば1400℃を越えるように発熱し、溶断破壊する。このとき、図3(a)及び図3(b)に示すように、絶縁膜24上に形成された接続部25aは、上方に向って膨張する。しかし、接続部25aは、図1(b)及び図1(c)に示すように、上方及び側方に形成されたカバー膜26により覆われている。このカバー膜26は、高い引っ張り応力を持つ膜である。従って、接続部25aは、図2(a)及び図2(b)に示すように、カバー膜26が形成されていない方向(カバー膜26が開口する方向)、即ち下方に向って膨張する。このように、下方に向って膨張する接続部25aは、絶縁膜24を突き破り、拡散領域22と接続される。即ち、図1(a)に示すプラグ29aとプラグ29b,29cの間は、導電体25(接続部25a)を溶断破壊することにより、接続状態となる。

【0016】

上記のヒューズ素子11は、例えば、図4に示すトリミング回路30に用いられる。

トリミング回路30は、ヒューズ素子11と、ドライバトランジスタT1と、抵抗R1を含む。

【0017】

ヒューズ素子11は、互いに絶縁された第1の電極(拡散領域)22と第2の電極(導電体)25とを含む。第1の電極25は第1の端子11aに接続され、第1の端子11aは出力ノードN1に接続されている。第2の電極25は、第2の端子11bと第3の端子11cとの間に接続されている。第2の端子11bは高電位電圧VDDが供給される配線31に接続され、第3の端子11cはドライバトランジスタT1に接続されている。第1〜第3の端子11a〜11cは、それぞれ図1(a)に示すプラグ29a〜29cに対応する。

【0018】

ドライバトランジスタT1は例えばNチャネルMOSトランジスタである。このドライバトランジスタT1のソースは、低電位電圧VSSが供給される配線32に接続され、ドレインがヒューズ素子11の第3の端子11cに接続され、ゲートにプログラム電圧VPRGが供給される。このドライバトランジスタT1は、上記のヒューズ素子11にプログラム電流Ipを流すように形成されている。例えば、ドライバトランジスタT1のゲート長Lは0.8μm、ゲート幅Wは1400μmである。

【0019】

出力ノードN1は抵抗R1の第1端子に接続され、抵抗R1の第2端子は配線32に接続されている。抵抗R1の抵抗値は例えば1MΩ(メガオーム)である。

トリミング回路30は、初期状態において、ヒューズ素子11の第1の電極11aと第2の電極が非導通状態にある。このとき、出力ノードN1は、抵抗R1によりプルダウンされ、低電位電圧VSSレベル(Lレベル)である。従って、トリミング回路30はLレベルの信号Soを生成する。

【0020】

ヒューズ素子11をプログラムするとき、ドライバトランジスタT1のゲートに、パルス状のプログラム電圧VPRGが供給される。プログラム電圧VPRGのパルス形状は、例えば、振幅が7V(ボルト)であり、パルス幅tWが100μS(マイクロ秒)立ち上がりエッジの遷移時間trが1μSである。

【0021】

ゲートに印加されるプログラム電圧VPRGに基づいてドライバトランジスタT1がオンすると、高電位電圧VDDが供給される配線31からヒューズ素子11とドライバトランジスタT1を介して低電位電圧VSSが供給される配線32に向って電流Ipが流れる。この電流Ipにより、ヒューズ素子11の第1の電極11aが溶断破壊し、第1の電極11aと第2の電極11bが互いに接続する。この結果、出力ノードN1は、高電位電圧VDDレベル(Hレベル)となる。従って、トリミング回路30はHレベルの信号Soを生成する。

【0022】

図5に示すように、半導体装置40には、トリミング回路30に含まれるヒューズ素子11.ドライバトランジスタT1,抵抗R1が形成されている。図中、黒丸はプラグを示す。

【0023】

ドライバトランジスタT1は、ゲート配線41と、ソース領域42と、ドレイン領域43を含む。ゲート配線41は多結晶シリコンにより形成される配線である。ソース領域42及びドレイン領域43は、N型の拡散領域である。抵抗R1は、多結晶シリコンにより形成される。従って、ヒューズ素子11の導電体25を、ドライバトランジスタT1のゲート配線41、抵抗R1と同時に形成することができる。

【0024】

図6は、半導体装置40の断面を示す。なお、説明の便宜上、図6において、ドライバトランジスタT1とヒューズ素子11と抵抗R1を一列に配置して示している。

図6に示すように、半導体基板(シリコン基板)51には、ドライバトランジスタT1に対応するP型のウェル領域52と、ヒューズ素子11に対応するN型のウェル領域53と、抵抗R1に対応するP型のウェル領域54が形成されている。N型のウェル領域53は、第1の導電体の一例である。また、半導体基板51には、素子分離領域55が形成されている。素子分離領域55は、例えば、LOCOS法により形成される。

【0025】

ウェル領域52には、ソース領域56とドレイン領域57が形成されている。ソース領域56とドレイン領域57はそれぞれ、低濃度のN−拡散領域と、高濃度のN+拡散領域を含む。ソース領域56とドレイン領域57にはそれぞれシリサイド層が形成されている。ウェル領域52上にはゲート酸化膜58を介してゲート配線59が形成されている。ゲート配線59は、多結晶シリコン(ポリシリコン)により形成されている。ゲート配線59の上部にはシリサイド層が形成されている。シリサイド層は、例えば、ポリシリコンに高融点金属材料(例えばコバルト(Co))を反応させて形成されている。ゲート配線59の側部にはサイドウォール60が形成されている。サイドウォール60は、例えば、ゲート配線59を覆うように形成したシリコン酸化膜をエッチバックして形成される。

【0026】

ウェル領域53上にはシリコン酸化膜61を介して導電体62が形成されている。導電体62は、両端が、素子分離領域55上まで延びるように形成されている。導電体62は、多結晶シリコン(ポリシリコン)により形成されている。導電体62の側部には、サイドウォール63が形成されている。

【0027】

ウェル領域55に対応する素子分離領域55上には抵抗R1が形成されている。抵抗R1は、多結晶シリコン(ポリシリコン)により形成されている。抵抗R1の側部には、サイドウォール64が形成されている。

【0028】

各素子(バルク)は、カバー膜65により被覆されている。カバー膜65は、引っ張り応力の高い膜、例えばシリコン窒化膜(SiN,Si3N4)である。カバー膜65上には層間絶縁膜66が形成されている。層間絶縁膜66は、例えば、シリコン酸化膜である。層間絶縁膜66の上面は平坦状に形成されている。

【0029】

半導体装置40には、ドライバトランジスタT1のソース領域56とドレイン領域57にそれぞれ接続されるプラグ67が形成されている。また、半導体装置40には、導電体62の両端にそれぞれ接続されるプラグ68が形成されている。なお、図6では省略したが、N型のウェル領域53に接続されるプラグが形成されている。また、半導体装置には、抵抗R1と接続されるプラグ69が形成されている。なお、図6では省略したが、抵抗R1の両端に接続されるプラグが形成されている。各プラグ67〜69は、例えばタングステン(W)である。

【0030】

次に、半導体装置40の製造方法を説明する。

図7(a)に示すように、半導体基板51の一主面(上面)に酸化膜71を形成し、酸化膜71上にシリコン窒化膜72を形成する。例えば、温度850℃の条件で半導体基板51を熱酸化して膜厚3nmの酸化膜71を形成する。例えば化学気相成長(CVD:Chemical Vapor Deposition)で、温度775℃の条件で膜厚115nmのシリコン窒化膜72を成膜する。次いで、フォトリソグラフィ法により形成したレジストマスクによりシリコン窒化膜72をエッチングし、図7(b)に示すように、素子分離に対応するシリコン窒化膜72a,72bを形成する。

【0031】

次いで、図7(c)に示すように、例えばイオン注入法により、ウェル領域52,53,54を形成する。半導体基板51に、N型の不純物(ドーパント:dopant)を導入してウェル領域53を形成する。N型のドーパント不純物は例えばリン(P)である。イオン注入条件は、例えば、加速電圧を180keV、ドーズ量を5.0×1012cm−2とする。また、半導体基板51に、P型の不純物(ドーパント)を導入してウェル領域52,54を形成する。P型のドーパント不純物は例えばホウ素(ボロン(B))である。イオン注入条件は、例えば、加速電圧を160keV、ドーズ量を1.2×1013cm−2とする。

【0032】

次いで、図7(d)に示すように、例えば、ウェット酸化で、温度1000℃の条件で、膜厚370nmの素子分離領域55を形成する。そして、図7(c)に示すシリコン窒化膜72a,72bを除去する。次いで、図7(e)に示すように、例えば温度1000℃の条件で熱酸化を行い、例えば18.5nmの酸化膜61,73を形成する。次いで、例えばCVD法により、膜厚300nmの多結晶シリコン膜(ポリシリコン膜)74を成膜する。

【0033】

次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜74をエッチングし、図8(a)に示すように、ドライバトランジスタT1のゲート配線59と、ヒューズ素子11の導電体62と、抵抗R1を形成する。次いで、図8(b)に示すように、例えばイオン注入法により、ウェル領域52に対してN型の不純物を導入して低濃度のN−拡散領域56a,57aを形成する。次いで、サイドウォール60.63.64を形成する。次いで、例えばイオン注入法により、ウェル領域52に対してN型の不純物を導入して高濃度のN+拡散領域56b,57bを形成する。

【0034】

次いで、図8(c)に示すように、ゲート配線59の上部、拡散領域56,57の上部にシリサイド層59a,56c,57cを形成する。次いで、例えばCVD法により、膜厚80nmのカバー膜65を成膜する。次いで、図8(d)に示すように、例えばCVD法により、バルク上に膜厚1400nmの層間絶縁膜66を成膜し、例えば化学機械的研磨(CMP:Chemical Mechanical Polishing)法により、層間絶縁膜66の表面を平坦化する。そして、カバー膜65をエッチングストッパ膜として層間絶縁膜66をエッチングし、深さが異なるコンタクトホールを形成する。次いで、カバー膜65をエッチングしてシリサイド層56c,57cを露出し、コンタクトホールに例えばCVD法によりタングステンを充填して図6に示すプラグ67〜69を形成する。

【0035】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)ヒューズ素子11は、半導体基板21に形成された拡散領域22と、拡散領域22の上に形成された絶縁膜24と、絶縁膜24上に形成された導電体25を含む。更に、ヒューズ素子11は、導電体25上のカバー膜26を含む。このカバー膜26は、絶縁膜24より高い引っ張り応力を持つ。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。導電体25には、プログラムのための電流Ipが供給される。導電体25は、電流Ipにより発熱し、溶断破壊する。そして、導電体25は、カバー膜26が形成されていない方向(カバー膜26が開口する方向)、即ち下方に向って膨張し、絶縁膜24を破壊する(突き破る)。この結果、導電体25は拡散領域22と接続される。

【0036】

このように、導電体25は供給される電流Ipにより拡散領域22と接続されるため、高電圧を供給する必要がない。そして、高電圧を必要としないため、ヒューズ素子11を含む半導体装置において、プログラムのための回路部分に耐圧を必要としない。従って、半導体装置の面積増大を抑制することができる。

【0037】

(2)ヒューズ素子11は、導電体25と拡散領域22とが短絡することにより、アンチヒューズとして働く。導電体25の両端に接続されるプラグ29b,29c間が電気的に切断されていなくてもよい。従って、切断箇所がストレス等によって短絡することを考慮する必要がなく、継続的に安定した状態を保つことができる。

【0038】

(3)ヒューズ素子11の導電体25はポリシリコンにより形成される。従って、導電体25は、導電体25にプログラムのための電流Ipを流すドライバトランジスタT1のゲート配線59と同様に形成することができるため、特別な製造工程を必要としない。また、導電体25とゲート配線59を1つの工程内で同時に形成することができ、製造工程の増加を抑制することができる。

【0039】

(4)半導体基板51に形成されたバルクを覆うカバー膜65は、カバー膜65の上に形成した層間絶縁膜66にコンタクトホール67〜69を形成する際のエッチングストッパ膜として利用される。従って、ドライバトランジスタT1のソース領域56及びドレイン領域57と接続されるプラグ67、導電体62と接続されるプラグ68,抵抗R1と接続されるプラグ69を確実に形成することができる。また、エッチングストッパ膜を別途形成する必要がなく、工程数の増加を抑制することができる。

【0040】

(別の実施形態)

図9(a)に示すように、半導体装置80にはヒューズ素子81が形成されている。ヒューズ素子81は、概略的に、第1の導電体92と、半導体基板の厚さ方向(図9(a)において図面の表裏方向)において第1の導電体92と一部重なるように第1の導電体92より上方に形成された第2の導電体94を含む。第1の導電体92は、例えば多結晶シリコン(ポリシリコン)膜である。第2の導電体94は、例えば多結晶シリコン膜である。

【0041】

図9(b)に示すように、第1の導電体92は、半導体基板に形成された絶縁領域91の上に形成されている。絶縁領域91は、例えば、LOCOSやSTIである。図9(a)に示すように、第1の導電体92は、直方体状に形成されている。

【0042】

図9(b)に示すように、第1の導電体92上には絶縁膜93が形成されている。絶縁膜93は,例えばシリコン酸化膜(SiO2),多層絶縁膜である。多層絶縁膜は、下層から上層に向って、例えば、シリコン酸化膜(SiO2)、シリコン窒化膜(SiN)、シリコン酸化膜(SiO2)が積層された膜(ONO膜)である。

【0043】

絶縁膜93上には、第2の導電体94が形成されている。導電体94は、所定の方向(図9(b)において左右方向)に沿って延びる長方形状に形成された接続部94aと、接続部94aの両端に矩形状に形成された端子部94b,94cとを有している。

【0044】

導電体94上には、カバー膜95が形成されている。カバー膜95は、半導体基板の主面(上面)側の全面を覆うように形成されている。従って、導電体94は、上面及び側面がカバー膜95により被覆されている。更に、カバー膜95は、第1の導電体92の上面及び側面を被覆するように形成されている。カバー膜95は、絶縁膜93より高い引っ張り応力を持つ。カバー膜95は、例えばシリコン窒化膜(SiN,Si3N4)である。

【0045】

カバー膜95上には層間絶縁膜96が形成されている。層間絶縁膜96は、例えばシリコン酸化膜である。層間絶縁膜96の上面は、平坦状に形成され、図示しない上層の配線を形成し易くしている。図9(b)に示すように、層間絶縁膜96には上面から第1の導電体92まで延びるコンタクトホール97aが形成されている。コンタクトホール97a内には、第1の導電体92と接続されるプラグ98aが形成されている。同様に、図9(b)に示すように、層間絶縁膜96には上面から導電体94の端子部94b,94cまで延びるコンタクトホール97b,97cが形成されている。コンタクトホール97b,97c内には、導電体94の接続部94b.94cとそれぞれ接続されるプラグ98b,98cが形成されている。

【0046】

上記したように、ヒューズ素子81は、半導体基板の厚さ方向に沿って重なるように形成されたポリシリコン膜92−絶縁膜93−ポリシリコン膜94を含む。このような多層膜は、例えば、浮遊ゲートを有する不揮発性メモリセルに用いられる。つまり、ヒューズ素子81は、不揮発性メモリセルと同じ工程で形成される。従って、特別な工程を必要とせず、工程の増加を抑えてヒューズ素子81を形成することができる。

【0047】

上記のヒューズ素子81は、例えば、図5に示すトリミング回路に用いられる。そして、ヒューズ素子81を用いたトリミング回路が形成された半導体装置の概略断面図を図10に示す。この半導体装置100は、図6に示す半導体装置40と同様に、ドライバトランジスタT1と、ヒューズ素子81と、抵抗R1を含む。ヒューズ素子81は、抵抗R1が形成された素子分離領域103の上に形成されている。

【0048】

素子分離領域103上には第1の導電体104が形成されている。第1の導電体104の側部にはサイドウォール105が形成されている。第1の導電体104上には絶縁膜106が形成され、その絶縁膜106上には第2の導電体107が形成されている。第2の導電体107の側部にはサイドウォール108が形成されている。

【0049】

各素子(バルク)は、カバー膜110により被覆されている。カバー膜110上には層間絶縁膜111が形成されている。その層間絶縁膜111を貫通して第2の導電体107の両端に接続されるプラグ113が形成されている。なお、図10では省略したが、第1の導電体104に接続されるプラグが形成されている。

【0050】

この半導体装置の製造方法を説明する。

図11(a)に示すように、半導体基板101の一主面(上面)に酸化膜121を形成し、酸化膜121上にシリコン窒化膜122を形成する。例えば、温度850℃の条件で半導体基板101を熱酸化して膜厚3nmの酸化膜121を形成する。例えば化学気相成長(CVD)で、温度775℃の条件で膜厚115nmのシリコン窒化膜122を成膜する。次いで、フォトリソグラフィ法により形成したレジストマスクによりシリコン窒化膜122をエッチングし、図11(b)に示すように、素子分離に対応するシリコン窒化膜122aを形成する。

【0051】

次いで、図11(c)に示すように、ウェル領域102を形成する。半導体基板101に、P型の不純物(ドーパント)を導入してウェル領域102を形成する。P型のドーパント不純物は例えばホウ素(ボロン(B))である。イオン注入条件は、例えば、加速電圧を160keV、ドーズ量を1.2×1013cm−2とする。次いで、図11(d)に示すように、例えば、ウェット酸化で、温度1000℃の条件で、膜厚370nmの素子分離領域103を形成する。そして、図11(c)に示すシリコン窒化膜122aを除去する。

【0052】

次いで、図11(e)に示すように、例えば温度1000℃の条件で熱酸化を行い、例えば18.5nmの酸化膜123を形成する。次いで、例えばCVD法により、膜厚300nmの多結晶シリコン膜(ポリシリコン膜)124を成膜する。次いで、図11(f)に示すように、例えばCVD法により、温度750℃の条件で膜厚25nmの酸化膜125を成膜する。次いで、例えばCVD法により、膜厚100nmの多結晶シリコン膜(ポリシリコン膜)126を成膜する。

【0053】

次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜126及び酸化膜125をエッチングし、図12(a)に示すように、第2の導電体107と、対応する絶縁膜106を形成する。次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜124をエッチングし、図12(b)に示すように、ドライバトランジスタT1のゲート配線59と、ヒューズ素子81の第1の導電体104と、抵抗R1を形成する。

【0054】

次いで、図12(c)に示すように、例えばイオン注入法により、ウェル領域102に対してN型の不純物を導入して低濃度のN−拡散領域56a,67aを形成する。次いで、サイドウォール60,64,105,108を形成する。次いで、例えばイオン注入法により、ウェル領域102に対してN型の不純物を導入して高濃度のN+拡散領域56b,57bを形成する。

【0055】

次いで、図12(d)に示すように、ゲート配線59の上部、拡散領域56,57の上部にシリサイド層59a,56c,57cを形成する。次いで、例えばCVD法により、膜厚80nmのカバー膜110を成膜する。次いで、図12(e)に示すように、例えばCVD法により、バルク上に膜厚1400nmの層間絶縁膜111を成膜し、例えば化学機械的研磨(CMP)法により、層間絶縁膜111の表面を平坦化する。

【0056】

以上記述したように、この別の実施形態によれば、上記実施形態の効果に加え、以下の効果を奏する。

(5)ヒューズ素子81は、素子分離領域上に形成された第1の導電体104,絶縁膜106,第2の導電体107を有する。従って、拡散領域やウェル領域を形成する必要がなく、任意の箇所に形成することができる。

【0057】

尚、上記各実施形態は、以下の態様で実施してもよい。

・上記各実施形態において、図9(a)及び図9(b)に示す導電体92,94等の材質を適宜変更してもよい。例えば、導電体92,94のうちの少なくとも一方を金属薄膜抵抗としてもよい。金属薄膜抵抗に用いられる材質は、例えばアルミニウム(Al)、モリブデン(Mo)、ニッケルクロム合金(NiCr)である。

【0058】

また、絶縁領域91を配線層間膜とする。配線層間膜上にヒューズ素子81を形成することができるため、例えばドライバトランジスタT1や抵抗R1の上方にヒューズ素子81を形成することができ、トリミング回路の面積を縮小することができる。従って、ヒューズ素子81を含む半導体装置の面積増大を抑制することができる。

【0059】

・上記各実施形態における接続部25a,94a、拡散領域22、第1の導電体92の形状、大きさ、膜厚、等は一例であり、適宜変更してもよい。

・製造工程において示す温度等の条件は一例であり、適宜変更してもよい。

【0060】

・不純物(ドーパント)を適宜変更してもよい。例えば、N型の不純物として、ヒ素(As)、アンチモン(Sb)等を用いることができる。また、P型の不純物として、アルミニウム(Al)等を用いることができる。

【0061】

・ドライバトランジスタT1をPチャネルMOSトランジスタとしてもよい。

・図4に示す配線31に低電位電圧VSSを供給し、配線32に高電位電圧VDDを供給するようにしてもよい。

【符号の説明】

【0062】

11,81 ヒューズ

22 拡散領域(第1の導電体)

24,61 絶縁膜

25,62 導電体(第2の導電体)

26,65 カバー膜

53 ウェル領域(第1の導電体)

92,104 第1の導電体

93,106 絶縁膜

94,107 第2の導電体

95,110 カバー膜

T1 ドライバトランジスタ

R2 抵抗

【技術分野】

【0001】

ヒューズ、半導体装置、半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体装置は、冗長回路などの設定や、抵抗値などの調整のために、トリミング回路を有している。トリミング回路は、印加する電圧や電流によって導通状態から非導通状態となる、つまり溶断する素子(ヒューズ:Fuse)を含む。このようなトリミング回路の場合、溶断箇所の絶縁距離を十分に確保することが難しく、時間経過によって切断箇所が接続状態に変化する場合がある。このため、別のトリミング回路は、書き込み電圧によって非導通状態から導通状態となる素子(アンチヒューズ:anti−fuse)を含む(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特表2007−536744号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところが、非導通状態から導通状態となる素子は、絶縁膜を挟む2つの導体間に、絶縁膜を破壊する高電圧を印加する必要がある。このようなトリミング回路を含む半導体装置には、高電圧に対応する素子や制御回路が必要となる。このような素子や制御回路は、半導体装置のサイズの増大を招く。

【課題を解決するための手段】

【0005】

本発明の一観点によれば、第1の導電体と、前記第1の導電体の上方にある絶縁膜と、前記絶縁膜の上方にある第2の導電体と、前記第2の導電体の上方にあり、引っ張り応力を有するカバー膜と、前記第1の導電体に接続する第1のプラグと、前記第2の導電体に接続する第2のプラグ及び第3のプラグを有する。

【発明の効果】

【0006】

本発明の一観点によれば、高電圧が不要で安定した状態を得ることができる。

【図面の簡単な説明】

【0007】

【図1】(a)はヒューズ素子の概略平面図、(b)はA−A線断面図、(c)はB−B線断面図である。

【図2】(a),(b)は動作説明図である。

【図3】(a),(b)は動作説明図である。

【図4】トリミング回路の回路図である。

【図5】半導体装置の概略平面図である。

【図6】半導体装置の概略断面図である。

【図7】(a)〜(e)は製造工程の説明図である。

【図8】(a)〜(d)は製造工程の説明図である。

【図9】別のヒューズ素子の(a)概略平面図、(b)断面図である。

【図10】別の半導体装置の概略断面図である。

【図11】(a)〜(f)は製造工程の説明図である。

【図12】(a)〜(e)は製造工程の説明図である。

【発明を実施するための形態】

【0008】

以下、一実施形態を添付図面に従って説明する。尚、添付図面は、構造の概略を説明するためのものであり、実際の大きさを表していない。

図1(a)に示すように、半導体装置10にはヒューズ素子11が形成されている。ヒューズ素子11は、概略的に、拡散領域22と、半導体基板21の厚さ方向(図1(a)において図面の表裏方向)において拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。拡散領域22は、第1の導電体の一例であり、導電体25は第2の導電体の一例である。

【0009】

図1(b)に示すように、半導体装置10の半導体基板21には、例えばN+型の拡散領域22が形成されている。拡散領域22は、平面視長方形状に形成されている。拡散領域22の幅は、例えば1.5μm(マイクロメートル)である。

【0010】

半導体基板21には素子分離領域23が形成されている。この素子分離領域23は、拡散領域22を、半導体基板21に形成された他の素子(図示略)と電気的に分離する。素子分離領域23は、例えば、LOCOS(local oxidation of silicon)やSTI(shallow trench isolation)により形成される。

【0011】

拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24は,例えばシリコン酸化膜(SiO2)である。この絶縁膜24の膜厚は、例えば18nm(ナノメートル)である。

【0012】

絶縁膜24上には、導電体25が形成されている。導電体25は、例えば多結晶シリコン(ポリシリコン:polycrystalline silicon)膜である。導電体25は、所定の方向(図1(b)において左右方向)に沿って延びる長方形状に形成された接続部25aと、接続部25aの両端に矩形状に形成された端子部25b,25cとを有している。接続部25aは例えば、長さが2μm、幅は1.2μm、厚さは400nmである。

【0013】

導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。カバー膜26は、例えばシリコン窒化膜(SiN,Si3N4)である。シリコン窒化膜は、高い引っ張り応力を持つ。例えば、膜厚30nmのシリコン窒化膜(SiN)は、1GPa(ギガパスカル)のテンシル(tensile)応力を持つ。

【0014】

カバー膜26上には層間絶縁膜27が形成されている。層間絶縁膜27は、例えばシリコン酸化膜である。層間絶縁膜27の上面は、平坦状に形成され、図示しない上層の配線を形成し易くしている。図1(c)に示すように、層間絶縁膜27には上面から拡散領域22まで延びるコンタクトホール28aが形成されている。コンタクトホール28a内には、拡散領域22と接続されるプラグ29aが形成されている。同様に、図1(b)に示すように、層間絶縁膜27には上面から導電体25の端子部25b,25cまで延びるコンタクトホール28b,28cが形成されている。コンタクトホール28b,28c内には、導電体25の端子部25b,25cとそれぞれ接続されるプラグ29b,29cが形成されている。プラグ29a〜29cは、例えばタングステン(W)である。

【0015】

上記のように形成されたヒューズ素子11において、導電体25に接続されるプラグ29b,29c間に、プログラムのための電流Ipが供給される。この電流は、100mA(ミリアンペア)〜400mAである。導電体25の接続部25aは、電流Ipにより、例えば1400℃を越えるように発熱し、溶断破壊する。このとき、図3(a)及び図3(b)に示すように、絶縁膜24上に形成された接続部25aは、上方に向って膨張する。しかし、接続部25aは、図1(b)及び図1(c)に示すように、上方及び側方に形成されたカバー膜26により覆われている。このカバー膜26は、高い引っ張り応力を持つ膜である。従って、接続部25aは、図2(a)及び図2(b)に示すように、カバー膜26が形成されていない方向(カバー膜26が開口する方向)、即ち下方に向って膨張する。このように、下方に向って膨張する接続部25aは、絶縁膜24を突き破り、拡散領域22と接続される。即ち、図1(a)に示すプラグ29aとプラグ29b,29cの間は、導電体25(接続部25a)を溶断破壊することにより、接続状態となる。

【0016】

上記のヒューズ素子11は、例えば、図4に示すトリミング回路30に用いられる。

トリミング回路30は、ヒューズ素子11と、ドライバトランジスタT1と、抵抗R1を含む。

【0017】

ヒューズ素子11は、互いに絶縁された第1の電極(拡散領域)22と第2の電極(導電体)25とを含む。第1の電極25は第1の端子11aに接続され、第1の端子11aは出力ノードN1に接続されている。第2の電極25は、第2の端子11bと第3の端子11cとの間に接続されている。第2の端子11bは高電位電圧VDDが供給される配線31に接続され、第3の端子11cはドライバトランジスタT1に接続されている。第1〜第3の端子11a〜11cは、それぞれ図1(a)に示すプラグ29a〜29cに対応する。

【0018】

ドライバトランジスタT1は例えばNチャネルMOSトランジスタである。このドライバトランジスタT1のソースは、低電位電圧VSSが供給される配線32に接続され、ドレインがヒューズ素子11の第3の端子11cに接続され、ゲートにプログラム電圧VPRGが供給される。このドライバトランジスタT1は、上記のヒューズ素子11にプログラム電流Ipを流すように形成されている。例えば、ドライバトランジスタT1のゲート長Lは0.8μm、ゲート幅Wは1400μmである。

【0019】

出力ノードN1は抵抗R1の第1端子に接続され、抵抗R1の第2端子は配線32に接続されている。抵抗R1の抵抗値は例えば1MΩ(メガオーム)である。

トリミング回路30は、初期状態において、ヒューズ素子11の第1の電極11aと第2の電極が非導通状態にある。このとき、出力ノードN1は、抵抗R1によりプルダウンされ、低電位電圧VSSレベル(Lレベル)である。従って、トリミング回路30はLレベルの信号Soを生成する。

【0020】

ヒューズ素子11をプログラムするとき、ドライバトランジスタT1のゲートに、パルス状のプログラム電圧VPRGが供給される。プログラム電圧VPRGのパルス形状は、例えば、振幅が7V(ボルト)であり、パルス幅tWが100μS(マイクロ秒)立ち上がりエッジの遷移時間trが1μSである。

【0021】

ゲートに印加されるプログラム電圧VPRGに基づいてドライバトランジスタT1がオンすると、高電位電圧VDDが供給される配線31からヒューズ素子11とドライバトランジスタT1を介して低電位電圧VSSが供給される配線32に向って電流Ipが流れる。この電流Ipにより、ヒューズ素子11の第1の電極11aが溶断破壊し、第1の電極11aと第2の電極11bが互いに接続する。この結果、出力ノードN1は、高電位電圧VDDレベル(Hレベル)となる。従って、トリミング回路30はHレベルの信号Soを生成する。

【0022】

図5に示すように、半導体装置40には、トリミング回路30に含まれるヒューズ素子11.ドライバトランジスタT1,抵抗R1が形成されている。図中、黒丸はプラグを示す。

【0023】

ドライバトランジスタT1は、ゲート配線41と、ソース領域42と、ドレイン領域43を含む。ゲート配線41は多結晶シリコンにより形成される配線である。ソース領域42及びドレイン領域43は、N型の拡散領域である。抵抗R1は、多結晶シリコンにより形成される。従って、ヒューズ素子11の導電体25を、ドライバトランジスタT1のゲート配線41、抵抗R1と同時に形成することができる。

【0024】

図6は、半導体装置40の断面を示す。なお、説明の便宜上、図6において、ドライバトランジスタT1とヒューズ素子11と抵抗R1を一列に配置して示している。

図6に示すように、半導体基板(シリコン基板)51には、ドライバトランジスタT1に対応するP型のウェル領域52と、ヒューズ素子11に対応するN型のウェル領域53と、抵抗R1に対応するP型のウェル領域54が形成されている。N型のウェル領域53は、第1の導電体の一例である。また、半導体基板51には、素子分離領域55が形成されている。素子分離領域55は、例えば、LOCOS法により形成される。

【0025】

ウェル領域52には、ソース領域56とドレイン領域57が形成されている。ソース領域56とドレイン領域57はそれぞれ、低濃度のN−拡散領域と、高濃度のN+拡散領域を含む。ソース領域56とドレイン領域57にはそれぞれシリサイド層が形成されている。ウェル領域52上にはゲート酸化膜58を介してゲート配線59が形成されている。ゲート配線59は、多結晶シリコン(ポリシリコン)により形成されている。ゲート配線59の上部にはシリサイド層が形成されている。シリサイド層は、例えば、ポリシリコンに高融点金属材料(例えばコバルト(Co))を反応させて形成されている。ゲート配線59の側部にはサイドウォール60が形成されている。サイドウォール60は、例えば、ゲート配線59を覆うように形成したシリコン酸化膜をエッチバックして形成される。

【0026】

ウェル領域53上にはシリコン酸化膜61を介して導電体62が形成されている。導電体62は、両端が、素子分離領域55上まで延びるように形成されている。導電体62は、多結晶シリコン(ポリシリコン)により形成されている。導電体62の側部には、サイドウォール63が形成されている。

【0027】

ウェル領域55に対応する素子分離領域55上には抵抗R1が形成されている。抵抗R1は、多結晶シリコン(ポリシリコン)により形成されている。抵抗R1の側部には、サイドウォール64が形成されている。

【0028】

各素子(バルク)は、カバー膜65により被覆されている。カバー膜65は、引っ張り応力の高い膜、例えばシリコン窒化膜(SiN,Si3N4)である。カバー膜65上には層間絶縁膜66が形成されている。層間絶縁膜66は、例えば、シリコン酸化膜である。層間絶縁膜66の上面は平坦状に形成されている。

【0029】

半導体装置40には、ドライバトランジスタT1のソース領域56とドレイン領域57にそれぞれ接続されるプラグ67が形成されている。また、半導体装置40には、導電体62の両端にそれぞれ接続されるプラグ68が形成されている。なお、図6では省略したが、N型のウェル領域53に接続されるプラグが形成されている。また、半導体装置には、抵抗R1と接続されるプラグ69が形成されている。なお、図6では省略したが、抵抗R1の両端に接続されるプラグが形成されている。各プラグ67〜69は、例えばタングステン(W)である。

【0030】

次に、半導体装置40の製造方法を説明する。

図7(a)に示すように、半導体基板51の一主面(上面)に酸化膜71を形成し、酸化膜71上にシリコン窒化膜72を形成する。例えば、温度850℃の条件で半導体基板51を熱酸化して膜厚3nmの酸化膜71を形成する。例えば化学気相成長(CVD:Chemical Vapor Deposition)で、温度775℃の条件で膜厚115nmのシリコン窒化膜72を成膜する。次いで、フォトリソグラフィ法により形成したレジストマスクによりシリコン窒化膜72をエッチングし、図7(b)に示すように、素子分離に対応するシリコン窒化膜72a,72bを形成する。

【0031】

次いで、図7(c)に示すように、例えばイオン注入法により、ウェル領域52,53,54を形成する。半導体基板51に、N型の不純物(ドーパント:dopant)を導入してウェル領域53を形成する。N型のドーパント不純物は例えばリン(P)である。イオン注入条件は、例えば、加速電圧を180keV、ドーズ量を5.0×1012cm−2とする。また、半導体基板51に、P型の不純物(ドーパント)を導入してウェル領域52,54を形成する。P型のドーパント不純物は例えばホウ素(ボロン(B))である。イオン注入条件は、例えば、加速電圧を160keV、ドーズ量を1.2×1013cm−2とする。

【0032】

次いで、図7(d)に示すように、例えば、ウェット酸化で、温度1000℃の条件で、膜厚370nmの素子分離領域55を形成する。そして、図7(c)に示すシリコン窒化膜72a,72bを除去する。次いで、図7(e)に示すように、例えば温度1000℃の条件で熱酸化を行い、例えば18.5nmの酸化膜61,73を形成する。次いで、例えばCVD法により、膜厚300nmの多結晶シリコン膜(ポリシリコン膜)74を成膜する。

【0033】

次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜74をエッチングし、図8(a)に示すように、ドライバトランジスタT1のゲート配線59と、ヒューズ素子11の導電体62と、抵抗R1を形成する。次いで、図8(b)に示すように、例えばイオン注入法により、ウェル領域52に対してN型の不純物を導入して低濃度のN−拡散領域56a,57aを形成する。次いで、サイドウォール60.63.64を形成する。次いで、例えばイオン注入法により、ウェル領域52に対してN型の不純物を導入して高濃度のN+拡散領域56b,57bを形成する。

【0034】

次いで、図8(c)に示すように、ゲート配線59の上部、拡散領域56,57の上部にシリサイド層59a,56c,57cを形成する。次いで、例えばCVD法により、膜厚80nmのカバー膜65を成膜する。次いで、図8(d)に示すように、例えばCVD法により、バルク上に膜厚1400nmの層間絶縁膜66を成膜し、例えば化学機械的研磨(CMP:Chemical Mechanical Polishing)法により、層間絶縁膜66の表面を平坦化する。そして、カバー膜65をエッチングストッパ膜として層間絶縁膜66をエッチングし、深さが異なるコンタクトホールを形成する。次いで、カバー膜65をエッチングしてシリサイド層56c,57cを露出し、コンタクトホールに例えばCVD法によりタングステンを充填して図6に示すプラグ67〜69を形成する。

【0035】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)ヒューズ素子11は、半導体基板21に形成された拡散領域22と、拡散領域22の上に形成された絶縁膜24と、絶縁膜24上に形成された導電体25を含む。更に、ヒューズ素子11は、導電体25上のカバー膜26を含む。このカバー膜26は、絶縁膜24より高い引っ張り応力を持つ。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。導電体25には、プログラムのための電流Ipが供給される。導電体25は、電流Ipにより発熱し、溶断破壊する。そして、導電体25は、カバー膜26が形成されていない方向(カバー膜26が開口する方向)、即ち下方に向って膨張し、絶縁膜24を破壊する(突き破る)。この結果、導電体25は拡散領域22と接続される。

【0036】

このように、導電体25は供給される電流Ipにより拡散領域22と接続されるため、高電圧を供給する必要がない。そして、高電圧を必要としないため、ヒューズ素子11を含む半導体装置において、プログラムのための回路部分に耐圧を必要としない。従って、半導体装置の面積増大を抑制することができる。

【0037】

(2)ヒューズ素子11は、導電体25と拡散領域22とが短絡することにより、アンチヒューズとして働く。導電体25の両端に接続されるプラグ29b,29c間が電気的に切断されていなくてもよい。従って、切断箇所がストレス等によって短絡することを考慮する必要がなく、継続的に安定した状態を保つことができる。

【0038】

(3)ヒューズ素子11の導電体25はポリシリコンにより形成される。従って、導電体25は、導電体25にプログラムのための電流Ipを流すドライバトランジスタT1のゲート配線59と同様に形成することができるため、特別な製造工程を必要としない。また、導電体25とゲート配線59を1つの工程内で同時に形成することができ、製造工程の増加を抑制することができる。

【0039】

(4)半導体基板51に形成されたバルクを覆うカバー膜65は、カバー膜65の上に形成した層間絶縁膜66にコンタクトホール67〜69を形成する際のエッチングストッパ膜として利用される。従って、ドライバトランジスタT1のソース領域56及びドレイン領域57と接続されるプラグ67、導電体62と接続されるプラグ68,抵抗R1と接続されるプラグ69を確実に形成することができる。また、エッチングストッパ膜を別途形成する必要がなく、工程数の増加を抑制することができる。

【0040】

(別の実施形態)

図9(a)に示すように、半導体装置80にはヒューズ素子81が形成されている。ヒューズ素子81は、概略的に、第1の導電体92と、半導体基板の厚さ方向(図9(a)において図面の表裏方向)において第1の導電体92と一部重なるように第1の導電体92より上方に形成された第2の導電体94を含む。第1の導電体92は、例えば多結晶シリコン(ポリシリコン)膜である。第2の導電体94は、例えば多結晶シリコン膜である。

【0041】

図9(b)に示すように、第1の導電体92は、半導体基板に形成された絶縁領域91の上に形成されている。絶縁領域91は、例えば、LOCOSやSTIである。図9(a)に示すように、第1の導電体92は、直方体状に形成されている。

【0042】

図9(b)に示すように、第1の導電体92上には絶縁膜93が形成されている。絶縁膜93は,例えばシリコン酸化膜(SiO2),多層絶縁膜である。多層絶縁膜は、下層から上層に向って、例えば、シリコン酸化膜(SiO2)、シリコン窒化膜(SiN)、シリコン酸化膜(SiO2)が積層された膜(ONO膜)である。

【0043】

絶縁膜93上には、第2の導電体94が形成されている。導電体94は、所定の方向(図9(b)において左右方向)に沿って延びる長方形状に形成された接続部94aと、接続部94aの両端に矩形状に形成された端子部94b,94cとを有している。

【0044】

導電体94上には、カバー膜95が形成されている。カバー膜95は、半導体基板の主面(上面)側の全面を覆うように形成されている。従って、導電体94は、上面及び側面がカバー膜95により被覆されている。更に、カバー膜95は、第1の導電体92の上面及び側面を被覆するように形成されている。カバー膜95は、絶縁膜93より高い引っ張り応力を持つ。カバー膜95は、例えばシリコン窒化膜(SiN,Si3N4)である。

【0045】

カバー膜95上には層間絶縁膜96が形成されている。層間絶縁膜96は、例えばシリコン酸化膜である。層間絶縁膜96の上面は、平坦状に形成され、図示しない上層の配線を形成し易くしている。図9(b)に示すように、層間絶縁膜96には上面から第1の導電体92まで延びるコンタクトホール97aが形成されている。コンタクトホール97a内には、第1の導電体92と接続されるプラグ98aが形成されている。同様に、図9(b)に示すように、層間絶縁膜96には上面から導電体94の端子部94b,94cまで延びるコンタクトホール97b,97cが形成されている。コンタクトホール97b,97c内には、導電体94の接続部94b.94cとそれぞれ接続されるプラグ98b,98cが形成されている。

【0046】

上記したように、ヒューズ素子81は、半導体基板の厚さ方向に沿って重なるように形成されたポリシリコン膜92−絶縁膜93−ポリシリコン膜94を含む。このような多層膜は、例えば、浮遊ゲートを有する不揮発性メモリセルに用いられる。つまり、ヒューズ素子81は、不揮発性メモリセルと同じ工程で形成される。従って、特別な工程を必要とせず、工程の増加を抑えてヒューズ素子81を形成することができる。

【0047】

上記のヒューズ素子81は、例えば、図5に示すトリミング回路に用いられる。そして、ヒューズ素子81を用いたトリミング回路が形成された半導体装置の概略断面図を図10に示す。この半導体装置100は、図6に示す半導体装置40と同様に、ドライバトランジスタT1と、ヒューズ素子81と、抵抗R1を含む。ヒューズ素子81は、抵抗R1が形成された素子分離領域103の上に形成されている。

【0048】

素子分離領域103上には第1の導電体104が形成されている。第1の導電体104の側部にはサイドウォール105が形成されている。第1の導電体104上には絶縁膜106が形成され、その絶縁膜106上には第2の導電体107が形成されている。第2の導電体107の側部にはサイドウォール108が形成されている。

【0049】

各素子(バルク)は、カバー膜110により被覆されている。カバー膜110上には層間絶縁膜111が形成されている。その層間絶縁膜111を貫通して第2の導電体107の両端に接続されるプラグ113が形成されている。なお、図10では省略したが、第1の導電体104に接続されるプラグが形成されている。

【0050】

この半導体装置の製造方法を説明する。

図11(a)に示すように、半導体基板101の一主面(上面)に酸化膜121を形成し、酸化膜121上にシリコン窒化膜122を形成する。例えば、温度850℃の条件で半導体基板101を熱酸化して膜厚3nmの酸化膜121を形成する。例えば化学気相成長(CVD)で、温度775℃の条件で膜厚115nmのシリコン窒化膜122を成膜する。次いで、フォトリソグラフィ法により形成したレジストマスクによりシリコン窒化膜122をエッチングし、図11(b)に示すように、素子分離に対応するシリコン窒化膜122aを形成する。

【0051】

次いで、図11(c)に示すように、ウェル領域102を形成する。半導体基板101に、P型の不純物(ドーパント)を導入してウェル領域102を形成する。P型のドーパント不純物は例えばホウ素(ボロン(B))である。イオン注入条件は、例えば、加速電圧を160keV、ドーズ量を1.2×1013cm−2とする。次いで、図11(d)に示すように、例えば、ウェット酸化で、温度1000℃の条件で、膜厚370nmの素子分離領域103を形成する。そして、図11(c)に示すシリコン窒化膜122aを除去する。

【0052】

次いで、図11(e)に示すように、例えば温度1000℃の条件で熱酸化を行い、例えば18.5nmの酸化膜123を形成する。次いで、例えばCVD法により、膜厚300nmの多結晶シリコン膜(ポリシリコン膜)124を成膜する。次いで、図11(f)に示すように、例えばCVD法により、温度750℃の条件で膜厚25nmの酸化膜125を成膜する。次いで、例えばCVD法により、膜厚100nmの多結晶シリコン膜(ポリシリコン膜)126を成膜する。

【0053】

次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜126及び酸化膜125をエッチングし、図12(a)に示すように、第2の導電体107と、対応する絶縁膜106を形成する。次いで、フォトリソグラフィ法により形成したレジストマスクを用いてポリシリコン膜124をエッチングし、図12(b)に示すように、ドライバトランジスタT1のゲート配線59と、ヒューズ素子81の第1の導電体104と、抵抗R1を形成する。

【0054】

次いで、図12(c)に示すように、例えばイオン注入法により、ウェル領域102に対してN型の不純物を導入して低濃度のN−拡散領域56a,67aを形成する。次いで、サイドウォール60,64,105,108を形成する。次いで、例えばイオン注入法により、ウェル領域102に対してN型の不純物を導入して高濃度のN+拡散領域56b,57bを形成する。

【0055】

次いで、図12(d)に示すように、ゲート配線59の上部、拡散領域56,57の上部にシリサイド層59a,56c,57cを形成する。次いで、例えばCVD法により、膜厚80nmのカバー膜110を成膜する。次いで、図12(e)に示すように、例えばCVD法により、バルク上に膜厚1400nmの層間絶縁膜111を成膜し、例えば化学機械的研磨(CMP)法により、層間絶縁膜111の表面を平坦化する。

【0056】

以上記述したように、この別の実施形態によれば、上記実施形態の効果に加え、以下の効果を奏する。

(5)ヒューズ素子81は、素子分離領域上に形成された第1の導電体104,絶縁膜106,第2の導電体107を有する。従って、拡散領域やウェル領域を形成する必要がなく、任意の箇所に形成することができる。

【0057】

尚、上記各実施形態は、以下の態様で実施してもよい。

・上記各実施形態において、図9(a)及び図9(b)に示す導電体92,94等の材質を適宜変更してもよい。例えば、導電体92,94のうちの少なくとも一方を金属薄膜抵抗としてもよい。金属薄膜抵抗に用いられる材質は、例えばアルミニウム(Al)、モリブデン(Mo)、ニッケルクロム合金(NiCr)である。

【0058】

また、絶縁領域91を配線層間膜とする。配線層間膜上にヒューズ素子81を形成することができるため、例えばドライバトランジスタT1や抵抗R1の上方にヒューズ素子81を形成することができ、トリミング回路の面積を縮小することができる。従って、ヒューズ素子81を含む半導体装置の面積増大を抑制することができる。

【0059】

・上記各実施形態における接続部25a,94a、拡散領域22、第1の導電体92の形状、大きさ、膜厚、等は一例であり、適宜変更してもよい。

・製造工程において示す温度等の条件は一例であり、適宜変更してもよい。

【0060】

・不純物(ドーパント)を適宜変更してもよい。例えば、N型の不純物として、ヒ素(As)、アンチモン(Sb)等を用いることができる。また、P型の不純物として、アルミニウム(Al)等を用いることができる。

【0061】

・ドライバトランジスタT1をPチャネルMOSトランジスタとしてもよい。

・図4に示す配線31に低電位電圧VSSを供給し、配線32に高電位電圧VDDを供給するようにしてもよい。

【符号の説明】

【0062】

11,81 ヒューズ

22 拡散領域(第1の導電体)

24,61 絶縁膜

25,62 導電体(第2の導電体)

26,65 カバー膜

53 ウェル領域(第1の導電体)

92,104 第1の導電体

93,106 絶縁膜

94,107 第2の導電体

95,110 カバー膜

T1 ドライバトランジスタ

R2 抵抗

【特許請求の範囲】

【請求項1】

第1の導電体と、

前記第1の導電体の上方にある絶縁膜と、

前記絶縁膜の上方にある第2の導電体と、

前記第2の導電体の上方にあり、引っ張り応力を有するカバー膜と、

前記第1の導電体に接続する第1のプラグと、

前記第2の導電体に接続する第2のプラグ及び第3のプラグと

を有するヒューズ。

【請求項2】

前記第2の導電体は、流れるプログラム電流によって前記絶縁膜を破壊し、前記第1の導電体と前記第2の導電体とが短絡される、ことを特徴とする請求項1記載のヒューズ。

【請求項3】

第1の導電体の上方に絶縁膜と第2の導電体がこの順番で形成され、前記第1の導電体の上面及び側面が引っ張り応力を有するカバー膜により被覆され、前記第1の導電体の第1端子が第1電位の第1ノードに接続され、前記第2の導電体は出力ノードに接続されたヒューズと、

前記第1の導電体の第2端子と第2電位の第2ノードとの間に接続され、ゲートに供給されるプログラム電圧に応じて前記第1の導電体にプログラム電流を流すトランジスタと、

前記出力ノードと前記第2ノードとの間に接続された抵抗と、

を含むことを特徴とする半導体装置。

【請求項4】

前記カバー膜はシリコン窒化膜である、ことを特徴とする請求項3記載の半導体装置。

【請求項5】

前記第1の導電体は、半導体基板に形成された拡散領域又はウェル領域であり、

前記第2の導電体は、半導体薄膜又は金属抵抗薄膜である、

ことを特徴とする請求項3又は4記載の半導体装置。

【請求項6】

前記第1の導電体は、素子分離領域の上方に形成された半導体薄膜又は金属抵抗薄膜であり、

前記第2の導電体は、半導体薄膜又は金属抵抗薄膜である、

ことを特徴とする請求項3又は4記載の半導体装置。

【請求項7】

請求項3記載の半導体装置を製造する製造方法であって、

半導体基板の主面にMOS型トランジスタのウェルを形成する工程と、

前記半導体基板の主面にヒューズの第1の導電体を形成する工程と、

前記半導体基板の主面上に絶縁膜を形成する工程と、

前記絶縁膜の上方にポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチングして前記MOS型トランジスタのゲート配線とヒューズ素子の第2の導電体とを形成する工程と、

前記半導体基板のバルク上にカバー膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項8】

前記ポリシリコン膜をエッチングする工程において、素子分離領域上の抵抗を形成する、ことを特徴とする請求項7記載の半導体装置の製造方法。

【請求項9】

請求項3記載の半導体装置を製造する製造方法であって、

半導体基板の主面にMOS型トランジスタのウェルを形成する工程と、

前記半導体基板の主面上に第1の絶縁膜を形成する工程と、

前記絶縁膜の上方に第1のポリシリコン膜を形成する工程と、

前記第1のポリシリコン膜の上方に第2の絶縁膜を形成する工程と、

前記絶縁膜の上方に第2のポリシリコン膜を形成する工程と、

前記第2のポリシリコン膜と前記第2の絶縁膜をエッチングしてヒューズの絶縁体及び第2の導電体を形成する工程と、

前記第1のポリシリコン膜をエッチングして前記MOS型トランジスタのゲート配線と前記ヒューズの第1の導電体を形成する工程と、

前記半導体基板のバルク上にカバー膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項10】

前記第1のポリシリコン膜をエッチングする工程において、素子分離領域上の抵抗を形成する、ことを特徴とする請求項9記載の半導体装置の製造方法。

【請求項1】

第1の導電体と、

前記第1の導電体の上方にある絶縁膜と、

前記絶縁膜の上方にある第2の導電体と、

前記第2の導電体の上方にあり、引っ張り応力を有するカバー膜と、

前記第1の導電体に接続する第1のプラグと、

前記第2の導電体に接続する第2のプラグ及び第3のプラグと

を有するヒューズ。

【請求項2】

前記第2の導電体は、流れるプログラム電流によって前記絶縁膜を破壊し、前記第1の導電体と前記第2の導電体とが短絡される、ことを特徴とする請求項1記載のヒューズ。

【請求項3】

第1の導電体の上方に絶縁膜と第2の導電体がこの順番で形成され、前記第1の導電体の上面及び側面が引っ張り応力を有するカバー膜により被覆され、前記第1の導電体の第1端子が第1電位の第1ノードに接続され、前記第2の導電体は出力ノードに接続されたヒューズと、

前記第1の導電体の第2端子と第2電位の第2ノードとの間に接続され、ゲートに供給されるプログラム電圧に応じて前記第1の導電体にプログラム電流を流すトランジスタと、

前記出力ノードと前記第2ノードとの間に接続された抵抗と、

を含むことを特徴とする半導体装置。

【請求項4】

前記カバー膜はシリコン窒化膜である、ことを特徴とする請求項3記載の半導体装置。

【請求項5】

前記第1の導電体は、半導体基板に形成された拡散領域又はウェル領域であり、

前記第2の導電体は、半導体薄膜又は金属抵抗薄膜である、

ことを特徴とする請求項3又は4記載の半導体装置。

【請求項6】

前記第1の導電体は、素子分離領域の上方に形成された半導体薄膜又は金属抵抗薄膜であり、

前記第2の導電体は、半導体薄膜又は金属抵抗薄膜である、

ことを特徴とする請求項3又は4記載の半導体装置。

【請求項7】

請求項3記載の半導体装置を製造する製造方法であって、

半導体基板の主面にMOS型トランジスタのウェルを形成する工程と、

前記半導体基板の主面にヒューズの第1の導電体を形成する工程と、

前記半導体基板の主面上に絶縁膜を形成する工程と、

前記絶縁膜の上方にポリシリコン膜を形成する工程と、

前記ポリシリコン膜をエッチングして前記MOS型トランジスタのゲート配線とヒューズ素子の第2の導電体とを形成する工程と、

前記半導体基板のバルク上にカバー膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項8】

前記ポリシリコン膜をエッチングする工程において、素子分離領域上の抵抗を形成する、ことを特徴とする請求項7記載の半導体装置の製造方法。

【請求項9】

請求項3記載の半導体装置を製造する製造方法であって、

半導体基板の主面にMOS型トランジスタのウェルを形成する工程と、

前記半導体基板の主面上に第1の絶縁膜を形成する工程と、

前記絶縁膜の上方に第1のポリシリコン膜を形成する工程と、

前記第1のポリシリコン膜の上方に第2の絶縁膜を形成する工程と、

前記絶縁膜の上方に第2のポリシリコン膜を形成する工程と、

前記第2のポリシリコン膜と前記第2の絶縁膜をエッチングしてヒューズの絶縁体及び第2の導電体を形成する工程と、

前記第1のポリシリコン膜をエッチングして前記MOS型トランジスタのゲート配線と前記ヒューズの第1の導電体を形成する工程と、

前記半導体基板のバルク上にカバー膜を形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項10】

前記第1のポリシリコン膜をエッチングする工程において、素子分離領域上の抵抗を形成する、ことを特徴とする請求項9記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−45802(P2013−45802A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−180676(P2011−180676)

【出願日】平成23年8月22日(2011.8.22)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月22日(2011.8.22)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]