ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は埋め込みゲートを有する半導体素子に関し、より詳しくはビットラインコンタクトの外部抵抗を改善するためにビットラインコンタクトと活性領域との接触面積を増加させることができる半導体素子に関する。

【背景技術】

【0002】

半導体素子は、シリコーンウェーハ内の一定領域に不純物を注入するか、新しい物質を蒸着するなどの過程を介し定められた目的に従い動作するように設計される。半導体素子は定められた目的を行うためにトランジスター、キャパシター、抵抗などの多数の素子を含んでおり、それぞれの素子などは導電層を介して連結されデータあるいは信号を取り交わす。

【0003】

半導体素子の製造技術が発展しながら半導体素子の集積度を向上させ、一つのウェーハにより多いチップを形成する努力は続けられて来た。これに伴い、集積度を高めるためにデザイン規則上の最小線幅(minimum feature size)は、ますます小さくなっている。

【0004】

単位セルの大きさが 6F2(F:minimum feature size)である半導体素子の活性領域は、その長軸がビットラインの進行方向と所定角度に傾いた状態で楕円形の形態を有し、ワードラインは半導体基板内に埋め込まれる埋込形ゲート(Buried Gate)の構造を有する。

【0005】

このような 6F2構造の半導体素子でビットラインコンタクトは埋込形ゲートの間の活性領域と接続され、ビットラインはビットラインコンタクトの上部と接続し積層される。

【0006】

ところが、半導体素子の高集積化で単位セルの大きさが減少することになればビットラインコンタクトのサイズも減少することになり、これによる高抵抗性のためセルに正常にデータを書き読みできない問題が発生することになる。

【0007】

したがって、このようなビットラインコンタクトのサイズ減少に伴う高抵抗性問題を解決することのできる方案が求められている実情である。

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は埋め込みゲートを有する半導体素子でビットラインコンタクトの構造を改善し、ビットラインコンタクトの接触面積を確保することができるようにしようとする。

【課題を解決するための手段】

【0009】

本発明の一実施例に係わる半導体素子は、活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触するコンタクトを含む。

【0010】

好ましくは、本発明の半導体素子は前記コンタクトと前記ゲートとの間に位置するシーリング膜をさらに含むことができる。

【0011】

好ましくは、前記コンタクトは前記第1ゲートと前記第2ゲートとの間の活性領域の上部を取り囲むように形成され得る。

【0012】

好ましくは、前記側面は前記第1トレンチと前記第2トレンチの内側面でもあり得、特に前記第1トレンチと前記第2トレンチの内側面のうちビットラインと重畳される領域でもあり得る。

【0013】

本発明の他の実施例に係わる半導体素子は、活性領域内のトレンチ下部に埋め込まれたゲート; 及び前記ゲート両側の前記活性領域の上部面及び側面と接触するコンタクトを含む。このとき、前記側面は前記トレンチの内側面でもあり得る。

【0014】

本発明の一実施例に係わる半導体素子の製造方法は、活性領域を画成する素子分離膜を形成する段階、前記活性領域に第1埋め込みゲートと第2埋め込みゲートを形成する段階、前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域を突出させるコンタクトホールを形成する段階、前記コンタクトホールを埋め込むコンタクト層を形成する段階、前記コンタクト層上部に導電膜を形成する段階、及び前記導電膜及び前記コンタクト層をエッチングしてビットライン及びビットラインコンタクトを形成する段階を含む。

【0015】

好ましくは、前記第1埋め込みゲートと前記第2埋め込みゲートを形成する段階は、前記活性領域をエッチングして第1トレンチ及び第2トレンチを形成する段階、前記第1トレンチと前記第2トレンチの下部にゲート導電膜を形成する段階、及び前記第1トレンチと前記第2トレンチが埋め込まれるように前記ゲート導電膜上部にシーリング膜を形成する段階を含むことができる。

【0016】

好ましくは、前記コンタクトホールを形成する段階は、前記ゲート導電膜と前記シーリング膜を含む活性領域上部に層間絶縁膜を形成する段階、及びビットラインコンタクトマスクを利用して前記層間絶縁膜、前記素子分離膜及び前記シーリング膜をエッチングして前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域の上部面、及び側面を露出させる段階を含むことができる。

【0017】

好ましくは、前記ビットライン及び前記ビットラインコンタクトを形成する段階は、ビットラインマスクを利用して前記導電膜及び前記コンタクト層を順次エッチングする。

【0018】

好ましくは、前記ビットラインコンタクトを形成する段階は、前記コンタクト層が前記活性領域の上部面及び前記第1トレンチと前記第2トレンチの内側面にのみ接触されるように前記コンタクト層をエッチングする。

【0019】

本発明のさらに他の実施例に係わる素子は、活性領域に埋め込まれた第1ワードラインと第2ワードライン、コンタクトを介して前記第1ワードラインと前記第2ワードラインとの間の活性領域と連結されるビットライン、及び前記ワードラインと前記ビットラインに連結されるメモリーセルを含むセルアレイ、及び前記ビットラインに連結され前記セルに格納されたデータをセンシングするセンスアンプを含み、前記コンタクトは第1ワードラインと前記第2ワードラインとの間の前記活性領域の上部面及び側面と接触される。

【0020】

好ましくは、本発明の半導体素子は前記セルアレイでデータがリード又はライトされるセルを選択するための選択信号を出力するローデコーダ、及び前記選択信号により選択されたセルと連結されたセンスアンプを動作させるための駆動信号を出力するカラムデコーダをさらに含むことができる。

【0021】

本発明の一実施例に係わる半導体モジュールは基板に搭載された複数個の半導体素子を有し、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0022】

本発明の一実施例に係わる半導体システムは、基板に搭載された複数個の半導体素子を有する半導体モジュール及び前記半導体モジュールの動作を制御する制御機を含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0023】

本発明の一実施例に係わるコンピューターシステムは、少なくとも一つの半導体モジュールを有する半導体システム及び前記半導体システムに格納されたデータを処理するプロセッサを含み、前記半導体モジュールは基板に搭載された半導体素子などを含み、前記半導体素子は活性領域内の第1メモリートレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0024】

本発明の一実施例に係わるデータプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、前記半導体モジュールは基板に搭載された半導体素子などを含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0025】

本発明の一実施例に係わる電子システムは、少なくとも一つのデータプロセッシングシステムを有し、前記データプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【発明の効果】

【0026】

本発明は、ビットラインコンタクトの構造を改善してビットラインコンタクトの接触面積を確保することによりビットラインコンタクトの高抵抗性フェイルを防止することができる。

【図面の簡単な説明】

【0027】

【図1】本発明に係わる半導体素子のセルアレイ構造を現わす平面図である。

【図2】図 1を Y-Y´及び X-X´方向に切断した断面形態を見せる断面図である。

【図3】図 2の構造を製造する過程を説明するための工程断面図である。

【図4】図 2の構造を製造する過程を説明するための工程断面図である。

【図5】図 2の構造を製造する過程を説明するための工程断面図である。

【図6】図 2の構造を製造する過程を説明するための工程断面図である。

【図7】ビットラインコンタクトマスクの形態を見せる図である。

【図8】図 1のセルアレイ構造が適用された半導体素子の構成を示す図である。

【図9】本発明の一実施例に係わる半導体モジュールの構成を示す図である。

【図10】本発明の一実施例に係わる半導体システムの構成を示す図である。

【図11】本発明の一実施例に係わるコンピューターシステムの構造を現わす図である。

【図12】本発明の一実施例に係わるデータプロセッシングシステムの構成を示す図である。

【図13】本発明の一実施例に係わる電子システムの構成を示す図である。

【発明を実施するための最良の形態】

【0028】

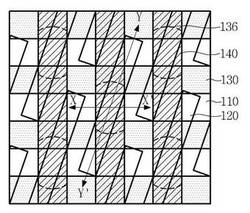

図1は、本発明に係わる半導体素子のセルアレイ構造を示す平面図であり、図 2は、図1を Y-Y´及び X-X´方向に切断した断面形態を見せる断面図である。図 2で (i) 図は、図 1を Y-Y´方向に切断した断面形態を見せる断面図であり、(ii) 図は、図 1を X-X´方向に切断した断面形態を見せる断面図である。

【0029】

半導体基板100上には素子分離膜110により画成された活性領域120が形成される。 各活性領域120は二つのゲート130と交差するように形成され、二つのゲート130により三つの領域に分離される。すなわち、活性領域120は二つのゲート130 の間のビットラインコンタクト領域と二つのゲート130の外側に位置するストレージノードコンタクト領域に分割される。このとき、ゲート130は活性領域120及び素子分離膜110 内に埋め込まれる埋め込みゲート形態に形成され、埋め込みゲート130上部にはシーリング膜132が形成される。ビットラインコンタクト領域及びストレージノードコンタクト領域の活性領域120上部には接合領域が形成される。

【0030】

ビットラインコンタクト領域の活性領域上にはビットラインコンタクト136´が形成され、ビットラインコンタクト136´上には埋め込みゲート130と交差する方向にビットライン140が形成される。ビットライン140は一定の幅のラインタイプに形成され、活性領域120の長軸と斜線方向に 15 〜 20度ほど傾斜して交差するように配置される。すなわち、図 1は 6F2のレイアウトを見せる。

【0031】

特に、本発明でビットラインコンタクト136´は、図 2でのように活性領域の上部を取り囲む形態に形成される。すなわち、ビットラインコンタクト136´は活性領域120の上部面だけでなく、活性領域120の側面とも接触されるように活性領域の上部を取り囲む構造に形成される。

【0032】

このとき、ビットラインコンタクト136はビットライン140と重畳される領域にのみ形成されることにより、隣合う他の活性領域上に形成されるストレージノードコンタクト(図示省略)との間隔を充分確保することができるように形成される。すなわち、本発明はビットラインコンタクト136と活性領域120の接触面積は最大限広く拡張させながら、ビットラインコンタクト136がビットライン140が形成される領域を外れないようにすることにより、隣合う活性領域上に形成されるストレージノードコンタクト(図示省略)との干渉を最小化する。

【0033】

もし、図 2の (iii) 図のようにビットライン140´とハードマストパターン150´の幅をさらに狭く形成する場合、ビットラインコンタクト136″は Y-Y´方向には活性領域120の側面と接触するが、 X-X´方向には活性領域120の側面と接触されないように形成され得る。 このような場合、ビットラインコンタクト136″と活性領域120の接触面積は多少低減することになるが、隣合う活性領域上に形成されるストレージノードコンタクト(図示省略)との干渉をさらに低減することができる。

【0034】

ビットライン140の上部には、ハードマスク層150が形成される。

【0035】

図 3 ないし図 6は、本発明の一実施例に係わり図 1 及び図 2の構造を有する半導体素子を製造する過程を説明するための工程断面図などである。各図で (i) 図は、図 1を Y-Y´方向に切断した断面形態を見せる断面図であり、(ii) 図は、図 1を X-X´方向に切断した断面形態を見せる断面図である。

【0036】

図3を参照すれば、公知されたSTI(Shallow Trench Isolation)工程を進めて基板 100に活性領域120を画成する素子分離膜110を形成する。

【0037】

例えば、半導体基板100上にペッド窒化膜(図示省略)を形成した後、その上部に素子分離領域を画成する感光膜パターン(図示省略)を形成する。次いで、感光膜パターンをエッチングマスクにペッド窒化膜及び半導体基板100をエッチングして素子分離用トレンチ(図示省略)を形成する。このとき、トレンチの形成を容易にするために半導体基板100 とペッド窒化膜との間にはペッド酸化膜をさらに形成することができる。

【0038】

次に、素子分離用トレンチの内側面に酸化膜(wall oxidation、図示省略) 及びライナー窒化膜(liner nitride、図示省略)を形成する。次いで、素子分離用トレンチが埋め込まれるように絶縁膜(図示省略)を形成する。絶縁膜は SOD(Spin On Dielectric)、HDP(High Density Plasma oxide) 及びこれらの組み合わせのうちいずれか一つに形成され得る。次いで、絶縁膜を平坦化(CMP;Chemical Mechanical Polishing)することにより素子分離膜110を形成する。

【0039】

次に、ゲート領域を画成するマスクを利用して素子分離膜110及び活性領域120をエッチングし、一定深さのリセス122を形成する。

【0040】

次に、図 4を参照すれば、リセス122の内側面にゲート絶縁膜124を形成した後、リセス122の下部が埋め込まれるようゲート絶縁膜124上に埋め込みゲート130を形成する。

【0041】

例えば、先ずリセス122が埋め込まれるようゲート絶縁膜124上にゲート導電膜を蒸着する。このとき、ゲート導電膜はチタニウム窒化膜(TiN)、タンタル窒化膜(TaN)、タングステン膜(W) などを含む。例えば、仕事関数の大きいチタニウム窒化膜(又はタンタル窒化膜)をゲート絶縁膜124上にコンフォーマル(Conformal)に薄く蒸着した後、抵抗を低めるためのタングステン膜をギャップフィルしてゲート導電膜を形成することができる。又は、チタニウム窒化膜とタンタル窒化膜を積層するかチタニウム窒化膜、タンタル窒化膜及びタンングステン膜を順次積層してゲート導電膜を形成することができる。

【0042】

次いで、ゲート導電膜に対し平坦化(CMP)及びエッチバック(Etchback)を順次進めてゲート導電膜の上部面が活性領域120の上部面より低くなるようにすることにより埋め込みゲート130を形成する。

【0043】

次いで、埋め込みゲート130上部にシーリング膜132を形成する。このとき、シーリング膜132は窒化膜に形成され得る。

【0044】

次に、図 5を参照すれば素子分離膜110、活性領域120及びシーリング膜132の上部に層間絶縁膜134を形成する。このとき、層間絶縁膜134はTEOS(Tetraethyl orthosilicate) が数百Åの厚さに形成され得る。

【0045】

次に、層間絶縁膜134上に図7のようなビットラインコンタクトマスクを形成した後、これをエッチングマスクに層間絶縁膜134、素子分離膜110及びシーリング膜132を順次エッチングしてビットラインコンタクトホール135を形成する。ビットラインコンタクトホール135が形成される領域は、図 4で円形に表示された領域に該当する。このとき、ビットラインコンタクトホール135の円形断面(水平断面)の直径長さは活性領域120の短縮長さより長く形成される。さらに、ビットラインコンタクトホール135の円形断面(水平断面)の直径長さは、埋め込みゲート130 の間の活性領域の長さより長く形成される。したがって、ビットラインコンタクトホール135の下部には埋め込みゲート130との間の活性領域の上部が一定高さで突出することになる。すなわち、埋め込みゲート130 の間の活性領域の上部面及び側面が露出される。

【0046】

次に、ビットラインコンタクトホール135が埋め込まれるように導電膜(図示省略)を形成した後、層間絶縁膜134が露出されるまで導電膜を平坦化してコンタクト層136を形成する。したがって、コンタクト層136は突出した活性領域120を全体的に取り囲む形態に形成される。すなわち、コンタクト層136は埋め込みゲート130 の間の活性領域120の上部面だけでなく、側面とも接触されることによりビットラインコンタクト136と活性領域120の接触面積が従来に比べ増加することになる。このとき、導電膜はポリで形成されるかバリアメタルと金属膜(W)の積層構造に形成され得る。

【0047】

次に、図6を参照すれば、コンタクト層136を含む層間絶縁膜134の上部にビットライン用導電膜(図示省略) 及びハードマスト層(図示省略)を形成する。このとき、ビットライン用導電膜はバリアメタルと金属膜(W)の積層構造に形成され得る。

【0048】

次に、ビットライン領域を画成するビットラインマスクを利用してハードマスク層、ビットライン用導電膜及びコンタクト層136をエッチングしてハードマスクパターン150、ビットライン140及びビットラインコンタクト136´を形成する。すなわち、コンタクト層136がビットラインマスクによりエッチングされコンタクト層136のうちビットライン140と重畳しない領域が除去される。したがって、ビットラインコンタクト136´は Y-Y´方向の長さはコンタクト層136と同一に維持されるが、 X-X´方向の長さはビットライン140の幅と同一となる。

【0049】

このようなビットラインコンタクト136´は活性領域120の上部を取り囲む形態に形成され、活性領域120との接触面積を増加させながらビットライン140 領域を外れないことにより隣合う活性領域上のストレージノードコンタクト(図示省略)とのマージンを充分確保することになる。

【0050】

このとき、ビットライン140の幅がさらに狭く形成される場合は、図2の (iii) 図でのように Y-Y´方向には活性領域の側面と接触できるが X-X´方向には活性領域の側面と接触されないビットラインコンタクト136″を形成することができる。

【0051】

以後、ビットラインコンタクト136´、ビットライン140及びハードマスクパターン150を覆う層間絶縁膜(図示省略)を形成した後ストレージノードコンタクト(図示省略)、 及びキャパシターのようなデータ格納手段(図示省略)が形成される。このような後続工程は、従来の工程と同一になされ得るので本実施例ではこのような後続工程に対する説明は略する。このとき、データ格納手段は半導体素子の種類に従い異なり得る。例えば、上述したビットラインコンタクト構造が DRAM(Dynamic Random Access Memory)に適用される場合はデータ格納手段としてキャパシターになることができ、FeRAM(Ferroelectric RAM)に適用される場合はキャパシター物質として強誘電体物質が使用され得る。そして、上述したビットラインコンタクト構造が MRAM(Magnetic RAM)に適用される場合はデータ格納手段としてMTJ(Magnetic Tunnel Junction)になることができ、PRAM(Phase Change RAM)又はReRAM (Resistance RAM)に適用される場合はデータ格納手段に相変換物質が使用され得る。

【0052】

図8は、図1のセルアレイ構造が適用された半導体素子の構成を現わす図である。

【0053】

半導体素子500はセルアレイ(Memory Cell Array)510、センスアンプ (Sense Amplifier)520、ローデコーダ(Row Decorder)530及びカラムデコーダ (Column Decorder)540を含むことができる。

【0054】

セルアレイ510は、ワードライン(埋め込みゲート)130及びビットライン140に連結されマトリックス形態に配列された多数のメモリーセル512を含む。このとき、各メモリーセル512及びメモリーセル512とビットライン140を連結するビットラインコンタクトは図 1 及び図 2と同一構造を有する。

【0055】

センスアンプ520は、ビットライン140と連結されセルアレイ610のメモリーセル512に格納されたデータを感知及び増幅する。

【0056】

ローデコーダ530は、データがリード又はライトされるメモリーセル512を選択するためのワードライン選択信号を発生させてワードライン130に印加する。

【0057】

カラムデコーダ540は、ローデコーダ530により選択されたセル512と連結されたセンスアンプ620を動作させるための駆動信号を発生させセンスアンプ620に出力する。

【0058】

センスアンプ520及びデコーダなど530、540は、通常の半導体素子に使用されるものであって、これらに対する具体的な構造及び動作説明は略する。

【0059】

このような半導体素子は、コンピューティングメモリー(Computing Memory、 例えば、DRAM、SRAM、DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM)、コンシューマー メモリー(Consumer Memory、例えば、DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM、SDR SDRAM)、グラフィックメモリー(Graphics Memory、例えば、DDR3 SDRAM、GDDR3 SDMRA、GDDR4 SDRAM、GDDR5 SDRAM)、モバイルメモリー(Mobile Memory、 例 え ば、Mobile SDR、Mobile DDR、Mobile DDR2、MCP(Multi Chip Package)、PoP(Package on Package)、PSRAM、LPDDR)、NAND フラッシュ、MRAM (Magnetic RAM)、FeRAM (Ferroelectric RAM)、PRAM(Phase Change RAM)、 ReRAM (Resistance RAM)、 SGRAM (Synchronous Graphics RAM) などに使用され得る。

【0060】

図9は、本発明の一実施例に係わる半導体モジュールの構成を現わす図である。

【0061】

半導体モジュール600は、モジュール基板610上に搭載された複数個の半導体素子620、半導体素子620が外部の制御機(図示省略)から制御信号(アドレス信号(ADDR)、コマンド信号(CMD)、クロック信号(CLK))の提供を受けることができるようにするコマンドリンク630及び半導体素子620と連結され入出力されるデータを送信するデータリンク640を含む。

【0062】

このとき、半導体素子620は、例えば図 8に対する説明で例示された半導体素子500等が使用され得る。モジュール基板610に搭載された半導体素子620は、図 1 及び図2で説明されたところのようにビットラインコンタクトが活性領域の上部面及び側面を取り囲む構造を含む。コマンドリンク630及びデータリンク640は、通常の半導体モジュールで使用されるものなどと同一又は類似に形成され得る。

【0063】

図9では、モジュール基板610の前面に8個の半導体素子620が搭載されている形態が示されているが、モジュール基板610の後面にも同一に半導体素子620等が搭載され得る。すなわち、モジュール基板610の一側又は両側に半導体素子620等が搭載されることができ、搭載される半導体素子620の数は図 9に限定されない。さらに、モジュール基板610の材料及び構造も特に制限されない。

【0064】

図10は、本発明の一実施例に係わる半導体システムの構成を現わす図である。

【0065】

半導体システム700は、複数個の半導体素子712が搭載された少なくとも一つの半導体モジュール710、及び半導体モジュール710と外部のシステム(図示省略)との間で両方向インターフェースを提供して半導体モジュール710の動作を制御する制御機720を含む。

【0066】

このような制御機720は、通常のデータプロセッシングシステムで複数の半導体モジュールの動作を制御するための制御機とその機能が同一、又は類似に形成され得る。したがって、本実施例ではこれに対する詳細な説明は略する。

【0067】

このとき、半導体モジュール710は、例えば図6に例示された半導体モジュール600が使用され得る。

【0068】

図 11は、本発明の一実施例に係わるコンピューターシステムの構造を現わす図である。

【0069】

コンピューターシステム800は、半導体システム810及びプロセッサ(CPU)820を含む。

【0070】

半導体システム810は、コンピューターシステム800の動作を制御するために要するデータを格納する。このとき、半導体システム810は、例えば図 7に例示された半導体システム700が使用され得る。

【0071】

プロセッサ820は、半導体システム810に格納されたデータを処理してコンピューターシステム800の動作を制御する。このようなプロセッサ820は、通常のコンピューターシステムに使用される中央処理装置とその機能が同一又は類似に形成され得る。

【0072】

コンピューターシステム800はモニター832、キーボード834、プリンター836、マウス838などのユーザーインターフェース装置などを含むことができる。

【0073】

図12は、本発明の一実施例に係わるデータプロセッシングシステムの構成を現わす図である。

【0074】

データプロセッシングシステム900は、電子システム(図示省略)に備えられ電子システムの幾多の機能などのうち特定機能を行なう。

【0075】

このようなデータプロセッシングシステム900は、基板に搭載された少なくとも一つの半導体素子910を含む。

【0076】

半導体素子910は、電子システムの特定機能を行うために要するデータが格納されるセルアレイ(図示省略)、及びセルアレイに格納されたデータを処理して当該特定機能が行われるように制御するプロセッサ(図示省略)を含む。すなわち、半導体素子910は一つの単位素子(die 又はチップ)にデータを格納するための手段と、その格納されたデータを処理して電子システムの特定機能を行うための手段とを全て含む。

【0077】

このとき、セルアレイは上述した図8のセルアレイ510が使用され得る。

【0078】

データプロセッシングシステム900は、リード等(leads)920を介して電子システムの他の構成要素(例えば、CPU)と連結され、単方向又は両方向にデータ及び制御信号を取り交わすことができる。

【0079】

図13は、本発明の一実施例に係わる電子システムの構成を現わす図である。

【0080】

電子システム1000は、少なくとも一つのデータプロセッシングシステム1010及びユーザーインターフェース1020を含む。

【0081】

データプロセッシングシステム1010は、電子システム1000の幾多の機能などのうち特定機能を行い、基板に搭載された少なくとも一つの半導体素子を含む。 そして、半導体素子は電子システム1000の特定機能を行うために要するデータが格納されるセルアレイ(図示省略)、 及びセルアレイに格納されたデータを処理して当該機能を制御するプロセッサ(図示省略)を含む。このとき、セルアレイは上述した図 8のセルアレイ510が使用され得る。

【0082】

ユーザーインターフェース1020は、使用者と回路モジュール1010との間のインターフェースを提供する。 ユーザーインターフェース1020は、電子装置に一体形に設けられたキーパッド、タッチスクリーン、スピーカーなどを含む。

【0083】

このような電子装置1000はコンピューター、家電製品、工場自動化システム、エレベータ、携帯電話など各種の電子・情報・通信機器に備えられたエンベデッドシステム(embedded system)を含む。

【0084】

上述した本発明の好ましい実施例は例示の目的のためのもので、当業者であれば添付された特許請求範囲の技術的思想と範囲を介して多様な修正、変更、代替及び付加が可能なはずであり、このような修正変更などは以下の特許請求範囲に属するものと見なければならないはずである。

【技術分野】

【0001】

本発明は埋め込みゲートを有する半導体素子に関し、より詳しくはビットラインコンタクトの外部抵抗を改善するためにビットラインコンタクトと活性領域との接触面積を増加させることができる半導体素子に関する。

【背景技術】

【0002】

半導体素子は、シリコーンウェーハ内の一定領域に不純物を注入するか、新しい物質を蒸着するなどの過程を介し定められた目的に従い動作するように設計される。半導体素子は定められた目的を行うためにトランジスター、キャパシター、抵抗などの多数の素子を含んでおり、それぞれの素子などは導電層を介して連結されデータあるいは信号を取り交わす。

【0003】

半導体素子の製造技術が発展しながら半導体素子の集積度を向上させ、一つのウェーハにより多いチップを形成する努力は続けられて来た。これに伴い、集積度を高めるためにデザイン規則上の最小線幅(minimum feature size)は、ますます小さくなっている。

【0004】

単位セルの大きさが 6F2(F:minimum feature size)である半導体素子の活性領域は、その長軸がビットラインの進行方向と所定角度に傾いた状態で楕円形の形態を有し、ワードラインは半導体基板内に埋め込まれる埋込形ゲート(Buried Gate)の構造を有する。

【0005】

このような 6F2構造の半導体素子でビットラインコンタクトは埋込形ゲートの間の活性領域と接続され、ビットラインはビットラインコンタクトの上部と接続し積層される。

【0006】

ところが、半導体素子の高集積化で単位セルの大きさが減少することになればビットラインコンタクトのサイズも減少することになり、これによる高抵抗性のためセルに正常にデータを書き読みできない問題が発生することになる。

【0007】

したがって、このようなビットラインコンタクトのサイズ減少に伴う高抵抗性問題を解決することのできる方案が求められている実情である。

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明は埋め込みゲートを有する半導体素子でビットラインコンタクトの構造を改善し、ビットラインコンタクトの接触面積を確保することができるようにしようとする。

【課題を解決するための手段】

【0009】

本発明の一実施例に係わる半導体素子は、活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触するコンタクトを含む。

【0010】

好ましくは、本発明の半導体素子は前記コンタクトと前記ゲートとの間に位置するシーリング膜をさらに含むことができる。

【0011】

好ましくは、前記コンタクトは前記第1ゲートと前記第2ゲートとの間の活性領域の上部を取り囲むように形成され得る。

【0012】

好ましくは、前記側面は前記第1トレンチと前記第2トレンチの内側面でもあり得、特に前記第1トレンチと前記第2トレンチの内側面のうちビットラインと重畳される領域でもあり得る。

【0013】

本発明の他の実施例に係わる半導体素子は、活性領域内のトレンチ下部に埋め込まれたゲート; 及び前記ゲート両側の前記活性領域の上部面及び側面と接触するコンタクトを含む。このとき、前記側面は前記トレンチの内側面でもあり得る。

【0014】

本発明の一実施例に係わる半導体素子の製造方法は、活性領域を画成する素子分離膜を形成する段階、前記活性領域に第1埋め込みゲートと第2埋め込みゲートを形成する段階、前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域を突出させるコンタクトホールを形成する段階、前記コンタクトホールを埋め込むコンタクト層を形成する段階、前記コンタクト層上部に導電膜を形成する段階、及び前記導電膜及び前記コンタクト層をエッチングしてビットライン及びビットラインコンタクトを形成する段階を含む。

【0015】

好ましくは、前記第1埋め込みゲートと前記第2埋め込みゲートを形成する段階は、前記活性領域をエッチングして第1トレンチ及び第2トレンチを形成する段階、前記第1トレンチと前記第2トレンチの下部にゲート導電膜を形成する段階、及び前記第1トレンチと前記第2トレンチが埋め込まれるように前記ゲート導電膜上部にシーリング膜を形成する段階を含むことができる。

【0016】

好ましくは、前記コンタクトホールを形成する段階は、前記ゲート導電膜と前記シーリング膜を含む活性領域上部に層間絶縁膜を形成する段階、及びビットラインコンタクトマスクを利用して前記層間絶縁膜、前記素子分離膜及び前記シーリング膜をエッチングして前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域の上部面、及び側面を露出させる段階を含むことができる。

【0017】

好ましくは、前記ビットライン及び前記ビットラインコンタクトを形成する段階は、ビットラインマスクを利用して前記導電膜及び前記コンタクト層を順次エッチングする。

【0018】

好ましくは、前記ビットラインコンタクトを形成する段階は、前記コンタクト層が前記活性領域の上部面及び前記第1トレンチと前記第2トレンチの内側面にのみ接触されるように前記コンタクト層をエッチングする。

【0019】

本発明のさらに他の実施例に係わる素子は、活性領域に埋め込まれた第1ワードラインと第2ワードライン、コンタクトを介して前記第1ワードラインと前記第2ワードラインとの間の活性領域と連結されるビットライン、及び前記ワードラインと前記ビットラインに連結されるメモリーセルを含むセルアレイ、及び前記ビットラインに連結され前記セルに格納されたデータをセンシングするセンスアンプを含み、前記コンタクトは第1ワードラインと前記第2ワードラインとの間の前記活性領域の上部面及び側面と接触される。

【0020】

好ましくは、本発明の半導体素子は前記セルアレイでデータがリード又はライトされるセルを選択するための選択信号を出力するローデコーダ、及び前記選択信号により選択されたセルと連結されたセンスアンプを動作させるための駆動信号を出力するカラムデコーダをさらに含むことができる。

【0021】

本発明の一実施例に係わる半導体モジュールは基板に搭載された複数個の半導体素子を有し、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0022】

本発明の一実施例に係わる半導体システムは、基板に搭載された複数個の半導体素子を有する半導体モジュール及び前記半導体モジュールの動作を制御する制御機を含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0023】

本発明の一実施例に係わるコンピューターシステムは、少なくとも一つの半導体モジュールを有する半導体システム及び前記半導体システムに格納されたデータを処理するプロセッサを含み、前記半導体モジュールは基板に搭載された半導体素子などを含み、前記半導体素子は活性領域内の第1メモリートレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0024】

本発明の一実施例に係わるデータプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、前記半導体モジュールは基板に搭載された半導体素子などを含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【0025】

本発明の一実施例に係わる電子システムは、少なくとも一つのデータプロセッシングシステムを有し、前記データプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、前記半導体素子は活性領域内の第1トレンチ下部に埋め込まれた第1ゲート、前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート及び前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含む。

【発明の効果】

【0026】

本発明は、ビットラインコンタクトの構造を改善してビットラインコンタクトの接触面積を確保することによりビットラインコンタクトの高抵抗性フェイルを防止することができる。

【図面の簡単な説明】

【0027】

【図1】本発明に係わる半導体素子のセルアレイ構造を現わす平面図である。

【図2】図 1を Y-Y´及び X-X´方向に切断した断面形態を見せる断面図である。

【図3】図 2の構造を製造する過程を説明するための工程断面図である。

【図4】図 2の構造を製造する過程を説明するための工程断面図である。

【図5】図 2の構造を製造する過程を説明するための工程断面図である。

【図6】図 2の構造を製造する過程を説明するための工程断面図である。

【図7】ビットラインコンタクトマスクの形態を見せる図である。

【図8】図 1のセルアレイ構造が適用された半導体素子の構成を示す図である。

【図9】本発明の一実施例に係わる半導体モジュールの構成を示す図である。

【図10】本発明の一実施例に係わる半導体システムの構成を示す図である。

【図11】本発明の一実施例に係わるコンピューターシステムの構造を現わす図である。

【図12】本発明の一実施例に係わるデータプロセッシングシステムの構成を示す図である。

【図13】本発明の一実施例に係わる電子システムの構成を示す図である。

【発明を実施するための最良の形態】

【0028】

図1は、本発明に係わる半導体素子のセルアレイ構造を示す平面図であり、図 2は、図1を Y-Y´及び X-X´方向に切断した断面形態を見せる断面図である。図 2で (i) 図は、図 1を Y-Y´方向に切断した断面形態を見せる断面図であり、(ii) 図は、図 1を X-X´方向に切断した断面形態を見せる断面図である。

【0029】

半導体基板100上には素子分離膜110により画成された活性領域120が形成される。 各活性領域120は二つのゲート130と交差するように形成され、二つのゲート130により三つの領域に分離される。すなわち、活性領域120は二つのゲート130 の間のビットラインコンタクト領域と二つのゲート130の外側に位置するストレージノードコンタクト領域に分割される。このとき、ゲート130は活性領域120及び素子分離膜110 内に埋め込まれる埋め込みゲート形態に形成され、埋め込みゲート130上部にはシーリング膜132が形成される。ビットラインコンタクト領域及びストレージノードコンタクト領域の活性領域120上部には接合領域が形成される。

【0030】

ビットラインコンタクト領域の活性領域上にはビットラインコンタクト136´が形成され、ビットラインコンタクト136´上には埋め込みゲート130と交差する方向にビットライン140が形成される。ビットライン140は一定の幅のラインタイプに形成され、活性領域120の長軸と斜線方向に 15 〜 20度ほど傾斜して交差するように配置される。すなわち、図 1は 6F2のレイアウトを見せる。

【0031】

特に、本発明でビットラインコンタクト136´は、図 2でのように活性領域の上部を取り囲む形態に形成される。すなわち、ビットラインコンタクト136´は活性領域120の上部面だけでなく、活性領域120の側面とも接触されるように活性領域の上部を取り囲む構造に形成される。

【0032】

このとき、ビットラインコンタクト136はビットライン140と重畳される領域にのみ形成されることにより、隣合う他の活性領域上に形成されるストレージノードコンタクト(図示省略)との間隔を充分確保することができるように形成される。すなわち、本発明はビットラインコンタクト136と活性領域120の接触面積は最大限広く拡張させながら、ビットラインコンタクト136がビットライン140が形成される領域を外れないようにすることにより、隣合う活性領域上に形成されるストレージノードコンタクト(図示省略)との干渉を最小化する。

【0033】

もし、図 2の (iii) 図のようにビットライン140´とハードマストパターン150´の幅をさらに狭く形成する場合、ビットラインコンタクト136″は Y-Y´方向には活性領域120の側面と接触するが、 X-X´方向には活性領域120の側面と接触されないように形成され得る。 このような場合、ビットラインコンタクト136″と活性領域120の接触面積は多少低減することになるが、隣合う活性領域上に形成されるストレージノードコンタクト(図示省略)との干渉をさらに低減することができる。

【0034】

ビットライン140の上部には、ハードマスク層150が形成される。

【0035】

図 3 ないし図 6は、本発明の一実施例に係わり図 1 及び図 2の構造を有する半導体素子を製造する過程を説明するための工程断面図などである。各図で (i) 図は、図 1を Y-Y´方向に切断した断面形態を見せる断面図であり、(ii) 図は、図 1を X-X´方向に切断した断面形態を見せる断面図である。

【0036】

図3を参照すれば、公知されたSTI(Shallow Trench Isolation)工程を進めて基板 100に活性領域120を画成する素子分離膜110を形成する。

【0037】

例えば、半導体基板100上にペッド窒化膜(図示省略)を形成した後、その上部に素子分離領域を画成する感光膜パターン(図示省略)を形成する。次いで、感光膜パターンをエッチングマスクにペッド窒化膜及び半導体基板100をエッチングして素子分離用トレンチ(図示省略)を形成する。このとき、トレンチの形成を容易にするために半導体基板100 とペッド窒化膜との間にはペッド酸化膜をさらに形成することができる。

【0038】

次に、素子分離用トレンチの内側面に酸化膜(wall oxidation、図示省略) 及びライナー窒化膜(liner nitride、図示省略)を形成する。次いで、素子分離用トレンチが埋め込まれるように絶縁膜(図示省略)を形成する。絶縁膜は SOD(Spin On Dielectric)、HDP(High Density Plasma oxide) 及びこれらの組み合わせのうちいずれか一つに形成され得る。次いで、絶縁膜を平坦化(CMP;Chemical Mechanical Polishing)することにより素子分離膜110を形成する。

【0039】

次に、ゲート領域を画成するマスクを利用して素子分離膜110及び活性領域120をエッチングし、一定深さのリセス122を形成する。

【0040】

次に、図 4を参照すれば、リセス122の内側面にゲート絶縁膜124を形成した後、リセス122の下部が埋め込まれるようゲート絶縁膜124上に埋め込みゲート130を形成する。

【0041】

例えば、先ずリセス122が埋め込まれるようゲート絶縁膜124上にゲート導電膜を蒸着する。このとき、ゲート導電膜はチタニウム窒化膜(TiN)、タンタル窒化膜(TaN)、タングステン膜(W) などを含む。例えば、仕事関数の大きいチタニウム窒化膜(又はタンタル窒化膜)をゲート絶縁膜124上にコンフォーマル(Conformal)に薄く蒸着した後、抵抗を低めるためのタングステン膜をギャップフィルしてゲート導電膜を形成することができる。又は、チタニウム窒化膜とタンタル窒化膜を積層するかチタニウム窒化膜、タンタル窒化膜及びタンングステン膜を順次積層してゲート導電膜を形成することができる。

【0042】

次いで、ゲート導電膜に対し平坦化(CMP)及びエッチバック(Etchback)を順次進めてゲート導電膜の上部面が活性領域120の上部面より低くなるようにすることにより埋め込みゲート130を形成する。

【0043】

次いで、埋め込みゲート130上部にシーリング膜132を形成する。このとき、シーリング膜132は窒化膜に形成され得る。

【0044】

次に、図 5を参照すれば素子分離膜110、活性領域120及びシーリング膜132の上部に層間絶縁膜134を形成する。このとき、層間絶縁膜134はTEOS(Tetraethyl orthosilicate) が数百Åの厚さに形成され得る。

【0045】

次に、層間絶縁膜134上に図7のようなビットラインコンタクトマスクを形成した後、これをエッチングマスクに層間絶縁膜134、素子分離膜110及びシーリング膜132を順次エッチングしてビットラインコンタクトホール135を形成する。ビットラインコンタクトホール135が形成される領域は、図 4で円形に表示された領域に該当する。このとき、ビットラインコンタクトホール135の円形断面(水平断面)の直径長さは活性領域120の短縮長さより長く形成される。さらに、ビットラインコンタクトホール135の円形断面(水平断面)の直径長さは、埋め込みゲート130 の間の活性領域の長さより長く形成される。したがって、ビットラインコンタクトホール135の下部には埋め込みゲート130との間の活性領域の上部が一定高さで突出することになる。すなわち、埋め込みゲート130 の間の活性領域の上部面及び側面が露出される。

【0046】

次に、ビットラインコンタクトホール135が埋め込まれるように導電膜(図示省略)を形成した後、層間絶縁膜134が露出されるまで導電膜を平坦化してコンタクト層136を形成する。したがって、コンタクト層136は突出した活性領域120を全体的に取り囲む形態に形成される。すなわち、コンタクト層136は埋め込みゲート130 の間の活性領域120の上部面だけでなく、側面とも接触されることによりビットラインコンタクト136と活性領域120の接触面積が従来に比べ増加することになる。このとき、導電膜はポリで形成されるかバリアメタルと金属膜(W)の積層構造に形成され得る。

【0047】

次に、図6を参照すれば、コンタクト層136を含む層間絶縁膜134の上部にビットライン用導電膜(図示省略) 及びハードマスト層(図示省略)を形成する。このとき、ビットライン用導電膜はバリアメタルと金属膜(W)の積層構造に形成され得る。

【0048】

次に、ビットライン領域を画成するビットラインマスクを利用してハードマスク層、ビットライン用導電膜及びコンタクト層136をエッチングしてハードマスクパターン150、ビットライン140及びビットラインコンタクト136´を形成する。すなわち、コンタクト層136がビットラインマスクによりエッチングされコンタクト層136のうちビットライン140と重畳しない領域が除去される。したがって、ビットラインコンタクト136´は Y-Y´方向の長さはコンタクト層136と同一に維持されるが、 X-X´方向の長さはビットライン140の幅と同一となる。

【0049】

このようなビットラインコンタクト136´は活性領域120の上部を取り囲む形態に形成され、活性領域120との接触面積を増加させながらビットライン140 領域を外れないことにより隣合う活性領域上のストレージノードコンタクト(図示省略)とのマージンを充分確保することになる。

【0050】

このとき、ビットライン140の幅がさらに狭く形成される場合は、図2の (iii) 図でのように Y-Y´方向には活性領域の側面と接触できるが X-X´方向には活性領域の側面と接触されないビットラインコンタクト136″を形成することができる。

【0051】

以後、ビットラインコンタクト136´、ビットライン140及びハードマスクパターン150を覆う層間絶縁膜(図示省略)を形成した後ストレージノードコンタクト(図示省略)、 及びキャパシターのようなデータ格納手段(図示省略)が形成される。このような後続工程は、従来の工程と同一になされ得るので本実施例ではこのような後続工程に対する説明は略する。このとき、データ格納手段は半導体素子の種類に従い異なり得る。例えば、上述したビットラインコンタクト構造が DRAM(Dynamic Random Access Memory)に適用される場合はデータ格納手段としてキャパシターになることができ、FeRAM(Ferroelectric RAM)に適用される場合はキャパシター物質として強誘電体物質が使用され得る。そして、上述したビットラインコンタクト構造が MRAM(Magnetic RAM)に適用される場合はデータ格納手段としてMTJ(Magnetic Tunnel Junction)になることができ、PRAM(Phase Change RAM)又はReRAM (Resistance RAM)に適用される場合はデータ格納手段に相変換物質が使用され得る。

【0052】

図8は、図1のセルアレイ構造が適用された半導体素子の構成を現わす図である。

【0053】

半導体素子500はセルアレイ(Memory Cell Array)510、センスアンプ (Sense Amplifier)520、ローデコーダ(Row Decorder)530及びカラムデコーダ (Column Decorder)540を含むことができる。

【0054】

セルアレイ510は、ワードライン(埋め込みゲート)130及びビットライン140に連結されマトリックス形態に配列された多数のメモリーセル512を含む。このとき、各メモリーセル512及びメモリーセル512とビットライン140を連結するビットラインコンタクトは図 1 及び図 2と同一構造を有する。

【0055】

センスアンプ520は、ビットライン140と連結されセルアレイ610のメモリーセル512に格納されたデータを感知及び増幅する。

【0056】

ローデコーダ530は、データがリード又はライトされるメモリーセル512を選択するためのワードライン選択信号を発生させてワードライン130に印加する。

【0057】

カラムデコーダ540は、ローデコーダ530により選択されたセル512と連結されたセンスアンプ620を動作させるための駆動信号を発生させセンスアンプ620に出力する。

【0058】

センスアンプ520及びデコーダなど530、540は、通常の半導体素子に使用されるものであって、これらに対する具体的な構造及び動作説明は略する。

【0059】

このような半導体素子は、コンピューティングメモリー(Computing Memory、 例えば、DRAM、SRAM、DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM)、コンシューマー メモリー(Consumer Memory、例えば、DDR3 SDRAM、DDR2 SDRAM、DDR SDRAM、SDR SDRAM)、グラフィックメモリー(Graphics Memory、例えば、DDR3 SDRAM、GDDR3 SDMRA、GDDR4 SDRAM、GDDR5 SDRAM)、モバイルメモリー(Mobile Memory、 例 え ば、Mobile SDR、Mobile DDR、Mobile DDR2、MCP(Multi Chip Package)、PoP(Package on Package)、PSRAM、LPDDR)、NAND フラッシュ、MRAM (Magnetic RAM)、FeRAM (Ferroelectric RAM)、PRAM(Phase Change RAM)、 ReRAM (Resistance RAM)、 SGRAM (Synchronous Graphics RAM) などに使用され得る。

【0060】

図9は、本発明の一実施例に係わる半導体モジュールの構成を現わす図である。

【0061】

半導体モジュール600は、モジュール基板610上に搭載された複数個の半導体素子620、半導体素子620が外部の制御機(図示省略)から制御信号(アドレス信号(ADDR)、コマンド信号(CMD)、クロック信号(CLK))の提供を受けることができるようにするコマンドリンク630及び半導体素子620と連結され入出力されるデータを送信するデータリンク640を含む。

【0062】

このとき、半導体素子620は、例えば図 8に対する説明で例示された半導体素子500等が使用され得る。モジュール基板610に搭載された半導体素子620は、図 1 及び図2で説明されたところのようにビットラインコンタクトが活性領域の上部面及び側面を取り囲む構造を含む。コマンドリンク630及びデータリンク640は、通常の半導体モジュールで使用されるものなどと同一又は類似に形成され得る。

【0063】

図9では、モジュール基板610の前面に8個の半導体素子620が搭載されている形態が示されているが、モジュール基板610の後面にも同一に半導体素子620等が搭載され得る。すなわち、モジュール基板610の一側又は両側に半導体素子620等が搭載されることができ、搭載される半導体素子620の数は図 9に限定されない。さらに、モジュール基板610の材料及び構造も特に制限されない。

【0064】

図10は、本発明の一実施例に係わる半導体システムの構成を現わす図である。

【0065】

半導体システム700は、複数個の半導体素子712が搭載された少なくとも一つの半導体モジュール710、及び半導体モジュール710と外部のシステム(図示省略)との間で両方向インターフェースを提供して半導体モジュール710の動作を制御する制御機720を含む。

【0066】

このような制御機720は、通常のデータプロセッシングシステムで複数の半導体モジュールの動作を制御するための制御機とその機能が同一、又は類似に形成され得る。したがって、本実施例ではこれに対する詳細な説明は略する。

【0067】

このとき、半導体モジュール710は、例えば図6に例示された半導体モジュール600が使用され得る。

【0068】

図 11は、本発明の一実施例に係わるコンピューターシステムの構造を現わす図である。

【0069】

コンピューターシステム800は、半導体システム810及びプロセッサ(CPU)820を含む。

【0070】

半導体システム810は、コンピューターシステム800の動作を制御するために要するデータを格納する。このとき、半導体システム810は、例えば図 7に例示された半導体システム700が使用され得る。

【0071】

プロセッサ820は、半導体システム810に格納されたデータを処理してコンピューターシステム800の動作を制御する。このようなプロセッサ820は、通常のコンピューターシステムに使用される中央処理装置とその機能が同一又は類似に形成され得る。

【0072】

コンピューターシステム800はモニター832、キーボード834、プリンター836、マウス838などのユーザーインターフェース装置などを含むことができる。

【0073】

図12は、本発明の一実施例に係わるデータプロセッシングシステムの構成を現わす図である。

【0074】

データプロセッシングシステム900は、電子システム(図示省略)に備えられ電子システムの幾多の機能などのうち特定機能を行なう。

【0075】

このようなデータプロセッシングシステム900は、基板に搭載された少なくとも一つの半導体素子910を含む。

【0076】

半導体素子910は、電子システムの特定機能を行うために要するデータが格納されるセルアレイ(図示省略)、及びセルアレイに格納されたデータを処理して当該特定機能が行われるように制御するプロセッサ(図示省略)を含む。すなわち、半導体素子910は一つの単位素子(die 又はチップ)にデータを格納するための手段と、その格納されたデータを処理して電子システムの特定機能を行うための手段とを全て含む。

【0077】

このとき、セルアレイは上述した図8のセルアレイ510が使用され得る。

【0078】

データプロセッシングシステム900は、リード等(leads)920を介して電子システムの他の構成要素(例えば、CPU)と連結され、単方向又は両方向にデータ及び制御信号を取り交わすことができる。

【0079】

図13は、本発明の一実施例に係わる電子システムの構成を現わす図である。

【0080】

電子システム1000は、少なくとも一つのデータプロセッシングシステム1010及びユーザーインターフェース1020を含む。

【0081】

データプロセッシングシステム1010は、電子システム1000の幾多の機能などのうち特定機能を行い、基板に搭載された少なくとも一つの半導体素子を含む。 そして、半導体素子は電子システム1000の特定機能を行うために要するデータが格納されるセルアレイ(図示省略)、 及びセルアレイに格納されたデータを処理して当該機能を制御するプロセッサ(図示省略)を含む。このとき、セルアレイは上述した図 8のセルアレイ510が使用され得る。

【0082】

ユーザーインターフェース1020は、使用者と回路モジュール1010との間のインターフェースを提供する。 ユーザーインターフェース1020は、電子装置に一体形に設けられたキーパッド、タッチスクリーン、スピーカーなどを含む。

【0083】

このような電子装置1000はコンピューター、家電製品、工場自動化システム、エレベータ、携帯電話など各種の電子・情報・通信機器に備えられたエンベデッドシステム(embedded system)を含む。

【0084】

上述した本発明の好ましい実施例は例示の目的のためのもので、当業者であれば添付された特許請求範囲の技術的思想と範囲を介して多様な修正、変更、代替及び付加が可能なはずであり、このような修正変更などは以下の特許請求範囲に属するものと見なければならないはずである。

【特許請求の範囲】

【請求項1】

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体素子。

【請求項2】

前記コンタクトと前記ゲートとの間に位置するシーリング膜をさらに含むことを特徴とする請求項1記載の半導体素子。

【請求項3】

前記コンタクトは

前記第1ゲートと前記第2ゲートとの間の活性領域の上部を取り囲むことを特徴とする請求項1または請求項2記載の半導体素子。

【請求項4】

前記側面は

前記第1トレンチと前記第2トレンチの内側面であることを特徴とする請求項1乃至請求項3のいずれか1項記載の半導体素子。

【請求項5】

前記側面は

前記第1トレンチと前記第2トレンチの内側面中ビットラインと重畳される領域であることを特徴とする請求項1乃至請求項4のいずれか1項記載の半導体素子。

【請求項6】

活性領域内のトレンチ下部に埋め込まれたゲート; 及び

前記ゲート両側の前記活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体素子。

【請求項7】

前記側面は

前記トレンチの内側面であることを特徴とする請求項6記載の半導体素子。

【請求項8】

活性領域を画成する素子分離膜を形成する段階;

前記活性領域に第1埋め込みゲートと第2埋め込みゲートを形成する段階;

前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域を突出させるコンタクトホールを形成する段階;

前記コンタクトホールを埋め込むコンタクト層を形成する段階;

前記コンタクト層上部に導電膜を形成する段階; 及び

前記導電膜及び前記コンタクト層をエッチングしてビットライン及びビットラインコンタクトを形成する段階を含むことを特徴とする半導体素子の製造方法。

【請求項9】

前記第1埋め込みゲートと前記第2埋め込みゲートを形成する段階は

前記活性領域をエッチングして第1トレンチ及び第2トレンチを形成する段階;

前記第1トレンチと前記第2トレンチとの下部にゲート導電膜を形成する段階; 及び

前記第1トレンチと前記第2トレンチが埋め込まれるように、前記ゲート導電膜上部にシーリング膜を形成する段階を含むことを特徴とする請求項8記載の半導体素子の製造方法。

【請求項10】

前記コンタクトホールを形成する段階は

前記ゲート導電膜と前記シーリング膜を含む活性領域上部に層間絶縁膜を形成する段階; 及び

ビットラインコンタクトマスクを利用して前記層間絶縁膜、前記素子分離膜及び前記シーリング膜をエッチングして前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域の上部面及び側面を露出させる段階を含むことを特徴とする請求項8または請求項9記載の半導体素子の製造方法。

【請求項11】

前記ビットライン及び前記ビットラインコンタクトを形成する段階は

ビットラインマスクを利用して前記導電膜及び前記コンタクト層を順次エッチングすることを特徴とする請求項8乃至請求項10のいずれか1項記載の半導体素子の製造方法。

【請求項12】

前記ビットラインコンタクトを形成する段階は

前記コンタクト層が前記活性領域の上部面及び前記第1トレンチと前記第2トレンチの内側面にのみ接触されるように、前記コンタクト層をエッチングすることを特徴とする請求項8乃至請求項11のいずれか1項記載の半導体素子の製造方法。

【請求項13】

活性領域に埋め込まれた第1ワードラインと第2ワードライン、コンタクトを介して前記第1ワードラインと前記第2ワードラインとの間の活性領域と連結されるビットライン、及び前記ワードラインと前記ビットラインに連結されるメモリーセルを含むセルアレイ; 及び

前記ビットラインに連結され前記セルに格納されたデータをセンシングするセンスアンプを含み、

前記コンタクトは第1ワードラインと前記第2ワードラインとの間の前記活性領域の上部面及び側面と接触されることを特徴とする半導体素子。

【請求項14】

前記セルアレイでデータがリード又はライトされるセルを選択するための選択信号を出力するローデコーダ; 及び

前記選択信号により選択されたセルと連結されたセンスアンプを動作させるための駆動信号を出力するカラムデコーダをさらに含むことを特徴とする請求項13記載の半導体素子。

【請求項15】

基板に搭載された複数個の半導体素子を有する半導体モジュールにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体モジュール。

【請求項16】

基板に搭載された複数個の半導体素子を有する半導体モジュール、及び前記半導体モジュールの動作を制御する制御機を含む半導体システムにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体システム。

【請求項17】

少なくとも一つの半導体モジュールを有する半導体システム、及び前記半導体システムに格納されたデータを処理するプロセッサを含むコンピューターシステムにおいて、

前記半導体モジュールは基板に搭載された半導体素子などを含み、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とするコンピューターシステム。

【請求項18】

基板に搭載された少なくとも一つの半導体素子を含むデータプロセッシングシステムにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とするデータプロセッシングシステム。

【請求項19】

少なくとも一つのデータプロセッシングシステムを有する電子システムにおいて、

前記データプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする含むことを特徴とする電子システム。

【請求項1】

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体素子。

【請求項2】

前記コンタクトと前記ゲートとの間に位置するシーリング膜をさらに含むことを特徴とする請求項1記載の半導体素子。

【請求項3】

前記コンタクトは

前記第1ゲートと前記第2ゲートとの間の活性領域の上部を取り囲むことを特徴とする請求項1または請求項2記載の半導体素子。

【請求項4】

前記側面は

前記第1トレンチと前記第2トレンチの内側面であることを特徴とする請求項1乃至請求項3のいずれか1項記載の半導体素子。

【請求項5】

前記側面は

前記第1トレンチと前記第2トレンチの内側面中ビットラインと重畳される領域であることを特徴とする請求項1乃至請求項4のいずれか1項記載の半導体素子。

【請求項6】

活性領域内のトレンチ下部に埋め込まれたゲート; 及び

前記ゲート両側の前記活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体素子。

【請求項7】

前記側面は

前記トレンチの内側面であることを特徴とする請求項6記載の半導体素子。

【請求項8】

活性領域を画成する素子分離膜を形成する段階;

前記活性領域に第1埋め込みゲートと第2埋め込みゲートを形成する段階;

前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域を突出させるコンタクトホールを形成する段階;

前記コンタクトホールを埋め込むコンタクト層を形成する段階;

前記コンタクト層上部に導電膜を形成する段階; 及び

前記導電膜及び前記コンタクト層をエッチングしてビットライン及びビットラインコンタクトを形成する段階を含むことを特徴とする半導体素子の製造方法。

【請求項9】

前記第1埋め込みゲートと前記第2埋め込みゲートを形成する段階は

前記活性領域をエッチングして第1トレンチ及び第2トレンチを形成する段階;

前記第1トレンチと前記第2トレンチとの下部にゲート導電膜を形成する段階; 及び

前記第1トレンチと前記第2トレンチが埋め込まれるように、前記ゲート導電膜上部にシーリング膜を形成する段階を含むことを特徴とする請求項8記載の半導体素子の製造方法。

【請求項10】

前記コンタクトホールを形成する段階は

前記ゲート導電膜と前記シーリング膜を含む活性領域上部に層間絶縁膜を形成する段階; 及び

ビットラインコンタクトマスクを利用して前記層間絶縁膜、前記素子分離膜及び前記シーリング膜をエッチングして前記第1埋め込みゲートと前記第2埋め込みゲートとの間の活性領域の上部面及び側面を露出させる段階を含むことを特徴とする請求項8または請求項9記載の半導体素子の製造方法。

【請求項11】

前記ビットライン及び前記ビットラインコンタクトを形成する段階は

ビットラインマスクを利用して前記導電膜及び前記コンタクト層を順次エッチングすることを特徴とする請求項8乃至請求項10のいずれか1項記載の半導体素子の製造方法。

【請求項12】

前記ビットラインコンタクトを形成する段階は

前記コンタクト層が前記活性領域の上部面及び前記第1トレンチと前記第2トレンチの内側面にのみ接触されるように、前記コンタクト層をエッチングすることを特徴とする請求項8乃至請求項11のいずれか1項記載の半導体素子の製造方法。

【請求項13】

活性領域に埋め込まれた第1ワードラインと第2ワードライン、コンタクトを介して前記第1ワードラインと前記第2ワードラインとの間の活性領域と連結されるビットライン、及び前記ワードラインと前記ビットラインに連結されるメモリーセルを含むセルアレイ; 及び

前記ビットラインに連結され前記セルに格納されたデータをセンシングするセンスアンプを含み、

前記コンタクトは第1ワードラインと前記第2ワードラインとの間の前記活性領域の上部面及び側面と接触されることを特徴とする半導体素子。

【請求項14】

前記セルアレイでデータがリード又はライトされるセルを選択するための選択信号を出力するローデコーダ; 及び

前記選択信号により選択されたセルと連結されたセンスアンプを動作させるための駆動信号を出力するカラムデコーダをさらに含むことを特徴とする請求項13記載の半導体素子。

【請求項15】

基板に搭載された複数個の半導体素子を有する半導体モジュールにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体モジュール。

【請求項16】

基板に搭載された複数個の半導体素子を有する半導体モジュール、及び前記半導体モジュールの動作を制御する制御機を含む半導体システムにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする半導体システム。

【請求項17】

少なくとも一つの半導体モジュールを有する半導体システム、及び前記半導体システムに格納されたデータを処理するプロセッサを含むコンピューターシステムにおいて、

前記半導体モジュールは基板に搭載された半導体素子などを含み、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とするコンピューターシステム。

【請求項18】

基板に搭載された少なくとも一つの半導体素子を含むデータプロセッシングシステムにおいて、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とするデータプロセッシングシステム。

【請求項19】

少なくとも一つのデータプロセッシングシステムを有する電子システムにおいて、

前記データプロセッシングシステムは基板に搭載された少なくとも一つの半導体素子を含み、

前記半導体素子は

活性領域内の第1トレンチ下部に埋め込まれた第1ゲート;

前記活性領域内の第2トレンチ下部に埋め込まれた第2ゲート; 及び

前記第1ゲートと前記第2ゲートに共有され、前記第1ゲートと前記第2ゲートとの間の活性領域の上部面及び側面と接触されるコンタクトを含むことを特徴とする含むことを特徴とする電子システム。

【図11】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図13】

【公開番号】特開2013−106040(P2013−106040A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2012−198120(P2012−198120)

【出願日】平成24年9月10日(2012.9.10)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成24年9月10日(2012.9.10)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]