フィルタ回路

【課題】選択性の高いフィルタ特性が得られるようにすること。

【解決手段】VHFローバンドの信号を通過させる時は、第2の容量6を入力端20とグランド間に介挿し、第3の容量7を出力端21とグランド間に介挿し、UHFバンドの信号を通過させる時は、第1のインダクタ2を入力端20とグランド間に介挿し、第2のインダクタ3を出力端21とグランド間に介挿し、VHFハイバンドの信号を通過させる時は、第3の回路12を入出力端間20−21に介挿すると共に第1の回路5の第1のインダクタ2と第2の回路9の第2の容量6を入力端20とグランド間に夫々介挿し、第1の回路5の第2のインダクタ3と第2の回路9の第3の容量7を出力端21とグランド間に夫々介挿する。これにより、第1、第2の及び第3の回路5、9、12の夫々において選択性の高いフィルタ特性が得られる。

【解決手段】VHFローバンドの信号を通過させる時は、第2の容量6を入力端20とグランド間に介挿し、第3の容量7を出力端21とグランド間に介挿し、UHFバンドの信号を通過させる時は、第1のインダクタ2を入力端20とグランド間に介挿し、第2のインダクタ3を出力端21とグランド間に介挿し、VHFハイバンドの信号を通過させる時は、第3の回路12を入出力端間20−21に介挿すると共に第1の回路5の第1のインダクタ2と第2の回路9の第2の容量6を入力端20とグランド間に夫々介挿し、第1の回路5の第2のインダクタ3と第2の回路9の第3の容量7を出力端21とグランド間に夫々介挿する。これにより、第1、第2の及び第3の回路5、9、12の夫々において選択性の高いフィルタ特性が得られる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、広帯域信号を複数の帯域の信号に分岐するフィルタ回路に関する。

【背景技術】

【0002】

連続する帯域の信号としてテレビジョン放送信号が知られており、テレビジョンチューナでは例えば50MHzから860MHzの広帯域信号をVHFローバンド、VHFハイバンド、UHFバンドの3バンドに分岐して受信している(例えば、特許文献1参照)。図5は、特許文献1で開示されたチューナの回路図である。同図において、VHFローバンドのテレビジョン信号を受信する際には、第3のスイッチ手段106をオンして、インダクタ101と第2のコンデンサ103とによってローパスフィルタを構成し、VHFハイバンドのテレビジョン信号を受信する際には、第4のスイッチ手段107をオンして、インダクタ101と別の第2のコンデンサ104とによってローパスフィルタを構成し、UHFバンドのテレビジョン信号を受信する際には、第1のスイッチ手段105と第3のスイッチ手段106と第4のスイッチ手段107とをオンにして、インダクタ101を高周波的に接地し、第1のコンデンサ102とインダクタ101とによってハイパスフィルタを構成する。

【0003】

第3のスイッチ手段106をオンにすると、VHFローバンドのテレビジョン信号が抽出されてVHFローバンド回路109に入力される。また、第4のスイッチ手段107をオンにすると、VHFハイバンドのテレビジョン信号が抽出されてVHFハイバンド回路110に入力される。また、第1のスイッチ手段105と第3のスイッチ手段106と第4のスイッチ手段107とをオンにすると、UHFバンドのテレビジョン信号が抽出されてUHFバンド回路108に入力される。

【0004】

ところで、上記チューナは、3つのバンドで1つのインダクタ101を共用するため、高い選択性は期待できない。そこで、周波数選択性を改善するために、独立してローパスフィルタ、ハイパスフィルタ及びバンドパスフィルタを構成し、スイッチング素子でフィルタを切替え可能にしたフィルタ回路が考えられている。

【0005】

図6は、周波数選択性を改善したフィルタ回路の構成図である。同図に示すフィルタ回路は、インダクタ120とコンデンサ121及び122とで構成したハイパスフィルタでUHFバンド(バンド2)のテレビジョン信号を抽出し、またインダクタ125及び127とコンデンサ126及び128とで構成したバンドパスフィルタでVHFハイバンド(バンド3)のテレビジョン信号を抽出し、またインダクタ131及び132とコンデンサ133で構成したローパスフィルタでVHFローバンド(バンド1)のテレビジョン信号を抽出する。ハイパスフィルタを選択するときは、スイッチングダイオード123及び124のみをオンし、バンドパスフィルタを選択するときは、スイッチングダイオード129及び130のみをオンし、ローパスフィルタを選択するときは、スイッチングダイオード134及び135のみをオンする。

【特許文献1】特開2001−359005号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述したフィルタ回路は、次のような問題がある。

受信バンドを切り替えるためにスイッチングダイオードを多数(6個)設ける必要があるので、コストアップになるといった問題がある。

【0007】

また、フィルタの切り替えをスイッチングダイオードで行っているが、スイッチングダイオードはオフ状態において端子間容量が存在するので、オフ時における端子間容量によってフィルタ特性が悪化する問題がある。図6に示すフィルタ回路においてバンド2を受信するためにスイッチングダイオード129、130、134、135をオフするが、図7に示すようにスイッチングダイオード134の端子間容量Cdiによって、この端子間容量Cdiとインダクタ131(L1)とコンデンサ133(C1)で直列共振が起こり、VHFハイバンドに影響を与えることになる。

【0008】

また、フィルタ回路の入力端子に信号強度の強い信号が入力されると、該入力端子に接続されているスイッチングダイオード(図6に示すスイッチングダイオード123、129及び134)が歪むために、受信精度が悪化するといった問題もある。

【0009】

本発明は、かかる点に鑑みてなされたものであり、スイッチング素子の数を減らしてコストダウンを図ることができると共に、スイッチングダイオードの端子間容量の影響を最小限に抑えることができ、しかも入力信号強度が大きい場合であってもスイッチング素子の歪みによる受信精度の低下を防止できるフィルタ回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明のフィルタ回路は、第1の帯域の信号を通過させる第1の回路と、前記第1の帯域の信号より周波数の高い第2の帯域の信号を通過させる第2の回路と、前記第1の回路と第2の回路とで共用する入出力端とを備え、前記第1の回路は、前記入出力端間に直列接続された第1及び第2のインダクタと、前記第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とを有し、前記第2の回路は、前記入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとを有し、前記第1の帯域の信号を通過させる場合、前記第2及び第3の容量の接続点をグランドに短絡させて、前記入力端とグランド間に前記第2の容量を介挿し、前記出力端とグランド間に前記第3の容量を介挿し、前記第2の帯域の信号を通過させる場合、前記第1及び第2のインダクタの接続点をグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタを介挿し、前記出力端とグランド間に前記第2のインダクタを介挿することを特徴とする。

【0011】

この構成によれば、第1の回路は、第1及び第2のインダクタと、第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とからローパスフィルタを構成し、第1の帯域の信号を通過させる場合には、第1の回路に対して、第2の回路の第2の容量を入力端とグランドとの間に介挿し、第2の回路の第3の容量を出力端とグランドとの間に介挿することにより、ローパスフィルタのフィルタ特性を改善することができる。また、第2の回路は、入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとからハイパスフィルタを構成し、第2の帯域の信号を通過させる場合には、第1の回路の第1のインダクタを入力端とグランドとの間に介挿し、第1の回路の第2のインダクタを出力端とグランドとの間に介挿することにより、ハイパスフィルタのフィルタ特性を改善することができる。

【0012】

また本発明は、上記フィルタ回路において、前記第1及び第2のインダクタの接続点とグランド間に第1のスイッチング素子を設け、前記第2及び第3の容量の接続点とグランド間に第2のスイッチング素子を設け、前記第1の帯域の信号を通過させる場合、前記第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンし、前記第2の帯域の信号を通過させる場合、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることを特徴とする。

【0013】

この構成によれば、第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンすることで第1の回路が選択されて第1の帯域の信号を通過させることができ、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることで第2の回路が選択されて第2の帯域の信号を通過させることができる。したがって、スイッチング素子の数を減らすことができる。また、第1の帯域の信号を通過させる時に、第1のスイッチング素子をオフすると共に、第2のスイッチング素子をオンすることで、第1の回路の前段に第2の回路の第2の容量が介挿され、第1の回路の後段に第2の回路の第3の容量が介挿される。また、第2の帯域の信号を通過させる時に、第1のスイッチング素子をオンすると共に、第2のスイッチング素子をオフすることで、第2の回路の前段に第1の回路の第1のインダクタが介挿され、第2の回路の後段に第1の回路の第2のインダクタが介挿される。これにより、信号強度の強い信号が入力された場合であっても、フィルタを介して信号が印加されることとなり、スイッチング素子での歪を抑制することができる。

【0014】

また本発明は、上記フィルタ回路において、前記第1の帯域の信号より周波数が高く、前記第2の帯域の信号より周波数が低い第3の帯域の信号を通過させる第3の回路を備え、前記第3の回路は、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路を有し、前記第3の帯域の信号を通過させる場合、前記第3の回路を入出力端間に接続すると共に、前記第1及び第2のインダクタの接続点と前記第2及び第3の容量の接続点とをそれぞれグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタと第2の容量をそれぞれ介挿し、前記出力端とグランド間に前記第2のインダクタと第3の容量をそれぞれ介挿することを特徴とする。

【0015】

この構成によれば、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路からバンドパスフィルタが構成され、第3の帯域の信号を通過させる時には、入力端とグランドとの間に第1の回路の第1のインダクタと第2の回路の第2の容量が介挿され、出力端とグランドとの間に第2の回路の第2のインダクタと第1の回路の第3の容量が介挿されるので、バンドパスフィルタのフィルタ特性を改善することができる。

【0016】

また本発明は、上記フィルタ回路において、前記第4の容量と第4のインダクタとの直列接続回路と前記出力端との間に第3のスイッチング素子を設け、前記第3の帯域の信号を通過させる場合、前記第1、第2及び第3のスイッチング素子を共にオンとしたことを特徴とする。

【0017】

この構成によれば、前記第1、第2及び第3のスイッチング素子を共にオンすることで、第3の回路が選択されて第3の帯域の信号を通過させることができ、スイッチング素子の数を減らすことができる。

【0018】

上記フィルタ回路において、前記第1、第2及び第3のスイッチング素子は、スイッチングダイオードで構成することができる。

【発明の効果】

【0019】

本発明によれば、スイッチング素子の数を減らしてコストダウンを図ることができると共に、スイッチングダイオードの端子間容量の影響を最小限に抑えることができ、しかも入力信号強度が大きい場合であってもスイッチング素子の歪みによる受信精度の低下を防止することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態について添付図面を参照して詳細に説明する。

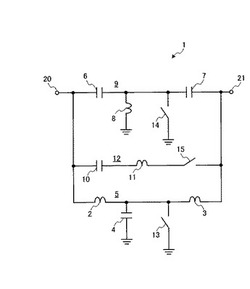

図1は、本発明の一実施の形態に係るフィルタ回路の概略構成を示すブロック図である。同図において、本実施の形態のフィルタ回路1は、第1のインダクタ2及び第2のインダクタ3と第1の容量4で構成され、VHFローバンド(第1の帯域)の信号を通過させる第1の回路となるローパスフィルタ5と、第2の容量6及び第3の容量7と第3のインダクタ8で構成され、VHFローバンドの信号より周波数の高いUHFバンド(第2の帯域)の信号を通過させる第2の回路となるハイパスフィルタ9と、第4の容量10と第4のインダクタ11で構成され、VHFローバンドとUHFバンドの間の帯域となるVHFハイバンド(第3の帯域)の信号を通過させる第3の回路となるバンドパスフィルタ12とを備える。

【0021】

ローパスフィルタ5には、第1のインダクタ2及び第2のインダクタ3の接続点とグランドとの間に第1のスイッチング素子13が接続されている。ハイパスフィルタ9には、第2の容量6及び第3の容量7の接続点とグランドとの間に第2のスイッチング素子14が接続されている。バンドパスフィルタ12には、第4のインダクタ11と出力端21との間に第3のスイッチング素子15が接続されている。ローパスフィルタ5、ハイパスフィルタ9及びバンドパスフィルタ12は、入力端20と出力端21との間に並列に接続され、3つのスイッチング素子13〜15で切り替え可能に構成されている。スイッチング素子13〜15はスイッチングダイオードで構成する。

【0022】

以上のように構成されたフィルタ回路1において、第1のバンドとなるVHFローバンドを受信する場合は、第2のスイッチング素子14のみオンして、ハイパスフィルタ9の第2の容量6及び第3の容量7の接続点をグランドに短絡させ、入力端20とグランドとの間に第2の容量6を介挿させると共に、出力端21とグランドとの間に第3の容量7を介挿させる。

【0023】

図2(a)はVHFローバンド受信時の等価回路を示している。VHFローバンドの信号を通過させるローパスフィルタ5は、第1のインダクタ2と第2のインダクタ3との中間接続点を第1の容量4を介して接地する基本構成に加え、このLPFの前後にハイパスフィルタ9の第2の容量6と第3の容量を付加することで、遮断周波数領域での減衰特性を急峻にすることができ、LPFのフィルタ特性を向上させている。すなわち、VHFローバンドを受信するためにローパスフィルタ5を選択した場合には、ハイパスフィルタ9の第2の容量6及び第3の容量7をローパスフィルタ5としての特性が改善されるように接続している。

【0024】

次に、第2のバンドとなるUHFバンドを受信する場合は、第1のスイッチング素子13のみオンして、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3の接続点をグランドに短絡させ、入力端20とグランドとの間に第1のインダクタ2を介挿させると共に、出力端21とグランドとの間に第2のインダクタ3を介挿させる。

【0025】

図2(c)は、UHFバンド受信時の等価回路を示している。UHFバンドの信号を通過させるハイパスフィルタ9は、入力端20と出力端21との間に直列に接続された第2の容量6及び第3の容量7と、第2及び第3の容量の接続点とグラウンドとの間に接続された第3のインダクタ8との基本構成に加え、このHPFの前後にローパスフィルタ5の第1のインダクタ2と第2のインダクタ3が付加されている。これにより、遮断周波数領域での減衰特性を急峻にすることができ、HPFのフィルタ特性を向上させている。すなわち、UHFバンドを受信するためにハイパスフィルタ9を選択した場合には、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3をハイパスフィルタ9としての特性が改善されるように接続している。

【0026】

次に、VHFハイバンドを受信する場合は、第1から第3のスイッチング素子13、14、15の全てをオンし、バンドパスフィルタ12を入力端21と出力端21との間に接続する。第1及び第2のスイッチング素子13、14により、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3がバンドパスフィルタ12の両端に接続され、第2のスイッチング素子14により、ハイパスフィルタ9の第2の容量6及び第3の容量7がバンドパスフィルタ12の両端に接続される。

【0027】

図2(b)は、VHFハイバンド受信時の等価回路を示している。VHFハイバンドの信号を通過させるバンドパスフィルタ12は、第4の容量10と第4のインダクタ11との直列共振回路からなる基本構成に加え、このBPFの前後にローパスフィルタ5の第1のインダクタ2及びハイパスフィルタ9の第2の容量6とローパスフィルタ5の第2のインダクタ3及びハイパスフィルタ9の第3の容量7が付加されており、低域側及び高域側それぞれの遮断周波数領域でのフィルタ特性が急峻となり、フィルタ特性を向上することができる。すなわち、VHFハイバンドを受信するためにバンドパスフィルタ12を選択した場合には、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3と、排パスフィルタ9の第2の容量6及び第3の容量7とを、バンドパスフィルタ12としての特性が改善されるように利用している。

【0028】

また本実施の形態では、第1のスイッチング素子13は、ローパスフィルタ5の第1のインダクタ2と第3の容量4の後段に配置し、第2のスイッチング素子14は、ハイパスフィルタ9の第1の容量6と第3のインダクタ8の後段に配置し、第3のスイッチング素子15は、バンドパスフィルタ12の第4の容量10と第4のインダクタ11との直列接続回路の後段に配置するようにしたので、入力端20に信号強度の大きい信号が印加された場合であってもスイッチング素子13〜15による歪みの発生を抑制でき、受信精度の改善を図ることができる。

【0029】

また、本実施の形態のフィルタ回路1では、フィルタ切り替えのために使用するスイッチング素子数を3個にしているので、コストダウンを図ることができる。

【0030】

図3は、本実施の形態に係るフィルタ回路1の周波数特性をシミュレーションするための回路モデルである。ローパスフィルタ5、ハイパスフィルタ9及びバンドパスフィルタ12のそれぞれを構成する各素子の値を以下のようにしている。

[ローパスフィルタ5]

第1のインダクタ2:50nH

第2のインダクタ3:50nH

第3の容量4:20pF

[ハイパスフィルタ9]

第2の容量6:4.5pF

第3の容量7:4.5pF

第3のインダクタ8:18nH

[バンドパスフィルタ12]

第4の容量10:8pF

第4のインダクタ11:50nH

スイッチング素子13〜15は、スイッチングダイオードの端子間容量を1000pFとしてコンデンサに置き換えている。

【0031】

図4は、図3の回路モデルを使用してフィルタ特性のシミュレーション結果を示す図である。同図において、符号30はローパスフィルタ5のフィルタ特性、符号31はハイパスフィルタ9のフィルタ特性、符号32はバンドパスフィルタ12のフィルタ特性である。

【0032】

ローパスフィルタ5のフィルタ特性30から、遮断周波数領域(0.2GHz〜0.6GHz)での減衰特性が急峻になっており、ローパスフィルタ5としての特性が改善されていることが確認できる。

【0033】

またハイパスフィルタ9のフィルタ特性31から、遮断周波数領域(0.15GHz〜0.5GHz)での減衰特性が急峻になっており、ハイパスフィルタ9としての特性が改善されていることが確認できる。

【0034】

またバンドパスフィルタ12のフィルタ特性32から、低域側及び高域側それぞれの遮断周波数領域でのフィルタ特性が急峻となっており、バンドパスフィルタ12としての特性が改善されていることが判る。

【0035】

このように、本実施の形態のフィルタ回路1によれば、VHFローバンド、VHFハイバンド、UHFバンドのそれぞれに対応したフィルタ特性を有するローパスフィルタ5、ハイパスフィルタ9、バンドパスフィルタ12を備え、それらフィルタを第1から第3のスイッチング13〜15のオン、オフの組み合わせで切替え可能とし、さらに選択フィルタ以外の構成要素が、当該選択フィルタに対して選択フィルタのフィルタ特性を強化するように接続されるように回路構成したので、フィルタ切り替えのためのスイッチング素子数を削減できると共に、選択フィルタのフィルタ特性を改善することができる。

【0036】

以上の説明では、3つのバンドを切り替えるフィルタ回路1について説明したが、第1の回路となるローパスフィルタ5と第2の回路となるハイパスフィルタ9の2つのバンドを切り替えるフィルタ回路にも適用可能である。また、フィルタ回路1の用途はテレビジョンチューナに限定されるものではなく、連続する帯域を複数に分岐するフィルタであれば他の用途にも適用可能である。

【産業上の利用可能性】

【0037】

本発明は、テレビジョンチューナ等のように広帯域の信号を複数バンドに分岐して選択的に取り出すフィルタ回路に適用可能である。

【図面の簡単な説明】

【0038】

【図1】本発明の一実施の形態に係るフィルタ回路を示す回路図である。

【図2】(a)VHFローバンド受信時のフィルタ回路の等価回路図、(b)VHFハイバンド受信時のフィルタ回路の等価回路図、(c)UHFバンド受信時のフィルタ回路の等価回路図である。

【図3】シミュレーションのためのフィルタ回路の回路モデルの回路図である。

【図4】図3の回路モデルを用いたフィルタ特性を示す図である。

【図5】従来のチューナを示す回路図である。

【図6】従来のフィルタ回路を示す回路図である。

【図7】従来のフィルタ回路においてオフ状態のスイッチングダイオードの端子間容量を追加した回路図である。

【符号の説明】

【0039】

1…フィルタ回路

2…第1のインダクタ

3…第2のインダクタ

4…第1の容量

5…第1の回路

6…第2の容量

7…第3の容量

8…第3のインダクタ

9…第2の回路

10…第4の容量

11…第4のインダクタ

12…第3の回路

13…スイッチング素子

14…スイッチング素子

15…スイッチング素子

20…入力端

21…出力端

【技術分野】

【0001】

本発明は、広帯域信号を複数の帯域の信号に分岐するフィルタ回路に関する。

【背景技術】

【0002】

連続する帯域の信号としてテレビジョン放送信号が知られており、テレビジョンチューナでは例えば50MHzから860MHzの広帯域信号をVHFローバンド、VHFハイバンド、UHFバンドの3バンドに分岐して受信している(例えば、特許文献1参照)。図5は、特許文献1で開示されたチューナの回路図である。同図において、VHFローバンドのテレビジョン信号を受信する際には、第3のスイッチ手段106をオンして、インダクタ101と第2のコンデンサ103とによってローパスフィルタを構成し、VHFハイバンドのテレビジョン信号を受信する際には、第4のスイッチ手段107をオンして、インダクタ101と別の第2のコンデンサ104とによってローパスフィルタを構成し、UHFバンドのテレビジョン信号を受信する際には、第1のスイッチ手段105と第3のスイッチ手段106と第4のスイッチ手段107とをオンにして、インダクタ101を高周波的に接地し、第1のコンデンサ102とインダクタ101とによってハイパスフィルタを構成する。

【0003】

第3のスイッチ手段106をオンにすると、VHFローバンドのテレビジョン信号が抽出されてVHFローバンド回路109に入力される。また、第4のスイッチ手段107をオンにすると、VHFハイバンドのテレビジョン信号が抽出されてVHFハイバンド回路110に入力される。また、第1のスイッチ手段105と第3のスイッチ手段106と第4のスイッチ手段107とをオンにすると、UHFバンドのテレビジョン信号が抽出されてUHFバンド回路108に入力される。

【0004】

ところで、上記チューナは、3つのバンドで1つのインダクタ101を共用するため、高い選択性は期待できない。そこで、周波数選択性を改善するために、独立してローパスフィルタ、ハイパスフィルタ及びバンドパスフィルタを構成し、スイッチング素子でフィルタを切替え可能にしたフィルタ回路が考えられている。

【0005】

図6は、周波数選択性を改善したフィルタ回路の構成図である。同図に示すフィルタ回路は、インダクタ120とコンデンサ121及び122とで構成したハイパスフィルタでUHFバンド(バンド2)のテレビジョン信号を抽出し、またインダクタ125及び127とコンデンサ126及び128とで構成したバンドパスフィルタでVHFハイバンド(バンド3)のテレビジョン信号を抽出し、またインダクタ131及び132とコンデンサ133で構成したローパスフィルタでVHFローバンド(バンド1)のテレビジョン信号を抽出する。ハイパスフィルタを選択するときは、スイッチングダイオード123及び124のみをオンし、バンドパスフィルタを選択するときは、スイッチングダイオード129及び130のみをオンし、ローパスフィルタを選択するときは、スイッチングダイオード134及び135のみをオンする。

【特許文献1】特開2001−359005号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、上述したフィルタ回路は、次のような問題がある。

受信バンドを切り替えるためにスイッチングダイオードを多数(6個)設ける必要があるので、コストアップになるといった問題がある。

【0007】

また、フィルタの切り替えをスイッチングダイオードで行っているが、スイッチングダイオードはオフ状態において端子間容量が存在するので、オフ時における端子間容量によってフィルタ特性が悪化する問題がある。図6に示すフィルタ回路においてバンド2を受信するためにスイッチングダイオード129、130、134、135をオフするが、図7に示すようにスイッチングダイオード134の端子間容量Cdiによって、この端子間容量Cdiとインダクタ131(L1)とコンデンサ133(C1)で直列共振が起こり、VHFハイバンドに影響を与えることになる。

【0008】

また、フィルタ回路の入力端子に信号強度の強い信号が入力されると、該入力端子に接続されているスイッチングダイオード(図6に示すスイッチングダイオード123、129及び134)が歪むために、受信精度が悪化するといった問題もある。

【0009】

本発明は、かかる点に鑑みてなされたものであり、スイッチング素子の数を減らしてコストダウンを図ることができると共に、スイッチングダイオードの端子間容量の影響を最小限に抑えることができ、しかも入力信号強度が大きい場合であってもスイッチング素子の歪みによる受信精度の低下を防止できるフィルタ回路を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明のフィルタ回路は、第1の帯域の信号を通過させる第1の回路と、前記第1の帯域の信号より周波数の高い第2の帯域の信号を通過させる第2の回路と、前記第1の回路と第2の回路とで共用する入出力端とを備え、前記第1の回路は、前記入出力端間に直列接続された第1及び第2のインダクタと、前記第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とを有し、前記第2の回路は、前記入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとを有し、前記第1の帯域の信号を通過させる場合、前記第2及び第3の容量の接続点をグランドに短絡させて、前記入力端とグランド間に前記第2の容量を介挿し、前記出力端とグランド間に前記第3の容量を介挿し、前記第2の帯域の信号を通過させる場合、前記第1及び第2のインダクタの接続点をグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタを介挿し、前記出力端とグランド間に前記第2のインダクタを介挿することを特徴とする。

【0011】

この構成によれば、第1の回路は、第1及び第2のインダクタと、第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とからローパスフィルタを構成し、第1の帯域の信号を通過させる場合には、第1の回路に対して、第2の回路の第2の容量を入力端とグランドとの間に介挿し、第2の回路の第3の容量を出力端とグランドとの間に介挿することにより、ローパスフィルタのフィルタ特性を改善することができる。また、第2の回路は、入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとからハイパスフィルタを構成し、第2の帯域の信号を通過させる場合には、第1の回路の第1のインダクタを入力端とグランドとの間に介挿し、第1の回路の第2のインダクタを出力端とグランドとの間に介挿することにより、ハイパスフィルタのフィルタ特性を改善することができる。

【0012】

また本発明は、上記フィルタ回路において、前記第1及び第2のインダクタの接続点とグランド間に第1のスイッチング素子を設け、前記第2及び第3の容量の接続点とグランド間に第2のスイッチング素子を設け、前記第1の帯域の信号を通過させる場合、前記第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンし、前記第2の帯域の信号を通過させる場合、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることを特徴とする。

【0013】

この構成によれば、第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンすることで第1の回路が選択されて第1の帯域の信号を通過させることができ、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることで第2の回路が選択されて第2の帯域の信号を通過させることができる。したがって、スイッチング素子の数を減らすことができる。また、第1の帯域の信号を通過させる時に、第1のスイッチング素子をオフすると共に、第2のスイッチング素子をオンすることで、第1の回路の前段に第2の回路の第2の容量が介挿され、第1の回路の後段に第2の回路の第3の容量が介挿される。また、第2の帯域の信号を通過させる時に、第1のスイッチング素子をオンすると共に、第2のスイッチング素子をオフすることで、第2の回路の前段に第1の回路の第1のインダクタが介挿され、第2の回路の後段に第1の回路の第2のインダクタが介挿される。これにより、信号強度の強い信号が入力された場合であっても、フィルタを介して信号が印加されることとなり、スイッチング素子での歪を抑制することができる。

【0014】

また本発明は、上記フィルタ回路において、前記第1の帯域の信号より周波数が高く、前記第2の帯域の信号より周波数が低い第3の帯域の信号を通過させる第3の回路を備え、前記第3の回路は、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路を有し、前記第3の帯域の信号を通過させる場合、前記第3の回路を入出力端間に接続すると共に、前記第1及び第2のインダクタの接続点と前記第2及び第3の容量の接続点とをそれぞれグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタと第2の容量をそれぞれ介挿し、前記出力端とグランド間に前記第2のインダクタと第3の容量をそれぞれ介挿することを特徴とする。

【0015】

この構成によれば、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路からバンドパスフィルタが構成され、第3の帯域の信号を通過させる時には、入力端とグランドとの間に第1の回路の第1のインダクタと第2の回路の第2の容量が介挿され、出力端とグランドとの間に第2の回路の第2のインダクタと第1の回路の第3の容量が介挿されるので、バンドパスフィルタのフィルタ特性を改善することができる。

【0016】

また本発明は、上記フィルタ回路において、前記第4の容量と第4のインダクタとの直列接続回路と前記出力端との間に第3のスイッチング素子を設け、前記第3の帯域の信号を通過させる場合、前記第1、第2及び第3のスイッチング素子を共にオンとしたことを特徴とする。

【0017】

この構成によれば、前記第1、第2及び第3のスイッチング素子を共にオンすることで、第3の回路が選択されて第3の帯域の信号を通過させることができ、スイッチング素子の数を減らすことができる。

【0018】

上記フィルタ回路において、前記第1、第2及び第3のスイッチング素子は、スイッチングダイオードで構成することができる。

【発明の効果】

【0019】

本発明によれば、スイッチング素子の数を減らしてコストダウンを図ることができると共に、スイッチングダイオードの端子間容量の影響を最小限に抑えることができ、しかも入力信号強度が大きい場合であってもスイッチング素子の歪みによる受信精度の低下を防止することができる。

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態について添付図面を参照して詳細に説明する。

図1は、本発明の一実施の形態に係るフィルタ回路の概略構成を示すブロック図である。同図において、本実施の形態のフィルタ回路1は、第1のインダクタ2及び第2のインダクタ3と第1の容量4で構成され、VHFローバンド(第1の帯域)の信号を通過させる第1の回路となるローパスフィルタ5と、第2の容量6及び第3の容量7と第3のインダクタ8で構成され、VHFローバンドの信号より周波数の高いUHFバンド(第2の帯域)の信号を通過させる第2の回路となるハイパスフィルタ9と、第4の容量10と第4のインダクタ11で構成され、VHFローバンドとUHFバンドの間の帯域となるVHFハイバンド(第3の帯域)の信号を通過させる第3の回路となるバンドパスフィルタ12とを備える。

【0021】

ローパスフィルタ5には、第1のインダクタ2及び第2のインダクタ3の接続点とグランドとの間に第1のスイッチング素子13が接続されている。ハイパスフィルタ9には、第2の容量6及び第3の容量7の接続点とグランドとの間に第2のスイッチング素子14が接続されている。バンドパスフィルタ12には、第4のインダクタ11と出力端21との間に第3のスイッチング素子15が接続されている。ローパスフィルタ5、ハイパスフィルタ9及びバンドパスフィルタ12は、入力端20と出力端21との間に並列に接続され、3つのスイッチング素子13〜15で切り替え可能に構成されている。スイッチング素子13〜15はスイッチングダイオードで構成する。

【0022】

以上のように構成されたフィルタ回路1において、第1のバンドとなるVHFローバンドを受信する場合は、第2のスイッチング素子14のみオンして、ハイパスフィルタ9の第2の容量6及び第3の容量7の接続点をグランドに短絡させ、入力端20とグランドとの間に第2の容量6を介挿させると共に、出力端21とグランドとの間に第3の容量7を介挿させる。

【0023】

図2(a)はVHFローバンド受信時の等価回路を示している。VHFローバンドの信号を通過させるローパスフィルタ5は、第1のインダクタ2と第2のインダクタ3との中間接続点を第1の容量4を介して接地する基本構成に加え、このLPFの前後にハイパスフィルタ9の第2の容量6と第3の容量を付加することで、遮断周波数領域での減衰特性を急峻にすることができ、LPFのフィルタ特性を向上させている。すなわち、VHFローバンドを受信するためにローパスフィルタ5を選択した場合には、ハイパスフィルタ9の第2の容量6及び第3の容量7をローパスフィルタ5としての特性が改善されるように接続している。

【0024】

次に、第2のバンドとなるUHFバンドを受信する場合は、第1のスイッチング素子13のみオンして、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3の接続点をグランドに短絡させ、入力端20とグランドとの間に第1のインダクタ2を介挿させると共に、出力端21とグランドとの間に第2のインダクタ3を介挿させる。

【0025】

図2(c)は、UHFバンド受信時の等価回路を示している。UHFバンドの信号を通過させるハイパスフィルタ9は、入力端20と出力端21との間に直列に接続された第2の容量6及び第3の容量7と、第2及び第3の容量の接続点とグラウンドとの間に接続された第3のインダクタ8との基本構成に加え、このHPFの前後にローパスフィルタ5の第1のインダクタ2と第2のインダクタ3が付加されている。これにより、遮断周波数領域での減衰特性を急峻にすることができ、HPFのフィルタ特性を向上させている。すなわち、UHFバンドを受信するためにハイパスフィルタ9を選択した場合には、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3をハイパスフィルタ9としての特性が改善されるように接続している。

【0026】

次に、VHFハイバンドを受信する場合は、第1から第3のスイッチング素子13、14、15の全てをオンし、バンドパスフィルタ12を入力端21と出力端21との間に接続する。第1及び第2のスイッチング素子13、14により、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3がバンドパスフィルタ12の両端に接続され、第2のスイッチング素子14により、ハイパスフィルタ9の第2の容量6及び第3の容量7がバンドパスフィルタ12の両端に接続される。

【0027】

図2(b)は、VHFハイバンド受信時の等価回路を示している。VHFハイバンドの信号を通過させるバンドパスフィルタ12は、第4の容量10と第4のインダクタ11との直列共振回路からなる基本構成に加え、このBPFの前後にローパスフィルタ5の第1のインダクタ2及びハイパスフィルタ9の第2の容量6とローパスフィルタ5の第2のインダクタ3及びハイパスフィルタ9の第3の容量7が付加されており、低域側及び高域側それぞれの遮断周波数領域でのフィルタ特性が急峻となり、フィルタ特性を向上することができる。すなわち、VHFハイバンドを受信するためにバンドパスフィルタ12を選択した場合には、ローパスフィルタ5の第1のインダクタ2及び第2のインダクタ3と、排パスフィルタ9の第2の容量6及び第3の容量7とを、バンドパスフィルタ12としての特性が改善されるように利用している。

【0028】

また本実施の形態では、第1のスイッチング素子13は、ローパスフィルタ5の第1のインダクタ2と第3の容量4の後段に配置し、第2のスイッチング素子14は、ハイパスフィルタ9の第1の容量6と第3のインダクタ8の後段に配置し、第3のスイッチング素子15は、バンドパスフィルタ12の第4の容量10と第4のインダクタ11との直列接続回路の後段に配置するようにしたので、入力端20に信号強度の大きい信号が印加された場合であってもスイッチング素子13〜15による歪みの発生を抑制でき、受信精度の改善を図ることができる。

【0029】

また、本実施の形態のフィルタ回路1では、フィルタ切り替えのために使用するスイッチング素子数を3個にしているので、コストダウンを図ることができる。

【0030】

図3は、本実施の形態に係るフィルタ回路1の周波数特性をシミュレーションするための回路モデルである。ローパスフィルタ5、ハイパスフィルタ9及びバンドパスフィルタ12のそれぞれを構成する各素子の値を以下のようにしている。

[ローパスフィルタ5]

第1のインダクタ2:50nH

第2のインダクタ3:50nH

第3の容量4:20pF

[ハイパスフィルタ9]

第2の容量6:4.5pF

第3の容量7:4.5pF

第3のインダクタ8:18nH

[バンドパスフィルタ12]

第4の容量10:8pF

第4のインダクタ11:50nH

スイッチング素子13〜15は、スイッチングダイオードの端子間容量を1000pFとしてコンデンサに置き換えている。

【0031】

図4は、図3の回路モデルを使用してフィルタ特性のシミュレーション結果を示す図である。同図において、符号30はローパスフィルタ5のフィルタ特性、符号31はハイパスフィルタ9のフィルタ特性、符号32はバンドパスフィルタ12のフィルタ特性である。

【0032】

ローパスフィルタ5のフィルタ特性30から、遮断周波数領域(0.2GHz〜0.6GHz)での減衰特性が急峻になっており、ローパスフィルタ5としての特性が改善されていることが確認できる。

【0033】

またハイパスフィルタ9のフィルタ特性31から、遮断周波数領域(0.15GHz〜0.5GHz)での減衰特性が急峻になっており、ハイパスフィルタ9としての特性が改善されていることが確認できる。

【0034】

またバンドパスフィルタ12のフィルタ特性32から、低域側及び高域側それぞれの遮断周波数領域でのフィルタ特性が急峻となっており、バンドパスフィルタ12としての特性が改善されていることが判る。

【0035】

このように、本実施の形態のフィルタ回路1によれば、VHFローバンド、VHFハイバンド、UHFバンドのそれぞれに対応したフィルタ特性を有するローパスフィルタ5、ハイパスフィルタ9、バンドパスフィルタ12を備え、それらフィルタを第1から第3のスイッチング13〜15のオン、オフの組み合わせで切替え可能とし、さらに選択フィルタ以外の構成要素が、当該選択フィルタに対して選択フィルタのフィルタ特性を強化するように接続されるように回路構成したので、フィルタ切り替えのためのスイッチング素子数を削減できると共に、選択フィルタのフィルタ特性を改善することができる。

【0036】

以上の説明では、3つのバンドを切り替えるフィルタ回路1について説明したが、第1の回路となるローパスフィルタ5と第2の回路となるハイパスフィルタ9の2つのバンドを切り替えるフィルタ回路にも適用可能である。また、フィルタ回路1の用途はテレビジョンチューナに限定されるものではなく、連続する帯域を複数に分岐するフィルタであれば他の用途にも適用可能である。

【産業上の利用可能性】

【0037】

本発明は、テレビジョンチューナ等のように広帯域の信号を複数バンドに分岐して選択的に取り出すフィルタ回路に適用可能である。

【図面の簡単な説明】

【0038】

【図1】本発明の一実施の形態に係るフィルタ回路を示す回路図である。

【図2】(a)VHFローバンド受信時のフィルタ回路の等価回路図、(b)VHFハイバンド受信時のフィルタ回路の等価回路図、(c)UHFバンド受信時のフィルタ回路の等価回路図である。

【図3】シミュレーションのためのフィルタ回路の回路モデルの回路図である。

【図4】図3の回路モデルを用いたフィルタ特性を示す図である。

【図5】従来のチューナを示す回路図である。

【図6】従来のフィルタ回路を示す回路図である。

【図7】従来のフィルタ回路においてオフ状態のスイッチングダイオードの端子間容量を追加した回路図である。

【符号の説明】

【0039】

1…フィルタ回路

2…第1のインダクタ

3…第2のインダクタ

4…第1の容量

5…第1の回路

6…第2の容量

7…第3の容量

8…第3のインダクタ

9…第2の回路

10…第4の容量

11…第4のインダクタ

12…第3の回路

13…スイッチング素子

14…スイッチング素子

15…スイッチング素子

20…入力端

21…出力端

【特許請求の範囲】

【請求項1】

第1の帯域の信号を通過させる第1の回路と、前記第1の帯域の信号より周波数の高い第2の帯域の信号を通過させる第2の回路と、前記第1の回路と第2の回路とで共用する入出力端とを備え、

前記第1の回路は、前記入出力端間に直列接続された第1及び第2のインダクタと、前記第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とを有し、

前記第2の回路は、前記入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとを有し、

前記第1の帯域の信号を通過させる場合、前記第2及び第3の容量の接続点をグランドに短絡させて、前記入力端とグランド間に前記第2の容量を介挿し、前記出力端とグランド間に前記第3の容量を介挿し、

前記第2の帯域の信号を通過させる場合、前記第1及び第2のインダクタの接続点をグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタを介挿し、前記出力端とグランド間に前記第2のインダクタを介挿することを特徴とするフィルタ回路。

【請求項2】

前記第1及び第2のインダクタの接続点とグランド間に第1のスイッチング素子を設け、前記第2及び第3の容量の接続点とグランド間に第2のスイッチング素子を設け、

前記第1の帯域の信号を通過させる場合、前記第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンし、

前記第2の帯域の信号を通過させる場合、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることを特徴とする請求項1に記載のフィルタ回路。

【請求項3】

前記第1の帯域の信号より周波数が高く、前記第2の帯域の信号より周波数が低い第3の帯域の信号を通過させる第3の回路を備え、

前記第3の回路は、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路を有し、

前記第3の帯域の信号を通過させる場合、前記第3の回路を入出力端間に接続すると共に、前記第1及び第2のインダクタの接続点と前記第2及び第3の容量の接続点とをそれぞれグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタと第2の容量をそれぞれ介挿し、前記出力端とグランド間に前記第2のインダクタと第3の容量をそれぞれ介挿することを特徴とする請求項1又は請求項2に記載のフィルタ回路。

【請求項4】

前記第4の容量と第4のインダクタとの直列接続回路と前記出力端との間に第3のスイッチング素子を設け、

前記第3の帯域の信号を通過させる場合、前記第1、第2及び第3のスイッチング素子を共にオンとしたことを特徴とする請求項3に記載のフィルタ回路。

【請求項5】

前記第1、第2及び第3のスイッチング素子をそれぞれスイッチングダイオードで構成したことを特徴とする請求項2から請求項4のいずれかに記載のフィルタ回路。

【請求項1】

第1の帯域の信号を通過させる第1の回路と、前記第1の帯域の信号より周波数の高い第2の帯域の信号を通過させる第2の回路と、前記第1の回路と第2の回路とで共用する入出力端とを備え、

前記第1の回路は、前記入出力端間に直列接続された第1及び第2のインダクタと、前記第1及び第2のインダクタの接続点とグランド間に接続された第1の容量とを有し、

前記第2の回路は、前記入出力端間に直列接続された第2及び第3の容量と、前記第2及び第3の容量の接続点とグランド間に接続された第3のインダクタとを有し、

前記第1の帯域の信号を通過させる場合、前記第2及び第3の容量の接続点をグランドに短絡させて、前記入力端とグランド間に前記第2の容量を介挿し、前記出力端とグランド間に前記第3の容量を介挿し、

前記第2の帯域の信号を通過させる場合、前記第1及び第2のインダクタの接続点をグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタを介挿し、前記出力端とグランド間に前記第2のインダクタを介挿することを特徴とするフィルタ回路。

【請求項2】

前記第1及び第2のインダクタの接続点とグランド間に第1のスイッチング素子を設け、前記第2及び第3の容量の接続点とグランド間に第2のスイッチング素子を設け、

前記第1の帯域の信号を通過させる場合、前記第1のスイッチング素子をオフすると共に、前記第2のスイッチング素子をオンし、

前記第2の帯域の信号を通過させる場合、前記第1のスイッチング素子をオンすると共に、前記第2のスイッチング素子をオフすることを特徴とする請求項1に記載のフィルタ回路。

【請求項3】

前記第1の帯域の信号より周波数が高く、前記第2の帯域の信号より周波数が低い第3の帯域の信号を通過させる第3の回路を備え、

前記第3の回路は、前記入力端に接続された第4の容量と第4のインダクタとの直列接続回路を有し、

前記第3の帯域の信号を通過させる場合、前記第3の回路を入出力端間に接続すると共に、前記第1及び第2のインダクタの接続点と前記第2及び第3の容量の接続点とをそれぞれグランドに短絡させて、前記入力端とグランド間に前記第1のインダクタと第2の容量をそれぞれ介挿し、前記出力端とグランド間に前記第2のインダクタと第3の容量をそれぞれ介挿することを特徴とする請求項1又は請求項2に記載のフィルタ回路。

【請求項4】

前記第4の容量と第4のインダクタとの直列接続回路と前記出力端との間に第3のスイッチング素子を設け、

前記第3の帯域の信号を通過させる場合、前記第1、第2及び第3のスイッチング素子を共にオンとしたことを特徴とする請求項3に記載のフィルタ回路。

【請求項5】

前記第1、第2及び第3のスイッチング素子をそれぞれスイッチングダイオードで構成したことを特徴とする請求項2から請求項4のいずれかに記載のフィルタ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−136175(P2010−136175A)

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願番号】特願2008−310911(P2008−310911)

【出願日】平成20年12月5日(2008.12.5)

【出願人】(000010098)アルプス電気株式会社 (4,263)

【Fターム(参考)】

【公開日】平成22年6月17日(2010.6.17)

【国際特許分類】

【出願日】平成20年12月5日(2008.12.5)

【出願人】(000010098)アルプス電気株式会社 (4,263)

【Fターム(参考)】

[ Back to top ]