フィン型チャンネル領域を有する不揮発性メモリ素子及びその製造方法

【課題】本体バイアス制御が可能であり、ビット当たりの面積を縮小させて高集積の可能な高性能不揮発性メモリ素子、及びその製造方法を提供する。

【解決手段】本体からそれぞれ突出され、一方向に離隔されてそれぞれ伸張する少なくとも一対のフィンの外側面及び上面の表面付近を少なくとも一対のチャンネル領域として利用でき、少なくとも一つ以上の制御ゲート電極は、チャンネル領域を横切って形成され、制御ゲート電極とチャンネル領域との間の少なくとも一部分には、少なくとも一対のストレージノードが介在されうる不揮発性メモリ素子である。

【解決手段】本体からそれぞれ突出され、一方向に離隔されてそれぞれ伸張する少なくとも一対のフィンの外側面及び上面の表面付近を少なくとも一対のチャンネル領域として利用でき、少なくとも一つ以上の制御ゲート電極は、チャンネル領域を横切って形成され、制御ゲート電極とチャンネル領域との間の少なくとも一部分には、少なくとも一対のストレージノードが介在されうる不揮発性メモリ素子である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、不揮発性メモリ素子に係り、特に、フィン型チャンネル領域を具備する不揮発性メモリ素子及びその製造方法に関する。例えば、本発明による不揮発性メモリ素子は、フラッシュメモリ及びSONOSメモリを含みうる。

【背景技術】

【0002】

不揮発性メモリ素子、例えば、フラッシュメモリは、制御ゲート電極と半導体基板との間に伝導性フローティングゲート電極を介在している。かかるフローティングゲート電極は、電荷保存のためのストレージノードとして利用される。フラッシュメモリは、フローティングゲート電極の電荷の蓄積の有無によって半導体基板のスレショルド電圧が変わることを利用し、半導体基板に伝導性チャンネル形成の有無、すなわち、電流フローの有無を判読する。一方、他の不揮発性メモリ素子、例えば、SONOSメモリは、制御ゲート電極と半導体基板との間に電荷トラップ型ストレージノードを介在している。SONOSメモリは、フラッシュメモリとほとんど類似した動作を行う。

【0003】

しかし、不揮発性メモリ素子において、微細工程技術の限界により、メモリ集積度及びメモリ速度増大は限界に直面している。それにより、さらに狭幅の微細工程技術を利用する以外に、メモリ容量及びメモリ速度を増大させることができる方法が研究されている。

【0004】

例えば、David M.Friedらによる特許文献1は、フィン−FET及びフィンメモリセルについて開示している。フィン−FETは、魚のヒレ状に形成されたフィンの上面及び側面をチャンネル領域として利用できる。それにより、フィン−FETは、平面形トランジスタよりチャンネル面積を広くでき、大きい電流のフローを提供できる。その結果、フィン−FETは、平面形トランジスタより高い性能を提供できる。

【0005】

しかし、前記特許文献1によるフィン−FETは、SOI基板を利用して製造されることにより、フィンが基板本体からフローティングされるという問題がある。それにより、ボディ・バイアス(body−bias)を利用したトランジスタのスレショルド電圧制御が不可能であり、その結果、CMOSトランジスタのスレショルド電圧調節が困難となりうる。また、従来のフィンメモリセルは、2ビット動作を提供するために1Fのゲート長を基準とし、少なくとも2FX2Fの面積を利用しており、ビット当たりの面積が2F2と大きくなってしまうという問題がある。その結果、フィンメモリセルの集積度が制限されうる。

【特許文献1】米国特許6,664,582号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

従って、本発明が解決しようとする技術的課題は、前述の問題点を克服するためであり、ボディバイアス制御が可能であり、かつビット当たりの面積を減少させて高集積の可能な高性能不揮発性メモリ素子を提供するところにある。

【0007】

本発明が解決しようとする他の技術的課題は、前記不揮発性メモリ素子の製造方法を提供するところにある。

【課題を解決するための手段】

【0008】

前記技術的課題を解決するための本発明の一様態によれば、本体及び前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板と、前記一対のフィンの間を埋め込み、前記本体上に形成された第1絶縁膜と、前記一方向に沿って所定間隔離隔され、前記一対のフィンにそれぞれ形成された少なくとも一対のソース及びドレインと、前記一対のソース及びドレイン間にある前記フィン部分の少なくとも外側面の上端部分及び上面の各表面付近にそれぞれ形成された少なくとも一対のチャンネル領域と、前記チャンネル領域上に形成された第2絶縁膜と、前記第1絶縁膜及び前記第2絶縁膜上を横切り、前記一方向と異なる方向に伸張し、前記半導体基板から絶縁された少なくとも一つ以上の制御ゲート電極と、前記制御ゲート電極と、前記一対のフィンの外側面の上端部分に形成されたチャンネル領域との間にそれぞれ介在された少なくとも一対のストレージノードとを備える不揮発性メモリ素子が提供される。

【0009】

前記技術的課題を解決するための本発明の他の様態によれば、本体及び前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板の前記一対のフィンからなる一対のビットラインと、前記一対のビットライン間を絶縁するために、前記一対のフィン及び前記本体間を埋め込む第1絶縁膜と、前記一対のフィンを横切ってそれぞれ伸張し、前記一方向に離隔されて配置され、前記半導体基板とそれぞれ絶縁された複数の制御ゲート電極からなる複数のワードラインと、前記ワードライン及び前記一対のフィン間に介在された第2絶縁膜と、前記ワードライン及び前記第2絶縁膜間の少なくとも一部分にそれぞれ介在された一対のストレージノードとを備えるNAND構造の不揮発性メモリ素子が提供される。

【0010】

前記他の技術的課題を解決するための本発明の一様態によれば、次のステップを含む不揮発性メモリ素子の製造方法が提供される。半導体基板上に第1絶縁層パターンを形成する。前記第1絶縁層パターンの側壁に、第2絶縁層スペーサを形成する。前記第1絶縁層パターン及び前記第2絶縁層スペーサをエッチング保護膜として前記半導体基板をエッチングし、第1トレンチを形成する。前記第1トレンチを埋め込み、前記第1トレンチの両方向の前記半導体基板上に所定幅ほどそれぞれ拡張する第1フォトレジストパターンを形成する。前記第1フォトレジストパターンをエッチング保護膜として前記半導体基板をエッチングし、第2トレンチを形成する。前記第1フォトレジストパターンを除去し、前記第1トレンチ及び第2トレンチにより限定され、前記半導体基板から突出された少なくとも一対のフィンを形成する。前記フィンを限定する前記第1トレンチ及び第2トレンチを埋め込む第3絶縁層を形成する。前記第2トレンチを埋め込んでいる前記第3絶縁層の部分を選択的に所定深さほどエッチングし、前記第1トレンチを埋め込む前記第3絶縁層の部分を覆う前記フィンの外側面を所定高さほど露出する。前記フィンの露出された外側面及び上面上にゲート絶縁膜を形成する。前記フィンの露出された外側面上に形成されたゲート絶縁膜部分の側壁にそれぞれストレージノードを形成する。前記ストレージノードが形成された結果物上に、前記フィン及び前記第3絶縁層を横切る制御ゲート電極を形成する。

【発明の効果】

【0011】

本発明による不揮発性メモリ素子は、SOI類似構造を利用しており、オフ電流を下げることができ、接合漏れ電流を減少させることができる。

【発明を実施するための最良の形態】

【0012】

以下、添付した図面を参照しつつ、本発明による望ましい実施形態を説明することにより、本発明を詳細に説明する。しかし、本発明は、以下にで開示される実施形態に限定されるものではなく、相異なる多様な形態に具現されるものであり、ただ本実施形態は、本発明の開示を完全なものにし、当業者に発明の範疇を完全に明らかにするために提供される。図面で、構成要素は、説明の便宜のためにその大きさが誇張されている。

【0013】

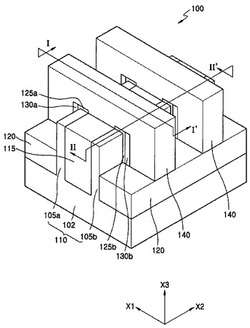

図1は、本発明の一実施形態による不揮発性メモリ素子100を示す斜視図である。図2Aは、図1の不揮発性メモリ素子100のI−I’で切り取った断面図であり、図2Bは、図1の不揮発性メモリ素子100のII−II’で切り取った断面図である。

【0014】

図1、図2A及び図2Bを参照すれば、不揮発性メモリ素子100は、一対のフィン105a,105bに形成されたチャンネル領域160a,160bと、フィン105a,105bを横切る複数の制御ゲート電極140とを備える。チャンネル領域160a,160b及び制御ゲート電極140間には、一対のストレージノード130a,130bが介在されている。例えば、不揮発性メモリ素子100は、フラッシュメモリまたはSONOSメモリでありうる。ただし、本発明の不揮発性メモリ素子100は、その名称に限定されず、その構成により限定されるのみである。

【0015】

半導体基板110は、本体102と、本体102から突出されるように形成され、互いに離隔された一対のフィン105a,105bとを備える。例えば、フィン105a,105bは、X1方向に沿って互いに離隔され、X2方向に沿って伸張できる。半導体基板110は、バルクシリコン、バルクシリコン・ゲルマニウム、またはそれらの上にシリコンまたはシリコン・ゲルマニウムエピ層を含む複合構造でありうる。すなわち、フィン105a,105bは、本体102と同じ物質であるか、または本体102上に形成されたエピ層でもありうる。図面には、一対のフィン105a,105bが図示されているが、複数対のフィンがX1方向に羅列されうる。

【0016】

一対のフィン105a,105bの間には、埋没絶縁膜115が埋め込まれている。埋没絶縁膜115は、フィン105a,105bの内側面を絶縁させる。フィン105a,105bの外側面には、本体102から所定高さの素子分離膜120が形成されうる。すなわち、素子分離膜120は、フィン105a,105bの外側面の下端部分を覆っているが、フィン105a,105bの上端部分は、露出している。その名称に制限されず、本発明にて埋没絶縁膜115及び素子分離膜120は、フィン105a,105b及び素子を分離させる役割を果たすことができる。例えば、埋没絶縁膜115及び素子分離膜120は、絶縁特性と埋め込み特性の良好なシリコン酸化膜を含みうる。

【0017】

X1方向を基準とするとき、順に、埋没絶縁膜115、フィン105a,105bの一つ及び制御ゲート電極140順の積層構造、すなわち、SOI構造が形成されうる。ただし、フィン105a,105bは、X3方向に沿って本体102と連結されているという点で、活性領域が本体からフローティングされた通常のSOI構造と異なる。従って、本発明では、半導体基板110の構造をSOI類似(SOI−like)構造と呼び、その特徴は後述する。

【0018】

フィン105a,105bの外側面と上面上には、それぞれゲート絶縁膜125a,125bが形成されうる。ゲート絶縁膜125a,125bは、電荷のトンネルリング通路になるという点で、トンネルリング絶縁膜と呼ばれもする。例えば、ゲート絶縁膜125a,125bは、シリコン酸化膜、シリコン窒化膜または高誘電率膜から形成されるか、またはそれらの複合膜から形成されうる。

【0019】

ゲート絶縁膜125a,125bと制御ゲート電極140との間の少なくとも一部分には、それぞれストレージノード130a,130bが介在されうる。例えば、ストレージノード130a,130bは、フィン105a,105bの外側面の側壁に形成され、フィン105a,105bの上面に沿っては、形成されない。なぜなら、フィン105a,105bの上面が側面に比べて相対的に面積が小さいためである。

【0020】

ストレージノード130a,130bは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成されうる。例えば、ポリシリコンまたはシリコンゲルマニウムから形成されたストレージノード130a,130bは、フローティング電荷保存層として使われうる。他の例として、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜から形成されたストレージノード130a,130bは、局部的な電荷トラップ層として利用されうる。フラッシュメモリは、フローティング電荷保存層を利用し、SONOSメモリは、電荷トラップ層を利用できる。

【0021】

チャンネル領域160a,160bは、フィン105a,105bの外側面の上端部分と上面の表面付近とに形成されうる。フィン105a,105bの内側面には、埋没絶縁膜115が埋め込まれており、チャンネルが形成されない。ただし、相対的な面積を考慮すれば、主要な電荷の伝導通路は、フィン105a,105bの外側面に形成されたチャンネル領域160a,160bになりうる。

【0022】

フィン105a,105bの高さ、さらに具体的には、素子分離膜120により露出されるフィン105a,105bの上端部分の高さを調節することにより、チャンネル領域160a,160bの面積を調節できる。従って、フィン105a,105bに形成されたチャンネル領域160a,160bを利用すれば、不揮発性メモリ素子100の動作電流、すなわち速度を速くでき、その結果、不揮発性メモリ素子100の性能を高められる。

【0023】

チャンネル領域160a,160b両側のフィン105a,105b部分には、少なくとも一対のソース145及びドレイン150が形成されうる。ソース145及びドレイン150は、形式上の区分に過ぎず、入れ替わって呼ばれることもある。ソース145及びドレイン150は、隣接するチャンネル領域160a,160bに共有されうる。ソース145及びドレイン150は、本体102または残りのフィン105a,105b領域にダイオード接合されている。例えば、ソース145及びドレイン150がn型不純物でドーピングされている場合、残りのフィン105a,105b領域または本体102は、p型不純物でドーピングされうる。

【0024】

制御ゲート電極140は、チャンネル領域160a,160b及び埋没絶縁膜115を覆い包み、素子分離膜120により本体102と絶縁されている。すなわち、制御ゲート電極140は、X1方向に伸張するように形成され、X2方向に沿って互いに離隔されうる。制御ゲート電極140の数は、本発明の範囲を制限しない。制御ゲート電極140は、ポリシリコン、金属、金属シリサイドまたはこれらの複合膜から形成されうる。

【0025】

たとえ図面には図示されていないとしても、不揮発性メモリ素子100は、制御ゲート電極140とストレージノード130a,130bとを絶縁するブロッキング絶縁膜をさらに備えることができる。特に、ストレージノード130a,130bがポリシリコンまたはシリコン・ゲルマニウムのような伝導性物質から形成されている場合には、ブロッキング絶縁膜が必要である。例えば、ブロッキング絶縁膜は、シリコン酸化膜により形成されうる。

【0026】

不揮発性メモリ素子100の動作特性について述べれば、フィン105a,105bに形成されたチャンネル領域160a,160b、ソース145及びドレイン150の空乏領域(depletion region)は、制限されうる。特に、フィン105a,105bの幅が薄いほど、空乏領域は、さらに制限されうる。さらに具体的に見れば、空乏領域は、フィン105a,105bの幅方向、X1方向にはかなり制限され、ただし、X3方向に沿ってのみ形成されうる。しかし、フィン105a,105bの幅が狭くなれば、X3方向に沿って形成された空乏領域の影響は、相当に縮小されるであろう。

【0027】

従って、フィン105a,105bが本体102に連結されているにもかかわらず、フィン105a,105bは、SOI構造と類似した、すなわち、SOI類似構造となる。それにより、空乏領域の拡張によって発生しうるオフ電流及び接合漏れ電流が減少しうる。それにもかかわらず、本体102に電圧を印加することにより、フィン105a,105bにボディバイアスを印加できるという長所は維持される。

【0028】

本発明による不揮発性メモリ素子100の例示的な回路配置が図3に図示されている。図1ないし図3を参照すれば、不揮発性メモリ素子100は、NAND構造のフラッシュメモリまたはSONOSメモリでありうる。制御ゲート電極140は、ワードラインWLとして利用され、フィン105a,105bは、ビットラインBLとして利用されうる。さらに具体的に見れば、フィン105a,105bのソース145及びドレイン150がビットラインBLに連結されうる。1つのNANDセルの単位により、ワードラインWLの数が決定されうる。

【0029】

一対のNANDセルは、埋没絶縁膜115を基準に互いに絶縁されうる。ビットラインBLは、ストリング選択ライン(SSL:String Select Line)を経由してワードラインWLと連結され、接地選択ライン(GSL:Ground Select Line)を経由して接地された共通ソースライン(CSL:Common Source Line)と連結されうる。従って、SSL及びGSLをターンオンさせ、1本のビットラインBLを選択することにより、一列に配置されたNANDセルに接近できる。NANDセルの具体的な動作は、該当技術分野で当業者に公知であるので、さらに詳細な説明は省略する。

【0030】

制御ゲート電極140のゲート長W1を1Fとするとき、フィン105a,105bの幅W2は、0.25F、埋没絶縁膜115の幅W3は、0.5Fとすることができる。一対のNANDセルを構成するフィン105a,105bそれぞれの外側面に隣接した素子分離膜120の幅W4は、それぞれ0.5Fでありうる。従って、ワードラインWL側、すなわち、X1方向を基準とするとき、一対のNANDセルの長さは、2Fとなる。また、制御ゲート電極140の離隔距離W5は1Fでありうる。従って、ビットラインBL、すなわち、X2方向を基準とするとき、1つの制御ゲート電極140を含む単位セルの長さは、2Fになりうる。一対の単位セルがX2方向に連結され、一対のNANDセル構造を形成できる。

【0031】

従って、2FX2F面積内に1本のワードラインWL及び2本のビットラインBLが含まれうる。すなわち、一対の単位セルが2FX2F面積内に形成されうる。従って、従来の2FX2F面積内に1つの単位セルが形成されることに比べ、本発明による不揮発性メモリ素子は、単位セル等の集積度を二倍とすることができる。すなわち、埋没絶縁膜115により分離された一対のNANDセルが従来の1つのNANDセルと同じ面積を占める。従って、1つのNANDセルが単一ビットを保存するSLC(Single Level Cell)方式の動作を行う場合、2ビットを作るために2FX2Fの面積が必要であり、ビット当たりの面積は、2F2になりうる。他の例として、1つのNANDセルが2ビットを保存するMLC(Multi Level Cell)方式の動作を行う場合、4ビットを作るために、2FX2F面積が必要でビット当たりの面積は1F2になりうる。

【0032】

図4ないし図11は、本発明の一実施形態による不揮発性メモリ素子の製造方法を説明する断面図である。前記製造方法による不揮発性メモリ素子の構造は、図1ないし図3の説明を参照できる。図4ないし図11は、図1のX1方向、すなわちI−I’で切り取った断面図である。

【0033】

図4を参照すれば、半導体基板205上に、第1絶縁層パターン208を形成する。例えば、第1絶縁層パターン208は、シリコン酸化膜により形成されうる。次に、第1絶縁層パターン208の側壁に第2絶縁層スペーサ212を形成する。例えば、第2絶縁層スペーサ212は、シリコン窒化膜でありうる。さらに具体的に見れば、第2絶縁層スペーサ212は、第2絶縁層(図示せず)を形成し、これを異方性エッチングして形成できる。

【0034】

図5を参照すれば、第1絶縁層パターン(図4の208)及び第2絶縁層スペーサ(図4の212)をエッチング保護膜として半導体基板205をエッチングし、第1トレンチ215を形成する。例えば、第1トレンチ215の幅は、後ほど形成される制御ゲート電極(図11の250)のゲート長を基準に、0.5Fに形成されうる。この場合、制御ゲート電極(図11の250)のゲート長は、1Fになりうる。次に、第1絶縁層パターン208及び第2絶縁層スペーサ212を除去する。

【0035】

図6を参照すれば、第1トレンチ215を埋め込み、第1トレンチ215の両方向に半導体基板205上に所定幅ほど拡張する第1フォトレジストパターン220を形成する。例えば、第1フォトレジストパターン220は、フォトレジスト層(図示せず)を、第1トレンチ215が形成された結果物の全面に形成し、フォトレジスト層をフォトリソグラフィ及びエッチング技術を利用してパターニングすることによって形成できる。

【0036】

図7を参照すれば、第1フォトレジストパターン(図6の220)をエッチング保護膜として前記半導体基板205をエッチングし、第2トレンチ222を形成する。次に、第1フォトレジストパターン(図6の220)を除去することにより、第1トレンチ215及び第2トレンチ222に限定され、半導体基板205から突出された少なくとも一対のフィン210を形成する。フィン210の幅は、第1フォトレジストパターン(図6の220)の半導体基板205上に拡張された幅により決定されうる。例えば、フィン210の幅は、0.25Fに形成されうる。

【0037】

図8を参照すれば、フィン210を限定する第1トレンチ(図7の215)及び第2トレンチ(図7の222)を埋め込む第3絶縁層225を形成する。例えば、第3絶縁層225は、フィン210が形成された結果物全面にシリコン酸化膜を蒸着し、そのシリコン酸化膜をフィン210が露出されるまで平坦化して形成できる。平坦化は、エッチバックまたは化学的機械的研磨法を利用して行える。

【0038】

図9を参照すれば、第2トレンチ(図7の222)を埋め込んでいる第3絶縁層225を選択的に所定深さほどエッチングする。さらに具体的に見れば、フィン210及び前記第1トレンチ215を埋め込む第3絶縁層225の部分を覆う第2フォトレジストパターン230を形成する。次に、第2フォトレジストパターン230をエッチング保護膜として第3絶縁層225をエッチングする。それにより、フィン210の外側面が所定高さほど露出されうる。すなわち、フィン210の外側面の上端部分は、露出され、フィン210の下端部分は、エッチングされた第3絶縁層225’により囲まれている。次に、第2フォトレジストパターン230を除去する。

【0039】

図10を参照すれば、第3絶縁層225を覆うフィン210の露出された外側面の上端部分及び上面上にゲート絶縁膜235を形成する。例えば、ゲート絶縁膜235は、シリコン酸化膜、シリコン窒化膜、高誘電膜またはそれらの複合膜でありうる。ゲート絶縁膜235は、フィン210を熱酸化させて形成するか、または化学気相蒸着法(CVD)を利用して物質膜を蒸着して形成することもできる。

【0040】

次に、フィン210の露出された外側面上に形成されたゲート絶縁膜235の側壁にストレージノード240を形成する。例えば、ストレージノード240は、半導体基板205上に直交するように形成されうる。ストレージノード240は、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成できる。

【0041】

次に、図11を参照すれば、ストレージノード240が形成された結果物上にフィン210及び第3絶縁層225を横切る制御ゲート電極250を形成する。制御ゲート電極250は、制御ゲート電極層(図示せず)を蒸着し、次に、制御ゲート電極層をフォトリソグラフィ及びエッチング技術を利用してパターニングすることによって形成されうる。制御ゲート電極層をパターニングする前に、制御ゲート電極層を平坦化するステップが付加されることもある。また、制御ゲート電極250の電極を形成する前に、ストレージノード240を覆い包むブロッキング絶縁膜(図示せず)をさらに形成することもできる。

【0042】

制御ゲート電極250の離隔距離は、1Fとすることができる。第3絶縁層225により分離された一対のストレージノード240を有する一対の単位セルは、2FX2F面積内に形成されうる。従って、本発明の製造方法による不揮発性メモリ素子は、ビット当たりの面積を基準とするとき、従来より二倍の集積度を有することができる。

【0043】

本発明の特定実施形態についての以上の説明は、例示及び説明を目的に提供された。本発明は、前記実施形態に限定されるものではなく、本発明の技術的思想内で該当分野で当業者により、前記実施形態を組み合わせて実施するなど、さまざまな多数の修正及び変更が可能であるということは、明白である。

【産業上の利用可能性】

【0044】

本発明のフィン型チャンネル領域を有する不揮発性メモリ素子及びその製造方法は、例えば、メモリ関連の技術分野に効果的に適用可能である。

【図面の簡単な説明】

【0045】

【図1】本発明の一実施形態による不揮発性メモリ素子を示す斜視図である。

【図2A】図1の不揮発性メモリ素子のI−I’で切り取った断面図である。

【図2B】図1の不揮発性メモリ素子のII−II’で切り取った断面図である。

【図3】本発明の一実施形態によるNAND構造の不揮発性メモリ素子の回路配置を示す概略図である。

【図4】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図5】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図6】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図7】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図8】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図9】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図10】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図11】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【符号の説明】

【0046】

100 不揮発性メモリ素子

102 本体

105a,105b,210 フィン

110,205 半導体基板

115 埋没絶縁膜

120 素子分離膜

125a,125b,235 ゲート絶縁膜

130a,130b,240 ストレージノード

140,250 制御ゲート電極

145 ソース

150 ドレイン

160a,160b チャンネル領域

208 第1絶縁層パターン

212 第2絶縁層スペーサ

215 第1トレンチ

220 第1フォトレジストパターン

222 第2トレンチ

225,225’ 第3絶縁層

230 第2フォトレジストパターン

BL ビットライン

CSL 共通ソースライン

GSL 接地選択ライン

SSL ストリング選択ライン

WL ワードライン

W1 制御ゲート電極のゲート長

W2 フィンの幅

W3 埋没絶縁膜の幅

W4 素子分離膜の幅

W5 制御ゲート電極の離隔距離

【技術分野】

【0001】

本発明は、不揮発性メモリ素子に係り、特に、フィン型チャンネル領域を具備する不揮発性メモリ素子及びその製造方法に関する。例えば、本発明による不揮発性メモリ素子は、フラッシュメモリ及びSONOSメモリを含みうる。

【背景技術】

【0002】

不揮発性メモリ素子、例えば、フラッシュメモリは、制御ゲート電極と半導体基板との間に伝導性フローティングゲート電極を介在している。かかるフローティングゲート電極は、電荷保存のためのストレージノードとして利用される。フラッシュメモリは、フローティングゲート電極の電荷の蓄積の有無によって半導体基板のスレショルド電圧が変わることを利用し、半導体基板に伝導性チャンネル形成の有無、すなわち、電流フローの有無を判読する。一方、他の不揮発性メモリ素子、例えば、SONOSメモリは、制御ゲート電極と半導体基板との間に電荷トラップ型ストレージノードを介在している。SONOSメモリは、フラッシュメモリとほとんど類似した動作を行う。

【0003】

しかし、不揮発性メモリ素子において、微細工程技術の限界により、メモリ集積度及びメモリ速度増大は限界に直面している。それにより、さらに狭幅の微細工程技術を利用する以外に、メモリ容量及びメモリ速度を増大させることができる方法が研究されている。

【0004】

例えば、David M.Friedらによる特許文献1は、フィン−FET及びフィンメモリセルについて開示している。フィン−FETは、魚のヒレ状に形成されたフィンの上面及び側面をチャンネル領域として利用できる。それにより、フィン−FETは、平面形トランジスタよりチャンネル面積を広くでき、大きい電流のフローを提供できる。その結果、フィン−FETは、平面形トランジスタより高い性能を提供できる。

【0005】

しかし、前記特許文献1によるフィン−FETは、SOI基板を利用して製造されることにより、フィンが基板本体からフローティングされるという問題がある。それにより、ボディ・バイアス(body−bias)を利用したトランジスタのスレショルド電圧制御が不可能であり、その結果、CMOSトランジスタのスレショルド電圧調節が困難となりうる。また、従来のフィンメモリセルは、2ビット動作を提供するために1Fのゲート長を基準とし、少なくとも2FX2Fの面積を利用しており、ビット当たりの面積が2F2と大きくなってしまうという問題がある。その結果、フィンメモリセルの集積度が制限されうる。

【特許文献1】米国特許6,664,582号明細書

【発明の開示】

【発明が解決しようとする課題】

【0006】

従って、本発明が解決しようとする技術的課題は、前述の問題点を克服するためであり、ボディバイアス制御が可能であり、かつビット当たりの面積を減少させて高集積の可能な高性能不揮発性メモリ素子を提供するところにある。

【0007】

本発明が解決しようとする他の技術的課題は、前記不揮発性メモリ素子の製造方法を提供するところにある。

【課題を解決するための手段】

【0008】

前記技術的課題を解決するための本発明の一様態によれば、本体及び前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板と、前記一対のフィンの間を埋め込み、前記本体上に形成された第1絶縁膜と、前記一方向に沿って所定間隔離隔され、前記一対のフィンにそれぞれ形成された少なくとも一対のソース及びドレインと、前記一対のソース及びドレイン間にある前記フィン部分の少なくとも外側面の上端部分及び上面の各表面付近にそれぞれ形成された少なくとも一対のチャンネル領域と、前記チャンネル領域上に形成された第2絶縁膜と、前記第1絶縁膜及び前記第2絶縁膜上を横切り、前記一方向と異なる方向に伸張し、前記半導体基板から絶縁された少なくとも一つ以上の制御ゲート電極と、前記制御ゲート電極と、前記一対のフィンの外側面の上端部分に形成されたチャンネル領域との間にそれぞれ介在された少なくとも一対のストレージノードとを備える不揮発性メモリ素子が提供される。

【0009】

前記技術的課題を解決するための本発明の他の様態によれば、本体及び前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板の前記一対のフィンからなる一対のビットラインと、前記一対のビットライン間を絶縁するために、前記一対のフィン及び前記本体間を埋め込む第1絶縁膜と、前記一対のフィンを横切ってそれぞれ伸張し、前記一方向に離隔されて配置され、前記半導体基板とそれぞれ絶縁された複数の制御ゲート電極からなる複数のワードラインと、前記ワードライン及び前記一対のフィン間に介在された第2絶縁膜と、前記ワードライン及び前記第2絶縁膜間の少なくとも一部分にそれぞれ介在された一対のストレージノードとを備えるNAND構造の不揮発性メモリ素子が提供される。

【0010】

前記他の技術的課題を解決するための本発明の一様態によれば、次のステップを含む不揮発性メモリ素子の製造方法が提供される。半導体基板上に第1絶縁層パターンを形成する。前記第1絶縁層パターンの側壁に、第2絶縁層スペーサを形成する。前記第1絶縁層パターン及び前記第2絶縁層スペーサをエッチング保護膜として前記半導体基板をエッチングし、第1トレンチを形成する。前記第1トレンチを埋め込み、前記第1トレンチの両方向の前記半導体基板上に所定幅ほどそれぞれ拡張する第1フォトレジストパターンを形成する。前記第1フォトレジストパターンをエッチング保護膜として前記半導体基板をエッチングし、第2トレンチを形成する。前記第1フォトレジストパターンを除去し、前記第1トレンチ及び第2トレンチにより限定され、前記半導体基板から突出された少なくとも一対のフィンを形成する。前記フィンを限定する前記第1トレンチ及び第2トレンチを埋め込む第3絶縁層を形成する。前記第2トレンチを埋め込んでいる前記第3絶縁層の部分を選択的に所定深さほどエッチングし、前記第1トレンチを埋め込む前記第3絶縁層の部分を覆う前記フィンの外側面を所定高さほど露出する。前記フィンの露出された外側面及び上面上にゲート絶縁膜を形成する。前記フィンの露出された外側面上に形成されたゲート絶縁膜部分の側壁にそれぞれストレージノードを形成する。前記ストレージノードが形成された結果物上に、前記フィン及び前記第3絶縁層を横切る制御ゲート電極を形成する。

【発明の効果】

【0011】

本発明による不揮発性メモリ素子は、SOI類似構造を利用しており、オフ電流を下げることができ、接合漏れ電流を減少させることができる。

【発明を実施するための最良の形態】

【0012】

以下、添付した図面を参照しつつ、本発明による望ましい実施形態を説明することにより、本発明を詳細に説明する。しかし、本発明は、以下にで開示される実施形態に限定されるものではなく、相異なる多様な形態に具現されるものであり、ただ本実施形態は、本発明の開示を完全なものにし、当業者に発明の範疇を完全に明らかにするために提供される。図面で、構成要素は、説明の便宜のためにその大きさが誇張されている。

【0013】

図1は、本発明の一実施形態による不揮発性メモリ素子100を示す斜視図である。図2Aは、図1の不揮発性メモリ素子100のI−I’で切り取った断面図であり、図2Bは、図1の不揮発性メモリ素子100のII−II’で切り取った断面図である。

【0014】

図1、図2A及び図2Bを参照すれば、不揮発性メモリ素子100は、一対のフィン105a,105bに形成されたチャンネル領域160a,160bと、フィン105a,105bを横切る複数の制御ゲート電極140とを備える。チャンネル領域160a,160b及び制御ゲート電極140間には、一対のストレージノード130a,130bが介在されている。例えば、不揮発性メモリ素子100は、フラッシュメモリまたはSONOSメモリでありうる。ただし、本発明の不揮発性メモリ素子100は、その名称に限定されず、その構成により限定されるのみである。

【0015】

半導体基板110は、本体102と、本体102から突出されるように形成され、互いに離隔された一対のフィン105a,105bとを備える。例えば、フィン105a,105bは、X1方向に沿って互いに離隔され、X2方向に沿って伸張できる。半導体基板110は、バルクシリコン、バルクシリコン・ゲルマニウム、またはそれらの上にシリコンまたはシリコン・ゲルマニウムエピ層を含む複合構造でありうる。すなわち、フィン105a,105bは、本体102と同じ物質であるか、または本体102上に形成されたエピ層でもありうる。図面には、一対のフィン105a,105bが図示されているが、複数対のフィンがX1方向に羅列されうる。

【0016】

一対のフィン105a,105bの間には、埋没絶縁膜115が埋め込まれている。埋没絶縁膜115は、フィン105a,105bの内側面を絶縁させる。フィン105a,105bの外側面には、本体102から所定高さの素子分離膜120が形成されうる。すなわち、素子分離膜120は、フィン105a,105bの外側面の下端部分を覆っているが、フィン105a,105bの上端部分は、露出している。その名称に制限されず、本発明にて埋没絶縁膜115及び素子分離膜120は、フィン105a,105b及び素子を分離させる役割を果たすことができる。例えば、埋没絶縁膜115及び素子分離膜120は、絶縁特性と埋め込み特性の良好なシリコン酸化膜を含みうる。

【0017】

X1方向を基準とするとき、順に、埋没絶縁膜115、フィン105a,105bの一つ及び制御ゲート電極140順の積層構造、すなわち、SOI構造が形成されうる。ただし、フィン105a,105bは、X3方向に沿って本体102と連結されているという点で、活性領域が本体からフローティングされた通常のSOI構造と異なる。従って、本発明では、半導体基板110の構造をSOI類似(SOI−like)構造と呼び、その特徴は後述する。

【0018】

フィン105a,105bの外側面と上面上には、それぞれゲート絶縁膜125a,125bが形成されうる。ゲート絶縁膜125a,125bは、電荷のトンネルリング通路になるという点で、トンネルリング絶縁膜と呼ばれもする。例えば、ゲート絶縁膜125a,125bは、シリコン酸化膜、シリコン窒化膜または高誘電率膜から形成されるか、またはそれらの複合膜から形成されうる。

【0019】

ゲート絶縁膜125a,125bと制御ゲート電極140との間の少なくとも一部分には、それぞれストレージノード130a,130bが介在されうる。例えば、ストレージノード130a,130bは、フィン105a,105bの外側面の側壁に形成され、フィン105a,105bの上面に沿っては、形成されない。なぜなら、フィン105a,105bの上面が側面に比べて相対的に面積が小さいためである。

【0020】

ストレージノード130a,130bは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成されうる。例えば、ポリシリコンまたはシリコンゲルマニウムから形成されたストレージノード130a,130bは、フローティング電荷保存層として使われうる。他の例として、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜から形成されたストレージノード130a,130bは、局部的な電荷トラップ層として利用されうる。フラッシュメモリは、フローティング電荷保存層を利用し、SONOSメモリは、電荷トラップ層を利用できる。

【0021】

チャンネル領域160a,160bは、フィン105a,105bの外側面の上端部分と上面の表面付近とに形成されうる。フィン105a,105bの内側面には、埋没絶縁膜115が埋め込まれており、チャンネルが形成されない。ただし、相対的な面積を考慮すれば、主要な電荷の伝導通路は、フィン105a,105bの外側面に形成されたチャンネル領域160a,160bになりうる。

【0022】

フィン105a,105bの高さ、さらに具体的には、素子分離膜120により露出されるフィン105a,105bの上端部分の高さを調節することにより、チャンネル領域160a,160bの面積を調節できる。従って、フィン105a,105bに形成されたチャンネル領域160a,160bを利用すれば、不揮発性メモリ素子100の動作電流、すなわち速度を速くでき、その結果、不揮発性メモリ素子100の性能を高められる。

【0023】

チャンネル領域160a,160b両側のフィン105a,105b部分には、少なくとも一対のソース145及びドレイン150が形成されうる。ソース145及びドレイン150は、形式上の区分に過ぎず、入れ替わって呼ばれることもある。ソース145及びドレイン150は、隣接するチャンネル領域160a,160bに共有されうる。ソース145及びドレイン150は、本体102または残りのフィン105a,105b領域にダイオード接合されている。例えば、ソース145及びドレイン150がn型不純物でドーピングされている場合、残りのフィン105a,105b領域または本体102は、p型不純物でドーピングされうる。

【0024】

制御ゲート電極140は、チャンネル領域160a,160b及び埋没絶縁膜115を覆い包み、素子分離膜120により本体102と絶縁されている。すなわち、制御ゲート電極140は、X1方向に伸張するように形成され、X2方向に沿って互いに離隔されうる。制御ゲート電極140の数は、本発明の範囲を制限しない。制御ゲート電極140は、ポリシリコン、金属、金属シリサイドまたはこれらの複合膜から形成されうる。

【0025】

たとえ図面には図示されていないとしても、不揮発性メモリ素子100は、制御ゲート電極140とストレージノード130a,130bとを絶縁するブロッキング絶縁膜をさらに備えることができる。特に、ストレージノード130a,130bがポリシリコンまたはシリコン・ゲルマニウムのような伝導性物質から形成されている場合には、ブロッキング絶縁膜が必要である。例えば、ブロッキング絶縁膜は、シリコン酸化膜により形成されうる。

【0026】

不揮発性メモリ素子100の動作特性について述べれば、フィン105a,105bに形成されたチャンネル領域160a,160b、ソース145及びドレイン150の空乏領域(depletion region)は、制限されうる。特に、フィン105a,105bの幅が薄いほど、空乏領域は、さらに制限されうる。さらに具体的に見れば、空乏領域は、フィン105a,105bの幅方向、X1方向にはかなり制限され、ただし、X3方向に沿ってのみ形成されうる。しかし、フィン105a,105bの幅が狭くなれば、X3方向に沿って形成された空乏領域の影響は、相当に縮小されるであろう。

【0027】

従って、フィン105a,105bが本体102に連結されているにもかかわらず、フィン105a,105bは、SOI構造と類似した、すなわち、SOI類似構造となる。それにより、空乏領域の拡張によって発生しうるオフ電流及び接合漏れ電流が減少しうる。それにもかかわらず、本体102に電圧を印加することにより、フィン105a,105bにボディバイアスを印加できるという長所は維持される。

【0028】

本発明による不揮発性メモリ素子100の例示的な回路配置が図3に図示されている。図1ないし図3を参照すれば、不揮発性メモリ素子100は、NAND構造のフラッシュメモリまたはSONOSメモリでありうる。制御ゲート電極140は、ワードラインWLとして利用され、フィン105a,105bは、ビットラインBLとして利用されうる。さらに具体的に見れば、フィン105a,105bのソース145及びドレイン150がビットラインBLに連結されうる。1つのNANDセルの単位により、ワードラインWLの数が決定されうる。

【0029】

一対のNANDセルは、埋没絶縁膜115を基準に互いに絶縁されうる。ビットラインBLは、ストリング選択ライン(SSL:String Select Line)を経由してワードラインWLと連結され、接地選択ライン(GSL:Ground Select Line)を経由して接地された共通ソースライン(CSL:Common Source Line)と連結されうる。従って、SSL及びGSLをターンオンさせ、1本のビットラインBLを選択することにより、一列に配置されたNANDセルに接近できる。NANDセルの具体的な動作は、該当技術分野で当業者に公知であるので、さらに詳細な説明は省略する。

【0030】

制御ゲート電極140のゲート長W1を1Fとするとき、フィン105a,105bの幅W2は、0.25F、埋没絶縁膜115の幅W3は、0.5Fとすることができる。一対のNANDセルを構成するフィン105a,105bそれぞれの外側面に隣接した素子分離膜120の幅W4は、それぞれ0.5Fでありうる。従って、ワードラインWL側、すなわち、X1方向を基準とするとき、一対のNANDセルの長さは、2Fとなる。また、制御ゲート電極140の離隔距離W5は1Fでありうる。従って、ビットラインBL、すなわち、X2方向を基準とするとき、1つの制御ゲート電極140を含む単位セルの長さは、2Fになりうる。一対の単位セルがX2方向に連結され、一対のNANDセル構造を形成できる。

【0031】

従って、2FX2F面積内に1本のワードラインWL及び2本のビットラインBLが含まれうる。すなわち、一対の単位セルが2FX2F面積内に形成されうる。従って、従来の2FX2F面積内に1つの単位セルが形成されることに比べ、本発明による不揮発性メモリ素子は、単位セル等の集積度を二倍とすることができる。すなわち、埋没絶縁膜115により分離された一対のNANDセルが従来の1つのNANDセルと同じ面積を占める。従って、1つのNANDセルが単一ビットを保存するSLC(Single Level Cell)方式の動作を行う場合、2ビットを作るために2FX2Fの面積が必要であり、ビット当たりの面積は、2F2になりうる。他の例として、1つのNANDセルが2ビットを保存するMLC(Multi Level Cell)方式の動作を行う場合、4ビットを作るために、2FX2F面積が必要でビット当たりの面積は1F2になりうる。

【0032】

図4ないし図11は、本発明の一実施形態による不揮発性メモリ素子の製造方法を説明する断面図である。前記製造方法による不揮発性メモリ素子の構造は、図1ないし図3の説明を参照できる。図4ないし図11は、図1のX1方向、すなわちI−I’で切り取った断面図である。

【0033】

図4を参照すれば、半導体基板205上に、第1絶縁層パターン208を形成する。例えば、第1絶縁層パターン208は、シリコン酸化膜により形成されうる。次に、第1絶縁層パターン208の側壁に第2絶縁層スペーサ212を形成する。例えば、第2絶縁層スペーサ212は、シリコン窒化膜でありうる。さらに具体的に見れば、第2絶縁層スペーサ212は、第2絶縁層(図示せず)を形成し、これを異方性エッチングして形成できる。

【0034】

図5を参照すれば、第1絶縁層パターン(図4の208)及び第2絶縁層スペーサ(図4の212)をエッチング保護膜として半導体基板205をエッチングし、第1トレンチ215を形成する。例えば、第1トレンチ215の幅は、後ほど形成される制御ゲート電極(図11の250)のゲート長を基準に、0.5Fに形成されうる。この場合、制御ゲート電極(図11の250)のゲート長は、1Fになりうる。次に、第1絶縁層パターン208及び第2絶縁層スペーサ212を除去する。

【0035】

図6を参照すれば、第1トレンチ215を埋め込み、第1トレンチ215の両方向に半導体基板205上に所定幅ほど拡張する第1フォトレジストパターン220を形成する。例えば、第1フォトレジストパターン220は、フォトレジスト層(図示せず)を、第1トレンチ215が形成された結果物の全面に形成し、フォトレジスト層をフォトリソグラフィ及びエッチング技術を利用してパターニングすることによって形成できる。

【0036】

図7を参照すれば、第1フォトレジストパターン(図6の220)をエッチング保護膜として前記半導体基板205をエッチングし、第2トレンチ222を形成する。次に、第1フォトレジストパターン(図6の220)を除去することにより、第1トレンチ215及び第2トレンチ222に限定され、半導体基板205から突出された少なくとも一対のフィン210を形成する。フィン210の幅は、第1フォトレジストパターン(図6の220)の半導体基板205上に拡張された幅により決定されうる。例えば、フィン210の幅は、0.25Fに形成されうる。

【0037】

図8を参照すれば、フィン210を限定する第1トレンチ(図7の215)及び第2トレンチ(図7の222)を埋め込む第3絶縁層225を形成する。例えば、第3絶縁層225は、フィン210が形成された結果物全面にシリコン酸化膜を蒸着し、そのシリコン酸化膜をフィン210が露出されるまで平坦化して形成できる。平坦化は、エッチバックまたは化学的機械的研磨法を利用して行える。

【0038】

図9を参照すれば、第2トレンチ(図7の222)を埋め込んでいる第3絶縁層225を選択的に所定深さほどエッチングする。さらに具体的に見れば、フィン210及び前記第1トレンチ215を埋め込む第3絶縁層225の部分を覆う第2フォトレジストパターン230を形成する。次に、第2フォトレジストパターン230をエッチング保護膜として第3絶縁層225をエッチングする。それにより、フィン210の外側面が所定高さほど露出されうる。すなわち、フィン210の外側面の上端部分は、露出され、フィン210の下端部分は、エッチングされた第3絶縁層225’により囲まれている。次に、第2フォトレジストパターン230を除去する。

【0039】

図10を参照すれば、第3絶縁層225を覆うフィン210の露出された外側面の上端部分及び上面上にゲート絶縁膜235を形成する。例えば、ゲート絶縁膜235は、シリコン酸化膜、シリコン窒化膜、高誘電膜またはそれらの複合膜でありうる。ゲート絶縁膜235は、フィン210を熱酸化させて形成するか、または化学気相蒸着法(CVD)を利用して物質膜を蒸着して形成することもできる。

【0040】

次に、フィン210の露出された外側面上に形成されたゲート絶縁膜235の側壁にストレージノード240を形成する。例えば、ストレージノード240は、半導体基板205上に直交するように形成されうる。ストレージノード240は、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成できる。

【0041】

次に、図11を参照すれば、ストレージノード240が形成された結果物上にフィン210及び第3絶縁層225を横切る制御ゲート電極250を形成する。制御ゲート電極250は、制御ゲート電極層(図示せず)を蒸着し、次に、制御ゲート電極層をフォトリソグラフィ及びエッチング技術を利用してパターニングすることによって形成されうる。制御ゲート電極層をパターニングする前に、制御ゲート電極層を平坦化するステップが付加されることもある。また、制御ゲート電極250の電極を形成する前に、ストレージノード240を覆い包むブロッキング絶縁膜(図示せず)をさらに形成することもできる。

【0042】

制御ゲート電極250の離隔距離は、1Fとすることができる。第3絶縁層225により分離された一対のストレージノード240を有する一対の単位セルは、2FX2F面積内に形成されうる。従って、本発明の製造方法による不揮発性メモリ素子は、ビット当たりの面積を基準とするとき、従来より二倍の集積度を有することができる。

【0043】

本発明の特定実施形態についての以上の説明は、例示及び説明を目的に提供された。本発明は、前記実施形態に限定されるものではなく、本発明の技術的思想内で該当分野で当業者により、前記実施形態を組み合わせて実施するなど、さまざまな多数の修正及び変更が可能であるということは、明白である。

【産業上の利用可能性】

【0044】

本発明のフィン型チャンネル領域を有する不揮発性メモリ素子及びその製造方法は、例えば、メモリ関連の技術分野に効果的に適用可能である。

【図面の簡単な説明】

【0045】

【図1】本発明の一実施形態による不揮発性メモリ素子を示す斜視図である。

【図2A】図1の不揮発性メモリ素子のI−I’で切り取った断面図である。

【図2B】図1の不揮発性メモリ素子のII−II’で切り取った断面図である。

【図3】本発明の一実施形態によるNAND構造の不揮発性メモリ素子の回路配置を示す概略図である。

【図4】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図5】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図6】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図7】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図8】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図9】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図10】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図11】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【符号の説明】

【0046】

100 不揮発性メモリ素子

102 本体

105a,105b,210 フィン

110,205 半導体基板

115 埋没絶縁膜

120 素子分離膜

125a,125b,235 ゲート絶縁膜

130a,130b,240 ストレージノード

140,250 制御ゲート電極

145 ソース

150 ドレイン

160a,160b チャンネル領域

208 第1絶縁層パターン

212 第2絶縁層スペーサ

215 第1トレンチ

220 第1フォトレジストパターン

222 第2トレンチ

225,225’ 第3絶縁層

230 第2フォトレジストパターン

BL ビットライン

CSL 共通ソースライン

GSL 接地選択ライン

SSL ストリング選択ライン

WL ワードライン

W1 制御ゲート電極のゲート長

W2 フィンの幅

W3 埋没絶縁膜の幅

W4 素子分離膜の幅

W5 制御ゲート電極の離隔距離

【特許請求の範囲】

【請求項1】

本体及び前記本体からそれぞれ突出し、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板と、

前記フィンの少なくとも外側面の上端部分及び上面の表面付近にそれぞれ形成された少なくとも一対のチャンネル領域と、

前記一方向と異なる方向に伸張し、前記半導体基板から絶縁された少なくとも一つ以上の制御ゲート電極と、

前記制御ゲート電極及び前記一対のフィンの外側面の上端部分に形成されたチャンネル領域間にそれぞれ介在された少なくとも一対のストレージノードとを備えることを特徴とする不揮発性メモリ素子。

【請求項2】

前記不揮発性メモリ素子は、NAND構造を有することを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項3】

前記フィンは、前記本体に対してフローティングされていないことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項4】

前記制御ゲート電極の前記一方向へのゲート長が1Fであり、前記フィンの前記他方向への幅は、それぞれ0.25Fであることを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項5】

前記一対のフィンをビットラインとして利用し、前記制御ゲート電極をワードラインとして利用することを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項6】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含むことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項7】

前記一対のフィン間を埋め込み、前記本体上に形成された第1絶縁膜と、

前記一方向に沿って所定間隔離隔され、前記一対のフィンにそれぞれ形成された少なくとも一対のソース及びドレインと、

前記チャンネル領域上に形成された第2絶縁膜とをさらに備え、前記一対のチャンネル領域は、前記一対のソース及びドレイン間に介在され、前記制御ゲート電極は、前記第1絶縁膜及び前記第2絶縁膜上を横切り、前記一方向と異なる方向に伸張したことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項8】

前記一対のフィンの外側面の下端部分及び前記本体上に、前記一対のフィンの外側面の上端部分を露出するように形成し、前記本体及び前記制御ゲート電極を絶縁させる第3絶縁膜をより備えることを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項9】

前記第1絶縁膜の前記他の方向への幅は、1Fであることを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項10】

前記第1絶縁膜は、シリコン酸化膜を含むことを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項11】

本体及び前記本体からそれぞれ突出し、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板の前記一対のフィンからなる一対のビットラインと、

前記一対のビットライン間を絶縁するために、前記一対のフィン及び前記本体間を埋め込む第1絶縁膜と、

前記一対のフィンを横切ってそれぞれ伸張し、前記一方向に離隔されるように配置され、前記半導体基板とそれぞれ絶縁された複数の制御ゲート電極からなる複数のワードラインと、

前記ワードライン及び前記一対のフィン間に介在された第2絶縁膜と、

前記ワードライン及び前記第2絶縁膜間の少なくとも一部分にそれぞれ介在された一対のストレージノードとを備えることを特徴とするNAND構造の不揮発性メモリ素子。

【請求項12】

前記制御ゲート電極の前記一方向へのゲート長が1Fであり、前記フィンの前記他方向への幅は、それぞれ0.25Fであることを特徴とする請求項11に記載の不揮発性メモリ素子。

【請求項13】

前記第1絶縁膜の前記他の方向への幅は、1Fであることを特徴とする請求項12に記載の不揮発性メモリ素子。

【請求項14】

前記制御ゲート電極の前記一方向への離隔距離は、1Fであることを特徴とする請求項12に記載の不揮発性メモリ素子。

【請求項15】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含むことを特徴とする請求項11に記載の不揮発性メモリ素子。

【請求項16】

前記第1絶縁膜は、シリコン酸化膜を含むことを特徴とする請求項15に記載の不揮発性メモリ素子。

【請求項17】

本体を含む半導体基板から前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを形成する段階と、

前記フィンの外側面上部及び上面上にゲート絶縁膜を形成する段階と、

前記フィンの外側面上に形成されたゲート絶縁膜部分の側壁にそれぞれストレージノードを形成する段階と、

前記ストレージノードが形成された結果物上に、前記フィンを横切る制御ゲート電極を形成する段階とを含むことを特徴とする不揮発性メモリ素子の製造方法。

【請求項18】

前記フィンは、前記本体に対してフローティングされていないことを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項19】

前記不揮発性メモリ素子は、NAND構造により製造することを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項20】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成することを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項21】

前記フィンを形成する段階は、

前記半導体基板上に第1絶縁層パターンを形成する段階と、

前記第1絶縁層パターンの側壁に第2絶縁層スペーサを形成する段階と、

前記第1絶縁層パターン及び前記第2絶縁層スペーサをエッチング保護膜として前記半導体基板をエッチングし、第1トレンチを形成する段階と、

前記第1トレンチを埋め込み、前記第1トレンチの両方向の前記半導体基板上に所定幅ほどそれぞれ拡張する第1フォトレジストパターンを形成する段階と、

前記第1フォトレジストパターンをエッチング保護膜として前記半導体基板をエッチングし、第2トレンチを形成する段階と、

前記第1フォトレジストパターンを除去し、前記第1トレンチ及び第2トレンチにより限定され、前記半導体基板から突出された少なくとも一対のフィンを形成する段階とを含むことを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項22】

前記制御ゲート電極のゲート長は1F、前記第1トレンチの幅は0.5F、前記第2トレンチの幅は1Fに形成することを特徴とする請求項21に記載の不揮発性メモリ素子の製造方法。

【請求項23】

前記フィンの幅は0.25Fにそれぞれ形成することを特徴とする請求項22に記載の不揮発性メモリ素子の製造方法。

【請求項24】

前記フィンを限定する前記第1トレンチ及び第2トレンチを埋め込む第3絶縁層を形成する段階と、

前記第2トレンチを埋め込んでいる前記第3絶縁層の部分を選択的に所定深さほどエッチングし、前記第1トレンチを埋め込む前記第3絶縁層の部分を覆う前記フィンの外側面を所定高さほど露出する段階とをさらに含み、

前記ゲート絶縁膜は、前記第3絶縁層を覆う前記フィンの露出された外側面及び上面上に形成され、

前記ストレージノードは、前記フィンの露出された外側面上に形成され、

前記制御ゲート電極は、前記第3絶縁層をさらに横切ることを特徴とする請求項21に記載の不揮発性メモリ素子の製造方法。

【請求項25】

前記第3絶縁層をエッチングする段階は、前記フィン及び前記第1トレンチを埋め込む前記第3絶縁層部分上に第2フォトレジストパターンを形成し、前記第2フォトレジストパターンをエッチング保護膜として前記第2トレンチを埋め込む前記第3絶縁層部分をエッチングすることを特徴とする請求項24に記載の不揮発性メモリ素子の製造方法。

【請求項26】

前記第3絶縁層は、シリコン酸化膜から形成することを特徴とする請求項24に記載の不揮発性メモリ素子の製造方法。

【請求項1】

本体及び前記本体からそれぞれ突出し、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板と、

前記フィンの少なくとも外側面の上端部分及び上面の表面付近にそれぞれ形成された少なくとも一対のチャンネル領域と、

前記一方向と異なる方向に伸張し、前記半導体基板から絶縁された少なくとも一つ以上の制御ゲート電極と、

前記制御ゲート電極及び前記一対のフィンの外側面の上端部分に形成されたチャンネル領域間にそれぞれ介在された少なくとも一対のストレージノードとを備えることを特徴とする不揮発性メモリ素子。

【請求項2】

前記不揮発性メモリ素子は、NAND構造を有することを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項3】

前記フィンは、前記本体に対してフローティングされていないことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項4】

前記制御ゲート電極の前記一方向へのゲート長が1Fであり、前記フィンの前記他方向への幅は、それぞれ0.25Fであることを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項5】

前記一対のフィンをビットラインとして利用し、前記制御ゲート電極をワードラインとして利用することを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項6】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含むことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項7】

前記一対のフィン間を埋め込み、前記本体上に形成された第1絶縁膜と、

前記一方向に沿って所定間隔離隔され、前記一対のフィンにそれぞれ形成された少なくとも一対のソース及びドレインと、

前記チャンネル領域上に形成された第2絶縁膜とをさらに備え、前記一対のチャンネル領域は、前記一対のソース及びドレイン間に介在され、前記制御ゲート電極は、前記第1絶縁膜及び前記第2絶縁膜上を横切り、前記一方向と異なる方向に伸張したことを特徴とする請求項1に記載の不揮発性メモリ素子。

【請求項8】

前記一対のフィンの外側面の下端部分及び前記本体上に、前記一対のフィンの外側面の上端部分を露出するように形成し、前記本体及び前記制御ゲート電極を絶縁させる第3絶縁膜をより備えることを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項9】

前記第1絶縁膜の前記他の方向への幅は、1Fであることを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項10】

前記第1絶縁膜は、シリコン酸化膜を含むことを特徴とする請求項7に記載の不揮発性メモリ素子。

【請求項11】

本体及び前記本体からそれぞれ突出し、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを備える半導体基板の前記一対のフィンからなる一対のビットラインと、

前記一対のビットライン間を絶縁するために、前記一対のフィン及び前記本体間を埋め込む第1絶縁膜と、

前記一対のフィンを横切ってそれぞれ伸張し、前記一方向に離隔されるように配置され、前記半導体基板とそれぞれ絶縁された複数の制御ゲート電極からなる複数のワードラインと、

前記ワードライン及び前記一対のフィン間に介在された第2絶縁膜と、

前記ワードライン及び前記第2絶縁膜間の少なくとも一部分にそれぞれ介在された一対のストレージノードとを備えることを特徴とするNAND構造の不揮発性メモリ素子。

【請求項12】

前記制御ゲート電極の前記一方向へのゲート長が1Fであり、前記フィンの前記他方向への幅は、それぞれ0.25Fであることを特徴とする請求項11に記載の不揮発性メモリ素子。

【請求項13】

前記第1絶縁膜の前記他の方向への幅は、1Fであることを特徴とする請求項12に記載の不揮発性メモリ素子。

【請求項14】

前記制御ゲート電極の前記一方向への離隔距離は、1Fであることを特徴とする請求項12に記載の不揮発性メモリ素子。

【請求項15】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含むことを特徴とする請求項11に記載の不揮発性メモリ素子。

【請求項16】

前記第1絶縁膜は、シリコン酸化膜を含むことを特徴とする請求項15に記載の不揮発性メモリ素子。

【請求項17】

本体を含む半導体基板から前記本体からそれぞれ突出され、一方向にそれぞれ伸張し互いに離隔される少なくとも一対のフィンを形成する段階と、

前記フィンの外側面上部及び上面上にゲート絶縁膜を形成する段階と、

前記フィンの外側面上に形成されたゲート絶縁膜部分の側壁にそれぞれストレージノードを形成する段階と、

前記ストレージノードが形成された結果物上に、前記フィンを横切る制御ゲート電極を形成する段階とを含むことを特徴とする不揮発性メモリ素子の製造方法。

【請求項18】

前記フィンは、前記本体に対してフローティングされていないことを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項19】

前記不揮発性メモリ素子は、NAND構造により製造することを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項20】

前記ストレージノードは、ポリシリコン、シリコンゲルマニウム、シリコンまたは金属ドット、ナノクリスタルまたはシリコン窒化膜を含んで形成することを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項21】

前記フィンを形成する段階は、

前記半導体基板上に第1絶縁層パターンを形成する段階と、

前記第1絶縁層パターンの側壁に第2絶縁層スペーサを形成する段階と、

前記第1絶縁層パターン及び前記第2絶縁層スペーサをエッチング保護膜として前記半導体基板をエッチングし、第1トレンチを形成する段階と、

前記第1トレンチを埋め込み、前記第1トレンチの両方向の前記半導体基板上に所定幅ほどそれぞれ拡張する第1フォトレジストパターンを形成する段階と、

前記第1フォトレジストパターンをエッチング保護膜として前記半導体基板をエッチングし、第2トレンチを形成する段階と、

前記第1フォトレジストパターンを除去し、前記第1トレンチ及び第2トレンチにより限定され、前記半導体基板から突出された少なくとも一対のフィンを形成する段階とを含むことを特徴とする請求項17に記載の不揮発性メモリ素子の製造方法。

【請求項22】

前記制御ゲート電極のゲート長は1F、前記第1トレンチの幅は0.5F、前記第2トレンチの幅は1Fに形成することを特徴とする請求項21に記載の不揮発性メモリ素子の製造方法。

【請求項23】

前記フィンの幅は0.25Fにそれぞれ形成することを特徴とする請求項22に記載の不揮発性メモリ素子の製造方法。

【請求項24】

前記フィンを限定する前記第1トレンチ及び第2トレンチを埋め込む第3絶縁層を形成する段階と、

前記第2トレンチを埋め込んでいる前記第3絶縁層の部分を選択的に所定深さほどエッチングし、前記第1トレンチを埋め込む前記第3絶縁層の部分を覆う前記フィンの外側面を所定高さほど露出する段階とをさらに含み、

前記ゲート絶縁膜は、前記第3絶縁層を覆う前記フィンの露出された外側面及び上面上に形成され、

前記ストレージノードは、前記フィンの露出された外側面上に形成され、

前記制御ゲート電極は、前記第3絶縁層をさらに横切ることを特徴とする請求項21に記載の不揮発性メモリ素子の製造方法。

【請求項25】

前記第3絶縁層をエッチングする段階は、前記フィン及び前記第1トレンチを埋め込む前記第3絶縁層部分上に第2フォトレジストパターンを形成し、前記第2フォトレジストパターンをエッチング保護膜として前記第2トレンチを埋め込む前記第3絶縁層部分をエッチングすることを特徴とする請求項24に記載の不揮発性メモリ素子の製造方法。

【請求項26】

前記第3絶縁層は、シリコン酸化膜から形成することを特徴とする請求項24に記載の不揮発性メモリ素子の製造方法。

【図1】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2A】

【図2B】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2007−36242(P2007−36242A)

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願番号】特願2006−200736(P2006−200736)

【出願日】平成18年7月24日(2006.7.24)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【Fターム(参考)】

【公開日】平成19年2月8日(2007.2.8)

【国際特許分類】

【出願日】平成18年7月24日(2006.7.24)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【Fターム(参考)】

[ Back to top ]