フィールド機器

【課題】製品毎に異なるファームウェアの統一化と選択的なインストールを可能とする。

【解決手段】センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納する。

【解決手段】センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器に関するものである。

【背景技術】

【0002】

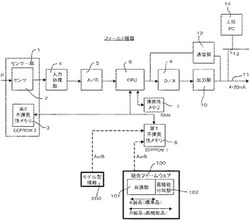

図7は、従来のフィールド機器の構成例を示す機能ブロック図である。以下で説明する実施例では、本発明が適用されるフィールド機器として、差圧/圧力伝送器への適用例を説明する。

【0003】

センサー部1は、差圧または圧力の物理量Pを入力するセンサー2と、センサー固有のパラメータを保持する第2不揮発性メモリ3(EEPROM_2)よりなる。センサー2の測定結果は入力処理部4で増幅・レンジ設定などの処理が実行され、A/D変換回路5でデジタル値に変換され、CPU6で信号処理される。

【0004】

CPU6は、ファームウェアが格納されてメイン処理を実行するためのRAM等による揮発性メモリ7と、ファームウェアやパラメーラ等を保持する第1不揮発性メモリ8(EEPROM_1)に接続されている。

【0005】

CPU6によるメイン処理の結果は、D/A変換回路9でアナログ値に変換され、出力部10により4−20mA等の電流信号に変換されて2線式の出力ケーブル11を介して外部機器に伝送される。

【0006】

CPU6と出力ケーブル11間には通信部12が接続され、通信部12によって、出力ケーブル11に接続されたネットワーク13を介してCPU6と上位PC14がハート等の通信規格でデジタル通信が可能となっている。

【0007】

差圧/圧力伝送器の製品ラインアップとして、標準製品(以下、製品A)と高機能製品(以下、製品B)の2機種が存在する場合を想定する。製品Aと製品Bの機能差は、第1不揮発性メモリ8にインストールされて保持されるファームウェアに依存する。

【0008】

一般に製品Aのファームウェアは、差圧/圧力伝送器の標準製品の仕様が記述された共通部で実現される。製品Bのファームウェアは、共通部の仕様とこれに付加した追加仕様が記述された形態をとる。追加仕様は、高度の診断アプリケーションや高精度の校正仕様等である。

【0009】

図7において、製品Aの仕様が記述されたファームウェア15と、製品Bの仕様が記述されたファームウェア16は、製造工程において選択的に第1不揮発メモリ8にインストールされることで2機種のラインアップを実現している。

【0010】

図8は、従来フィールド機器の製品Aおよび製品B毎のファームウェア読み込みのイメージ図である。図8(イ)は、ハードウェア的なインストールイメージ、図8(ロ)はソフトウェア的なインストールイメージを示している。

【0011】

図8(イ)において、製品(A)では、RAMおよび第1不揮発性メモリ(EEPROM_1)を保有するCPUアセンブリには、製品A用のファームウェアがインストールされ、第2不揮発性メモリ(EEPROM_2)を保有する共通仕様のセンサー部に実装される。

【0012】

製品(B)では、RAMおよび第1不揮発性メモリ(EEPROM_1)を保有するCPUアセンブリには、製品B用のファームウェアがインストールされ、第2不揮発性メモリ3(EEPROM_2)を保有する共通仕様のセンサー部に実装される。

【0013】

図8(ロ)に示すソフトウェ的なイメージは、製品(A)および製品(B)は共通である。ステップS1で第1および第2不揮発性メモリから内部データを読み込み、ステップS2の起動処理で揮発性メモリにこのデータを格納し、ステップS3のメイン処理で製品Aまたは製品Bの動作を実現させる。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2005−309913号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

従来構成のフィールド機器では、製品Aと製品Bの違いは、第1不揮発性メモリ8に保持されているデータ(伝送器として動作するのに必要なパラメータ群)の値と付加された追加仕様のファームウェアであり、メイン処理等(共通部の仕様を実行する処理)は同等であるのに、製品Aと製品Bとで別々のファームウェアを管理する必要があり、保守性に欠ける。また、別々にすることで開発及び生産時の工数が増加し、非効率である。

【0016】

本発明の目的は、製品毎に異なるファームウェアの統合化と選択的なインストールを可能とするフィールド機器を実現することにある。

【課題を解決するための手段】

【0017】

このような課題を達成するために、本発明は次の通りの構成になっている。

(1)センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、

前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、

前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、

前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納することを特徴とするフィールド機器。

【0018】

(2)前記モデル型情報保持手段は、前記第1不揮発性メモリに形成されることを特徴とする(1)に記載のフィールド機器。

【0019】

(3)前記センサー固有の情報を保持する第2不揮発性メモリを備え、

前記モデル型情報保持手段は、前記第2不揮発性メモリに形成されることを特徴とする(1)または(2)に記載のフィールド機器。

【0020】

(4)前記標準製品または前記高機能製品に実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴とする(1)に記載のフィールド機器。

【0021】

(5)通信ターミナルを介して行われる通信の種別情報を前記モデル型情報とすることを特徴とする(1)に記載のフィールド機器。

【発明の効果】

【0022】

本発明によれば、次のような効果を期待することができる。

(1)製品毎のファームウェアの統合が可能であり、統一化されることでメンテナンス等の保守性に優れる。

【0023】

(2)ファームウェアが統合されることで、開発工数および生産工数が削減でき、効率的である。CPUアセンブリに依存することなく、接続するセンサーによって製品Aでも製品Bでも動作可能である。例えば、製品Aで動作していたCPUアセンブリを製品Bのセンサーに接続することで、製品Bの動作をさせることも可能である。

【0024】

(3)製品A、製品Bの2種類に限定することなく、機種が3以上に増えても対応可能である。これにより複数の異なる機種を統合ファームウェアにより一元管理することが可能となる。

【図面の簡単な説明】

【0025】

【図1】本発明を適用したフィールド機器の一実施例を示す機能ブロック図である。

【図2】本発明フィールド機器のファームウェアおよびモデル型情報読み込みのイメージ図である。

【図3】ファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。

【図4】本発明を適用したフィールド機器の他の実施形態におけるファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。

【図5】本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。

【図6】本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。

【図7】従来のフィールド機器の構成例を示す機能ブロック図である。

【図8】従来フィールド機器のファームウェア読み込みのイメージ図である。

【発明を実施するための形態】

【0026】

以下、本発明を図面を用いて詳細に説明する。図1は、本発明を適用したフィールド機器の一実施例を示す機能ブロック図である。図7で説明した従来構成と同一要素には同一符号を付して説明を省略する。

【0027】

図7に示した従来構成と相違する本発明の特徴部は、統合ファームウェア100およびモデル型情報200にある。統合ファームウェア100の構成は、共通部101とこの共通部に追加記述された高機能付加部102よりなる。

【0028】

製品Aを実現する場合には、CPU6は、起動処理において、統合ファームウェア100から共通部101を読み出して揮発性メモリ7(RAM)に格納する。また、製品Bを実現する場合には、統合ファームウェア100から共通部101および高機能付加部102を結合したファームウェアを読み出してRAMに格納する。

【0029】

モデル型情報200は、製品Aと製品Bを識別するための情報であり、第1不揮発性メモリ8または第2不揮発性メモリ3に保持させることで、モデル型情報保持手段を実現させる。この情報は、保持するデータのサイズ、タイプは特に指定はなく、例えば、0ならば製品A、1ならば製品Bとする等、識別可能な2値データであればよい。

【0030】

CPU6は、第1不揮発性メモリ8または第2不揮発性メモリ3に形成されたモデル型情報保持手段から取得したモデル型情報200に基づいて、統合ファームウェア100の共通部101または統合ファームウェア全体(101+102)を選択的に読み出し、揮発メモリ7に格納する。

【0031】

図2は、本発明フィールド機器のファームウェアおよびモデル型情報読み込みのイメージ図である。図2(イ)は、ハードウェア的なインストールイメージ、図2(ロ)はソフトウェア的なインストールイメージを示している。

【0032】

図2(イ)において、製品(A)または製品Bを実現するためのファームウェアは、揮発性メモリおよび第1不揮発性メモリを保有する共通のCPUアセンブリの第1不揮発性メモリ8にインストールされている。

【0033】

モデル型情報保持手段から取得されるモデル型情報に基づき、製品(A)を製造する場合には、統合ファームウェア100の共通部101を読み出して不揮発性メモリに格納したCPUアセンブリを、第2不揮発性メモリ3を保有する共通仕様のセンサー部に実装する。

【0034】

モデル型情報保持手段から取得されるモデル型情報に基づき、製品(B)を製造する場合には、統合ファームウェア100より統合ファームウェア全体(101+102)を読み出して不揮発性メモリに格納したCPUアセンブリを、第2不揮発性メモリ3を保有する共通仕様のセンサー部に実装する。

【0035】

図2(ロ)に示すソフトウェ的なイメージは、製品(A)および製品(B)で共通であり、ステップS1で第1および第2不揮発性メモリから内部データを読み込み、ステップS2でモデル型情報を読み込み、ステップS3の起動処理で選択されたファームウェアのデータを揮発性メモリに格納し、ステップS4のメイン処理で製品Aまたは製品Bの動作を実現させる。

【0036】

図3は、ファームウェアおよびモデル型情報読み込みの処理手順を示す詳細フローチャートである。電源オン後のステップS1で第1不揮発性メモリ8から内部データ(ファームウェア)を取得する。

【0037】

モデル情報識別部のステップS2では仮決定処理を実行し、製品Aを製造モデルとして統合ファームウェアの共通部を読み込んで仮決定する。ステップS3では、第1不揮発性メモリ8(または第2不揮発性メモリ3)に形成されたモデル型情報保持手段からモデル型情報を取得し、揮発性メモリ7に格納する。

【0038】

起動処理部のステップS4では、取得したモデル型情報に基づいて統合ファームウェアから取得するデータを揮発メモリに格納する起動処理が実行され、ステップS5で製品Aと製品Bの分岐処理が実行される。

【0039】

メイン処理部のステップS6は、ステップS5の分岐処理が製品Aの場合には、製品Aとしてのメイン処理を開始する。メイン処理部のステップS7はステップS5の分岐処理が製品Bの場合には、製品Bしてのメイン処理を開始する。これらメイン処理は電源オフで終了する。

【0040】

図4は、本発明を適用したフィールド機器の他の実施形態におけるファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。不揮発性メモリ8のEEPROM_1が故障した場合の対策として、不揮発性メモリ3のEEPROM_2にもモデル型情報を持たせておき、EEPROM_1からモデル型情報が正常に読み込みができた場合はEEPROM_1の情報で動作し、EEPROM_1が故障(異常)の場合には、EEPROM_2のモデル型情報で動作するようにしたものである。

【0041】

図4のフローチャートのモデル識別部に追加されたステップS8は、不揮発性メモリ8のEEPROM_1のチェックを実行し、正常の場合には図3と同じ処理フローとなる。異常の場合にはステップS9で不揮発性メモリ3のEEPROM_2のチェックを実行し、正常の場合にはステップS10に進み、EEPROM_2のモデル型情報を取得しステップS4に進み、図3と同じ処理フローとなる。EEPROM_2も異常の場合には、ステップS6に進み、製品Aとしてメイン処理を開始する。

【0042】

図5は、本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。この実施例の特徴は、製品Aまたは製品Bに実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴としている。

【0043】

共通のCPUアセンブリにLCD1を接続すると、CPU6はLCD1を表すハードウェアの種別情報を取得し製品Aで動作し、LCD2を接続すると、CPU6はLCD2を表すハードウェアの種別情報を取得し製品Bで動作する。この場合、例えば、LCD1は高精度のフルドットタイプLCD、LCD2はセグメントタイプLCD等が考えられる。

【0044】

図6は、本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。この実施例の特徴は、接続される通信の種別情報を前記モデル型情報とすることを特徴としている。

【0045】

通信ターミナルを介して接続、実行される通信の形態が4−20mAの電流出力の場合には、CPU6は電流出力を表す通信の種別情報を取得し製品Aで動作する。接続される通信の形態がデジタル通信の場合には、CPU6はデジタル通信を表す通信の種別情報を取得し製品Bで動作する。接続される通信の形態が1−5Vの電圧出力の場合には、CPU6は電圧出力を表す通信の種別情報を取得し製品Cで動作する。

【0046】

以上説明した実施例では、フィールド機器として差圧/圧力伝送器を例示したが、本発明は複数モデルを製造するフィールド機器一般に適用することができる。

【0047】

また、実施例では、標準機能の製品Aと高機能が付加された製品Bの例を説明したが、これに限定されるものではなく、統合的ファームウェアを利用可能な3種以上のモデル型の製品製造に応用することが可能である。

【符号の説明】

【0048】

1 センサー部

2 センサー

3 第2不揮発性メモリ(EEPROM_2)

4 入力処理部

5 A/D変換回路

6 CPU

7 揮発性メモリ(RAM)

8 第1不揮発性メモリ(EEPROM_1)

9 D/A変換回路

10 出力部

100 統合ファームウェア

101 共通部

102 高機能付加部

200 モデル型情報

【技術分野】

【0001】

本発明は、センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器に関するものである。

【背景技術】

【0002】

図7は、従来のフィールド機器の構成例を示す機能ブロック図である。以下で説明する実施例では、本発明が適用されるフィールド機器として、差圧/圧力伝送器への適用例を説明する。

【0003】

センサー部1は、差圧または圧力の物理量Pを入力するセンサー2と、センサー固有のパラメータを保持する第2不揮発性メモリ3(EEPROM_2)よりなる。センサー2の測定結果は入力処理部4で増幅・レンジ設定などの処理が実行され、A/D変換回路5でデジタル値に変換され、CPU6で信号処理される。

【0004】

CPU6は、ファームウェアが格納されてメイン処理を実行するためのRAM等による揮発性メモリ7と、ファームウェアやパラメーラ等を保持する第1不揮発性メモリ8(EEPROM_1)に接続されている。

【0005】

CPU6によるメイン処理の結果は、D/A変換回路9でアナログ値に変換され、出力部10により4−20mA等の電流信号に変換されて2線式の出力ケーブル11を介して外部機器に伝送される。

【0006】

CPU6と出力ケーブル11間には通信部12が接続され、通信部12によって、出力ケーブル11に接続されたネットワーク13を介してCPU6と上位PC14がハート等の通信規格でデジタル通信が可能となっている。

【0007】

差圧/圧力伝送器の製品ラインアップとして、標準製品(以下、製品A)と高機能製品(以下、製品B)の2機種が存在する場合を想定する。製品Aと製品Bの機能差は、第1不揮発性メモリ8にインストールされて保持されるファームウェアに依存する。

【0008】

一般に製品Aのファームウェアは、差圧/圧力伝送器の標準製品の仕様が記述された共通部で実現される。製品Bのファームウェアは、共通部の仕様とこれに付加した追加仕様が記述された形態をとる。追加仕様は、高度の診断アプリケーションや高精度の校正仕様等である。

【0009】

図7において、製品Aの仕様が記述されたファームウェア15と、製品Bの仕様が記述されたファームウェア16は、製造工程において選択的に第1不揮発メモリ8にインストールされることで2機種のラインアップを実現している。

【0010】

図8は、従来フィールド機器の製品Aおよび製品B毎のファームウェア読み込みのイメージ図である。図8(イ)は、ハードウェア的なインストールイメージ、図8(ロ)はソフトウェア的なインストールイメージを示している。

【0011】

図8(イ)において、製品(A)では、RAMおよび第1不揮発性メモリ(EEPROM_1)を保有するCPUアセンブリには、製品A用のファームウェアがインストールされ、第2不揮発性メモリ(EEPROM_2)を保有する共通仕様のセンサー部に実装される。

【0012】

製品(B)では、RAMおよび第1不揮発性メモリ(EEPROM_1)を保有するCPUアセンブリには、製品B用のファームウェアがインストールされ、第2不揮発性メモリ3(EEPROM_2)を保有する共通仕様のセンサー部に実装される。

【0013】

図8(ロ)に示すソフトウェ的なイメージは、製品(A)および製品(B)は共通である。ステップS1で第1および第2不揮発性メモリから内部データを読み込み、ステップS2の起動処理で揮発性メモリにこのデータを格納し、ステップS3のメイン処理で製品Aまたは製品Bの動作を実現させる。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開2005−309913号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

従来構成のフィールド機器では、製品Aと製品Bの違いは、第1不揮発性メモリ8に保持されているデータ(伝送器として動作するのに必要なパラメータ群)の値と付加された追加仕様のファームウェアであり、メイン処理等(共通部の仕様を実行する処理)は同等であるのに、製品Aと製品Bとで別々のファームウェアを管理する必要があり、保守性に欠ける。また、別々にすることで開発及び生産時の工数が増加し、非効率である。

【0016】

本発明の目的は、製品毎に異なるファームウェアの統合化と選択的なインストールを可能とするフィールド機器を実現することにある。

【課題を解決するための手段】

【0017】

このような課題を達成するために、本発明は次の通りの構成になっている。

(1)センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、

前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、

前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、

前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納することを特徴とするフィールド機器。

【0018】

(2)前記モデル型情報保持手段は、前記第1不揮発性メモリに形成されることを特徴とする(1)に記載のフィールド機器。

【0019】

(3)前記センサー固有の情報を保持する第2不揮発性メモリを備え、

前記モデル型情報保持手段は、前記第2不揮発性メモリに形成されることを特徴とする(1)または(2)に記載のフィールド機器。

【0020】

(4)前記標準製品または前記高機能製品に実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴とする(1)に記載のフィールド機器。

【0021】

(5)通信ターミナルを介して行われる通信の種別情報を前記モデル型情報とすることを特徴とする(1)に記載のフィールド機器。

【発明の効果】

【0022】

本発明によれば、次のような効果を期待することができる。

(1)製品毎のファームウェアの統合が可能であり、統一化されることでメンテナンス等の保守性に優れる。

【0023】

(2)ファームウェアが統合されることで、開発工数および生産工数が削減でき、効率的である。CPUアセンブリに依存することなく、接続するセンサーによって製品Aでも製品Bでも動作可能である。例えば、製品Aで動作していたCPUアセンブリを製品Bのセンサーに接続することで、製品Bの動作をさせることも可能である。

【0024】

(3)製品A、製品Bの2種類に限定することなく、機種が3以上に増えても対応可能である。これにより複数の異なる機種を統合ファームウェアにより一元管理することが可能となる。

【図面の簡単な説明】

【0025】

【図1】本発明を適用したフィールド機器の一実施例を示す機能ブロック図である。

【図2】本発明フィールド機器のファームウェアおよびモデル型情報読み込みのイメージ図である。

【図3】ファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。

【図4】本発明を適用したフィールド機器の他の実施形態におけるファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。

【図5】本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。

【図6】本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。

【図7】従来のフィールド機器の構成例を示す機能ブロック図である。

【図8】従来フィールド機器のファームウェア読み込みのイメージ図である。

【発明を実施するための形態】

【0026】

以下、本発明を図面を用いて詳細に説明する。図1は、本発明を適用したフィールド機器の一実施例を示す機能ブロック図である。図7で説明した従来構成と同一要素には同一符号を付して説明を省略する。

【0027】

図7に示した従来構成と相違する本発明の特徴部は、統合ファームウェア100およびモデル型情報200にある。統合ファームウェア100の構成は、共通部101とこの共通部に追加記述された高機能付加部102よりなる。

【0028】

製品Aを実現する場合には、CPU6は、起動処理において、統合ファームウェア100から共通部101を読み出して揮発性メモリ7(RAM)に格納する。また、製品Bを実現する場合には、統合ファームウェア100から共通部101および高機能付加部102を結合したファームウェアを読み出してRAMに格納する。

【0029】

モデル型情報200は、製品Aと製品Bを識別するための情報であり、第1不揮発性メモリ8または第2不揮発性メモリ3に保持させることで、モデル型情報保持手段を実現させる。この情報は、保持するデータのサイズ、タイプは特に指定はなく、例えば、0ならば製品A、1ならば製品Bとする等、識別可能な2値データであればよい。

【0030】

CPU6は、第1不揮発性メモリ8または第2不揮発性メモリ3に形成されたモデル型情報保持手段から取得したモデル型情報200に基づいて、統合ファームウェア100の共通部101または統合ファームウェア全体(101+102)を選択的に読み出し、揮発メモリ7に格納する。

【0031】

図2は、本発明フィールド機器のファームウェアおよびモデル型情報読み込みのイメージ図である。図2(イ)は、ハードウェア的なインストールイメージ、図2(ロ)はソフトウェア的なインストールイメージを示している。

【0032】

図2(イ)において、製品(A)または製品Bを実現するためのファームウェアは、揮発性メモリおよび第1不揮発性メモリを保有する共通のCPUアセンブリの第1不揮発性メモリ8にインストールされている。

【0033】

モデル型情報保持手段から取得されるモデル型情報に基づき、製品(A)を製造する場合には、統合ファームウェア100の共通部101を読み出して不揮発性メモリに格納したCPUアセンブリを、第2不揮発性メモリ3を保有する共通仕様のセンサー部に実装する。

【0034】

モデル型情報保持手段から取得されるモデル型情報に基づき、製品(B)を製造する場合には、統合ファームウェア100より統合ファームウェア全体(101+102)を読み出して不揮発性メモリに格納したCPUアセンブリを、第2不揮発性メモリ3を保有する共通仕様のセンサー部に実装する。

【0035】

図2(ロ)に示すソフトウェ的なイメージは、製品(A)および製品(B)で共通であり、ステップS1で第1および第2不揮発性メモリから内部データを読み込み、ステップS2でモデル型情報を読み込み、ステップS3の起動処理で選択されたファームウェアのデータを揮発性メモリに格納し、ステップS4のメイン処理で製品Aまたは製品Bの動作を実現させる。

【0036】

図3は、ファームウェアおよびモデル型情報読み込みの処理手順を示す詳細フローチャートである。電源オン後のステップS1で第1不揮発性メモリ8から内部データ(ファームウェア)を取得する。

【0037】

モデル情報識別部のステップS2では仮決定処理を実行し、製品Aを製造モデルとして統合ファームウェアの共通部を読み込んで仮決定する。ステップS3では、第1不揮発性メモリ8(または第2不揮発性メモリ3)に形成されたモデル型情報保持手段からモデル型情報を取得し、揮発性メモリ7に格納する。

【0038】

起動処理部のステップS4では、取得したモデル型情報に基づいて統合ファームウェアから取得するデータを揮発メモリに格納する起動処理が実行され、ステップS5で製品Aと製品Bの分岐処理が実行される。

【0039】

メイン処理部のステップS6は、ステップS5の分岐処理が製品Aの場合には、製品Aとしてのメイン処理を開始する。メイン処理部のステップS7はステップS5の分岐処理が製品Bの場合には、製品Bしてのメイン処理を開始する。これらメイン処理は電源オフで終了する。

【0040】

図4は、本発明を適用したフィールド機器の他の実施形態におけるファームウェアおよびモデル型情報読み込みの処理手順を示すフローチャートである。不揮発性メモリ8のEEPROM_1が故障した場合の対策として、不揮発性メモリ3のEEPROM_2にもモデル型情報を持たせておき、EEPROM_1からモデル型情報が正常に読み込みができた場合はEEPROM_1の情報で動作し、EEPROM_1が故障(異常)の場合には、EEPROM_2のモデル型情報で動作するようにしたものである。

【0041】

図4のフローチャートのモデル識別部に追加されたステップS8は、不揮発性メモリ8のEEPROM_1のチェックを実行し、正常の場合には図3と同じ処理フローとなる。異常の場合にはステップS9で不揮発性メモリ3のEEPROM_2のチェックを実行し、正常の場合にはステップS10に進み、EEPROM_2のモデル型情報を取得しステップS4に進み、図3と同じ処理フローとなる。EEPROM_2も異常の場合には、ステップS6に進み、製品Aとしてメイン処理を開始する。

【0042】

図5は、本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。この実施例の特徴は、製品Aまたは製品Bに実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴としている。

【0043】

共通のCPUアセンブリにLCD1を接続すると、CPU6はLCD1を表すハードウェアの種別情報を取得し製品Aで動作し、LCD2を接続すると、CPU6はLCD2を表すハードウェアの種別情報を取得し製品Bで動作する。この場合、例えば、LCD1は高精度のフルドットタイプLCD、LCD2はセグメントタイプLCD等が考えられる。

【0044】

図6は、本発明を適用したフィールド機器の更に他の実施形態におけるファームウェアおよびモデル型情報読み込みのイメージ図である。この実施例の特徴は、接続される通信の種別情報を前記モデル型情報とすることを特徴としている。

【0045】

通信ターミナルを介して接続、実行される通信の形態が4−20mAの電流出力の場合には、CPU6は電流出力を表す通信の種別情報を取得し製品Aで動作する。接続される通信の形態がデジタル通信の場合には、CPU6はデジタル通信を表す通信の種別情報を取得し製品Bで動作する。接続される通信の形態が1−5Vの電圧出力の場合には、CPU6は電圧出力を表す通信の種別情報を取得し製品Cで動作する。

【0046】

以上説明した実施例では、フィールド機器として差圧/圧力伝送器を例示したが、本発明は複数モデルを製造するフィールド機器一般に適用することができる。

【0047】

また、実施例では、標準機能の製品Aと高機能が付加された製品Bの例を説明したが、これに限定されるものではなく、統合的ファームウェアを利用可能な3種以上のモデル型の製品製造に応用することが可能である。

【符号の説明】

【0048】

1 センサー部

2 センサー

3 第2不揮発性メモリ(EEPROM_2)

4 入力処理部

5 A/D変換回路

6 CPU

7 揮発性メモリ(RAM)

8 第1不揮発性メモリ(EEPROM_1)

9 D/A変換回路

10 出力部

100 統合ファームウェア

101 共通部

102 高機能付加部

200 モデル型情報

【特許請求の範囲】

【請求項1】

センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、

前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、

前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、

前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納することを特徴とするフィールド機器。

【請求項2】

前記モデル型情報保持手段は、前記第1不揮発性メモリに形成されることを特徴とする請求項1に記載のフィールド機器。

【請求項3】

前記センサー固有の情報を保持する第2不揮発性メモリを備え、

前記モデル型情報保持手段は、前記第2不揮発性メモリに形成されることを特徴とする請求項1または2に記載のフィールド機器。

【請求項4】

前記標準製品または前記高機能製品に実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴とする請求項1に記載のフィールド機器。

【請求項5】

通信ターミナルを介して行われる通信の種別情報を前記モデル型情報とすることを特徴とする請求項1に記載のフィールド機器。

【請求項1】

センサーからの入力信号を処理するCPUが、第1不揮発性メモリに保持されているファームウェアを読み出して揮発性メモリに格納する起動処理を実行後メイン処理が実行されるフィールド機器において、

前記第1不揮発性メモリは、標準製品の仕様が記述された共通部と、前記標準製品の仕様に追加仕様が付加された高機能製品の前記加仕様が記述された高機能付加部とを含む統合ファームウェアを保持し、

前記標準製品と前記高機能製品のいずれかを選択するためのモデル型情報を保持するモデル型情報保持手段を備え、

前記CPUは、前記モデル型情報保持手段から読み出されるモデル型情報に基づいて、前記第1不揮発性メモリに保持された前記統合ファームウェアより前記共通部、または前記共通部および前記高機能付加部を読み出して前記揮発性メモリに格納することを特徴とするフィールド機器。

【請求項2】

前記モデル型情報保持手段は、前記第1不揮発性メモリに形成されることを特徴とする請求項1に記載のフィールド機器。

【請求項3】

前記センサー固有の情報を保持する第2不揮発性メモリを備え、

前記モデル型情報保持手段は、前記第2不揮発性メモリに形成されることを特徴とする請求項1または2に記載のフィールド機器。

【請求項4】

前記標準製品または前記高機能製品に実装されるハードウェアの種別情報を前記モデル型情報とすることを特徴とする請求項1に記載のフィールド機器。

【請求項5】

通信ターミナルを介して行われる通信の種別情報を前記モデル型情報とすることを特徴とする請求項1に記載のフィールド機器。

【図1】

【図3】

【図4】

【図7】

【図2】

【図5】

【図6】

【図8】

【図3】

【図4】

【図7】

【図2】

【図5】

【図6】

【図8】

【公開番号】特開2013−73342(P2013−73342A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−210791(P2011−210791)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

[ Back to top ]