フライバックコンバーター

【課題】フライバックトランスに発生する励磁電流を抑制するとともに、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくいフライバックコンバーターを提供する。

【解決手段】フライバックトランスT1の1次巻線N1に対して印加する電圧のオンオフを切換えるためのパワーMOSトランジスタTR1と、パワーMOSトランジスタTR1のスイッチング制御を行う電源制御IC11とを備え、電源制御IC11は、負荷30が第1閾値以上のときは連続発振を行い、負荷30が前記第1閾値未満のときは間欠発振を行うように構成されており、電源制御IC11は、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返す構成としてある。

【解決手段】フライバックトランスT1の1次巻線N1に対して印加する電圧のオンオフを切換えるためのパワーMOSトランジスタTR1と、パワーMOSトランジスタTR1のスイッチング制御を行う電源制御IC11とを備え、電源制御IC11は、負荷30が第1閾値以上のときは連続発振を行い、負荷30が前記第1閾値未満のときは間欠発振を行うように構成されており、電源制御IC11は、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返す構成としてある。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はフライバックコンバーターに関し、特にFETのスイッチングを制御する制御ICを備える他励式のフライバックコンバーターに関する。

【背景技術】

【0002】

待機時消費電力の削減は、国際機関や各国において行われており、現在発売されている最新の電気製品の多くは、待機時消費電力の限度値1W以下を達成している。

このような待機時消費電力の削減のために、低滞期電力・擬似共振型RCC電源では、スイッチングのオン時間を調節することにより出力電圧を一定に安定化させる通常の動作と、通常の動作での発振と発振停止とを繰り返し行う間欠周期固定方式のバースト動作とを、通常モードと待機モードとで使い分けることが行われている(例えば特許文献1参照)。

また、特許文献2には、電気機器が待機モードにある場合に、電流が流れる時間を流れない時間に比してはるかに短く設定して間欠的にトランスに通電することによってトランスの励磁電流による消費電力を大幅に減少させることについて開示されている。

また、特許文献3,4には、間欠動作時に、トランジスタの電流の振幅及びオン時間幅を徐々に増加させ、徐々に減少させることにより、トランスに磁束の急激な変化を防止し、トランスのうなりを抑制することについて開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−136125号公報

【特許文献2】特開2000−116027号公報

【特許文献3】特開2000−023458号公報

【特許文献4】特開平11−215819号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来の技術では、待機時の消費電力を削減した間欠発振においてトランスに発生するうなりを防止する対策としては不十分であった。

【0005】

本発明は、上記課題に鑑みてなされたもので、待機時に間欠発振を行うフライバックコンバーターにおいて、電力消費を抑えつつうなりを低減することが可能にすることを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明にかかるフライバックコンバーターでは、フライバックトランスの1次巻線に対して印加する電圧のオンオフを切換えるためのスイッチング素子と、当該スイッチング素子のスイッチング制御を行う制御ICとを備え、前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する他励式のフライバックコンバーターにおいて、前記制御ICは、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を所定の発振周期にて繰り返す構成としてある。

【0007】

前記構成において、前記制御ICは、フライバックトランスの1次巻線に印加する電圧のオンオフを切換えるためのスイッチング素子のスイッチング制御を実行可能である。そして、前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する。なお、前記負荷量は、例えば、前記フライバックトランスの1次巻線に流れる電流(前記スイッチング素子を電界効果トランジスタで構成するの場合は、ドレイン電流)に基づいて検知したり、前記フライバックトランスの2次側に流れる電流に基づいて検知したりすることができる。

【0008】

さらに、前記制御ICは、前記間欠発振の周波数が、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を前記間欠発振の周期にて繰り返す構成としてある。当該構成においては、間欠発振における発振単位を複数のオン期間で構成することにより、当該発振単位を構成する1つのオン期間を短くすることができる。よって、フライバックトランスに発生する励磁電流が抑制される。また、間欠発振における発振単位を構成する複数のオン期間の周期を人の可聴範囲外となる周期とすることにより、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくくなる。

【0009】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間の発振波形は同一波形となるように構成される。当該構成によれば、消費電力をミニマイズした状態が継続され、最小限の電力に追い込むことができる。これにより、出力を最小限にした状態を継続することができる。

【0010】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間のそれぞれは、1μ秒〜1n秒となるように構成される。当該構成によれば、間欠発振における発振単位を構成する1つのオン期間が具体的に実現され、フライバックトランスに発生する励磁電流が確実に抑制される。

【0011】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間は、当該複数のオン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように決定される構成とされる。当該構成によれば、間欠発振における発振単位を構成する1つのオン期間を具体的に特定するための指標が提供され、フライバックトランスに発生する励磁電流が確実に抑制される。

【0012】

また、本発明の選択的な一態様では、前記制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返し、前記3〜4回のオン期間は、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流が、変更前のオン期間に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように1μ秒〜1n秒の範囲で決定される構成とされる。

【発明の効果】

【0013】

以上説明したように本発明によれば、フライバックトランスに発生する励磁電流を抑制するとともに、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくいフライバックコンバーターを提供することができる。

請求項2にかかる発明によれば、出力を最小限にした状態を継続し、うなりの発生を低減することができる。

請求項3にかかる発明によればフライバックトランスに発生する励磁電流が確実に抑制される。

請求項4にかかる発明によれば、フライバックトランスに発生する励磁電流が確実に抑制される。

請求項5のようなより具体的な構成において、上述した請求項1〜請求項4の各発明と同様の作用効果を奏することはいうまでもない。

【図面の簡単な説明】

【0014】

【図1】電気機器の概略構成を示すブロック図である。

【図2】電源回路の構成を示す回路図である。

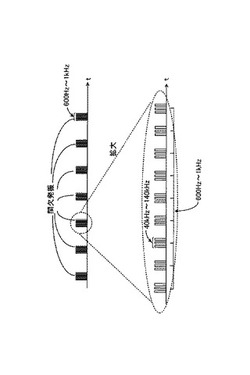

【図3】間欠発振の周波数が可聴域に入ったときに行われるスイッチング制御の説明図である。

【発明を実施するための形態】

【0015】

以下、下記の順序に従って本発明の実施形態を説明する。

(1)電気機器の構成:

(2)電源回路の構成・動作:

(3)電源回路の行う間欠発振:

(4)まとめ:

【0016】

(1)電気機器の構成:

図1は、本発明のフライバックコンバーターの実施形態を備える電気機器の概略構成を示すブロック図である。同図に示すように、電気機器100は、電源回路10、負荷30、を備えている。電気機器100は、例えばテレビジョンで構成される。なお、本実施形態において電気機器とは、アナログ回路を備えるもののみならず、IC等の電子回路を備えるものも当然に含まれる。

電源回路10は、本実施形態ではフライバックコンバーターの構成とされる。

負荷30は電源回路10から電源電圧を供給されて動作するものである。負荷30は、通常状態と、当該通常状態よりも消費電力の少ない待機状態と、を切換え可能になっており、例えばマイクロコンピュータで構成される。通常状態と待機状態の切換は、不図示の操作部に対してユーザーが行う操作入力に基づいて行われてもよいし、負荷30自身が何らかの判断処理により行ってもよい。

【0017】

(2)電源回路の構成・動作:

図2は、電源回路の構成を示す回路図である。

同図の回路構成において、交流電源ACからの交流はダイオードスタックDS1により整流され、コンデンサC6で平滑された直流がフライバックトランスT1の1次巻線N1に供給される。1次巻線N1にはスイッチング素子であるパワーMOSトランジスタTR1が直列に接続されており、電源制御IC11からの駆動信号によりパワーMOSトランジスタTR1がオン(ON)、オフ(OFF)し、これによりフライバックトランスT1の2次巻線N2に脈流が発生する。この脈流はダイオードスタックDS2,DS3によって整流され、コンデンサC16,C17で平滑されて図示しない負荷に供給される。

【0018】

上記負荷への出力電圧は抵抗R22,R24,RV1により分圧されて検出され、その検出値がフォトカプラPC1を介し、フィードバック信号として電源制御IC11のFB端子に入力される。また、フライバックトランスT1の1次巻線N1に電流が流れると補助巻線N3にも電圧が発生し、この電圧はダイオードD4により整流され、コンデンサC13で平滑されて、電源制御IC11の電源端子であるVcc端子に供給される。

【0019】

また、電源制御IC11のZCD端子には、補助巻線N3に接続された抵抗R14が接続されている。C8,C21はコンデンサ、IC2はシャントレギュレータ、R20は電流制限用の抵抗、R5は電流検出用のセンス抵抗である。

【0020】

なお、電源制御IC11は、外部端子として、上記のFB端子、Vcc端子およびZCD端子の他に、接地用のGND端子、パワーMOSトランジスタTR1のゲートドライブ用のOUT端子、パワーMOSトランジスタTR1のドレイン電流検出用のIS端子、高電圧系からVcc端子に電流を供給するVH端子およびVH端子の隣接ピンである未接続のNC端子を持つ標準の8ピン構成となっている。

【0021】

上記のように構成されたスイッチング電源回路は、電源制御IC11によってスイッチング動作が制御されるが、電源制御IC11のFB端子には負荷への出力電圧に応じたフィードバック信号が入力され、その端子電圧により負荷状態に応じた信号が出力されてスイッチングが制御される。

【0022】

ここで、負荷が低下したとき自動的に出力を低下させた省電力状態に移行するために、電源制御IC11は、オートスタンバイ機能を備えている。オートスタンバイ機能とは、軽負荷時にスイッチング素子のドレイン電流が減少し、所定の閾値になると自動的に間欠発振(バースト発振)を行うものである。本実施形態では、センス抵抗R5によりスイッチング素子のドレイン電流に相当する電圧を検出しており、当該電圧が電源制御IC11のIS端子に入力されている。

【0023】

すなわち、電源制御IC11は、IS端子に入力されている電圧を監視することにより、電源回路10に接続されている負荷の大小を検知することが可能であり、負荷が軽くなると出力を低下させてスタンバイモードに自動的に移行させる制御を行う。

具体的には、負荷の大小に応じてスイッチング素子のスイッチング制御態様を変更する。すなわち、負荷が第1閾値以上のときは連続発振とし、負荷が第1閾値未満のときは連続発振を間欠的に行う間欠発振とする。ここで第1閾値は、電源回路10の設計者が適宜に設定するものであり、例えば、上述したマイクロコンピュータを負荷とすると、マイクロコンピュータが通常状態のときの負荷と、マイクロコンピュータが待機状態ののときの負荷との間にの負荷が第1閾値とされる。

【0024】

ここで、軽負荷時の効率を改善するために間欠発振の周波数は数kHz以下(例えば600Hz〜1kHz)になるが、間欠発振の周波数が人の可聴領域(一般に20Hz〜20kHz)に入ると、トランスの音鳴りが生じる場合がある。そこで、電源制御IC11は、間欠発振の周波数が可聴領域に入ると、前記間欠発振におけるスイッチング素子の各オン期間を、通常のオン期間よりも短い複数のオン期間に変更する。この変更について、図3を参照して説明する。

【0025】

(3)電源回路の行う間欠発振:

図3は、間欠発振の周波数が可聴域に入ったときに行われるスイッチング制御の説明図である。同図に示すように、間欠発振の周波数が可聴領域外のときは、スイッチングのオン期間が一定の連続発振が一定期間継続的に行われた後、次に一定期間スイッチング動作を停止状態にする繰り返し間欠発振動作が行われる。一方、間欠発振の周波数が可聴領域のときは、各オン期間を40kHz〜140kHz間隔で行われる複数(2以上であり、例えば3〜4)の短縮されたオン期間(以下、短縮オン期間と記載する。)に変更する。従って、40kHz〜140kHz間隔で行われる複数の短縮オン期間を1セットとして、当該セットが数kHz以下(例えば600Hz〜1kHz)で繰り返し行われることになる。このように、1回のオン期間を短縮して複数回のオン期間に変更することにより、フライバックトランスT1の励磁電流(パワーMOSトランジスタTR1のドレイン電流)によりコアが振動して発生したりトランス内部の巻線が振動したりして発生するうなりを低減することができる。

【0026】

なお、短縮オン時間は、上述した複数回のスイッチで発生するドレイン電流が、短縮される前のオン期間でオンした場合に発生するドレイン電流の1/5〜1/10となるように定めると好適である。この方針に従えば、例えば、短縮オン期間を1μ秒〜1n秒とすることができる。短縮オン期間が1n秒とすると、1次側のオン期間と2次側のオン期間とを合わせれば500kHz程になり、短縮オン期間を実現するために十分な周波数となる。

【0027】

また、上述した複数回の短縮オン期間は全て同じ波形とする。このように同一波形で複数回の発振を行うことにより、消費電力をミニマイズした状態が継続され、最小限の電力に追い込むことができる。これにより、出力を最小限にした状態を継続することができる。

【0028】

(4)まとめ:

以上説明したように、本実施形態にかかる電源回路10は、フライバックトランスT1の1次巻線N1に対して印加する電圧のオンオフを切換えるためのパワーMOSトランジスタTR1と、パワーMOSトランジスタTR1のスイッチング制御を行う電源制御IC11とを備え、電源制御IC11は、負荷30が第1閾値以上のときは連続発振を行い、負荷30が前記第1閾値未満のときは間欠発振を行うように構成されており、電源制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返す構成としてある。当該構成によれば、フライバックトランスに発生する励磁電流を抑制するとともに、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくいフライバックコンバーターを提供することができる。

【0029】

なお、本発明は上記実施例に限られるものでないことは言うまでもない。当業者であれば言うまでもないことであるが、

・上記実施例の中で開示した相互に置換可能な部材および構成等を適宜その組み合わせを変更して適用すること

・上記実施例の中で開示されていないが、公知技術であって上記実施例の中で開示した部材および構成等と相互に置換可能な部材および構成等を適宜置換し、またその組み合わせを変更して適用すること

・上記実施例の中で開示されていないが、公知技術等に基づいて当業者が上記実施例の中で開示した部材および構成等の代用として想定し得る部材および構成等と適宜置換し、またその組み合わせを変更して適用すること

は本発明の一実施例として開示されるものである。

【符号の説明】

【0030】

10…電源回路、30…負荷、100…電気機器、11…電源制御IC、C6…コンデンサ、C13…コンデンサ、C16…コンデンサ、C17…コンデンサ、D4…ダイオード、DS1…ダイオードスタック、DS2,DS3…ダイオードスタック、N1…1次巻線、N2…2次巻線、N3…補助巻線、PC1…フォトカプラ、R5…センス抵抗、R14…抵抗、R22…抵抗、R24…抵抗、T1…フライバックトランス、TR1…パワーMOSトランジスタ

【技術分野】

【0001】

本発明はフライバックコンバーターに関し、特にFETのスイッチングを制御する制御ICを備える他励式のフライバックコンバーターに関する。

【背景技術】

【0002】

待機時消費電力の削減は、国際機関や各国において行われており、現在発売されている最新の電気製品の多くは、待機時消費電力の限度値1W以下を達成している。

このような待機時消費電力の削減のために、低滞期電力・擬似共振型RCC電源では、スイッチングのオン時間を調節することにより出力電圧を一定に安定化させる通常の動作と、通常の動作での発振と発振停止とを繰り返し行う間欠周期固定方式のバースト動作とを、通常モードと待機モードとで使い分けることが行われている(例えば特許文献1参照)。

また、特許文献2には、電気機器が待機モードにある場合に、電流が流れる時間を流れない時間に比してはるかに短く設定して間欠的にトランスに通電することによってトランスの励磁電流による消費電力を大幅に減少させることについて開示されている。

また、特許文献3,4には、間欠動作時に、トランジスタの電流の振幅及びオン時間幅を徐々に増加させ、徐々に減少させることにより、トランスに磁束の急激な変化を防止し、トランスのうなりを抑制することについて開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−136125号公報

【特許文献2】特開2000−116027号公報

【特許文献3】特開2000−023458号公報

【特許文献4】特開平11−215819号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した従来の技術では、待機時の消費電力を削減した間欠発振においてトランスに発生するうなりを防止する対策としては不十分であった。

【0005】

本発明は、上記課題に鑑みてなされたもので、待機時に間欠発振を行うフライバックコンバーターにおいて、電力消費を抑えつつうなりを低減することが可能にすることを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明にかかるフライバックコンバーターでは、フライバックトランスの1次巻線に対して印加する電圧のオンオフを切換えるためのスイッチング素子と、当該スイッチング素子のスイッチング制御を行う制御ICとを備え、前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する他励式のフライバックコンバーターにおいて、前記制御ICは、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を所定の発振周期にて繰り返す構成としてある。

【0007】

前記構成において、前記制御ICは、フライバックトランスの1次巻線に印加する電圧のオンオフを切換えるためのスイッチング素子のスイッチング制御を実行可能である。そして、前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する。なお、前記負荷量は、例えば、前記フライバックトランスの1次巻線に流れる電流(前記スイッチング素子を電界効果トランジスタで構成するの場合は、ドレイン電流)に基づいて検知したり、前記フライバックトランスの2次側に流れる電流に基づいて検知したりすることができる。

【0008】

さらに、前記制御ICは、前記間欠発振の周波数が、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を前記間欠発振の周期にて繰り返す構成としてある。当該構成においては、間欠発振における発振単位を複数のオン期間で構成することにより、当該発振単位を構成する1つのオン期間を短くすることができる。よって、フライバックトランスに発生する励磁電流が抑制される。また、間欠発振における発振単位を構成する複数のオン期間の周期を人の可聴範囲外となる周期とすることにより、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくくなる。

【0009】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間の発振波形は同一波形となるように構成される。当該構成によれば、消費電力をミニマイズした状態が継続され、最小限の電力に追い込むことができる。これにより、出力を最小限にした状態を継続することができる。

【0010】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間のそれぞれは、1μ秒〜1n秒となるように構成される。当該構成によれば、間欠発振における発振単位を構成する1つのオン期間が具体的に実現され、フライバックトランスに発生する励磁電流が確実に抑制される。

【0011】

また、本発明の選択的な一態様では、前記発振単位を構成する複数のオン期間は、当該複数のオン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように決定される構成とされる。当該構成によれば、間欠発振における発振単位を構成する1つのオン期間を具体的に特定するための指標が提供され、フライバックトランスに発生する励磁電流が確実に抑制される。

【0012】

また、本発明の選択的な一態様では、前記制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返し、前記3〜4回のオン期間は、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流が、変更前のオン期間に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように1μ秒〜1n秒の範囲で決定される構成とされる。

【発明の効果】

【0013】

以上説明したように本発明によれば、フライバックトランスに発生する励磁電流を抑制するとともに、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくいフライバックコンバーターを提供することができる。

請求項2にかかる発明によれば、出力を最小限にした状態を継続し、うなりの発生を低減することができる。

請求項3にかかる発明によればフライバックトランスに発生する励磁電流が確実に抑制される。

請求項4にかかる発明によれば、フライバックトランスに発生する励磁電流が確実に抑制される。

請求項5のようなより具体的な構成において、上述した請求項1〜請求項4の各発明と同様の作用効果を奏することはいうまでもない。

【図面の簡単な説明】

【0014】

【図1】電気機器の概略構成を示すブロック図である。

【図2】電源回路の構成を示す回路図である。

【図3】間欠発振の周波数が可聴域に入ったときに行われるスイッチング制御の説明図である。

【発明を実施するための形態】

【0015】

以下、下記の順序に従って本発明の実施形態を説明する。

(1)電気機器の構成:

(2)電源回路の構成・動作:

(3)電源回路の行う間欠発振:

(4)まとめ:

【0016】

(1)電気機器の構成:

図1は、本発明のフライバックコンバーターの実施形態を備える電気機器の概略構成を示すブロック図である。同図に示すように、電気機器100は、電源回路10、負荷30、を備えている。電気機器100は、例えばテレビジョンで構成される。なお、本実施形態において電気機器とは、アナログ回路を備えるもののみならず、IC等の電子回路を備えるものも当然に含まれる。

電源回路10は、本実施形態ではフライバックコンバーターの構成とされる。

負荷30は電源回路10から電源電圧を供給されて動作するものである。負荷30は、通常状態と、当該通常状態よりも消費電力の少ない待機状態と、を切換え可能になっており、例えばマイクロコンピュータで構成される。通常状態と待機状態の切換は、不図示の操作部に対してユーザーが行う操作入力に基づいて行われてもよいし、負荷30自身が何らかの判断処理により行ってもよい。

【0017】

(2)電源回路の構成・動作:

図2は、電源回路の構成を示す回路図である。

同図の回路構成において、交流電源ACからの交流はダイオードスタックDS1により整流され、コンデンサC6で平滑された直流がフライバックトランスT1の1次巻線N1に供給される。1次巻線N1にはスイッチング素子であるパワーMOSトランジスタTR1が直列に接続されており、電源制御IC11からの駆動信号によりパワーMOSトランジスタTR1がオン(ON)、オフ(OFF)し、これによりフライバックトランスT1の2次巻線N2に脈流が発生する。この脈流はダイオードスタックDS2,DS3によって整流され、コンデンサC16,C17で平滑されて図示しない負荷に供給される。

【0018】

上記負荷への出力電圧は抵抗R22,R24,RV1により分圧されて検出され、その検出値がフォトカプラPC1を介し、フィードバック信号として電源制御IC11のFB端子に入力される。また、フライバックトランスT1の1次巻線N1に電流が流れると補助巻線N3にも電圧が発生し、この電圧はダイオードD4により整流され、コンデンサC13で平滑されて、電源制御IC11の電源端子であるVcc端子に供給される。

【0019】

また、電源制御IC11のZCD端子には、補助巻線N3に接続された抵抗R14が接続されている。C8,C21はコンデンサ、IC2はシャントレギュレータ、R20は電流制限用の抵抗、R5は電流検出用のセンス抵抗である。

【0020】

なお、電源制御IC11は、外部端子として、上記のFB端子、Vcc端子およびZCD端子の他に、接地用のGND端子、パワーMOSトランジスタTR1のゲートドライブ用のOUT端子、パワーMOSトランジスタTR1のドレイン電流検出用のIS端子、高電圧系からVcc端子に電流を供給するVH端子およびVH端子の隣接ピンである未接続のNC端子を持つ標準の8ピン構成となっている。

【0021】

上記のように構成されたスイッチング電源回路は、電源制御IC11によってスイッチング動作が制御されるが、電源制御IC11のFB端子には負荷への出力電圧に応じたフィードバック信号が入力され、その端子電圧により負荷状態に応じた信号が出力されてスイッチングが制御される。

【0022】

ここで、負荷が低下したとき自動的に出力を低下させた省電力状態に移行するために、電源制御IC11は、オートスタンバイ機能を備えている。オートスタンバイ機能とは、軽負荷時にスイッチング素子のドレイン電流が減少し、所定の閾値になると自動的に間欠発振(バースト発振)を行うものである。本実施形態では、センス抵抗R5によりスイッチング素子のドレイン電流に相当する電圧を検出しており、当該電圧が電源制御IC11のIS端子に入力されている。

【0023】

すなわち、電源制御IC11は、IS端子に入力されている電圧を監視することにより、電源回路10に接続されている負荷の大小を検知することが可能であり、負荷が軽くなると出力を低下させてスタンバイモードに自動的に移行させる制御を行う。

具体的には、負荷の大小に応じてスイッチング素子のスイッチング制御態様を変更する。すなわち、負荷が第1閾値以上のときは連続発振とし、負荷が第1閾値未満のときは連続発振を間欠的に行う間欠発振とする。ここで第1閾値は、電源回路10の設計者が適宜に設定するものであり、例えば、上述したマイクロコンピュータを負荷とすると、マイクロコンピュータが通常状態のときの負荷と、マイクロコンピュータが待機状態ののときの負荷との間にの負荷が第1閾値とされる。

【0024】

ここで、軽負荷時の効率を改善するために間欠発振の周波数は数kHz以下(例えば600Hz〜1kHz)になるが、間欠発振の周波数が人の可聴領域(一般に20Hz〜20kHz)に入ると、トランスの音鳴りが生じる場合がある。そこで、電源制御IC11は、間欠発振の周波数が可聴領域に入ると、前記間欠発振におけるスイッチング素子の各オン期間を、通常のオン期間よりも短い複数のオン期間に変更する。この変更について、図3を参照して説明する。

【0025】

(3)電源回路の行う間欠発振:

図3は、間欠発振の周波数が可聴域に入ったときに行われるスイッチング制御の説明図である。同図に示すように、間欠発振の周波数が可聴領域外のときは、スイッチングのオン期間が一定の連続発振が一定期間継続的に行われた後、次に一定期間スイッチング動作を停止状態にする繰り返し間欠発振動作が行われる。一方、間欠発振の周波数が可聴領域のときは、各オン期間を40kHz〜140kHz間隔で行われる複数(2以上であり、例えば3〜4)の短縮されたオン期間(以下、短縮オン期間と記載する。)に変更する。従って、40kHz〜140kHz間隔で行われる複数の短縮オン期間を1セットとして、当該セットが数kHz以下(例えば600Hz〜1kHz)で繰り返し行われることになる。このように、1回のオン期間を短縮して複数回のオン期間に変更することにより、フライバックトランスT1の励磁電流(パワーMOSトランジスタTR1のドレイン電流)によりコアが振動して発生したりトランス内部の巻線が振動したりして発生するうなりを低減することができる。

【0026】

なお、短縮オン時間は、上述した複数回のスイッチで発生するドレイン電流が、短縮される前のオン期間でオンした場合に発生するドレイン電流の1/5〜1/10となるように定めると好適である。この方針に従えば、例えば、短縮オン期間を1μ秒〜1n秒とすることができる。短縮オン期間が1n秒とすると、1次側のオン期間と2次側のオン期間とを合わせれば500kHz程になり、短縮オン期間を実現するために十分な周波数となる。

【0027】

また、上述した複数回の短縮オン期間は全て同じ波形とする。このように同一波形で複数回の発振を行うことにより、消費電力をミニマイズした状態が継続され、最小限の電力に追い込むことができる。これにより、出力を最小限にした状態を継続することができる。

【0028】

(4)まとめ:

以上説明したように、本実施形態にかかる電源回路10は、フライバックトランスT1の1次巻線N1に対して印加する電圧のオンオフを切換えるためのパワーMOSトランジスタTR1と、パワーMOSトランジスタTR1のスイッチング制御を行う電源制御IC11とを備え、電源制御IC11は、負荷30が第1閾値以上のときは連続発振を行い、負荷30が前記第1閾値未満のときは間欠発振を行うように構成されており、電源制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返す構成としてある。当該構成によれば、フライバックトランスに発生する励磁電流を抑制するとともに、仮にフライバックトランスに振動が発生しても人の耳に聞こえるうなりが発生しにくいフライバックコンバーターを提供することができる。

【0029】

なお、本発明は上記実施例に限られるものでないことは言うまでもない。当業者であれば言うまでもないことであるが、

・上記実施例の中で開示した相互に置換可能な部材および構成等を適宜その組み合わせを変更して適用すること

・上記実施例の中で開示されていないが、公知技術であって上記実施例の中で開示した部材および構成等と相互に置換可能な部材および構成等を適宜置換し、またその組み合わせを変更して適用すること

・上記実施例の中で開示されていないが、公知技術等に基づいて当業者が上記実施例の中で開示した部材および構成等の代用として想定し得る部材および構成等と適宜置換し、またその組み合わせを変更して適用すること

は本発明の一実施例として開示されるものである。

【符号の説明】

【0030】

10…電源回路、30…負荷、100…電気機器、11…電源制御IC、C6…コンデンサ、C13…コンデンサ、C16…コンデンサ、C17…コンデンサ、D4…ダイオード、DS1…ダイオードスタック、DS2,DS3…ダイオードスタック、N1…1次巻線、N2…2次巻線、N3…補助巻線、PC1…フォトカプラ、R5…センス抵抗、R14…抵抗、R22…抵抗、R24…抵抗、T1…フライバックトランス、TR1…パワーMOSトランジスタ

【特許請求の範囲】

【請求項1】

フライバックトランスの1次巻線に対して印加する電圧のオンオフを切換えるためのスイッチング素子と、当該スイッチング素子のスイッチング制御を行う制御ICとを備え、

前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する他励式のフライバックコンバーターにおいて、

前記制御ICは、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を所定の発振周期にて繰り返すことを特徴とするフライバックコンバーター。

【請求項2】

前記発振単位を構成する複数のオン期間の発振波形は、同一波形とされる請求項1に記載のフライバックコンバーター。

【請求項3】

前記発振単位を構成する複数のオン期間のそれぞれは、1μ秒〜1n秒とされる請求項1または請求項2に記載のフライバックコンバーター。

【請求項4】

前記発振単位を構成する複数のオン期間は、当該複数のオン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように決定される請求項1〜請求項3の何れか1項に記載のフライバックコンバーター。

【請求項5】

前記制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返し、

前記3〜4回のオン期間は、各オン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように1μ秒〜1n秒の範囲で決定される請求項1に記載のフライバックコンバーター。

【請求項1】

フライバックトランスの1次巻線に対して印加する電圧のオンオフを切換えるためのスイッチング素子と、当該スイッチング素子のスイッチング制御を行う制御ICとを備え、

前記制御ICは、当該フライバックコンバーターの出力側に接続される負荷が第1閾値以上のときは前記スイッチング素子を連続発振にてスイッチング制御し、当該フライバックコンバーターの出力側に接続される負荷が前記第1閾値未満のときは前記スイッチング素子を間欠発振にてスイッチング制御する他励式のフライバックコンバーターにおいて、

前記制御ICは、人の可聴範囲外となる周期であって前記間欠発振の周期より短い周期にてオン期間を複数回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を所定の発振周期にて繰り返すことを特徴とするフライバックコンバーター。

【請求項2】

前記発振単位を構成する複数のオン期間の発振波形は、同一波形とされる請求項1に記載のフライバックコンバーター。

【請求項3】

前記発振単位を構成する複数のオン期間のそれぞれは、1μ秒〜1n秒とされる請求項1または請求項2に記載のフライバックコンバーター。

【請求項4】

前記発振単位を構成する複数のオン期間は、当該複数のオン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように決定される請求項1〜請求項3の何れか1項に記載のフライバックコンバーター。

【請求項5】

前記制御ICは、40kHz〜140kHzでオン期間を3〜4回繰り返す組合せを前記間欠発振における発振単位とし、前記間欠発振における発振中は前記発振単位を600Hz〜1kHzの周期にて繰り返し、

前記3〜4回のオン期間は、各オン期間に前記フライバックトランスの1次巻線に流れる電流が、当該複数のオン期間をまとめて1つのオン期間とした場合に前記フライバックトランスの1次巻線に流れる電流に比べて、1/5〜1/10となるように1μ秒〜1n秒の範囲で決定される請求項1に記載のフライバックコンバーター。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−182953(P2012−182953A)

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願番号】特願2011−45605(P2011−45605)

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000201113)船井電機株式会社 (7,855)

【Fターム(参考)】

【公開日】平成24年9月20日(2012.9.20)

【国際特許分類】

【出願日】平成23年3月2日(2011.3.2)

【出願人】(000201113)船井電機株式会社 (7,855)

【Fターム(参考)】

[ Back to top ]