フラッシュメモリの管理方法及びフラッシュメモリデバイス

【課題】予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るための管理方法及び該方法を使用するフラッシュメモリデバイスの提供。

【解決方法】

フラッシュメモリデバイスにエラー訂正回路と予備ブロック管理手段とを設け、予備ブロックの残数が前記予備ブロック管理手段に設定された閾値に至った後、ホストからの読み出し命令を受け、前記エラー訂正回路によってエラーが検出されたときに、該エラーを起こしたデータを含むブロックのデータをリフレッシュする。

【解決方法】

フラッシュメモリデバイスにエラー訂正回路と予備ブロック管理手段とを設け、予備ブロックの残数が前記予備ブロック管理手段に設定された閾値に至った後、ホストからの読み出し命令を受け、前記エラー訂正回路によってエラーが検出されたときに、該エラーを起こしたデータを含むブロックのデータをリフレッシュする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フラッシュメモリの管理方法及び該方法を使用するフラッシュメモリデバイスに関する。

【背景技術】

【0002】

EEPROM(電気的にデータの消去及び書き換えが可能な不揮発性メモリ)の一種としてフラッシュメモリが知られている。取り分けNAND型フラッシュメモリは、安価で且つデータの書き込み時間が短いため、ハードディスクの置き換えや、各種コンテンツを格納する用途で使用されている。NAND型フラッシュメモリは、その構造上、製造段階で不良ブロックが存在する。また、書き込み回数や読み出し回数の増大によってもデータ化けが生じ、不良ブロックとなる。このため、ユーザ領域の他、予備のブロックを予め設けておき、不良ブロックを予備のブロックに置き換えている。予備ブロックがゼロになると、もはやメモリは使用不可能となる。そのため、本出願人は、斯かる事態が発生する前に代替品と交換させるべく、管理者に通知する記憶装置について提案している。

【0003】

しかしながら、専らコンテンツを読み出す用途に使用されている場合、リードディスターブエラーによりユーザ領域の多数のブロックが一度に不良ブロックになり、予備領域が急激に減少する可能性がある。斯かる場合には、管理者に通知後、新品との交換に間に合わない事態も想定される。

【特許文献1】特開2000−181805号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ここにおいて、本発明が解決すべき課題は、予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るための管理方法及び該方法を使用するフラッシュメモリデバイスの提供にある。その他の課題は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0005】

上記課題解決のため、本発明方法は、以下に上位概念から下位概念に亙り列挙する新規な特徴的構成を採用する。

【0006】

即ち、本発明方法は、

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新するフラッシュメモリの管理方法を提供する。

【0007】

(作用)

本構成では、エラー訂正回路により得られるbitエラー数の閾値を2個設け、その閾値に基づいて、予備ブロックの残数が閾値に至る前後で不良ブロックの処理方法を変えることにより、リードディスターブエラーによるデータ破壊を効率よく、且つ確実に防止するとともに、メモリデバイスの寿命を延ばすことが可能となる。即ち、予備ブロックの残数が閾値に至る前は、不良ブロックを予備ブロックに代替するポイントを、マージンを持たせてエラー訂正回路の能力値n(訂正可能な上限値)よりも低いbitエラー数閾値mに設定することにより、データ破壊を確実に防止することができる。また、リフレッシュを行わないので、ホストからのメモリアクセスの一時的な中断を回避することができる。予備ブロックの残数が閾値に至った後は、予備ブロックに代替するポイントをnとし、m以上n未満のときはリフレッシュを実行する。このことにより、今まで不良ブロックとして捨てていたブロックを、有効なブロックとして扱うことができ、延いてはフラッシュメモリの寿命を延ばすことが可能となる。

【0008】

ここで、エラー訂正回路によって得られるbitエラー数が閾値m未満のときは、予備ブロックの残数に関係なく、エラーを起こしたデータをエラー訂正回路により訂正してからホストへ返すことのみを行う。即ち、bitエラー数がエラー訂正回路の能力値nよりも充分に小さい範囲にあるときは、読み出し対象となっているブロックが寿命に達するまでには猶予があるため、予備ブロックへの代替やリフレッシュを行わない。従って、データ転送の一時的な中断を回避してホストからのメモリアクセスを優先させることができ、且つ、メモリデバイスの寿命を延ばすことが可能となる。

【0009】

また、前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することが好ましい。

【0010】

(作用)

予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った以降のリフレッシュは、データが書き込まれていない未使用の領域を使用して行われる。即ち、エラーを起こしたデータを含むブロックの全データを、エラーを起こしたデータに関してデータ誤りの訂正を行った後、未使用の領域であるユーザ領域中の空きブロック若しくは予備ブロックにコピーし、元のブロックの全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとしてブロック管理テーブルを更新する。コピーのために読み出されたデータは一旦バッファに保存され、その後ユーザ領域中の空きブロック若しくは予備ブロックに転送される。データのコピー完了後に、元のブロックのデータを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとすることにより、コピーの途中で突然の電源遮断が起こっても、データは元のブロックに保存されており消失しない。これにより、メモリデバイスの信頼性を高めることが可能となる。

【0011】

また、前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻してもよい。

【0012】

(作用)

これにより、ブロック管理テーブルの更新を行わずにリフレッシュすることが可能となる。

【0013】

また、表示手段をさらに有し、予備ブロック残数が所定数に至った段階で、該表示手段を駆動してもよいし、予備ブロック残数が所定数に至った段階で、ホストに通知してもよい。

【0014】

これにより、予備ブロックの状態を管理者が知ることができ、新品とタイムリーに交換することにより、システムのより安全な運用を図ることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0016】

(システム基本構成)

図1は、本発明におけるフラッシュメモリデバイスのシステム基本構成図である。本発明は、NAND型フラッシュメモリ12(本明細書において、特に必要のない限り、単に“フラッシュメモリ”という)とフラッシュメモリ12にデータの書き込みや読み出しを実行するコントローラ11からなるフラッシュメモリデバイス2と、フラッシュメモリデバイス2にデータの書き込みや読み出しのコマンドを発行するホスト1を基本構成として有するシステムで実行され得る。尚、コントローラ11には、必要に応じRAM13を接続する。フラッシュメモリデバイス2とホスト1は、例えばMPEG音楽プレーヤのように、所定の機器として一体に構成されていてもよいし、ホスト1がPCで構成され、フラッシュメモリデバイス2がPCとUSB接続される機器のように、別体で構成してもよい。近年では、ハードディスクの置き換えとして、SSD(Solid

State Drive)のように、複数のフラッシュメモリ12とコントローラ11とRAM13とが一体に構成され、PCとIDE接続される機器もある。

【0017】

フラッシュメモリ12は、複数の物理ブロックで構成されているが、周知の通り、フラッシュメモリ12は、ユーザ領域の他、ユーザ領域が不良となった場合の代替領域である予備領域を含む。

【0018】

図2、図3及び図4は、フラッシュメモリ12の物理ブロックを模式的に表した図であり、ブロック管理テーブルにおけるブロックの管理方法の模式図である。フラッシュメモリ12は、Block0からBlock8191までの8192ブロックで構成され、各ブロック番号(Block0〜8191)は、メモリセルアレイ21乃至26の同じ物理ブロックに対応している。図2は不良ブロック処理におけるブロック管理テーブルの例であり、図3はリフレッシュにおけるブロック管理テーブルの第1の例、図4はリフレッシュにおけるブロック管理テーブルの第2の例である。図2に示すメモリセルアレイ21、及び、図3に示すメモリセルアレイ23、図4に示すメモリセルアレイ25は、ブロック管理テーブル14における、不良ブロック処理前の物理ブロックの状態を表す。図2に示すメモリセルアレイ22、及び、図3に示すメモリセルアレイ24、図4に示すメモリセルアレイ26は、ブロック管理テーブル14における、不良ブロック処理後の物理ブロックの状態を表す。尚、いうまでもないが、メモリセルアレイ21乃至26は、便宜上区別して表しているが、実質同一のものである。

【0019】

コントローラ11は、ブロック管理テーブル14と予備ブロック管理手段16とを含む。ブロック管理テーブル14は、論理ブロックのアドレスと物理ブロックのアドレスとの対応付けを行うものであり、物理ブロックのユーザ領域と、予備領域(本発明では予備領域を構成するブロックを予備ブロックという)との管理も行う。ユーザ領域には、データが何も書かれていないブロック(本発明では「ユーザ領域中の空きブロック」という)を含むものとする。予備ブロック(reserve)35は、ユーザ領域の有効な、実際に使用中のデータが書き込まれている有効ブロック(valid)31,32が不良となったときに(ここでは、不良となったブロックを(error)34としている)、有効ブロック(valid)31,32と置き換えられるものであり、ブロック管理テーブル14を更新することにより、有効ブロック(valid)37として使用可能とする。エラーのあったブロック(error)34は、不良ブロック(bad)36としてブロック管理テーブル14のアドレスの対応付けのエントリーから外される。予備ブロック管理手段16は、予備ブロックの残数を計数するためのカウンター回路と、予備ブロックの残数の閾値を設定するための回路とで構成され、予備ブロックの残数と閾値とを比較判定する機能を有する。尚、ブロック管理テーブル14はフラッシュメモリ12内に設けることもできる。

【0020】

更に、コントローラ11はエラー訂正回路(ECC)15を含む。エラー訂正回路15は、フラッシュメモリ12がホスト1から書き込み命令を受けると、エラー訂正によって元のデータに復元するためのエラーチェックコードを書き込みデータに付加する。そして、エラーチェックコードを含む書き込みデータが、フラッシュメモリ12の書き込み及び読み出しの単位であるセクター内に記憶される。次に、読み出し命令を受けたとき、エラー訂正回路15によってエラーが検出(エラーチェック)されると、誤ったデータを訂正してからホスト1に送出する。更にエラー訂正回路15は、bitエラー数の閾値設定、bitエラー数と閾値との比較判定ができるように構成されている。尚、コントローラ11には、不図示のCPU並びに該CPUに実行させるためのプログラム(ファームウエア)が具備されており、後述する図6の処理は、CPUが当該ファームウエアに基づき実行するものである。

【0021】

(ブロックの管理方法)

以下、図2、図5及び図6を用いて、ブロックの管理方法について説明する。

【0022】

(bitエラーがない場合)

図6は、ブロックの管理方法を示すフローチャートである。先ず、ST1で、フラッシュメモリデバイス2がホスト1から読み出し命令を受けると読み出しが開始される。次に、コントローラ11に設けられたエラー訂正回路15によってエラーチェックが行われ(ST2)、エラーがあるかないか判断し(ST3)、エラーがない場合は、フラッシュメモリに12記憶されているユーザデータをそのままホスト1へ送出し(ST15)、読み出しを完了する。

【0023】

(bitエラーがあり、予備ブロック残数が閾値(50%)に至る前)

デバイス使用開始直後は、不良ブロックが発生する確率が低く、予備ブロックを殆ど使用しないため、予備ブロック残数は100%に近い値を示し、その後デバイスの使用回数が増加してくると、不良ブロックの代替が行われて予備ブロックが少なくなり、予備ブロック残数は50%に近づく。尚、図6において、予備ブロック残数の閾値を50%として説明するが、実際にはブロック数で設定している。

【0024】

ST3において、エラーチェックの結果、bitエラーがあると判定されると、予備ブロック残数チェックが行われる(ST4)。予備ブロック残数が予備ブロック管理手段16に設定された閾値(50%)に至る前かどうか判断し(ST5)、Yesであり、且つ、エラー訂正回路15により、bitエラー数が4(閾値m)以上であるか判断し(ST6)、Noであればエラー訂正回路15によりbitエラーを訂正して(ST7)、データをホスト1へ送出し(ST15)、読み出しを完了する。

【0025】

次に、ST6で、bitエラー数が4(閾値m)以上と判定された場合の不良ブロックの処理方法について、図2を用いて説明する。今、メモリセルアレイ21に示すBlock3(error)34でbitエラーが発生しているとする。エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、メモリセルアレイ21の予備ブロックであるBlock8000(reserve)35に転送する。その後、エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブル14を更新して、Block3をメモリセルアレイ22に示すBlock3(Bad)36の状態にすると同時に、Block8000(reserve)35をメモリセルアレイ22に示すBlock8000(valid)37の状態にする(ST8)。そして、RAM13に設けたバッファに一旦保存されたデータをホスト1へ送出し(S15)、読み出しを完了する。

【0026】

(bitエラーがあり、予備ブロック残数が閾値(50%)に至った後)

デバイス使用開始から時間が経過してくると、不良ブロックが発生する確率が高くなり、予備ブロック残数は50%以下となり、更にデバイスを使用し続けると0%となる。

【0027】

ST5において、予備ブロック残数が閾値(50%)以下と判断されると、エラー訂正回路15によりbitエラー数が4(閾値m)以上であるか判断し(ST9)、Noであれば、エラー訂正回路15によりbitエラーを訂正して(ST10)、データをホスト1へ送出し(ST15)、読み出しを完了する。

【0028】

ST9において、bitエラー数が4(閾値m)以上と判定されると、更に、bitエラー数が6(閾値n・・エラー訂正回路の能力値)以上かの判定がなされる(ST11)。bitエラー数が6(閾値n)未満の場合、リフレッシュを行い(ST12)、データをホスト1へ送出し(ST15)、読み出しを完了する。リフレッシュ方法及びホスト1へのデータの送出については後述する。

【0029】

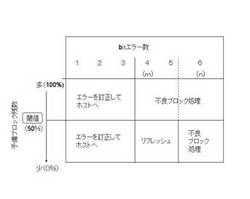

ST11において、bitエラー数が6(閾値n)以上と判定されると、ST13へ進み、bitエラー数が仮に7以上であるか判断し、Yesであれば、ホスト1にエラーを通知する(ST16)。7未満であれば、ST8と同様の不良ブロック処理が行われ(ST14)、データをホスト1へ送出し(ST15)、読み出しを完了する。以上の処理をマップ状に表したものが図5である。尚、ST15のホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0030】

(リフレッシュの方法例1)

図6に示すST12におけるリフレッシュのやり方の第1の例について、図3を用いて説明する。今、メモリセルアレイ23に示すBlock3(error)34でbitエラーが発生しているとする。読み出しの際、エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、メモリセルアレイ23に示すユーザ領域中の空きブロックであるBlock2(empty)33に転送する。その後、Block3(error)34はその全データを消去し、ユーザ領域中の空きブロックとしてブロック管理テーブル14を更新し、Block3をメモリセルアレイ24に示すBlock3(empty)39の状態にする。それと同時に、Block2をメモリセルアレイ24に示すBlock2(valid)38の状態にする。尚、上記の例では、データの転送先をユーザ領域中の空きブロックとしたが、これに代えて予備ブロック(例えば、Block8000(reserve)35)をデータ転送先とし、転送元のブロック(Block3(error)34)はその全データを消去し、予備ブロックとしてブロック管理テーブル14を更新してもよい。ホスト1に対しては、前記バッファに一時保存しておいたデータを送出する。ホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0031】

(リフレッシュの方法例2)

次に、リフレッシュのやり方の第2例について図4を用いて説明する。今、メモリセルアレイ25に示すBlock3(error)34でbitエラーが発生しているとする。読み出しの際、エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、Block3(error)34を消去する。そして、元のBlock3(error)34に転送する。この場合、説明の便宜上、ブロックの状態がメモリセルアレイ25に示すBlock3(error)34から、メモリセルアレイ26に示すBlock3(valid)40に変化しているが、Block3(error)34は、不良ブロック処理前の状態であり、有効ブロックである。つまり、データを元のブロックに書き戻しているにすぎないため、ブロック管理テーブル14の更新を行う必要はない。尚、この場合もホスト1に対しては、前記バッファに一時保存しておいたデータを送出すればよい。ホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0032】

尚、本フラッシュメモリデバイスに表示手段をさらに設け、予備ブロック残数が所定数に至った段階で、該表示手段を駆動してもよいし、予備ブロック残数が所定数に至った段階で、ホスト1に通知してもよい。これにより、予備ブロックの状態を管理者が知ることができ、新品とタイムリーに交換することにより、システムのより安全な運用を図ることができる。

【図面の簡単な説明】

【0033】

【図1】本発明の実施形態を実行するシステムの基本構成例である。

【図2】不良ブロック処理におけるブロック管理テーブルの例である。

【図3】リフレッシュにおけるブロック管理テーブルの第1の例である。

【図4】リフレッシュにおけるブロック管理テーブルの第2の例である。

【図5】不良ブロック処理方法例をマップ状に表したものである。

【図6】本発明方法の実施形態を実行するフローチャートの例である。

【符号の説明】

【0034】

1 ホスト

2 フラッシュメモリデバイス

11 コントローラ

12 NAND型フラッシュメモリ

13 RAM

14 ブロック管理テーブル

15 エラー訂正回路

16 予備ブロック管理手段

【技術分野】

【0001】

本発明は、フラッシュメモリの管理方法及び該方法を使用するフラッシュメモリデバイスに関する。

【背景技術】

【0002】

EEPROM(電気的にデータの消去及び書き換えが可能な不揮発性メモリ)の一種としてフラッシュメモリが知られている。取り分けNAND型フラッシュメモリは、安価で且つデータの書き込み時間が短いため、ハードディスクの置き換えや、各種コンテンツを格納する用途で使用されている。NAND型フラッシュメモリは、その構造上、製造段階で不良ブロックが存在する。また、書き込み回数や読み出し回数の増大によってもデータ化けが生じ、不良ブロックとなる。このため、ユーザ領域の他、予備のブロックを予め設けておき、不良ブロックを予備のブロックに置き換えている。予備ブロックがゼロになると、もはやメモリは使用不可能となる。そのため、本出願人は、斯かる事態が発生する前に代替品と交換させるべく、管理者に通知する記憶装置について提案している。

【0003】

しかしながら、専らコンテンツを読み出す用途に使用されている場合、リードディスターブエラーによりユーザ領域の多数のブロックが一度に不良ブロックになり、予備領域が急激に減少する可能性がある。斯かる場合には、管理者に通知後、新品との交換に間に合わない事態も想定される。

【特許文献1】特開2000−181805号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

ここにおいて、本発明が解決すべき課題は、予備ブロックの急激な減少を防止して、フラッシュメモリデバイスの安全な運用を図るための管理方法及び該方法を使用するフラッシュメモリデバイスの提供にある。その他の課題は、明細書、図面、特に特許請求の範囲から自ずと明らかとなろう。

【課題を解決するための手段】

【0005】

上記課題解決のため、本発明方法は、以下に上位概念から下位概念に亙り列挙する新規な特徴的構成を採用する。

【0006】

即ち、本発明方法は、

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新するフラッシュメモリの管理方法を提供する。

【0007】

(作用)

本構成では、エラー訂正回路により得られるbitエラー数の閾値を2個設け、その閾値に基づいて、予備ブロックの残数が閾値に至る前後で不良ブロックの処理方法を変えることにより、リードディスターブエラーによるデータ破壊を効率よく、且つ確実に防止するとともに、メモリデバイスの寿命を延ばすことが可能となる。即ち、予備ブロックの残数が閾値に至る前は、不良ブロックを予備ブロックに代替するポイントを、マージンを持たせてエラー訂正回路の能力値n(訂正可能な上限値)よりも低いbitエラー数閾値mに設定することにより、データ破壊を確実に防止することができる。また、リフレッシュを行わないので、ホストからのメモリアクセスの一時的な中断を回避することができる。予備ブロックの残数が閾値に至った後は、予備ブロックに代替するポイントをnとし、m以上n未満のときはリフレッシュを実行する。このことにより、今まで不良ブロックとして捨てていたブロックを、有効なブロックとして扱うことができ、延いてはフラッシュメモリの寿命を延ばすことが可能となる。

【0008】

ここで、エラー訂正回路によって得られるbitエラー数が閾値m未満のときは、予備ブロックの残数に関係なく、エラーを起こしたデータをエラー訂正回路により訂正してからホストへ返すことのみを行う。即ち、bitエラー数がエラー訂正回路の能力値nよりも充分に小さい範囲にあるときは、読み出し対象となっているブロックが寿命に達するまでには猶予があるため、予備ブロックへの代替やリフレッシュを行わない。従って、データ転送の一時的な中断を回避してホストからのメモリアクセスを優先させることができ、且つ、メモリデバイスの寿命を延ばすことが可能となる。

【0009】

また、前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することが好ましい。

【0010】

(作用)

予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った以降のリフレッシュは、データが書き込まれていない未使用の領域を使用して行われる。即ち、エラーを起こしたデータを含むブロックの全データを、エラーを起こしたデータに関してデータ誤りの訂正を行った後、未使用の領域であるユーザ領域中の空きブロック若しくは予備ブロックにコピーし、元のブロックの全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとしてブロック管理テーブルを更新する。コピーのために読み出されたデータは一旦バッファに保存され、その後ユーザ領域中の空きブロック若しくは予備ブロックに転送される。データのコピー完了後に、元のブロックのデータを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとすることにより、コピーの途中で突然の電源遮断が起こっても、データは元のブロックに保存されており消失しない。これにより、メモリデバイスの信頼性を高めることが可能となる。

【0011】

また、前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻してもよい。

【0012】

(作用)

これにより、ブロック管理テーブルの更新を行わずにリフレッシュすることが可能となる。

【0013】

また、表示手段をさらに有し、予備ブロック残数が所定数に至った段階で、該表示手段を駆動してもよいし、予備ブロック残数が所定数に至った段階で、ホストに通知してもよい。

【0014】

これにより、予備ブロックの状態を管理者が知ることができ、新品とタイムリーに交換することにより、システムのより安全な運用を図ることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について図面を用いて説明するが、本発明は特許請求の範囲内において種々の形態を採ることができ、下記実施形態に限定されないことはいうまでもない。

【0016】

(システム基本構成)

図1は、本発明におけるフラッシュメモリデバイスのシステム基本構成図である。本発明は、NAND型フラッシュメモリ12(本明細書において、特に必要のない限り、単に“フラッシュメモリ”という)とフラッシュメモリ12にデータの書き込みや読み出しを実行するコントローラ11からなるフラッシュメモリデバイス2と、フラッシュメモリデバイス2にデータの書き込みや読み出しのコマンドを発行するホスト1を基本構成として有するシステムで実行され得る。尚、コントローラ11には、必要に応じRAM13を接続する。フラッシュメモリデバイス2とホスト1は、例えばMPEG音楽プレーヤのように、所定の機器として一体に構成されていてもよいし、ホスト1がPCで構成され、フラッシュメモリデバイス2がPCとUSB接続される機器のように、別体で構成してもよい。近年では、ハードディスクの置き換えとして、SSD(Solid

State Drive)のように、複数のフラッシュメモリ12とコントローラ11とRAM13とが一体に構成され、PCとIDE接続される機器もある。

【0017】

フラッシュメモリ12は、複数の物理ブロックで構成されているが、周知の通り、フラッシュメモリ12は、ユーザ領域の他、ユーザ領域が不良となった場合の代替領域である予備領域を含む。

【0018】

図2、図3及び図4は、フラッシュメモリ12の物理ブロックを模式的に表した図であり、ブロック管理テーブルにおけるブロックの管理方法の模式図である。フラッシュメモリ12は、Block0からBlock8191までの8192ブロックで構成され、各ブロック番号(Block0〜8191)は、メモリセルアレイ21乃至26の同じ物理ブロックに対応している。図2は不良ブロック処理におけるブロック管理テーブルの例であり、図3はリフレッシュにおけるブロック管理テーブルの第1の例、図4はリフレッシュにおけるブロック管理テーブルの第2の例である。図2に示すメモリセルアレイ21、及び、図3に示すメモリセルアレイ23、図4に示すメモリセルアレイ25は、ブロック管理テーブル14における、不良ブロック処理前の物理ブロックの状態を表す。図2に示すメモリセルアレイ22、及び、図3に示すメモリセルアレイ24、図4に示すメモリセルアレイ26は、ブロック管理テーブル14における、不良ブロック処理後の物理ブロックの状態を表す。尚、いうまでもないが、メモリセルアレイ21乃至26は、便宜上区別して表しているが、実質同一のものである。

【0019】

コントローラ11は、ブロック管理テーブル14と予備ブロック管理手段16とを含む。ブロック管理テーブル14は、論理ブロックのアドレスと物理ブロックのアドレスとの対応付けを行うものであり、物理ブロックのユーザ領域と、予備領域(本発明では予備領域を構成するブロックを予備ブロックという)との管理も行う。ユーザ領域には、データが何も書かれていないブロック(本発明では「ユーザ領域中の空きブロック」という)を含むものとする。予備ブロック(reserve)35は、ユーザ領域の有効な、実際に使用中のデータが書き込まれている有効ブロック(valid)31,32が不良となったときに(ここでは、不良となったブロックを(error)34としている)、有効ブロック(valid)31,32と置き換えられるものであり、ブロック管理テーブル14を更新することにより、有効ブロック(valid)37として使用可能とする。エラーのあったブロック(error)34は、不良ブロック(bad)36としてブロック管理テーブル14のアドレスの対応付けのエントリーから外される。予備ブロック管理手段16は、予備ブロックの残数を計数するためのカウンター回路と、予備ブロックの残数の閾値を設定するための回路とで構成され、予備ブロックの残数と閾値とを比較判定する機能を有する。尚、ブロック管理テーブル14はフラッシュメモリ12内に設けることもできる。

【0020】

更に、コントローラ11はエラー訂正回路(ECC)15を含む。エラー訂正回路15は、フラッシュメモリ12がホスト1から書き込み命令を受けると、エラー訂正によって元のデータに復元するためのエラーチェックコードを書き込みデータに付加する。そして、エラーチェックコードを含む書き込みデータが、フラッシュメモリ12の書き込み及び読み出しの単位であるセクター内に記憶される。次に、読み出し命令を受けたとき、エラー訂正回路15によってエラーが検出(エラーチェック)されると、誤ったデータを訂正してからホスト1に送出する。更にエラー訂正回路15は、bitエラー数の閾値設定、bitエラー数と閾値との比較判定ができるように構成されている。尚、コントローラ11には、不図示のCPU並びに該CPUに実行させるためのプログラム(ファームウエア)が具備されており、後述する図6の処理は、CPUが当該ファームウエアに基づき実行するものである。

【0021】

(ブロックの管理方法)

以下、図2、図5及び図6を用いて、ブロックの管理方法について説明する。

【0022】

(bitエラーがない場合)

図6は、ブロックの管理方法を示すフローチャートである。先ず、ST1で、フラッシュメモリデバイス2がホスト1から読み出し命令を受けると読み出しが開始される。次に、コントローラ11に設けられたエラー訂正回路15によってエラーチェックが行われ(ST2)、エラーがあるかないか判断し(ST3)、エラーがない場合は、フラッシュメモリに12記憶されているユーザデータをそのままホスト1へ送出し(ST15)、読み出しを完了する。

【0023】

(bitエラーがあり、予備ブロック残数が閾値(50%)に至る前)

デバイス使用開始直後は、不良ブロックが発生する確率が低く、予備ブロックを殆ど使用しないため、予備ブロック残数は100%に近い値を示し、その後デバイスの使用回数が増加してくると、不良ブロックの代替が行われて予備ブロックが少なくなり、予備ブロック残数は50%に近づく。尚、図6において、予備ブロック残数の閾値を50%として説明するが、実際にはブロック数で設定している。

【0024】

ST3において、エラーチェックの結果、bitエラーがあると判定されると、予備ブロック残数チェックが行われる(ST4)。予備ブロック残数が予備ブロック管理手段16に設定された閾値(50%)に至る前かどうか判断し(ST5)、Yesであり、且つ、エラー訂正回路15により、bitエラー数が4(閾値m)以上であるか判断し(ST6)、Noであればエラー訂正回路15によりbitエラーを訂正して(ST7)、データをホスト1へ送出し(ST15)、読み出しを完了する。

【0025】

次に、ST6で、bitエラー数が4(閾値m)以上と判定された場合の不良ブロックの処理方法について、図2を用いて説明する。今、メモリセルアレイ21に示すBlock3(error)34でbitエラーが発生しているとする。エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、メモリセルアレイ21の予備ブロックであるBlock8000(reserve)35に転送する。その後、エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブル14を更新して、Block3をメモリセルアレイ22に示すBlock3(Bad)36の状態にすると同時に、Block8000(reserve)35をメモリセルアレイ22に示すBlock8000(valid)37の状態にする(ST8)。そして、RAM13に設けたバッファに一旦保存されたデータをホスト1へ送出し(S15)、読み出しを完了する。

【0026】

(bitエラーがあり、予備ブロック残数が閾値(50%)に至った後)

デバイス使用開始から時間が経過してくると、不良ブロックが発生する確率が高くなり、予備ブロック残数は50%以下となり、更にデバイスを使用し続けると0%となる。

【0027】

ST5において、予備ブロック残数が閾値(50%)以下と判断されると、エラー訂正回路15によりbitエラー数が4(閾値m)以上であるか判断し(ST9)、Noであれば、エラー訂正回路15によりbitエラーを訂正して(ST10)、データをホスト1へ送出し(ST15)、読み出しを完了する。

【0028】

ST9において、bitエラー数が4(閾値m)以上と判定されると、更に、bitエラー数が6(閾値n・・エラー訂正回路の能力値)以上かの判定がなされる(ST11)。bitエラー数が6(閾値n)未満の場合、リフレッシュを行い(ST12)、データをホスト1へ送出し(ST15)、読み出しを完了する。リフレッシュ方法及びホスト1へのデータの送出については後述する。

【0029】

ST11において、bitエラー数が6(閾値n)以上と判定されると、ST13へ進み、bitエラー数が仮に7以上であるか判断し、Yesであれば、ホスト1にエラーを通知する(ST16)。7未満であれば、ST8と同様の不良ブロック処理が行われ(ST14)、データをホスト1へ送出し(ST15)、読み出しを完了する。以上の処理をマップ状に表したものが図5である。尚、ST15のホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0030】

(リフレッシュの方法例1)

図6に示すST12におけるリフレッシュのやり方の第1の例について、図3を用いて説明する。今、メモリセルアレイ23に示すBlock3(error)34でbitエラーが発生しているとする。読み出しの際、エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、メモリセルアレイ23に示すユーザ領域中の空きブロックであるBlock2(empty)33に転送する。その後、Block3(error)34はその全データを消去し、ユーザ領域中の空きブロックとしてブロック管理テーブル14を更新し、Block3をメモリセルアレイ24に示すBlock3(empty)39の状態にする。それと同時に、Block2をメモリセルアレイ24に示すBlock2(valid)38の状態にする。尚、上記の例では、データの転送先をユーザ領域中の空きブロックとしたが、これに代えて予備ブロック(例えば、Block8000(reserve)35)をデータ転送先とし、転送元のブロック(Block3(error)34)はその全データを消去し、予備ブロックとしてブロック管理テーブル14を更新してもよい。ホスト1に対しては、前記バッファに一時保存しておいたデータを送出する。ホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0031】

(リフレッシュの方法例2)

次に、リフレッシュのやり方の第2例について図4を用いて説明する。今、メモリセルアレイ25に示すBlock3(error)34でbitエラーが発生しているとする。読み出しの際、エラー訂正回路15によりbitエラーを訂正してから、Block3(error)34の全データを、一旦、RAM13に設けたバッファに読み出した後、Block3(error)34を消去する。そして、元のBlock3(error)34に転送する。この場合、説明の便宜上、ブロックの状態がメモリセルアレイ25に示すBlock3(error)34から、メモリセルアレイ26に示すBlock3(valid)40に変化しているが、Block3(error)34は、不良ブロック処理前の状態であり、有効ブロックである。つまり、データを元のブロックに書き戻しているにすぎないため、ブロック管理テーブル14の更新を行う必要はない。尚、この場合もホスト1に対しては、前記バッファに一時保存しておいたデータを送出すればよい。ホスト1へのデータの送出は、各不良ブロックの処理と同時に行なってもよい。

【0032】

尚、本フラッシュメモリデバイスに表示手段をさらに設け、予備ブロック残数が所定数に至った段階で、該表示手段を駆動してもよいし、予備ブロック残数が所定数に至った段階で、ホスト1に通知してもよい。これにより、予備ブロックの状態を管理者が知ることができ、新品とタイムリーに交換することにより、システムのより安全な運用を図ることができる。

【図面の簡単な説明】

【0033】

【図1】本発明の実施形態を実行するシステムの基本構成例である。

【図2】不良ブロック処理におけるブロック管理テーブルの例である。

【図3】リフレッシュにおけるブロック管理テーブルの第1の例である。

【図4】リフレッシュにおけるブロック管理テーブルの第2の例である。

【図5】不良ブロック処理方法例をマップ状に表したものである。

【図6】本発明方法の実施形態を実行するフローチャートの例である。

【符号の説明】

【0034】

1 ホスト

2 フラッシュメモリデバイス

11 コントローラ

12 NAND型フラッシュメモリ

13 RAM

14 ブロック管理テーブル

15 エラー訂正回路

16 予備ブロック管理手段

【特許請求の範囲】

【請求項1】

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新することを特徴とするフラッシュメモリの管理方法。

【請求項2】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項3】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻すことを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項4】

予備ブロック残数が閾値に至った段階で、表示手段を駆動し若しくはホストに通知すすることを特徴とする請求項1乃至請求項3いずれか1項記載のフラッシュメモリの管理方法。

【請求項5】

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新することを特徴とするフラッシュメモリデバイス。

【請求項6】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することを特徴とする請求項5記載のフラッシュメモリデバイス。

【請求項7】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻すことを特徴とする請求項5記載のフラッシュメモリデバイス。

【請求項8】

表示手段をさらに有し、予備ブロック残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項5乃至請求項7いずれか1項記載のフラッシュメモリデバイス。

【請求項9】

予備ブロック残数が所定数に至った段階で、ホストに通知することを特徴とする請求項5乃至請求項7いずれか1項記載のフラッシュメモリデバイス。

【請求項1】

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新することを特徴とするフラッシュメモリの管理方法。

【請求項2】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項3】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻すことを特徴とする請求項1記載のフラッシュメモリの管理方法。

【請求項4】

予備ブロック残数が閾値に至った段階で、表示手段を駆動し若しくはホストに通知すすることを特徴とする請求項1乃至請求項3いずれか1項記載のフラッシュメモリの管理方法。

【請求項5】

ホストからの読み出し命令を受けたとき、エラー訂正回路によって得られるbitエラー数が、前記エラー訂正回路の能力値n(nは正の整数)より小さい閾値m(mは正の整数,m<n)以上であったときに、当該エラーを起こしたデータを含むブロックの全データをエラー訂正して予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとしてブロック管理テーブルを更新し、前記予備ブロックの残数が予備ブロック管理手段に設定された閾値に至った後、前記エラー訂正回路によって得られるbitエラー数が閾値m以上n未満であったときに当該エラーを起こしたデータを含むブロックの全データをエラー訂正してリフレッシュし、閾値nに至ったときは当該エラーを起こしたデータを含むブロックの全データをエラー訂正して前記予備ブロックにコピーした後、前記エラーを起こしたデータを含むブロックを不良ブロックとして前記ブロック管理テーブルを更新することを特徴とするフラッシュメモリデバイス。

【請求項6】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを、一旦バッファに読み出してからユーザ領域中の空きブロック若しくは予備ブロックに転送し、前記エラーを起こしたデータを含むブロックはその全データを消去し、ユーザ領域中の空きブロック若しくは予備ブロックとして前記ブロック管理テーブル更新することを特徴とする請求項5記載のフラッシュメモリデバイス。

【請求項7】

前記リフレッシュは、前記エラー訂正回路によりエラー訂正した後、当該エラーを起こしたデータを含むブロックの全データを一旦バッファに転送し、該ブロックを消去後、バッファから該ブロックに書き戻すことを特徴とする請求項5記載のフラッシュメモリデバイス。

【請求項8】

表示手段をさらに有し、予備ブロック残数が所定数に至った段階で、該表示手段を駆動することを特徴とする請求項5乃至請求項7いずれか1項記載のフラッシュメモリデバイス。

【請求項9】

予備ブロック残数が所定数に至った段階で、ホストに通知することを特徴とする請求項5乃至請求項7いずれか1項記載のフラッシュメモリデバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2010−61507(P2010−61507A)

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願番号】特願2008−228035(P2008−228035)

【出願日】平成20年9月5日(2008.9.5)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

【公開日】平成22年3月18日(2010.3.18)

【国際特許分類】

【出願日】平成20年9月5日(2008.9.5)

【出願人】(594096966)株式会社ハギワラシスコム (32)

【Fターム(参考)】

[ Back to top ]