フラッシュメモリセルの自動昇圧システム

【課題】NANDストリングの異なったセルのプログラミングサイクル中にワードライン0に結合されたメモリセルのしきい値電圧のシフトを減らしたり、または防止する。

【解決手段】消去された領域の自己昇圧と局部的な自己昇圧方式を含む色々な異なった自己昇圧方式のいずれかで実施される。改造された消去された領域の自己昇圧方式では、低い電圧が選択されたワードラインのソース側の2本以上のワードラインに印加され、帯域から帯域へのトンネリングを低減すると共に2つの昇圧されたチャネル領域間の絶縁を改善する。改造された局部的な自己昇圧方式では、0ボルトまたは低い電圧が選択されたワードラインのソース側の2本以上のワードラインとドレイン側の2本以上のワードラインに印加されて、帯域から帯域へのトンネリングを低減すると共に選択されたワードラインに結合されたチャネル領域の絶縁を改善する。

【解決手段】消去された領域の自己昇圧と局部的な自己昇圧方式を含む色々な異なった自己昇圧方式のいずれかで実施される。改造された消去された領域の自己昇圧方式では、低い電圧が選択されたワードラインのソース側の2本以上のワードラインに印加され、帯域から帯域へのトンネリングを低減すると共に2つの昇圧されたチャネル領域間の絶縁を改善する。改造された局部的な自己昇圧方式では、0ボルトまたは低い電圧が選択されたワードラインのソース側の2本以上のワードラインとドレイン側の2本以上のワードラインに印加されて、帯域から帯域へのトンネリングを低減すると共に選択されたワードラインに結合されたチャネル領域の絶縁を改善する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、全体としてフラッシュEEPROM(電気的に消去可能でプログラム可能な読み出し専用メモリ)形の不揮発性半導体メモリ、特にNAND形メモリセルアレイを操作する構造および方法に関する。

【背景技術】

【0002】

特にフラッシュEEPROMセルのアレイを使っている小形のファクタカードの形式で今日使用されている商業的に成功している不揮発性メモリ製品が数多くある。

【0003】

一般的なフラッシュEEPROMの構成の1つに、NANDアレイを使用しているものがあり、その場合、多数のメモリセルのストリングが、1つ以上の選択トランジスタを介して個々のビットラインと基準電位との間に接続されている。そのようなアレイの一部分が図2Aの平面図に示されている。BL0〜BL4(そのうちのBL1〜BL3は、さらに12〜16とラベル付けされている)は、大域の垂直金属ビットライン(図示せず)への拡散されたビットライン接続部を表している。4つのフローティングゲートメモリセルが各ストリングに示されているが、個々のストリングは、一般的には列にフローティングゲートなどの16、32またはそれよりも多いメモリセル電荷記憶素子を有している。WL0〜WL3とラベル付けされたコントロールゲート(ワード)ライン(図2Aの線A−Aに沿った断面の図2BでP2とラベル付けされている)とストリング選択ラインSGD、SGSは、しばしばポリシリコン(図2BにおいてP1とラベル付けされている)の幾つかのフローティングゲートの行の上側を渡って多くのストリングを交差して延びている。一方、トランジスタ40、50に対して、コントロールゲートとフローティングゲートとは電気的に接続されてもよい(図示せず)。コントロールゲートラインは、一般的に自己整合されたスタックとしてフローティングゲートの上側に形成され、また図2Bに示されているように、中間の誘電体層19を介して互いに容量結合されている。ストリングの頂部および底部は、周辺機器から電気的に駆動されているトランジスタのアクティブゲートとしてフローティングゲート材(P1)を使用するトランジスタを通常は介して、ビットラインおよび共通のソースラインに各々接続している。フローティングゲートとコントロールゲートとの間にはこのような容量結合があるため、フローティングゲートに結合されたコントロールゲート上の電圧を高めることでフローティングゲートの電圧を高めることができる。列内の個々のセルは、各ストリングを流れる電流が主として選択されたワードラインの下方のアドレス指定されたセルに記憶された電荷のレベルにのみ依存するように、ストリングの残りのセルがそれらの各々のワードライン上に比較的高い電圧をかけ、さらに1つの選択されたワードライン上に比較的低い電圧をかけることでストリングの残りのセルをオンにすることによってプログラミング中に読み出されて検証される。その電流は、一般に多数の並列なストリングに対して検知され、それによってフローティングゲートの行に平行に沿って電荷のレベル状態が読み出される。

【0004】

NAND形フラッシュメモリシステムとそれらの動作の関連例が、米国特許第5,570,315号(特許文献1)、第5,774,397号(特許文献2)、第6,046,935号(特許文献3)、第6,456,528号(特許文献4)、第6,522,580号(特許文献5)に示され、これらの特許の全ては本願明細書において参照により援用されている。

【0005】

現在のフラッシュEEPROMアレイの電荷記憶素子は、一般にドープされたポリシリコン材から形成された最も一般的な導電性フローティングゲートとなっている。一方、必ずしも導電性である必要はないが電荷記憶能力を有する他の材料も使用される。そのような代わりの材料の例として窒化ケイ素がある。そのようなセルについては、野崎隆明らによる論文「半導体ディスクに適用するMONOSメモリセルを有する1−MbのEEPROM」,固体回路のIEEEジャーナル,第26巻,第4号,1991年4月,第497頁〜501頁 (Takaaki Nozaki et al.,“A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application", IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501)(非特許文献1)で説明されている。

【0006】

一般的な不揮発性フラッシュアレイのメモリセルは、同時に消去される独立したセルのブロックに分割される。即ち、2つ以上のブロックが1回の消去動作で消去されることもあるが、ブロックは、消去ユニットとして個別に同時に消去可能な最小数のセルを有している。各ブロックは、プログラミングと読み出しの基本ユニットとしてデータプログラミングおよび読み出し動作を同時に受ける最小数のセルとして定義されるページで、一般に1ページ以上のデータを記憶するが、2ページ以上が1回の操作でプログラムされたり、または読み出されることもある。各ページは、一般に1セクタ以上のデータを記憶するものであり、セクタの大きさは、ホストシステムによって規定されている。一例として、512バイトのユーザデータのセクタがあり、ユーザデータに関する何バイトかのオーバーヘッド情報および/またはそれを記憶しているブロックに加えて磁気ディスクドライブと共に確立された基準に従っている。

【0007】

集積回路への適用のほとんどに見られるように、或る集積回路の機能を実行するのに必要なシリコン基板の領域を縮小すると言うプレッシャーがフラッシュEEPROMアレイにもある。所定サイズのメモリカードと他の種類のパッケージの記憶容量を増やしたり、または容量の増大とサイズの縮小の両方を行うために、シリコン基板の所定領域に記憶されるデジタルデータの量を増やすことが引き続き求められている。データの記憶密度を高めるもう1つの方法は、メモリセルの電荷記憶素子当り1つよりも多いビットのデータを記憶することである。このことは、電荷記憶素子の許容電圧または電荷記憶ウインドウを2つよりも多い状態に分割することで達成される。そのような4つの状態を使用することで、各セルが2ビットのデータを記憶することができるようにし、8つの状態がセル当り3ビットのデータを記憶することができるようにする等々である。多状態のフラッシュEEPROMの構造と動作が、米国特許第5,043,940号(特許文献6)、第5,172,338号(特許文献7)、第5,570,315号(特許文献1)および第6,046,935号(特許文献3)に説明されている。

【0008】

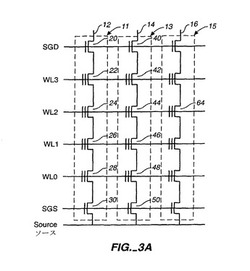

NAND構造を使用したフラッシュメモリシステム用の一般的な構成であれば、NANDアレイが含まれ、その場合、各アレイは幾つかのNANDストリングを有している。例えば、図3Aは、図2AのメモリアレイのNANDストリング11、13、15を3つだけ示し、そのアレイは3つより多いNANDストリングを収容している。図3AのNANDストリングの各々は、2つの選択トランジスタと4つのメモリセルとを有している。例えば、NANDストリング11は、選択トランジスタ20、30とメモリセル22、24、26、28を有している。NANDストリング13は、選択トランジスタ40、50とメモリセル42、44、46、48とを有している。各ストリングは、その選択トランジスタ(例えば、選択トランジスタ30と選択トランジスタ50)によってソースラインに接続されている。選択ラインSGSは、ソース側の選択ゲートを制御するために使用されている。色々なNANDストリングが、選択ラインSGDによって制御される選択トランジスタ20、40などによってそれぞれのビットラインに接続されている。他の実施形態では、選択ラインは必ずしも共通である必要はない。ワードラインWL3は、メモリセル22およびメモリセル42用のコントロールゲートに接続されている。ワードラインWL2は、メモリセル24およびメモリセル44用のコントロールゲートに接続されている。ワードラインWL1は、メモリセル26およびメモリセル46用のコントロールゲートに接続されている。ワードラインWL0は、メモリセル28およびメモリセル48用のコントロールゲートに接続されている。図に示されているように、各ビットラインとそれぞれのNANDストリングは、メモリセルアレイの列を有している。ワードライン(WL3、WL2、WL1、WL0)は、アレイの行を有している。各ワードラインは、その行にある各メモリセルのコントロールゲートに接続している。例えば、ワードラインWL2は、メモリセル24、44、64用のコントロールゲートに接続されている。

【0009】

図3Bは、各アレイを1組の共通のワードラインによって制御した状態で幾つかのNANDアレイを描いた回路図である。図2Aと図3のアレイは、図3Bでは1番上のアレイとして現れている。図3Bに示されているように、同じアレイにおける各NANDストリング(例えば、11、13)は、複数のビットライン12、14・・・のうちの1つおよび共通のソースラインに接続され、また共通の組のワードライン(WL0〜WL3)によって制御されている。

【0010】

各メモリセルは、データ(アナログまたはデジタル)を記憶することができる。1ビットのデジタルデータ(バイナリメモリセル)を記憶する場合、メモリセルの取りうるしきい値電圧の範囲は、論理データの「1」および「0」が割り当てられる2つの範囲に分割される。NAND形フラッシュメモリの一例では、メモリセルの消去後、電圧しきい値は負であり、論理「1」として定義されている。プログラミング動作後のしきい値電圧は正であり、論理「0」として定義されている。しきい値電圧が負で、そのコントロールゲートに0ボルトが印加され、読み出しが実施されると、メモリセルは電流を通して、論理1が記憶されていることを示すことになる。しきい値電圧が正で、読み出し動作が試みられると、メモリセルはオンに切り替わらず、それによって論理0が記憶されていることが示される。メモリセルは、さらに多くのレベルの情報を、例えば多くのビットのデジタルデータを記憶することができる。多くのレベルのデータを記憶する場合、取りうるしきい値電圧の範囲は、データのレベル数に分割される。例えば、4つのレベルの情報が記憶されれば、4つのしきい値電圧範囲が存在することになり、各範囲は1つのデータ値に割り当てられる。しきい値電圧の複数の(2よりも多い)範囲間の区別によってデータを記憶するメモリは、多重状態メモリとして知られている。NAND形メモリの一例では、消去動作後のしきい値電圧は、負であり、「11」として定義されている。正のしきい値電圧は、「10」、「01」および「00」の状態に対して使用される。

【0011】

NANDフラッシュメモリセルをプログラムする場合、プログラム電圧がコントロールゲートに印加され、またプログラムするために選択されるNANDストリングのチャネル領域が接地される(0ボルト)。NANDストリングの下方のチャネル領域からの電子は、フローティングゲート内に注入される。電子がフローティングゲートに蓄積すると、そのフローティングゲートは負に充電され、またセルのしきい値電圧が高められる。選択されたNANDストリングのチャネル領域を接地するために、対応するビットラインは接地される(0ボルト)一方、SGDは、選択トランジスタのしきい値電圧よりも高い十分な高電圧(一般には、例えば3.3ボルトのVdd)に接続される。プログラム電圧をプログラムされているセルのコントロールゲートに印加するために、そのプログラム電圧は適切なワードラインに印加される。前に説明したように、そのワードラインは、同じワードラインを使用している他のNANDストリングの各々にある1つのセルにも接続されている。例えば、図3Aのセル24をプログラムする場合、プログラム電圧がセル44のコントロールゲートにも印加されることになる。これは、両方のセルが同じワードラインを共有しているためである。同じワードラインに接続された他のセルをプログラムせずにワードライン上の1つのセルをプログラムしたい場合、例えばセル24をプログラムして、セル44をプログラムしたくない場合、問題が生じる。プログラム電圧はワードラインに接続された全てのセルに印加されるので、そのワードライン上の選択されなかったセル(プログラムされるべきでないセル)は、不注意でプログラムされるかもしれない。例えば、セル44はセル24に隣接している。セル24をプログラムする場合、セル44が何気無くプログラムされるおそれがある。選択されたワードライン上の選択されていないセルの何気無いプログラミングは、「プログラム障害」と称される。一般的に言って、「プログラム障害」は、正または負のいずれかの方向へのあらゆる望まないしきい値電圧シフトを説明するのに使用されるものであり、そのシフトはプログラミング動作中に起きて、選択されたワードラインに必ずしも限定されるものではない。

【0012】

プログラム障害を防ぐためには幾つかの技術を利用することができる。「自己昇圧」(「SB」)として知られている一つの方法が、K.D.スーらによる「インクリメンタル・ステップ・パルスプログラミング方式を有する3.3ボルト、32MbのNANDフラッシュメモリ」,固体回路のジャーナル,第30巻,第11号,1995年11月,第1149〜1155頁 (K. D. Suh et al.,“A 3.3V 32Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme," Journal of Solid-State Circuits, Vol. 30, No. 11, Nov. 1995, pp. 1149-55)(非特許文献2)において提案されている。SB方式を使用したプログラミング中に、選択されなかったNANDストリングのチャネル領域は、それらの対応するビットラインから電気的に絶縁されている。引き続いて、中間のパス電圧(例えば、10ボルト)が選択されなかったワードラインに印加される一方、高いプログラム電圧(例えば、18ボルト)が選択されたワードラインに印加される。この用例では、用語「絶縁」と「電気的に絶縁」とは互いに交換可能に使用され、また用語「書き込み電圧」、「プログラム電圧」および「プログラミング電圧」は互いに交換可能に使用される。選択されなかったNANDストリングのチャネル領域は、選択されなかったワードラインに容量的に結合され、選択されなかったNANDストリングのチャネル領域に電圧(例えば、0.6の結合比を仮定すると6ボルト)を存在させる。この所謂「自己昇圧」は、選択されなかったNANDストリングのチャネル領域と選択されたワードラインに印加されるプログラム電圧との間の電位差を小さくする。その結果、選択されなかったNANDストリングにおけるメモリセルに対して、また特に選択されたワードライン上のこのようなストリングにおけるメモリセルに対して、トンネル酸化物を渡る電圧とそれに伴いプログラム障害とが大幅に低減される。

【0013】

図3Aを参照すると、ビットライン12上のセルのうちの1つをプログラムするために自己昇圧プログラミング技術が、図3Aにおけるメモリアレイに適用される場合、例えば0ボルトがビットライン12に印加されると共に電圧Vdd(例えば、3.3ボルト)がビットライン14に印加される。その電圧Vddは、ドレイン側の選択ラインSGDに印加されてトランジスタ20、40をオンに切り替え、また0ボルトがソース側の選択ラインSGSに印加されてトランジスタ30、50をオフに切り替える。アレイ42〜48における全てのメモリセルが正規のオン状態(例えば、消去されたり、または負のしきい値電圧状態)になっていると仮定すると、トランジスタ40と50との間のNANDストリングにおける全てのセルのチャネル電位は、SGDに印加されるVddと選択トランジスタ40のしきい値電圧との間の差によって与えられる。例えば、Vddが3.3ボルトでかつトランジスタ40のしきい値電圧が1.3ボルトであれば、その場合全てのセル42〜48のチャネル電位は2ボルトに充電される。チャネル電位はこの場合約2ボルトの予め規定された電位に事前に充電されるので、この動作は「事前充電」と称される。NANDストリングのチャネル電位が十分に高い値(この場合2ボルト)に到達した後にトランジスタ50がオフに切り替えられ、かつトランジスタ40が自動的にオフに切り替わるので、メモリセル42〜48の電位は浮遊状態になる。従って、高いプログラム電圧Vpgm(例えば、18ボルト)がワードラインWL2に印加されると共に中間電圧Vpass(例えば、10ボルト)が残りのワードラインに印加されると、メモリセル42〜48のチャネル電位は、約0.6の結合比を取る場合、容量結合によって最初の事前充電レベルの2ボルトから8ボルトなどの値にブートストラップされたり、または昇圧される。従って、18ボルトなどの高い電圧がメモリセル44のコントロールゲートに印加されても、そのような高い電圧とチャネル電位との間の電位差は、メモリセル44のフローティングゲートに至る酸化物を通った電子トンネリングを起こすには適切ではなく、それによってプログラム障害が防止される。

【0014】

NANDストリングは、一般には(しかし常時ではないが)ソース側からドレイン側に、例えばメモリセル28からメモリセル22にプログラムされる。プログラミング処理がNANDの最後の(または最後に近い)メモリセルをプログラムする準備ができたときに、抑制されているストリング(例えば、ストリング13)上の全てのまたは大部分の事前にプログラムされたセルがプログラムされたならば、その際に事前にプログラムされたセルのフローティングゲートに負の電荷が存在する。このような負の電荷がフローティングゲート上に存在するので、事前充電は完全には行われず、結果的にNANDストリングの下のチャネル領域の最初の電位は低くなり、引き続いて起きるこのチャネル領域の自己昇圧も不十分なものとなる。従って、選択されなかったNANDストリングのチャネルにおける昇圧された電位は十分には高くならず、最後の23本のワードライン上に依然としてプログラム障害が存在する。例えば、プログラム電圧がWL3に印加されるときに、抑制されているストリング上のセル48、46、44がプログラムされていたならば、その際にそれらメモリセル44、46、48の各々はそのフローティングゲート上に負の電荷を有し、それが自己昇圧の昇圧レベルを制限し、多分にセル42上にプログラム障害を起こすことになる。

【0015】

前述したような問題点を鑑み、改善策として、T.S.ユングらによる「大規模記憶用途の3.3V・128MbのマルチレベルNANDフラッシュメモリ」,ISSCC96,セッション2,フラッシュメモリ,論文TP2.1,IEEE,第32ページ (T. S. Jung et al.,“A 3.3V 128Mb Multi-Level NAND Flash Memory for Storage Applications", ISSCC 96, Session 2, Flash Memory, Paper TP 2.1, IEEE, pp. 32)(非特許文献3)においてローカルな自己昇圧(「LSB」)技術を提案した。

【0016】

LSB方式では、高いプログラム電圧をワードラインWL2に印加するときに、抑制されているストリング上のメモリセル44に関してプログラム障害を低減したり、または防ぐために、メモリセル42、46がオフに切り替えられるように0ボルトがワードラインWL1、WL3に印加される。その場合、メモリセル44におけるチャネル電位は、メモリセル42、46、48のチャネル領域における自己昇圧によって影響を受けないか、または少なくとも影響を受けにくくなる。従って、メモリセル44のチャネル領域のチャネル電位は、高いプログラム電圧Vpgmによって、メモリセル44のチャネル領域が残りのメモリセル42、46、48の自己昇圧の影響を受けるときに達成される電圧レベルよりも高い電圧レベルに自己昇圧され得る。これによって、メモリセル24がプログラムされているときのプログラム障害を防ぐ。自己昇圧とローカルな自己昇圧についてのより詳細な説明については、米国特許第6,107,658号(特許文献8)の特にコラム6〜10の記載を参照されたい。

【0017】

ローカルな自己昇圧の代りとして提案された1つの別の技術は、田中らに付与された米国特許第6,525,964号(特許文献9)に説明され、消去された領域の自己昇圧(「EASB」)として知られている。EASBは、次の点でLSBとは異なっている。即ち、LSBのようにセルのプログラム障害を防ぐために選択されなかったセルの各側の両メモリセルもオフに切り替えるのではなく、EASBは選択されなかったセルのソース側のメモリセルのみをオフに切り替える点で異なっている。例えば、メモリセル24がプログラムされている場合に、セル44におけるプログラム障害を防ぐために、メモリセル42はオフにせず、メモリセル46のみがオフに切り替えられている。

【0018】

LSBおよびEASBは多くの用途にとって有利ではあるが、これらの方式が今の形式で使用されると、特に次世代のデバイスにおけるメモリセルの寸法が引き続き縮小したり、または小さくなると、依然としてやはり或る種の問題が発生する。従って、そのような問題が解消される改良形自己昇圧方式を提供することが望まれている。

【先行技術文献】

【特許文献】

【0019】

【特許文献1】米国特許第5,570,315号

【特許文献2】米国特許第5,774,397号

【特許文献3】米国特許第6,046,935号

【特許文献4】米国特許第6,456,528号

【特許文献5】米国特許第6,522,580号

【特許文献6】米国特許第5,043,940号

【特許文献7】米国特許第5,172,338号

【特許文献8】米国特許第6,107,658号

【特許文献9】米国特許第6,525,964号

【特許文献10】米国特許第5,887,145号

【特許文献11】米国公開特許出願第2003/0147278号

【非特許文献】

【0020】

【非特許文献1】野崎隆明らによる論文「半導体ディスクに適用するMONOSメモリセルを有した1−MbのEEPROM」,固体回路のIEEEジャーナル,第26巻,第4号,1991年4月,第497頁〜501頁

【非特許文献2】K.D.スーらによる「インクリメンタル・ステップ・パルスプログラミング方式を有する3.3ボルト、32MbのNANDフラッシュメモリ」,固体回路のジャーナル,第30巻,第11号,1995年11月,第1149〜1155頁

【非特許文献3】T.S.ユングらによる「大規模記憶用途の3.3V・128MbのマルチレベルNANDフラッシュメモリ」,ISSCC96,セッション2,フラッシュメモリ,論文TP2.1,IEEE,第32ページ

【発明の概要】

【0021】

図2Bおよび図3を参照すると、N+の拡散された領域49は、ソース側選択トランジスタ50のドレインとして、また隣のメモリセルまたはトランジスタ48のソースとしての働きをする。用語「メモリセル」、「電荷記憶トランジスタ」および「トランジスタ」は、図2Bおよび図3に示されているもののようなフラッシュメモリのストリングの要素を参照すると、本願明細書では互いに交換可能に使用される。トランジスタ22、24または26のうちのいずれか1つについての前述した自己昇圧方式のいずれか1つにおけるプログラミング中に、0ボルトがトランジスタ50のゲートに印加され、また大部分の例では、中間電圧Vpass(例えば、10ボルト)がトランジスタ48のコントロールゲートに印加される。かくして、トランジスタ48のチャネル領域は、0.6の結合比を取る場合(チャネル領域は、昇圧前に2ボルトに事前充電されると仮定する場合)、8ボルトなどの値に昇圧される。トランジスタ48のこのような昇圧されたチャネル電圧は、多分に帯域から帯域へのトンネリングによってトランジスタ50のドレイン領域49のブレークダウンを起こす。このようなブレークダウンは、チャネル電位が下がるように、同じNANDストリングのトランジスタ48の昇圧されたチャネル領域と他のメモリセルのチャネル領域とを放電させることになってプログラム障害を起こし得る。生じ得るもう1つ別のメカニズムは、ブレークダウンによって発生される電子は、トランジスタ48の下方の昇圧されたチャネル領域に向かって加速されるものであり、このことで、しきい値電圧シフトを起こしながら引き続いてトランジスタ48のフローティングゲートに注入される所謂ホットエレクトロンをもたらす。このしきい値電圧シフトは、トランジスタ48を1つのプログラムされた状態から別のプログラムされた状態へなど、1つの充電状態からもう1つの別の状態へ変化させ得るものであり、それは望ましくない。状態のそのような変化は、トランジスタ50のドレイン領域49のブレークダウンを防ぐことを目的とした適切なバイアス状態を使用することによって防止することができる。

【0022】

充電状態の望ましくない変化は、マルチレベルのしきい値電圧形メモリにおいても、また2進レベルのしきい値電圧形メモリにおいても適切なバイアス条件を使用することによって防止され得る。適切なバイアス条件を適用することで、ソース側選択トランジスタのドレイン側における帯域から帯域へのトンネリングなどのブレークダウンメカニズムは、次の程度まで、即ちそのメカニズムがソース側選択トランジスタの隣のトランジスタの所望の電荷記憶状態が別の電荷状態に変化することにならない程度まで減衰されるようにする効果が享受でき、幾つかの場合には、そのようなメカニズムは完全に抑制される。

【0023】

一実施形態では、ドレイン領域におけるソース側選択トランジスタのブレークダウンは、ソース側選択トランジスタの隣のストリングのトランジスタ(目標トランジスタ)に印加される電圧を自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に下げてプログラム障害を減らしたり、または防止することで防止される。そのような実施形態での一実装例において、目標トランジスタに印加される電圧は1から3ボルトの範囲となり得る。もう1つ別の実装例では、プログラム障害を防止するために目標トランジスタとは別のトランジスタのうちの幾つかに結合される昇圧電圧は、目標トランジスタに結合された電圧よりも少なくとも50%だけさらに高くなり得る。

【0024】

ドレイン側の選択ゲートは一般に、昇圧中に一般的に0ボルトのゲート電圧になっているソース側選択ゲートよりも、昇圧中に1.5〜2.5ボルトの範囲のようなより高いゲート電圧になっているとは言え、図2Bにおけるドレイン側選択トランジスタ40のトランジスタ領域51などのドレイン側選択トランジスタの隣のストリングのトランジスタのドレイン領域でも前述したようなブレークダウンが起きる。ソース領域におけるドレイン側選択トランジスタのブレークダウンは、ドレイン側選択トランジスタの隣のストリングのトランジスタ(目標トランジスタ)に印加される電圧を自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に下げてプログラム障害を減らしたり、または防止することで防止される。そのような実施形態の一実装例において、目標トランジスタに印加される電圧は1から3ボルトの範囲となり得る。もう1つ別の実装例では、プログラム障害を防止するために目標トランジスタとは別のトランジスタのうちの幾つかに結合される昇圧電圧は、目標トランジスタに結合される電圧よりも少なくとも50%だけさらに高くなり得る。

【0025】

前述したソース側選択トランジスタのドレイン領域のブレークダウンおよびドレイン側選択トランジスタのソース領域のブレークダウンは、電荷記憶トランジスタのストリングにおけるトランジスタのうちのいずれかの書き込み中またはプログラミング中に起きうるものでる。従って、プログラム障害を減らすために、前述した方式は、ストリングにおける2つ以上のトランジスタを逐次プログラムしたり、または書き込んでいる間に、或いは実のところソース側またはドレイン側の選択トランジスタに直近したトランジスタのプログラミング中を除外してストリングの全てのトランジスタを逐次プログラムしたり、または書き込みしている間に適用される。

【0026】

同じ趣旨で前述した方式は、必要ならば、本願明細書において説明した自己昇圧と事前充電方式のうちのいずれか1つ以上と、また本願明細書において説明したものとは異なった事前充電方式などの他の自己昇圧方式と関連して適用される。

【0027】

次世代のデバイスのメモリセルの寸法がより小さくなると、EASB方式におけるメモリセルのチャネル長さは余りにも短くなって、選択されたワードラインに結合されたトランジスタの各々のドレイン側およびソース側で別々に昇圧される2つのチャネル領域を電気的に絶縁することができなくなる。その結果、昇圧されたチャネル電圧は低下されてプログラム障害をもたらすことになる。出願人は、選択されたワードラインに結合されたトランジスタのソース側およびその隣で2本以上のワードラインまたはコントロールゲートに、好ましくは互いに隣接したもの同士にバイアスを掛けることで2つの昇圧された領域間の絶縁を改善し、絶縁メモリセルまたはトランジスタのチャネル長さを効果的に長くし、それによって2つの昇圧された領域間の漏電を減らすように提案している。好ましくは、バイアスを掛ける条件は、帯域から帯域へのトンネリングも漏電の低減と共に同時に低減されるようにするものである。

【0028】

前述した改善されたEASB方式では、絶縁は選択されたワードラインに結合されたトランジスタのソース側でのみ起きるので、少なくとも幾つかの実施形態ではそのようなトランジスタのドレイン側でセルまたはトランジスタに結合された昇圧電圧を同様に下げる必要が無く、その結果2本以上のワードラインまたはコントロールゲートに結合された電圧レベルは、そのようなトランジスタのドレイン側でセルまたはトランジスタに結合された電圧レベルよりも低くなる。前述したように、前述した改善されたEASB方式は、130または100ナノメータよりも小さい寸法のように小さなセル寸法を有するメモリアレイに特に有用である。

【0029】

次世代のデバイスのメモリセルの寸法がより小さくなると、LSB方式におけるメモリセルのチャネル長さも余りにも短くなり、選択されたワードラインに結合されて選択されなかったトランジスタのチャネル領域と、そのようなトランジスタのドレイン側とソース側における昇圧されたチャネル領域とを電気的に絶縁させることができない。その結果、昇圧されたチャネル電圧は低下されてプログラム障害をもたらすことになる。出願人は、選択されたワードラインに結合されたトランジスタのソース側とドレイン側の両方でかつその隣で2本以上のワードラインまたはコントロールゲートに、好ましくは互いに隣接したもの同士にバイアスを掛けることで、メモリセルの短いチャネル長さによって起こされる漏電を低減して、絶縁メモリセルまたはトランジスタのチャネル長さを効果的に長くするように提案している。換言すれば、電圧レベルは2組のトランジスタに結合されて、選択されたワードラインに結合された少なくとも1つの選択されなかったトランジスタのチャネル領域を選択されなかったトランジスタと同じストリングにおける隣のチャネル領域から電気的に絶縁するものであり、その場合、各組は少なくとも2つのトランジスタを有していて、また2組は選択されたワードラインに結合された選択されなかったトランジスタの両側に配置されている。好ましくは、その電圧レベルは、この電圧レベルのうちの少なくとも1つに結合されて選択されたストリングにおいてより低い電圧しきい値の取りうる充電された状態のうちの1つ(例えば、プログラムされていないトランジスタのしきい値電圧のような負のしきい値電圧を有するもの)を有するトランジスタが、オンに切り替えられるようなものとなっているが、この電圧レベルのうちの少なくとも1つに結合されて選択されたストリングにおいてより高い電圧しきい値の取りうる充電された状態のうちの1つ(例えば、プログラムされるトランジスタのしきい値電圧のような正のしきい値電圧を有するもの)を有するトランジスタが、オフに切り替えられるようなものとなっている。好ましくは、その電圧レベルは、メモリセルの短いチャネル長さによる漏電と、帯域から帯域へのトンネリングで誘発されるブレークダウンの両方が同時に減らされるようなものとなっている。

【0030】

幾つかの応用と設計のために、LSB方式における選択されたワードラインのドレイン側での完全な電気的絶縁は必要が無いか、または望ましいものではない。そのような場合、改造されたLSB方式が実行され、そこで選択されたワードラインのドレイン側でセルまたはトランジスタに結合された昇圧電圧は、これらのトランジスタが完全にオフに切り替えさせない値となっているが、選択されたワードラインのドレイン側には或る電気的に絶縁が与えられる。

【0031】

2つの昇圧された領域間で漏電を減らすことは、Vpassの低い電圧に対して重要であり、また絶縁トランジスタとしての働きをするメモリセルのしきい値電圧が消去された状態になっている場合に重要である。これらのトランジスタが消去された状態になっている場合に絶縁トランジスタをオフに切り換えることができるようにするために、ソース側において或る一定の正の昇圧された電圧が必要とされる。この正の電圧は、Vpassの電圧が低い電圧(例えば、0ボルト)から高い電圧(例えば、5〜10ボルトの範囲)に上げられる昇圧処理の開始時に形成される。Vpassの低い値では、チャネル領域はそれほど高くない電圧へと昇圧され、その結果、絶縁トランジスタは後でオフに切り変わり、かくしてより多くの電荷がより高く昇圧されたドレイン領域から転送されるようにし、それによってドレイン側の領域の昇圧された電圧を低下させる。絶縁トランジスタとしての働きをする2つ以上のメモリセルを有することで、チャネル長さを効果的に延ばし、それによってそれら絶縁トランジスタの絶縁特性を高める。さらに、2つ以上のメモリセルが絶縁トランジスタとして使用されると、それら2つ以上のメモリセルが消去された状態になっている確率は、ただ1つのメモリセルが絶縁トランジスタとして働く確率よりも小さい。4つのレベルが記憶されているMLCメモリセルの場合、両方の絶縁メモリセルが消去された状態になっている確率は、ほんの6.25%にすぎず、一方でただ1つの絶縁メモリセルの場合は、その確率は25%になっている。

【0032】

プログラム障害を起こし得るもうひとつ別のメカニズムは、特にVpassの比較的高い値で起きる。そのような場合、ドレイン側領域は、選択されたワードラインの隣に配置されている絶縁トランジスタのドレイン側でブレークダウンを起こす高い電圧に昇圧される。そのようなブレークダウンの推定することができるメカニズムは、絶縁メモリセルのドレイン領域の縁でのまたはその縁の近くでの帯域から帯域へのトンネリングである。他のブレークダウンメカニズムもある。ブレークダウンによって、所謂「ホットエレクトロン」となる電子が発生され、その理由はこれらの電子が選択されたワードラインの近くに存在している強力な電界によって加速されるからである。これらのホットエレクトロンは、選択されたワードライン上のメモリセルのフローティングゲートまたは隣接しているメモリセルのフローティングゲートに注入され、かくしてそれらメモリセルのしきい値電圧を変えると共に多分にメモリセルの電荷記憶状態における変化を起こす。絶縁メモリセルに対して適切なバイアス電圧を選択することで、絶縁トランジスタのドレイン側領域でのブレークダウンは防止されるかまたは少なくとも大幅に抑制される。ブレークダウンのもう1つ別の取りうる副次的作用は、ドレイン側の昇圧された領域がそのブレークダウンによって部分的に放電されることである。そのようなブレークダウンはホール/電子の対を発生させるので、ドレイン側の昇圧されたチャネル領域へ流れる電子はその領域の昇圧された電位を下げることになり、それによって多分にプログラム障害を増大させることになる。

【図面の簡単な説明】

【0033】

【図1】本発明のメモリセルアレイおよび操作改善が実施される種類のメモリシステムのブロック図である。

【図2A】従来技術のNANDアレイの平面図である。

【図2B】A−Aに沿って切り取られた図2Aの従来技術のNANDアレイの断面図である。

【図3A】図2AのNANDストリングのうちの3つを描いた回路図である。

【図3B】各アレイが1組の共通のワードラインによって制御された状態の幾つかのNANDアレイを描いた回路図である。

【図4A】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4B】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4C】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4D】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図5A】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5B】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5C】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5D】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6A】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6B】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6C】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6D】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6E】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7A】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7B】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7C】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7D】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7E】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8A】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8B】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8C】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8D】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8E】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9A】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9B】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9C】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9D】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9E】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【発明を実施するための形態】

【0034】

説明を簡略化するために、本願では、同じ構成要素は同じ番号が付されている。

【0035】

メモリシステム

本発明の色々な態様が実施される例示のメモリシステムを図1のブロック図で示す。マトリックス上に配列された複数のメモリセルMを有するメモリセルアレイ1は、列制御回路2、行制御回路3、c−ソース制御回路4およびc−p−ウェル制御回路5によって制御される。メモリセルアレイ1は、この例では背景技術の欄で既に説明し、本願明細書において参照により援用されているNAND形となっている。制御回路2は、メモリセル(M)に記憶されたデータを読み出したり、プログラミング動作中にメモリセル(M)の状態を決めたり、またプログラミングを促進したり、またはプログラミングを禁止するためにビットライン(BL)の電位レベルを制御するためにメモリセルアレイ1のビットライン(BL)に接続されている。行制御回路3は、ワードライン(WL)のうちの1つを選択したり、読み出し電圧を印加したり、列制御回路2によって制御されるビットライン電位レベルと結合されたプログラム電圧を印加したり、またメモリセル(M)が上に形成されているp形領域(セルP−ウェル)の電圧と結合された消去電圧を印加するためにワードライン(WL)に接続されている。c−ソース制御回路4は、メモリセル(M)に接続された共通のソースラインを制御する。c−p−ウェル制御回路5は、セルのP−ウェル電圧を制御する。

【0036】

メモリセル(M)に記憶されたデータは、列制御回路2によって読み出され、I/Oラインとデータ入出力バッファ6とを経由して外部のI/Oラインに出力される。メモリセルに記憶されるプログラミングデータは、外部のI/Oラインを経由してデータ入出力バッファ6に入力されると共に列制御回路2に転送される。外部のI/Oラインはコントローラ9に接続されている。コントローラ9は、色々な形のレジスタと揮発性ランダムアクセスメモリ(RAM)10を含む他のメモリとを有している。

【0037】

フラッシュメモリデバイスを制御するコマンドデータは、コントローラ9に接続した外部の制御ラインに接続されたコマンド回路7に入力される。コマンドデータは、フラッシュメモリにどのような操作が必要とされているかについて知らせる。入力されたコマンドは、列制御回路2、行制御回路3、c−ソース制御回路4、c−p−ウェル制御回路5およびデータ入出力バッファ6を制御する状態マシン8に転送される。状態マシン8は、READY/BUSYまたはPASS/FAILなどのフラッシュメモリの状態データを出力する。

【0038】

コントローラ9は、パーソナルコンピュータ、デジタルカメラまたは携帯用移動端末(PDA)などのホストシステムと接続されたり、または接続可能となっている。メモリアレイ1にデータを記憶したり、またはデータを読み出すなどのコマンドを開始し、そのようなデータをそれぞれ提供したり、または受け取るのがホストの役目である。コントローラは、そのようなコマンドをコマンド回路7によって解釈されたり、実行されるコマンド信号に変換する。コントローラはさらに、メモリアレイに書き込まれたり、または読み出されるユーザデータのためのバッファメモリを一般に収容している。一般的なメモリシステムは、コントローラ9を含む1つの集積回路チップ11Aと、メモリアレイ、関連した制御回路、入出力回路および状態マシン回路を各々収容した1つ以上の集積回路チップ11Bとを有している。メモリアレイとシステムのコントローラ回路とを共に1つ以上の集積回路チップ上に統合することも可能である。

【0039】

図1のメモリシステムは、ホストシステムの一部として組み込まれたり、またはホストシステムの嵌合ソケット内に取り外し可能に挿入されるメモリカードに包含されたりする。そのようなカードは、全体のメモリシステムを含んだり、または関連した周辺回路と共にコントローラおよびメモリアレイが別のカードに設けられたりする。幾つかのカードの実装例については、例えばその全体が本願明細書において参照により明確に援用されている米国特許第5,887,145号(特許文献10)に説明されている。

【0040】

図4A〜4Dは、本発明の或る態様を例示するために役立つ従来の自己昇圧プログラミング方式における4つの異なった連続したタイムインターバル中におけるストリングのバイアス電圧を示すNANDストリング100の断面図である。前述したように、NANDストリングは、一般的にソース側からドレイン側に、よって図4A〜4DではWL0〜WL4へ逐次プログラムされるようになっていて、プログラムされる第1のセルはメモリセル122となり、次のものはメモリセル124となるなどメモリセルまたはトランジスタ130まで逐次プログラムされるようになっている。NANDストリング100は、図4Aに示されている5つのセル122〜130よりも多くのセルを収容し、一般には16または32のメモリセルが1本のNANDストリングに直列状に接続されている。NANDストリング100は、他の実装例も可能ではあるが、図2Bを参照すると上の方に示されている形で実施される。NANDストリング100は、前述した方式で制御されかつ動作される。

【0041】

図4Aは、ストリングのセル122がプログラムされているときにNANDストリング100に印加されるバイアス電圧を示す。図4Aに示されているように、0ボルトがソース側選択トランジスタ120のゲートのSGSに印加される。さらに、0ボルトかまたはそれより幾分高い電圧のVsがソースラインに印加される。プログラミング中に0ボルトよりも高い電圧をソースラインに印加することで選択トランジスタ120の絶縁特性を改善する。図4Aに示されているように、高いプログラム電圧VPGM がワードラインWL0に印加されると共に中間の電圧VPASSが残りのワードラインに印加される。高いVPGM は、チャネルからの電子を酸化物を通ってトランジスタ122のフローティングゲートFG0へトンネリングさせる。前述したように、そのような選択されなかったトランジスタのチャネル電位を昇圧することによってワードラインWL0によりアドレス指定された選択されなかったセルまたはトランジスタにおけるプログラム障害を減らしたり、または防止するために、中間電圧VPASSが印加される。これは従来の自己昇圧方式である。プログラム電圧VPGM は、トランジスタ122のしきい値電圧を検査するために読み出しサイクルが各増分の後に続くような増大インクリメントで印加される。これらのステップは図1のメモリシステムによって実行される。プログラミングがトランジスタ122のしきい値電圧を目標しきい値に到達させた後に、メモリシステムは次いで図4Bに示されているような次のプログラミングタイムインターバルでトランジスタ124をプログラムするように移行し続ける。かくして、図4Bに示されているように、高い書き込み電圧が代わりにワードラインWL1に印加されると共に中間電圧VPASSが残りのワードラインに印加されて、トランジスタ122をプログラムするために前述したのと同じ方式でトランジスタ124をプログラムする。トランジスタ124がプログラムされた後は、次に高い書き込み電圧がワードラインWL2に印加されると共に中間電圧が残りのワードラインに印加される図4Cに示されているようなトランジスタ126のプログラミングのために次のプログラミングタイムインターバル中にメモリシステムは進行する。これが完了されると、このシステムでは、次のプログラミングタイムインターバルにおいて図4Dに示されているようなトランジスタ128のプログラミングのために、また次いで引き続いたプログラミングタイムインターバル中にトランジスタ130のプログラミングのために進行する。この処理は、ソース側選択トランジスタに最も近いトランジスタから開始し、次いでストリング100の全てのトランジスタがプログラムされてしまうまで、トランジスタがソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続して反復される。

【0042】

図2Bを参照して前に説明したように、トランジスタ122の昇圧されたチャネル電圧は、図4B〜4Dに示されている4つのプログラミングタイムインターバルのうちの3つの間隔でソース側選択トランジスタ120のドレイン領域のブレークダウンを起こし、その結果フローティングゲートFG0が既にプログラムされてしまった後に、フローティングゲートFG0内に注入されるホットエレクトロンが発生される。この電子の注入でFG0のしきい値電圧をシフトさせることになり、それは所望の電荷記憶状態から別の間違った電荷記憶状態へのFG0の切り替えをもたらすことになる。同じことがメモリアレイにおける他のストリングに対しても言うことができる。図2Bを参照して前に説明したように、トランジスタ122における昇圧されたチャネル電圧は、図4A〜4Dに示されている4つのプログラミングタイムインターバル中にソース側選択トランジスタ120のドレイン領域のブレークダウンを起こす。結果的に、NANDストリングのチャネル領域における低下された昇圧電位が理由でプログラム障害が起きる。この種のプログラム障害は、VPGM がワードラインに印加されるときのようにワードラインがプログラミングのために選択されるときにいずれかのワードラインで起きる。前にも述べたプログラム障害のもう1つ別の可能性は、ソース側選択トランジスタ120のドレインの近くで、またはメモリセル122のチャネル領域で発生され、引き続いてフローティングゲートFG0に注入されるホットエレクトロンによるものである。ホットエレクトロンはソース側選択トランジスタ120のドレインの近くまたはメモリセル122のチャネル領域の小さな領域に極限されかつ限定されるので、後者のメカニズムはWL0上のメモリセルにただ影響するだけのようである。このようなホットエレクトロンの注入は、FG0のしきい値電圧をシフトさせることになり、それは所望の電荷記憶状態から別の間違った電荷記憶状態へのFG0の切り替えをもたらすことになる。同じことはメモリアレイにおける他のストリングに対しても言うことができる。

【0043】

セルの全てがプログラムされるときに前述したブレークダウン現象が起き続けるので、続いたワードラインがプログラムされるに従ってセル122のしきい値電圧分布が徐々に悪化することが分かった。全てのワードラインがプログラムされた後に、しきい値電圧分布がシフトアップして大幅に拡がったことが見つかった。幾つかのフラッシュメモリでは、電荷レベルの電圧範囲の窓が4つの状態に分割され、その場合上昇された状態「11」は負のしきい値電圧範囲を有し、残りの3つの状態「10」、「00」、「01」は昇順で正のしきい値電圧分布を有する。従来の自己昇圧方式が適用される場合、メモリセルの全てがプログラムされた後には、「10」のしきい値電圧分布がより高い値にシフトされて、「10」が「00」として読み出されるように大幅に拡がったことが分かる。「00」のしきい値電圧分布も幾分影響を受けたのも分かる。WL0に印加される電圧を低下させることで、「10」の電荷状態のアップシフトと拡張とが全て共に大きく低減されたり、または削除されることになることが予想される。

【0044】

本発明の一態様は、かくしてソース側選択トランジスタのドレイン領域のそのようなブレークダウンがワードラインに電位を印加することによって全て回避されたり防止されたりするという認識に基づき、その結果前述したプログラム障害のメカニズムが抑制され、また昇圧がFG0における電荷状態を変えるようなことがない。一実装例では、このことは、従来の自己昇圧中に通常印加されるVPASSのための5〜10ボルトの中間電圧の代わりに1〜3ボルトの範囲の電圧などのVPASSより低い値にWL0に供給される電圧を下げることにより達成される。このことを図5A〜5Dに示す。

【0045】

図5A〜5Dは、本発明の一態様を例示するための従来の自己昇圧中に印加されるものとは異なったバイアス電圧を伴ったNANDストリング100の断面図である。セル122がプログラムされているとき、印加されるバイアス電圧は従来の自己昇圧方式で採用されたものと同じである。しかし、セル124、126、128がプログラムされる後続のプログラミングタイムインターバル中には、一般に8〜10ボルトの範囲で従来のVPASSをワードラインWL0に印加する代わりに、より低い電圧VLOW が代わりにワードラインWL0に印加される。前述したように、一実装例では、VLOW は1〜3ボルトの範囲かまたはそれらのボルトとすることができる。そのような低い電圧は、ワードラインWL0の下のセルに対するプログラミングタイムインターバルの間隔中を除き、メモリアレイにおけるセルの全てをプログラムするためのプログラミングタイムインターバルのうちの少なくとも幾つかの間隔中に、好ましくは全ての間隔中にワードラインWL0に印加されることになる。低い電圧をWL0に印加することによって、WL1、WL2などの下の昇圧されたチャネル電位はソース側選択トランジスタのドレインに完全には転送され得ない。その結果、ソース側選択トランジスタのドレイン電圧はより低くなっていて、ブレークダウンは防止されたり、または大幅に減らされる。例えば、図5Bの場合、全てのメモリセル122〜130が約−2ボルトの消去しきい値電圧で消去された状態になっていると仮定すると、メモリセル124〜130の下のチャネル領域は例えば8ボルトに(VPASSの値に応じて)昇圧されることになる。さらに、1.5ボルトの電圧VLOW がメモリセル122の−2ボルトのしきい値電圧と組み合わせてWL0に印加されると仮定すると、このことはメモリセル122が導電状態になっていることを意味している。その結果、メモリセル124〜130のチャネル領域の昇圧された電荷の一部分はメモリセル122のソース側に転送され、その結果ソース側の電位は上昇することになる。しかし、メモリセル122のソース側電位が約3.5ボルトの値(ゲート電圧−しきい値電圧)に到達した後はその上昇は止まる。その結果、ソース側選択トランジスタのドレイン電位は、3.5ボルトの値までただ昇圧されるに過ぎず、一方で従来の場合にはその電位は8ボルトまで昇圧されていた。ドレイン電圧が非常に顕著に低下することで選択トランジスタのドレインにおけるブレークダウンを防止したり、または少なくとも大幅に減らすことは明らかである。そのような方式によって、セル122の電荷状態がトランジスタ122〜130のチャネル領域に印加される自己昇圧電圧によっては変化しないような程度まで帯域から帯域へのトンネリングは低減される。

【0046】

ドレイン側選択ゲートが一般に昇圧中に0ボルトのゲート電圧となっているソース側選択ゲートよりもより高い昇圧中の1.5〜2.5ボルトなどのゲート電圧を有していても、前述したようなブレークダウンは、図2Bのドレイン側選択トランジスタ40のソース領域51などの、ドレイン側選択トランジスタの隣のストリングのトランジスタのソース領域でも起きる。ソース領域でのドレイン側選択トランジスタのブレークダウンは、ドレイン側選択トランジスタの隣のストリングのトランジスタに印加される電圧を、プログラム障害を減らしたり、または防止するために自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に低下することで防止される。かくして、図5A〜5Dは、このことを示すために若干改変される必要がある。ソース側選択トランジスタになっている代わりに、トランジスタ120は、代わりにソース側選択トランジスタよりも高い昇圧中の1.5〜2.5ボルトの範囲などのゲート電圧を有するドレイン側選択トランジスタになっている。ワードラインのラベル付けの解釈も、WL0がドレイン側選択トランジスタ120に1番近いワードラインとなるように見直される。プログラミングシーケンスは、次に、ドレイン側選択トランジスタ120に最も近いトランジスタ122に到達するまでストリングのドレイン側に向かってソース側選択トランジスタに最も近いトランジスタからの開始へと進む。かくして、図5D〜図5Aは、そのような順番でそのようなプログラミングシーケンスの最後の数サイクルを示している。トランジスタ122(ドレイン側選択トランジスタの次のトランジスタ)に結合されたワードラインWL0に0ボルトを印加する代わりに、低い正の電圧VLOW が印加される。一実装例では、トランジスタ122に印加される電圧VLOW は、1〜3ボルトの範囲とすることができる。もう1つ別の実装例では、プログラム障害を防止するためにトランジスタ122とは別の幾つかのトランジスタに結合される昇圧電圧は、トランジスタ122に結合される電圧(VLOW )よりも少なくとも50%だけさらに高くすることができる。ドレイン側および/またはソース側選択トランジスタの隣のトランジスタのソースおよび/またはドレイン領域のブレークダウンに関連した前述したような特徴は、限定はされないがSB、LSBおよびEASBのいずれかの形態を含んだあらゆる自己昇圧方式との関連で使用される。

【0047】

図5A〜5Dに示されている処理は、好ましくはソース側選択トランジスタに最も近いトランジスタから始まり、次いでストリング100におけるトランジスタの全てがプログラムされてしまうまで、トランジスタがソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続的に反復される。

【0048】

図6A〜6Eは、ストリングにおけるそれぞれのセルの従来のEASBプログラミングを例示するためのNANDストリング100の断面図である。前述したように、EASBシステムは、下方のワードラインと上方のワードラインの2つの昇圧されたチャネル領域がワードライン上に0ボルトを有するメモリセルによって隔離されるように、プログラミング中に選択されたワードラインのソース側のワードラインに0ボルトを印加する。このことにより、そのようなメモリセルはオフに切り替えられ、それによって2つの昇圧されるチャネル領域を隔離する。2つのチャネル領域を分離した結果、ドレイン側の昇圧効率が改善される。ソース側のメモリセルの幾つかがプログラムされた状態にあり、かつそれによってより高いしきい値電圧を有するので、ソース側のチャネル領域は、昇圧される度合いが少ない。選択されたワードラインのドレイン側のチャネル領域は、ドレイン側の全てのセルが負のしきい値電圧で依然として消去された状態になっているので、ビットラインを介して(ほぼ)完全に事前に充電され、より効率的に昇圧される。図6Bを参照して、例えばセル124がプログラムされている場合、0ボルトがWL0に印加される。セル126が図6Cに示されているようにプログラムされている場合、0ボルトがWL1に印加される。セル128がプログラムされている場合、0ボルトがWL2に印加され、またセル130がプログラムされている場合、0ボルトがストリング100のWL3に印加される。

【0049】

従来のEASBの不利な点は、ブレークダウンに関連した漏電(および/または帯域から帯域へのトンネリング)が接地されたワードラインの下のセルのドレイン領域で起きる点である。このブレークダウンは、選択されたワードライン上のセルのフローティングゲート内へのホットエレクトロンの注入を、またはSBメカニズムに対して説明したのと同様に昇圧されたチャネル電位の低下を間接的に起こし、それによって多分にプログラム障害を起こすことになる。さらに、次世代のデバイスのメモリセルの寸法がより小さくなると、オフに切り替えられたメモリセルのチャネル長さも短くなり、2つの別々に昇圧されるチャネル領域を選択されたワードラインのドレイン側とソース側で電気的に絶縁することができるようになる。かくして本発明のもう1つ別の態様は、2本以上のワードライン(好ましくは互いに隣接しあっている)または選択されたトランジスタまたはワードラインのソース側におけるコントロールゲートを適切にバイアスをかけて絶縁メモリセルのチャネル長さを効果的に長くすることによって2つの昇圧された領域間の帯域から帯域へのトンネリングおよび/または漏電が同時に低減されるという認識に基づいている。改良されたEASB方式における絶縁は選択されたメモリセルまたはワードラインのソース側でのみ起きるので、一般的に選択されたトランジスタのドレイン側のセルに結合された電圧を同様に下げる必要はない。本発明のこの態様を図7A〜7Eに示す。5つのフローティングゲートのメモリセルが図7A〜7Eの各ストリングに示されているが、個々のストリングは一般に16または32またはそれ以上のメモリセルの電荷記憶素子を有している。

【0050】

図7A〜7Eは、本発明のこの態様を例示するために改良されたEASB方式におけるストリングに印加されるバイアス電圧を示すNANDストリング100の断面図である。図7A〜7Eの改造された方式は、選択されたワードラインのソース側の2本のワードライン(好ましくは互いに隣接しあっている)が従来のEASB方式におけるようにただ1本のワードラインの代わりに接地されている点で図6A〜6Eのものとは異なっている。かくして図7C〜7Eでは、例えばセル126、128、130がシーケンシャルなプログラミングタイムインターバルでプログラムされている場合、選択されるワードラインに直近した2本のソース側ワードラインは接地されている。かくして、図7Cにおいて、セル126がプログラムされている場合、0ボルトがWL0とWL1に印加される。図7Dにおいて、ワードラインWL3がセル128をプログラムするために選択される場合、0ボルトがWL1とWL2に印加される。図7Eにおいて、セル130がプログラムされていてかつWL4が選択される場合、0ボルトがWL2とWL3に印加される。

【0051】

0ボルトを2本のソース側の隣接したワードラインに印加することは、絶縁領域のチャネル長さを長くする作用を有している。絶縁領域のチャネル長さを2つの隣接したセルによって設定された長さまで長くすることで、選択されるセルのドレイン側チャネル領域の昇圧が改善され、それによってプログラム障害も低減する。必要ならば、0ボルトが2本より多い隣接したワードラインに印加されて、昇圧されたチャネル領域間の絶縁領域の長さをさらに長くする。必要ならば、接地されたワードラインは、選択されたワードラインから1本以上のワードラインによって分離される。2本以上のワードラインを0ボルトにバイアスを掛けることで得られるもう1つ別の利点は、ソース側とドレイン側の昇圧されたチャネル領域間での漏電に対する最悪の状況がより起きそうもない点である。最悪の状況は、0ボルトのワードラインの下のセルが消去された負のしきい値電圧状態になっている場合に起き、その状況で、メモリセルが一部分の昇圧動作中に(負のしきい値電圧の故に)電気を通しているので、昇圧されたドレイン側チャネル電荷の幾分かは依然として漏れ出る。2本のワードラインが0ボルトに接続されている場合、両方のワードラインの下で、消去された状態のメモリセルが存在している確率は、ただ1本のワードラインが0ボルトにバイアスが掛けられている場合よりも小さい。

【0052】

図4A〜4Dの処理におけるように、図7A〜7Eにおける処理は、好ましくは、ソース側選択トランジスタに最も近いトランジスタから始まり、また次にストリング100におけるトランジスタの全てがプログラムされてしまうまで、ソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続的に反復される。

【0053】

漏電および/または帯域から帯域へのトンネリングによるブレークダウンは、接地されたセルとプログラムされているセルとの間で、また接地されたセルと中間電圧VPASSが印加されたセルとの間で依然起き得る。これは、特に短いチャネル長さのメモリセルに対する場合である。かくして、ブレークダウンは、図7Dにおけるセル126とセル128との間と同図におけるセル122とセル124との間のドレイン側ジャンクションでまたはドレイン側ジャンクションの近くで起きる。そのようなブレークダウンを減らすために、選択されたワードラインのソース側で2本のワードラインを接地する代わりに、低い正の電圧が代わりに印加される。これは、絶縁セル124、126のジャンクション領域(メモリセルのドレインとソース)と図7Dにおけるメモリセル122、128のフローティングゲート電位との間の電位差を低減する作用を有する。フローティングゲートとその対応する高く昇圧されたドレイン領域またはソース領域との間の電位差を低減することで、ブレークダウンの起きる見込みを低くする。図7DにおけるワードラインWL1、WL2に印加される1ボルトから3ボルトのオーダーの小さなバイアス電圧は、漏電および/または帯域から帯域へのトンネリングなどのブレークダウンメカニズムを抑制するのに十分なようである一方、EASB方式における2つの昇圧された領域を隔離するのに適している。そのような改造された方式を図8A〜8Eに示す。2組の図(図7A〜7Eと図8A〜8E)の比較から、図7A〜7Eにおけるように選択されたワードラインのソース側においてそれに直近した2本のワードラインを接地する代わりに低い電圧VLOW1、VLOW2が図8A〜8Eに示されているように代わりに印加される点に留意されたい。

【0054】

図8A〜8Eの実施形態も図5A〜5Dを参照して前述した本発明の態様を採用している。図7B〜7Eにおけるように、中間電圧VPASSをWL0に印加する代わりに、低い電圧VLOW3が図8Dと図8Eに示されているように代わりに印加される。これによってワードラインWL0の下のFG0のしきい値電圧に影響するソース側選択トランジスタ120のドレイン側のブレークダウンを少なくしたり、または防止することになる。同じような表現様式で本発明のこのような態様(低い電圧をWL0に印加すること)を、LSB方式と組み合わせてもよい。そのような目的のために、図8A〜8Eは若干改変されて、電圧(例えば、0ボルト)を選択されたワードラインのドレイン側のワードラインに印加すると共に選択されたワードラインに結合された選択されていないセルをドレイン側のそれらの隣接しているセルのチャネル領域から隔離するようにしている。

【0055】

図8A〜8Eを参照して、取りうるSBとEASBのバイアス方式の概要を要約した表を下に記している。下の表の電圧V1 、V2 、V3 は、必ずしも異なっている必要がない点に留意されたい。これら3つの電圧のための一般的な値は、1ボルトから3ボルトまたは凡そその範囲となり得る。別に変えることも可能であるが、好ましい構成としてVLOW1とVLOW3が1ボルトから3ボルトの範囲であり、好ましくは1.8ボルトのオーダーとなっているVddに等しくなり、また電圧VLOW2が約0ボルトになるようにしている。そのような電圧の構成は、2本の絶縁ワードラインのうちの一方が接地されているので、選択ゲートと絶縁ワードラインの両方においてブレークダウンを抑制したり、または防止したりし、また効率的に2つの昇圧されたチャネル領域を絶縁することになり、それによって接地されたワードラインに結合されたトランジスタをオフに切り替える。そのような値で、選択されたトランジスタ(例えば、130)が、トランジスタの同じストリングにおける少なくとももう1つ別のトランジスタ(例えば、128)によって0ボルトが印加されるワードラインに結合されたトランジスタ(例えば、126)から分離されている点が図8Eから留意されるが、その場合、0ボルトよりもむしろ低い正の電圧がそのようなトランジスタ(例えば、128)に印加される。

V1 とV3 は好ましくは約1〜3ボルトの範囲となり、V2 は約0ボルトが好ましい。

【0056】

さらにもう1つ別の実施形態を例示すると、ストリング100は、トランジスタ130のドレイン側にストリングのもう1つ別のセルまたはトランジスタ(図示せず)を有し、その場合、そのようなトランジスタは、WL4のドレイン側においてもう1つ別のワードラインWL5(図示せず)に結合されている。この実施形態では、プログラミング電圧VpgmはワードラインWL5に印加され、また残りのワードラインはWL4=V1 =1.5V、WL3=V2 =0V、WL2=V1 =1.5V、WL1=Vpass、WL0=V3 =1.5Vとなるように電圧がそれら残りのワードラインに印加される。これで、0ボルトが印加されるワードラインWL3の両側でブレークダウンを防ぐことになり得る。より一般的な言い方をすると、低い電圧が3本の隣接したワードラインに印加され、その場合3本のワードラインのうちの中央のものに印加される電圧(0ボルトなど)は、それに結合されたプログラムされるトランジスタをオフに切り替えさせる。

【0057】

前述したEASB方式に類似した方式もLSBのために使用される。従来のLSBの不利な点は、選択されたワードラインに結合されたチャネル領域と選択されたワードラインのソース側において接地されたワードラインの下のセルのドレイン領域およびソース領域との間でブレークダウンが起きる点である。このブレークダウンは選択されたワードライン上のセルのフローティングゲート内へのホットエレクトロンの注入および/または昇圧されたチャネル電位の減少を間接的に起こし、それによって多分に望ましくないそのようなセルのしきい値電圧を変える。次世代のデバイスのメモリセルの寸法がより小さくなる場合は、オフに切り替えられるメモリセルのチャネル長さも余りにも短くなって、選択されたワードラインに結合されたチャネル領域を選択されたワードラインのソース側とドレイン側のチャネル領域から電気的に絶縁することができず、結果的に昇圧された電荷が漏電を起こすと共に昇圧された電位が低減されて、多分にプログラム障害が生じることになる。かくして、本発明のもう1つ別の態様は、選択されたトランジスタまたはワードラインのソース側における2本以上のワードライン(好ましくは、互いに接近している)に適切にバイアスを掛けると共にそのドレイン側における2本以上のワードライン(好ましくは、互いに接近している)に適切にバイアスを掛けて絶縁メモリセルのチャネル長さを効果的に長くし、それによって3つの昇圧された領域間での帯域から帯域へのトンネリングと漏電の両方がそれによって同時に低減されると言う認識に基づいている。本発明のこのような態様を図9A〜9Eに示す。

【0058】

図9A〜9Eは、本発明のこの態様を例示するために改造されたLSB方式においてストリングに印加されるバイアス電圧を示すNANDストリング100の断面図である。図9A〜9Eの改造された方式は、図8A〜8Eの方式とは次の点で異なっている。即ち、ゼロまたは低い正の電圧レベルVLOW4、VLOW5が、選択されたワードラインのソース側の電圧レベルに加えて選択されたワードラインにおける2本のワードライン(好ましくは、互いに隣接している)に印加される点で異なっている。かくして、図9A〜9Cでは、例えば、セル122、124、126がシーケンシャルなプログラミングタイムインターバルでプログラムされている場合、ゼロまたは低い正の電圧のレベルが、選択されたワードラインに直近した2本のドレイン側ワードラインに印加される。かくして、図9Aでは、セル122がプログラムされている場合、0ボルトまたは低い正の電圧レベルVLOW4、VLOW5がワードラインWL1、WL2に印加される。図9Bでは、ワードラインWL1がセル124をプログラムするために選択されると、0ボルトまたは低い正の電圧のレベルVLOW4、VLOW5がWL2とWL3に印加される。図9Cでは、セル126がプログラムされかつWL2が選択されると、0ボルトまたは低い正の電圧レベルVLOW4、VLOW5がWL3とWL4に印加される。

【0059】

0ボルトをソース側の隣接したワードラインに印加することで絶縁領域のチャネル長さを長くする作用が得られる。絶縁領域のチャネル長さを選択されたワードラインの各側の2つ以上の隣接したセルによって限定された長さまで長くすることで、選択されたワードラインに結合された選択されていないセルのチャネル領域の昇圧は改善され、それによってもプログラム障害を減らすことができる。必要ならば、0ボルトまたは低い正の電圧レベルが、2本よりも多い隣接したワードラインに印加されて、昇圧されたチャネル領域間の絶縁領域の長さをさらに長くする。必要ならば、接地されたワードラインは、選択されたワードラインから1本以上のワードラインによって分離される。

【0060】

図4A〜4Dの処理におけるように、図9A〜9Eにおけるプログラミング処理は、好ましくはソース側選択トランジスタに最も近いトランジスタから始まり、次に、ストリング100におけるトランジスタの全てがプログラムされてしまうまで、ソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間でトランジスタが展開されているのと同じ順番で逐次連続して反復される。そのようなプログラミング方式の下では、選択されたワードライン(例えば、図9AにおけるWL0)に隣接したドレイン側でワードライン(例えば、図9AにおけるWL1またはWL2)に印加された0ボルトは、選択されたトランジスタ(例えば、図9Aにおける122)と同じでかつそのようなワードライン(例えば、図9AにおけるWL1またはWL2)に結合されたストリングにおけるトランジスタ(例えば、図9Aにおける124または126)をオフに切り替えることがなく、その理由はそのようなトランジスタが依然として消去された状態になっていてかつ負のしきい値電圧を有しているからである。その結果、完全な絶縁は可能ではないが、ただ1つのトランジスタが0ボルトでバイアスがかけられている場合よりも良くなるものと想定される。同じ理由でVLOW4とVLOW5に対して好ましい電圧は0ボルトであり、その理由はフローティングゲートと昇圧されたドレイン側/ソース側領域との間の電位差がプログラムされたセルに対してよりもむしろ消去されたセルに対してより小さくなっているために、消去された状態になっているセルの場合に帯域から帯域へのトンネリングの危険性がない間は絶縁を最適化するからである。しかし、0ボルトの結合電圧は、プログラムされたトランジスタを選択されたトランジスタと同じストリングにおいて正のしきい値電圧で完全にオフに切り替える。

【0061】

VPGM に接続されている選択されたワードラインの直近の接地されたセルのドレイン側またはソース側で、また接地されたセルおよび中間電圧VPASSが印加されているセルのドレイン側またはソース側で依然としてブレークダウンは起き得る。かくして、ブレークダウンは図9Aにおけるセル124のソース側と同図のセル126のドレイン側で起きる。そのようなブレークダウンを低減するために、選択されたワードラインはドレイン側で2本のワードラインを接地する代わりに、低い正の電圧が代わりに印加される。このことは、メモリセル124のフローティングゲートとその高く昇圧されたソース側との間の電位差を小さくすると共にメモリセル126のフローティングゲートとWL3、WL4などによって図9の電圧VPASSで昇圧されるその昇圧されたドレイン側との間の電位差を小さくする作用を有する。しかし、一般にはLSB方法によるように、選択されたセルのドレイン側のセルは、依然として消去された状態(負のしきい値電圧)になり、その結果帯域から帯域へのトンネリングが最高のプログラムされた状態(約2.5ボルト〜3ボルトのしきい値電圧)になっているメモリセルのドレイン側またはソース側で主に起きるので、帯域から帯域へのトンネリングを低減するために低い正の電圧を印加する必要はなくなる。

【0062】

別の変形例も図9A〜9Eで可能ではあるが、好ましい構成は、VLOW1とVLOW3が1ボルトから3ボルトの範囲で、好ましくは1.8ボルトのオーダーとなっているVddに全て等しくなっていて、かつ電圧VLOW2、VLOW4、VLOW5が約0ボルトになっている場合である。そのような電圧の構成は、選択ゲートと絶縁ワードラインの両方でのブレークダウンを抑制したり、または防止すると共に選択されたワードラインに結合されたチャネル領域を効率的に絶縁し、その理由はソース側の2本の絶縁ワードラインのうちの一方および少なくとも一方が、好ましい場合にはドレイン側の2本の絶縁ワードラインの両方が接地されていて、それによって接地されたワードラインに結合されたトランジスタをオフに切り替えるためである。そのような値では、0ボルトをメモリセル128に印加するのが好ましいであろうが、選択されたトランジスタ(例えば、126)が、トランジスタの同じストリングにおいて少なくとももう1つ別のトランジスタ(例えば、124と128)によって0ボルトが印加されるワードラインに結合されたトランジスタ(例えば、122と130)から分離されると共に小さな正の電圧がそのような分離トランジスタ(例えば、124と128)に印加される点に図9Cから留意されたい。

【0063】

幾つかの状況では、プログラミング処理中に選択されたトランジスタのチャネル領域の電圧を若干高めることができることが望ましい場合がある。そのようなことができるのが望ましい状況の1つの例が、本願明細書において参照により援用されている米国公開特許出願第2003/0147278号(特許文献11)に記載されている。これを可能にするために、選択されたストリングが選択されたワードラインのドレイン側セルのチャネル領域を介して選択トランジスタのチャネル領域に連通されるように、ビットライン上の低い正の電圧(例えば、0.5ボルト)ができるようにすることが望ましい。図9A〜9Eを参照して前に説明されたLSB方式は、そのような目的のために若干改変される。VLOW4とVLOW5を約0ボルトに設定する代わりに、好ましくは、それらは1ボルトから3ボルトの範囲などの、好ましくは1.8ボルトのオーダーなどの低い正の電圧に設定される。もう1つ別の可能性は、それらのうちのただ1つを約0ボルトに設定することであり、残りを1ボルトから3ボルトの範囲の電圧などの、好ましくは1.8ボルトのオーダーの低い正の電圧としている。そのような場合、ブレークダウンを減らしたり、または回避するために、好ましくはVLOW4がそのような低い正の電圧に設定されると共にVLOW5が約0ボルトに設定される。代わりに、VLOW4がそのような低い正の電圧に設定され、またVLOW5が一般的に5ボルトから10ボルトのオーダーとなっているVPASSなどのより高い電圧となっている。

【0064】

本発明を色々な実施形態を参照して説明してきたが、添付された特許請求の範囲とそれらの同等物とによってのみ限定されることになる本発明の技術範囲から逸脱しない限り、変更と改造が行え得るものであることが理解される。参照されている全ての参考文献は、本願明細書において参照により援用されている。

【技術分野】

【0001】

本発明は、全体としてフラッシュEEPROM(電気的に消去可能でプログラム可能な読み出し専用メモリ)形の不揮発性半導体メモリ、特にNAND形メモリセルアレイを操作する構造および方法に関する。

【背景技術】

【0002】

特にフラッシュEEPROMセルのアレイを使っている小形のファクタカードの形式で今日使用されている商業的に成功している不揮発性メモリ製品が数多くある。

【0003】

一般的なフラッシュEEPROMの構成の1つに、NANDアレイを使用しているものがあり、その場合、多数のメモリセルのストリングが、1つ以上の選択トランジスタを介して個々のビットラインと基準電位との間に接続されている。そのようなアレイの一部分が図2Aの平面図に示されている。BL0〜BL4(そのうちのBL1〜BL3は、さらに12〜16とラベル付けされている)は、大域の垂直金属ビットライン(図示せず)への拡散されたビットライン接続部を表している。4つのフローティングゲートメモリセルが各ストリングに示されているが、個々のストリングは、一般的には列にフローティングゲートなどの16、32またはそれよりも多いメモリセル電荷記憶素子を有している。WL0〜WL3とラベル付けされたコントロールゲート(ワード)ライン(図2Aの線A−Aに沿った断面の図2BでP2とラベル付けされている)とストリング選択ラインSGD、SGSは、しばしばポリシリコン(図2BにおいてP1とラベル付けされている)の幾つかのフローティングゲートの行の上側を渡って多くのストリングを交差して延びている。一方、トランジスタ40、50に対して、コントロールゲートとフローティングゲートとは電気的に接続されてもよい(図示せず)。コントロールゲートラインは、一般的に自己整合されたスタックとしてフローティングゲートの上側に形成され、また図2Bに示されているように、中間の誘電体層19を介して互いに容量結合されている。ストリングの頂部および底部は、周辺機器から電気的に駆動されているトランジスタのアクティブゲートとしてフローティングゲート材(P1)を使用するトランジスタを通常は介して、ビットラインおよび共通のソースラインに各々接続している。フローティングゲートとコントロールゲートとの間にはこのような容量結合があるため、フローティングゲートに結合されたコントロールゲート上の電圧を高めることでフローティングゲートの電圧を高めることができる。列内の個々のセルは、各ストリングを流れる電流が主として選択されたワードラインの下方のアドレス指定されたセルに記憶された電荷のレベルにのみ依存するように、ストリングの残りのセルがそれらの各々のワードライン上に比較的高い電圧をかけ、さらに1つの選択されたワードライン上に比較的低い電圧をかけることでストリングの残りのセルをオンにすることによってプログラミング中に読み出されて検証される。その電流は、一般に多数の並列なストリングに対して検知され、それによってフローティングゲートの行に平行に沿って電荷のレベル状態が読み出される。

【0004】

NAND形フラッシュメモリシステムとそれらの動作の関連例が、米国特許第5,570,315号(特許文献1)、第5,774,397号(特許文献2)、第6,046,935号(特許文献3)、第6,456,528号(特許文献4)、第6,522,580号(特許文献5)に示され、これらの特許の全ては本願明細書において参照により援用されている。

【0005】

現在のフラッシュEEPROMアレイの電荷記憶素子は、一般にドープされたポリシリコン材から形成された最も一般的な導電性フローティングゲートとなっている。一方、必ずしも導電性である必要はないが電荷記憶能力を有する他の材料も使用される。そのような代わりの材料の例として窒化ケイ素がある。そのようなセルについては、野崎隆明らによる論文「半導体ディスクに適用するMONOSメモリセルを有する1−MbのEEPROM」,固体回路のIEEEジャーナル,第26巻,第4号,1991年4月,第497頁〜501頁 (Takaaki Nozaki et al.,“A 1-Mb EEPROM with MONOS Memory Cell for Semiconductor Disk Application", IEEE Journal of Solid-State Circuits, Vol. 26, No. 4, April 1991, pp. 497-501)(非特許文献1)で説明されている。

【0006】

一般的な不揮発性フラッシュアレイのメモリセルは、同時に消去される独立したセルのブロックに分割される。即ち、2つ以上のブロックが1回の消去動作で消去されることもあるが、ブロックは、消去ユニットとして個別に同時に消去可能な最小数のセルを有している。各ブロックは、プログラミングと読み出しの基本ユニットとしてデータプログラミングおよび読み出し動作を同時に受ける最小数のセルとして定義されるページで、一般に1ページ以上のデータを記憶するが、2ページ以上が1回の操作でプログラムされたり、または読み出されることもある。各ページは、一般に1セクタ以上のデータを記憶するものであり、セクタの大きさは、ホストシステムによって規定されている。一例として、512バイトのユーザデータのセクタがあり、ユーザデータに関する何バイトかのオーバーヘッド情報および/またはそれを記憶しているブロックに加えて磁気ディスクドライブと共に確立された基準に従っている。

【0007】

集積回路への適用のほとんどに見られるように、或る集積回路の機能を実行するのに必要なシリコン基板の領域を縮小すると言うプレッシャーがフラッシュEEPROMアレイにもある。所定サイズのメモリカードと他の種類のパッケージの記憶容量を増やしたり、または容量の増大とサイズの縮小の両方を行うために、シリコン基板の所定領域に記憶されるデジタルデータの量を増やすことが引き続き求められている。データの記憶密度を高めるもう1つの方法は、メモリセルの電荷記憶素子当り1つよりも多いビットのデータを記憶することである。このことは、電荷記憶素子の許容電圧または電荷記憶ウインドウを2つよりも多い状態に分割することで達成される。そのような4つの状態を使用することで、各セルが2ビットのデータを記憶することができるようにし、8つの状態がセル当り3ビットのデータを記憶することができるようにする等々である。多状態のフラッシュEEPROMの構造と動作が、米国特許第5,043,940号(特許文献6)、第5,172,338号(特許文献7)、第5,570,315号(特許文献1)および第6,046,935号(特許文献3)に説明されている。

【0008】

NAND構造を使用したフラッシュメモリシステム用の一般的な構成であれば、NANDアレイが含まれ、その場合、各アレイは幾つかのNANDストリングを有している。例えば、図3Aは、図2AのメモリアレイのNANDストリング11、13、15を3つだけ示し、そのアレイは3つより多いNANDストリングを収容している。図3AのNANDストリングの各々は、2つの選択トランジスタと4つのメモリセルとを有している。例えば、NANDストリング11は、選択トランジスタ20、30とメモリセル22、24、26、28を有している。NANDストリング13は、選択トランジスタ40、50とメモリセル42、44、46、48とを有している。各ストリングは、その選択トランジスタ(例えば、選択トランジスタ30と選択トランジスタ50)によってソースラインに接続されている。選択ラインSGSは、ソース側の選択ゲートを制御するために使用されている。色々なNANDストリングが、選択ラインSGDによって制御される選択トランジスタ20、40などによってそれぞれのビットラインに接続されている。他の実施形態では、選択ラインは必ずしも共通である必要はない。ワードラインWL3は、メモリセル22およびメモリセル42用のコントロールゲートに接続されている。ワードラインWL2は、メモリセル24およびメモリセル44用のコントロールゲートに接続されている。ワードラインWL1は、メモリセル26およびメモリセル46用のコントロールゲートに接続されている。ワードラインWL0は、メモリセル28およびメモリセル48用のコントロールゲートに接続されている。図に示されているように、各ビットラインとそれぞれのNANDストリングは、メモリセルアレイの列を有している。ワードライン(WL3、WL2、WL1、WL0)は、アレイの行を有している。各ワードラインは、その行にある各メモリセルのコントロールゲートに接続している。例えば、ワードラインWL2は、メモリセル24、44、64用のコントロールゲートに接続されている。

【0009】

図3Bは、各アレイを1組の共通のワードラインによって制御した状態で幾つかのNANDアレイを描いた回路図である。図2Aと図3のアレイは、図3Bでは1番上のアレイとして現れている。図3Bに示されているように、同じアレイにおける各NANDストリング(例えば、11、13)は、複数のビットライン12、14・・・のうちの1つおよび共通のソースラインに接続され、また共通の組のワードライン(WL0〜WL3)によって制御されている。

【0010】

各メモリセルは、データ(アナログまたはデジタル)を記憶することができる。1ビットのデジタルデータ(バイナリメモリセル)を記憶する場合、メモリセルの取りうるしきい値電圧の範囲は、論理データの「1」および「0」が割り当てられる2つの範囲に分割される。NAND形フラッシュメモリの一例では、メモリセルの消去後、電圧しきい値は負であり、論理「1」として定義されている。プログラミング動作後のしきい値電圧は正であり、論理「0」として定義されている。しきい値電圧が負で、そのコントロールゲートに0ボルトが印加され、読み出しが実施されると、メモリセルは電流を通して、論理1が記憶されていることを示すことになる。しきい値電圧が正で、読み出し動作が試みられると、メモリセルはオンに切り替わらず、それによって論理0が記憶されていることが示される。メモリセルは、さらに多くのレベルの情報を、例えば多くのビットのデジタルデータを記憶することができる。多くのレベルのデータを記憶する場合、取りうるしきい値電圧の範囲は、データのレベル数に分割される。例えば、4つのレベルの情報が記憶されれば、4つのしきい値電圧範囲が存在することになり、各範囲は1つのデータ値に割り当てられる。しきい値電圧の複数の(2よりも多い)範囲間の区別によってデータを記憶するメモリは、多重状態メモリとして知られている。NAND形メモリの一例では、消去動作後のしきい値電圧は、負であり、「11」として定義されている。正のしきい値電圧は、「10」、「01」および「00」の状態に対して使用される。

【0011】

NANDフラッシュメモリセルをプログラムする場合、プログラム電圧がコントロールゲートに印加され、またプログラムするために選択されるNANDストリングのチャネル領域が接地される(0ボルト)。NANDストリングの下方のチャネル領域からの電子は、フローティングゲート内に注入される。電子がフローティングゲートに蓄積すると、そのフローティングゲートは負に充電され、またセルのしきい値電圧が高められる。選択されたNANDストリングのチャネル領域を接地するために、対応するビットラインは接地される(0ボルト)一方、SGDは、選択トランジスタのしきい値電圧よりも高い十分な高電圧(一般には、例えば3.3ボルトのVdd)に接続される。プログラム電圧をプログラムされているセルのコントロールゲートに印加するために、そのプログラム電圧は適切なワードラインに印加される。前に説明したように、そのワードラインは、同じワードラインを使用している他のNANDストリングの各々にある1つのセルにも接続されている。例えば、図3Aのセル24をプログラムする場合、プログラム電圧がセル44のコントロールゲートにも印加されることになる。これは、両方のセルが同じワードラインを共有しているためである。同じワードラインに接続された他のセルをプログラムせずにワードライン上の1つのセルをプログラムしたい場合、例えばセル24をプログラムして、セル44をプログラムしたくない場合、問題が生じる。プログラム電圧はワードラインに接続された全てのセルに印加されるので、そのワードライン上の選択されなかったセル(プログラムされるべきでないセル)は、不注意でプログラムされるかもしれない。例えば、セル44はセル24に隣接している。セル24をプログラムする場合、セル44が何気無くプログラムされるおそれがある。選択されたワードライン上の選択されていないセルの何気無いプログラミングは、「プログラム障害」と称される。一般的に言って、「プログラム障害」は、正または負のいずれかの方向へのあらゆる望まないしきい値電圧シフトを説明するのに使用されるものであり、そのシフトはプログラミング動作中に起きて、選択されたワードラインに必ずしも限定されるものではない。

【0012】

プログラム障害を防ぐためには幾つかの技術を利用することができる。「自己昇圧」(「SB」)として知られている一つの方法が、K.D.スーらによる「インクリメンタル・ステップ・パルスプログラミング方式を有する3.3ボルト、32MbのNANDフラッシュメモリ」,固体回路のジャーナル,第30巻,第11号,1995年11月,第1149〜1155頁 (K. D. Suh et al.,“A 3.3V 32Mb NAND Flash Memory with Incremental Step Pulse Programming Scheme," Journal of Solid-State Circuits, Vol. 30, No. 11, Nov. 1995, pp. 1149-55)(非特許文献2)において提案されている。SB方式を使用したプログラミング中に、選択されなかったNANDストリングのチャネル領域は、それらの対応するビットラインから電気的に絶縁されている。引き続いて、中間のパス電圧(例えば、10ボルト)が選択されなかったワードラインに印加される一方、高いプログラム電圧(例えば、18ボルト)が選択されたワードラインに印加される。この用例では、用語「絶縁」と「電気的に絶縁」とは互いに交換可能に使用され、また用語「書き込み電圧」、「プログラム電圧」および「プログラミング電圧」は互いに交換可能に使用される。選択されなかったNANDストリングのチャネル領域は、選択されなかったワードラインに容量的に結合され、選択されなかったNANDストリングのチャネル領域に電圧(例えば、0.6の結合比を仮定すると6ボルト)を存在させる。この所謂「自己昇圧」は、選択されなかったNANDストリングのチャネル領域と選択されたワードラインに印加されるプログラム電圧との間の電位差を小さくする。その結果、選択されなかったNANDストリングにおけるメモリセルに対して、また特に選択されたワードライン上のこのようなストリングにおけるメモリセルに対して、トンネル酸化物を渡る電圧とそれに伴いプログラム障害とが大幅に低減される。

【0013】

図3Aを参照すると、ビットライン12上のセルのうちの1つをプログラムするために自己昇圧プログラミング技術が、図3Aにおけるメモリアレイに適用される場合、例えば0ボルトがビットライン12に印加されると共に電圧Vdd(例えば、3.3ボルト)がビットライン14に印加される。その電圧Vddは、ドレイン側の選択ラインSGDに印加されてトランジスタ20、40をオンに切り替え、また0ボルトがソース側の選択ラインSGSに印加されてトランジスタ30、50をオフに切り替える。アレイ42〜48における全てのメモリセルが正規のオン状態(例えば、消去されたり、または負のしきい値電圧状態)になっていると仮定すると、トランジスタ40と50との間のNANDストリングにおける全てのセルのチャネル電位は、SGDに印加されるVddと選択トランジスタ40のしきい値電圧との間の差によって与えられる。例えば、Vddが3.3ボルトでかつトランジスタ40のしきい値電圧が1.3ボルトであれば、その場合全てのセル42〜48のチャネル電位は2ボルトに充電される。チャネル電位はこの場合約2ボルトの予め規定された電位に事前に充電されるので、この動作は「事前充電」と称される。NANDストリングのチャネル電位が十分に高い値(この場合2ボルト)に到達した後にトランジスタ50がオフに切り替えられ、かつトランジスタ40が自動的にオフに切り替わるので、メモリセル42〜48の電位は浮遊状態になる。従って、高いプログラム電圧Vpgm(例えば、18ボルト)がワードラインWL2に印加されると共に中間電圧Vpass(例えば、10ボルト)が残りのワードラインに印加されると、メモリセル42〜48のチャネル電位は、約0.6の結合比を取る場合、容量結合によって最初の事前充電レベルの2ボルトから8ボルトなどの値にブートストラップされたり、または昇圧される。従って、18ボルトなどの高い電圧がメモリセル44のコントロールゲートに印加されても、そのような高い電圧とチャネル電位との間の電位差は、メモリセル44のフローティングゲートに至る酸化物を通った電子トンネリングを起こすには適切ではなく、それによってプログラム障害が防止される。

【0014】

NANDストリングは、一般には(しかし常時ではないが)ソース側からドレイン側に、例えばメモリセル28からメモリセル22にプログラムされる。プログラミング処理がNANDの最後の(または最後に近い)メモリセルをプログラムする準備ができたときに、抑制されているストリング(例えば、ストリング13)上の全てのまたは大部分の事前にプログラムされたセルがプログラムされたならば、その際に事前にプログラムされたセルのフローティングゲートに負の電荷が存在する。このような負の電荷がフローティングゲート上に存在するので、事前充電は完全には行われず、結果的にNANDストリングの下のチャネル領域の最初の電位は低くなり、引き続いて起きるこのチャネル領域の自己昇圧も不十分なものとなる。従って、選択されなかったNANDストリングのチャネルにおける昇圧された電位は十分には高くならず、最後の23本のワードライン上に依然としてプログラム障害が存在する。例えば、プログラム電圧がWL3に印加されるときに、抑制されているストリング上のセル48、46、44がプログラムされていたならば、その際にそれらメモリセル44、46、48の各々はそのフローティングゲート上に負の電荷を有し、それが自己昇圧の昇圧レベルを制限し、多分にセル42上にプログラム障害を起こすことになる。

【0015】

前述したような問題点を鑑み、改善策として、T.S.ユングらによる「大規模記憶用途の3.3V・128MbのマルチレベルNANDフラッシュメモリ」,ISSCC96,セッション2,フラッシュメモリ,論文TP2.1,IEEE,第32ページ (T. S. Jung et al.,“A 3.3V 128Mb Multi-Level NAND Flash Memory for Storage Applications", ISSCC 96, Session 2, Flash Memory, Paper TP 2.1, IEEE, pp. 32)(非特許文献3)においてローカルな自己昇圧(「LSB」)技術を提案した。

【0016】

LSB方式では、高いプログラム電圧をワードラインWL2に印加するときに、抑制されているストリング上のメモリセル44に関してプログラム障害を低減したり、または防ぐために、メモリセル42、46がオフに切り替えられるように0ボルトがワードラインWL1、WL3に印加される。その場合、メモリセル44におけるチャネル電位は、メモリセル42、46、48のチャネル領域における自己昇圧によって影響を受けないか、または少なくとも影響を受けにくくなる。従って、メモリセル44のチャネル領域のチャネル電位は、高いプログラム電圧Vpgmによって、メモリセル44のチャネル領域が残りのメモリセル42、46、48の自己昇圧の影響を受けるときに達成される電圧レベルよりも高い電圧レベルに自己昇圧され得る。これによって、メモリセル24がプログラムされているときのプログラム障害を防ぐ。自己昇圧とローカルな自己昇圧についてのより詳細な説明については、米国特許第6,107,658号(特許文献8)の特にコラム6〜10の記載を参照されたい。

【0017】

ローカルな自己昇圧の代りとして提案された1つの別の技術は、田中らに付与された米国特許第6,525,964号(特許文献9)に説明され、消去された領域の自己昇圧(「EASB」)として知られている。EASBは、次の点でLSBとは異なっている。即ち、LSBのようにセルのプログラム障害を防ぐために選択されなかったセルの各側の両メモリセルもオフに切り替えるのではなく、EASBは選択されなかったセルのソース側のメモリセルのみをオフに切り替える点で異なっている。例えば、メモリセル24がプログラムされている場合に、セル44におけるプログラム障害を防ぐために、メモリセル42はオフにせず、メモリセル46のみがオフに切り替えられている。

【0018】

LSBおよびEASBは多くの用途にとって有利ではあるが、これらの方式が今の形式で使用されると、特に次世代のデバイスにおけるメモリセルの寸法が引き続き縮小したり、または小さくなると、依然としてやはり或る種の問題が発生する。従って、そのような問題が解消される改良形自己昇圧方式を提供することが望まれている。

【先行技術文献】

【特許文献】

【0019】

【特許文献1】米国特許第5,570,315号

【特許文献2】米国特許第5,774,397号

【特許文献3】米国特許第6,046,935号

【特許文献4】米国特許第6,456,528号

【特許文献5】米国特許第6,522,580号

【特許文献6】米国特許第5,043,940号

【特許文献7】米国特許第5,172,338号

【特許文献8】米国特許第6,107,658号

【特許文献9】米国特許第6,525,964号

【特許文献10】米国特許第5,887,145号

【特許文献11】米国公開特許出願第2003/0147278号

【非特許文献】

【0020】

【非特許文献1】野崎隆明らによる論文「半導体ディスクに適用するMONOSメモリセルを有した1−MbのEEPROM」,固体回路のIEEEジャーナル,第26巻,第4号,1991年4月,第497頁〜501頁

【非特許文献2】K.D.スーらによる「インクリメンタル・ステップ・パルスプログラミング方式を有する3.3ボルト、32MbのNANDフラッシュメモリ」,固体回路のジャーナル,第30巻,第11号,1995年11月,第1149〜1155頁

【非特許文献3】T.S.ユングらによる「大規模記憶用途の3.3V・128MbのマルチレベルNANDフラッシュメモリ」,ISSCC96,セッション2,フラッシュメモリ,論文TP2.1,IEEE,第32ページ

【発明の概要】

【0021】

図2Bおよび図3を参照すると、N+の拡散された領域49は、ソース側選択トランジスタ50のドレインとして、また隣のメモリセルまたはトランジスタ48のソースとしての働きをする。用語「メモリセル」、「電荷記憶トランジスタ」および「トランジスタ」は、図2Bおよび図3に示されているもののようなフラッシュメモリのストリングの要素を参照すると、本願明細書では互いに交換可能に使用される。トランジスタ22、24または26のうちのいずれか1つについての前述した自己昇圧方式のいずれか1つにおけるプログラミング中に、0ボルトがトランジスタ50のゲートに印加され、また大部分の例では、中間電圧Vpass(例えば、10ボルト)がトランジスタ48のコントロールゲートに印加される。かくして、トランジスタ48のチャネル領域は、0.6の結合比を取る場合(チャネル領域は、昇圧前に2ボルトに事前充電されると仮定する場合)、8ボルトなどの値に昇圧される。トランジスタ48のこのような昇圧されたチャネル電圧は、多分に帯域から帯域へのトンネリングによってトランジスタ50のドレイン領域49のブレークダウンを起こす。このようなブレークダウンは、チャネル電位が下がるように、同じNANDストリングのトランジスタ48の昇圧されたチャネル領域と他のメモリセルのチャネル領域とを放電させることになってプログラム障害を起こし得る。生じ得るもう1つ別のメカニズムは、ブレークダウンによって発生される電子は、トランジスタ48の下方の昇圧されたチャネル領域に向かって加速されるものであり、このことで、しきい値電圧シフトを起こしながら引き続いてトランジスタ48のフローティングゲートに注入される所謂ホットエレクトロンをもたらす。このしきい値電圧シフトは、トランジスタ48を1つのプログラムされた状態から別のプログラムされた状態へなど、1つの充電状態からもう1つの別の状態へ変化させ得るものであり、それは望ましくない。状態のそのような変化は、トランジスタ50のドレイン領域49のブレークダウンを防ぐことを目的とした適切なバイアス状態を使用することによって防止することができる。

【0022】

充電状態の望ましくない変化は、マルチレベルのしきい値電圧形メモリにおいても、また2進レベルのしきい値電圧形メモリにおいても適切なバイアス条件を使用することによって防止され得る。適切なバイアス条件を適用することで、ソース側選択トランジスタのドレイン側における帯域から帯域へのトンネリングなどのブレークダウンメカニズムは、次の程度まで、即ちそのメカニズムがソース側選択トランジスタの隣のトランジスタの所望の電荷記憶状態が別の電荷状態に変化することにならない程度まで減衰されるようにする効果が享受でき、幾つかの場合には、そのようなメカニズムは完全に抑制される。

【0023】

一実施形態では、ドレイン領域におけるソース側選択トランジスタのブレークダウンは、ソース側選択トランジスタの隣のストリングのトランジスタ(目標トランジスタ)に印加される電圧を自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に下げてプログラム障害を減らしたり、または防止することで防止される。そのような実施形態での一実装例において、目標トランジスタに印加される電圧は1から3ボルトの範囲となり得る。もう1つ別の実装例では、プログラム障害を防止するために目標トランジスタとは別のトランジスタのうちの幾つかに結合される昇圧電圧は、目標トランジスタに結合された電圧よりも少なくとも50%だけさらに高くなり得る。

【0024】

ドレイン側の選択ゲートは一般に、昇圧中に一般的に0ボルトのゲート電圧になっているソース側選択ゲートよりも、昇圧中に1.5〜2.5ボルトの範囲のようなより高いゲート電圧になっているとは言え、図2Bにおけるドレイン側選択トランジスタ40のトランジスタ領域51などのドレイン側選択トランジスタの隣のストリングのトランジスタのドレイン領域でも前述したようなブレークダウンが起きる。ソース領域におけるドレイン側選択トランジスタのブレークダウンは、ドレイン側選択トランジスタの隣のストリングのトランジスタ(目標トランジスタ)に印加される電圧を自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に下げてプログラム障害を減らしたり、または防止することで防止される。そのような実施形態の一実装例において、目標トランジスタに印加される電圧は1から3ボルトの範囲となり得る。もう1つ別の実装例では、プログラム障害を防止するために目標トランジスタとは別のトランジスタのうちの幾つかに結合される昇圧電圧は、目標トランジスタに結合される電圧よりも少なくとも50%だけさらに高くなり得る。

【0025】

前述したソース側選択トランジスタのドレイン領域のブレークダウンおよびドレイン側選択トランジスタのソース領域のブレークダウンは、電荷記憶トランジスタのストリングにおけるトランジスタのうちのいずれかの書き込み中またはプログラミング中に起きうるものでる。従って、プログラム障害を減らすために、前述した方式は、ストリングにおける2つ以上のトランジスタを逐次プログラムしたり、または書き込んでいる間に、或いは実のところソース側またはドレイン側の選択トランジスタに直近したトランジスタのプログラミング中を除外してストリングの全てのトランジスタを逐次プログラムしたり、または書き込みしている間に適用される。

【0026】

同じ趣旨で前述した方式は、必要ならば、本願明細書において説明した自己昇圧と事前充電方式のうちのいずれか1つ以上と、また本願明細書において説明したものとは異なった事前充電方式などの他の自己昇圧方式と関連して適用される。

【0027】

次世代のデバイスのメモリセルの寸法がより小さくなると、EASB方式におけるメモリセルのチャネル長さは余りにも短くなって、選択されたワードラインに結合されたトランジスタの各々のドレイン側およびソース側で別々に昇圧される2つのチャネル領域を電気的に絶縁することができなくなる。その結果、昇圧されたチャネル電圧は低下されてプログラム障害をもたらすことになる。出願人は、選択されたワードラインに結合されたトランジスタのソース側およびその隣で2本以上のワードラインまたはコントロールゲートに、好ましくは互いに隣接したもの同士にバイアスを掛けることで2つの昇圧された領域間の絶縁を改善し、絶縁メモリセルまたはトランジスタのチャネル長さを効果的に長くし、それによって2つの昇圧された領域間の漏電を減らすように提案している。好ましくは、バイアスを掛ける条件は、帯域から帯域へのトンネリングも漏電の低減と共に同時に低減されるようにするものである。

【0028】

前述した改善されたEASB方式では、絶縁は選択されたワードラインに結合されたトランジスタのソース側でのみ起きるので、少なくとも幾つかの実施形態ではそのようなトランジスタのドレイン側でセルまたはトランジスタに結合された昇圧電圧を同様に下げる必要が無く、その結果2本以上のワードラインまたはコントロールゲートに結合された電圧レベルは、そのようなトランジスタのドレイン側でセルまたはトランジスタに結合された電圧レベルよりも低くなる。前述したように、前述した改善されたEASB方式は、130または100ナノメータよりも小さい寸法のように小さなセル寸法を有するメモリアレイに特に有用である。

【0029】

次世代のデバイスのメモリセルの寸法がより小さくなると、LSB方式におけるメモリセルのチャネル長さも余りにも短くなり、選択されたワードラインに結合されて選択されなかったトランジスタのチャネル領域と、そのようなトランジスタのドレイン側とソース側における昇圧されたチャネル領域とを電気的に絶縁させることができない。その結果、昇圧されたチャネル電圧は低下されてプログラム障害をもたらすことになる。出願人は、選択されたワードラインに結合されたトランジスタのソース側とドレイン側の両方でかつその隣で2本以上のワードラインまたはコントロールゲートに、好ましくは互いに隣接したもの同士にバイアスを掛けることで、メモリセルの短いチャネル長さによって起こされる漏電を低減して、絶縁メモリセルまたはトランジスタのチャネル長さを効果的に長くするように提案している。換言すれば、電圧レベルは2組のトランジスタに結合されて、選択されたワードラインに結合された少なくとも1つの選択されなかったトランジスタのチャネル領域を選択されなかったトランジスタと同じストリングにおける隣のチャネル領域から電気的に絶縁するものであり、その場合、各組は少なくとも2つのトランジスタを有していて、また2組は選択されたワードラインに結合された選択されなかったトランジスタの両側に配置されている。好ましくは、その電圧レベルは、この電圧レベルのうちの少なくとも1つに結合されて選択されたストリングにおいてより低い電圧しきい値の取りうる充電された状態のうちの1つ(例えば、プログラムされていないトランジスタのしきい値電圧のような負のしきい値電圧を有するもの)を有するトランジスタが、オンに切り替えられるようなものとなっているが、この電圧レベルのうちの少なくとも1つに結合されて選択されたストリングにおいてより高い電圧しきい値の取りうる充電された状態のうちの1つ(例えば、プログラムされるトランジスタのしきい値電圧のような正のしきい値電圧を有するもの)を有するトランジスタが、オフに切り替えられるようなものとなっている。好ましくは、その電圧レベルは、メモリセルの短いチャネル長さによる漏電と、帯域から帯域へのトンネリングで誘発されるブレークダウンの両方が同時に減らされるようなものとなっている。

【0030】

幾つかの応用と設計のために、LSB方式における選択されたワードラインのドレイン側での完全な電気的絶縁は必要が無いか、または望ましいものではない。そのような場合、改造されたLSB方式が実行され、そこで選択されたワードラインのドレイン側でセルまたはトランジスタに結合された昇圧電圧は、これらのトランジスタが完全にオフに切り替えさせない値となっているが、選択されたワードラインのドレイン側には或る電気的に絶縁が与えられる。

【0031】

2つの昇圧された領域間で漏電を減らすことは、Vpassの低い電圧に対して重要であり、また絶縁トランジスタとしての働きをするメモリセルのしきい値電圧が消去された状態になっている場合に重要である。これらのトランジスタが消去された状態になっている場合に絶縁トランジスタをオフに切り換えることができるようにするために、ソース側において或る一定の正の昇圧された電圧が必要とされる。この正の電圧は、Vpassの電圧が低い電圧(例えば、0ボルト)から高い電圧(例えば、5〜10ボルトの範囲)に上げられる昇圧処理の開始時に形成される。Vpassの低い値では、チャネル領域はそれほど高くない電圧へと昇圧され、その結果、絶縁トランジスタは後でオフに切り変わり、かくしてより多くの電荷がより高く昇圧されたドレイン領域から転送されるようにし、それによってドレイン側の領域の昇圧された電圧を低下させる。絶縁トランジスタとしての働きをする2つ以上のメモリセルを有することで、チャネル長さを効果的に延ばし、それによってそれら絶縁トランジスタの絶縁特性を高める。さらに、2つ以上のメモリセルが絶縁トランジスタとして使用されると、それら2つ以上のメモリセルが消去された状態になっている確率は、ただ1つのメモリセルが絶縁トランジスタとして働く確率よりも小さい。4つのレベルが記憶されているMLCメモリセルの場合、両方の絶縁メモリセルが消去された状態になっている確率は、ほんの6.25%にすぎず、一方でただ1つの絶縁メモリセルの場合は、その確率は25%になっている。

【0032】

プログラム障害を起こし得るもうひとつ別のメカニズムは、特にVpassの比較的高い値で起きる。そのような場合、ドレイン側領域は、選択されたワードラインの隣に配置されている絶縁トランジスタのドレイン側でブレークダウンを起こす高い電圧に昇圧される。そのようなブレークダウンの推定することができるメカニズムは、絶縁メモリセルのドレイン領域の縁でのまたはその縁の近くでの帯域から帯域へのトンネリングである。他のブレークダウンメカニズムもある。ブレークダウンによって、所謂「ホットエレクトロン」となる電子が発生され、その理由はこれらの電子が選択されたワードラインの近くに存在している強力な電界によって加速されるからである。これらのホットエレクトロンは、選択されたワードライン上のメモリセルのフローティングゲートまたは隣接しているメモリセルのフローティングゲートに注入され、かくしてそれらメモリセルのしきい値電圧を変えると共に多分にメモリセルの電荷記憶状態における変化を起こす。絶縁メモリセルに対して適切なバイアス電圧を選択することで、絶縁トランジスタのドレイン側領域でのブレークダウンは防止されるかまたは少なくとも大幅に抑制される。ブレークダウンのもう1つ別の取りうる副次的作用は、ドレイン側の昇圧された領域がそのブレークダウンによって部分的に放電されることである。そのようなブレークダウンはホール/電子の対を発生させるので、ドレイン側の昇圧されたチャネル領域へ流れる電子はその領域の昇圧された電位を下げることになり、それによって多分にプログラム障害を増大させることになる。

【図面の簡単な説明】

【0033】

【図1】本発明のメモリセルアレイおよび操作改善が実施される種類のメモリシステムのブロック図である。

【図2A】従来技術のNANDアレイの平面図である。

【図2B】A−Aに沿って切り取られた図2Aの従来技術のNANDアレイの断面図である。

【図3A】図2AのNANDストリングのうちの3つを描いた回路図である。

【図3B】各アレイが1組の共通のワードラインによって制御された状態の幾つかのNANDアレイを描いた回路図である。

【図4A】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4B】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4C】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図4D】ストリングにおけるそれぞれのセルの従来技術の自己昇圧プログラミング方法を例示するために4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を例示するNANDストリングの断面図である。

【図5A】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5B】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5C】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図5D】本発明の一実施形態を例示するために改良された自己昇圧プログラミング方式における4つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6A】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6B】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6C】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6D】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図6E】ストリングにおけるそれぞれのセルの従来技術の消去された領域の自己昇圧プログラミング方式を例示するために5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7A】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7B】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7C】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7D】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図7E】本発明のもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8A】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8B】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8C】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8D】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図8E】本発明のさらにもう1つ別の実施形態を例示するために改造されたEASBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9A】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9B】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9C】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9D】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【図9E】本発明のさらにもう1つ別の実施形態を例示するために改造されたLSBプログラミング方式における5つの連続したタイムインターバル中のストリングにおけるバイアス電圧を示すNANDストリングの断面図である。

【発明を実施するための形態】

【0034】

説明を簡略化するために、本願では、同じ構成要素は同じ番号が付されている。

【0035】

メモリシステム

本発明の色々な態様が実施される例示のメモリシステムを図1のブロック図で示す。マトリックス上に配列された複数のメモリセルMを有するメモリセルアレイ1は、列制御回路2、行制御回路3、c−ソース制御回路4およびc−p−ウェル制御回路5によって制御される。メモリセルアレイ1は、この例では背景技術の欄で既に説明し、本願明細書において参照により援用されているNAND形となっている。制御回路2は、メモリセル(M)に記憶されたデータを読み出したり、プログラミング動作中にメモリセル(M)の状態を決めたり、またプログラミングを促進したり、またはプログラミングを禁止するためにビットライン(BL)の電位レベルを制御するためにメモリセルアレイ1のビットライン(BL)に接続されている。行制御回路3は、ワードライン(WL)のうちの1つを選択したり、読み出し電圧を印加したり、列制御回路2によって制御されるビットライン電位レベルと結合されたプログラム電圧を印加したり、またメモリセル(M)が上に形成されているp形領域(セルP−ウェル)の電圧と結合された消去電圧を印加するためにワードライン(WL)に接続されている。c−ソース制御回路4は、メモリセル(M)に接続された共通のソースラインを制御する。c−p−ウェル制御回路5は、セルのP−ウェル電圧を制御する。

【0036】

メモリセル(M)に記憶されたデータは、列制御回路2によって読み出され、I/Oラインとデータ入出力バッファ6とを経由して外部のI/Oラインに出力される。メモリセルに記憶されるプログラミングデータは、外部のI/Oラインを経由してデータ入出力バッファ6に入力されると共に列制御回路2に転送される。外部のI/Oラインはコントローラ9に接続されている。コントローラ9は、色々な形のレジスタと揮発性ランダムアクセスメモリ(RAM)10を含む他のメモリとを有している。

【0037】

フラッシュメモリデバイスを制御するコマンドデータは、コントローラ9に接続した外部の制御ラインに接続されたコマンド回路7に入力される。コマンドデータは、フラッシュメモリにどのような操作が必要とされているかについて知らせる。入力されたコマンドは、列制御回路2、行制御回路3、c−ソース制御回路4、c−p−ウェル制御回路5およびデータ入出力バッファ6を制御する状態マシン8に転送される。状態マシン8は、READY/BUSYまたはPASS/FAILなどのフラッシュメモリの状態データを出力する。

【0038】

コントローラ9は、パーソナルコンピュータ、デジタルカメラまたは携帯用移動端末(PDA)などのホストシステムと接続されたり、または接続可能となっている。メモリアレイ1にデータを記憶したり、またはデータを読み出すなどのコマンドを開始し、そのようなデータをそれぞれ提供したり、または受け取るのがホストの役目である。コントローラは、そのようなコマンドをコマンド回路7によって解釈されたり、実行されるコマンド信号に変換する。コントローラはさらに、メモリアレイに書き込まれたり、または読み出されるユーザデータのためのバッファメモリを一般に収容している。一般的なメモリシステムは、コントローラ9を含む1つの集積回路チップ11Aと、メモリアレイ、関連した制御回路、入出力回路および状態マシン回路を各々収容した1つ以上の集積回路チップ11Bとを有している。メモリアレイとシステムのコントローラ回路とを共に1つ以上の集積回路チップ上に統合することも可能である。

【0039】

図1のメモリシステムは、ホストシステムの一部として組み込まれたり、またはホストシステムの嵌合ソケット内に取り外し可能に挿入されるメモリカードに包含されたりする。そのようなカードは、全体のメモリシステムを含んだり、または関連した周辺回路と共にコントローラおよびメモリアレイが別のカードに設けられたりする。幾つかのカードの実装例については、例えばその全体が本願明細書において参照により明確に援用されている米国特許第5,887,145号(特許文献10)に説明されている。

【0040】

図4A〜4Dは、本発明の或る態様を例示するために役立つ従来の自己昇圧プログラミング方式における4つの異なった連続したタイムインターバル中におけるストリングのバイアス電圧を示すNANDストリング100の断面図である。前述したように、NANDストリングは、一般的にソース側からドレイン側に、よって図4A〜4DではWL0〜WL4へ逐次プログラムされるようになっていて、プログラムされる第1のセルはメモリセル122となり、次のものはメモリセル124となるなどメモリセルまたはトランジスタ130まで逐次プログラムされるようになっている。NANDストリング100は、図4Aに示されている5つのセル122〜130よりも多くのセルを収容し、一般には16または32のメモリセルが1本のNANDストリングに直列状に接続されている。NANDストリング100は、他の実装例も可能ではあるが、図2Bを参照すると上の方に示されている形で実施される。NANDストリング100は、前述した方式で制御されかつ動作される。

【0041】

図4Aは、ストリングのセル122がプログラムされているときにNANDストリング100に印加されるバイアス電圧を示す。図4Aに示されているように、0ボルトがソース側選択トランジスタ120のゲートのSGSに印加される。さらに、0ボルトかまたはそれより幾分高い電圧のVsがソースラインに印加される。プログラミング中に0ボルトよりも高い電圧をソースラインに印加することで選択トランジスタ120の絶縁特性を改善する。図4Aに示されているように、高いプログラム電圧VPGM がワードラインWL0に印加されると共に中間の電圧VPASSが残りのワードラインに印加される。高いVPGM は、チャネルからの電子を酸化物を通ってトランジスタ122のフローティングゲートFG0へトンネリングさせる。前述したように、そのような選択されなかったトランジスタのチャネル電位を昇圧することによってワードラインWL0によりアドレス指定された選択されなかったセルまたはトランジスタにおけるプログラム障害を減らしたり、または防止するために、中間電圧VPASSが印加される。これは従来の自己昇圧方式である。プログラム電圧VPGM は、トランジスタ122のしきい値電圧を検査するために読み出しサイクルが各増分の後に続くような増大インクリメントで印加される。これらのステップは図1のメモリシステムによって実行される。プログラミングがトランジスタ122のしきい値電圧を目標しきい値に到達させた後に、メモリシステムは次いで図4Bに示されているような次のプログラミングタイムインターバルでトランジスタ124をプログラムするように移行し続ける。かくして、図4Bに示されているように、高い書き込み電圧が代わりにワードラインWL1に印加されると共に中間電圧VPASSが残りのワードラインに印加されて、トランジスタ122をプログラムするために前述したのと同じ方式でトランジスタ124をプログラムする。トランジスタ124がプログラムされた後は、次に高い書き込み電圧がワードラインWL2に印加されると共に中間電圧が残りのワードラインに印加される図4Cに示されているようなトランジスタ126のプログラミングのために次のプログラミングタイムインターバル中にメモリシステムは進行する。これが完了されると、このシステムでは、次のプログラミングタイムインターバルにおいて図4Dに示されているようなトランジスタ128のプログラミングのために、また次いで引き続いたプログラミングタイムインターバル中にトランジスタ130のプログラミングのために進行する。この処理は、ソース側選択トランジスタに最も近いトランジスタから開始し、次いでストリング100の全てのトランジスタがプログラムされてしまうまで、トランジスタがソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続して反復される。

【0042】

図2Bを参照して前に説明したように、トランジスタ122の昇圧されたチャネル電圧は、図4B〜4Dに示されている4つのプログラミングタイムインターバルのうちの3つの間隔でソース側選択トランジスタ120のドレイン領域のブレークダウンを起こし、その結果フローティングゲートFG0が既にプログラムされてしまった後に、フローティングゲートFG0内に注入されるホットエレクトロンが発生される。この電子の注入でFG0のしきい値電圧をシフトさせることになり、それは所望の電荷記憶状態から別の間違った電荷記憶状態へのFG0の切り替えをもたらすことになる。同じことがメモリアレイにおける他のストリングに対しても言うことができる。図2Bを参照して前に説明したように、トランジスタ122における昇圧されたチャネル電圧は、図4A〜4Dに示されている4つのプログラミングタイムインターバル中にソース側選択トランジスタ120のドレイン領域のブレークダウンを起こす。結果的に、NANDストリングのチャネル領域における低下された昇圧電位が理由でプログラム障害が起きる。この種のプログラム障害は、VPGM がワードラインに印加されるときのようにワードラインがプログラミングのために選択されるときにいずれかのワードラインで起きる。前にも述べたプログラム障害のもう1つ別の可能性は、ソース側選択トランジスタ120のドレインの近くで、またはメモリセル122のチャネル領域で発生され、引き続いてフローティングゲートFG0に注入されるホットエレクトロンによるものである。ホットエレクトロンはソース側選択トランジスタ120のドレインの近くまたはメモリセル122のチャネル領域の小さな領域に極限されかつ限定されるので、後者のメカニズムはWL0上のメモリセルにただ影響するだけのようである。このようなホットエレクトロンの注入は、FG0のしきい値電圧をシフトさせることになり、それは所望の電荷記憶状態から別の間違った電荷記憶状態へのFG0の切り替えをもたらすことになる。同じことはメモリアレイにおける他のストリングに対しても言うことができる。

【0043】

セルの全てがプログラムされるときに前述したブレークダウン現象が起き続けるので、続いたワードラインがプログラムされるに従ってセル122のしきい値電圧分布が徐々に悪化することが分かった。全てのワードラインがプログラムされた後に、しきい値電圧分布がシフトアップして大幅に拡がったことが見つかった。幾つかのフラッシュメモリでは、電荷レベルの電圧範囲の窓が4つの状態に分割され、その場合上昇された状態「11」は負のしきい値電圧範囲を有し、残りの3つの状態「10」、「00」、「01」は昇順で正のしきい値電圧分布を有する。従来の自己昇圧方式が適用される場合、メモリセルの全てがプログラムされた後には、「10」のしきい値電圧分布がより高い値にシフトされて、「10」が「00」として読み出されるように大幅に拡がったことが分かる。「00」のしきい値電圧分布も幾分影響を受けたのも分かる。WL0に印加される電圧を低下させることで、「10」の電荷状態のアップシフトと拡張とが全て共に大きく低減されたり、または削除されることになることが予想される。

【0044】

本発明の一態様は、かくしてソース側選択トランジスタのドレイン領域のそのようなブレークダウンがワードラインに電位を印加することによって全て回避されたり防止されたりするという認識に基づき、その結果前述したプログラム障害のメカニズムが抑制され、また昇圧がFG0における電荷状態を変えるようなことがない。一実装例では、このことは、従来の自己昇圧中に通常印加されるVPASSのための5〜10ボルトの中間電圧の代わりに1〜3ボルトの範囲の電圧などのVPASSより低い値にWL0に供給される電圧を下げることにより達成される。このことを図5A〜5Dに示す。

【0045】

図5A〜5Dは、本発明の一態様を例示するための従来の自己昇圧中に印加されるものとは異なったバイアス電圧を伴ったNANDストリング100の断面図である。セル122がプログラムされているとき、印加されるバイアス電圧は従来の自己昇圧方式で採用されたものと同じである。しかし、セル124、126、128がプログラムされる後続のプログラミングタイムインターバル中には、一般に8〜10ボルトの範囲で従来のVPASSをワードラインWL0に印加する代わりに、より低い電圧VLOW が代わりにワードラインWL0に印加される。前述したように、一実装例では、VLOW は1〜3ボルトの範囲かまたはそれらのボルトとすることができる。そのような低い電圧は、ワードラインWL0の下のセルに対するプログラミングタイムインターバルの間隔中を除き、メモリアレイにおけるセルの全てをプログラムするためのプログラミングタイムインターバルのうちの少なくとも幾つかの間隔中に、好ましくは全ての間隔中にワードラインWL0に印加されることになる。低い電圧をWL0に印加することによって、WL1、WL2などの下の昇圧されたチャネル電位はソース側選択トランジスタのドレインに完全には転送され得ない。その結果、ソース側選択トランジスタのドレイン電圧はより低くなっていて、ブレークダウンは防止されたり、または大幅に減らされる。例えば、図5Bの場合、全てのメモリセル122〜130が約−2ボルトの消去しきい値電圧で消去された状態になっていると仮定すると、メモリセル124〜130の下のチャネル領域は例えば8ボルトに(VPASSの値に応じて)昇圧されることになる。さらに、1.5ボルトの電圧VLOW がメモリセル122の−2ボルトのしきい値電圧と組み合わせてWL0に印加されると仮定すると、このことはメモリセル122が導電状態になっていることを意味している。その結果、メモリセル124〜130のチャネル領域の昇圧された電荷の一部分はメモリセル122のソース側に転送され、その結果ソース側の電位は上昇することになる。しかし、メモリセル122のソース側電位が約3.5ボルトの値(ゲート電圧−しきい値電圧)に到達した後はその上昇は止まる。その結果、ソース側選択トランジスタのドレイン電位は、3.5ボルトの値までただ昇圧されるに過ぎず、一方で従来の場合にはその電位は8ボルトまで昇圧されていた。ドレイン電圧が非常に顕著に低下することで選択トランジスタのドレインにおけるブレークダウンを防止したり、または少なくとも大幅に減らすことは明らかである。そのような方式によって、セル122の電荷状態がトランジスタ122〜130のチャネル領域に印加される自己昇圧電圧によっては変化しないような程度まで帯域から帯域へのトンネリングは低減される。

【0046】

ドレイン側選択ゲートが一般に昇圧中に0ボルトのゲート電圧となっているソース側選択ゲートよりもより高い昇圧中の1.5〜2.5ボルトなどのゲート電圧を有していても、前述したようなブレークダウンは、図2Bのドレイン側選択トランジスタ40のソース領域51などの、ドレイン側選択トランジスタの隣のストリングのトランジスタのソース領域でも起きる。ソース領域でのドレイン側選択トランジスタのブレークダウンは、ドレイン側選択トランジスタの隣のストリングのトランジスタに印加される電圧を、プログラム障害を減らしたり、または防止するために自己昇圧方式でチャネル電圧を昇圧するのに通常使用されるものよりも低い値に低下することで防止される。かくして、図5A〜5Dは、このことを示すために若干改変される必要がある。ソース側選択トランジスタになっている代わりに、トランジスタ120は、代わりにソース側選択トランジスタよりも高い昇圧中の1.5〜2.5ボルトの範囲などのゲート電圧を有するドレイン側選択トランジスタになっている。ワードラインのラベル付けの解釈も、WL0がドレイン側選択トランジスタ120に1番近いワードラインとなるように見直される。プログラミングシーケンスは、次に、ドレイン側選択トランジスタ120に最も近いトランジスタ122に到達するまでストリングのドレイン側に向かってソース側選択トランジスタに最も近いトランジスタからの開始へと進む。かくして、図5D〜図5Aは、そのような順番でそのようなプログラミングシーケンスの最後の数サイクルを示している。トランジスタ122(ドレイン側選択トランジスタの次のトランジスタ)に結合されたワードラインWL0に0ボルトを印加する代わりに、低い正の電圧VLOW が印加される。一実装例では、トランジスタ122に印加される電圧VLOW は、1〜3ボルトの範囲とすることができる。もう1つ別の実装例では、プログラム障害を防止するためにトランジスタ122とは別の幾つかのトランジスタに結合される昇圧電圧は、トランジスタ122に結合される電圧(VLOW )よりも少なくとも50%だけさらに高くすることができる。ドレイン側および/またはソース側選択トランジスタの隣のトランジスタのソースおよび/またはドレイン領域のブレークダウンに関連した前述したような特徴は、限定はされないがSB、LSBおよびEASBのいずれかの形態を含んだあらゆる自己昇圧方式との関連で使用される。

【0047】

図5A〜5Dに示されている処理は、好ましくはソース側選択トランジスタに最も近いトランジスタから始まり、次いでストリング100におけるトランジスタの全てがプログラムされてしまうまで、トランジスタがソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続的に反復される。

【0048】

図6A〜6Eは、ストリングにおけるそれぞれのセルの従来のEASBプログラミングを例示するためのNANDストリング100の断面図である。前述したように、EASBシステムは、下方のワードラインと上方のワードラインの2つの昇圧されたチャネル領域がワードライン上に0ボルトを有するメモリセルによって隔離されるように、プログラミング中に選択されたワードラインのソース側のワードラインに0ボルトを印加する。このことにより、そのようなメモリセルはオフに切り替えられ、それによって2つの昇圧されるチャネル領域を隔離する。2つのチャネル領域を分離した結果、ドレイン側の昇圧効率が改善される。ソース側のメモリセルの幾つかがプログラムされた状態にあり、かつそれによってより高いしきい値電圧を有するので、ソース側のチャネル領域は、昇圧される度合いが少ない。選択されたワードラインのドレイン側のチャネル領域は、ドレイン側の全てのセルが負のしきい値電圧で依然として消去された状態になっているので、ビットラインを介して(ほぼ)完全に事前に充電され、より効率的に昇圧される。図6Bを参照して、例えばセル124がプログラムされている場合、0ボルトがWL0に印加される。セル126が図6Cに示されているようにプログラムされている場合、0ボルトがWL1に印加される。セル128がプログラムされている場合、0ボルトがWL2に印加され、またセル130がプログラムされている場合、0ボルトがストリング100のWL3に印加される。

【0049】

従来のEASBの不利な点は、ブレークダウンに関連した漏電(および/または帯域から帯域へのトンネリング)が接地されたワードラインの下のセルのドレイン領域で起きる点である。このブレークダウンは、選択されたワードライン上のセルのフローティングゲート内へのホットエレクトロンの注入を、またはSBメカニズムに対して説明したのと同様に昇圧されたチャネル電位の低下を間接的に起こし、それによって多分にプログラム障害を起こすことになる。さらに、次世代のデバイスのメモリセルの寸法がより小さくなると、オフに切り替えられたメモリセルのチャネル長さも短くなり、2つの別々に昇圧されるチャネル領域を選択されたワードラインのドレイン側とソース側で電気的に絶縁することができるようになる。かくして本発明のもう1つ別の態様は、2本以上のワードライン(好ましくは互いに隣接しあっている)または選択されたトランジスタまたはワードラインのソース側におけるコントロールゲートを適切にバイアスをかけて絶縁メモリセルのチャネル長さを効果的に長くすることによって2つの昇圧された領域間の帯域から帯域へのトンネリングおよび/または漏電が同時に低減されるという認識に基づいている。改良されたEASB方式における絶縁は選択されたメモリセルまたはワードラインのソース側でのみ起きるので、一般的に選択されたトランジスタのドレイン側のセルに結合された電圧を同様に下げる必要はない。本発明のこの態様を図7A〜7Eに示す。5つのフローティングゲートのメモリセルが図7A〜7Eの各ストリングに示されているが、個々のストリングは一般に16または32またはそれ以上のメモリセルの電荷記憶素子を有している。

【0050】

図7A〜7Eは、本発明のこの態様を例示するために改良されたEASB方式におけるストリングに印加されるバイアス電圧を示すNANDストリング100の断面図である。図7A〜7Eの改造された方式は、選択されたワードラインのソース側の2本のワードライン(好ましくは互いに隣接しあっている)が従来のEASB方式におけるようにただ1本のワードラインの代わりに接地されている点で図6A〜6Eのものとは異なっている。かくして図7C〜7Eでは、例えばセル126、128、130がシーケンシャルなプログラミングタイムインターバルでプログラムされている場合、選択されるワードラインに直近した2本のソース側ワードラインは接地されている。かくして、図7Cにおいて、セル126がプログラムされている場合、0ボルトがWL0とWL1に印加される。図7Dにおいて、ワードラインWL3がセル128をプログラムするために選択される場合、0ボルトがWL1とWL2に印加される。図7Eにおいて、セル130がプログラムされていてかつWL4が選択される場合、0ボルトがWL2とWL3に印加される。

【0051】

0ボルトを2本のソース側の隣接したワードラインに印加することは、絶縁領域のチャネル長さを長くする作用を有している。絶縁領域のチャネル長さを2つの隣接したセルによって設定された長さまで長くすることで、選択されるセルのドレイン側チャネル領域の昇圧が改善され、それによってプログラム障害も低減する。必要ならば、0ボルトが2本より多い隣接したワードラインに印加されて、昇圧されたチャネル領域間の絶縁領域の長さをさらに長くする。必要ならば、接地されたワードラインは、選択されたワードラインから1本以上のワードラインによって分離される。2本以上のワードラインを0ボルトにバイアスを掛けることで得られるもう1つ別の利点は、ソース側とドレイン側の昇圧されたチャネル領域間での漏電に対する最悪の状況がより起きそうもない点である。最悪の状況は、0ボルトのワードラインの下のセルが消去された負のしきい値電圧状態になっている場合に起き、その状況で、メモリセルが一部分の昇圧動作中に(負のしきい値電圧の故に)電気を通しているので、昇圧されたドレイン側チャネル電荷の幾分かは依然として漏れ出る。2本のワードラインが0ボルトに接続されている場合、両方のワードラインの下で、消去された状態のメモリセルが存在している確率は、ただ1本のワードラインが0ボルトにバイアスが掛けられている場合よりも小さい。

【0052】

図4A〜4Dの処理におけるように、図7A〜7Eにおける処理は、好ましくは、ソース側選択トランジスタに最も近いトランジスタから始まり、また次にストリング100におけるトランジスタの全てがプログラムされてしまうまで、ソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間に展開されているのと同じ順番で逐次連続的に反復される。

【0053】

漏電および/または帯域から帯域へのトンネリングによるブレークダウンは、接地されたセルとプログラムされているセルとの間で、また接地されたセルと中間電圧VPASSが印加されたセルとの間で依然起き得る。これは、特に短いチャネル長さのメモリセルに対する場合である。かくして、ブレークダウンは、図7Dにおけるセル126とセル128との間と同図におけるセル122とセル124との間のドレイン側ジャンクションでまたはドレイン側ジャンクションの近くで起きる。そのようなブレークダウンを減らすために、選択されたワードラインのソース側で2本のワードラインを接地する代わりに、低い正の電圧が代わりに印加される。これは、絶縁セル124、126のジャンクション領域(メモリセルのドレインとソース)と図7Dにおけるメモリセル122、128のフローティングゲート電位との間の電位差を低減する作用を有する。フローティングゲートとその対応する高く昇圧されたドレイン領域またはソース領域との間の電位差を低減することで、ブレークダウンの起きる見込みを低くする。図7DにおけるワードラインWL1、WL2に印加される1ボルトから3ボルトのオーダーの小さなバイアス電圧は、漏電および/または帯域から帯域へのトンネリングなどのブレークダウンメカニズムを抑制するのに十分なようである一方、EASB方式における2つの昇圧された領域を隔離するのに適している。そのような改造された方式を図8A〜8Eに示す。2組の図(図7A〜7Eと図8A〜8E)の比較から、図7A〜7Eにおけるように選択されたワードラインのソース側においてそれに直近した2本のワードラインを接地する代わりに低い電圧VLOW1、VLOW2が図8A〜8Eに示されているように代わりに印加される点に留意されたい。

【0054】

図8A〜8Eの実施形態も図5A〜5Dを参照して前述した本発明の態様を採用している。図7B〜7Eにおけるように、中間電圧VPASSをWL0に印加する代わりに、低い電圧VLOW3が図8Dと図8Eに示されているように代わりに印加される。これによってワードラインWL0の下のFG0のしきい値電圧に影響するソース側選択トランジスタ120のドレイン側のブレークダウンを少なくしたり、または防止することになる。同じような表現様式で本発明のこのような態様(低い電圧をWL0に印加すること)を、LSB方式と組み合わせてもよい。そのような目的のために、図8A〜8Eは若干改変されて、電圧(例えば、0ボルト)を選択されたワードラインのドレイン側のワードラインに印加すると共に選択されたワードラインに結合された選択されていないセルをドレイン側のそれらの隣接しているセルのチャネル領域から隔離するようにしている。

【0055】

図8A〜8Eを参照して、取りうるSBとEASBのバイアス方式の概要を要約した表を下に記している。下の表の電圧V1 、V2 、V3 は、必ずしも異なっている必要がない点に留意されたい。これら3つの電圧のための一般的な値は、1ボルトから3ボルトまたは凡そその範囲となり得る。別に変えることも可能であるが、好ましい構成としてVLOW1とVLOW3が1ボルトから3ボルトの範囲であり、好ましくは1.8ボルトのオーダーとなっているVddに等しくなり、また電圧VLOW2が約0ボルトになるようにしている。そのような電圧の構成は、2本の絶縁ワードラインのうちの一方が接地されているので、選択ゲートと絶縁ワードラインの両方においてブレークダウンを抑制したり、または防止したりし、また効率的に2つの昇圧されたチャネル領域を絶縁することになり、それによって接地されたワードラインに結合されたトランジスタをオフに切り替える。そのような値で、選択されたトランジスタ(例えば、130)が、トランジスタの同じストリングにおける少なくとももう1つ別のトランジスタ(例えば、128)によって0ボルトが印加されるワードラインに結合されたトランジスタ(例えば、126)から分離されている点が図8Eから留意されるが、その場合、0ボルトよりもむしろ低い正の電圧がそのようなトランジスタ(例えば、128)に印加される。

V1 とV3 は好ましくは約1〜3ボルトの範囲となり、V2 は約0ボルトが好ましい。

【0056】

さらにもう1つ別の実施形態を例示すると、ストリング100は、トランジスタ130のドレイン側にストリングのもう1つ別のセルまたはトランジスタ(図示せず)を有し、その場合、そのようなトランジスタは、WL4のドレイン側においてもう1つ別のワードラインWL5(図示せず)に結合されている。この実施形態では、プログラミング電圧VpgmはワードラインWL5に印加され、また残りのワードラインはWL4=V1 =1.5V、WL3=V2 =0V、WL2=V1 =1.5V、WL1=Vpass、WL0=V3 =1.5Vとなるように電圧がそれら残りのワードラインに印加される。これで、0ボルトが印加されるワードラインWL3の両側でブレークダウンを防ぐことになり得る。より一般的な言い方をすると、低い電圧が3本の隣接したワードラインに印加され、その場合3本のワードラインのうちの中央のものに印加される電圧(0ボルトなど)は、それに結合されたプログラムされるトランジスタをオフに切り替えさせる。

【0057】

前述したEASB方式に類似した方式もLSBのために使用される。従来のLSBの不利な点は、選択されたワードラインに結合されたチャネル領域と選択されたワードラインのソース側において接地されたワードラインの下のセルのドレイン領域およびソース領域との間でブレークダウンが起きる点である。このブレークダウンは選択されたワードライン上のセルのフローティングゲート内へのホットエレクトロンの注入および/または昇圧されたチャネル電位の減少を間接的に起こし、それによって多分に望ましくないそのようなセルのしきい値電圧を変える。次世代のデバイスのメモリセルの寸法がより小さくなる場合は、オフに切り替えられるメモリセルのチャネル長さも余りにも短くなって、選択されたワードラインに結合されたチャネル領域を選択されたワードラインのソース側とドレイン側のチャネル領域から電気的に絶縁することができず、結果的に昇圧された電荷が漏電を起こすと共に昇圧された電位が低減されて、多分にプログラム障害が生じることになる。かくして、本発明のもう1つ別の態様は、選択されたトランジスタまたはワードラインのソース側における2本以上のワードライン(好ましくは、互いに接近している)に適切にバイアスを掛けると共にそのドレイン側における2本以上のワードライン(好ましくは、互いに接近している)に適切にバイアスを掛けて絶縁メモリセルのチャネル長さを効果的に長くし、それによって3つの昇圧された領域間での帯域から帯域へのトンネリングと漏電の両方がそれによって同時に低減されると言う認識に基づいている。本発明のこのような態様を図9A〜9Eに示す。

【0058】

図9A〜9Eは、本発明のこの態様を例示するために改造されたLSB方式においてストリングに印加されるバイアス電圧を示すNANDストリング100の断面図である。図9A〜9Eの改造された方式は、図8A〜8Eの方式とは次の点で異なっている。即ち、ゼロまたは低い正の電圧レベルVLOW4、VLOW5が、選択されたワードラインのソース側の電圧レベルに加えて選択されたワードラインにおける2本のワードライン(好ましくは、互いに隣接している)に印加される点で異なっている。かくして、図9A〜9Cでは、例えば、セル122、124、126がシーケンシャルなプログラミングタイムインターバルでプログラムされている場合、ゼロまたは低い正の電圧のレベルが、選択されたワードラインに直近した2本のドレイン側ワードラインに印加される。かくして、図9Aでは、セル122がプログラムされている場合、0ボルトまたは低い正の電圧レベルVLOW4、VLOW5がワードラインWL1、WL2に印加される。図9Bでは、ワードラインWL1がセル124をプログラムするために選択されると、0ボルトまたは低い正の電圧のレベルVLOW4、VLOW5がWL2とWL3に印加される。図9Cでは、セル126がプログラムされかつWL2が選択されると、0ボルトまたは低い正の電圧レベルVLOW4、VLOW5がWL3とWL4に印加される。

【0059】

0ボルトをソース側の隣接したワードラインに印加することで絶縁領域のチャネル長さを長くする作用が得られる。絶縁領域のチャネル長さを選択されたワードラインの各側の2つ以上の隣接したセルによって限定された長さまで長くすることで、選択されたワードラインに結合された選択されていないセルのチャネル領域の昇圧は改善され、それによってもプログラム障害を減らすことができる。必要ならば、0ボルトまたは低い正の電圧レベルが、2本よりも多い隣接したワードラインに印加されて、昇圧されたチャネル領域間の絶縁領域の長さをさらに長くする。必要ならば、接地されたワードラインは、選択されたワードラインから1本以上のワードラインによって分離される。

【0060】

図4A〜4Dの処理におけるように、図9A〜9Eにおけるプログラミング処理は、好ましくはソース側選択トランジスタに最も近いトランジスタから始まり、次に、ストリング100におけるトランジスタの全てがプログラムされてしまうまで、ソース側選択トランジスタ(例えば、図3Aのトランジスタ50)とドレイン側選択トランジスタ(例えば、図3Aのトランジスタ40)との間でトランジスタが展開されているのと同じ順番で逐次連続して反復される。そのようなプログラミング方式の下では、選択されたワードライン(例えば、図9AにおけるWL0)に隣接したドレイン側でワードライン(例えば、図9AにおけるWL1またはWL2)に印加された0ボルトは、選択されたトランジスタ(例えば、図9Aにおける122)と同じでかつそのようなワードライン(例えば、図9AにおけるWL1またはWL2)に結合されたストリングにおけるトランジスタ(例えば、図9Aにおける124または126)をオフに切り替えることがなく、その理由はそのようなトランジスタが依然として消去された状態になっていてかつ負のしきい値電圧を有しているからである。その結果、完全な絶縁は可能ではないが、ただ1つのトランジスタが0ボルトでバイアスがかけられている場合よりも良くなるものと想定される。同じ理由でVLOW4とVLOW5に対して好ましい電圧は0ボルトであり、その理由はフローティングゲートと昇圧されたドレイン側/ソース側領域との間の電位差がプログラムされたセルに対してよりもむしろ消去されたセルに対してより小さくなっているために、消去された状態になっているセルの場合に帯域から帯域へのトンネリングの危険性がない間は絶縁を最適化するからである。しかし、0ボルトの結合電圧は、プログラムされたトランジスタを選択されたトランジスタと同じストリングにおいて正のしきい値電圧で完全にオフに切り替える。

【0061】

VPGM に接続されている選択されたワードラインの直近の接地されたセルのドレイン側またはソース側で、また接地されたセルおよび中間電圧VPASSが印加されているセルのドレイン側またはソース側で依然としてブレークダウンは起き得る。かくして、ブレークダウンは図9Aにおけるセル124のソース側と同図のセル126のドレイン側で起きる。そのようなブレークダウンを低減するために、選択されたワードラインはドレイン側で2本のワードラインを接地する代わりに、低い正の電圧が代わりに印加される。このことは、メモリセル124のフローティングゲートとその高く昇圧されたソース側との間の電位差を小さくすると共にメモリセル126のフローティングゲートとWL3、WL4などによって図9の電圧VPASSで昇圧されるその昇圧されたドレイン側との間の電位差を小さくする作用を有する。しかし、一般にはLSB方法によるように、選択されたセルのドレイン側のセルは、依然として消去された状態(負のしきい値電圧)になり、その結果帯域から帯域へのトンネリングが最高のプログラムされた状態(約2.5ボルト〜3ボルトのしきい値電圧)になっているメモリセルのドレイン側またはソース側で主に起きるので、帯域から帯域へのトンネリングを低減するために低い正の電圧を印加する必要はなくなる。

【0062】

別の変形例も図9A〜9Eで可能ではあるが、好ましい構成は、VLOW1とVLOW3が1ボルトから3ボルトの範囲で、好ましくは1.8ボルトのオーダーとなっているVddに全て等しくなっていて、かつ電圧VLOW2、VLOW4、VLOW5が約0ボルトになっている場合である。そのような電圧の構成は、選択ゲートと絶縁ワードラインの両方でのブレークダウンを抑制したり、または防止すると共に選択されたワードラインに結合されたチャネル領域を効率的に絶縁し、その理由はソース側の2本の絶縁ワードラインのうちの一方および少なくとも一方が、好ましい場合にはドレイン側の2本の絶縁ワードラインの両方が接地されていて、それによって接地されたワードラインに結合されたトランジスタをオフに切り替えるためである。そのような値では、0ボルトをメモリセル128に印加するのが好ましいであろうが、選択されたトランジスタ(例えば、126)が、トランジスタの同じストリングにおいて少なくとももう1つ別のトランジスタ(例えば、124と128)によって0ボルトが印加されるワードラインに結合されたトランジスタ(例えば、122と130)から分離されると共に小さな正の電圧がそのような分離トランジスタ(例えば、124と128)に印加される点に図9Cから留意されたい。

【0063】

幾つかの状況では、プログラミング処理中に選択されたトランジスタのチャネル領域の電圧を若干高めることができることが望ましい場合がある。そのようなことができるのが望ましい状況の1つの例が、本願明細書において参照により援用されている米国公開特許出願第2003/0147278号(特許文献11)に記載されている。これを可能にするために、選択されたストリングが選択されたワードラインのドレイン側セルのチャネル領域を介して選択トランジスタのチャネル領域に連通されるように、ビットライン上の低い正の電圧(例えば、0.5ボルト)ができるようにすることが望ましい。図9A〜9Eを参照して前に説明されたLSB方式は、そのような目的のために若干改変される。VLOW4とVLOW5を約0ボルトに設定する代わりに、好ましくは、それらは1ボルトから3ボルトの範囲などの、好ましくは1.8ボルトのオーダーなどの低い正の電圧に設定される。もう1つ別の可能性は、それらのうちのただ1つを約0ボルトに設定することであり、残りを1ボルトから3ボルトの範囲の電圧などの、好ましくは1.8ボルトのオーダーの低い正の電圧としている。そのような場合、ブレークダウンを減らしたり、または回避するために、好ましくはVLOW4がそのような低い正の電圧に設定されると共にVLOW5が約0ボルトに設定される。代わりに、VLOW4がそのような低い正の電圧に設定され、またVLOW5が一般的に5ボルトから10ボルトのオーダーとなっているVPASSなどのより高い電圧となっている。

【0064】

本発明を色々な実施形態を参照して説明してきたが、添付された特許請求の範囲とそれらの同等物とによってのみ限定されることになる本発明の技術範囲から逸脱しない限り、変更と改造が行え得るものであることが理解される。参照されている全ての参考文献は、本願明細書において参照により援用されている。

【特許請求の範囲】

【請求項1】

メモリシステムをプログラムする方法であって、前記システムが異なった電荷状態を記憶するために電荷記憶トランジスタのストリングを複数有し、前記ストリングが、第1および第2のストリングを有し、各ストリングは、複数のビットラインのうちの1つとソースラインとの間に接続され、かつ共通のワードラインによって制御される方法において、

第1のストリングにおける少なくとも2つの電荷記憶トランジスタによってソースラインから離された第1のストリングにおける選択されたトランジスタをプログラムするために、前記選択されたトランジスタに結合された選択されたワードラインにプログラム電圧を印加するステップと、

第2のストリングにおけるトランジスタのチャネル領域の電位をプログラム電圧により近い1つまたは複数の値に昇圧してプログラム障害を低減するために、選択されたワードラインと第2のストリングに接続されたビットラインとの間の第2のストリングにおけるトランジスタの全てに第1の電圧レベルを結合するステップと、

前記第1の電圧レベルよりも低い第2の電圧レベルを前記選択されたワードラインと前記ソースラインとの間の第2のストリングにおける少なくとも2つの隣接する電荷記憶トランジスタに結合するステップであって、前記第2の電圧レベルは、前記少なくとも2つの隣接するトランジスタのソース側における前記第2のストリングのチャネル領域がプログラム障害を低減するために前記選択されたワードラインによって制御される前記第2のストリングにおけるトランジスタから電気的に絶縁されるようになり、前記第2の電圧レベルは、0ボルトまたは約0ボルトの電圧レベルと正の電圧レベルとを含む、結合するステップと、

を有する方法。

【請求項2】

請求項1記載の方法において、

前記第2のストリングにおける少なくとも2つの隣接するトランジスタのうちの少なくとも1つに結合された第2の電圧レベルは、そのような少なくとも1つのトランジスタをオフに切り替えるものである方法。

【請求項3】

請求項2記載の方法において、

前記少なくとも2つの隣接するトランジスタに結合された第2の電圧レベルは、オフに切り替えられる少なくとも1つのトランジスタが、第2のストリングにおける少なくとも1つの電荷記憶トランジスタによって前記選択されたワードラインから離されるようなものとなっている方法。

【請求項4】

請求項3記載の方法において、

前記正の電圧は、オフに切り替えられる前記トランジスタから前記選択されたワードラインを離す第2のストリングにおける前記少なくとも1つのトランジスタに結合される方法。

【請求項5】

請求項4記載の方法において、

前記正の電圧は、約1ボルトから3ボルトの範囲となっている方法。

【請求項6】

請求項4記載の方法において、

前記第2の電圧レベルが、前記選択されたワードラインに隣り合ってはいるが、前記少なくとも2つの隣接するトランジスタによって前記選択されたワードラインから離されている第2のストリングにおける少なくとも1つのトランジスタに結合された正の電圧を含む方法。

【請求項7】

請求項1記載の方法において、

前記第2のストリングは、2つの選択トランジスタを有し、第2のストリングにあり、かつ2つの選択トランジスタのうちの一方に直近した第1のトランジスタは、所望の電荷記憶状態になり、前記方法は、第3の電圧レベルの結合と第2のストリングのチャネル領域の電位の昇圧とが第1のトランジスタの所望の電荷記憶状態を別の電荷状態に変えないように、第3の電圧レベルを所望の電荷記憶状態における第1のトランジスタに結合するステップをさらに有する方法。

【請求項8】

請求項7記載の方法において、

第3の電圧レベルと第2のストリングのチャネル領域の電位の昇圧との結果としての1つの選択トランジスタのドレイン側またはソース側におけるブレークダウンは、前記第1のトランジスタの所望の電荷記憶状態が別の電荷状態に変化してしまわない程度まで低減される方法。

【請求項9】

請求項7記載の方法において、

前記所望の電荷記憶状態は、前記第1のトランジスタの2つよりも多い取りうる電荷記憶状態のうちの1つになり、前記第3の電圧レベルの第1のトランジスタへの結合は、2つよりも多い取りうる電荷状態のうちの別のものに第1のトランジスタの所望の電荷記憶状態を変化させないものである方法。

【請求項10】

請求項1記載の方法において、

前記第2のストリングは2つの選択トランジスタを有し、第2のストリングにあり、かつ2つの選択トランジスタのうちの一方に直近したトランジスタは、所望の電荷記憶状態になり、前記プログラム電圧は、少なくとも2つの選択トランジスタと容量結合された2つのコントロールゲートにプログラム電圧を印加することで、第1のストリングにおける少なくとも2つの選択された電荷記憶トランジスタに逐次結合され、

前記プログラム電圧が2つのコントロールゲートに印加されると、所望の電荷記憶状態にあるトランジスタに第3の電圧レベルを結合するステップであって、その結果前記第3の電圧レベルの結合と第2のストリングのチャネル領域の電位の昇圧とが所望の電荷記憶状態を別の電荷状態に変えなくなり、前記第3の電圧レベルが前記第1の電圧レベルよりも低くなっている、結合するステップを有する方法。

【請求項11】

請求項1記載の方法において、

前記第2のストリングにおける少なくとも2つの隣接するトランジスタは、第1の電圧レベルのうちの1つが結合されている少なくとも1つの電荷記憶トランジスタによって離されている方法。

【請求項12】

メモリシステムであって、

異なった電荷状態を記憶するための電荷記憶トランジスタの複数のストリングであって、前記ストリングの各々が、複数のビットラインのうちの1つとソースラインとの間に接続されると共に共通のワードラインによって制御される第1および第2のストリングを有し、前記トランジスタが、約130nmよりも短いチャネル長さを有するストリングと、

前記第1のストリングにおける少なくとも2つの電荷記憶トランジスタによって前記ソースラインから離された前記第1のストリングにおける選択されたトランジスタをプログラムするために、前記選択されたトランジスタに結合された選択されたワードラインにプログラム電圧を印加する回路と、を有し、

前記回路は、前記選択されたワードラインと第2のストリングに接続されたビットラインとの間の第2のストリングにおけるトランジスタの少なくとも幾つかに少なくとも1つの第1の電圧レベルを結合して第2のストリングにおけるトランジスタのチャネル領域の少なくとも1つの電位を昇圧し、

前記回路は、前記少なくとも1つの第1の電圧レベルとは異なった第2の電圧レベルを、選択されたワードラインとソースラインとの間における第2のストリングにおける少なくとも2つの隣接するトランジスタに結合し、前記第2の電圧レベルは、プログラム障害を低減するために、少なくとも2つの隣接するトランジスタのソース側における第2のストリングのチャネル領域が、選択されたワードラインによって制御される第2のストリングにおけるトランジスタから電気的に絶縁されるようなものとなり、かつ少なくとも2つの電圧レベルを含むメモリシステム。

【請求項13】

請求項12記載のメモリシステムにおいて、

少なくとも2つの異なった電圧レベルは、0ボルトまたは約0ボルトの電圧レベルと正の電圧レベルとを含むメモリシステム。

【請求項14】

請求項12記載のメモリシステムにおいて、

前記トランジスタは、約100nmよりも小さい寸法を有するメモリシステム。

【請求項15】

請求項12記載のメモリシステムにおいて、

前記回路は、前記選択されたワードラインと第2のストリングに接続されたビットラインとの間の第2のストリングにおけるトランジスタの全てに前記少なくとも1つの第1の電圧レベルを結合して第2のストリングにおけるトランジスタのチャネル領域の少なくとも1つの電位をプログラム電圧により近い値に昇圧してプログラム障害を低減するメモリシステム。

【請求項16】

請求項12記載のメモリシステムにおいて、

前記第2の電圧レベルは、前記少なくとも1つの第1の電圧レベルよりも低くなっているメモリシステム。

【請求項17】

請求項12記載のメモリシステムにおいて、

前記第2のストリングにおける少なくとも2つの隣接するトランジスタのうちの少なくとも1つに結合された第2の電圧レベルは、そのような少なくとも1つのトランジスタをオフに切り替えるメモリシステム。

【請求項18】

請求項17記載のメモリシステムにおいて、

少なくとも2つの隣接するトランジスタに結合された第2の電圧レベルは、オフに切り替えられる少なくとも1つのトランジスタが、第2のストリングにおける少なくとも1つのトランジスタによって前記選択されたワードラインから離されるようなものとなっているメモリシステム。

【請求項19】

請求項18記載のメモリシステムにおいて、

前記第2の電圧レベルは、オフに切り替えられる前記トランジスタから前記選択されたワードラインを離す第2のストリングにおける前記少なくとも1つのトランジスタに結合される正の電圧を含むメモリシステム。

【請求項20】

請求項19記載のメモリシステムにおいて、

前記正の電圧は、約1から3ボルトの範囲となっているメモリシステム。

【請求項21】

請求項12記載のメモリシステムにおいて、

少なくとも2つの異なった電圧レベルは、前記少なくとも2つの隣接するトランジスタのソース側における第2のストリングのチャネル領域が前記選択されたワードラインによって制御される前記第2のストリングにおけるトランジスタから電気的に絶縁され、かつ前記少なくとも2つの隣接するトランジスタにおける漏電と帯域から帯域へのトンネリングが抑制されるようなものとなっているメモリシステム。

【請求項22】

請求項12記載のメモリシステムにおいて、

前記第2のストリングは、2つの選択トランジスタを有し、第2のストリングにあり、かつ2つの選択トランジスタのうちの一方に直近した第1のトランジスタは、所望の電荷記憶状態になり、前記回路は、第3の電圧レベルの結合と第2のストリングのチャネル領域の少なくとも1つの電位の昇圧とが前記第1のトランジスタの所望の電荷記憶状態を別の電荷状態に変えないように、第3の電圧レベルを所望の電荷記憶状態における第1のトランジスタに結合するメモリシステム。

【請求項23】

請求項22記載のメモリシステムにおいて、

第3の電圧レベルと第2のストリングのチャネル領域の少なくとも1つの電位の昇圧との結果としての1つの選択トランジスタのドレイン側またはソース側におけるブレークダウンは、前記第1のトランジスタの所望の電荷記憶状態が別の電荷状態に変化してしまわない程度まで低減されるメモリシステム。

【請求項24】

請求項22記載のメモリシステムにおいて、

前記所望の電荷記憶状態は、前記第1のトランジスタの2つよりも多い取りうる電荷記憶状態のうちの1つになり、前記第3の電圧レベルの第1のトランジスタへの結合は、2つよりも多い取りうる電荷記憶状態のうちの別のものに第1のトランジスタの所望の電荷記憶状態を変化させないものであるメモリシステム。

【請求項25】

請求項12記載のメモリシステムにおいて、

前記第2のストリングは2つの選択トランジスタを有し、第2のストリングにあり、かつ2つの選択トランジスタのうちの一方に直近したトランジスタは、所望の電荷記憶状態になり、前記回路は、少なくとも2つの選択トランジスタに容量結合された2つのコントロールゲートにプログラム電圧を印加することで、第1のストリングにおける少なくとも2つの選択されたトランジスタに逐次プログラム電圧を結合し、

前記プログラム電圧が2つのコントロールゲートに印加されると、前記回路は、所望の電荷記憶状態にあるトランジスタに第3の電圧レベルを結合し、その結果前記第3の電圧レベルの結合と第2のストリングのチャネル領域の少なくとも1つの電位の昇圧とが所望の電荷記憶状態を別の電荷状態に変えなくなり、前記第3の電圧レベルが前記少なくとも1つの第1の電圧レベルよりも低くなっているメモリシステム。

【請求項26】

メモリシステムをプログラムする方法であって、前記システムが異なった電荷状態を記憶するために電荷記憶トランジスタのストリングを複数有し、前記ストリングが、第1および第2のストリングを有し、各ストリングは、複数のビットラインのうちの1つとソースラインとの間に接続され、かつ共通のワードラインによって制御される方法において、