フリップチップキャリア、及びこれを用いた半導体実装方法

【課題】従来のMPS−C2半導体パッケージに起きる半田材ブリッジとパッケージ反りを抑制可能なフリップチップキャリア、及びこれを用いた半導体実装方法を提供する。

【解決手段】フリップチップキャリア100は、基板110と複数の独立パッドマスク120とを含む。基板110は、上表面111、および、上表面111に設置される複数のパッド112を有する。独立パッドマスク120は、パッド112を覆う。各独立パッドマスク120は、対応するパッド112と貼り付ける感光性粘着層121、及び感光性粘着層121上に形成される透光性の取放素子122を有する。

【解決手段】フリップチップキャリア100は、基板110と複数の独立パッドマスク120とを含む。基板110は、上表面111、および、上表面111に設置される複数のパッド112を有する。独立パッドマスク120は、パッド112を覆う。各独立パッドマスク120は、対応するパッド112と貼り付ける感光性粘着層121、及び感光性粘着層121上に形成される透光性の取放素子122を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体実装技術に関し、特に独立パッドマスクを有するフリップチップキャリア、及びこれを用いた半導体実装方法に関するものである。

【背景技術】

【0002】

「金属ポストの半田付けによるチップ接合」(以下「MPS−C2(Metal Post Solder−Chip Connection)」という。)は、先進のフリップチップ接合技術である。従来のフリップチップ接合は、基板と接合するバンプとしてチップの主動面上に複数の半田ボールを設置し、主動面を基板に向かせるようにチップを引っくり返し、リフローによって接合し、半田ボールを基板の対応パッド上に電気的および機械的に接合することになる。但し、バンプ同士の間隔は段々小さい設計となる場合、半田ボールは円弧状の側壁を有するので、隣接する半田ボールが容易に半田付けにより接合されるため、半田ボールのフリップチップ接合では間隔が100μmより小さい微細ピッチバンプ接合の要求を満足することができない。

一方、特許文献1のバンプ構造、バンプの形成方法、実装接続体によると、フリップチップ接合用のバンプとして従来の半田ボールを代替して金属ポストを採用し、半田材で金属ポストを基板上に接合する。リフローによって半田材は溶融し、金属ポストはリフロー温度よりも高い融点を有してポスト状が確保できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平09−097791号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載の技術により、チップバンプの間隔として金属ポストは縮小しても従来の半田ボールのブリッジ短絡現象が起きない。図1に示すように、従来の典型的な「金属ポストの半田付けによるチップ接合」(MPS−C2)の半導体パッケージ1は、主に基板10、チップ20および封止体30を含む。複数の金属ポスト21は、チップ20のハンダパッド23上に設置され、そして、半田材22で基板10上に位置する複数のパッド12に接合される。封止体30は、アンダーフィル樹脂であって良好な流動性を有することでチップ20と基板10との隙間に充填することができる。チップ20と基板10との両者の熱膨張係数の差、あるいは/及び、封止体30の硬化収縮により、半導体パッケージ1ではパッケージ反りの問題が容易に発生する。また、金属ポスト21群同士の間隔は段々小さくなると、隣接する金属ポスト21の下方の半田材22はリフローによって接合され易く、半田材22のブリッジに起因して隣接する金属ポスト21の短絡が問題となる。

【0005】

上述問題を解決するため、本発明の主な目的は、独立パッドマスクを有するフリップチップキャリアおよびこれをMPS−C2に応用する実装方法を提供する。これにより、従来のMPS−C2半導体パッケージに起きる半田材ブリッジとパッケージ反りの問題が解決できる。

【課題を解決するための手段】

【0006】

上述目的を達成するために本発明では、次に述べる技術が提案されている。本発明では、独立パッドマスクを有するフリップチップキャリアは、1つの基板と複数の独立パッドマスクとを含む。

基板は、上表面、および、上表面に設置される複数のパッドを有する。

独立パッドマスク群は、パッド群を覆う。各独立パッドマスクは、対応するパッドと貼り付ける感光性粘着層、及び、感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有する。

【0007】

本発明はさらに上述独立パッドマスクを有するフリップチップキャリアを使用する半導体実装方法を開示する。

上述の目的を達成するために本発明では、さらに他の技術を採用する。

フリップチップキャリアにおいて、さらに充填粒子を混合する封止体を含む。封止体は、基板の上表面に形成されて独立パッドマスク群の厚さよりも薄い厚さを有することにより、各取放素子は封止体の外に露出する取放表面を有する。

フリップチップキャリアにおいて、充填粒子群は無機粒子であってもよい。

フリップチップキャリアにおいて、封止体は熱硬化性であってもよい。

フリップチップキャリアにおいて、取放素子群は熱硬化性電気絶縁ポストであってもよい。

【図面の簡単な説明】

【0008】

【図1】従来のMPS−C2半導体パッケージを示す断面図である。

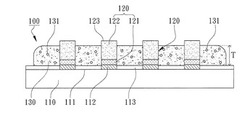

【図2】本発明の一実施形態による独立パッドマスクを有するフリップチップキャリアを示す断面図である。

【図3A】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3B】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3C】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3D】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3E】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図4】図3B製作過程に対応するステップの素子を示す斜視図である。

【図5】図3E製作過程に対応するステップの素子を示す斜視図である。

【図6】本発明の一実施形態による独立パッドマスクを有するフリップチップキャリア上に形成される封止体の素子を示す斜視図である。

【図7A】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図7B】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図7C】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図8】図7B製作過程に対応するステップの素子を示す斜視図である。

【図9】図7C製作過程に対応するステップの一部を拡大した状態を示す断面図である。

【図10】本発明の一実施形態によるフリップチップキャリアを使用するMPS−C2型半導体パッケージを示す断面図である。

【発明を実施するための形態】

【0009】

以下、添付された図面を参照して、本発明の実施形態について説明する。しかしながら、図面においては、本発明の基本構成や実施方法を示す概略図であり、本発明に係る要素と構成だけを示し、実際に実施する部材の個数、外形、寸法を一定の比率で記載するものではなく、説明の便宜及び明確性のために簡略または誇張されている。一方、実際に使われる個数、外形、寸法は様々な設計に応じ、部材の配置はより複雑になる可能性がある。

【0010】

(一実施形態)

図2に示すように、本発明の一実施例による独立パッドマスクを有するフリップチップキャリア100は、主に基板110と複数の独立パッドマスク(Individual Pad Mask:IPM)120とを含む。

【0011】

基板110は、上表面111と上表面111に設置される複数のパッド112とを有する。基板110は、プリント回路基板、セラミック回路基板、あるいは、半導体インタポーザであってもよい。基板110の内部には、図示しない適当な線路構造やメッキスルーホール(Plated Through Hole:PTH)が設けられ、外接用としてパッド112群と電気的に接続している。通常、基板110の上表面111に1つの半田マスク層113が形成され半田マスク層113はパッド112群を覆わないこととなっている。

【0012】

図5は、封止体130を形成する前のフリップチップキャリア100を示す斜視図である。図2および図5を参照して、独立パッドマスク120群は、パッド112群を覆っている。ここで、独立パッドマスク120群は、パッド112群の上にそれぞれ固定され、互いに直接接続しない。各独立パッドマスク120は、対応するパッド112と貼り付ける感光性粘着層121および感光性粘着層121上に形成される透光性の取放素子122を有する。

【0013】

感光性粘着層121は、UV光線に当てられると周知のウェハダイシングテープの表面粘着層のように老化して粘着性が喪失するという特性を持ち、例えば、アクリル樹脂(acrylic resin)は、パッド112群だけを覆って基板110の上表面111を全面的に覆うことではない。

【0014】

取放素子122群は、透明特性を持ち、目視で全透明と半透明であり、プロピレンオキシド(PO:propylene oxide)、ポリ塩化ビニル(PVC:polyvinyl chloride)、あるいは、ポリエチレンテレフタレート(PET、polyethylene terephthalate)などの材質からなってもよい。

本実施形態において、取放素子122群は、熱硬化性電気絶縁ポストであってもよい。これにより、取放素子122群と感光性粘着層121群との特性変化は、形成プロセスにおいて個別に処理することができる。取放素子122群が熱硬化成形されるとき、感光性粘着層121群は依然に粘着性を有し、感光性粘着層121群が光線に当てられるときに粘着性を失い、取放素子122群は依然に良好な固体形状を保持して取放方式で引出されることが便利となる。取放素子122群を引出した後に残るスペースは、封止体130を構成する金属ポスト置き穴として利用することができるため、従来のMPS−C2型半導体パッケージに起きる半田材ブリッジとパッケージ反りの問題が解決できる。また、独立パッドマスク120群の高さは、製作予定のMPS−C2型半導体パッケージの金属ポストの高さよりも高くなってもよい。

【0015】

具体的に、フリップチップキャリア100は、さらに充填粒子131を混合する封止体130を有する。封止体130は、基板110の上表面111に形成されて独立パッドマスク120群の厚さTよりも薄い厚さを有することにより、各取放素子122は封止体130の外に露出する取放表面123を有するようにさせる。

本実施形態において、充填粒子群は無機粒子であってもよい。例えば、シリカ粒子は、封止体130の熱膨張係数を調和することに利用されて封止体130とフリップチップ接合のチップとの両者の熱膨張係数の差が無いようにする。封止体130の熱膨張係数は、フリップチップ接合のチップの熱膨張係数と基板110の熱膨張係数との間に介し、かつ、フリップチップ接合のチップの熱膨張係数に接近することが好ましい。封止体130は、熱硬化特性を持ってもよい。封止体130は、フリップチップキャリア100の製作が完成する時に形成することができ、あるいは、フリップチップキャリア100のMPS−C2実装過程中に形成することも可能である。

【0016】

図3A〜図3Eに示すよう、本実施形態では、さらにフリップチップキャリア100の形成方法を開示する。図3Aに示すよう、先ず、基板110を提供し、基板110の上表面111にパッド112群を設置して半田マスク層113を形成する。図3Bおよび図4に示すよう、基板110の上表面111にカバー310を設置する。カバー310は、複数の空孔311を有し、各空孔311をパッド112に位置合わせし、かつ、パッド112が露出するようにする。ここで、カバー310は、露光と現像プロセスを経て形成したフォトレジスト材料、あるいは、プリント板である。図3Cに示すよう、プリント方式を用いて空孔311群の内に位置するパッド112群上に感光性粘着層121をコーティングして、かつプリベーキングによって少々固める。そして、図3Dに示すよう、カバー310の空孔311群の内には取放素子122の硬化前の熱硬化性樹脂が満ちるように第二回プリント方式でコーティングして、かつ、プリベーキングによって少々固める。図3Eおよび図5に示すよう、カバー310を除去した後、再度ベーキングによって上述の熱硬化性樹脂は硬化して取放素子122群になって基板110上に設置される複数の独立パッドマスク120を構成する。

最後に、図6に示すように、コーティングヘッド320を利用して充填粒子131を混合する封止体130を提供する。封止体130は、基板110の上表面111に形成されて独立パッドマスク120群の厚さよりも薄い厚さを有する。これにより、各取放素子122は、封止体130の外に露出する取放表面123を有することになる。封止体130は、B−ステージ、あるいは、半硬化特性をもってもよく、プリベーキングによって一部硬化させて稠密状、あるいはゼリーのような凝固状になる。

【0017】

図7A〜図7Cに示すよう、本実施形態では、さらにフリップチップキャリア100を応用する半導体実装方法を開示する。先ず、図7Aに示すよう、発光装置330で適当波長の光線、例えばUV光線を提供して基板110を照らし、光線が取放素子122群を透過して感光性粘着層121群を照らすことにより、感光性粘着層121は老化して粘着性を失うことになる。図7Bおよび図8に示すように、取放ノズル340を利用して独立パッドマスク120の取放表面123に真空吸付力を提供し、取放方式で取放素子122群を引出してパッド112群を露出させる。その時、独立パッドマスク120群が引出された後の位置は、封止体130の金属ポスト置き穴132になる。このステップの利点は、独立パッドマスク120群が光線に当てられた後に機械的に引出されることによって金属ポスト置き穴132群が形成され、パッド112群を損傷することがなく、封止体130を汚染することない。例えば、フォトレジスト除去液による汚染が生じない。また、封止体130は、感光性と高流動性という特性をもつ必要がないため、実装材料のコストを低減でき、かつパッド112群の露出表面もかなりきれいである。

【0018】

図7Cに示すよう、チップ200を封止体130上に設置する。チップ200は、複数の金属ポスト210を有する。各金属ポスト210の下方の断面に半田材220を形成し、リフロー方式を利用して金属ポスト210群をパッド112群に接合する。ここで、様々な集積回路がチップ200の主動面に形成され、複数のボンディングパッド230は、集積回路の外接用として主動面上に設置され、かつ、1つの保護層240の外に露出される。金属ポスト210群は、メッキあるいは植球方式を用いてボンディングパッド230群の上に設置することができ、ボンディングパッド230群に直接に接合され、あるいは、ボンディングパッド230群と金属ポスト210群との間に図示しないアンダーバンプメタル層を設置することもできる。図9に示すよう、リフローする前、先に半田材220をパッド112群に接触させ、金属ポスト210群を対応する金属ポスト置き穴132群の内に置くことで、チップ200は基板110へ向かって過度に押されても、半田材220が溢れて相隣の金属ポスト210を汚染することがない。

なお、チップ200を設置した後、さらに加熱方式で封止体130を熱硬化することにより、図10に示すMPS−C2型半導体パッケージを製造することができる。このようなMPS−C2型半導体パッケージは、薄型化の設計ができるだけでなく、パッケージ反りの問題も解決できる。また、半田材220による金属ポスト210同士のブリッジが発生しない。従って、本実施形態の特徴では、独立パッドマスク120群を利用してMPS−C2型半導体パッケージにおいて充填粒子131を混合する低コストの封止体130を使用することが可能であり、封止体130の充填が困難にならず、かつ充填粒子131は捕えられて半田材220とパッド112群との間に隔てられることで起きる半田付け不良の問題が防止できる。

なお、封止体130は、ドロップキャスティング方式で形成してもよい。

【0019】

以上、本発明をその好適な実施例に基づいて説明したが、本発明の技術的範囲は特許請求の範囲の記載に基づいて特定される。特許請求の範囲の記載に基づいて、本発明の趣旨を逸脱しないどんな変更や修正も本発明の技術的範囲に属する。

【符号の説明】

【0020】

1・・・半導体パッケージ

10・・・基板

12・・・パッド

20・・・チップ

21・・・金属ポスト

22・・・半田材

23・・・ボンディングパッド

30・・・封止体

100・・・独立パッドマスクを有するフリップチップキャリア

110・・・基板

111・・・上表面

112・・・パッド

113・・・半田マスク層

120・・・独立パッドマスク

121・・・感光性粘着層

122・・・取放素子

123・・・取放表面

130・・・封止体

131・・・充填粒子

132・・・金属ポスト置き穴

200・・・チップ

210・・・金属ポスト

220・・・半田材

230・・・ボンディングパッド

240・・・保護層

310・・・カバー

311・・・空孔

320・・・コーティングヘッド

330・・・発光装置

340・・・取放ノズル

T・・・封止体の厚さ

【技術分野】

【0001】

本発明は、半導体実装技術に関し、特に独立パッドマスクを有するフリップチップキャリア、及びこれを用いた半導体実装方法に関するものである。

【背景技術】

【0002】

「金属ポストの半田付けによるチップ接合」(以下「MPS−C2(Metal Post Solder−Chip Connection)」という。)は、先進のフリップチップ接合技術である。従来のフリップチップ接合は、基板と接合するバンプとしてチップの主動面上に複数の半田ボールを設置し、主動面を基板に向かせるようにチップを引っくり返し、リフローによって接合し、半田ボールを基板の対応パッド上に電気的および機械的に接合することになる。但し、バンプ同士の間隔は段々小さい設計となる場合、半田ボールは円弧状の側壁を有するので、隣接する半田ボールが容易に半田付けにより接合されるため、半田ボールのフリップチップ接合では間隔が100μmより小さい微細ピッチバンプ接合の要求を満足することができない。

一方、特許文献1のバンプ構造、バンプの形成方法、実装接続体によると、フリップチップ接合用のバンプとして従来の半田ボールを代替して金属ポストを採用し、半田材で金属ポストを基板上に接合する。リフローによって半田材は溶融し、金属ポストはリフロー温度よりも高い融点を有してポスト状が確保できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平09−097791号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1に記載の技術により、チップバンプの間隔として金属ポストは縮小しても従来の半田ボールのブリッジ短絡現象が起きない。図1に示すように、従来の典型的な「金属ポストの半田付けによるチップ接合」(MPS−C2)の半導体パッケージ1は、主に基板10、チップ20および封止体30を含む。複数の金属ポスト21は、チップ20のハンダパッド23上に設置され、そして、半田材22で基板10上に位置する複数のパッド12に接合される。封止体30は、アンダーフィル樹脂であって良好な流動性を有することでチップ20と基板10との隙間に充填することができる。チップ20と基板10との両者の熱膨張係数の差、あるいは/及び、封止体30の硬化収縮により、半導体パッケージ1ではパッケージ反りの問題が容易に発生する。また、金属ポスト21群同士の間隔は段々小さくなると、隣接する金属ポスト21の下方の半田材22はリフローによって接合され易く、半田材22のブリッジに起因して隣接する金属ポスト21の短絡が問題となる。

【0005】

上述問題を解決するため、本発明の主な目的は、独立パッドマスクを有するフリップチップキャリアおよびこれをMPS−C2に応用する実装方法を提供する。これにより、従来のMPS−C2半導体パッケージに起きる半田材ブリッジとパッケージ反りの問題が解決できる。

【課題を解決するための手段】

【0006】

上述目的を達成するために本発明では、次に述べる技術が提案されている。本発明では、独立パッドマスクを有するフリップチップキャリアは、1つの基板と複数の独立パッドマスクとを含む。

基板は、上表面、および、上表面に設置される複数のパッドを有する。

独立パッドマスク群は、パッド群を覆う。各独立パッドマスクは、対応するパッドと貼り付ける感光性粘着層、及び、感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有する。

【0007】

本発明はさらに上述独立パッドマスクを有するフリップチップキャリアを使用する半導体実装方法を開示する。

上述の目的を達成するために本発明では、さらに他の技術を採用する。

フリップチップキャリアにおいて、さらに充填粒子を混合する封止体を含む。封止体は、基板の上表面に形成されて独立パッドマスク群の厚さよりも薄い厚さを有することにより、各取放素子は封止体の外に露出する取放表面を有する。

フリップチップキャリアにおいて、充填粒子群は無機粒子であってもよい。

フリップチップキャリアにおいて、封止体は熱硬化性であってもよい。

フリップチップキャリアにおいて、取放素子群は熱硬化性電気絶縁ポストであってもよい。

【図面の簡単な説明】

【0008】

【図1】従来のMPS−C2半導体パッケージを示す断面図である。

【図2】本発明の一実施形態による独立パッドマスクを有するフリップチップキャリアを示す断面図である。

【図3A】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3B】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3C】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3D】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図3E】本発明の一実施形態によるフリップチップキャリアを提供するプロセスを示す断面図である。

【図4】図3B製作過程に対応するステップの素子を示す斜視図である。

【図5】図3E製作過程に対応するステップの素子を示す斜視図である。

【図6】本発明の一実施形態による独立パッドマスクを有するフリップチップキャリア上に形成される封止体の素子を示す斜視図である。

【図7A】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図7B】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図7C】本発明の一実施形態によるフリップチップキャリアを使用する半導体実装プロセスを示す断面図である。

【図8】図7B製作過程に対応するステップの素子を示す斜視図である。

【図9】図7C製作過程に対応するステップの一部を拡大した状態を示す断面図である。

【図10】本発明の一実施形態によるフリップチップキャリアを使用するMPS−C2型半導体パッケージを示す断面図である。

【発明を実施するための形態】

【0009】

以下、添付された図面を参照して、本発明の実施形態について説明する。しかしながら、図面においては、本発明の基本構成や実施方法を示す概略図であり、本発明に係る要素と構成だけを示し、実際に実施する部材の個数、外形、寸法を一定の比率で記載するものではなく、説明の便宜及び明確性のために簡略または誇張されている。一方、実際に使われる個数、外形、寸法は様々な設計に応じ、部材の配置はより複雑になる可能性がある。

【0010】

(一実施形態)

図2に示すように、本発明の一実施例による独立パッドマスクを有するフリップチップキャリア100は、主に基板110と複数の独立パッドマスク(Individual Pad Mask:IPM)120とを含む。

【0011】

基板110は、上表面111と上表面111に設置される複数のパッド112とを有する。基板110は、プリント回路基板、セラミック回路基板、あるいは、半導体インタポーザであってもよい。基板110の内部には、図示しない適当な線路構造やメッキスルーホール(Plated Through Hole:PTH)が設けられ、外接用としてパッド112群と電気的に接続している。通常、基板110の上表面111に1つの半田マスク層113が形成され半田マスク層113はパッド112群を覆わないこととなっている。

【0012】

図5は、封止体130を形成する前のフリップチップキャリア100を示す斜視図である。図2および図5を参照して、独立パッドマスク120群は、パッド112群を覆っている。ここで、独立パッドマスク120群は、パッド112群の上にそれぞれ固定され、互いに直接接続しない。各独立パッドマスク120は、対応するパッド112と貼り付ける感光性粘着層121および感光性粘着層121上に形成される透光性の取放素子122を有する。

【0013】

感光性粘着層121は、UV光線に当てられると周知のウェハダイシングテープの表面粘着層のように老化して粘着性が喪失するという特性を持ち、例えば、アクリル樹脂(acrylic resin)は、パッド112群だけを覆って基板110の上表面111を全面的に覆うことではない。

【0014】

取放素子122群は、透明特性を持ち、目視で全透明と半透明であり、プロピレンオキシド(PO:propylene oxide)、ポリ塩化ビニル(PVC:polyvinyl chloride)、あるいは、ポリエチレンテレフタレート(PET、polyethylene terephthalate)などの材質からなってもよい。

本実施形態において、取放素子122群は、熱硬化性電気絶縁ポストであってもよい。これにより、取放素子122群と感光性粘着層121群との特性変化は、形成プロセスにおいて個別に処理することができる。取放素子122群が熱硬化成形されるとき、感光性粘着層121群は依然に粘着性を有し、感光性粘着層121群が光線に当てられるときに粘着性を失い、取放素子122群は依然に良好な固体形状を保持して取放方式で引出されることが便利となる。取放素子122群を引出した後に残るスペースは、封止体130を構成する金属ポスト置き穴として利用することができるため、従来のMPS−C2型半導体パッケージに起きる半田材ブリッジとパッケージ反りの問題が解決できる。また、独立パッドマスク120群の高さは、製作予定のMPS−C2型半導体パッケージの金属ポストの高さよりも高くなってもよい。

【0015】

具体的に、フリップチップキャリア100は、さらに充填粒子131を混合する封止体130を有する。封止体130は、基板110の上表面111に形成されて独立パッドマスク120群の厚さTよりも薄い厚さを有することにより、各取放素子122は封止体130の外に露出する取放表面123を有するようにさせる。

本実施形態において、充填粒子群は無機粒子であってもよい。例えば、シリカ粒子は、封止体130の熱膨張係数を調和することに利用されて封止体130とフリップチップ接合のチップとの両者の熱膨張係数の差が無いようにする。封止体130の熱膨張係数は、フリップチップ接合のチップの熱膨張係数と基板110の熱膨張係数との間に介し、かつ、フリップチップ接合のチップの熱膨張係数に接近することが好ましい。封止体130は、熱硬化特性を持ってもよい。封止体130は、フリップチップキャリア100の製作が完成する時に形成することができ、あるいは、フリップチップキャリア100のMPS−C2実装過程中に形成することも可能である。

【0016】

図3A〜図3Eに示すよう、本実施形態では、さらにフリップチップキャリア100の形成方法を開示する。図3Aに示すよう、先ず、基板110を提供し、基板110の上表面111にパッド112群を設置して半田マスク層113を形成する。図3Bおよび図4に示すよう、基板110の上表面111にカバー310を設置する。カバー310は、複数の空孔311を有し、各空孔311をパッド112に位置合わせし、かつ、パッド112が露出するようにする。ここで、カバー310は、露光と現像プロセスを経て形成したフォトレジスト材料、あるいは、プリント板である。図3Cに示すよう、プリント方式を用いて空孔311群の内に位置するパッド112群上に感光性粘着層121をコーティングして、かつプリベーキングによって少々固める。そして、図3Dに示すよう、カバー310の空孔311群の内には取放素子122の硬化前の熱硬化性樹脂が満ちるように第二回プリント方式でコーティングして、かつ、プリベーキングによって少々固める。図3Eおよび図5に示すよう、カバー310を除去した後、再度ベーキングによって上述の熱硬化性樹脂は硬化して取放素子122群になって基板110上に設置される複数の独立パッドマスク120を構成する。

最後に、図6に示すように、コーティングヘッド320を利用して充填粒子131を混合する封止体130を提供する。封止体130は、基板110の上表面111に形成されて独立パッドマスク120群の厚さよりも薄い厚さを有する。これにより、各取放素子122は、封止体130の外に露出する取放表面123を有することになる。封止体130は、B−ステージ、あるいは、半硬化特性をもってもよく、プリベーキングによって一部硬化させて稠密状、あるいはゼリーのような凝固状になる。

【0017】

図7A〜図7Cに示すよう、本実施形態では、さらにフリップチップキャリア100を応用する半導体実装方法を開示する。先ず、図7Aに示すよう、発光装置330で適当波長の光線、例えばUV光線を提供して基板110を照らし、光線が取放素子122群を透過して感光性粘着層121群を照らすことにより、感光性粘着層121は老化して粘着性を失うことになる。図7Bおよび図8に示すように、取放ノズル340を利用して独立パッドマスク120の取放表面123に真空吸付力を提供し、取放方式で取放素子122群を引出してパッド112群を露出させる。その時、独立パッドマスク120群が引出された後の位置は、封止体130の金属ポスト置き穴132になる。このステップの利点は、独立パッドマスク120群が光線に当てられた後に機械的に引出されることによって金属ポスト置き穴132群が形成され、パッド112群を損傷することがなく、封止体130を汚染することない。例えば、フォトレジスト除去液による汚染が生じない。また、封止体130は、感光性と高流動性という特性をもつ必要がないため、実装材料のコストを低減でき、かつパッド112群の露出表面もかなりきれいである。

【0018】

図7Cに示すよう、チップ200を封止体130上に設置する。チップ200は、複数の金属ポスト210を有する。各金属ポスト210の下方の断面に半田材220を形成し、リフロー方式を利用して金属ポスト210群をパッド112群に接合する。ここで、様々な集積回路がチップ200の主動面に形成され、複数のボンディングパッド230は、集積回路の外接用として主動面上に設置され、かつ、1つの保護層240の外に露出される。金属ポスト210群は、メッキあるいは植球方式を用いてボンディングパッド230群の上に設置することができ、ボンディングパッド230群に直接に接合され、あるいは、ボンディングパッド230群と金属ポスト210群との間に図示しないアンダーバンプメタル層を設置することもできる。図9に示すよう、リフローする前、先に半田材220をパッド112群に接触させ、金属ポスト210群を対応する金属ポスト置き穴132群の内に置くことで、チップ200は基板110へ向かって過度に押されても、半田材220が溢れて相隣の金属ポスト210を汚染することがない。

なお、チップ200を設置した後、さらに加熱方式で封止体130を熱硬化することにより、図10に示すMPS−C2型半導体パッケージを製造することができる。このようなMPS−C2型半導体パッケージは、薄型化の設計ができるだけでなく、パッケージ反りの問題も解決できる。また、半田材220による金属ポスト210同士のブリッジが発生しない。従って、本実施形態の特徴では、独立パッドマスク120群を利用してMPS−C2型半導体パッケージにおいて充填粒子131を混合する低コストの封止体130を使用することが可能であり、封止体130の充填が困難にならず、かつ充填粒子131は捕えられて半田材220とパッド112群との間に隔てられることで起きる半田付け不良の問題が防止できる。

なお、封止体130は、ドロップキャスティング方式で形成してもよい。

【0019】

以上、本発明をその好適な実施例に基づいて説明したが、本発明の技術的範囲は特許請求の範囲の記載に基づいて特定される。特許請求の範囲の記載に基づいて、本発明の趣旨を逸脱しないどんな変更や修正も本発明の技術的範囲に属する。

【符号の説明】

【0020】

1・・・半導体パッケージ

10・・・基板

12・・・パッド

20・・・チップ

21・・・金属ポスト

22・・・半田材

23・・・ボンディングパッド

30・・・封止体

100・・・独立パッドマスクを有するフリップチップキャリア

110・・・基板

111・・・上表面

112・・・パッド

113・・・半田マスク層

120・・・独立パッドマスク

121・・・感光性粘着層

122・・・取放素子

123・・・取放表面

130・・・封止体

131・・・充填粒子

132・・・金属ポスト置き穴

200・・・チップ

210・・・金属ポスト

220・・・半田材

230・・・ボンディングパッド

240・・・保護層

310・・・カバー

311・・・空孔

320・・・コーティングヘッド

330・・・発光装置

340・・・取放ノズル

T・・・封止体の厚さ

【特許請求の範囲】

【請求項1】

上表面および上表面に設置される複数のパッドを有する基板と、

前記複数のパッドを覆う複数の独立パッドマスクと、

を備え、

それぞれの前記独立パッドマスクは、対応する前記パッドと貼り付ける感光性粘着層、及び、前記感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有することを特徴とするフリップチップキャリア。

【請求項2】

さらに充填粒子を混合する封止体を備え、

前記封止体は、前記基板の前記上表面に形成され、前記独立パッドマスクの厚さよりも薄い厚さを有することにより、それぞれの前記取放素子が前記封止体の外に露出する取放表面を有することを特徴とする請求項1記載のフリップチップキャリア。

【請求項3】

前記充填粒子は、無機粒子であることを特徴とする請求項2記載のフリップチップキャリア。

【請求項4】

前記封止体は、熱硬化性であることを特徴とする請求項2記載のフリップチップキャリア。

【請求項5】

前記取放素子は、熱硬化性電気絶縁ポストであることを特徴とする請求項1記載のフリップチップキャリア。

【請求項6】

上表面および前記上表面に設置される複数のパッドを有する基板と、前記複数のパッドを覆い、対応する前記パッドと貼り付ける感光性粘着層、及び、前記感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有する複数の独立パッドマスクとを備えるフリップチップキャリアを提供するステップと、

前記基板の前記上表面に形成され、充填粒子を混合する封止体であって、前記独立パッドマスクの厚さよりも薄い厚さを有することにより、前記取放素子が当該封止体の外に露出する取放表面を有する封止体を形成するステップと、

前記感光性粘着層に粘着性を喪失させる光線を前記取放素子を透過して前記感光性粘着層に照らすステップと、

前記パッドを露出させるよう前記取放素子を抜き取るステップと、

複数の金属ポストを有するチップを前記封止体上に設置するステップと、

半田材で前記金属ポストを前記パッドに接合するステップと、

を含むことを特徴とする半導体実装方法。

【請求項7】

前記封止体は、ドロップキャスティング方式で形成されることを特徴とする請求項6記載の半導体実装方法。

【請求項8】

前記充填粒子は、無機粒子であることを特徴とする請求項6記載の半導体実装方法。

【請求項9】

前記チップを設置した後、さらに加熱方式で前記封止体を熱硬化することを特徴とする請求項6記載の半導体実装方法。

【請求項10】

前記取放素子は、熱硬化性電気絶縁ポストであり、カバーの空孔群の内にプリントしてベーキングによって成形されることを特徴とする請求項6記載の半導体実装方法。

【請求項1】

上表面および上表面に設置される複数のパッドを有する基板と、

前記複数のパッドを覆う複数の独立パッドマスクと、

を備え、

それぞれの前記独立パッドマスクは、対応する前記パッドと貼り付ける感光性粘着層、及び、前記感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有することを特徴とするフリップチップキャリア。

【請求項2】

さらに充填粒子を混合する封止体を備え、

前記封止体は、前記基板の前記上表面に形成され、前記独立パッドマスクの厚さよりも薄い厚さを有することにより、それぞれの前記取放素子が前記封止体の外に露出する取放表面を有することを特徴とする請求項1記載のフリップチップキャリア。

【請求項3】

前記充填粒子は、無機粒子であることを特徴とする請求項2記載のフリップチップキャリア。

【請求項4】

前記封止体は、熱硬化性であることを特徴とする請求項2記載のフリップチップキャリア。

【請求項5】

前記取放素子は、熱硬化性電気絶縁ポストであることを特徴とする請求項1記載のフリップチップキャリア。

【請求項6】

上表面および前記上表面に設置される複数のパッドを有する基板と、前記複数のパッドを覆い、対応する前記パッドと貼り付ける感光性粘着層、及び、前記感光性粘着層上に抜き取り可能に設けられる透光性の取放素子を有する複数の独立パッドマスクとを備えるフリップチップキャリアを提供するステップと、

前記基板の前記上表面に形成され、充填粒子を混合する封止体であって、前記独立パッドマスクの厚さよりも薄い厚さを有することにより、前記取放素子が当該封止体の外に露出する取放表面を有する封止体を形成するステップと、

前記感光性粘着層に粘着性を喪失させる光線を前記取放素子を透過して前記感光性粘着層に照らすステップと、

前記パッドを露出させるよう前記取放素子を抜き取るステップと、

複数の金属ポストを有するチップを前記封止体上に設置するステップと、

半田材で前記金属ポストを前記パッドに接合するステップと、

を含むことを特徴とする半導体実装方法。

【請求項7】

前記封止体は、ドロップキャスティング方式で形成されることを特徴とする請求項6記載の半導体実装方法。

【請求項8】

前記充填粒子は、無機粒子であることを特徴とする請求項6記載の半導体実装方法。

【請求項9】

前記チップを設置した後、さらに加熱方式で前記封止体を熱硬化することを特徴とする請求項6記載の半導体実装方法。

【請求項10】

前記取放素子は、熱硬化性電気絶縁ポストであり、カバーの空孔群の内にプリントしてベーキングによって成形されることを特徴とする請求項6記載の半導体実装方法。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【図2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図8】

【図9】

【図10】

【公開番号】特開2013−62469(P2013−62469A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−201597(P2011−201597)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(506292169)力成科技股▲分▼有限公司 (36)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(506292169)力成科技股▲分▼有限公司 (36)

【Fターム(参考)】

[ Back to top ]