フリップチップ実装構造

【課題】フレキシブル基板に半導体素子をフェイスダウンで実装する半導体装置において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めるフリップチップ実装構造を提供する。

【解決手段】半導体素子1とフレキシブル基板10とがバンプ2を介して接合され、半導体素子とフレキシブル基板との間が封止樹脂9により封止されたフリップチップ実装構造において、フレキシブル基板には、半導体素子と対抗する面の一部にランド3が形成され、フレキシブル基板は、バンプと接合されることで画定される領域の内側で屈曲し、このときのランドと半導体素子との間隔が、バンプと接合後の半導体素子とランドとの間隔よりも狭小になっている。

【解決手段】半導体素子1とフレキシブル基板10とがバンプ2を介して接合され、半導体素子とフレキシブル基板との間が封止樹脂9により封止されたフリップチップ実装構造において、フレキシブル基板には、半導体素子と対抗する面の一部にランド3が形成され、フレキシブル基板は、バンプと接合されることで画定される領域の内側で屈曲し、このときのランドと半導体素子との間隔が、バンプと接合後の半導体素子とランドとの間隔よりも狭小になっている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造に関するものである。

【背景技術】

【0002】

近年、デジタルカメラや携帯電話に代表される電子機器の小型化・高性能化が進んでいる。この小型化・高性能化に対応するため、機器内に搭載される半導体パッケージの実装形態として、フリップチップ実装型のパッケージ構造が多く採用されている。

【0003】

フリップチップ実装では、半導体素子と配線基板とをバンプを介して直接電気的に接合する。そのためワイヤーボンディングが不要となることで高周波特性に優れ、高速伝送特性が向上し、電子機器の高性能化に寄与している。ワイヤーボンディングがなくなる分、配線基板側のボンディングパッドを半導体素子の下側に設置するので、半導体パッケージの小型化が可能となり、そのため実装面積も低減できる。

【0004】

半導体素子の樹脂による保護も、半導体素子全体をモールドする方法と異なり、フリップチップ実装では半導体素子と配線基板の間を封止樹脂で封止する構造であるため、薄型化を可能にしている。

【0005】

このフリップチップ実装の一つとして、半導体素子をフレキシブル基板にフリップチップ実装する技術が知られている。半導体素子をフレキシブル基板にフリップチップ実装するTAB(Tape Automated Bonding)やCOF(Chip On Film)と呼ばれる実装技術は、主に液晶ドライバやICタグの実装などに用いられている。

【0006】

さらに近年では、デジタルカメラなどに搭載されるイメージセンサユニットを、このTABやCOFの実装技術を用いて高周波特性を向上させつつ薄型化し、筐体サイズを小型・薄型化する実装構造も開発されている。

【0007】

一方、近年の半導体素子の高集積化と消費電力の増大に伴い、その発熱量の増加が問題となっている。イメージセンサにおいては、撮像素子の発熱により出力信号にノイズが発生し、撮影した画像が劣化するという問題が発生する。

【0008】

従来、フリップチップ実装を含め一般的な半導体パッケージの放熱手段として、ヒートシンクのような放熱部材を設置して、半導体素子を冷却する方法がある。しかし、デジタルカメラや携帯電話のような、その筐体サイズに制限がある機器内にヒートシンクを設置することは望ましくない。また、ヒートシンクの部材費や設置プロセスが増加し、コストアップに繋がる。

【0009】

このフレキシブル基板にフリップチップ実装した半導体素子の放熱性向上という課題に対し、特許文献1では、画像表示ドライバの半導体素子にダミーバンプを設け、フレキシブル基板に形成された大面積の金属箔と接続し放熱させる方法が提案されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2008−275803号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかし、特許文献1の方法は、放熱性を高めるためには金属箔の面積を大きくする必要があり、その結果フレキシブル基板の面積が大きくなるという課題がある。そのため、筐体サイズの大きいディスプレイなどには有効な方法であるが、小型機器に搭載する場合には不利である。

【0012】

また、画像表示ドライバのような細型の半導体素子と異なり、半導体素子の面積が大きく、ダミーバンプと半導体素子上の発熱源との距離が大きい場合や、発熱源が複数ある場合は、熱が半導体素子全面に拡散するという課題がある。

【0013】

本発明は上記の課題を解決するもので、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めることを目的としている。

【課題を解決するための手段】

【0014】

本発明のフリップチップ実装構造は、半導体素子とフレキシブル基板とがバンプを介して接合され、前記半導体素子と前記フレキシブル基板との間が封止樹脂により封止されたフリップチップ実装構造において、前記フレキシブル基板には、前記半導体素子と対向する面の一部にランドが形成され、前記フレキシブル基板は、前記バンプと接合されることで画定される領域の内側で屈曲し、このときの前記ランドと前記半導体素子との間隔が、前記バンプと接合後の前記半導体素子と前記ランドとの間隔よりも狭小であることを特徴とする。

【発明の効果】

【0015】

本発明の一態様によれば、フレキシブル基板が屈曲し、半導体素子と対抗する面に設けられたランドが半導体素子の表面に近接または接触することにより、半導体素子の熱がバンプからだけでなく、ランドを介してフレキシブル基板へ伝熱される。これにより、半導体素子の面積が大きい場合や、発熱源が半導体素子上に複数ある場合でも、半導体素子の表面からフレキシブル基板へ伝熱されるため、半導体素子から効率よく放熱することができる。

【0016】

その結果、ヒートシンクなどの放熱部材を設けることなく、半導体素子の放熱特性を向上することができるため、コストダウンが可能になると同時に、フリップチップ実装構造の薄型構造を妨げることがない。

【0017】

また、ランドは、フレキシブル基板の製造時に他の配線と同時に形成することが可能であり、低コストに形成可能である。

【0018】

本発明の別の態様によれば、前記ランドはフレキシブル基板の配線と接続されることにより、配線を介して放熱できるので、新たに放熱用の金属箔などを設ける必要が無く、フレキシブル基板の大型化を防ぐことができる。このとき、ランドと接続される配線はグランド配線のような広面積な配線であれば、より放熱性を高めることができ、かつフレキシブル基板が大型化しない。

【0019】

さらに、本発明の別の態様によれば、フレキシブル基板のバンプと接続されることで画定される領域内にスリットがあるため、フレキシブル基板の屈曲時にバンプに応力が加わることを防止しつつ、ランドを半導体素子の表面に近接させることができる。

【図面の簡単な説明】

【0020】

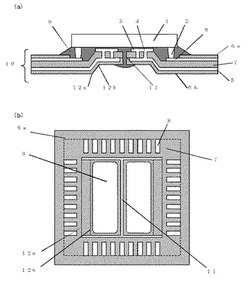

【図1】(a)本発明の実施形態におけるフリップチップ実装構造の断面図である。(b)本発明の実施形態に使用するフレキシブル基板の上面模式図である。

【図2】(a)本発明のフリップチップ実装構造を用いたイメージセンサユニットの断面図である。(b)本発明のフリップチップ実装構造を用いたイメージセンサユニットに使用されるフレキシブル基板の上面模式図である。

【図3】従来のフリップチップ実装構造を示す断面図である。

【発明を実施するための形態】

【0021】

本発明の実施形態を図面に基づいて説明する。

【0022】

[実施形態1]

図1(a)は本発明の実施形態であるフリップチップ実装構造の断面図であり、図1(b)は、本発明の実施形態に使用されるフレキシブル基板の半導体素子搭載部周辺を示す上面図である。

【0023】

半導体素子1とフレキシブル基板10は、バンプ2と接続パッド8を介して電気的に接続され、半導体素子1とフレキシブル基板10との間に形成される空間、およびバンプ2と接続パッド8の周囲は封止樹脂9により封止、保護されている。

さらに、フレキシブル基板10は、屈曲部12a、12bで屈曲することにより、ビア4を介して、グランド配線5と接続されたランド3が半導体素子1の表面に近接している。

なお、ランドは、フレキシブル基板の製造プロセス時に、他の接続用パッドや配線パターンと同時にエッチングで形成される。具体的には、樹脂フィルムをベースとした銅張積層板の接続用パッドや配線パターンが形成される部分に、印刷や露光によりエッチングレジストを形成する。このとき、ランドが形成される部分にもエッジングレジストを形成しておく。その後、銅張積層板をエッチングすることで、接続用パッドや配線パターンと同様に、エッチングレジストで保護された銅がランドとして形成される。従って、フレキシブル基板の製造プロセスに別途ランドを設けるプロセスを加える必要がない。そのため、ランドを形成することによるコストアップがない。

【0024】

このとき、ランド3と半導体素子1とが、バンプと接合後の半導体素子とランドとの間隔より近接して狭小であることにより、半導体素子1で発生した熱はランド3を介してグランド配線へと伝熱される。さらに、ランド3の一部が半導体素子1と接している場合には、より伝熱効率を高めることができる。その結果、半導体素子1は動作時の熱を表面から効率よく放熱できるため、発熱による誤動作などを防止することができる。

【0025】

屈曲部12a、12bは、半導体素子1とフレキシブル基板10を封止樹脂9により封止する工程で形成することができる。具体的には、まず半導体素子1とフレキシブル基板10の間隔に封止樹脂9を注入する。次にフレキシブル基板10の、半導体素子1のバンプ2で画定される領域の内側を、半導体素子1と反対側の面から複数のピン状の突起を有する治具でフレキシブル基板10を押し込み、屈曲部12a、12bを屈曲させる。さらにこの屈曲部12a、12bが屈曲した状態で加熱し、封止樹脂9を硬化させる。結果、屈曲部12a、12bが形成され半導体素子1とランド3を近接、または接触させることが可能になる。

また、このとき、複数の突起を有する治具で加圧することにより、封止樹脂9を少なくとも一本のスリット11(図1では一本)から、半導体素子搭載面の反対側の面へと染み出す。

【0026】

その結果、スリット11の縁部は、フレキシブル基板の半導体素子側とは反対側に染み出した封止樹脂9のアンカー効果により密着強度が高まり、スリット11からの剥離を防止でき、ひいては本発明のフリップチップ実装構造の信頼性を高めることができる。

【0027】

[実施形態2]

図2(a)は本発明の実施形態におけるフリップチップ実装構造を用いたイメージセンサユニットの断面図である。図2(b)は、本発明の実施形態におけるフリップチップ実装構造を用いたイメージセンサに使用されるフレキシブル基板の撮像素子搭載部周辺を示す上面図である。

【0028】

半導体素子として撮像素子101が、受光部102と対向する位置に開口部105が形成されたフレキシブル基板10にフリップチップ実装され、バンプ2と接続パッド8の周囲は封止樹脂9により封止、保護されている。また、撮像素子101を異物や水分から保護するための保護ガラス103が接着剤104により接着され、イメージセンサユニットを構成している。

【0029】

このイメージセンサユニットは、フレキシブル基板10の屈曲部12a、12bで屈曲することにより、ビア4を介して、グランド配線5と接続されたランド3が撮像素子101の表面に近接している。ランド3と撮像素子101とが近接していることにより、撮像素子101で発生した熱はランド3を介してグランド配線5へと伝熱される。さらに、ランド3の一部が撮像素子101と接している場合には、より伝熱効率を高めることができる。その結果、撮像素子101は動作時の熱を効率よく放熱できるため、発熱によって発生する画像信号のノイズを低減することができる。

【0030】

また、このイメージセンサユニットの製造時に、フレキシブル基板10を屈曲させた状態で封止樹脂9を注入すると、余剰な封止樹脂9は、スリット11から毛細管現象により、撮像素子搭載面と反対側の方向へと染み出す。これにより、受光部102へ封止樹脂109が流出することを防止する効果を得ることができる。

【実施例】

【0031】

本発明の効果を確認すべく、シミュレーションを行った。

図3に示す従来のフリップチップ実装構造のモデルと、図1(a)に示す本発明のフリップチップ実装構造のモデルとの半導体素子温度を比較した。図3中、図1と同じ符号は図1と同じ部材を表す。

【0032】

このときの従来のフリップチップ実装構造のモデルサイズを以下に示す。半導体素子のサイズは、5.0×5.0mmで、厚さは0.1mmである。フレキシブル基板と接続されるバンプはAuバンプであり、サイズは0.02×0.02mmで、高さは0.05mmである。

【0033】

バンプの配置は半導体素子の回路上を避け、ペリフェラル状に0.2mmピッチで配置し、バンプ数は96個である。半導体素子とフレキシブル基板の間隔は、0.05mmであり、エポキシ樹脂で封止されている。フレキシブル基板は10.0×10.0mmで、ベースフィルムとカバーフィルムの材質はポリイミドで、厚さはそれぞれ0.025mmである。接続パッドおよびグランド配線を形成するCuの厚さは0.020mmである。

【0034】

次に、本発明のフリップチップ実装構造のモデルサイズを以下に示すが、半導体素子、バンプ、フレキシブル基板のサイズおよび材質は全て従来のフリップチップ実装構造と同じである。従来のフリップチップ実装構造と異なる点は、フレキシブル基板には、半導体素子と対抗する面にランドが形成されている点と、フレキシブル基板がバンプと接合されることで画定される領域の内側で屈曲し、ランドと前記半導体素子との間隔が、バンプの高さよりも狭い点である。

【0035】

ランドの材質はCuで、図1(b)に示すよう2ヶ所に形成され、サイズはそれぞれ3.5×2.0mmで、厚さは他の配線と同様に0.02mmで、ビアを介してグランド配線に接続されている。半導体素子とランドとの間隔は0.003mmであり、エポキシ樹脂で封止されている。

【0036】

周囲温度25℃の条件における、半導体素子の発熱量と定常状態における半導体素子温度のシミュレーション結果を表1に示す。

【表1】

【0037】

シミュレーションの結果によれば、従来のフレキシブル基板にフェイスダウンで実装されたフリップチップ実装構造の半導体素子温度と比較し、本発明のフリップチップ実装構造では半導体素子の温度が低下していることを確認できる。

【0038】

またこのとき、周囲温度25℃における改善効率は、0.10Wでは3.5%、0.15Wでは4.6%、0.20Wでは5.0%であった。

【0039】

以上のように、本発明によれば、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めることができる。

【符号の説明】

【0040】

1 半導体素子

2 バンプ

3 ランド

4 ビア

5 グランド配線

6a、6b カバーフィルム

7 ベースフィルム

8 接続パッド

9 封止樹脂

10 フレキシブル基板

11 スリット

12a、12b 屈曲部

101 撮像素子

102 受光部

103 保護ガラス

104 接着剤

105 開口部

【技術分野】

【0001】

本発明は、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造に関するものである。

【背景技術】

【0002】

近年、デジタルカメラや携帯電話に代表される電子機器の小型化・高性能化が進んでいる。この小型化・高性能化に対応するため、機器内に搭載される半導体パッケージの実装形態として、フリップチップ実装型のパッケージ構造が多く採用されている。

【0003】

フリップチップ実装では、半導体素子と配線基板とをバンプを介して直接電気的に接合する。そのためワイヤーボンディングが不要となることで高周波特性に優れ、高速伝送特性が向上し、電子機器の高性能化に寄与している。ワイヤーボンディングがなくなる分、配線基板側のボンディングパッドを半導体素子の下側に設置するので、半導体パッケージの小型化が可能となり、そのため実装面積も低減できる。

【0004】

半導体素子の樹脂による保護も、半導体素子全体をモールドする方法と異なり、フリップチップ実装では半導体素子と配線基板の間を封止樹脂で封止する構造であるため、薄型化を可能にしている。

【0005】

このフリップチップ実装の一つとして、半導体素子をフレキシブル基板にフリップチップ実装する技術が知られている。半導体素子をフレキシブル基板にフリップチップ実装するTAB(Tape Automated Bonding)やCOF(Chip On Film)と呼ばれる実装技術は、主に液晶ドライバやICタグの実装などに用いられている。

【0006】

さらに近年では、デジタルカメラなどに搭載されるイメージセンサユニットを、このTABやCOFの実装技術を用いて高周波特性を向上させつつ薄型化し、筐体サイズを小型・薄型化する実装構造も開発されている。

【0007】

一方、近年の半導体素子の高集積化と消費電力の増大に伴い、その発熱量の増加が問題となっている。イメージセンサにおいては、撮像素子の発熱により出力信号にノイズが発生し、撮影した画像が劣化するという問題が発生する。

【0008】

従来、フリップチップ実装を含め一般的な半導体パッケージの放熱手段として、ヒートシンクのような放熱部材を設置して、半導体素子を冷却する方法がある。しかし、デジタルカメラや携帯電話のような、その筐体サイズに制限がある機器内にヒートシンクを設置することは望ましくない。また、ヒートシンクの部材費や設置プロセスが増加し、コストアップに繋がる。

【0009】

このフレキシブル基板にフリップチップ実装した半導体素子の放熱性向上という課題に対し、特許文献1では、画像表示ドライバの半導体素子にダミーバンプを設け、フレキシブル基板に形成された大面積の金属箔と接続し放熱させる方法が提案されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2008−275803号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

しかし、特許文献1の方法は、放熱性を高めるためには金属箔の面積を大きくする必要があり、その結果フレキシブル基板の面積が大きくなるという課題がある。そのため、筐体サイズの大きいディスプレイなどには有効な方法であるが、小型機器に搭載する場合には不利である。

【0012】

また、画像表示ドライバのような細型の半導体素子と異なり、半導体素子の面積が大きく、ダミーバンプと半導体素子上の発熱源との距離が大きい場合や、発熱源が複数ある場合は、熱が半導体素子全面に拡散するという課題がある。

【0013】

本発明は上記の課題を解決するもので、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めることを目的としている。

【課題を解決するための手段】

【0014】

本発明のフリップチップ実装構造は、半導体素子とフレキシブル基板とがバンプを介して接合され、前記半導体素子と前記フレキシブル基板との間が封止樹脂により封止されたフリップチップ実装構造において、前記フレキシブル基板には、前記半導体素子と対向する面の一部にランドが形成され、前記フレキシブル基板は、前記バンプと接合されることで画定される領域の内側で屈曲し、このときの前記ランドと前記半導体素子との間隔が、前記バンプと接合後の前記半導体素子と前記ランドとの間隔よりも狭小であることを特徴とする。

【発明の効果】

【0015】

本発明の一態様によれば、フレキシブル基板が屈曲し、半導体素子と対抗する面に設けられたランドが半導体素子の表面に近接または接触することにより、半導体素子の熱がバンプからだけでなく、ランドを介してフレキシブル基板へ伝熱される。これにより、半導体素子の面積が大きい場合や、発熱源が半導体素子上に複数ある場合でも、半導体素子の表面からフレキシブル基板へ伝熱されるため、半導体素子から効率よく放熱することができる。

【0016】

その結果、ヒートシンクなどの放熱部材を設けることなく、半導体素子の放熱特性を向上することができるため、コストダウンが可能になると同時に、フリップチップ実装構造の薄型構造を妨げることがない。

【0017】

また、ランドは、フレキシブル基板の製造時に他の配線と同時に形成することが可能であり、低コストに形成可能である。

【0018】

本発明の別の態様によれば、前記ランドはフレキシブル基板の配線と接続されることにより、配線を介して放熱できるので、新たに放熱用の金属箔などを設ける必要が無く、フレキシブル基板の大型化を防ぐことができる。このとき、ランドと接続される配線はグランド配線のような広面積な配線であれば、より放熱性を高めることができ、かつフレキシブル基板が大型化しない。

【0019】

さらに、本発明の別の態様によれば、フレキシブル基板のバンプと接続されることで画定される領域内にスリットがあるため、フレキシブル基板の屈曲時にバンプに応力が加わることを防止しつつ、ランドを半導体素子の表面に近接させることができる。

【図面の簡単な説明】

【0020】

【図1】(a)本発明の実施形態におけるフリップチップ実装構造の断面図である。(b)本発明の実施形態に使用するフレキシブル基板の上面模式図である。

【図2】(a)本発明のフリップチップ実装構造を用いたイメージセンサユニットの断面図である。(b)本発明のフリップチップ実装構造を用いたイメージセンサユニットに使用されるフレキシブル基板の上面模式図である。

【図3】従来のフリップチップ実装構造を示す断面図である。

【発明を実施するための形態】

【0021】

本発明の実施形態を図面に基づいて説明する。

【0022】

[実施形態1]

図1(a)は本発明の実施形態であるフリップチップ実装構造の断面図であり、図1(b)は、本発明の実施形態に使用されるフレキシブル基板の半導体素子搭載部周辺を示す上面図である。

【0023】

半導体素子1とフレキシブル基板10は、バンプ2と接続パッド8を介して電気的に接続され、半導体素子1とフレキシブル基板10との間に形成される空間、およびバンプ2と接続パッド8の周囲は封止樹脂9により封止、保護されている。

さらに、フレキシブル基板10は、屈曲部12a、12bで屈曲することにより、ビア4を介して、グランド配線5と接続されたランド3が半導体素子1の表面に近接している。

なお、ランドは、フレキシブル基板の製造プロセス時に、他の接続用パッドや配線パターンと同時にエッチングで形成される。具体的には、樹脂フィルムをベースとした銅張積層板の接続用パッドや配線パターンが形成される部分に、印刷や露光によりエッチングレジストを形成する。このとき、ランドが形成される部分にもエッジングレジストを形成しておく。その後、銅張積層板をエッチングすることで、接続用パッドや配線パターンと同様に、エッチングレジストで保護された銅がランドとして形成される。従って、フレキシブル基板の製造プロセスに別途ランドを設けるプロセスを加える必要がない。そのため、ランドを形成することによるコストアップがない。

【0024】

このとき、ランド3と半導体素子1とが、バンプと接合後の半導体素子とランドとの間隔より近接して狭小であることにより、半導体素子1で発生した熱はランド3を介してグランド配線へと伝熱される。さらに、ランド3の一部が半導体素子1と接している場合には、より伝熱効率を高めることができる。その結果、半導体素子1は動作時の熱を表面から効率よく放熱できるため、発熱による誤動作などを防止することができる。

【0025】

屈曲部12a、12bは、半導体素子1とフレキシブル基板10を封止樹脂9により封止する工程で形成することができる。具体的には、まず半導体素子1とフレキシブル基板10の間隔に封止樹脂9を注入する。次にフレキシブル基板10の、半導体素子1のバンプ2で画定される領域の内側を、半導体素子1と反対側の面から複数のピン状の突起を有する治具でフレキシブル基板10を押し込み、屈曲部12a、12bを屈曲させる。さらにこの屈曲部12a、12bが屈曲した状態で加熱し、封止樹脂9を硬化させる。結果、屈曲部12a、12bが形成され半導体素子1とランド3を近接、または接触させることが可能になる。

また、このとき、複数の突起を有する治具で加圧することにより、封止樹脂9を少なくとも一本のスリット11(図1では一本)から、半導体素子搭載面の反対側の面へと染み出す。

【0026】

その結果、スリット11の縁部は、フレキシブル基板の半導体素子側とは反対側に染み出した封止樹脂9のアンカー効果により密着強度が高まり、スリット11からの剥離を防止でき、ひいては本発明のフリップチップ実装構造の信頼性を高めることができる。

【0027】

[実施形態2]

図2(a)は本発明の実施形態におけるフリップチップ実装構造を用いたイメージセンサユニットの断面図である。図2(b)は、本発明の実施形態におけるフリップチップ実装構造を用いたイメージセンサに使用されるフレキシブル基板の撮像素子搭載部周辺を示す上面図である。

【0028】

半導体素子として撮像素子101が、受光部102と対向する位置に開口部105が形成されたフレキシブル基板10にフリップチップ実装され、バンプ2と接続パッド8の周囲は封止樹脂9により封止、保護されている。また、撮像素子101を異物や水分から保護するための保護ガラス103が接着剤104により接着され、イメージセンサユニットを構成している。

【0029】

このイメージセンサユニットは、フレキシブル基板10の屈曲部12a、12bで屈曲することにより、ビア4を介して、グランド配線5と接続されたランド3が撮像素子101の表面に近接している。ランド3と撮像素子101とが近接していることにより、撮像素子101で発生した熱はランド3を介してグランド配線5へと伝熱される。さらに、ランド3の一部が撮像素子101と接している場合には、より伝熱効率を高めることができる。その結果、撮像素子101は動作時の熱を効率よく放熱できるため、発熱によって発生する画像信号のノイズを低減することができる。

【0030】

また、このイメージセンサユニットの製造時に、フレキシブル基板10を屈曲させた状態で封止樹脂9を注入すると、余剰な封止樹脂9は、スリット11から毛細管現象により、撮像素子搭載面と反対側の方向へと染み出す。これにより、受光部102へ封止樹脂109が流出することを防止する効果を得ることができる。

【実施例】

【0031】

本発明の効果を確認すべく、シミュレーションを行った。

図3に示す従来のフリップチップ実装構造のモデルと、図1(a)に示す本発明のフリップチップ実装構造のモデルとの半導体素子温度を比較した。図3中、図1と同じ符号は図1と同じ部材を表す。

【0032】

このときの従来のフリップチップ実装構造のモデルサイズを以下に示す。半導体素子のサイズは、5.0×5.0mmで、厚さは0.1mmである。フレキシブル基板と接続されるバンプはAuバンプであり、サイズは0.02×0.02mmで、高さは0.05mmである。

【0033】

バンプの配置は半導体素子の回路上を避け、ペリフェラル状に0.2mmピッチで配置し、バンプ数は96個である。半導体素子とフレキシブル基板の間隔は、0.05mmであり、エポキシ樹脂で封止されている。フレキシブル基板は10.0×10.0mmで、ベースフィルムとカバーフィルムの材質はポリイミドで、厚さはそれぞれ0.025mmである。接続パッドおよびグランド配線を形成するCuの厚さは0.020mmである。

【0034】

次に、本発明のフリップチップ実装構造のモデルサイズを以下に示すが、半導体素子、バンプ、フレキシブル基板のサイズおよび材質は全て従来のフリップチップ実装構造と同じである。従来のフリップチップ実装構造と異なる点は、フレキシブル基板には、半導体素子と対抗する面にランドが形成されている点と、フレキシブル基板がバンプと接合されることで画定される領域の内側で屈曲し、ランドと前記半導体素子との間隔が、バンプの高さよりも狭い点である。

【0035】

ランドの材質はCuで、図1(b)に示すよう2ヶ所に形成され、サイズはそれぞれ3.5×2.0mmで、厚さは他の配線と同様に0.02mmで、ビアを介してグランド配線に接続されている。半導体素子とランドとの間隔は0.003mmであり、エポキシ樹脂で封止されている。

【0036】

周囲温度25℃の条件における、半導体素子の発熱量と定常状態における半導体素子温度のシミュレーション結果を表1に示す。

【表1】

【0037】

シミュレーションの結果によれば、従来のフレキシブル基板にフェイスダウンで実装されたフリップチップ実装構造の半導体素子温度と比較し、本発明のフリップチップ実装構造では半導体素子の温度が低下していることを確認できる。

【0038】

またこのとき、周囲温度25℃における改善効率は、0.10Wでは3.5%、0.15Wでは4.6%、0.20Wでは5.0%であった。

【0039】

以上のように、本発明によれば、フレキシブル基板に半導体素子をフェイスダウンで実装したフリップチップ実装構造において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めることができる。

【符号の説明】

【0040】

1 半導体素子

2 バンプ

3 ランド

4 ビア

5 グランド配線

6a、6b カバーフィルム

7 ベースフィルム

8 接続パッド

9 封止樹脂

10 フレキシブル基板

11 スリット

12a、12b 屈曲部

101 撮像素子

102 受光部

103 保護ガラス

104 接着剤

105 開口部

【特許請求の範囲】

【請求項1】

半導体素子とフレキシブル基板とがバンプを介して接合され、前記半導体素子と前記フレキシブル基板との間が封止樹脂により封止されたフリップチップ実装構造において、前記フレキシブル基板には、前記半導体素子と対抗する面の一部にランドが形成され、前記フレキシブル基板は、前記バンプと接合されることで画定される領域の内側で屈曲し、このときの前記ランドと前記半導体素子との間隔が、前記バンプと接合後の前記半導体素子と前記ランドとの間隔よりも狭小であることを特徴とするフリップチップ実装構造。

【請求項2】

前記ランドは、前記フレキシブル基板に設けられた何れかの配線と接続されている、請求項1に記載のフリップチップ実装構造。

【請求項3】

前記フレキシブル基板の、前記バンプと接合されることで画定される領域の内側に、少なくとも一本のスリットが形成されている、請求項1または2に記載のフリップチップ実装構造。

【請求項1】

半導体素子とフレキシブル基板とがバンプを介して接合され、前記半導体素子と前記フレキシブル基板との間が封止樹脂により封止されたフリップチップ実装構造において、前記フレキシブル基板には、前記半導体素子と対抗する面の一部にランドが形成され、前記フレキシブル基板は、前記バンプと接合されることで画定される領域の内側で屈曲し、このときの前記ランドと前記半導体素子との間隔が、前記バンプと接合後の前記半導体素子と前記ランドとの間隔よりも狭小であることを特徴とするフリップチップ実装構造。

【請求項2】

前記ランドは、前記フレキシブル基板に設けられた何れかの配線と接続されている、請求項1に記載のフリップチップ実装構造。

【請求項3】

前記フレキシブル基板の、前記バンプと接合されることで画定される領域の内側に、少なくとも一本のスリットが形成されている、請求項1または2に記載のフリップチップ実装構造。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−134256(P2012−134256A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2010−283763(P2010−283763)

【出願日】平成22年12月20日(2010.12.20)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成22年12月20日(2010.12.20)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]