フレキシブル基板及び半導体装置

【課題】半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができるフレキシブル基板と、このフレキシブル基板を備えた半導体装置とを提供する。

【解決手段】フレキシブル基板101は、半導体チップ搭載領域103を一表面に有する基材100と、その一表面上に形成された複数のインナーリード106と、この複数のインナーリード106のうちの2つに結線されたジャンパ配線111とを備えている。ジャンパ配線111の第1配線部121は半導体チップ搭載領域103を横断している。これにより、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果を高めることができる。

【解決手段】フレキシブル基板101は、半導体チップ搭載領域103を一表面に有する基材100と、その一表面上に形成された複数のインナーリード106と、この複数のインナーリード106のうちの2つに結線されたジャンパ配線111とを備えている。ジャンパ配線111の第1配線部121は半導体チップ搭載領域103を横断している。これにより、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果を高めることができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はフレキシブル基板及び半導体装置に関する。

【背景技術】

【0002】

図7に、従来のCOF(チップ・オン・フィルム:Chip On Film)型半導体装置を斜め上方から見た概略図を示す。

【0003】

上記半導体装置は、フレキシブル基板701と、このフレキシブル基板701に搭載された半導体チップ704とを備えている。

【0004】

上記半導体チップ704はフレキシブル基板701に対してフリップチップ接続される。そして、上記半導体チップ704とフレキシブル基板701との間には、通常、樹脂が充填される。

【0005】

図8に、特開2001−237265号公報(特許文献1)に記載のフレキシブル基板801の要部を上方から見た概略図を示す。

【0006】

上記フレキシブル基板801は、半導体チップ搭載領域803を一表面に有する基材800を備えている。

【0007】

上記半導体チップ搭載領域803には、図示しない半導体チップが搭載される。より詳しくは、上記半導体チップの突起電極は、図示しないACF(異方性導電膜:Anisotropic Conductive Film)を介して熱圧着によりインナーリード806に接続される。

【0008】

上記インナーリード806は、ソルダレジスト812の開口813から露出すると共に、半導体チップ搭載領域803内に入っている。

【0009】

上記半導体チップ搭載領域803には、ACFの加熱圧着時に発生する気泡を導くガイド814が形成されている。上記気泡は、ガイド814に案内されて吐出口815から半導体チップ搭載領域803外へ排出される。

【0010】

上記気泡はその内部に水分や不純物を溜め不具合の元となるため、気泡を半導体チップ搭載領域803外へ排出するのは必要である。

【0011】

図9に、特開2004−6462号公報(特許文献2)に記載のフレキシブル基板901の要部を上方から見た概略図を示す。

【0012】

上記フレキシブル基板901は、半導体チップ搭載領域903に形成されたジャンパ配線911を備えている。

【0013】

上記半導体チップ搭載領域903には、図示しないが、LSI(大規模集積回路)などのチップ部品が接着樹脂を介して搭載される。

【0014】

上記チップ部品は半導体チップ搭載領域903に接着樹脂を介して加熱圧着される。この際、上記半導体チップ搭載領域903に形成されたジャンパ配線911によって、接着樹脂の流動性は良好となる。

【0015】

上記ジャンパ配線911は、直線形状の幹配線部921と、この幹配線部921の一端に結線された直線形状の枝配線部922と、その幹配線部921の他端に結線された直線形状の枝配線部923とで構成されている。

【0016】

上記幹配線部921は、チップ部品の長方形状の下面の長辺方向つまり図9中左右方向に沿って延びるように形成されている。

【0017】

上記枝配線部922,923が延びる方向は、幹配線部921が延びる方向に対して135±15°を成すように設定されている。また、上記枝配線部922,923は幹配線部921から延びてインナーリード906に結線されている。

【0018】

上記インナーリード906は、ソルダレジスト912の開口913から露出すると共に、半導体チップ搭載領域903内に入っている。このインナーリード906にはチップ部品の突起電極が接続される。

【0019】

このようなフレキシブル基板901では、ジャンパ配線911によって接着樹脂の流動性を良好にして、フレキシブル基板901とチップ部品との間に気泡が溜まるのを防ごうとしている。

【0020】

しかしながら、上記フレキシブル基板801,901には、それぞれ、次のような問題がある。

【0021】

上記フレキシブル基板801は、ガイド814同士の間隔が半導体チップ搭載領域803の中央部に比べて周縁部で狭くなっている。言い換えれば、上記気泡をガイド814で案内するための空間は広いが、気泡が半導体チップ搭載領域803外に出るための出口となる吐出口815が狭くなっている。

【0022】

したがって、上記フレキシブル基板801には、吐出口815から気泡をスムーズに排出できないという問題がある。

【0023】

一方、上記フレキシブル基板901では、フレキシブル基板801の吐出口815のような開口をジャンパ配線911に形成していない。

【0024】

また、上記チップ部品の突起電極とインナーリード906とが接続された接続部は狭ピッチで密集しているため、この接続部同士の間から気泡を半導体チップ搭載領域903外に排出するのは実質困難となっている。

【0025】

したがって、上記気泡が半導体チップ搭載領域903内に閉じ込められるので、気泡を半導体チップ搭載領域903外に排出することはできないという問題がある。

【0026】

すなわち、上記フレキシブル基板801,901の両方とも、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果が低いという問題がある。

【特許文献1】特開2001−237265号公報

【特許文献2】特開2004−6462号公報

【発明の開示】

【発明が解決しようとする課題】

【0027】

そこで、本発明の課題は、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができるフレキシブル基板と、このフレキシブル基板を備えた半導体装置とを提供することにある。

【課題を解決するための手段】

【0028】

上記課題を解決するため、本発明のフレキシブル基板は、

半導体チップ搭載領域を一表面に有する基材と、

上記基材の上記一表面上に形成された複数のインナーリードと、

上記インナーリードに結線され、上記半導体チップ搭載領域を横断する配線と

を備えたことを特徴としている。

【0029】

上記構成のフレキシブル基板によれば、上記配線が半導体チップ搭載領域を横断するので、半導体チップ搭載領域内の気泡が配線によって半導体チップ搭載領域外にスムーズに案内される。

【0030】

したがって、上記半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができる。

【0031】

また、上記配線は、半導体チップ搭載領域を横断するので、半導体チップ搭載領域内でループを形成しない。

【0032】

したがって、上記配線によって半導体チップ搭載領域内に気泡が閉じ込められるのを防ぐことができる。

【0033】

また、上記配線はインナーリードに結成されているので、そのインナーリードの電位を配線に持たせることができる。

【0034】

一実施形態のフレキシブル基板では、

上記配線に結線された上記インナーリードの幅は、上記配線に結線されていない上記インナーリードの幅とは異なる。

【0035】

上記実施形態のフレキシブル基板によれば、上記配線に結線されたインナーリードの幅を、配線に結線されていないインナーリードの幅よりも広くした場合、その配線に対して、例えば半導体チップの電極のうち最も大きな電流を扱う電極を接続しても、配線の電流印加時の焼損を防ぐことができる。

【0036】

したがって、上記フレキシブル基板と半導体チップとを備えた半導体装置の信頼性を確保することができる。

【0037】

一実施形態のフレキシブル基板では、

上記基材の上記一表面上に形成されたパターン保護膜を備え、

上記配線の上記半導体チップ搭載領域外の部分に関して少なくとも一部が、上記パターン保護膜に覆われずに露出している。

【0038】

上記実施形態のフレキシブル基板によれば、上記配線に例えば半導体チップの電極を接続した場合、配線の半導体チップ搭載領域外の部分に関して少なくとも一部がパターン保護膜に覆われずに露出しているので、その少なくとも一部を介して半導体チップの熱を放出して、熱によって半導体チップの不具合が発生するのを防ぐことができる。

【0039】

一実施形態のフレキシブル基板では、

上記配線は、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔である。

【0040】

本発明の半導体装置は、

本発明のフレキシブル基板と、

上記フレキシブル基板の上記半導体チップ搭載領域に搭載された半導体チップと

を備えたことを特徴としている。

【0041】

上記構成の半導体装置によれば、上記フレキシブル基板を備えるので、気泡による半導体チップの不具合の発生を防いで信頼性を高めることができる。

【0042】

より詳しくは、上記フレキシブル基板と半導体チップとの間に例えば樹脂を充填する場合、フレキシブル基板の配線は半導体チップ搭載領域を横断するので、その配線によって半導体チップ搭載領域内の樹脂が半導体チップ搭載領域外にスムーズに案内される。

【0043】

したがって、上記フレキシブル基板と半導体チップとの間に、不具合の発生させる気泡が残るのを防いで、信頼性を高めることができる。

【0044】

また、上記気泡の残存を防ぐために特別な材料や装置などを用いなくてもよいので、半導体装置の製造コストの上昇を防ぐことができる。

【0045】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記半導体チップの上記フレキシブル基板側の表面は長方形状であり、

上記突起電極は、上記半導体チップの上記フレキシブル基板側の表面の短辺近傍以外の部分に形成されている。

【0046】

上記実施形態の半導体装置によれば、上記突起電極は、半導体チップのフレキシブル基板側の表面の短辺近傍以外の部分に形成されているので、半導体チップのフレキシブル基板側の表面の短辺近傍から気泡を排出することができる。

【0047】

また、上記半導体チップのフレキシブル基板側の表面の長辺近傍に突起電極を形成することによって、突起電極の個数を多くすることができる。

【0048】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極の電位はグランド電位である。

【0049】

上記実施形態の半導体装置によれば、上記配線に接続される突起電極の電位はグランド電位であるので、電気特性を安定化することができて、品質向上効果を得ることができる。

【0050】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極が扱う電流は、上記半導体チップが外部へ出力する電流である。

【0051】

上記実施形態の半導体装置によれば、上記配線に接続される突起電極が扱う電流は、半導体チップが外部へ出力する電流であるので、上記配線に結線されたインナーリードを介して上記電流を取り出すことができる。

【発明の効果】

【0052】

本発明のフレキシブル基板によれば、配線が半導体チップ搭載領域を横断することによって、半導体チップ搭載領域内の気泡が配線でチップ搭載領域外にスムーズに案内されるので、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができる。

【0053】

本発明の半導体装置によれば、上記フレキシブル基板を備えるので、気泡による半導体チップの不具合の発生を防いで信頼性を高めることができる。

【発明を実施するための最良の形態】

【0054】

(第1実施形態)

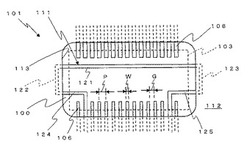

図1に、本発明の第1実施形態のフレキシブル基板101の要部を上方から見た概略図を示す。

【0055】

上記フレキシブル基板101は、図1,図2に示すように、平面視で長方形状の半導体チップ搭載領域103を一表面に有する基材100と、その一表面上に形成された複数のインナーリード106と、この複数のインナーリード106のうちの2つに結線されたジャンパ配線111とを備えている。なお、上記ジャンパ配線111が配線の一例である。

【0056】

上記基材100は、例えば厚さ40μmのポリイミドフィルムから成っている。

【0057】

上記ジャンパ配線111は、第1配線部121、第2配線部122、第3配線部123、第4配線部124及び第5配線部125で構成されている。

【0058】

上記第1配線部121は、半導体チップ搭載領域103の長辺に沿って延びて、半導体チップ搭載領域103を横断している。つまり、上記第1配線部121は、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。

【0059】

上記第2配線部122は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第2配線部122の一端は第1配線部123の一端に連なっている。

【0060】

上記第3配線部123は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第3配線部123の一端は第1配線部123の他端に連なっている。

【0061】

上記第4配線部124は、半導体チップ搭載領域103の長辺に沿って、第1配線部121に対して平行に延びている。そして、上記第4配線部124も、第1配線部121と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第4配線部124の一端は第2配線部122の他端に連なっている。一方、上記第4配線部124の他端は、インナーリード106の先端に結線されている。このインナーリード106の線幅は、第4配線部124の線幅と略同一となっている。

【0062】

上記第5配線部125は半導体チップ搭載領域103の長辺に沿って、第1配線部121に対して平行延びている。そして、上記第5配線部125も、第1配線部121と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第5配線部125の一端は第3配線部123の他端に連なっている。一方、上記第5配線部125の他端はインナーリード106の先端に結線されている。このインナーリード106の線幅は、第5配線部125の線幅と略同一となっている。

【0063】

また、上記第1配線部121、第2配線部122、第3配線部123、第4配線部124及び第5配線部125の線幅は全て略同一となっている。

【0064】

また、上記第4,第5配線部124,125の他端に接続するインナーリード106は、他のインナーリード106よりも長くなるように形成されている。

【0065】

また、上記第1配線部121と第4配線部124との間の距離は、第1配線部121と第5配線部125との間の距離と略同一となっている。

【0066】

また、上記ジャンパ配線111の半導体チップ搭載領域103外の部分に関して一部が、ソルダレジスト112に覆われずに露出している。より詳しくは、上記半導体チップ搭載領域103外においては、第1配線部121の一部と、第4配線部124の一部と、第5配線部125の一部とが、ソルダレジスト112に覆われずに露出している。なお、上記ソルダレジスト112がパターン保護膜の一例である。

【0067】

また、上記第1配線部121の両端部と、第2,第3配線部122,123の全部と、第4,第5配線部124,125の一端部とが、ソルダレジスト112に覆われている。これにより、上記ジャンパ配線111の信頼性を高めることができる。

【0068】

上記インナーリード106は、ソルダレジスト112の開口113内に位置するように形成されている。そして、上記インナーリード106の形成ピッチつまりインナーリードピッチPは、後述する突起電極105の形成ピッチに合わせて50μmとしている。また、上記インナーリード106同士の間隔つまりインナーリードギャップGは25μmとなっている。また、上記インナーリード106の幅Wも25μmとなっている。

【0069】

上記インナーリードギャップGとインナーリード106の幅Wとは、エッチング残りや、エッチング残りによるマイグレーション等のインナーリード106同士が近接するリスクと、インナーリード106のパターン欠けや電流容量低下等の細線化によるリスクとのバランスを考慮して設定されている。

【0070】

図2に、本発明の第1実施形態の半導体装置を斜め上方から見た概略図を示す。また、図3に、図2の半導体チップ搭載領域103の拡大図を示す。なお、図3では、理解容易のため、樹脂110を透明なものとして図示している。

【0071】

上記半導体装置は、図2,図3に示すように、フレキシブル基板101と、このフレキシブル基板101にフリップチップ接続で接続されると共に、半導体チップ搭載領域103に搭載される半導体チップ104と、ソルダレジスト112の開口113を覆う樹脂110とを備えている。

【0072】

上記半導体チップ104の下面(フレキシブル基板101側の表面)には複数の突起電極105が形成されている。より詳しくは、上記半導体チップ104の下面は長方形状となっており、この下面の長辺に沿って複数の突起電極105を形成している。これにより、後述する配線102の各パターンを直線形状にして単純化することができる。

【0073】

上記複数の突起電極105において、半導体チップ104の下面の一方の長辺近傍の突起電極105が出力側電極であり、半導体チップ104の下面の他方の長辺近傍の突起電極105が入力側電極である。また、上記半導体チップ104の下面の短辺近傍には突起電極105を形成していない。

【0074】

上記フレキシブル基板101の一構成部である基材100の一表面(半導体チップ104側の表面)には、配線102が形成されており、この配線102の大部分を覆うようにソルダレジスト112が形成されている。

【0075】

上記配線102は厚さ8μmの銅箔から成っている。また、上記配線102の半導体チップ搭載領域103側の端部がインナーリード106となっている。つまり、上記インナーリード106は配線102の一部である。

【0076】

上記樹脂110は半導体チップ104の周囲に存在する。この樹脂110の一部はフレキシブル基板101と半導体チップ104との間Sに入っている。

【0077】

上記半導体チップ104の下面の長辺近傍では、突起電極105とインナーリード106とが直線上に密集して並んでいるため、それらが実質は壁のようにフレキシブル基板101と半導体チップ104との間Sを閉じた格好となっている。

【0078】

一方、上記半導体チップ104の下面の短辺近傍では、突起電極105が存在せず、ジャンパ配線111の第1配線部121が半導体チップ104の下面の長辺に沿って延びて半導体チップ搭載領域103を横断して、半導体チップ搭載領域103内から半導体チップ搭載領域103外へ向かって突出している。

【0079】

このように、上記半導体チップ104の下面の短辺近傍に突起電極105を形成していないことと、ジャンパ配線111の第1配線部121が半導体チップ104の下面の長辺に沿って延びて半導体チップ搭載領域103を横断していることによって、フレキシブル基板101と半導体チップ104との間Sの気泡を半導体チップ104の下面の短辺近傍から半導体チップ搭載領域103外に排出することができる。

【0080】

したがって、上記フレキシブル基板101は、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果が高いものである。

【0081】

また、上記ジャンパ配線111は、半導体チップ搭載領域103内でループを形成していないので、半導体チップ搭載領域103内に気泡が閉じ込められるのを防ぐことができる。

【0082】

上記第1実施形態では、第2配線部122は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第2配線部122は、ソルダレジスト112で覆わないようにしてもよい。

【0083】

上記第1実施形態では、第3配線部123は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第3配線部123は、ソルダレジスト112で覆わないようにしてもよい。

【0084】

上記第1実施形態では、インナーリード106の幅Wは25μmであったが、これ以外の幅であってもよい。また、上記インナーリード106の厚さは8μmであったが、これ以外の厚さであってもよい。つまり、上記第1実施形態において、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔から成るインナーリードを用いてもよい。

【0085】

上記第1実施形態において、上記インナーリード106の幅よりも狭い幅を有するジャンパ配線を用いてもよい。

【0086】

上記第1実施形態において、上記ジャンパ配線111に電流が流れるようにしてもよいし、ジャンパ配線111に電流が流れないようにしてもよい。

【0087】

(第2実施形態)

図4に、本発明の第2実施形態の半導体装置の要部を上方から見た概略図を示す。また、図4において、図1に示した第1実施形態の構成部と同一構成部は、図1における構成部と同一参照番号を付して説明を省略する。また、図4では、上記半導体装置が備える半導体チップ204の図示を省略している。

【0088】

上記半導体装置は、フレキシブル基板201と、このフレキシブル基板201にフリップチップ接続で接続されると共に、半導体チップ搭載領域103に搭載される半導体チップ104とを備えている。

【0089】

上記フレキシブル基板201は、第1配線部221、第2配線部222、第3配線部223、第4配線部224及び第5配線部225から成るジャンパ配線211を備えている。なお、上記ジャンパ配線211は配線の一例である。

【0090】

上記第1配線部221は、半導体チップ搭載領域103の長辺に沿って延びて、半導体チップ搭載領域103を横断している。つまり、上記第1配線部221は、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。

【0091】

上記第2配線部222は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第2配線部222の一端は第1配線部223の一端に連なっている。

【0092】

上記第3配線部223は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第3配線部223の一端は第1配線部223の他端に連なっている。

【0093】

上記第4配線部224は、半導体チップ搭載領域103の長辺に沿って、第1配線部221に対して平行に延びている。そして、上記第4配線部224も、第1配線部221と同様に、半導体チップ搭載領域103から半導体チップ搭載領域103外の領域に渡って形成されている。また、上記第4配線部224の一端は第2配線部222の他端に連なっている。一方、上記第4配線部224の他端は、インナーリード206の先端に結線されている。このインナーリード206の線幅は、第4配線部224の線幅と略同一であり、かつ、インナーリード106の線幅よりも広くなっている。

【0094】

上記第5配線部225は半導体チップ搭載領域103の長辺に沿って、第1配線部221に対して平行に延びている。そして、上記第5配線部225も、第1配線部221と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第5配線部225の一端は第3配線部223の他端に連なっている。一方、上記第5配線部225の他端はインナーリード206の先端に結線されている。このインナーリード206の線幅は、第5配線部225の線幅と略同一であり、かつ、インナーリード106の線幅よりも広くなっている。

【0095】

また、上記第1配線部221、第2配線部222、第3配線部223、第4配線部224及び第5配線部225の線幅は全て略同一となっている。

【0096】

また、上記第4,第5配線部224,225の他端に接続するインナーリード206は、他のインナーリード106よりも長くなるように形成されている。

【0097】

また、上記第1配線部221と第4配線部224との間の距離は、第1配線部221と第5配線部225との間の距離と略同一となっている。

【0098】

また、上記ジャンパ配線211の半導体チップ搭載領域103外の部分に関して一部が、ソルダレジスト112に覆われずに露出している。より詳しくは、上記半導体チップ搭載領域103外においては、第1配線部221の一部と、第4配線部224の一部と、第5配線部225の一部とが、ソルダレジスト112に覆われずに露出している。また、上記第1配線部221の両端部と、第2,第3配線部222,223の全部と、第4,第5配線部224,225の一端部とが、ソルダレジスト112に覆われている。これにより、上記ジャンパ配線211の信頼性を高めることができる。なお、上記ソルダレジスト112がパターン保護膜の一例である。

【0099】

また、上記第1配線部221及びインナーリード206には突起電極205が接続される。

【0100】

図5に、図4のV−V線から見た概略断面図を示す。

【0101】

上記半導体チップ204の下面(フレキシブル基板201側の表面)には、突起電極105,205が形成されている。また、上記半導体チップ204の下面は長方形状となっている。

【0102】

上記第1配線部221に接続する突起電極205は、半導体チップ104の下面においてその長辺から少し離れた箇所に形成されている。

【0103】

上記インナーリード206に接続する突起電極205は、半導体チップ104の下面の長辺近傍に形成されている。

【0104】

上記半導体チップ204は、図示しないプリンタヘッドへ電圧を供給するプリンタドライバであり、そのプリンタヘッドへ電圧を供給する際に発生する電流がインナーリード206及びジャンパ配線211を流れる。このため、上記インナーリード206及びジャンパ配線211はその電流による焼損のないよう十分抵抗を低くする配線寸法とする必要がある。具体的には、上記インナーリード206及びジャンパ配線211は、厚さ8μmかつ幅40μmの銅箔で形成している。このインナーリード206及びジャンパ配線211の断面積は320μm2であるため、インナーリード206及びジャンパ配線211が電流によって焼損するのを十分防止できる。

【0105】

発明者は、実験により、実際に半導体チップ205が扱う電流0.2Aに対するマージンを持った設計として10倍の電流2Aを適用する配線幅を考慮した場合、配線断面積として300μm2が必要であることを見出した。

【0106】

したがって、現状のフレキシブル基板の配線形成限界である厚さ1μmであれば、配線幅は300μm必要である。逆に、配線を厚くすると配線幅は小さくて済み、従来TCP(テープ・キャリア・パッケージ:Tape Carrier Package)に用いるような配線として厚さ50μmの銅箔を採用すれば、配線幅を6μmと小さくすることができる。

【0107】

また、上記フレキシブル基板201においても、フレキシブル基板101と同様に、フレキシブル基板201と半導体チップ204との間の気泡を半導体チップ204の下面の短辺近傍から半導体チップ搭載領域103外に排出することができる。

【0108】

したがって、上記フレキシブル基板201は、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果が高いものである。

【0109】

上記第2実施形態では、第2配線部222は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第2配線部222は、ソルダレジスト212で覆わないようにしてもよい。

【0110】

上記第2実施形態では、第3配線部223は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第3配線部223は、ソルダレジスト112で覆わないようにしてもよい。

【0111】

上記第2実施形態において、半導体装置は、ソルダレジスト112の開口113を覆う樹脂を備えてもよい。

【0112】

(第3実施形態)

図6に、本発明の第3実施形態の半導体装置の要部を上方から見た概略図を示す。また、図6において、図1に示した第1実施形態の構成部と同一構成部は、図1における構成部と同一参照番号を付して説明を省略する。また、図6では、上記半導体装置が備える半導体チップの図示を省略している。

【0113】

上記半導体装置は、ジャンパ配線111の第1配線部121に突起電極305を接続している点が、上記第1実施形態とは異なる。

【0114】

上記半導体チップは液晶ドライバである。そして、上記半導体チップの下面(フレキシブル基板101側の表面)には、突起電極105,305が形成されている。また、上記半導体チップの下面は長方形状となっている。

【0115】

上記突起電極305は、半導体チップ104の下面において長辺から少し離れた箇所に形成されている。また、上記突起電極305の電位はグランド電位である。

【0116】

入力信号のシリアル化により動作周波数が高くなった近年の液晶ドライバチップでは高周波回路的設計要素が不可欠であり、グランド電位安定化のため所望の位置にグランド電位の電極を配置したい。このため、上記突起電極305を、半導体チップの下面に形成して、ジャンパ配線111の第1配線部121に接続した。

【0117】

このように、上記突起電極305を、半導体チップの下面に形成して、ジャンパ配線111の第1配線部121に接続することにより、半導体装置の電気的な機能が向上する。

【図面の簡単な説明】

【0118】

【図1】図1は本発明の第1実施形態のフレキシブル基板の要部の概略平面図である。

【図2】図2は本発明の第1実施形態の半導体装置の概略斜視図である。

【図3】図3は図2の半導体チップ搭載領域の拡大図である。

【図4】図4は本発明の第2実施形態の半導体装置の要部の概略平面図である。

【図5】図5は図4のV−V線矢視断面図である。

【図6】図6は本発明の第3実施形態の半導体装置の要部の概略平面図である。

【図7】図7は従来のCOF型半導体装置の概略斜視図である。

【図8】図8は従来のフレキシブル基板の要部の概略平面図である。

【図9】図9は他の従来のフレキシブル基板の要部の概略平面図である。

【符号の説明】

【0119】

100 基材

101,201 フレキシブル基板

102 配線

103 半導体チップ搭載領域

105,205,305 突起電極

106,206 インナーリード

111,211 ジャンパ配線

112 ソルダレジスト

121,221 第1配線部

122,222 第2配線部

123,223 第3配線部

124,224 第4配線部

125,225 第5配線部

【技術分野】

【0001】

本発明はフレキシブル基板及び半導体装置に関する。

【背景技術】

【0002】

図7に、従来のCOF(チップ・オン・フィルム:Chip On Film)型半導体装置を斜め上方から見た概略図を示す。

【0003】

上記半導体装置は、フレキシブル基板701と、このフレキシブル基板701に搭載された半導体チップ704とを備えている。

【0004】

上記半導体チップ704はフレキシブル基板701に対してフリップチップ接続される。そして、上記半導体チップ704とフレキシブル基板701との間には、通常、樹脂が充填される。

【0005】

図8に、特開2001−237265号公報(特許文献1)に記載のフレキシブル基板801の要部を上方から見た概略図を示す。

【0006】

上記フレキシブル基板801は、半導体チップ搭載領域803を一表面に有する基材800を備えている。

【0007】

上記半導体チップ搭載領域803には、図示しない半導体チップが搭載される。より詳しくは、上記半導体チップの突起電極は、図示しないACF(異方性導電膜:Anisotropic Conductive Film)を介して熱圧着によりインナーリード806に接続される。

【0008】

上記インナーリード806は、ソルダレジスト812の開口813から露出すると共に、半導体チップ搭載領域803内に入っている。

【0009】

上記半導体チップ搭載領域803には、ACFの加熱圧着時に発生する気泡を導くガイド814が形成されている。上記気泡は、ガイド814に案内されて吐出口815から半導体チップ搭載領域803外へ排出される。

【0010】

上記気泡はその内部に水分や不純物を溜め不具合の元となるため、気泡を半導体チップ搭載領域803外へ排出するのは必要である。

【0011】

図9に、特開2004−6462号公報(特許文献2)に記載のフレキシブル基板901の要部を上方から見た概略図を示す。

【0012】

上記フレキシブル基板901は、半導体チップ搭載領域903に形成されたジャンパ配線911を備えている。

【0013】

上記半導体チップ搭載領域903には、図示しないが、LSI(大規模集積回路)などのチップ部品が接着樹脂を介して搭載される。

【0014】

上記チップ部品は半導体チップ搭載領域903に接着樹脂を介して加熱圧着される。この際、上記半導体チップ搭載領域903に形成されたジャンパ配線911によって、接着樹脂の流動性は良好となる。

【0015】

上記ジャンパ配線911は、直線形状の幹配線部921と、この幹配線部921の一端に結線された直線形状の枝配線部922と、その幹配線部921の他端に結線された直線形状の枝配線部923とで構成されている。

【0016】

上記幹配線部921は、チップ部品の長方形状の下面の長辺方向つまり図9中左右方向に沿って延びるように形成されている。

【0017】

上記枝配線部922,923が延びる方向は、幹配線部921が延びる方向に対して135±15°を成すように設定されている。また、上記枝配線部922,923は幹配線部921から延びてインナーリード906に結線されている。

【0018】

上記インナーリード906は、ソルダレジスト912の開口913から露出すると共に、半導体チップ搭載領域903内に入っている。このインナーリード906にはチップ部品の突起電極が接続される。

【0019】

このようなフレキシブル基板901では、ジャンパ配線911によって接着樹脂の流動性を良好にして、フレキシブル基板901とチップ部品との間に気泡が溜まるのを防ごうとしている。

【0020】

しかしながら、上記フレキシブル基板801,901には、それぞれ、次のような問題がある。

【0021】

上記フレキシブル基板801は、ガイド814同士の間隔が半導体チップ搭載領域803の中央部に比べて周縁部で狭くなっている。言い換えれば、上記気泡をガイド814で案内するための空間は広いが、気泡が半導体チップ搭載領域803外に出るための出口となる吐出口815が狭くなっている。

【0022】

したがって、上記フレキシブル基板801には、吐出口815から気泡をスムーズに排出できないという問題がある。

【0023】

一方、上記フレキシブル基板901では、フレキシブル基板801の吐出口815のような開口をジャンパ配線911に形成していない。

【0024】

また、上記チップ部品の突起電極とインナーリード906とが接続された接続部は狭ピッチで密集しているため、この接続部同士の間から気泡を半導体チップ搭載領域903外に排出するのは実質困難となっている。

【0025】

したがって、上記気泡が半導体チップ搭載領域903内に閉じ込められるので、気泡を半導体チップ搭載領域903外に排出することはできないという問題がある。

【0026】

すなわち、上記フレキシブル基板801,901の両方とも、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果が低いという問題がある。

【特許文献1】特開2001−237265号公報

【特許文献2】特開2004−6462号公報

【発明の開示】

【発明が解決しようとする課題】

【0027】

そこで、本発明の課題は、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができるフレキシブル基板と、このフレキシブル基板を備えた半導体装置とを提供することにある。

【課題を解決するための手段】

【0028】

上記課題を解決するため、本発明のフレキシブル基板は、

半導体チップ搭載領域を一表面に有する基材と、

上記基材の上記一表面上に形成された複数のインナーリードと、

上記インナーリードに結線され、上記半導体チップ搭載領域を横断する配線と

を備えたことを特徴としている。

【0029】

上記構成のフレキシブル基板によれば、上記配線が半導体チップ搭載領域を横断するので、半導体チップ搭載領域内の気泡が配線によって半導体チップ搭載領域外にスムーズに案内される。

【0030】

したがって、上記半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができる。

【0031】

また、上記配線は、半導体チップ搭載領域を横断するので、半導体チップ搭載領域内でループを形成しない。

【0032】

したがって、上記配線によって半導体チップ搭載領域内に気泡が閉じ込められるのを防ぐことができる。

【0033】

また、上記配線はインナーリードに結成されているので、そのインナーリードの電位を配線に持たせることができる。

【0034】

一実施形態のフレキシブル基板では、

上記配線に結線された上記インナーリードの幅は、上記配線に結線されていない上記インナーリードの幅とは異なる。

【0035】

上記実施形態のフレキシブル基板によれば、上記配線に結線されたインナーリードの幅を、配線に結線されていないインナーリードの幅よりも広くした場合、その配線に対して、例えば半導体チップの電極のうち最も大きな電流を扱う電極を接続しても、配線の電流印加時の焼損を防ぐことができる。

【0036】

したがって、上記フレキシブル基板と半導体チップとを備えた半導体装置の信頼性を確保することができる。

【0037】

一実施形態のフレキシブル基板では、

上記基材の上記一表面上に形成されたパターン保護膜を備え、

上記配線の上記半導体チップ搭載領域外の部分に関して少なくとも一部が、上記パターン保護膜に覆われずに露出している。

【0038】

上記実施形態のフレキシブル基板によれば、上記配線に例えば半導体チップの電極を接続した場合、配線の半導体チップ搭載領域外の部分に関して少なくとも一部がパターン保護膜に覆われずに露出しているので、その少なくとも一部を介して半導体チップの熱を放出して、熱によって半導体チップの不具合が発生するのを防ぐことができる。

【0039】

一実施形態のフレキシブル基板では、

上記配線は、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔である。

【0040】

本発明の半導体装置は、

本発明のフレキシブル基板と、

上記フレキシブル基板の上記半導体チップ搭載領域に搭載された半導体チップと

を備えたことを特徴としている。

【0041】

上記構成の半導体装置によれば、上記フレキシブル基板を備えるので、気泡による半導体チップの不具合の発生を防いで信頼性を高めることができる。

【0042】

より詳しくは、上記フレキシブル基板と半導体チップとの間に例えば樹脂を充填する場合、フレキシブル基板の配線は半導体チップ搭載領域を横断するので、その配線によって半導体チップ搭載領域内の樹脂が半導体チップ搭載領域外にスムーズに案内される。

【0043】

したがって、上記フレキシブル基板と半導体チップとの間に、不具合の発生させる気泡が残るのを防いで、信頼性を高めることができる。

【0044】

また、上記気泡の残存を防ぐために特別な材料や装置などを用いなくてもよいので、半導体装置の製造コストの上昇を防ぐことができる。

【0045】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記半導体チップの上記フレキシブル基板側の表面は長方形状であり、

上記突起電極は、上記半導体チップの上記フレキシブル基板側の表面の短辺近傍以外の部分に形成されている。

【0046】

上記実施形態の半導体装置によれば、上記突起電極は、半導体チップのフレキシブル基板側の表面の短辺近傍以外の部分に形成されているので、半導体チップのフレキシブル基板側の表面の短辺近傍から気泡を排出することができる。

【0047】

また、上記半導体チップのフレキシブル基板側の表面の長辺近傍に突起電極を形成することによって、突起電極の個数を多くすることができる。

【0048】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極の電位はグランド電位である。

【0049】

上記実施形態の半導体装置によれば、上記配線に接続される突起電極の電位はグランド電位であるので、電気特性を安定化することができて、品質向上効果を得ることができる。

【0050】

一実施形態の半導体装置では、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極が扱う電流は、上記半導体チップが外部へ出力する電流である。

【0051】

上記実施形態の半導体装置によれば、上記配線に接続される突起電極が扱う電流は、半導体チップが外部へ出力する電流であるので、上記配線に結線されたインナーリードを介して上記電流を取り出すことができる。

【発明の効果】

【0052】

本発明のフレキシブル基板によれば、配線が半導体チップ搭載領域を横断することによって、半導体チップ搭載領域内の気泡が配線でチップ搭載領域外にスムーズに案内されるので、半導体チップ搭載領域内から半導体チップ搭載領域外への気泡の排出効果を高めることができる。

【0053】

本発明の半導体装置によれば、上記フレキシブル基板を備えるので、気泡による半導体チップの不具合の発生を防いで信頼性を高めることができる。

【発明を実施するための最良の形態】

【0054】

(第1実施形態)

図1に、本発明の第1実施形態のフレキシブル基板101の要部を上方から見た概略図を示す。

【0055】

上記フレキシブル基板101は、図1,図2に示すように、平面視で長方形状の半導体チップ搭載領域103を一表面に有する基材100と、その一表面上に形成された複数のインナーリード106と、この複数のインナーリード106のうちの2つに結線されたジャンパ配線111とを備えている。なお、上記ジャンパ配線111が配線の一例である。

【0056】

上記基材100は、例えば厚さ40μmのポリイミドフィルムから成っている。

【0057】

上記ジャンパ配線111は、第1配線部121、第2配線部122、第3配線部123、第4配線部124及び第5配線部125で構成されている。

【0058】

上記第1配線部121は、半導体チップ搭載領域103の長辺に沿って延びて、半導体チップ搭載領域103を横断している。つまり、上記第1配線部121は、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。

【0059】

上記第2配線部122は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第2配線部122の一端は第1配線部123の一端に連なっている。

【0060】

上記第3配線部123は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第3配線部123の一端は第1配線部123の他端に連なっている。

【0061】

上記第4配線部124は、半導体チップ搭載領域103の長辺に沿って、第1配線部121に対して平行に延びている。そして、上記第4配線部124も、第1配線部121と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第4配線部124の一端は第2配線部122の他端に連なっている。一方、上記第4配線部124の他端は、インナーリード106の先端に結線されている。このインナーリード106の線幅は、第4配線部124の線幅と略同一となっている。

【0062】

上記第5配線部125は半導体チップ搭載領域103の長辺に沿って、第1配線部121に対して平行延びている。そして、上記第5配線部125も、第1配線部121と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第5配線部125の一端は第3配線部123の他端に連なっている。一方、上記第5配線部125の他端はインナーリード106の先端に結線されている。このインナーリード106の線幅は、第5配線部125の線幅と略同一となっている。

【0063】

また、上記第1配線部121、第2配線部122、第3配線部123、第4配線部124及び第5配線部125の線幅は全て略同一となっている。

【0064】

また、上記第4,第5配線部124,125の他端に接続するインナーリード106は、他のインナーリード106よりも長くなるように形成されている。

【0065】

また、上記第1配線部121と第4配線部124との間の距離は、第1配線部121と第5配線部125との間の距離と略同一となっている。

【0066】

また、上記ジャンパ配線111の半導体チップ搭載領域103外の部分に関して一部が、ソルダレジスト112に覆われずに露出している。より詳しくは、上記半導体チップ搭載領域103外においては、第1配線部121の一部と、第4配線部124の一部と、第5配線部125の一部とが、ソルダレジスト112に覆われずに露出している。なお、上記ソルダレジスト112がパターン保護膜の一例である。

【0067】

また、上記第1配線部121の両端部と、第2,第3配線部122,123の全部と、第4,第5配線部124,125の一端部とが、ソルダレジスト112に覆われている。これにより、上記ジャンパ配線111の信頼性を高めることができる。

【0068】

上記インナーリード106は、ソルダレジスト112の開口113内に位置するように形成されている。そして、上記インナーリード106の形成ピッチつまりインナーリードピッチPは、後述する突起電極105の形成ピッチに合わせて50μmとしている。また、上記インナーリード106同士の間隔つまりインナーリードギャップGは25μmとなっている。また、上記インナーリード106の幅Wも25μmとなっている。

【0069】

上記インナーリードギャップGとインナーリード106の幅Wとは、エッチング残りや、エッチング残りによるマイグレーション等のインナーリード106同士が近接するリスクと、インナーリード106のパターン欠けや電流容量低下等の細線化によるリスクとのバランスを考慮して設定されている。

【0070】

図2に、本発明の第1実施形態の半導体装置を斜め上方から見た概略図を示す。また、図3に、図2の半導体チップ搭載領域103の拡大図を示す。なお、図3では、理解容易のため、樹脂110を透明なものとして図示している。

【0071】

上記半導体装置は、図2,図3に示すように、フレキシブル基板101と、このフレキシブル基板101にフリップチップ接続で接続されると共に、半導体チップ搭載領域103に搭載される半導体チップ104と、ソルダレジスト112の開口113を覆う樹脂110とを備えている。

【0072】

上記半導体チップ104の下面(フレキシブル基板101側の表面)には複数の突起電極105が形成されている。より詳しくは、上記半導体チップ104の下面は長方形状となっており、この下面の長辺に沿って複数の突起電極105を形成している。これにより、後述する配線102の各パターンを直線形状にして単純化することができる。

【0073】

上記複数の突起電極105において、半導体チップ104の下面の一方の長辺近傍の突起電極105が出力側電極であり、半導体チップ104の下面の他方の長辺近傍の突起電極105が入力側電極である。また、上記半導体チップ104の下面の短辺近傍には突起電極105を形成していない。

【0074】

上記フレキシブル基板101の一構成部である基材100の一表面(半導体チップ104側の表面)には、配線102が形成されており、この配線102の大部分を覆うようにソルダレジスト112が形成されている。

【0075】

上記配線102は厚さ8μmの銅箔から成っている。また、上記配線102の半導体チップ搭載領域103側の端部がインナーリード106となっている。つまり、上記インナーリード106は配線102の一部である。

【0076】

上記樹脂110は半導体チップ104の周囲に存在する。この樹脂110の一部はフレキシブル基板101と半導体チップ104との間Sに入っている。

【0077】

上記半導体チップ104の下面の長辺近傍では、突起電極105とインナーリード106とが直線上に密集して並んでいるため、それらが実質は壁のようにフレキシブル基板101と半導体チップ104との間Sを閉じた格好となっている。

【0078】

一方、上記半導体チップ104の下面の短辺近傍では、突起電極105が存在せず、ジャンパ配線111の第1配線部121が半導体チップ104の下面の長辺に沿って延びて半導体チップ搭載領域103を横断して、半導体チップ搭載領域103内から半導体チップ搭載領域103外へ向かって突出している。

【0079】

このように、上記半導体チップ104の下面の短辺近傍に突起電極105を形成していないことと、ジャンパ配線111の第1配線部121が半導体チップ104の下面の長辺に沿って延びて半導体チップ搭載領域103を横断していることによって、フレキシブル基板101と半導体チップ104との間Sの気泡を半導体チップ104の下面の短辺近傍から半導体チップ搭載領域103外に排出することができる。

【0080】

したがって、上記フレキシブル基板101は、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果が高いものである。

【0081】

また、上記ジャンパ配線111は、半導体チップ搭載領域103内でループを形成していないので、半導体チップ搭載領域103内に気泡が閉じ込められるのを防ぐことができる。

【0082】

上記第1実施形態では、第2配線部122は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第2配線部122は、ソルダレジスト112で覆わないようにしてもよい。

【0083】

上記第1実施形態では、第3配線部123は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第3配線部123は、ソルダレジスト112で覆わないようにしてもよい。

【0084】

上記第1実施形態では、インナーリード106の幅Wは25μmであったが、これ以外の幅であってもよい。また、上記インナーリード106の厚さは8μmであったが、これ以外の厚さであってもよい。つまり、上記第1実施形態において、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔から成るインナーリードを用いてもよい。

【0085】

上記第1実施形態において、上記インナーリード106の幅よりも狭い幅を有するジャンパ配線を用いてもよい。

【0086】

上記第1実施形態において、上記ジャンパ配線111に電流が流れるようにしてもよいし、ジャンパ配線111に電流が流れないようにしてもよい。

【0087】

(第2実施形態)

図4に、本発明の第2実施形態の半導体装置の要部を上方から見た概略図を示す。また、図4において、図1に示した第1実施形態の構成部と同一構成部は、図1における構成部と同一参照番号を付して説明を省略する。また、図4では、上記半導体装置が備える半導体チップ204の図示を省略している。

【0088】

上記半導体装置は、フレキシブル基板201と、このフレキシブル基板201にフリップチップ接続で接続されると共に、半導体チップ搭載領域103に搭載される半導体チップ104とを備えている。

【0089】

上記フレキシブル基板201は、第1配線部221、第2配線部222、第3配線部223、第4配線部224及び第5配線部225から成るジャンパ配線211を備えている。なお、上記ジャンパ配線211は配線の一例である。

【0090】

上記第1配線部221は、半導体チップ搭載領域103の長辺に沿って延びて、半導体チップ搭載領域103を横断している。つまり、上記第1配線部221は、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。

【0091】

上記第2配線部222は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第2配線部222の一端は第1配線部223の一端に連なっている。

【0092】

上記第3配線部223は半導体チップ搭載領域103の短辺に沿って延びている。また、上記第3配線部223の一端は第1配線部223の他端に連なっている。

【0093】

上記第4配線部224は、半導体チップ搭載領域103の長辺に沿って、第1配線部221に対して平行に延びている。そして、上記第4配線部224も、第1配線部221と同様に、半導体チップ搭載領域103から半導体チップ搭載領域103外の領域に渡って形成されている。また、上記第4配線部224の一端は第2配線部222の他端に連なっている。一方、上記第4配線部224の他端は、インナーリード206の先端に結線されている。このインナーリード206の線幅は、第4配線部224の線幅と略同一であり、かつ、インナーリード106の線幅よりも広くなっている。

【0094】

上記第5配線部225は半導体チップ搭載領域103の長辺に沿って、第1配線部221に対して平行に延びている。そして、上記第5配線部225も、第1配線部221と同様に、半導体チップ搭載領域103と、半導体チップ搭載領域103外の領域とに渡って形成されている。また、上記第5配線部225の一端は第3配線部223の他端に連なっている。一方、上記第5配線部225の他端はインナーリード206の先端に結線されている。このインナーリード206の線幅は、第5配線部225の線幅と略同一であり、かつ、インナーリード106の線幅よりも広くなっている。

【0095】

また、上記第1配線部221、第2配線部222、第3配線部223、第4配線部224及び第5配線部225の線幅は全て略同一となっている。

【0096】

また、上記第4,第5配線部224,225の他端に接続するインナーリード206は、他のインナーリード106よりも長くなるように形成されている。

【0097】

また、上記第1配線部221と第4配線部224との間の距離は、第1配線部221と第5配線部225との間の距離と略同一となっている。

【0098】

また、上記ジャンパ配線211の半導体チップ搭載領域103外の部分に関して一部が、ソルダレジスト112に覆われずに露出している。より詳しくは、上記半導体チップ搭載領域103外においては、第1配線部221の一部と、第4配線部224の一部と、第5配線部225の一部とが、ソルダレジスト112に覆われずに露出している。また、上記第1配線部221の両端部と、第2,第3配線部222,223の全部と、第4,第5配線部224,225の一端部とが、ソルダレジスト112に覆われている。これにより、上記ジャンパ配線211の信頼性を高めることができる。なお、上記ソルダレジスト112がパターン保護膜の一例である。

【0099】

また、上記第1配線部221及びインナーリード206には突起電極205が接続される。

【0100】

図5に、図4のV−V線から見た概略断面図を示す。

【0101】

上記半導体チップ204の下面(フレキシブル基板201側の表面)には、突起電極105,205が形成されている。また、上記半導体チップ204の下面は長方形状となっている。

【0102】

上記第1配線部221に接続する突起電極205は、半導体チップ104の下面においてその長辺から少し離れた箇所に形成されている。

【0103】

上記インナーリード206に接続する突起電極205は、半導体チップ104の下面の長辺近傍に形成されている。

【0104】

上記半導体チップ204は、図示しないプリンタヘッドへ電圧を供給するプリンタドライバであり、そのプリンタヘッドへ電圧を供給する際に発生する電流がインナーリード206及びジャンパ配線211を流れる。このため、上記インナーリード206及びジャンパ配線211はその電流による焼損のないよう十分抵抗を低くする配線寸法とする必要がある。具体的には、上記インナーリード206及びジャンパ配線211は、厚さ8μmかつ幅40μmの銅箔で形成している。このインナーリード206及びジャンパ配線211の断面積は320μm2であるため、インナーリード206及びジャンパ配線211が電流によって焼損するのを十分防止できる。

【0105】

発明者は、実験により、実際に半導体チップ205が扱う電流0.2Aに対するマージンを持った設計として10倍の電流2Aを適用する配線幅を考慮した場合、配線断面積として300μm2が必要であることを見出した。

【0106】

したがって、現状のフレキシブル基板の配線形成限界である厚さ1μmであれば、配線幅は300μm必要である。逆に、配線を厚くすると配線幅は小さくて済み、従来TCP(テープ・キャリア・パッケージ:Tape Carrier Package)に用いるような配線として厚さ50μmの銅箔を採用すれば、配線幅を6μmと小さくすることができる。

【0107】

また、上記フレキシブル基板201においても、フレキシブル基板101と同様に、フレキシブル基板201と半導体チップ204との間の気泡を半導体チップ204の下面の短辺近傍から半導体チップ搭載領域103外に排出することができる。

【0108】

したがって、上記フレキシブル基板201は、半導体チップ搭載領域103内から半導体チップ搭載領域103外への気泡の排出効果が高いものである。

【0109】

上記第2実施形態では、第2配線部222は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第2配線部222は、ソルダレジスト212で覆わないようにしてもよい。

【0110】

上記第2実施形態では、第3配線部223は、ソルダレジスト112の開口113外に位置するように形成していたが、ソルダレジスト112の開口113内に位置するように形成してもよい。つまり、上記第3配線部223は、ソルダレジスト112で覆わないようにしてもよい。

【0111】

上記第2実施形態において、半導体装置は、ソルダレジスト112の開口113を覆う樹脂を備えてもよい。

【0112】

(第3実施形態)

図6に、本発明の第3実施形態の半導体装置の要部を上方から見た概略図を示す。また、図6において、図1に示した第1実施形態の構成部と同一構成部は、図1における構成部と同一参照番号を付して説明を省略する。また、図6では、上記半導体装置が備える半導体チップの図示を省略している。

【0113】

上記半導体装置は、ジャンパ配線111の第1配線部121に突起電極305を接続している点が、上記第1実施形態とは異なる。

【0114】

上記半導体チップは液晶ドライバである。そして、上記半導体チップの下面(フレキシブル基板101側の表面)には、突起電極105,305が形成されている。また、上記半導体チップの下面は長方形状となっている。

【0115】

上記突起電極305は、半導体チップ104の下面において長辺から少し離れた箇所に形成されている。また、上記突起電極305の電位はグランド電位である。

【0116】

入力信号のシリアル化により動作周波数が高くなった近年の液晶ドライバチップでは高周波回路的設計要素が不可欠であり、グランド電位安定化のため所望の位置にグランド電位の電極を配置したい。このため、上記突起電極305を、半導体チップの下面に形成して、ジャンパ配線111の第1配線部121に接続した。

【0117】

このように、上記突起電極305を、半導体チップの下面に形成して、ジャンパ配線111の第1配線部121に接続することにより、半導体装置の電気的な機能が向上する。

【図面の簡単な説明】

【0118】

【図1】図1は本発明の第1実施形態のフレキシブル基板の要部の概略平面図である。

【図2】図2は本発明の第1実施形態の半導体装置の概略斜視図である。

【図3】図3は図2の半導体チップ搭載領域の拡大図である。

【図4】図4は本発明の第2実施形態の半導体装置の要部の概略平面図である。

【図5】図5は図4のV−V線矢視断面図である。

【図6】図6は本発明の第3実施形態の半導体装置の要部の概略平面図である。

【図7】図7は従来のCOF型半導体装置の概略斜視図である。

【図8】図8は従来のフレキシブル基板の要部の概略平面図である。

【図9】図9は他の従来のフレキシブル基板の要部の概略平面図である。

【符号の説明】

【0119】

100 基材

101,201 フレキシブル基板

102 配線

103 半導体チップ搭載領域

105,205,305 突起電極

106,206 インナーリード

111,211 ジャンパ配線

112 ソルダレジスト

121,221 第1配線部

122,222 第2配線部

123,223 第3配線部

124,224 第4配線部

125,225 第5配線部

【特許請求の範囲】

【請求項1】

半導体チップ搭載領域を一表面に有する基材と、

上記基材の上記一表面上に形成された複数のインナーリードと、

上記インナーリードに結線され、上記半導体チップ搭載領域を横断する配線と

を備えたことを特徴とするフレキシブル基板。

【請求項2】

請求項1に記載のフレキシブル基板において、

上記配線に結線された上記インナーリードの幅は、上記配線に結線されていない上記インナーリードの幅とは異なることを特徴とするフレキシブル基板。

【請求項3】

請求項1に記載のフレキシブル基板において、

上記基材の上記一表面上に形成されたパターン保護膜を備え、

上記配線の上記半導体チップ搭載領域外の部分に関して少なくとも一部が、上記パターン保護膜に覆われずに露出していることを特徴とするフレキシブル基板。

【請求項4】

請求項1に記載のフレキシブル基板において、

上記配線は、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔であることを特徴とするフレキシブル基板。

【請求項5】

請求項1に記載のフレキシブル基板と、

上記フレキシブル基板の上記半導体チップ搭載領域に搭載された半導体チップと

を備えたことを特徴とする半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記半導体チップの上記フレキシブル基板側の表面は長方形状であり、

上記突起電極は、上記半導体チップの上記フレキシブル基板側の表面の短辺近傍以外の部分に形成されていることを特徴とする半導体装置。

【請求項7】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極の電位はグランド電位であることを特徴とする半導体装置。

【請求項8】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極が扱う電流は、上記半導体チップが外部へ出力する電流であることを特徴とする半導体装置。

【請求項1】

半導体チップ搭載領域を一表面に有する基材と、

上記基材の上記一表面上に形成された複数のインナーリードと、

上記インナーリードに結線され、上記半導体チップ搭載領域を横断する配線と

を備えたことを特徴とするフレキシブル基板。

【請求項2】

請求項1に記載のフレキシブル基板において、

上記配線に結線された上記インナーリードの幅は、上記配線に結線されていない上記インナーリードの幅とは異なることを特徴とするフレキシブル基板。

【請求項3】

請求項1に記載のフレキシブル基板において、

上記基材の上記一表面上に形成されたパターン保護膜を備え、

上記配線の上記半導体チップ搭載領域外の部分に関して少なくとも一部が、上記パターン保護膜に覆われずに露出していることを特徴とするフレキシブル基板。

【請求項4】

請求項1に記載のフレキシブル基板において、

上記配線は、厚さ1〜50μmの範囲内、かつ、幅6〜300μmの範囲内の金属箔であることを特徴とするフレキシブル基板。

【請求項5】

請求項1に記載のフレキシブル基板と、

上記フレキシブル基板の上記半導体チップ搭載領域に搭載された半導体チップと

を備えたことを特徴とする半導体装置。

【請求項6】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記半導体チップの上記フレキシブル基板側の表面は長方形状であり、

上記突起電極は、上記半導体チップの上記フレキシブル基板側の表面の短辺近傍以外の部分に形成されていることを特徴とする半導体装置。

【請求項7】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極の電位はグランド電位であることを特徴とする半導体装置。

【請求項8】

請求項5に記載の半導体装置において、

上記半導体チップの上記フレキシブル基板側の表面には複数の突起電極が形成されていて、

上記配線に接続される上記突起電極が扱う電流は、上記半導体チップが外部へ出力する電流であることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2008−177477(P2008−177477A)

【公開日】平成20年7月31日(2008.7.31)

【国際特許分類】

【出願番号】特願2007−11385(P2007−11385)

【出願日】平成19年1月22日(2007.1.22)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成20年7月31日(2008.7.31)

【国際特許分類】

【出願日】平成19年1月22日(2007.1.22)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]