フレキシブル配線基板、及びそれを用いた半導体装置および電子機器

【課題】従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターンの形状を良好にすることができると共に、配線パターンと半導体素子との接続状態を良好にすることができ、非接続部の配線パターンの機械的強度をも従来と比較して同等に向上させることが可能となるフレキシブル配線基板、及びそれを用いた半導体装置および電子機器を提供する。

【解決手段】絶縁テープ6と、絶縁テープ6上に形成された配線パターン57とを備えたフレキシブル配線基板において、配線パターン57は、所定のパターンに形成されていると共に、半導体素子2を接続および搭載する搭載領域内に、半導体素子2と接続するための接続部を有しており、上記接続部のみの配線パターン57の厚さだけが、非接続部における配線層の厚さよりも薄い。

【解決手段】絶縁テープ6と、絶縁テープ6上に形成された配線パターン57とを備えたフレキシブル配線基板において、配線パターン57は、所定のパターンに形成されていると共に、半導体素子2を接続および搭載する搭載領域内に、半導体素子2と接続するための接続部を有しており、上記接続部のみの配線パターン57の厚さだけが、非接続部における配線層の厚さよりも薄い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フレキシブル配線基板、それを用いた半導体装置および電子機器、並びにフレキシブル配線基板の製造方法に関するものである。より詳しくは、半導体素子を搭載するフレキシブル配線基板と、それを用いた半導体装置および電子機器、並びにフレキシブル配線基板の製造方法に関するものである。

【背景技術】

【0002】

フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置としては、TCP(Tape Carrier Package)やCOF(Chip On Film)等がある。これらTCPとCOFとの相違点としては、例えば以下の点が挙げられる。

【0003】

まず、TCPは、予め絶縁テープに半導体素子を搭載させるための開口部が設けられており、配線パターンが片持ち梁状に突き出した状態で形成され、この配線パターンの先端部分と半導体素子とが接合されている。これに対して、COFは、半導体素子を搭載するための開口部を有しておらず、半導体素子は薄膜絶縁テープの表面上に形成された配線パターンに接合・搭載されている点で相違する。

【0004】

また、TCPは、配線パターンが片持ち梁状に突き出した状態であるために、配線パターンの厚みは18μm以上となっており、配線ピッチが45μm未満の配線パターンを製造することが困難である。これに対して、COFは、薄膜絶縁テープの表面上に配線パターンを形成するので、配線パターンの厚みを8μm以下とすることができ、配線ピッチが35μm以下の配線パターンを製造することが容易である点で相違する。

【0005】

また、TCPは、液晶パネル等へ実装した後に折り曲げる部分にはあらかじめスリットが設けられている。これに対して、COFは、折り曲げ用のスリットを有しておらず、薄膜絶縁テープのどこでも自由に折り曲げられる点で相違する。

【0006】

さらに、TCPは、ポリイミドからなる絶縁テープ上に、接着剤を用いて銅箔をラミネートして形成している。これに対して、COFは、銅箔裏面にポリイミド等を塗布、硬化して形成(キャスティング法)する、あるいはポリイミド等からなる薄膜絶縁テープ上に銅をスパッタで積層して形成(スパッタ法、メタライジング法)している点で相違する。

【0007】

COFは、その使用目的から自由に折り曲げることが可能な薄膜絶縁テープが使用される。また、薄膜絶縁テープの表面上に配置された配線パターンの各配線は、半導体素子の対応する端子と電気的に接続され、外部接続用コネクタ部には、液晶パネルやプリント基板などに接続される。上記以外の配線パターン露出部は、ソルダーレジストが塗布され、絶縁状態が確保される。

【0008】

上述のように、COFは、配線パターンのファインピッチ化(微細化)が容易な技術であるものの、実際には配線パターンの配線ピッチ35〜50μm以上に合わせて、配線パターンの厚み8〜18μmが使用されている。ただし、配線パターンの厚みに関する技術が記載された特許文献はない。一方、TCPでは、配線パターンの厚みに関する技術が記載された文献として、例えば特許文献1が挙げられる。

【0009】

また、従来のCOFについて図11および図12に基づいて説明する。図11は、従来のCOF101の概略構成を示す断面図である。図12は、図11に示すC−C’線で切断した場合におけるCOF101の概略構成を示す断面図である。図11および図12に示すように、COF101は、半導体素子102がテープキャリア103上に接続・搭載された構成を有している。

【0010】

図11および図12に示すCOF101のテープキャリア103では、絶縁テープ104上に配線パターン105が形成されている。この配線パターン105は、厚さ8〜18μmの銅箔またはスパッタ銅がキャスティング法またはスパッタ法(メタライジング法)によって形成されている。図11および図12に示すように、配線パターン105は、半導体素子102を接続・搭載する領域とそれ以外の領域との全ての領域において同じ厚さで形成されている。

【特許文献1】特開平10−32227号公報(平成10年(1998)2月3日公開)

【発明の開示】

【発明が解決しようとする課題】

【0011】

上記特許文献1では、半導体素子を搭載する開口部、および折り曲げ用スリット部の配線パターンの厚みは、機械的強度を上げるために厚く(26μm)なっており、液晶パネルや基板と接続するOLB(Outer Lead Bonding)部の配線パターンの厚みは、配線パターンのトップ幅を広くして接続面積を確保するために薄く(18μm)するとしている。

【0012】

しかしながら、実際には半導体素子を搭載する開口部の配線パターンが最もファインピッチとなるため、配線パターンの厚みを薄くする必要性がある。また、全ての箇所を同じ18μmの厚さで形成しても機械的強度には問題はなく、実際の量産品において、18μm厚の配線パターンも採用されている。すなわち、特許文献1に記載された技術は現実的ではなく、また必要性もないものである。このように、実際のTCPでは、配線パターンのファインピッチ化が困難である。

【0013】

これに対して、COFはTCPに比較して、配線パターン(インナーリード)のファインピッチ化が容易である。量産における配線パターン(インナーリード)の配線ピッチは、TCPの限界が45μmであるのに対して、COFは35μmが量産されており、30μm以下も可能であると考えられている。

【0014】

しかしながら、発明者の検討によれば、COFをファインピッチ化する場合には、以下の問題点が見出された。

【0015】

例えば、COFをファインピッチ化する際の問題点の一つとして、配線パターン(インナーリード)のファインピッチ化、特に配線ピッチが30μm以下になった場合に、配線パターンの厚みが現状の8μmでは配線パターン(インナーリード)を良好な形状にパターンエッチングすることが困難になってくることがある。

【0016】

すなわち、配線パターン(インナーリード)のファインピッチ化に伴い、配線パターン(インナーリード)の幅も狭くする必要があり、配線パターンの良好な断面形状である台形にパターンエッチングすることが困難となる。このため、配線パターンの断面形状が、より三角形に近い断面形状になると共に、配線パターン(インナーリード)の厚さバラツキも大きくなってくることがある。

【0017】

この点について図13に基づいて具体的に説明する。図13は、図11および図12に示す従来のCOF101の配線パターン105をファインピッチ化したものである。例えば、配線ピッチが35μmを超える場合はほぼ問題ないものの、35μm未満になると、配線パターン105の良好な断面形状である台形となるようにエッチング加工することが困難になってくる。この場合、図13に示すように、配線パターン105の断面形状は、より三角形に近いものとなる。また、エッチング加工後の配線パターン105の厚さバラツキも大きくなり、半導体素子102と配線パターン105との接続状態が悪くなることがわかる。

【0018】

これを解決する方法としては、銅箔またはスパッタ銅(配線パターン)の薄膜化がある。銅箔またはスパッタ銅(配線パターン)の厚みを薄くすれば、配線パターンを良好な形状にパターンエッチングすることが可能となってくる。例えば、配線パターン(インナーリード)の配線ピッチが30μmの場合でも、銅箔またはスパッタ銅(配線パターン)の厚みを5μm程度に薄くすれば、配線パターンを良好な断面形状である台形にパターンエッチングすることが容易となってくる。

【0019】

しかしながら、配線パターン(インナーリード)のファインピッチ化に伴う配線パターンの薄膜化により、配線パターンの機械的強度が低下するという問題点を有する。このため、半導体素子の接続・搭載工程〜COF半導体装置のモジュール実装工程の間で、配線パターンが断線、または剥離することがある。

【0020】

この点について図14および図15に基づいて具体的に説明する。図14は、図11および図12に示す従来のCOF101の配線パターン105を形成する銅箔またはスパッタ銅の厚さを薄くしたものである。図15は、図14に示すD−D’線で切断した場合におけるCOF101の概略構成を示す断面図である。図14および図15に示すように、銅箔またはスパッタ銅の厚さを薄くすれば、配線パターンを良好な断面形状となるようにエッチング加工することは可能となる。しかしながら、配線パターンの機械的強度が低下するために、半導体素子の接続・搭載工程〜モジュール実装工程の間で、配線パターンの断線、または剥離が発生しやすくなる。

【0021】

現在、COFへの要求の一つとして、多ピン化への対応がある。また、他の要求として小型・薄型化がある。これらの要求も同時に満足するためには、半導体素子との接続部、および配線パターンの外部接続用コネクタ部のファインピッチ化、絶縁テープ、配線パターン等の薄膜化が必要となる。このためには、配線パターン(インナーリード)の幅も小さく、厚みも薄くする必要がある。しかしながら、COFは自由に折り曲げることが可能な反面、配線パターンの薄膜化に伴い機械的強度の向上が必要であり、上述のように、従来の技術では、ファインピッチ化が困難であるという問題点を有している。

【0022】

本発明は、上記問題点を解決するものであり、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターンの形状を良好にすることができると共に、配線パターンと半導体素子との接続状態を良好にすることができ、非接続部の配線パターンの機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターンの断線、または剥離による不良を従来の50%以下に低減でき、さらに、半導体素子との接続時に発生する位置ずれをも低減することができるフレキシブル配線基板、及びそれを用いた半導体装置および電子機器を提供することにある。

【課題を解決するための手段】

【0023】

本発明に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域内に、該電子部品と接続するための接続部を有しており、上記接続部のみの配線層の厚さだけが、非接続部における配線層の厚さよりも薄いことを特徴としている。

【0024】

上記の構成によれば、配線層は、所定のパターンに形成されており、これにより、複数の配線を有している。所定のパターンとは、フレキシブル配線基板の使用用途に応じて任意に決められる複数の配線からなるパターンである。また、配線層の複数の配線には、電子部品と接続するための接続部を有している。この接続部は、電子部品を接続および搭載する搭載領域内に設けられている。すなわち、配線層は、電子部品が搭載される領域としての搭載領域を有しており、この搭載領域内に電子部品と接続する接続部を有する構成となっている。また、絶縁層上に形成された配線層は、接続部における配線層の厚さが、非接続部における配線層の厚さよりも薄くなっている。このため、接続部の加工が容易になる。なお、非接続部とは、配線層における接続部以外の領域のことである。

【0025】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0026】

また、非接続部の配線層の厚さは、接続部の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができる。

【0027】

また、本発明に係るフレキシブル配線基板では、上記配線層は、搭載領域における非接続部の厚さと、非搭載領域における非接続部の厚さとが同じであることが好ましい。上記の構成によれば、非接続部が全領域に渡って同じ厚さとなっていることから、配線層の機械的強度をより向上させることができ、フレキシブル配線基板を折り曲げる最においても、パターンの断線、または剥離の発生を防止することが可能となる。

【0028】

本発明に係るフレキシブル配線基板では、上記パターンにおける少なくとも1組の隣接する配線の間隔が35μm未満である場合に、より効果がある。上記の構成によれば、配線層のパターンのファインピッチ化が可能になる。

【0029】

本発明に係るフレキシブル配線基板では、上記搭載領域または接続部における配線層の厚さが3〜6μmの範囲内であることが好ましい。上記の構成によれば、搭載領域または接続部の配線をエッチングする場合であっても、断面が良好な形状となるようにエッチングすることが可能となる。また、パターンの各配線の厚さバラツキを低減することが可能となり、電子部品との接続状態を良好にすることが可能となる。

【0030】

本発明に係るフレキシブル配線基板では、上記非搭載領域または非接続部における配線層の厚さが8μm以上であることが好ましい。上記の構成によれば、配線層の機械的強度を向上させることができるため、フレキシブル配線基板を折り曲げる最においても、パターンの断線、または剥離の発生を防止することが可能となる。

【0031】

本発明に係るフレキシブル配線基板では、上記接続部は、インナーリード部である。上記の構成によれば、搭載領域内には接続部を有しており、電子部品との接続状態を良好にすることができると共に、配線層の機械的強度を向上させることができる。

【0032】

本発明に係る半導体装置は、上記課題を解決するために、上記いずれかに記載のフレキシブル配線基板と、フレキシブル配線基板の接続部に接続された半導体素子とを備えていることを特徴としている。上記の構成によれば、配線のファインピッチ化が可能であると共に、機械的強度を向上させた半導体装置とすることができる。

【0033】

本発明に係る電子機器は、上記課題を解決するために、上記半導体装置を備えていることを特徴としている。上記の構成によれば、配線のファインピッチ化が可能であると共に、機械的強度を向上させた電子機器とすることができる。

【発明の効果】

【0034】

本発明に係るフレキシブル配線基板は、以上のように、配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域を有しており、上記搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄くなっている。また、本発明に係るフレキシブル配線基板の製造方法は、以上のように、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層の、電子部品と接続する部分の厚さを薄くする薄層化工程をさらに有している。また、本発明に係るフレキシブル配線基板の製造方法は、以上のように、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層形成工程は、第1配線層を形成する第1配線層形成工程と、上記第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層を形成する第2配線層形成工程とを有している。このため、配線層のパターンのエッチング形状や電子部品との接続状態を良好にすることで微細化(ファインピッチ化)することが可能になると共に、配線層の機械的強度を向上させることができ、接続不良を防止すると共にフレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0035】

〔参考形態1〕

本発明の参考形態1について図1ないし図4に基づいて説明すれば以下の通りである。図1は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図2は、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0036】

図1および図2に示すように、半導体装置1は、半導体素子(電子部品)2およびテープキャリア(フレキシブル配線基板)3を備えている。半導体素子2は、テープキャリア3と接続され、テープキャリア3上に搭載された状態になっている。また、テープキャリア3と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。このように、本参考形態では、テープキャリア3上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。

【0037】

上記半導体素子2としては、例えば、CPU(Central Processing Unit)やメモリ等の集積回路(LSI:Large Scaled Integrated circuit)を挙げることができる。また、半導体素子2には突起電極5が複数設けられている。

【0038】

突起電極5は、半導体素子2をテープキャリア3に搭載する際に、テープキャリア3と対向する側の面から略垂直方向に突出した電極であり、半導体素子2とテープキャリア3とを電気的に接続するために用いられる電極である。このため、突起電極5は導電性材料からなっていればよく、その形状は限定されない。ただし、テープキャリア3との接続が容易となる形状であることが好ましい。突起電極5としては、例えば、Auや半田からなる円柱状、角柱状またはボール状の電極とすることができる。

【0039】

テープキャリア3は、半導体素子2を接続・搭載するためのものであり、絶縁テープ(絶縁層)6、配線パターン(配線層、パターン)7、ソルダーレジスト8を備えている。

【0040】

絶縁テープ6は、その面上に配線パターン7を配置するための基材である。絶縁テープ6は、絶縁性を有することはもちろん、様々な形状で使用されることから、自由に折り曲げることが可能な柔軟性の高い(可撓性を有する)ことが必要である。このため、絶縁テープ6を形成する材料としては、例えば、ポリイミド、ガラスエポキシ、ポリエステルなどの樹脂材料が用いられる。なお、本参考形態では、ポリイミド樹脂を用いた絶縁テープ6を例に挙げて説明する。

【0041】

また、絶縁テープ6は、折り曲げを容易にするために、また、半導体装置1を小型化・薄型化するために、薄膜のテープ状基材であることが好ましい。絶縁テープ6の厚さは、使用目的に応じて適宜設定すればよいが、例えば、15〜40μmの範囲内であることが好ましい。

【0042】

配線パターン7は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン7は、銅箔またはスパッタ銅(以下、単に「銅箔」と総称する)をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。本参考形態では配線パターン7に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0043】

なお、半導体装置1を他の電子部品と接続するために、配線パターン7には外部接続用端子(図示せず)が設けられている。また、上記配線パターン7の表面には、図示しない錫メッキや金メッキが施されている。この配線パターン7の詳細な構成については後述する。

【0044】

ソルダーレジスト8は、配線パターン7上に形成されたレジストである。ソルダーレジスト8は、例えば耐熱性被覆材料からなっており、接続部以外の露出を防止するものである。従って、ソルダーレジスト8は、半導体素子2が搭載される領域以外の部分や、外部接続用端子が設けられていない部分の配線パターン7上に形成されている。すなわち、ソルダーレジスト8は、テープキャリア3上に半導体素子2等を接続・搭載した際に、露出する配線パターン7上に形成されている。

【0045】

上記絶縁テープ6には、半導体素子2を搭載するための開口部が設けられていない。このため、半導体素子2に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン7とを接合することによって、絶縁テープ6に半導体素子2が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン7の各配線と、各配線に対応する半導体素子2の突起電極5とを接続することにより行われる。これにより、配線パターン7と半導体素子2とが電気的に接続される。

【0046】

上記配線パターン7は、部分的に厚さが異なっている。具体的には、配線パターン7における、半導体素子2が接続・搭載される領域(搭載領域;接続部)の厚さが、半導体素子2が接続・搭載されない領域(非搭載領域)の厚さよりも薄くなっている。これにより、搭載領域では配線パターン7をファインピッチ化することが可能となり、非搭載領域では配線パターン7の機械的強度を向上させることが可能となり、半導体装置1の強度も向上する。

【0047】

なお、搭載領域とは、配線パターン7と半導体素子2とが接続・搭載される領域のことである。すなわち、搭載領域は、突起電極5と配線パターン7とが接続する部分を示すものであるが、半導体素子2をテープキャリア3上に搭載した際に、半導体素子2の占める領域を示す。従って、搭載領域にて半導体素子2と接続される配線パターン7は、いわゆるインナーリードである。また、非搭載領域とは、搭載領域以外の領域のことである。

【0048】

また、接続部とは、配線パターン7のうち、半導体素子2と実際に接続される部分のことを示し、非接続部とは、接続部以外の領域のことである。本参考形態では、接続部は、搭載領域に含まれている。

【0049】

上記搭載領域の配線パターン7の厚さは、例えば、3〜6μmの範囲内であることが好ましい。配線パターン7の厚さが3μm未満の場合には、絶縁テープ6の表面に突起電極5が接触してしまうといった不具合が発生してしまうことがある。また、配線パターン7の厚さが6μmを超える場合には、エッチングによる配線パターン7の形状や半導体素子2との接続状態を良好にすることが困難となる。

【0050】

ただし、搭載領域の配線パターン7の厚さは、上記厚さに限定されるものではない。すなわち、搭載領域の配線パターン7の厚さは、配線パターン7のファインピッチ化を可能とするための厚さ、すなわち配線パターン7をパターンエッチングにより良好な形状とすることを可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0051】

また、上記配線パターン7は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリア3とすることができる。

【0052】

なお、上記半導体装置1は、他の電子部品と接続することによって半導体モジュール(電子機器)9とすることもできる。この半導体モジュール9では、例えば、半導体装置1が他の電子部品を駆動・制御することもできる。図3は、本参考形態における半導体モジュール9の概略構成を示す断面図である。図3では、半導体装置1を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール9では、半導体装置1における配線パターン7の外部接続用端子と、上記液晶パネル10や他のプリント基板11等とが接続されている。

【0053】

次に、上記構成を有する半導体装置1の製造方法について図4に基づいて説明する。図4は、半導体装置1の製造方法の概略構成を示す断面図である。本参考形態における半導体装置1の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン7を形成する前に、搭載領域の銅箔の厚みをハーフエッチングによって非搭載領域の銅箔の厚みよりも薄くする方法である。

【0054】

まず、図4(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔(配線層)12を形成する。ここで、キャスティング法とは、銅箔にポリイミドを塗布した後に硬化させる方法である。一方、スパッタ法(メタライジング法)とは、ポリイミドやカプトン等のフィルム上にスパッタリングで金属シード層を形成した後に、電気メッキによって金属シード層上に銅メッキを析出させ、銅メッキを積み上げる方法である。

【0055】

次に、図4(b)に示すように、搭載領域に相当する部分の銅箔12の表面にエッチング加工を施す。このエッチング加工は、搭載領域の銅箔12の厚さが非搭載領域の銅箔12の厚さよりも薄くなるように行われる。このエッチング加工を、以下においてはハーフエッチングと称することもある。

【0056】

搭載領域の銅箔12の厚さが所望の厚さとなるように、ハーフエッチングは、例えば、テープ整面塗布装置を用い、温度、時間、速度、等を調整することにより、銅箔12の厚さを制御することができる。

【0057】

そして、図4(c)に示すように、銅箔12が所定のパターンとなるように、銅箔12に対するエッチング加工を行い、所望の配線パターン7を形成する。この配線パターン7の形成は、搭載領域および非搭載領域の配線パターン7を形成すべき全ての領域において行われる。その後、図4(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン7上にソルダーレジスト8を塗布する。これにより、テープキャリア3が作製される。

【0058】

次に、上記にて作製されたテープキャリア3上に半導体素子2を接続・搭載する。この接続は、突起電極5と配線パターン7とが対応するように半導体素子2とテープキャリア3とを配置し、この突起電極5と配線パターン7とを接続することによって行われる。この接続は、例えばAu−Sn共晶接合などにより行うことができる。これにより、半導体素子2がテープキャリア3上に接続・搭載される。

【0059】

テープキャリア3上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア3との間にできる隙間に、絶縁性樹脂4が注入され封止される。絶縁性樹脂4を注入・封止することにより、半導体素子2と配線パターン7との接続部分における外部との絶縁状態を確保することができる。これにより、本参考形態の半導体装置1が製造される。

【0060】

なお、上記半導体装置1を他の電子部品と接続する場合には、配線パターン7の外部接続用端子に、例えば、液晶パネルやプリント基板等を接続すればよい。

【0061】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア3では、搭載領域の配線パターン7の厚さが、非搭載領域の配線パターン7の厚さよりも薄くなっている。特に、非搭載領域の配線パターン7の厚さが8〜18μmであるのに対して、搭載領域の配線パターン7の厚さは3〜6μmとなっている。

【0062】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン7の形状を良好にすることができると共に、配線パターン7と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン7の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン7の断線、または剥離による不良を従来の50%以下に低減できる。

【0063】

〔参考形態2〕

本発明の参考形態2について図1ないし図3および図5に基づいて説明すれば以下の通りである。図1は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図2は、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0064】

図1に示すように、半導体装置1は、半導体素子2およびテープキャリア3を備えている。本参考形態では、上記参考形態1と比較して、半導体装置1の製造方法が異なるものであり、半導体装置1の構成は同一である。このため、参考形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置1の製造方法について説明する。また、特に断らない限り、本参考形態で用いる用語についても、上記参考形態1と同様の意味とする。

【0065】

ここで、本参考形態における半導体装置1の製造方法について図5に基づいて具体的に説明する。図5は、本参考形態における半導体装置1の製造方法の概略構成を示す断面図である。

【0066】

本参考形態の半導体装置1の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン7を形成した後に、搭載領域の銅箔の厚みをハーフエッチングによって非搭載領域の銅箔の厚みよりも薄くする方法である。

【0067】

まず、図5(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔12を形成する。

【0068】

次に、図5(b)に示すように、銅箔12が所定のパターンとなるように、銅箔12に対するエッチング加工を行い、所望の配線パターン7を形成する。この配線パターン7の形成は、搭載領域および非搭載領域の配線パターン7を形成すべき全ての領域において行われる。

【0069】

そして、図5(c)に示すように、搭載領域に相当する部分の配線パターン7の表面にエッチング加工を施す。このエッチング加工は、ハーフエッチングにて行われる。すなわち、搭載領域の配線パターン7の厚さが非搭載領域の配線パターン7の厚さよりも薄くなるように行われる。その後、図5(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン7上にソルダーレジスト8を塗布する。これにより、テープキャリア3が作製される。

【0070】

次に、上記参考形態1と同様にして半導体素子2をテープキャリア3上に接続・搭載する。そして、テープキャリア3上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア3との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置1が製造される。

【0071】

なお、上記半導体装置1を他の電子部品と接続して半導体モジュール9とする場合には、図3に示すように、配線パターン7の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0072】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア3では、搭載領域の配線パターン7の厚さが、非搭載領域の配線パターン7の厚さよりも薄くなっている。特に、非搭載領域の配線パターン7の厚さが8〜18μmであるのに対して、搭載領域の配線パターン7の厚さは3〜6μmとなっている。

【0073】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン7の形状を良好にすることができると共に、配線パターン7と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン7の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン7の断線、または剥離による不良を従来の50%以下に低減できる。

【0074】

また、本参考形態におけるテープキャリア3は、エッチング加工による配線パターン7の形成後に、搭載領域の配線パターン7の厚みをハーフエッチングによって薄くしている。このため、参考形態1のテープキャリア3と比較して、搭載領域の配線パターン7の厚みをより均一にすることが可能となる。

【0075】

〔参考形態3〕

本発明の参考形態3について図6ないし図9に基づいて説明すれば以下の通りである。図6は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図7は、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0076】

図6および図7に示すように、半導体装置21は、半導体素子2およびテープキャリア(フレキシブル配線基板)23を備えている。半導体素子2はテープキャリア23と接続され、テープキャリア23上に搭載された状態になっている。また、テープキャリア23と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。本参考形態においても、テープキャリア23上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。なお、参考形態1および2にて説明した部材と同一の部材については、同一の符号を付し、その説明を省略する。また、本参考形態で用いる用語で、参考形態1と同じ用語については、特に断らない限り同様の意味とする。

【0077】

半導体素子2には突起電極5が複数設けられている。また、テープキャリア23は、半導体素子2を接続・搭載するためのものであり、絶縁テープ6、配線パターン(配線層、パターン)27、ソルダーレジスト8を備えている。

【0078】

配線パターン27は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン27は、銅箔またはスパッタ銅(以下、単に「銅箔」と総称する)をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。なお、参考形態においても、配線パターン7に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0079】

配線パターン27は、第1配線層27aおよび第2配線層27bを備えている。第1配線層27aは、絶縁テープ6上に設けられた銅箔からなる層であり、第2配線層27bは、第1配線層27a上に設けられた銅箔からなる層である。

【0080】

上記第2配線層27bは、第1配線層27a上の一部分に設けられている。本参考形態では、第2配線層27bは、第1配線層27a上の非搭載領域に設けられている。すなわち、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン27の厚さよりも厚くなっている。これにより、第1配線層27aの厚さを制御することで、配線パターン27のファインピッチ化が可能となる。また、第2配線層27bの厚さを制御することで、配線パターン27の機械的強度を向上させることが可能となる。

【0081】

上記第1配線層27aの厚さは、例えば、3〜6μmの範囲内であることが好ましい。第1配線層27aの厚さが3μm未満の場合には、絶縁テープ6の表面に突起電極5が接触してしまうといった不具合が発生してしまうことがある。また、第1配線層27aの厚さが6μmを超える場合には、エッチングによる配線パターン27の形状を良好にすることや、半導体素子2との接続状態を良好にすることが困難となる。

【0082】

また、第2配線層27bの厚さは、第1配線層27aの厚さに応じて適宜設定すればよい。例えば、第1配線層27aの厚さが3〜6μmの範囲内である場合には、第2配線層27bの厚さは、第1配線層27aの厚さとの合計が8〜18μmの範囲内となる厚さであることが好ましい。

【0083】

ただし、第1配線層27aの厚さは、上記厚さに限定されるものではない。すなわち、第1配線層27aの厚さは、配線パターン27のファインピッチ化を可能とするための厚さ、すなわち配線パターン27をパターンエッチングにより良好な形状とすることを可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0084】

また、第2配線層27bの厚さも上記厚さに限定されるものではなく、第1配線層27aと第2配線層27bとの合計の厚みによって、機械的強度が十分に得られる厚さであればよい。

【0085】

また、上記配線パターン27は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリア23とすることができる。

【0086】

なお、半導体装置21を他の電子部品と接続するために、配線パターン27には外部接続用端子(図示せず)が設けられている。また、上記配線パターン27の表面には、図示しない錫メッキや金メッキが施されている。

【0087】

また、上記絶縁テープ6には、半導体素子21を搭載するための開口部が設けられていない。このため、半導体素子21に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン27とを接合することによって、絶縁テープ6に半導体素子21が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン27の各配線と、各配線に対応する半導体素子21の突起電極5とを接続することにより行われる。これにより、配線パターン27と半導体素子21とが電気的に接続される。

【0088】

なお、上記半導体装置21は、他の電子部品と接続することによって半導体モジュール(電子機器)29とすることもできる。この半導体モジュール29では、例えば、半導体装置21が他の電子部品を駆動・制御することもできる。図8は、本参考形態における半導体モジュール29の概略構成を示す断面図である。図8では、半導体装置21を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール29では、半導体装置21における配線パターン27の外部接続用端子と、上記液晶パネル10や他のプリント基板11等とが接続されている。

【0089】

次に、上記構成を有する半導体装置21の製造方法について図9に基づいて説明する。図9は、半導体装置21の製造方法の概略構成を示す断面図である。本参考形態における半導体装置21の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン27を形成する前に、非搭載領域の銅箔の厚みを電気メッキ等によって搭載領域の銅箔の厚みよりも厚くする方法である。

【0090】

まず、図9(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層32を形成する。そして、図9(b)に示すように、非搭載領域に相当する部分の第1銅箔層32上に、さらに第2銅箔層33を形成する。

【0091】

この第2銅箔層33は、例えば電気メッキにより銅メッキを析出させて、第1銅箔層32上に積み上げることによって形成される。これにより、搭載領域と非搭載領域との銅箔の厚みを異ならせることができる。また、電気メッキにより第2銅箔層33を形成する場合には、第2銅箔層33の厚さを任意に制御することができる。このため、第1銅箔層32の厚さに応じて第2銅箔層33の厚さを適宜変更することが可能となる。従って、例えば、第1銅箔層32と第2銅箔層33との合計の厚さが8〜18μmとなるように第2銅箔層33を形成することも容易となる。

【0092】

そして、図9(c)に示すように、第1銅箔層32および第2銅箔層33が所定のパターンとなるように、第1銅箔層32および第2銅箔層33に対するエッチング加工を行い、所望の配線パターン27を形成する。これにより、第1配線層27aおよび第2配線層27bからなる配線パターン27が形成される。この配線パターン27の形成は、搭載領域および非搭載領域の配線パターン27を形成すべき全ての領域において行われる。

【0093】

その後、図9(d)に示すように、後の工程で半導体素子22を搭載した際に露出する部分の配線パターン27上にソルダーレジスト8を塗布する。これにより、テープキャリア23が作製される。

【0094】

次に、上記にて作製されたテープキャリア23上に半導体素子2を接続・搭載する。この接続は、突起電極5と配線パターン27とが対応するように半導体素子2とテープキャリア23とを配置し、この突起電極5と配線パターン27とを接続することによって行われる。この接続は、例えばAu−Sn共晶接合などにより行うことができる。これにより、半導体素子22がテープキャリア23上に接続・搭載される。

【0095】

テープキャリア23上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア23との間にできる隙間に、絶縁性樹脂4が注入され封止される。絶縁性樹脂4を注入・封止することにより、半導体素子2と配線パターン27との接続部分における外部との絶縁状態を確保することができる。これにより、本参考形態の半導体装置21が製造される。

【0096】

なお、上記半導体装置21を他の電子部品と接続する場合には、配線パターン27の外部接続用端子に、例えば、液晶パネルやプリント基板等を接続すればよい。

【0097】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア23では、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン7の厚さよりも厚くなっている。特に、搭載領域の配線パターン27の厚さは3〜6μmであるのに対して、非搭載領域の配線パターン27の厚さが8〜18μmとなっている。

【0098】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン27の形状を良好にすることができると共に、配線パターン27と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン27の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン27の断線、または剥離による不良を従来の50%以下に低減できる。

【0099】

〔参考形態4〕

本発明の参考形態4について図6ないし図8および図10に基づいて説明すれば以下の通りである。図6は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図7は、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0100】

図6に示すように、半導体装置21は、半導体素子2およびテープキャリア23を備えている。本参考形態では、上記参考形態3と比較して、半導体装置21の製造方法が異なるものであり、半導体装置21の構成は同一である。このため、参考形態3にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置21の製造方法について説明する。また、特に断らない限り、本参考形態で用いる用語についても、上記参考形態3と同様の意味とする。

【0101】

ここで、本参考形態における半導体装置21の製造方法について図10に基づいて具体的に説明する。図10は、本参考形態における半導体装置21の製造方法の概略構成を示す断面図である。

【0102】

本参考形態の半導体装置21の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン27を形成した後に、非搭載領域の銅箔の厚みを電気メッキ等によって搭載領域の銅箔の厚みよりも厚くする方法である。

【0103】

まず、図10(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層32を形成する。

【0104】

次に、図10(b)に示すように、第1銅箔層32が所定のパターンとなるように、第1銅箔層32に対するエッチング加工を行い、所望のパターンを有する第1配線層27aを形成する。この第1配線層27aの形成は、搭載領域および非搭載領域の配線パターン27を形成すべき全ての領域において行われる。

【0105】

そして、図10(c)に示すように、非搭載領域に相当する部分の第1配線層27a上に、さらに銅箔を積み上げて第2配線層27bを形成する。これにより、所望のパターンの形状にエッチング加工された第1配線層27aおよび第2配線層27bからなる配線パターン27が形成される。この第2配線層27bは、例えば電気メッキにより銅メッキを析出させて、第1配線層27a上に積み上げることによって形成される。

【0106】

これにより、搭載領域と非搭載領域との配線パターン27の厚みを異ならせることができる。また、電気メッキにより第2配線層27bを形成する場合には、第2配線層27bの厚さを任意に制御することができる。このため、第1配線層27aの厚さに応じて第2配線層27bの厚さを適宜変更することが可能となる。従って、例えば、第1配線層27aと第2配線層27bとの合計の厚さが8〜18μmとなるように第2配線層27bを形成することも容易となる。

【0107】

その後、図10(d)2に示すように、後の工程で半導体素子を搭載した際に露出する部分の配線パターン27上にソルダーレジスト8を塗布する。これにより、テープキャリア23が作製される。

【0108】

次に、上記参考態3と同様にして半導体素子2をテープキャリア23上に接続・搭載する。そして、テープキャリア23上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア23との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置21が製造される。

【0109】

なお、参考形態3と同様に、上記半導体装置21を他の電子部品と接続して半導体モジュールとする場合には、図8に示すように、配線パターン27の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0110】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア23では、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン27の厚さよりも厚くなっている。特に、搭載領域の配線パターン27の厚さは3〜6μmであるのに対して、非搭載領域の配線パターン27の厚さが8〜18μmとなっている。

【0111】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン27の形状を良好にすることができると共に、配線パターン27と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン27の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン27の断線、または剥離による不良を従来の50%以下に低減できる。

【0112】

〔実施の形態1〕

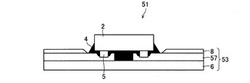

本発明の第1の実施の形態について図16ないし図18に基づいて説明すれば以下の通りである。図16は、本実施の形態に係る半導体装置の概略構成を示す断面図である。

【0113】

図16に示すように、半導体装置51は、半導体素子2およびテープキャリア(フレキシブル基板)53を備えている。半導体素子2はテープキャリア53と接続され、テープキャリア53上に搭載された状態になっている。また、テープキャリア53と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。本実施の形態においても、テープキャリア53上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。なお、参考形態1にて説明した部材と同一の部材については、同一の符号を付し、その説明を省略する。また、本実施の形態で用いる用語で、参考形態1と同じ用語については、特に断らない限り同様の意味とする。

【0114】

半導体素子2には突起電極5が複数設けられている。また、テープキャリア53は、半導体素子2を接続・搭載するためのものであり、絶縁テープ6、配線パターン57、ソルダーレジスト8を備えている。

【0115】

配線パターン57は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン57は、銅箔をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。なお、本実施の形態においても、配線パターン57に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0116】

上記配線パターン57は、部分的に厚さが異なっている。具体的には、配線パターン57と半導体素子2とが接続されている部分(接続部)のみの厚さが、それ以外の部分(非接続部)の厚さよりも薄くなっている。これにより、接続部では配線パターン57をファインピッチ化することが可能となり、非接続部では配線パターン57の機械的強度を向上させることが可能となり、半導体装置51の強度も向上する。

【0117】

また、本実施の形態では、接続部の厚さのみ薄くなっており、接続部の外側および内側(接続部よりも搭載領域外側および搭載領域内側)で厚くなっている。さらに、本実施の形態では、接続部の外側の配線パターン57の厚さと、接続部の内側の配線パターン57の厚さとが同じ厚さになっている。

【0118】

なお、接続部とは、半導体素子2の突起電極5と配線パターン57とが接続されている部分のことであり、上記搭載領域に含まれている。すなわち、搭載領域のうち、半導体素子2の突起電極5と配線パターン57とが接続する部分が接続部となっている。

【0119】

また、上記接続部は、接続部の長さが突起電極(接続部材)5の長さよりも40μm程度大きくなるように形成されている。この「接続部の長さ」とは、接続部における配線パターン57の厚さが薄くなっている部分の長さのことであり、「突起電極5の長さ」とは、突起電極5の設計長のことである。すなわち、この場合、突起電極5を接続部の中央部分に接続すると、突起電極5の側端部と接続部の端部との距離が20μm程度となる。このように形成することで、例えば、半導体素子2のテープキャリア53への接続精度が±15μmであり、突起電極5の製造サイズの公差が±10μmである場合においても、半導体素子2が接続部を外れた状態でテープキャリア53に接続されることを回避することができる。ただし、上記大きさは40μmに限定されるものではない。また、上記接続部の配線パターン57の厚さは、例えば、3〜6μmの範囲内であることが好ましい。ただし、配線パターン57の厚さはこれに限定されるものではなく、配線パターン57のファインピッチ化を可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0120】

また、上記配線パターン57は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリアとすることができる。

【0121】

なお、半導体装置51を他の電子部品と接続するために、配線パターン57には外部接続用端子(図示せず)が設けられている。また、上記配線パターン57の表面には、図示しない錫メッキや金メッキが施されている。

【0122】

また、上記絶縁テープ6には、半導体素子2を搭載するための開口部が設けられていない。このため、半導体素子2に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン57とを接合することによって、絶縁テープ6に半導体素子2が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン57の各配線と、各配線に対応する半導体素子2の突起電極5とを接続することにより行われる。これにより、配線パターン57と半導体素子2とが電気的に接続される。

【0123】

なお、上記半導体装置51は、他の電子部品と接続することによって半導体モジュールとすることもできる。この半導体モジュールでは、例えば、半導体装置51が他の電子部品を駆動・制御することもできる。図17は、本実施の形態における半導体モジュール59の概略構成を示す断面図である。図17では、半導体装置51を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール59では、半導体装置51における配線パターン57の外部接続用端子と、上記液晶パネルや他のプリント基板等とが接続されている。

【0124】

次に、上記構成を有する半導体装置51の製造方法について図18に基づいて説明する。図18は、半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態における半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成する前に、接続部に相当する部分の銅箔の厚みをハーフエッチングによって、非接続部の銅箔の厚みよりも薄くする方法である。

【0125】

まず、図18(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔62を形成する。

【0126】

次に、図18(b)に示すように、接続部に相当する部分(ライン)の銅箔62の表面にエッチング加工(ハーフエッチング)を施す。このエッチング加工は、接続部の銅箔62の厚さが非接続部の銅箔62の厚さよりも薄くなるように行われる。また、このエッチング加工は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように行われる。

【0127】

そして、図18(c)に示すように、銅箔62が所定のパターンとなるように、銅箔62に対するエッチング加工を行い、所望の配線パターン57を形成する。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域において行われる。その後、図18(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0128】

次に、上記参考形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0129】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0130】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0131】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。

【0132】

また、接続部の配線パターン57の厚さのみを薄くしており、非接続部の配線パターン57の厚さは、従来のCOF型の半導体装置用のテープキャリアと同等であることから、非接続部の配線パターン57の機械的強度を従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良をより低減できると共に、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0133】

〔実施の形態2〕

本発明の第2の実施の形態について図16、図17および図19に基づいて説明すれば以下の通りである。

【0134】

図16は、本実施の形態に係る半導体装置51の概略構成を示す断面図である。本実施の形態では、上記実施の形態1と比較して、半導体装置51の製造方法が異なるものであり、半導体装置51の構成は同一である。このため、実施の形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本実施の形態では、主として、半導体装置51の製造方法について説明する。また、本実施の形態で用いる用語についても、上記実施の形態1と同様の意味とする。

【0135】

本実施の形態における半導体装置51の製造方法について図19に基づいて具体的に説明する。図19は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成した後に、接続部の銅箔の厚みをハーフエッチングによって非接続部の銅箔の厚みよりも薄くする方法である。

【0136】

まず、図19(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔62を形成する。

【0137】

次に、図19(b)に示すように、銅箔62が所定のパターンとなるように、銅箔62に対するエッチング加工を行い、所望の配線パターン57を形成する。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域において行われる。

【0138】

そして、図19(c)に示すように、接続部に相当する部分の配線パターン57の表面にエッチング加工を施す。このエッチング加工は、ハーフエッチングにて行われる。すなわち、接続部の配線パターン57の厚さが非接続部の配線パターン57の厚さよりも薄くなるように行われる。また、このエッチング加工は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように行われる。

【0139】

その後、図19(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジストを塗布する。これにより、テープキャリア53が作製される。

【0140】

次に、上記実施の形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0141】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0142】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0143】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0144】

〔実施の形態3〕

本発明の第3の実施の形態について図16、図17および図20に基づいて説明すれば以下の通りである。

【0145】

図16は、本実施の形態に係る半導体装置51の概略構成を示す断面図である。本実施の形態の半導体装置51は、配線パターン57が2層(第1配線層および第2配線層)から構成されているものであり、上記実施の形態1と比較して基本的な構成は同一である。このため、実施の形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本実施の形態では、主として、半導体装置51の製造方法について説明する。また、本実施の形態で用いる用語についても、上記実施の形態1と同様の意味とする。

【0146】

本実施の形態における半導体装置51の製造方法について図20に基づいて具体的に説明する。図20は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成する前に、非接続部の銅箔の厚みを電気メッキ等によって接続部の銅箔の厚みよりも厚くする方法である。

【0147】

まず、図20(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層72を形成する。そして、図20(b)に示すように、非接続部に相当する部分の第1銅箔層72上に、さらに第2銅箔層73を形成する。第2銅箔層73は、第1銅箔層72と第2銅箔層73との合計の厚さが8〜18μmとなるように形成される。また、第2銅箔層73は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように形成される。

【0148】

そして、図20(c)に示すように、第1銅箔層72および第2銅箔層73が所定のパターンとなるように、第1銅箔層72および第2銅箔層73に対するエッチング加工を行い、所望の配線パターン57を形成する。これにより、第1配線層57aおよび第2配線層57bからなる配線パターン57が形成される。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域にて行われる。

【0149】

その後、図20(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0150】

次に、上記実施の形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0151】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0152】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0153】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0154】

〔参考形態5〕

本発明の参考形態5について図16、図17および図21に基づいて説明すれば以下の通りである。

【0155】

図16は、本参考形態に係る半導体装置51の概略構成を示す断面図である。本参考形態の半導体装置51は、配線パターン57が2層(第1配線層および第2配線層)から構成されているものであり、上記実施の形態5と比較して基本的な構成は同一である。このため、実施の形態5にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置51の製造方法について説明する。また、本参考形態で用いる用語についても、上記実施の形態5と同様の意味とする。

【0156】

本参考形態における半導体装置51の製造方法について図21に基づいて具体的に説明する。図21は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本参考形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成した後に、非接続部の銅箔の厚みを電気メッキ等によって接続部の銅箔の厚みよりも厚くする方法である。

【0157】

まず、図21(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層72を形成する。

【0158】

次に、図21(b)に示すように、第1銅箔層72が所定のパターンとなるように、第1銅箔層72に対するエッチング加工を行い、所望のパターンを有する第1配線層57aを形成する。この第1配線層57aの形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域にて行われる。

【0159】

そして、図21(c)に示すように、非接続部に相当する部分の第1配線層57a上に、さらに銅箔を積み上げて第2配線層57bを形成する。これにより、所望のパターンの形状にエッチング加工された第1配線層57aおよび第2配線層57bからなる配線パターン57が形成される。この第2配線層57bは、例えば電気メッキにより銅メッキを析出させて、第1配線層57a上に積み上げることによって形成される。また、第2配線層57は、第1配線層57aと第2配線層57bとの合計の厚さが8〜18μmとなるように形成される。さらに、第2銅箔層73は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように形成される。

【0160】

その後、図21(d)に示すにように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0161】

次に、上記実施の形態5と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置51が製造される。

【0162】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0163】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0164】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0165】

なお、本発明のテープキャリアは、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF半導体装置となる薄膜の絶縁テープであり、前記半導体素子を接続・搭載する領域の前記配線パターンの配線ピッチが35μm未満となる前記絶縁テープにおいて、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さよりも、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さを薄く形成しているCOF半導体装置用テープキャリアとも表現できる。上記のテープキャリアでは、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さを3〜6μmに形成していてもよい。

【0166】

また、本発明のテープキャリアの製造方法は、前記配線パターンをパターンエッチングにより形成する前に、後に前記半導体素子を接続・搭載する前記配線パターンの形成領域の厚さをハーフエッチングにより、その他の領域より薄くした後に、その他の領域を含め、前記配線パターンをパターンエッチングにより形成する方法とも表現できる。

【0167】

上記の製造方法では、前記配線パターンをパターンエッチングにより形成した後に、後に前記半導体素子を接続・搭載する領域の前記配線パターンの厚さをハーフエッチングにより、その他の領域の前記配線パターンより薄く形成していてもよい。

【0168】

また、本発明のテープキャリアは、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF半導体装置となる薄膜の絶縁テープであり、前記半導体素子を接続・搭載する領域の前記配線パターンの配線ピッチが35μm未満となる前記絶縁テープにおいて、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さよりも、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さを厚く形成しているCOF半導体装置用テープキャリアとも表現できる。上記のテープキャリアでは、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さを8μm以上に形成していてもよい。

【0169】

また、本発明のテープキャリアの製造方法は、前記配線パターンをパターンエッチングする前に、後に前記半導体素子を接続・搭載する領域以外の前記配線パターン形成領域の厚さをスパッタ法(メタライジング法)により、前記半導体素子を接続・搭載する前記配線パターンの形成領域より厚く積み上げた後に、前記配線パターンをパターンエッチングにより形成する方法とも表現できる。

【0170】

上記の製造方法では、前記配線パターンをパターンエッチングにより形成した後に、後に前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さをスパッタ法(メタライジング法)により、前記半導体素子を接続・搭載する領域の前記配線パターンより、厚く積み上げて形成していてもよい。

【0171】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【0172】

〔参考形態〕

本参考例に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域を有しており、上記搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄いことを特徴としている。

【0173】

上記の構成によれば、配線層は、所定のパターンに形成されており、これにより、複数の配線を有している。所定のパターンとは、フレキシブル配線基板の使用用途に応じて任意に決められる複数の配線からなるパターンである。また、配線層は、電子部品を接続および搭載する搭載領域を有している。搭載領域とは、配線層のうち電子部品が搭載される領域のことであり、具体的には電子部品にて覆われている領域のことである。この搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄いため、接続部の加工が容易になる。非搭載領域とは、配線層における搭載領域以外の領域のことである。

【0174】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0175】

また、非搭載領域の配線層の厚さは、搭載領域の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができる。

【0176】

本参考例に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品と接続するための接続部を有しており、上記接続部における配線層の厚さが、非接続部(接続部以外の部分)における配線層の厚さよりも薄いことを特徴としている。

【0177】

本参考例に係るフレキシブル配線基板では、上記電子部品が、上記接続部と接続するための接続部材を有しており、上記接続部における配線層は、接続部と接続部材との接続精度、および接続部材の製造サイズの公差を考慮した範囲で薄くなっていることが好ましい。また、上記接続精度が±15μmであり、上記接続部材の製造サイズの公差が±10μmである場合に、上記接続部における配線層は、少なくとも、接続部材の設計長+40μmの範囲で薄くなっていることが好ましい。

【0178】

上記の構成によれば、接続部における配線層の薄い領域は、接続精度および接続部材の製造サイズの公差を考慮した範囲となっている。例えば、電子部品の接続部への接続精度が15μm程度であり、接続部材の製造サイズの公差が±10μmである場合には接続部における配線層は、少なくとも、接続部材の設計長+40μmの範囲で薄くなっている。これにより、電子部品の接続部材が接続部から外れることなく接続させることが可能となり、接続不良となることを回避することができる。なお、接続精度とは、接続部と接続部材とを接続する際における位置ずれの精度のことである。また、接続部材の製造サイズの公差とは、接続部材を製造する際に生じるサイズ誤差の範囲のことである。また、接続部材の設計長とは、製造サイズの公差を考慮する前の製造時の狙い値(設計値)のことであり、設計長に製造サイズの公差を加減したものが実際の仕上がりサイズとなる。

【0179】

本参考例に係るフレキシブル配線基板の製造方法は、上記課題を解決するために、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層の、電子部品と接続する部分の厚さを薄くする薄層化工程をさらに有することを特徴としている。

【0180】

上記の構成によれば、薄層化工程により、配線層の、電子部品と接続する部分の厚さを薄くことができるため、電子部品との接続部分の加工が容易になる。従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0181】

また、電子部品との接続部分以外の配線層の厚さは、接続部分の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことのないフレキシブル配線基板を製造することができる。

【0182】

本参考例に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、配線層形成工程とパターン形成工程との間に実行されることが好ましい。上記の構成によれば、配線層の、電子部品との接続部分を薄くした後に、パターン形成工程を行う。この場合、比較的大きな領域の薄層化を行うため、精度の高い方法を用いることなく、容易に薄層化を行うことができる。

【0183】

本参考例に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、パターン形成工程の後に実行されることが好ましい。上記の構成によれば、パターンを形成した後に薄層化を行うため、パターンの厚みのバラツキを低減することができる。

【0184】

本発明に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、エッチング法を用いて実行されることが好ましい。上記の構成によれば、配線層の薄層化を容易に行うことができる。

【0185】

本参考例に係るフレキシブル配線基板の製造方法は、上記課題を解決するために、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層形成工程は、第1配線層を形成する第1配線層形成工程と、上記第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層を形成する第2配線層形成工程とを有することを特徴としている。

【0186】

上記の構成によれば、第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層が形成されている。すなわち、配線層は、電子部品と接続する部分の厚さが、それ以外の部分の厚さよりも薄くなっている。このため、電子部品と接続する部分の加工が容易になる。

【0187】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0188】

また、電子部品との接続部分以外の配線層の厚さは、接続部分の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことのないフレキシブル配線基板を製造することができる。

【0189】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、第1配線層形成工程とパターン形成工程との間に実行されることが好ましい。上記の構成によれば、電子部品との接続部分以外の第1配線層上に第2配線層を形成した後に、パターン形成工程を行う。この場合、比較的大きな領域の第2配線層の形成を行うため、精度の高い方法を用いることなく、第2配線層の積層を容易に行うことができる。

【0190】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、パターン形成工程の後に実行されることが好ましい。上記の構成によれば、パターンを形成した後に配線層を厚くするため、パターンの厚みのバラツキを低減することができる。

【0191】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、スパッタ法(メタライジング法)を用いて実行されることが好ましい。上記の構成によれば、電子部品との接続部分以外の配線層の厚さを、接続部分の配線層の厚さよりも厚くすることを容易に行うことができる。

【産業上の利用可能性】

【0192】

以上のように、本発明にかかるフレキシブル配線基板の製造方法を用いることによって、得られるフレキシブル配線基板は、配線パターンのファインピッチ化が可能になると共に、機械的強度を向上させることができ、半導体素子との電気的接続を良好なものとすることができる。それゆえ、本発明にかかるフレキシブル配線基板は、小型化、薄型化された電子機器の配線板等として特に好適に用いることができる。

【0193】

したがって、本発明は、単に、フレキシブル配線基板を製造する産業分野だけでなく、各種の電子・電気機器やその部品を製造する産業分野に好適に用いることができる。

【図面の簡単な説明】

【0194】

【図1】本発明の参考の一形態を示すものであり、半導体装置の概略構成を示す断面図である。

【図2】本発明の参考の一形態を示すものであり、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【図3】本発明の参考の一形態を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図4】本発明の参考の一形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図5】本発明の他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図6】本発明のさらに他の参考の形態を示すものであり、半導体装置の概略構成を示す断面図である。

【図7】本発明のさらに他の参考の形態を示すものであり、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【図8】本発明のさらに他の参考の形態を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図9】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図10】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図11】従来の半導体装置の概略構成を示す断面図である。

【図12】従来の半導体装置の概略構成を示す断面図である。

【図13】従来の半導体装置の概略構成を示す断面図である。

【図14】従来の半導体装置の概略構成を示す断面図である。

【図15】従来の半導体装置の概略構成を示す断面図である。

【図16】本発明の実施の形態1、2および3を示すものであり、半導体装置の概略構成を示す断面図である。

【図17】本発明の実施の形態1、2および3を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図18】本発明の実施の形態1を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図19】本発明の実施の形態2を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図20】本発明の実施の形態3を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図21】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【符号の説明】

【0195】

1・21・51 半導体装置

2 半導体素子(電子部品)

3・23・53 テープキャリア(フレキシブル配線基板)

6 絶縁テープ(絶縁層)

7・27・57 配線パターン(配線層、パターン)

9・29・59 半導体モジュール(電子機器)

12・62 銅箔(配線層)

32・72 第1銅箔層(配線層)

33・73 第2銅箔層(配線層)

【技術分野】

【0001】

本発明は、フレキシブル配線基板、それを用いた半導体装置および電子機器、並びにフレキシブル配線基板の製造方法に関するものである。より詳しくは、半導体素子を搭載するフレキシブル配線基板と、それを用いた半導体装置および電子機器、並びにフレキシブル配線基板の製造方法に関するものである。

【背景技術】

【0002】

フレキシブル配線基板上に半導体素子が接合・搭載された半導体装置としては、TCP(Tape Carrier Package)やCOF(Chip On Film)等がある。これらTCPとCOFとの相違点としては、例えば以下の点が挙げられる。

【0003】

まず、TCPは、予め絶縁テープに半導体素子を搭載させるための開口部が設けられており、配線パターンが片持ち梁状に突き出した状態で形成され、この配線パターンの先端部分と半導体素子とが接合されている。これに対して、COFは、半導体素子を搭載するための開口部を有しておらず、半導体素子は薄膜絶縁テープの表面上に形成された配線パターンに接合・搭載されている点で相違する。

【0004】

また、TCPは、配線パターンが片持ち梁状に突き出した状態であるために、配線パターンの厚みは18μm以上となっており、配線ピッチが45μm未満の配線パターンを製造することが困難である。これに対して、COFは、薄膜絶縁テープの表面上に配線パターンを形成するので、配線パターンの厚みを8μm以下とすることができ、配線ピッチが35μm以下の配線パターンを製造することが容易である点で相違する。

【0005】

また、TCPは、液晶パネル等へ実装した後に折り曲げる部分にはあらかじめスリットが設けられている。これに対して、COFは、折り曲げ用のスリットを有しておらず、薄膜絶縁テープのどこでも自由に折り曲げられる点で相違する。

【0006】

さらに、TCPは、ポリイミドからなる絶縁テープ上に、接着剤を用いて銅箔をラミネートして形成している。これに対して、COFは、銅箔裏面にポリイミド等を塗布、硬化して形成(キャスティング法)する、あるいはポリイミド等からなる薄膜絶縁テープ上に銅をスパッタで積層して形成(スパッタ法、メタライジング法)している点で相違する。

【0007】

COFは、その使用目的から自由に折り曲げることが可能な薄膜絶縁テープが使用される。また、薄膜絶縁テープの表面上に配置された配線パターンの各配線は、半導体素子の対応する端子と電気的に接続され、外部接続用コネクタ部には、液晶パネルやプリント基板などに接続される。上記以外の配線パターン露出部は、ソルダーレジストが塗布され、絶縁状態が確保される。

【0008】

上述のように、COFは、配線パターンのファインピッチ化(微細化)が容易な技術であるものの、実際には配線パターンの配線ピッチ35〜50μm以上に合わせて、配線パターンの厚み8〜18μmが使用されている。ただし、配線パターンの厚みに関する技術が記載された特許文献はない。一方、TCPでは、配線パターンの厚みに関する技術が記載された文献として、例えば特許文献1が挙げられる。

【0009】

また、従来のCOFについて図11および図12に基づいて説明する。図11は、従来のCOF101の概略構成を示す断面図である。図12は、図11に示すC−C’線で切断した場合におけるCOF101の概略構成を示す断面図である。図11および図12に示すように、COF101は、半導体素子102がテープキャリア103上に接続・搭載された構成を有している。

【0010】

図11および図12に示すCOF101のテープキャリア103では、絶縁テープ104上に配線パターン105が形成されている。この配線パターン105は、厚さ8〜18μmの銅箔またはスパッタ銅がキャスティング法またはスパッタ法(メタライジング法)によって形成されている。図11および図12に示すように、配線パターン105は、半導体素子102を接続・搭載する領域とそれ以外の領域との全ての領域において同じ厚さで形成されている。

【特許文献1】特開平10−32227号公報(平成10年(1998)2月3日公開)

【発明の開示】

【発明が解決しようとする課題】

【0011】

上記特許文献1では、半導体素子を搭載する開口部、および折り曲げ用スリット部の配線パターンの厚みは、機械的強度を上げるために厚く(26μm)なっており、液晶パネルや基板と接続するOLB(Outer Lead Bonding)部の配線パターンの厚みは、配線パターンのトップ幅を広くして接続面積を確保するために薄く(18μm)するとしている。

【0012】

しかしながら、実際には半導体素子を搭載する開口部の配線パターンが最もファインピッチとなるため、配線パターンの厚みを薄くする必要性がある。また、全ての箇所を同じ18μmの厚さで形成しても機械的強度には問題はなく、実際の量産品において、18μm厚の配線パターンも採用されている。すなわち、特許文献1に記載された技術は現実的ではなく、また必要性もないものである。このように、実際のTCPでは、配線パターンのファインピッチ化が困難である。

【0013】

これに対して、COFはTCPに比較して、配線パターン(インナーリード)のファインピッチ化が容易である。量産における配線パターン(インナーリード)の配線ピッチは、TCPの限界が45μmであるのに対して、COFは35μmが量産されており、30μm以下も可能であると考えられている。

【0014】

しかしながら、発明者の検討によれば、COFをファインピッチ化する場合には、以下の問題点が見出された。

【0015】

例えば、COFをファインピッチ化する際の問題点の一つとして、配線パターン(インナーリード)のファインピッチ化、特に配線ピッチが30μm以下になった場合に、配線パターンの厚みが現状の8μmでは配線パターン(インナーリード)を良好な形状にパターンエッチングすることが困難になってくることがある。

【0016】

すなわち、配線パターン(インナーリード)のファインピッチ化に伴い、配線パターン(インナーリード)の幅も狭くする必要があり、配線パターンの良好な断面形状である台形にパターンエッチングすることが困難となる。このため、配線パターンの断面形状が、より三角形に近い断面形状になると共に、配線パターン(インナーリード)の厚さバラツキも大きくなってくることがある。

【0017】

この点について図13に基づいて具体的に説明する。図13は、図11および図12に示す従来のCOF101の配線パターン105をファインピッチ化したものである。例えば、配線ピッチが35μmを超える場合はほぼ問題ないものの、35μm未満になると、配線パターン105の良好な断面形状である台形となるようにエッチング加工することが困難になってくる。この場合、図13に示すように、配線パターン105の断面形状は、より三角形に近いものとなる。また、エッチング加工後の配線パターン105の厚さバラツキも大きくなり、半導体素子102と配線パターン105との接続状態が悪くなることがわかる。

【0018】

これを解決する方法としては、銅箔またはスパッタ銅(配線パターン)の薄膜化がある。銅箔またはスパッタ銅(配線パターン)の厚みを薄くすれば、配線パターンを良好な形状にパターンエッチングすることが可能となってくる。例えば、配線パターン(インナーリード)の配線ピッチが30μmの場合でも、銅箔またはスパッタ銅(配線パターン)の厚みを5μm程度に薄くすれば、配線パターンを良好な断面形状である台形にパターンエッチングすることが容易となってくる。

【0019】

しかしながら、配線パターン(インナーリード)のファインピッチ化に伴う配線パターンの薄膜化により、配線パターンの機械的強度が低下するという問題点を有する。このため、半導体素子の接続・搭載工程〜COF半導体装置のモジュール実装工程の間で、配線パターンが断線、または剥離することがある。

【0020】

この点について図14および図15に基づいて具体的に説明する。図14は、図11および図12に示す従来のCOF101の配線パターン105を形成する銅箔またはスパッタ銅の厚さを薄くしたものである。図15は、図14に示すD−D’線で切断した場合におけるCOF101の概略構成を示す断面図である。図14および図15に示すように、銅箔またはスパッタ銅の厚さを薄くすれば、配線パターンを良好な断面形状となるようにエッチング加工することは可能となる。しかしながら、配線パターンの機械的強度が低下するために、半導体素子の接続・搭載工程〜モジュール実装工程の間で、配線パターンの断線、または剥離が発生しやすくなる。

【0021】

現在、COFへの要求の一つとして、多ピン化への対応がある。また、他の要求として小型・薄型化がある。これらの要求も同時に満足するためには、半導体素子との接続部、および配線パターンの外部接続用コネクタ部のファインピッチ化、絶縁テープ、配線パターン等の薄膜化が必要となる。このためには、配線パターン(インナーリード)の幅も小さく、厚みも薄くする必要がある。しかしながら、COFは自由に折り曲げることが可能な反面、配線パターンの薄膜化に伴い機械的強度の向上が必要であり、上述のように、従来の技術では、ファインピッチ化が困難であるという問題点を有している。

【0022】

本発明は、上記問題点を解決するものであり、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターンの形状を良好にすることができると共に、配線パターンと半導体素子との接続状態を良好にすることができ、非接続部の配線パターンの機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターンの断線、または剥離による不良を従来の50%以下に低減でき、さらに、半導体素子との接続時に発生する位置ずれをも低減することができるフレキシブル配線基板、及びそれを用いた半導体装置および電子機器を提供することにある。

【課題を解決するための手段】

【0023】

本発明に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域内に、該電子部品と接続するための接続部を有しており、上記接続部のみの配線層の厚さだけが、非接続部における配線層の厚さよりも薄いことを特徴としている。

【0024】

上記の構成によれば、配線層は、所定のパターンに形成されており、これにより、複数の配線を有している。所定のパターンとは、フレキシブル配線基板の使用用途に応じて任意に決められる複数の配線からなるパターンである。また、配線層の複数の配線には、電子部品と接続するための接続部を有している。この接続部は、電子部品を接続および搭載する搭載領域内に設けられている。すなわち、配線層は、電子部品が搭載される領域としての搭載領域を有しており、この搭載領域内に電子部品と接続する接続部を有する構成となっている。また、絶縁層上に形成された配線層は、接続部における配線層の厚さが、非接続部における配線層の厚さよりも薄くなっている。このため、接続部の加工が容易になる。なお、非接続部とは、配線層における接続部以外の領域のことである。

【0025】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0026】

また、非接続部の配線層の厚さは、接続部の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができる。

【0027】

また、本発明に係るフレキシブル配線基板では、上記配線層は、搭載領域における非接続部の厚さと、非搭載領域における非接続部の厚さとが同じであることが好ましい。上記の構成によれば、非接続部が全領域に渡って同じ厚さとなっていることから、配線層の機械的強度をより向上させることができ、フレキシブル配線基板を折り曲げる最においても、パターンの断線、または剥離の発生を防止することが可能となる。

【0028】

本発明に係るフレキシブル配線基板では、上記パターンにおける少なくとも1組の隣接する配線の間隔が35μm未満である場合に、より効果がある。上記の構成によれば、配線層のパターンのファインピッチ化が可能になる。

【0029】

本発明に係るフレキシブル配線基板では、上記搭載領域または接続部における配線層の厚さが3〜6μmの範囲内であることが好ましい。上記の構成によれば、搭載領域または接続部の配線をエッチングする場合であっても、断面が良好な形状となるようにエッチングすることが可能となる。また、パターンの各配線の厚さバラツキを低減することが可能となり、電子部品との接続状態を良好にすることが可能となる。

【0030】

本発明に係るフレキシブル配線基板では、上記非搭載領域または非接続部における配線層の厚さが8μm以上であることが好ましい。上記の構成によれば、配線層の機械的強度を向上させることができるため、フレキシブル配線基板を折り曲げる最においても、パターンの断線、または剥離の発生を防止することが可能となる。

【0031】

本発明に係るフレキシブル配線基板では、上記接続部は、インナーリード部である。上記の構成によれば、搭載領域内には接続部を有しており、電子部品との接続状態を良好にすることができると共に、配線層の機械的強度を向上させることができる。

【0032】

本発明に係る半導体装置は、上記課題を解決するために、上記いずれかに記載のフレキシブル配線基板と、フレキシブル配線基板の接続部に接続された半導体素子とを備えていることを特徴としている。上記の構成によれば、配線のファインピッチ化が可能であると共に、機械的強度を向上させた半導体装置とすることができる。

【0033】

本発明に係る電子機器は、上記課題を解決するために、上記半導体装置を備えていることを特徴としている。上記の構成によれば、配線のファインピッチ化が可能であると共に、機械的強度を向上させた電子機器とすることができる。

【発明の効果】

【0034】

本発明に係るフレキシブル配線基板は、以上のように、配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域を有しており、上記搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄くなっている。また、本発明に係るフレキシブル配線基板の製造方法は、以上のように、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層の、電子部品と接続する部分の厚さを薄くする薄層化工程をさらに有している。また、本発明に係るフレキシブル配線基板の製造方法は、以上のように、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層形成工程は、第1配線層を形成する第1配線層形成工程と、上記第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層を形成する第2配線層形成工程とを有している。このため、配線層のパターンのエッチング形状や電子部品との接続状態を良好にすることで微細化(ファインピッチ化)することが可能になると共に、配線層の機械的強度を向上させることができ、接続不良を防止すると共にフレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができるという効果を奏する。

【発明を実施するための最良の形態】

【0035】

〔参考形態1〕

本発明の参考形態1について図1ないし図4に基づいて説明すれば以下の通りである。図1は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図2は、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0036】

図1および図2に示すように、半導体装置1は、半導体素子(電子部品)2およびテープキャリア(フレキシブル配線基板)3を備えている。半導体素子2は、テープキャリア3と接続され、テープキャリア3上に搭載された状態になっている。また、テープキャリア3と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。このように、本参考形態では、テープキャリア3上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。

【0037】

上記半導体素子2としては、例えば、CPU(Central Processing Unit)やメモリ等の集積回路(LSI:Large Scaled Integrated circuit)を挙げることができる。また、半導体素子2には突起電極5が複数設けられている。

【0038】

突起電極5は、半導体素子2をテープキャリア3に搭載する際に、テープキャリア3と対向する側の面から略垂直方向に突出した電極であり、半導体素子2とテープキャリア3とを電気的に接続するために用いられる電極である。このため、突起電極5は導電性材料からなっていればよく、その形状は限定されない。ただし、テープキャリア3との接続が容易となる形状であることが好ましい。突起電極5としては、例えば、Auや半田からなる円柱状、角柱状またはボール状の電極とすることができる。

【0039】

テープキャリア3は、半導体素子2を接続・搭載するためのものであり、絶縁テープ(絶縁層)6、配線パターン(配線層、パターン)7、ソルダーレジスト8を備えている。

【0040】

絶縁テープ6は、その面上に配線パターン7を配置するための基材である。絶縁テープ6は、絶縁性を有することはもちろん、様々な形状で使用されることから、自由に折り曲げることが可能な柔軟性の高い(可撓性を有する)ことが必要である。このため、絶縁テープ6を形成する材料としては、例えば、ポリイミド、ガラスエポキシ、ポリエステルなどの樹脂材料が用いられる。なお、本参考形態では、ポリイミド樹脂を用いた絶縁テープ6を例に挙げて説明する。

【0041】

また、絶縁テープ6は、折り曲げを容易にするために、また、半導体装置1を小型化・薄型化するために、薄膜のテープ状基材であることが好ましい。絶縁テープ6の厚さは、使用目的に応じて適宜設定すればよいが、例えば、15〜40μmの範囲内であることが好ましい。

【0042】

配線パターン7は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン7は、銅箔またはスパッタ銅(以下、単に「銅箔」と総称する)をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。本参考形態では配線パターン7に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0043】

なお、半導体装置1を他の電子部品と接続するために、配線パターン7には外部接続用端子(図示せず)が設けられている。また、上記配線パターン7の表面には、図示しない錫メッキや金メッキが施されている。この配線パターン7の詳細な構成については後述する。

【0044】

ソルダーレジスト8は、配線パターン7上に形成されたレジストである。ソルダーレジスト8は、例えば耐熱性被覆材料からなっており、接続部以外の露出を防止するものである。従って、ソルダーレジスト8は、半導体素子2が搭載される領域以外の部分や、外部接続用端子が設けられていない部分の配線パターン7上に形成されている。すなわち、ソルダーレジスト8は、テープキャリア3上に半導体素子2等を接続・搭載した際に、露出する配線パターン7上に形成されている。

【0045】

上記絶縁テープ6には、半導体素子2を搭載するための開口部が設けられていない。このため、半導体素子2に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン7とを接合することによって、絶縁テープ6に半導体素子2が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン7の各配線と、各配線に対応する半導体素子2の突起電極5とを接続することにより行われる。これにより、配線パターン7と半導体素子2とが電気的に接続される。

【0046】

上記配線パターン7は、部分的に厚さが異なっている。具体的には、配線パターン7における、半導体素子2が接続・搭載される領域(搭載領域;接続部)の厚さが、半導体素子2が接続・搭載されない領域(非搭載領域)の厚さよりも薄くなっている。これにより、搭載領域では配線パターン7をファインピッチ化することが可能となり、非搭載領域では配線パターン7の機械的強度を向上させることが可能となり、半導体装置1の強度も向上する。

【0047】

なお、搭載領域とは、配線パターン7と半導体素子2とが接続・搭載される領域のことである。すなわち、搭載領域は、突起電極5と配線パターン7とが接続する部分を示すものであるが、半導体素子2をテープキャリア3上に搭載した際に、半導体素子2の占める領域を示す。従って、搭載領域にて半導体素子2と接続される配線パターン7は、いわゆるインナーリードである。また、非搭載領域とは、搭載領域以外の領域のことである。

【0048】

また、接続部とは、配線パターン7のうち、半導体素子2と実際に接続される部分のことを示し、非接続部とは、接続部以外の領域のことである。本参考形態では、接続部は、搭載領域に含まれている。

【0049】

上記搭載領域の配線パターン7の厚さは、例えば、3〜6μmの範囲内であることが好ましい。配線パターン7の厚さが3μm未満の場合には、絶縁テープ6の表面に突起電極5が接触してしまうといった不具合が発生してしまうことがある。また、配線パターン7の厚さが6μmを超える場合には、エッチングによる配線パターン7の形状や半導体素子2との接続状態を良好にすることが困難となる。

【0050】

ただし、搭載領域の配線パターン7の厚さは、上記厚さに限定されるものではない。すなわち、搭載領域の配線パターン7の厚さは、配線パターン7のファインピッチ化を可能とするための厚さ、すなわち配線パターン7をパターンエッチングにより良好な形状とすることを可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0051】

また、上記配線パターン7は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリア3とすることができる。

【0052】

なお、上記半導体装置1は、他の電子部品と接続することによって半導体モジュール(電子機器)9とすることもできる。この半導体モジュール9では、例えば、半導体装置1が他の電子部品を駆動・制御することもできる。図3は、本参考形態における半導体モジュール9の概略構成を示す断面図である。図3では、半導体装置1を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール9では、半導体装置1における配線パターン7の外部接続用端子と、上記液晶パネル10や他のプリント基板11等とが接続されている。

【0053】

次に、上記構成を有する半導体装置1の製造方法について図4に基づいて説明する。図4は、半導体装置1の製造方法の概略構成を示す断面図である。本参考形態における半導体装置1の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン7を形成する前に、搭載領域の銅箔の厚みをハーフエッチングによって非搭載領域の銅箔の厚みよりも薄くする方法である。

【0054】

まず、図4(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔(配線層)12を形成する。ここで、キャスティング法とは、銅箔にポリイミドを塗布した後に硬化させる方法である。一方、スパッタ法(メタライジング法)とは、ポリイミドやカプトン等のフィルム上にスパッタリングで金属シード層を形成した後に、電気メッキによって金属シード層上に銅メッキを析出させ、銅メッキを積み上げる方法である。

【0055】

次に、図4(b)に示すように、搭載領域に相当する部分の銅箔12の表面にエッチング加工を施す。このエッチング加工は、搭載領域の銅箔12の厚さが非搭載領域の銅箔12の厚さよりも薄くなるように行われる。このエッチング加工を、以下においてはハーフエッチングと称することもある。

【0056】

搭載領域の銅箔12の厚さが所望の厚さとなるように、ハーフエッチングは、例えば、テープ整面塗布装置を用い、温度、時間、速度、等を調整することにより、銅箔12の厚さを制御することができる。

【0057】

そして、図4(c)に示すように、銅箔12が所定のパターンとなるように、銅箔12に対するエッチング加工を行い、所望の配線パターン7を形成する。この配線パターン7の形成は、搭載領域および非搭載領域の配線パターン7を形成すべき全ての領域において行われる。その後、図4(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン7上にソルダーレジスト8を塗布する。これにより、テープキャリア3が作製される。

【0058】

次に、上記にて作製されたテープキャリア3上に半導体素子2を接続・搭載する。この接続は、突起電極5と配線パターン7とが対応するように半導体素子2とテープキャリア3とを配置し、この突起電極5と配線パターン7とを接続することによって行われる。この接続は、例えばAu−Sn共晶接合などにより行うことができる。これにより、半導体素子2がテープキャリア3上に接続・搭載される。

【0059】

テープキャリア3上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア3との間にできる隙間に、絶縁性樹脂4が注入され封止される。絶縁性樹脂4を注入・封止することにより、半導体素子2と配線パターン7との接続部分における外部との絶縁状態を確保することができる。これにより、本参考形態の半導体装置1が製造される。

【0060】

なお、上記半導体装置1を他の電子部品と接続する場合には、配線パターン7の外部接続用端子に、例えば、液晶パネルやプリント基板等を接続すればよい。

【0061】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア3では、搭載領域の配線パターン7の厚さが、非搭載領域の配線パターン7の厚さよりも薄くなっている。特に、非搭載領域の配線パターン7の厚さが8〜18μmであるのに対して、搭載領域の配線パターン7の厚さは3〜6μmとなっている。

【0062】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン7の形状を良好にすることができると共に、配線パターン7と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン7の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン7の断線、または剥離による不良を従来の50%以下に低減できる。

【0063】

〔参考形態2〕

本発明の参考形態2について図1ないし図3および図5に基づいて説明すれば以下の通りである。図1は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図2は、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0064】

図1に示すように、半導体装置1は、半導体素子2およびテープキャリア3を備えている。本参考形態では、上記参考形態1と比較して、半導体装置1の製造方法が異なるものであり、半導体装置1の構成は同一である。このため、参考形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置1の製造方法について説明する。また、特に断らない限り、本参考形態で用いる用語についても、上記参考形態1と同様の意味とする。

【0065】

ここで、本参考形態における半導体装置1の製造方法について図5に基づいて具体的に説明する。図5は、本参考形態における半導体装置1の製造方法の概略構成を示す断面図である。

【0066】

本参考形態の半導体装置1の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン7を形成した後に、搭載領域の銅箔の厚みをハーフエッチングによって非搭載領域の銅箔の厚みよりも薄くする方法である。

【0067】

まず、図5(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔12を形成する。

【0068】

次に、図5(b)に示すように、銅箔12が所定のパターンとなるように、銅箔12に対するエッチング加工を行い、所望の配線パターン7を形成する。この配線パターン7の形成は、搭載領域および非搭載領域の配線パターン7を形成すべき全ての領域において行われる。

【0069】

そして、図5(c)に示すように、搭載領域に相当する部分の配線パターン7の表面にエッチング加工を施す。このエッチング加工は、ハーフエッチングにて行われる。すなわち、搭載領域の配線パターン7の厚さが非搭載領域の配線パターン7の厚さよりも薄くなるように行われる。その後、図5(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン7上にソルダーレジスト8を塗布する。これにより、テープキャリア3が作製される。

【0070】

次に、上記参考形態1と同様にして半導体素子2をテープキャリア3上に接続・搭載する。そして、テープキャリア3上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア3との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置1が製造される。

【0071】

なお、上記半導体装置1を他の電子部品と接続して半導体モジュール9とする場合には、図3に示すように、配線パターン7の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0072】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア3では、搭載領域の配線パターン7の厚さが、非搭載領域の配線パターン7の厚さよりも薄くなっている。特に、非搭載領域の配線パターン7の厚さが8〜18μmであるのに対して、搭載領域の配線パターン7の厚さは3〜6μmとなっている。

【0073】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン7の形状を良好にすることができると共に、配線パターン7と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン7の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン7の断線、または剥離による不良を従来の50%以下に低減できる。

【0074】

また、本参考形態におけるテープキャリア3は、エッチング加工による配線パターン7の形成後に、搭載領域の配線パターン7の厚みをハーフエッチングによって薄くしている。このため、参考形態1のテープキャリア3と比較して、搭載領域の配線パターン7の厚みをより均一にすることが可能となる。

【0075】

〔参考形態3〕

本発明の参考形態3について図6ないし図9に基づいて説明すれば以下の通りである。図6は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図7は、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0076】

図6および図7に示すように、半導体装置21は、半導体素子2およびテープキャリア(フレキシブル配線基板)23を備えている。半導体素子2はテープキャリア23と接続され、テープキャリア23上に搭載された状態になっている。また、テープキャリア23と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。本参考形態においても、テープキャリア23上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。なお、参考形態1および2にて説明した部材と同一の部材については、同一の符号を付し、その説明を省略する。また、本参考形態で用いる用語で、参考形態1と同じ用語については、特に断らない限り同様の意味とする。

【0077】

半導体素子2には突起電極5が複数設けられている。また、テープキャリア23は、半導体素子2を接続・搭載するためのものであり、絶縁テープ6、配線パターン(配線層、パターン)27、ソルダーレジスト8を備えている。

【0078】

配線パターン27は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン27は、銅箔またはスパッタ銅(以下、単に「銅箔」と総称する)をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。なお、参考形態においても、配線パターン7に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0079】

配線パターン27は、第1配線層27aおよび第2配線層27bを備えている。第1配線層27aは、絶縁テープ6上に設けられた銅箔からなる層であり、第2配線層27bは、第1配線層27a上に設けられた銅箔からなる層である。

【0080】

上記第2配線層27bは、第1配線層27a上の一部分に設けられている。本参考形態では、第2配線層27bは、第1配線層27a上の非搭載領域に設けられている。すなわち、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン27の厚さよりも厚くなっている。これにより、第1配線層27aの厚さを制御することで、配線パターン27のファインピッチ化が可能となる。また、第2配線層27bの厚さを制御することで、配線パターン27の機械的強度を向上させることが可能となる。

【0081】

上記第1配線層27aの厚さは、例えば、3〜6μmの範囲内であることが好ましい。第1配線層27aの厚さが3μm未満の場合には、絶縁テープ6の表面に突起電極5が接触してしまうといった不具合が発生してしまうことがある。また、第1配線層27aの厚さが6μmを超える場合には、エッチングによる配線パターン27の形状を良好にすることや、半導体素子2との接続状態を良好にすることが困難となる。

【0082】

また、第2配線層27bの厚さは、第1配線層27aの厚さに応じて適宜設定すればよい。例えば、第1配線層27aの厚さが3〜6μmの範囲内である場合には、第2配線層27bの厚さは、第1配線層27aの厚さとの合計が8〜18μmの範囲内となる厚さであることが好ましい。

【0083】

ただし、第1配線層27aの厚さは、上記厚さに限定されるものではない。すなわち、第1配線層27aの厚さは、配線パターン27のファインピッチ化を可能とするための厚さ、すなわち配線パターン27をパターンエッチングにより良好な形状とすることを可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0084】

また、第2配線層27bの厚さも上記厚さに限定されるものではなく、第1配線層27aと第2配線層27bとの合計の厚みによって、機械的強度が十分に得られる厚さであればよい。

【0085】

また、上記配線パターン27は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリア23とすることができる。

【0086】

なお、半導体装置21を他の電子部品と接続するために、配線パターン27には外部接続用端子(図示せず)が設けられている。また、上記配線パターン27の表面には、図示しない錫メッキや金メッキが施されている。

【0087】

また、上記絶縁テープ6には、半導体素子21を搭載するための開口部が設けられていない。このため、半導体素子21に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン27とを接合することによって、絶縁テープ6に半導体素子21が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン27の各配線と、各配線に対応する半導体素子21の突起電極5とを接続することにより行われる。これにより、配線パターン27と半導体素子21とが電気的に接続される。

【0088】

なお、上記半導体装置21は、他の電子部品と接続することによって半導体モジュール(電子機器)29とすることもできる。この半導体モジュール29では、例えば、半導体装置21が他の電子部品を駆動・制御することもできる。図8は、本参考形態における半導体モジュール29の概略構成を示す断面図である。図8では、半導体装置21を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール29では、半導体装置21における配線パターン27の外部接続用端子と、上記液晶パネル10や他のプリント基板11等とが接続されている。

【0089】

次に、上記構成を有する半導体装置21の製造方法について図9に基づいて説明する。図9は、半導体装置21の製造方法の概略構成を示す断面図である。本参考形態における半導体装置21の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン27を形成する前に、非搭載領域の銅箔の厚みを電気メッキ等によって搭載領域の銅箔の厚みよりも厚くする方法である。

【0090】

まず、図9(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層32を形成する。そして、図9(b)に示すように、非搭載領域に相当する部分の第1銅箔層32上に、さらに第2銅箔層33を形成する。

【0091】

この第2銅箔層33は、例えば電気メッキにより銅メッキを析出させて、第1銅箔層32上に積み上げることによって形成される。これにより、搭載領域と非搭載領域との銅箔の厚みを異ならせることができる。また、電気メッキにより第2銅箔層33を形成する場合には、第2銅箔層33の厚さを任意に制御することができる。このため、第1銅箔層32の厚さに応じて第2銅箔層33の厚さを適宜変更することが可能となる。従って、例えば、第1銅箔層32と第2銅箔層33との合計の厚さが8〜18μmとなるように第2銅箔層33を形成することも容易となる。

【0092】

そして、図9(c)に示すように、第1銅箔層32および第2銅箔層33が所定のパターンとなるように、第1銅箔層32および第2銅箔層33に対するエッチング加工を行い、所望の配線パターン27を形成する。これにより、第1配線層27aおよび第2配線層27bからなる配線パターン27が形成される。この配線パターン27の形成は、搭載領域および非搭載領域の配線パターン27を形成すべき全ての領域において行われる。

【0093】

その後、図9(d)に示すように、後の工程で半導体素子22を搭載した際に露出する部分の配線パターン27上にソルダーレジスト8を塗布する。これにより、テープキャリア23が作製される。

【0094】

次に、上記にて作製されたテープキャリア23上に半導体素子2を接続・搭載する。この接続は、突起電極5と配線パターン27とが対応するように半導体素子2とテープキャリア23とを配置し、この突起電極5と配線パターン27とを接続することによって行われる。この接続は、例えばAu−Sn共晶接合などにより行うことができる。これにより、半導体素子22がテープキャリア23上に接続・搭載される。

【0095】

テープキャリア23上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア23との間にできる隙間に、絶縁性樹脂4が注入され封止される。絶縁性樹脂4を注入・封止することにより、半導体素子2と配線パターン27との接続部分における外部との絶縁状態を確保することができる。これにより、本参考形態の半導体装置21が製造される。

【0096】

なお、上記半導体装置21を他の電子部品と接続する場合には、配線パターン27の外部接続用端子に、例えば、液晶パネルやプリント基板等を接続すればよい。

【0097】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア23では、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン7の厚さよりも厚くなっている。特に、搭載領域の配線パターン27の厚さは3〜6μmであるのに対して、非搭載領域の配線パターン27の厚さが8〜18μmとなっている。

【0098】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン27の形状を良好にすることができると共に、配線パターン27と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン27の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン27の断線、または剥離による不良を従来の50%以下に低減できる。

【0099】

〔参考形態4〕

本発明の参考形態4について図6ないし図8および図10に基づいて説明すれば以下の通りである。図6は、本参考形態に係る半導体装置の概略構成を示す断面図である。また、図7は、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【0100】

図6に示すように、半導体装置21は、半導体素子2およびテープキャリア23を備えている。本参考形態では、上記参考形態3と比較して、半導体装置21の製造方法が異なるものであり、半導体装置21の構成は同一である。このため、参考形態3にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置21の製造方法について説明する。また、特に断らない限り、本参考形態で用いる用語についても、上記参考形態3と同様の意味とする。

【0101】

ここで、本参考形態における半導体装置21の製造方法について図10に基づいて具体的に説明する。図10は、本参考形態における半導体装置21の製造方法の概略構成を示す断面図である。

【0102】

本参考形態の半導体装置21の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン27を形成した後に、非搭載領域の銅箔の厚みを電気メッキ等によって搭載領域の銅箔の厚みよりも厚くする方法である。

【0103】

まず、図10(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層32を形成する。

【0104】

次に、図10(b)に示すように、第1銅箔層32が所定のパターンとなるように、第1銅箔層32に対するエッチング加工を行い、所望のパターンを有する第1配線層27aを形成する。この第1配線層27aの形成は、搭載領域および非搭載領域の配線パターン27を形成すべき全ての領域において行われる。

【0105】

そして、図10(c)に示すように、非搭載領域に相当する部分の第1配線層27a上に、さらに銅箔を積み上げて第2配線層27bを形成する。これにより、所望のパターンの形状にエッチング加工された第1配線層27aおよび第2配線層27bからなる配線パターン27が形成される。この第2配線層27bは、例えば電気メッキにより銅メッキを析出させて、第1配線層27a上に積み上げることによって形成される。

【0106】

これにより、搭載領域と非搭載領域との配線パターン27の厚みを異ならせることができる。また、電気メッキにより第2配線層27bを形成する場合には、第2配線層27bの厚さを任意に制御することができる。このため、第1配線層27aの厚さに応じて第2配線層27bの厚さを適宜変更することが可能となる。従って、例えば、第1配線層27aと第2配線層27bとの合計の厚さが8〜18μmとなるように第2配線層27bを形成することも容易となる。

【0107】

その後、図10(d)2に示すように、後の工程で半導体素子を搭載した際に露出する部分の配線パターン27上にソルダーレジスト8を塗布する。これにより、テープキャリア23が作製される。

【0108】

次に、上記参考態3と同様にして半導体素子2をテープキャリア23上に接続・搭載する。そして、テープキャリア23上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア23との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置21が製造される。

【0109】

なお、参考形態3と同様に、上記半導体装置21を他の電子部品と接続して半導体モジュールとする場合には、図8に示すように、配線パターン27の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0110】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア23では、非搭載領域の配線パターン27の厚さが、搭載領域の配線パターン27の厚さよりも厚くなっている。特に、搭載領域の配線パターン27の厚さは3〜6μmであるのに対して、非搭載領域の配線パターン27の厚さが8〜18μmとなっている。

【0111】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン27の形状を良好にすることができると共に、配線パターン27と半導体素子2との接続状態を良好にすることができる。加えて、非搭載領域の配線パターン27の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン27の断線、または剥離による不良を従来の50%以下に低減できる。

【0112】

〔実施の形態1〕

本発明の第1の実施の形態について図16ないし図18に基づいて説明すれば以下の通りである。図16は、本実施の形態に係る半導体装置の概略構成を示す断面図である。

【0113】

図16に示すように、半導体装置51は、半導体素子2およびテープキャリア(フレキシブル基板)53を備えている。半導体素子2はテープキャリア53と接続され、テープキャリア53上に搭載された状態になっている。また、テープキャリア53と半導体素子2との間に存在する隙間には絶縁性樹脂4が封止されている。本実施の形態においても、テープキャリア53上に半導体素子2が搭載されたCOF型の半導体装置を例に挙げて説明する。なお、参考形態1にて説明した部材と同一の部材については、同一の符号を付し、その説明を省略する。また、本実施の形態で用いる用語で、参考形態1と同じ用語については、特に断らない限り同様の意味とする。

【0114】

半導体素子2には突起電極5が複数設けられている。また、テープキャリア53は、半導体素子2を接続・搭載するためのものであり、絶縁テープ6、配線パターン57、ソルダーレジスト8を備えている。

【0115】

配線パターン57は、絶縁テープ6の表面にパターン状に形成された配線である。配線パターン57は、銅箔をキャスティング法またはスパッタ法(メタライジング法)等によって絶縁テープ6上に形成し、この銅箔を所望のパターンにエッチングすることにより形成されたものである。なお、本実施の形態においても、配線パターン57に用いられる材質として銅を例に挙げて説明するが、これに限定されるものではなく、例えば銀等の導電性を有する金属を用いることができる。

【0116】

上記配線パターン57は、部分的に厚さが異なっている。具体的には、配線パターン57と半導体素子2とが接続されている部分(接続部)のみの厚さが、それ以外の部分(非接続部)の厚さよりも薄くなっている。これにより、接続部では配線パターン57をファインピッチ化することが可能となり、非接続部では配線パターン57の機械的強度を向上させることが可能となり、半導体装置51の強度も向上する。

【0117】

また、本実施の形態では、接続部の厚さのみ薄くなっており、接続部の外側および内側(接続部よりも搭載領域外側および搭載領域内側)で厚くなっている。さらに、本実施の形態では、接続部の外側の配線パターン57の厚さと、接続部の内側の配線パターン57の厚さとが同じ厚さになっている。

【0118】

なお、接続部とは、半導体素子2の突起電極5と配線パターン57とが接続されている部分のことであり、上記搭載領域に含まれている。すなわち、搭載領域のうち、半導体素子2の突起電極5と配線パターン57とが接続する部分が接続部となっている。

【0119】

また、上記接続部は、接続部の長さが突起電極(接続部材)5の長さよりも40μm程度大きくなるように形成されている。この「接続部の長さ」とは、接続部における配線パターン57の厚さが薄くなっている部分の長さのことであり、「突起電極5の長さ」とは、突起電極5の設計長のことである。すなわち、この場合、突起電極5を接続部の中央部分に接続すると、突起電極5の側端部と接続部の端部との距離が20μm程度となる。このように形成することで、例えば、半導体素子2のテープキャリア53への接続精度が±15μmであり、突起電極5の製造サイズの公差が±10μmである場合においても、半導体素子2が接続部を外れた状態でテープキャリア53に接続されることを回避することができる。ただし、上記大きさは40μmに限定されるものではない。また、上記接続部の配線パターン57の厚さは、例えば、3〜6μmの範囲内であることが好ましい。ただし、配線パターン57の厚さはこれに限定されるものではなく、配線パターン57のファインピッチ化を可能とするための厚さであればよく、突起電極5が絶縁テープ6に接触することのない厚さであればよい。

【0120】

また、上記配線パターン57は、各配線の間隔である配線ピッチが35μm未満である場合に、より効果がある。配線ピッチが35μm未満である場合には、いわゆるファインピッチ化されたテープキャリアとすることができる。

【0121】

なお、半導体装置51を他の電子部品と接続するために、配線パターン57には外部接続用端子(図示せず)が設けられている。また、上記配線パターン57の表面には、図示しない錫メッキや金メッキが施されている。

【0122】

また、上記絶縁テープ6には、半導体素子2を搭載するための開口部が設けられていない。このため、半導体素子2に設けられた突起電極5と、絶縁テープ6の表面上に形成された配線パターン57とを接合することによって、絶縁テープ6に半導体素子2が接続・搭載される。すなわち、この接続は、絶縁テープ6の表面上に配置された配線パターン57の各配線と、各配線に対応する半導体素子2の突起電極5とを接続することにより行われる。これにより、配線パターン57と半導体素子2とが電気的に接続される。

【0123】

なお、上記半導体装置51は、他の電子部品と接続することによって半導体モジュールとすることもできる。この半導体モジュールでは、例えば、半導体装置51が他の電子部品を駆動・制御することもできる。図17は、本実施の形態における半導体モジュール59の概略構成を示す断面図である。図17では、半導体装置51を液晶表示装置に用いる場合を示している。この場合、他の電子部品としては、液晶パネル10や他のプリント基板11を挙げることができる。半導体モジュール59では、半導体装置51における配線パターン57の外部接続用端子と、上記液晶パネルや他のプリント基板等とが接続されている。

【0124】

次に、上記構成を有する半導体装置51の製造方法について図18に基づいて説明する。図18は、半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態における半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成する前に、接続部に相当する部分の銅箔の厚みをハーフエッチングによって、非接続部の銅箔の厚みよりも薄くする方法である。

【0125】

まず、図18(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔62を形成する。

【0126】

次に、図18(b)に示すように、接続部に相当する部分(ライン)の銅箔62の表面にエッチング加工(ハーフエッチング)を施す。このエッチング加工は、接続部の銅箔62の厚さが非接続部の銅箔62の厚さよりも薄くなるように行われる。また、このエッチング加工は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように行われる。

【0127】

そして、図18(c)に示すように、銅箔62が所定のパターンとなるように、銅箔62に対するエッチング加工を行い、所望の配線パターン57を形成する。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域において行われる。その後、図18(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0128】

次に、上記参考形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0129】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0130】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0131】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。

【0132】

また、接続部の配線パターン57の厚さのみを薄くしており、非接続部の配線パターン57の厚さは、従来のCOF型の半導体装置用のテープキャリアと同等であることから、非接続部の配線パターン57の機械的強度を従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良をより低減できると共に、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0133】

〔実施の形態2〕

本発明の第2の実施の形態について図16、図17および図19に基づいて説明すれば以下の通りである。

【0134】

図16は、本実施の形態に係る半導体装置51の概略構成を示す断面図である。本実施の形態では、上記実施の形態1と比較して、半導体装置51の製造方法が異なるものであり、半導体装置51の構成は同一である。このため、実施の形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本実施の形態では、主として、半導体装置51の製造方法について説明する。また、本実施の形態で用いる用語についても、上記実施の形態1と同様の意味とする。

【0135】

本実施の形態における半導体装置51の製造方法について図19に基づいて具体的に説明する。図19は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成した後に、接続部の銅箔の厚みをハーフエッチングによって非接続部の銅箔の厚みよりも薄くする方法である。

【0136】

まず、図19(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが8〜18μmとなるように銅箔62を形成する。

【0137】

次に、図19(b)に示すように、銅箔62が所定のパターンとなるように、銅箔62に対するエッチング加工を行い、所望の配線パターン57を形成する。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域において行われる。

【0138】

そして、図19(c)に示すように、接続部に相当する部分の配線パターン57の表面にエッチング加工を施す。このエッチング加工は、ハーフエッチングにて行われる。すなわち、接続部の配線パターン57の厚さが非接続部の配線パターン57の厚さよりも薄くなるように行われる。また、このエッチング加工は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように行われる。

【0139】

その後、図19(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジストを塗布する。これにより、テープキャリア53が作製される。

【0140】

次に、上記実施の形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0141】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0142】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0143】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0144】

〔実施の形態3〕

本発明の第3の実施の形態について図16、図17および図20に基づいて説明すれば以下の通りである。

【0145】

図16は、本実施の形態に係る半導体装置51の概略構成を示す断面図である。本実施の形態の半導体装置51は、配線パターン57が2層(第1配線層および第2配線層)から構成されているものであり、上記実施の形態1と比較して基本的な構成は同一である。このため、実施の形態1にて説明した部材については同一の符号を付し、その説明を省略する。また、本実施の形態では、主として、半導体装置51の製造方法について説明する。また、本実施の形態で用いる用語についても、上記実施の形態1と同様の意味とする。

【0146】

本実施の形態における半導体装置51の製造方法について図20に基づいて具体的に説明する。図20は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本実施の形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成する前に、非接続部の銅箔の厚みを電気メッキ等によって接続部の銅箔の厚みよりも厚くする方法である。

【0147】

まず、図20(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層72を形成する。そして、図20(b)に示すように、非接続部に相当する部分の第1銅箔層72上に、さらに第2銅箔層73を形成する。第2銅箔層73は、第1銅箔層72と第2銅箔層73との合計の厚さが8〜18μmとなるように形成される。また、第2銅箔層73は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように形成される。

【0148】

そして、図20(c)に示すように、第1銅箔層72および第2銅箔層73が所定のパターンとなるように、第1銅箔層72および第2銅箔層73に対するエッチング加工を行い、所望の配線パターン57を形成する。これにより、第1配線層57aおよび第2配線層57bからなる配線パターン57が形成される。この配線パターン57の形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域にて行われる。

【0149】

その後、図20(d)に示すように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0150】

次に、上記実施の形態1と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本実施の形態の半導体装置51が製造される。

【0151】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0152】

上記のように、本実施の形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0153】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0154】

〔参考形態5〕

本発明の参考形態5について図16、図17および図21に基づいて説明すれば以下の通りである。

【0155】

図16は、本参考形態に係る半導体装置51の概略構成を示す断面図である。本参考形態の半導体装置51は、配線パターン57が2層(第1配線層および第2配線層)から構成されているものであり、上記実施の形態5と比較して基本的な構成は同一である。このため、実施の形態5にて説明した部材については同一の符号を付し、その説明を省略する。また、本参考形態では、主として、半導体装置51の製造方法について説明する。また、本参考形態で用いる用語についても、上記実施の形態5と同様の意味とする。

【0156】

本参考形態における半導体装置51の製造方法について図21に基づいて具体的に説明する。図21は、本実施の形態における半導体装置51の製造方法の概略構成を示す断面図である。本参考形態の半導体装置51の製造方法は、絶縁テープ6表面に形成された銅箔をエッチング加工することによって配線パターン57を形成した後に、非接続部の銅箔の厚みを電気メッキ等によって接続部の銅箔の厚みよりも厚くする方法である。

【0157】

まず、図21(a)に示すように、絶縁テープ6表面に、キャスティング法またはスパッタ法(メタライジング法)等によって、厚さが3〜6μmとなるように第1銅箔層72を形成する。

【0158】

次に、図21(b)に示すように、第1銅箔層72が所定のパターンとなるように、第1銅箔層72に対するエッチング加工を行い、所望のパターンを有する第1配線層57aを形成する。この第1配線層57aの形成は、接続部および非接続部の配線パターン57を形成すべき全ての領域にて行われる。

【0159】

そして、図21(c)に示すように、非接続部に相当する部分の第1配線層57a上に、さらに銅箔を積み上げて第2配線層57bを形成する。これにより、所望のパターンの形状にエッチング加工された第1配線層57aおよび第2配線層57bからなる配線パターン57が形成される。この第2配線層57bは、例えば電気メッキにより銅メッキを析出させて、第1配線層57a上に積み上げることによって形成される。また、第2配線層57は、第1配線層57aと第2配線層57bとの合計の厚さが8〜18μmとなるように形成される。さらに、第2銅箔層73は、接続部の長さが、後に接続する半導体素子2の突起電極5の長さよりも40μm程度大きくなるように形成される。

【0160】

その後、図21(d)に示すにように、後の工程で半導体素子2を搭載した際に露出する部分の配線パターン57上にソルダーレジスト8を塗布する。これにより、テープキャリア53が作製される。

【0161】

次に、上記実施の形態5と同様にして半導体素子2をテープキャリア53上に接続・搭載する。そして、テープキャリア53上に半導体素子2を接続・搭載した後には、半導体素子2とテープキャリア53との間にできる隙間に、絶縁性樹脂4が注入され封止される。これにより、本参考形態の半導体装置51が製造される。

【0162】

なお、上記半導体装置51を他の電子部品と接続して半導体モジュール59とする場合には、図17に示すように、配線パターン57の外部接続用端子に、例えば、液晶パネル10やプリント基板11等を接続すればよい。

【0163】

上記のように、本参考形態におけるCOF型の半導体装置用のテープキャリア53では、接続部の配線パターン57の厚さが、非接続部の配線パターン57の厚さよりも薄くなっている。特に、非接続部の配線パターン57の厚さが8〜18μmであるのに対して、接続部の配線パターン57の厚さは3〜6μmとなっている。

【0164】

これにより、従来のCOF型の半導体装置用のテープキャリアと比較して、エッチング後の配線パターン57の形状を良好にすることができると共に、配線パターン57と半導体素子2との接続状態を良好にすることができる。加えて、非接続部の配線パターン57の機械的強度をも従来と比較して同等に向上させることが可能となり、配線パターン57の断線、または剥離による不良を従来の50%以下に低減できる。さらに、半導体素子2との接続時に発生する位置ずれをも低減することができる。

【0165】

なお、本発明のテープキャリアは、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF半導体装置となる薄膜の絶縁テープであり、前記半導体素子を接続・搭載する領域の前記配線パターンの配線ピッチが35μm未満となる前記絶縁テープにおいて、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さよりも、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さを薄く形成しているCOF半導体装置用テープキャリアとも表現できる。上記のテープキャリアでは、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さを3〜6μmに形成していてもよい。

【0166】

また、本発明のテープキャリアの製造方法は、前記配線パターンをパターンエッチングにより形成する前に、後に前記半導体素子を接続・搭載する前記配線パターンの形成領域の厚さをハーフエッチングにより、その他の領域より薄くした後に、その他の領域を含め、前記配線パターンをパターンエッチングにより形成する方法とも表現できる。

【0167】

上記の製造方法では、前記配線パターンをパターンエッチングにより形成した後に、後に前記半導体素子を接続・搭載する領域の前記配線パターンの厚さをハーフエッチングにより、その他の領域の前記配線パターンより薄く形成していてもよい。

【0168】

また、本発明のテープキャリアは、表面に複数配置した配線パターンと半導体素子の突起電極とを電気的に接続し、絶縁性樹脂で封止することでCOF半導体装置となる薄膜の絶縁テープであり、前記半導体素子を接続・搭載する領域の前記配線パターンの配線ピッチが35μm未満となる前記絶縁テープにおいて、前記半導体素子を接続・搭載する領域の前記配線パターンの厚さよりも、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さを厚く形成しているCOF半導体装置用テープキャリアとも表現できる。上記のテープキャリアでは、前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さを8μm以上に形成していてもよい。

【0169】

また、本発明のテープキャリアの製造方法は、前記配線パターンをパターンエッチングする前に、後に前記半導体素子を接続・搭載する領域以外の前記配線パターン形成領域の厚さをスパッタ法(メタライジング法)により、前記半導体素子を接続・搭載する前記配線パターンの形成領域より厚く積み上げた後に、前記配線パターンをパターンエッチングにより形成する方法とも表現できる。

【0170】

上記の製造方法では、前記配線パターンをパターンエッチングにより形成した後に、後に前記半導体素子を接続・搭載する領域以外の前記配線パターンの厚さをスパッタ法(メタライジング法)により、前記半導体素子を接続・搭載する領域の前記配線パターンより、厚く積み上げて形成していてもよい。

【0171】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【0172】

〔参考形態〕

本参考例に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域を有しており、上記搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄いことを特徴としている。

【0173】

上記の構成によれば、配線層は、所定のパターンに形成されており、これにより、複数の配線を有している。所定のパターンとは、フレキシブル配線基板の使用用途に応じて任意に決められる複数の配線からなるパターンである。また、配線層は、電子部品を接続および搭載する搭載領域を有している。搭載領域とは、配線層のうち電子部品が搭載される領域のことであり、具体的には電子部品にて覆われている領域のことである。この搭載領域における配線層の厚さが、非搭載領域における配線層の厚さよりも薄いため、接続部の加工が容易になる。非搭載領域とは、配線層における搭載領域以外の領域のことである。

【0174】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0175】

また、非搭載領域の配線層の厚さは、搭載領域の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことを防止することができる。

【0176】

本参考例に係るフレキシブル配線基板は、上記課題を解決するために、絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、上記配線層は、所定のパターンに形成されていると共に、電子部品と接続するための接続部を有しており、上記接続部における配線層の厚さが、非接続部(接続部以外の部分)における配線層の厚さよりも薄いことを特徴としている。

【0177】

本参考例に係るフレキシブル配線基板では、上記電子部品が、上記接続部と接続するための接続部材を有しており、上記接続部における配線層は、接続部と接続部材との接続精度、および接続部材の製造サイズの公差を考慮した範囲で薄くなっていることが好ましい。また、上記接続精度が±15μmであり、上記接続部材の製造サイズの公差が±10μmである場合に、上記接続部における配線層は、少なくとも、接続部材の設計長+40μmの範囲で薄くなっていることが好ましい。

【0178】

上記の構成によれば、接続部における配線層の薄い領域は、接続精度および接続部材の製造サイズの公差を考慮した範囲となっている。例えば、電子部品の接続部への接続精度が15μm程度であり、接続部材の製造サイズの公差が±10μmである場合には接続部における配線層は、少なくとも、接続部材の設計長+40μmの範囲で薄くなっている。これにより、電子部品の接続部材が接続部から外れることなく接続させることが可能となり、接続不良となることを回避することができる。なお、接続精度とは、接続部と接続部材とを接続する際における位置ずれの精度のことである。また、接続部材の製造サイズの公差とは、接続部材を製造する際に生じるサイズ誤差の範囲のことである。また、接続部材の設計長とは、製造サイズの公差を考慮する前の製造時の狙い値(設計値)のことであり、設計長に製造サイズの公差を加減したものが実際の仕上がりサイズとなる。

【0179】

本参考例に係るフレキシブル配線基板の製造方法は、上記課題を解決するために、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層の、電子部品と接続する部分の厚さを薄くする薄層化工程をさらに有することを特徴としている。

【0180】

上記の構成によれば、薄層化工程により、配線層の、電子部品と接続する部分の厚さを薄くことができるため、電子部品との接続部分の加工が容易になる。従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0181】

また、電子部品との接続部分以外の配線層の厚さは、接続部分の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことのないフレキシブル配線基板を製造することができる。

【0182】

本参考例に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、配線層形成工程とパターン形成工程との間に実行されることが好ましい。上記の構成によれば、配線層の、電子部品との接続部分を薄くした後に、パターン形成工程を行う。この場合、比較的大きな領域の薄層化を行うため、精度の高い方法を用いることなく、容易に薄層化を行うことができる。

【0183】

本参考例に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、パターン形成工程の後に実行されることが好ましい。上記の構成によれば、パターンを形成した後に薄層化を行うため、パターンの厚みのバラツキを低減することができる。

【0184】

本発明に係るフレキシブル配線基板の製造方法では、上記薄層化工程は、エッチング法を用いて実行されることが好ましい。上記の構成によれば、配線層の薄層化を容易に行うことができる。

【0185】

本参考例に係るフレキシブル配線基板の製造方法は、上記課題を解決するために、絶縁層上に配線層を形成する配線層形成工程と、該配線層を所定のパターンに形成するパターン形成工程とを有するフレキシブル配線基板の製造方法において、上記配線層形成工程は、第1配線層を形成する第1配線層形成工程と、上記第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層を形成する第2配線層形成工程とを有することを特徴としている。

【0186】

上記の構成によれば、第1配線層と電子部品とが接続する部分以外の第1配線層上に第2配線層が形成されている。すなわち、配線層は、電子部品と接続する部分の厚さが、それ以外の部分の厚さよりも薄くなっている。このため、電子部品と接続する部分の加工が容易になる。

【0187】

従って、例えば、配線をエッチングする際には、配線を良好な形状となるようにエッチングすることができ、複数有る各配線の厚さのバラツキも低減することができる。このため、配線層のパターンを微細化(ファインピッチ化)することが可能となる。

【0188】

また、電子部品との接続部分以外の配線層の厚さは、接続部分の配線層の厚さよりも厚いため、配線層の機械的強度を向上させることができる。このため、フレキシブル配線基板を折り曲げる際においても、配線層のパターンが断線、または剥離してしまうことのないフレキシブル配線基板を製造することができる。

【0189】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、第1配線層形成工程とパターン形成工程との間に実行されることが好ましい。上記の構成によれば、電子部品との接続部分以外の第1配線層上に第2配線層を形成した後に、パターン形成工程を行う。この場合、比較的大きな領域の第2配線層の形成を行うため、精度の高い方法を用いることなく、第2配線層の積層を容易に行うことができる。

【0190】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、パターン形成工程の後に実行されることが好ましい。上記の構成によれば、パターンを形成した後に配線層を厚くするため、パターンの厚みのバラツキを低減することができる。

【0191】

本参考例に係るフレキシブル配線基板の製造方法では、上記第2配線層形成工程は、スパッタ法(メタライジング法)を用いて実行されることが好ましい。上記の構成によれば、電子部品との接続部分以外の配線層の厚さを、接続部分の配線層の厚さよりも厚くすることを容易に行うことができる。

【産業上の利用可能性】

【0192】

以上のように、本発明にかかるフレキシブル配線基板の製造方法を用いることによって、得られるフレキシブル配線基板は、配線パターンのファインピッチ化が可能になると共に、機械的強度を向上させることができ、半導体素子との電気的接続を良好なものとすることができる。それゆえ、本発明にかかるフレキシブル配線基板は、小型化、薄型化された電子機器の配線板等として特に好適に用いることができる。

【0193】

したがって、本発明は、単に、フレキシブル配線基板を製造する産業分野だけでなく、各種の電子・電気機器やその部品を製造する産業分野に好適に用いることができる。

【図面の簡単な説明】

【0194】

【図1】本発明の参考の一形態を示すものであり、半導体装置の概略構成を示す断面図である。

【図2】本発明の参考の一形態を示すものであり、図1に示すA−A’線で切断した場合における半導体装置の概略構成を示す断面図である。

【図3】本発明の参考の一形態を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図4】本発明の参考の一形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図5】本発明の他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図6】本発明のさらに他の参考の形態を示すものであり、半導体装置の概略構成を示す断面図である。

【図7】本発明のさらに他の参考の形態を示すものであり、図6に示すB−B’線で切断した場合における半導体装置の概略構成を示す断面図である。

【図8】本発明のさらに他の参考の形態を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図9】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図10】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図11】従来の半導体装置の概略構成を示す断面図である。

【図12】従来の半導体装置の概略構成を示す断面図である。

【図13】従来の半導体装置の概略構成を示す断面図である。

【図14】従来の半導体装置の概略構成を示す断面図である。

【図15】従来の半導体装置の概略構成を示す断面図である。

【図16】本発明の実施の形態1、2および3を示すものであり、半導体装置の概略構成を示す断面図である。

【図17】本発明の実施の形態1、2および3を示すものであり、半導体モジュールの概略構成を示す断面図である。

【図18】本発明の実施の形態1を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図19】本発明の実施の形態2を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図20】本発明の実施の形態3を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【図21】本発明のさらに他の参考の形態を示すものであり、半導体装置の製造方法の概略構成を示す断面図である。

【符号の説明】

【0195】

1・21・51 半導体装置

2 半導体素子(電子部品)

3・23・53 テープキャリア(フレキシブル配線基板)

6 絶縁テープ(絶縁層)

7・27・57 配線パターン(配線層、パターン)

9・29・59 半導体モジュール(電子機器)

12・62 銅箔(配線層)

32・72 第1銅箔層(配線層)

33・73 第2銅箔層(配線層)

【特許請求の範囲】

【請求項1】

絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、

上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域内に、該電子部品と接続するための接続部を有しており、

上記接続部のみの配線層の厚さだけが、非接続部における配線層の厚さよりも薄いことを特徴とするフレキシブル配線基板。

【請求項2】

上記配線層は、搭載領域における非接続部の厚さと、非搭載領域における非接続部の厚さとが同じであることを特徴とする請求項1に記載のフレキシブル配線基板。

【請求項3】

上記パターンにおける少なくとも1組の隣接する配線の間隔が35μm未満であることを特徴とする請求項1または2に記載のフレキシブル配線基板。

【請求項4】

上記接続部における配線層の厚さが3〜6μmの範囲内であることを特徴とする請求項1ないし3のいずれか1項に記載のフレキシブル配線基板。

【請求項5】

上記非接続部における配線層の厚さが8μm以上であることを特徴とする請求項1ないし4のいずれか1項に記載のフレキシブル配線基板。

【請求項6】

上記接続部は、インナーリード部であることを特徴とする請求項1ないし5のいずれか1項に記載のフレキシブル配線基板。

【請求項7】

請求項1ないし6のいずれか1項に記載のフレキシブル配線基板と、フレキシブル配線基板の接続部に接続された半導体素子とを備えていることを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置を備えていることを特徴とする電子機器。

【請求項1】

絶縁層と、該絶縁層上に形成された配線層とを備えたフレキシブル配線基板において、

上記配線層は、所定のパターンに形成されていると共に、電子部品を接続および搭載する搭載領域内に、該電子部品と接続するための接続部を有しており、

上記接続部のみの配線層の厚さだけが、非接続部における配線層の厚さよりも薄いことを特徴とするフレキシブル配線基板。

【請求項2】

上記配線層は、搭載領域における非接続部の厚さと、非搭載領域における非接続部の厚さとが同じであることを特徴とする請求項1に記載のフレキシブル配線基板。

【請求項3】

上記パターンにおける少なくとも1組の隣接する配線の間隔が35μm未満であることを特徴とする請求項1または2に記載のフレキシブル配線基板。

【請求項4】

上記接続部における配線層の厚さが3〜6μmの範囲内であることを特徴とする請求項1ないし3のいずれか1項に記載のフレキシブル配線基板。

【請求項5】

上記非接続部における配線層の厚さが8μm以上であることを特徴とする請求項1ないし4のいずれか1項に記載のフレキシブル配線基板。

【請求項6】

上記接続部は、インナーリード部であることを特徴とする請求項1ないし5のいずれか1項に記載のフレキシブル配線基板。

【請求項7】

請求項1ないし6のいずれか1項に記載のフレキシブル配線基板と、フレキシブル配線基板の接続部に接続された半導体素子とを備えていることを特徴とする半導体装置。

【請求項8】

請求項7に記載の半導体装置を備えていることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2008−177618(P2008−177618A)

【公開日】平成20年7月31日(2008.7.31)

【国際特許分類】

【出願番号】特願2008−102621(P2008−102621)

【出願日】平成20年4月10日(2008.4.10)

【分割の表示】特願2005−299402(P2005−299402)の分割

【原出願日】平成17年10月13日(2005.10.13)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成20年7月31日(2008.7.31)

【国際特許分類】

【出願日】平成20年4月10日(2008.4.10)

【分割の表示】特願2005−299402(P2005−299402)の分割

【原出願日】平成17年10月13日(2005.10.13)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]