ブートストラップ回路、半導体装置

【課題】ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供する。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

【解決手段】ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ブートストラップ回路および半導体装置に関する。

【背景技術】

【0002】

従来、スイッチング素子およびこのスイッチング素子を駆動するための駆動回路を備えた、各種の電力変換回路が知られている。

例えば、特開平1−170378号公報は、DC/AC変換器に関するものであり、トランジスタの制御電極とソースの間の電圧を閾値電圧より高く保つことを保証するために、電圧レベルをシフトするブートストラップ回路について記載している(当該公報の3ページ目における紙面右下欄参照)。コンデンサ、抵抗器およびツェナーダイオードにより、電圧レベルシフトを行うことができる制御回路についても記載している(当該公報の5ページ目における紙面左上欄参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平1−170378号公報

【特許文献2】特開平9−298871号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

アーム回路あるいはハーフブリッジ回路は、高電位側に配置されたハイサイドスイッチング素子と、低電位側に配置されたローサイドスイッチング素子とを備えている。一般に、ハイサイドスイッチング素子を駆動するために、これを駆動するハイサイド駆動回路の電源を、ハイサイドスイッチング素子の電位(MOSFETであればソース電位、IGBTであればエミッタ電位)よりも一定電位だけ高くする必要がある。この電圧を印加するための方式の1つとして、ブートストラップ回路方式が知られている。

【0005】

従来、ブートストラップ回路として知られる構成として、次のようなものがあった。図11は、本願発明が解決しようとする課題を説明するために用いる、従来のブートストラップ回路の構成を説明するための図である。図11において、DIP−IPM(Dual-in-line Package Intelligent Power Module)2は、高耐圧ICであるHVIC4と、低耐圧ICであるLVIC6とを備えている。HVIC4のVcc端子およびLVIC6のVcc端子は、共通の電源に接続している。

【0006】

HVIC4のHO端子はスイッチング素子(IGBT)SW1のゲート端子と接続し、LVIC6のLO端子はスイッチング素子(IGBT)SW2のゲート端子と接続している。HVIC4のVS端子は、スイッチング素子SW1のエミッタとスイッチング素子SW2のコレクタとの間に接続している。LVIC6のVNO端子はスイッチング素子SW2のエミッタと接続している。スイッチング素子SW1のコレクタはP母線と接続し、スイッチング素子SW2のエミッタはN母線と接続している。P母線とN母線の間に、平滑コンデンサが設けられている。

【0007】

HVIC4のVB端子は、コンデンサC1の一方の端子と接続している。コンデンサC1の他方の端子は、HVIC4のVS端子に接続している。コンデンサC1と並列にツェナーダイオードD1が接続されている。コンデンサC1の他方の端子およびツェナーダイオードD1のアノードは、リアクトルL1の一方の端子に接続している。リアクトルL1の他方の端子は、グランド(GND)に接続されている。

【0008】

図11の回路は、ブートストラップ回路200を備えている。ブートストラップ回路200は、抵抗R200およびダイオードDi20の直列回路を備えている。この直列回路は、HVIC4のVcc端子側の配線と、HVIC4のVB端子側の配線との間に並列に接続している。すなわち、ブートストラップ回路200の抵抗R200の一端が、HVIC4のVcc端子側の配線と接続し、ブートストラップ回路200のダイオードDi20の他端(カソード)が、HVIC4のVB端子側の配線と接続している。ダイオードDi20は、いわゆるブートストラップダイオード(BSD)である。

【0009】

ハイサイドスイッチング素子(スイッチング素子SW1)を駆動するためには、HVIC(ハイサイド駆動回路)の電源を、ハイサイドスイッチング素子の電位(MOSFETであればソース電位、IGBTであればエミッタ電位)よりもVccだけ高い電位とする必要がある。図11の回路において、ブートストラップ回路200(つまり抵抗R200およびダイオードDi20)を介して、コンデンサC1が充電される。この電圧で、HVIC4を動作させることができる。

【0010】

しかしながら、上記従来のブートストラップ回路方式は、ブートストラップダイオード(BSD)を必須構成とするものであった。本願発明者は、鋭意研究の結果、従来のブートストラップ回路方式とは異なり、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路についての着想を得た。

【0011】

本発明は、上述のような課題を解決するためになされたもので、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供することを目的とする。

また、本発明の他の目的は、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を用いた半導体装置を提供することである。

【課題を解決するための手段】

【0012】

第1の発明にかかるブートストラップ回路は、

充電された電圧をスイッチング素子駆動用回路に印加する第1コンデンサと、

メイン電源母線に一方の端子が接続し、他方の端子が前記第1コンデンサと接続して、前記メイン電源母線の電圧を前記第1コンデンサに印加する抵抗と、

を備えることを特徴とする。

【0013】

第2の発明にかかる半導体装置は、

メイン電源母線と接続するハイサイドスイッチング素子と、

前記ハイサイドスイッチング素子を駆動するスイッチング素子駆動用回路と、

前記スイッチング素子駆動用回路と接続する前記第1の発明にかかるブートストラップ回路と、

を備えることを特徴とする。

【発明の効果】

【0014】

第1の発明にかかるブートストラップ回路によれば、メイン電源側からブートストラップ回路のコンデンサを充電することができ、ブートストラップダイオード(BSD)を省略することができる。

【0015】

第2の発明によれば、ブートストラップダイオード(BSD)を省略したブートストラップ回路を備えた半導体装置が提供される。

【図面の簡単な説明】

【0016】

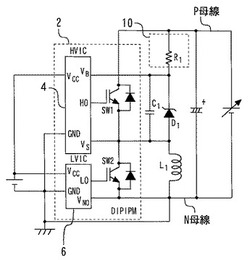

【図1】本発明の実施の形態1にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図2】本発明の実施の形態2にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図3】本発明の実施の形態3にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図4】本発明の実施の形態4にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図5】本発明の実施の形態5にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図6】本発明の実施の形態6にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図7】本発明の実施の形態7にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図8】本発明の実施の形態8にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図9】本発明の実施の形態9にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図10】本発明の実施の形態10にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図11】本願発明が解決しようとする課題を説明するために用いる、従来のブートストラップ回路の構成を説明するための図である。

【発明を実施するための形態】

【0017】

実施の形態1.

図1は、本発明の実施の形態1にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。図1には図11と共通する構成として、DIP−IPM(Dual-in-line Package Intelligent Power Module)2と、高耐圧ICであるHVIC4と、低耐圧ICであるLVIC6と、スイッチング素子(IGBT)SW1およびスイッチング素子(IGBT)SW2と、コンデンサC1と、ツェナーダイオードD1と、リアクトルL1などが示されている。これらの回路素子は、図11において説明したのと同様の接続関係で回路を形成しており、重複した説明を避けるため、図11と同様の点は説明を省略する。なお、符号2を付した図面中の破線領域内が、DIP−IPM2の内部構成を意味している。この符号2を付した破線領域内の構成が、例えばケースに収納されたり、トランスファーモールド樹脂封止されたりして、IPMとして提供されるものである。

【0018】

図1の回路は、ブートストラップ部用電源供給部10を備えている。ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。ハイサイドスイッチング素子(スイッチング素子SW1)を駆動するためには、HVIC4(ハイサイド駆動回路)の電源を、ハイサイドスイッチング素子の電位(スイッチング素子SW1のエミッタ電位)よりもVccだけ高い電位とする必要がある。この電圧を印加するための方式の1つが、ブートストラップ回路方式である。図1の回路において、抵抗R1を介して、メイン電源(P母線とN母線間から得られる電圧)によって、コンデンサC1が充電される。この電圧で、HVIC4を動作させることができる。

【0019】

実施の形態1にかかるブートストラップ回路によれば、抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。従って、図11に示したブートストラップ回路とは異なり、実施の形態1にかかるブートストラップ回路ではブートストラップダイオード(BSD)を省略することができる。

【0020】

実施の形態2.

図2は、本発明の実施の形態2にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態2にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部20を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部20は、抵抗R2およびコンデンサC2を備えている。抵抗R2は、実施の形態1にかかる抵抗R1と同様にコンデンサC1と接続しており、抵抗R1と同様の作用効果を発揮することができる。また、コンデンサC2により、スイッチング動作時におけるdv/dtで、ブートストラップ回路におけるコンデンサC1を充電できるようになる。

【0021】

実施の形態3.

図3は、本発明の実施の形態3にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態3にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部30を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部30は、抵抗R3およびダイオードDi3を備えている。抵抗R3およびダイオードDi3は直列に接続しており、抵抗R3およびダイオードDi3の直列回路は、実施の形態1にかかる抵抗R1と同様にコンデンサC1と接続している。具体的には、ダイオードDi3のアノードは、抵抗R3を介してP母線と接続しており、ダイオードDi3のカソードはコンデンサC1と接続している。

抵抗R3とダイオードDi3の直列回路を介して、実施の形態1の抵抗R1と同様に、メイン電源母線の電圧をコンデンサC1に印加するという作用効果を得ることができる。さらに、ダイオードDi3が逆流防止用のダイオードとして機能することができる。

【0022】

実施の形態4.

図4は、本発明の実施の形態4にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態4にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部40を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部40は、抵抗R4、コンデンサC4およびダイオードDi4を備えている。コンデンサC4は、抵抗R4およびダイオードDi4は、実施の形態3にかかる抵抗R3およびダイオードDi3と同様の直列回路を構成しており、ダイオードDi4はダイオードDi3と同様に逆流防止用のダイオードとして機能する。また、抵抗R4とダイオードDi4の直列回路に対してコンデンサC4が並列に接続しており、コンデンサC4は実施の形態2のコンデンサC2と同様の作用を発揮する。

【0023】

実施の形態5.

図5は、本発明の実施の形態5にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態5にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部50を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部50は、コンデンサC5、抵抗R51および抵抗R52を備えている。コンデンサC5および抵抗R51の直列回路に対し、抵抗R52が並列に接続している。抵抗R52は、実施の形態1にかかる抵抗R1と同様に、メイン電源側からコンデンサC1へと電源供給を行うことができる。また、ブートストラップ部用電源供給部50によれば、コンデンサC5に抵抗R51を直列に接続することで、ツェナーダイオードD1を保護することができる。

【0024】

実施の形態6.

図6は、本発明の実施の形態6にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態6にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部60を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部60は、コンデンサC6、抵抗R6、およびリアクトルL6を備えている。コンデンサC6およびリアクトルL6の直列回路と、抵抗R6とが、並列に接続している。抵抗R6は、実施の形態1にかかる抵抗R1と同様に、メイン電源側からコンデンサC1へと電源供給を行うことができる。また、ブートストラップ部用電源供給部60によれば、コンデンサC6にリアクトルL6を直列に接続することで、ツェナーダイオードD1を保護することができる。

【0025】

実施の形態7.

図7は、本発明の実施の形態7にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態7にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部70を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部70は、ダイオードDi7、抵抗R7およびコンデンサC7を備えている。ダイオードDi7のアノードが、P母線と接続している。ダイオードDi7のカソードはコンデンサC7と接続し、ダイオードDi7とコンデンサC7は直列回路を形成している。抵抗R7は、コンデンサC7に並列に接続している。ブートストラップ部用電源供給部70によっても、メイン電源側を利用してコンデンサC1を充電することができる。さらに、コンデンサC7が、実施の形態2におけるコンデンサC2と同様の作用効果を奏し、また、ダイオードDi7によりツェナーダイオードD1を保護することができる。

【0026】

実施の形態8.

図8は、本発明の実施の形態8にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態8にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部80を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部80は、抵抗R82、抵抗R81およびコンデンサC8を備えている。抵抗R82およびコンデンサC8は直列に接続しており、抵抗R81はコンデンサC8に並列に接続している。抵抗R82およびコンデンサC8の直列回路が、P母線と、コンデンサC1の一方の端子との間に介在している。抵抗R81は、抵抗R82よりも高抵抗とする。つまり、「抵抗R81の抵抗値>抵抗R82の抵抗値」という関係が成立するように、抵抗R81および抵抗R82を選定する。抵抗R81>抵抗R82という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。

【0027】

実施の形態9.

図9は、本発明の実施の形態9にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態9にかかるブートストラップ回路は、ブートストラップ部用電源供給部80に代えてブートストラップ部用電源供給部90を備えている点で、実施の形態8にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部90は、抵抗R92、抵抗R91、コンデンサC9およびダイオードDi9を備えている。抵抗R92、コンデンサC9およびダイオードDi9は直列に接続しており、抵抗R91はコンデンサC9に並列に接続している。抵抗R92、コンデンサC9およびダイオードDi9の直列回路が、P母線と、コンデンサC1の一方の端子との間に介在している。抵抗R91は、抵抗R92よりも高抵抗とする(抵抗R91>抵抗R92)。抵抗R91>抵抗R92という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。ダイオードDi9が逆流(逆電流)を防止することができる。

【0028】

実施の形態10.

図10は、本発明の実施の形態10にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態10にかかるブートストラップ回路は、ブートストラップ部用電源供給部80に代えてブートストラップ部用電源供給部100を備えている点で、実施の形態8にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部100は、抵抗R12、抵抗R11、コンデンサC10およびダイオードDi10を備えている。抵抗R12およびコンデンサC10は直列に接続している。コンデンサC10に対して、抵抗R11およびダイオードDi10の直列回路が並列に接続している。ダイオードDi10のアノードは、抵抗R12を介してP母線に接続している。ダイオードDi10のカソードは、抵抗R11と接続している。抵抗R11は、抵抗R12よりも高抵抗とする(抵抗R11>抵抗R12)。抵抗R11>抵抗R12という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。ダイオードDi10が逆流(逆電流)を防止することができる。

【符号の説明】

【0029】

2 DIP−IPM

4 HVIC

6 LVIC

10、20、30、40、50、60、70、80、90、100 ブートストラップ部用電源供給部

C1〜C10 コンデンサ

D1 ツェナーダイオード

Di3、4、7、9、10、20 ダイオード

L1、6 リアクトル

R1、2、3、6、7 抵抗

SW1 スイッチング素子

SW2 スイッチング素子

【技術分野】

【0001】

本発明は、ブートストラップ回路および半導体装置に関する。

【背景技術】

【0002】

従来、スイッチング素子およびこのスイッチング素子を駆動するための駆動回路を備えた、各種の電力変換回路が知られている。

例えば、特開平1−170378号公報は、DC/AC変換器に関するものであり、トランジスタの制御電極とソースの間の電圧を閾値電圧より高く保つことを保証するために、電圧レベルをシフトするブートストラップ回路について記載している(当該公報の3ページ目における紙面右下欄参照)。コンデンサ、抵抗器およびツェナーダイオードにより、電圧レベルシフトを行うことができる制御回路についても記載している(当該公報の5ページ目における紙面左上欄参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平1−170378号公報

【特許文献2】特開平9−298871号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

アーム回路あるいはハーフブリッジ回路は、高電位側に配置されたハイサイドスイッチング素子と、低電位側に配置されたローサイドスイッチング素子とを備えている。一般に、ハイサイドスイッチング素子を駆動するために、これを駆動するハイサイド駆動回路の電源を、ハイサイドスイッチング素子の電位(MOSFETであればソース電位、IGBTであればエミッタ電位)よりも一定電位だけ高くする必要がある。この電圧を印加するための方式の1つとして、ブートストラップ回路方式が知られている。

【0005】

従来、ブートストラップ回路として知られる構成として、次のようなものがあった。図11は、本願発明が解決しようとする課題を説明するために用いる、従来のブートストラップ回路の構成を説明するための図である。図11において、DIP−IPM(Dual-in-line Package Intelligent Power Module)2は、高耐圧ICであるHVIC4と、低耐圧ICであるLVIC6とを備えている。HVIC4のVcc端子およびLVIC6のVcc端子は、共通の電源に接続している。

【0006】

HVIC4のHO端子はスイッチング素子(IGBT)SW1のゲート端子と接続し、LVIC6のLO端子はスイッチング素子(IGBT)SW2のゲート端子と接続している。HVIC4のVS端子は、スイッチング素子SW1のエミッタとスイッチング素子SW2のコレクタとの間に接続している。LVIC6のVNO端子はスイッチング素子SW2のエミッタと接続している。スイッチング素子SW1のコレクタはP母線と接続し、スイッチング素子SW2のエミッタはN母線と接続している。P母線とN母線の間に、平滑コンデンサが設けられている。

【0007】

HVIC4のVB端子は、コンデンサC1の一方の端子と接続している。コンデンサC1の他方の端子は、HVIC4のVS端子に接続している。コンデンサC1と並列にツェナーダイオードD1が接続されている。コンデンサC1の他方の端子およびツェナーダイオードD1のアノードは、リアクトルL1の一方の端子に接続している。リアクトルL1の他方の端子は、グランド(GND)に接続されている。

【0008】

図11の回路は、ブートストラップ回路200を備えている。ブートストラップ回路200は、抵抗R200およびダイオードDi20の直列回路を備えている。この直列回路は、HVIC4のVcc端子側の配線と、HVIC4のVB端子側の配線との間に並列に接続している。すなわち、ブートストラップ回路200の抵抗R200の一端が、HVIC4のVcc端子側の配線と接続し、ブートストラップ回路200のダイオードDi20の他端(カソード)が、HVIC4のVB端子側の配線と接続している。ダイオードDi20は、いわゆるブートストラップダイオード(BSD)である。

【0009】

ハイサイドスイッチング素子(スイッチング素子SW1)を駆動するためには、HVIC(ハイサイド駆動回路)の電源を、ハイサイドスイッチング素子の電位(MOSFETであればソース電位、IGBTであればエミッタ電位)よりもVccだけ高い電位とする必要がある。図11の回路において、ブートストラップ回路200(つまり抵抗R200およびダイオードDi20)を介して、コンデンサC1が充電される。この電圧で、HVIC4を動作させることができる。

【0010】

しかしながら、上記従来のブートストラップ回路方式は、ブートストラップダイオード(BSD)を必須構成とするものであった。本願発明者は、鋭意研究の結果、従来のブートストラップ回路方式とは異なり、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路についての着想を得た。

【0011】

本発明は、上述のような課題を解決するためになされたもので、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を提供することを目的とする。

また、本発明の他の目的は、ブートストラップダイオード(BSD)を用いない新たな方式のブートストラップ回路を用いた半導体装置を提供することである。

【課題を解決するための手段】

【0012】

第1の発明にかかるブートストラップ回路は、

充電された電圧をスイッチング素子駆動用回路に印加する第1コンデンサと、

メイン電源母線に一方の端子が接続し、他方の端子が前記第1コンデンサと接続して、前記メイン電源母線の電圧を前記第1コンデンサに印加する抵抗と、

を備えることを特徴とする。

【0013】

第2の発明にかかる半導体装置は、

メイン電源母線と接続するハイサイドスイッチング素子と、

前記ハイサイドスイッチング素子を駆動するスイッチング素子駆動用回路と、

前記スイッチング素子駆動用回路と接続する前記第1の発明にかかるブートストラップ回路と、

を備えることを特徴とする。

【発明の効果】

【0014】

第1の発明にかかるブートストラップ回路によれば、メイン電源側からブートストラップ回路のコンデンサを充電することができ、ブートストラップダイオード(BSD)を省略することができる。

【0015】

第2の発明によれば、ブートストラップダイオード(BSD)を省略したブートストラップ回路を備えた半導体装置が提供される。

【図面の簡単な説明】

【0016】

【図1】本発明の実施の形態1にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図2】本発明の実施の形態2にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図3】本発明の実施の形態3にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図4】本発明の実施の形態4にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図5】本発明の実施の形態5にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図6】本発明の実施の形態6にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図7】本発明の実施の形態7にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図8】本発明の実施の形態8にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図9】本発明の実施の形態9にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図10】本発明の実施の形態10にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。

【図11】本願発明が解決しようとする課題を説明するために用いる、従来のブートストラップ回路の構成を説明するための図である。

【発明を実施するための形態】

【0017】

実施の形態1.

図1は、本発明の実施の形態1にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。図1には図11と共通する構成として、DIP−IPM(Dual-in-line Package Intelligent Power Module)2と、高耐圧ICであるHVIC4と、低耐圧ICであるLVIC6と、スイッチング素子(IGBT)SW1およびスイッチング素子(IGBT)SW2と、コンデンサC1と、ツェナーダイオードD1と、リアクトルL1などが示されている。これらの回路素子は、図11において説明したのと同様の接続関係で回路を形成しており、重複した説明を避けるため、図11と同様の点は説明を省略する。なお、符号2を付した図面中の破線領域内が、DIP−IPM2の内部構成を意味している。この符号2を付した破線領域内の構成が、例えばケースに収納されたり、トランスファーモールド樹脂封止されたりして、IPMとして提供されるものである。

【0018】

図1の回路は、ブートストラップ部用電源供給部10を備えている。ブートストラップ部用電源供給部10は、抵抗R1からなる回路である。抵抗R1の一方の端子は、P母線と接続している。抵抗R1の他方の端子は、コンデンサC1およびツェナーダイオードD1の並列回路の一端と接続している。コンデンサC1は、充電された電圧をスイッチング素子駆動用回路(HVIC4)に印加する。抵抗R1は、メイン電源母線に一方の端子が接続し、他方の端子がコンデンサC1と接続して、メイン電源母線の電圧をコンデンサC1に印加する。ハイサイドスイッチング素子(スイッチング素子SW1)を駆動するためには、HVIC4(ハイサイド駆動回路)の電源を、ハイサイドスイッチング素子の電位(スイッチング素子SW1のエミッタ電位)よりもVccだけ高い電位とする必要がある。この電圧を印加するための方式の1つが、ブートストラップ回路方式である。図1の回路において、抵抗R1を介して、メイン電源(P母線とN母線間から得られる電圧)によって、コンデンサC1が充電される。この電圧で、HVIC4を動作させることができる。

【0019】

実施の形態1にかかるブートストラップ回路によれば、抵抗R1によって、メイン電源側からブートストラップ回路のコンデンサC1を充電することができる。従って、図11に示したブートストラップ回路とは異なり、実施の形態1にかかるブートストラップ回路ではブートストラップダイオード(BSD)を省略することができる。

【0020】

実施の形態2.

図2は、本発明の実施の形態2にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態2にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部20を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部20は、抵抗R2およびコンデンサC2を備えている。抵抗R2は、実施の形態1にかかる抵抗R1と同様にコンデンサC1と接続しており、抵抗R1と同様の作用効果を発揮することができる。また、コンデンサC2により、スイッチング動作時におけるdv/dtで、ブートストラップ回路におけるコンデンサC1を充電できるようになる。

【0021】

実施の形態3.

図3は、本発明の実施の形態3にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態3にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部30を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部30は、抵抗R3およびダイオードDi3を備えている。抵抗R3およびダイオードDi3は直列に接続しており、抵抗R3およびダイオードDi3の直列回路は、実施の形態1にかかる抵抗R1と同様にコンデンサC1と接続している。具体的には、ダイオードDi3のアノードは、抵抗R3を介してP母線と接続しており、ダイオードDi3のカソードはコンデンサC1と接続している。

抵抗R3とダイオードDi3の直列回路を介して、実施の形態1の抵抗R1と同様に、メイン電源母線の電圧をコンデンサC1に印加するという作用効果を得ることができる。さらに、ダイオードDi3が逆流防止用のダイオードとして機能することができる。

【0022】

実施の形態4.

図4は、本発明の実施の形態4にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態4にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部40を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部40は、抵抗R4、コンデンサC4およびダイオードDi4を備えている。コンデンサC4は、抵抗R4およびダイオードDi4は、実施の形態3にかかる抵抗R3およびダイオードDi3と同様の直列回路を構成しており、ダイオードDi4はダイオードDi3と同様に逆流防止用のダイオードとして機能する。また、抵抗R4とダイオードDi4の直列回路に対してコンデンサC4が並列に接続しており、コンデンサC4は実施の形態2のコンデンサC2と同様の作用を発揮する。

【0023】

実施の形態5.

図5は、本発明の実施の形態5にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態5にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部50を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部50は、コンデンサC5、抵抗R51および抵抗R52を備えている。コンデンサC5および抵抗R51の直列回路に対し、抵抗R52が並列に接続している。抵抗R52は、実施の形態1にかかる抵抗R1と同様に、メイン電源側からコンデンサC1へと電源供給を行うことができる。また、ブートストラップ部用電源供給部50によれば、コンデンサC5に抵抗R51を直列に接続することで、ツェナーダイオードD1を保護することができる。

【0024】

実施の形態6.

図6は、本発明の実施の形態6にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態6にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部60を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部60は、コンデンサC6、抵抗R6、およびリアクトルL6を備えている。コンデンサC6およびリアクトルL6の直列回路と、抵抗R6とが、並列に接続している。抵抗R6は、実施の形態1にかかる抵抗R1と同様に、メイン電源側からコンデンサC1へと電源供給を行うことができる。また、ブートストラップ部用電源供給部60によれば、コンデンサC6にリアクトルL6を直列に接続することで、ツェナーダイオードD1を保護することができる。

【0025】

実施の形態7.

図7は、本発明の実施の形態7にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態7にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部70を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部70は、ダイオードDi7、抵抗R7およびコンデンサC7を備えている。ダイオードDi7のアノードが、P母線と接続している。ダイオードDi7のカソードはコンデンサC7と接続し、ダイオードDi7とコンデンサC7は直列回路を形成している。抵抗R7は、コンデンサC7に並列に接続している。ブートストラップ部用電源供給部70によっても、メイン電源側を利用してコンデンサC1を充電することができる。さらに、コンデンサC7が、実施の形態2におけるコンデンサC2と同様の作用効果を奏し、また、ダイオードDi7によりツェナーダイオードD1を保護することができる。

【0026】

実施の形態8.

図8は、本発明の実施の形態8にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態8にかかるブートストラップ回路は、ブートストラップ部用電源供給部10に代えてブートストラップ部用電源供給部80を備えている点で、実施の形態1にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部80は、抵抗R82、抵抗R81およびコンデンサC8を備えている。抵抗R82およびコンデンサC8は直列に接続しており、抵抗R81はコンデンサC8に並列に接続している。抵抗R82およびコンデンサC8の直列回路が、P母線と、コンデンサC1の一方の端子との間に介在している。抵抗R81は、抵抗R82よりも高抵抗とする。つまり、「抵抗R81の抵抗値>抵抗R82の抵抗値」という関係が成立するように、抵抗R81および抵抗R82を選定する。抵抗R81>抵抗R82という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。

【0027】

実施の形態9.

図9は、本発明の実施の形態9にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態9にかかるブートストラップ回路は、ブートストラップ部用電源供給部80に代えてブートストラップ部用電源供給部90を備えている点で、実施の形態8にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部90は、抵抗R92、抵抗R91、コンデンサC9およびダイオードDi9を備えている。抵抗R92、コンデンサC9およびダイオードDi9は直列に接続しており、抵抗R91はコンデンサC9に並列に接続している。抵抗R92、コンデンサC9およびダイオードDi9の直列回路が、P母線と、コンデンサC1の一方の端子との間に介在している。抵抗R91は、抵抗R92よりも高抵抗とする(抵抗R91>抵抗R92)。抵抗R91>抵抗R92という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。ダイオードDi9が逆流(逆電流)を防止することができる。

【0028】

実施の形態10.

図10は、本発明の実施の形態10にかかるブートストラップ回路およびこれを備えた半導体装置の構成を示す回路図である。実施の形態10にかかるブートストラップ回路は、ブートストラップ部用電源供給部80に代えてブートストラップ部用電源供給部100を備えている点で、実施の形態8にかかるブートストラップ回路と相違している。ブートストラップ部用電源供給部100は、抵抗R12、抵抗R11、コンデンサC10およびダイオードDi10を備えている。抵抗R12およびコンデンサC10は直列に接続している。コンデンサC10に対して、抵抗R11およびダイオードDi10の直列回路が並列に接続している。ダイオードDi10のアノードは、抵抗R12を介してP母線に接続している。ダイオードDi10のカソードは、抵抗R11と接続している。抵抗R11は、抵抗R12よりも高抵抗とする(抵抗R11>抵抗R12)。抵抗R11>抵抗R12という関係が成立することで、ブートストラップ部への電源供給(つまりコンデンサC1の充電)を安定させることができる。ダイオードDi10が逆流(逆電流)を防止することができる。

【符号の説明】

【0029】

2 DIP−IPM

4 HVIC

6 LVIC

10、20、30、40、50、60、70、80、90、100 ブートストラップ部用電源供給部

C1〜C10 コンデンサ

D1 ツェナーダイオード

Di3、4、7、9、10、20 ダイオード

L1、6 リアクトル

R1、2、3、6、7 抵抗

SW1 スイッチング素子

SW2 スイッチング素子

【特許請求の範囲】

【請求項1】

充電された電圧をスイッチング素子駆動用回路に印加する第1コンデンサと、

メイン電源母線に一方の端子が接続し、他方の端子が前記第1コンデンサと接続して、前記メイン電源母線の電圧を前記第1コンデンサに印加する第1抵抗と、

を備えることを特徴とするブートストラップ回路。

【請求項2】

前記第1抵抗に並列に接続する第2コンデンサを、さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項3】

前記第1抵抗と前記第1コンデンサとの間に設けられ、アノードが前記抵抗と接続しカソードが前記第1コンデンサと接続するダイオードを、

さらに備えることを特徴とする請求項1または2に記載のブートストラップ回路。

【請求項4】

コンデンサおよび抵抗を有し、このコンデンサの一方の端子が前記P母線側と接続し、このコンデンサの他方の端子がこの抵抗の一方の端子と接続し、且つこの抵抗の他方の端子が前記第1コンデンサと前記第1抵抗との間に接続する直列回路を、

さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項5】

コンデンサおよびリアクトルを有し、このコンデンサの一方の端子が前記P母線側と接続し、このコンデンサの他方の端子がこのリアクトルの一方の端子と接続し、且つこのリアクトルの他方の端子が前記第1コンデンサと前記第1抵抗との間に接続する直列回路を、さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項6】

前記第1抵抗と前記メイン電源母線との間に設けられ、アノードが前記メイン電源母線と接続しカソードが前記第1抵抗と接続するダイオードと、

一方の端子が前記第1抵抗と前記ダイオードの前記カソードとの間に接続し、他方の端子が前記第1抵抗と前記第1コンデンサとの間に接続するコンデンサと、

を備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項7】

前記第1抵抗と前記メイン電源母線との間に設けられ、一方の端子が前記メイン電源母線と接続し他方の端子が前記第1抵抗と接続し、前記第1抵抗よりも低い抵抗値を有する第3抵抗と、

一方の端子が前記第1抵抗と前記第3抵抗との間に接続し、他方の端子が前記第1抵抗と前記第1コンデンサとの間に接続するコンデンサと、

を備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項8】

前記メイン電源母線と前記第3抵抗の間に設けられ、アノードが前記第3抵抗と接続し、カソードが前記第1抵抗と接続するダイオードを、

さらに備えることを特徴とする請求項7に記載のブートストラップ回路。

【請求項9】

前記第1抵抗と前記第3抵抗の間に設けられ、アノードが前記メイン電源母線と接続し、カソードが前記第3抵抗と接続するダイオードを、

さらに備えることを特徴とする請求項7に記載のブートストラップ回路。

【請求項10】

メイン電源母線と接続するハイサイドスイッチング素子と、

前記ハイサイドスイッチング素子を駆動するスイッチング素子駆動用回路と、

前記スイッチング素子駆動用回路と接続する請求項1乃至9のいずれか1項に記載のブートストラップ回路と、

を備えることを特徴とする半導体装置。

【請求項1】

充電された電圧をスイッチング素子駆動用回路に印加する第1コンデンサと、

メイン電源母線に一方の端子が接続し、他方の端子が前記第1コンデンサと接続して、前記メイン電源母線の電圧を前記第1コンデンサに印加する第1抵抗と、

を備えることを特徴とするブートストラップ回路。

【請求項2】

前記第1抵抗に並列に接続する第2コンデンサを、さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項3】

前記第1抵抗と前記第1コンデンサとの間に設けられ、アノードが前記抵抗と接続しカソードが前記第1コンデンサと接続するダイオードを、

さらに備えることを特徴とする請求項1または2に記載のブートストラップ回路。

【請求項4】

コンデンサおよび抵抗を有し、このコンデンサの一方の端子が前記P母線側と接続し、このコンデンサの他方の端子がこの抵抗の一方の端子と接続し、且つこの抵抗の他方の端子が前記第1コンデンサと前記第1抵抗との間に接続する直列回路を、

さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項5】

コンデンサおよびリアクトルを有し、このコンデンサの一方の端子が前記P母線側と接続し、このコンデンサの他方の端子がこのリアクトルの一方の端子と接続し、且つこのリアクトルの他方の端子が前記第1コンデンサと前記第1抵抗との間に接続する直列回路を、さらに備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項6】

前記第1抵抗と前記メイン電源母線との間に設けられ、アノードが前記メイン電源母線と接続しカソードが前記第1抵抗と接続するダイオードと、

一方の端子が前記第1抵抗と前記ダイオードの前記カソードとの間に接続し、他方の端子が前記第1抵抗と前記第1コンデンサとの間に接続するコンデンサと、

を備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項7】

前記第1抵抗と前記メイン電源母線との間に設けられ、一方の端子が前記メイン電源母線と接続し他方の端子が前記第1抵抗と接続し、前記第1抵抗よりも低い抵抗値を有する第3抵抗と、

一方の端子が前記第1抵抗と前記第3抵抗との間に接続し、他方の端子が前記第1抵抗と前記第1コンデンサとの間に接続するコンデンサと、

を備えることを特徴とする請求項1に記載のブートストラップ回路。

【請求項8】

前記メイン電源母線と前記第3抵抗の間に設けられ、アノードが前記第3抵抗と接続し、カソードが前記第1抵抗と接続するダイオードを、

さらに備えることを特徴とする請求項7に記載のブートストラップ回路。

【請求項9】

前記第1抵抗と前記第3抵抗の間に設けられ、アノードが前記メイン電源母線と接続し、カソードが前記第3抵抗と接続するダイオードを、

さらに備えることを特徴とする請求項7に記載のブートストラップ回路。

【請求項10】

メイン電源母線と接続するハイサイドスイッチング素子と、

前記ハイサイドスイッチング素子を駆動するスイッチング素子駆動用回路と、

前記スイッチング素子駆動用回路と接続する請求項1乃至9のいずれか1項に記載のブートストラップ回路と、

を備えることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−55549(P2013−55549A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−193089(P2011−193089)

【出願日】平成23年9月5日(2011.9.5)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月5日(2011.9.5)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]