プラズマディスプレイパネルの駆動方法およびプラズマディスプレイ装置

【課題】高精細なプラズマディスプレイパネルにおいて、書込み期間の放電を確実に起こして放電セルで誤放電が発生すること防止し、駆動コストを低減しつつ駆動性能を向上させる。

【解決手段】複数の走査電極群にそれぞれ含まれる走査電極と、走査電極に略平行に配置される複数の維持電極と、走査電極および維持電極に放電空間を挟んで略直交するように配置される複数のデータ電極からなる交差部にそれぞれ放電セルを有するプラズマディスプレイパネルを、1フィールド期間を書込み期間と維持期間を備える複数のサブフィールドに分けて駆動する駆動装置であって、走査電極群ごとに書込み期間に印加する駆動電圧が異なり、最後に書込みを行う走査電極群の走査電極の数が最も多いことを特徴とするプラズマディスプレイパネルの駆動装置である。

【解決手段】複数の走査電極群にそれぞれ含まれる走査電極と、走査電極に略平行に配置される複数の維持電極と、走査電極および維持電極に放電空間を挟んで略直交するように配置される複数のデータ電極からなる交差部にそれぞれ放電セルを有するプラズマディスプレイパネルを、1フィールド期間を書込み期間と維持期間を備える複数のサブフィールドに分けて駆動する駆動装置であって、走査電極群ごとに書込み期間に印加する駆動電圧が異なり、最後に書込みを行う走査電極群の走査電極の数が最も多いことを特徴とするプラズマディスプレイパネルの駆動装置である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プラズマディスプレイパネルの駆動方法ならびにそれを用いたプラズマディスプレイ装置に関する。

【背景技術】

【0002】

プラズマディスプレイパネル(以下、「パネル」と略記する)として代表的な交流面放電型パネルは、対向配置された前面板と背面板との間に多数の放電セルを備える。

【0003】

前面板は、前面ガラス基板、複数の表示電極、誘電体層および保護層により構成される。各表示電極は、一対の走査電極および維持電極からなる。複数の表示電極は、前面ガラス基板上に互いに平行に形成され、それらの表示電極を覆うように誘電体層および保護層が形成されている。

【0004】

背面板は、背面ガラス基板、複数のデータ電極、誘電体層、複数の隔壁および蛍光体層により構成される。背面ガラス基板上に複数のデータ電極が平行に形成され、それらを覆うように誘電体層が形成されている。その誘電体層上にデータ電極と平行に複数の隔壁がそれぞれ形成され、誘電体層の表面と隔壁の側面とにR(赤)、G(緑)およびB(青)の蛍光体層が形成されている。

【0005】

そして、表示電極とデータ電極とが立体交差するように前面板と背面板とが対向配置されて密封され、内部の放電空間には放電ガスが封入されている。表示電極とデータ電極とが対向する部分に放電セルが形成される。

【0006】

このような構成を有するパネルにおいて、各放電セル内でガス放電により紫外線が発生し、その紫外線でR、GおよびBの蛍光体が励起されて発光する。それにより、カラー表示が行われる。

【0007】

パネルを駆動する方法としてはサブフィールド法が用いられている(例えば、特許文献1参照)。サブフィールド法では、1フィールド期間が複数のサブフィールドに分割され、それぞれのサブフィールドで各放電セルを発光または非発光させることにより階調表示が行われる。各サブフィールドは、初期化期間、書込み期間および維持期間を有する。

【0008】

初期化期間においては、各走査電極に初期化パルスが印加され、各放電セルで初期化放電が行われる。それにより、各放電セルにおいて、続く書込み動作のために必要な壁電荷が形成される。

【0009】

書込み期間では、走査電極に順次走査パルスを印加するとともに、データ電極には表示すべき画像信号に対応した書込みパルスを印加する。それにより、走査電極とデータ電極との間で選択的に書込み放電が発生し、選択的な壁電荷形成が行われる。

【0010】

続く維持期間では、表示させるべき輝度に応じた所定の回数の維持パルスを走査電極と維持電極との間に印加する。それにより、書込み放電による壁電荷形成が行われた放電セルで選択的に放電が起こり、その放電セルが発光する。

【0011】

複数の走査電極は走査電極駆動回路により駆動され、複数の維持電極は維持電極駆動回路により駆動され、複数のデータ電極はデータ電極駆動回路により駆動される。

【0012】

一方、書込み期間における走査電極への走査パルス電圧の印加は、各走査電極に対して順次に行われるため、特に高精細化されたパネルにおいては、走査電極数の増加によって書込みに費やす時間が長くなってしまう。そのため、書込み期間の最後の方に書込み動作がなされる放電セルでは、書込み期間の最初の方に書込み動作がなされる放電セルに比べて、壁電荷の消失量が多く、書込み放電が不安定になりやすい。そこで、書込み期間の最後の方に書込み動作がなされる放電セルに合わせて壁電荷の量を調整するように波形を設計すると、今度は書込み期間の最初の方で書込み動作が行われる放電セルにおいて壁電荷が過剰となるため、書込み放電が強くなり、壁電荷が隣接セルに移動してしまい、結果誤放電が発生するという問題が起こる。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2006−18298号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

ところで、上述したように、書込み期間においては、複数の走査電極に走査パルスが順次印加される。従って、複数の放電セルのうち走査パルスが印加される順番が遅い放電セルにおいては、初期化パルスが印加されてから走査パルスが印加されるまでの間の時間が長くなる。

【0015】

ここで、初期化放電によって放電セルに形成された壁電荷は、他の放電セルに書込み放電を発生させるためにデータ電極に印加される書込みパルスの影響を受けて徐々に減少する。この放電セルに形成された壁電荷は、走査パルスが印加される走査電極の順序に対して、対数関数的に減少する。そのため、走査パルスが印加される順番が遅い放電セルにおいては、その放電セルに走査パルスおよび書込みパルスが印加されるまでに壁電荷が減少し、書込み放電の放電不良が発生する場合がある。

【0016】

その書込み不良を防止するために、走査パルスが印加される順番が遅い放電セルで放電不良が発生しないように波形を設計すると、今度は走査パルスが印加される順番が早い放電セルに蓄積される壁電荷量が過剰となるため、書込み放電強度が強くなり、壁電荷が隣接セルに移動してしまい、誤放電が発生してしまう。

【0017】

本発明の目的は、書込み放電の放電不良と誤放電とを防止することができるプラズマディスプレイパネルの駆動装置および駆動方法ならびにそれを用いたプラズマディスプレイ装置を提供することである。

【課題を解決するための手段】

【0018】

これらの課題を解決するために本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、複数の第1、第2および第3の走査電極、複数の維持電極ならびに複数のデータ電極の交差部にそれぞれ放電セルを有するプラズマディスプレイパネルを、1フィールド期間を複数のサブフィールドに分けて駆動する駆動装置であって、複数の第1の走査電極を駆動する第1の回路と、複数の第2の走査電極を駆動する第2の回路と、複数の第3の走査電極を駆動する第3の回路とを備え、複数の第1、第2および第3の回路は、複数のサブフィールドのうち少なくとも1つのサブフィールドにおいて、パネル特性に応じて3相駆動動作を行い、第1の回路は、3相駆動動作時には、サブフィールドの初期化期間において第1の電位から第2の電位に下降する第1のランプ波形を複数の第1の走査電極に印加し、書込み期間において複数の第1の走査電極に順に走査パルスを印加し、第2の回路は、3相駆動動作時には、初期化期間において第1の電位から第2の電位よりも高い第3の電位に下降する第2のランプ波形を複数の第2の走査電極に印加し、書込み期間において複数の第2の走査電極を第3の電位よりも高い第4の電位に保持しつつ複数の第1の走査電極への走査パルスの印加後に複数の第2の走査電極に順に走査パルスを印加し、第3の回路は、3相駆動動作時には、初期化期間において第2のランプ波形を複数の第3の走査電極に印加し、書込み期間において複数の第3の走査電極を第4の電位に保持しつつ複数の第2の走査電極への走査パルスの印加後に複数の第3の走査電極に順に走査パルスを印加し、第3の回路が駆動する複数の第3の走査電極の数が最も多く、第2の回路が駆動する複数の第2の走査電極の数が次に多く、第1の回路が駆動する複数の第1の走査電極の数が最も少ないことを特徴とするものである。

【0019】

また本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、3相駆動動作時に第2の回路が、書込み期間において複数の第1の走査電極への走査パルスの印加後で、複数の第2の走査電極への走査パルスの印加前に、第4の電位以下の第5の電位へ下降する第3のランプ波形を複数の第2の走査電極に印加し、第3の回路は、3相駆動動作時には、書込み期間において複数の第1の走査電極への走査パルスの印加後で、複数の第2の走査電極への走査パルスの印加前に、第4の電位以下で第5の電位よりも高い第6の電位へ下降する第4のランプ波形を複数の第3の走査電極に印加するものであってもよい。

【0020】

また本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、3相駆動動作時に第3の駆動回路が、書込み期間において複数の第2の走査電極への走査パルスの印加後で複数の第3の走査電極への走査パルスの印加前に第4の電位以下の第7の電位へ下降する第5のランプ波形を複数の第3の走査電極に印加するものであってもよい。

【0021】

本発明によれば、第1の走査電極に走査パルスが印加されている間に第2の走査電極上の放電セルの壁電荷が減少しても、第2の走査電極への走査パルスの印加時に第2の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができ、同様に第2の走査電極に走査パルスが印加されている間に第3の走査電極上の放電セルの壁電荷が減少しても、第3の走査電極への走査パルスの印加時に第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第2、第3の走査電極上の放電セルに放電不良や誤放電が発生することを防止することができる。

【発明の効果】

【0022】

この駆動装置においては、複数のサブフィールドのうち少なくとも1つのサブフィールドにおいて、第1、第2および第3の回路により3相駆動動作が行われる。3相駆動動作時には、初期化期間において、第1の回路により第1の電位から第2の電位に下降する第1のランプ波形が複数の第1の走査電極に印加される。それにより、第1の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。その結果、第1の走査電極上の放電セルにおける壁電荷の量が書込み動作に適した状態になる。また、初期化期間において、第2の回路により第1の電位から第3の電位に下降する第2のランプ波形が複数の第2の走査電極に印加される。それにより、第2の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。

【0023】

ここで、第1のランプ波形が第2の電位まで下降するのに対して、第2のランプ波形は第2の電位よりも高い第3の電位までしか下降しない。そのため、第2の走査電極上の放電セルで移動する電荷の量は、第1の走査電極上の放電セルで移動する電荷の量よりも少ない。それにより、初期化期間の終了時に、第2の走査電極上の放電セルには十分な量の壁電荷が残る。同様に、初期化期間において、第3の回路により第1の電位から第3の電位に下降する第2のランプ波形が複数の第3の走査電極に印加される。それにより、第3の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。そのため、初期化期間の終了時に、第3の走査電極上の放電セルには十分な量の壁電荷が残る。

【0024】

書込み期間においては、第1の回路により複数の第1の走査電極に順に走査パルスが印加される。それにより、第1の走査電極上の選択された放電セルにおいて書込み放電が発生する。また、複数の第1の走査電極への走査パルスの印加後に、第2の回路により複数の第2の走査電極に順に走査パルスが印加される。それにより、第2の走査電極上の選択された放電セルにおいて書込み放電が発生する。また、複数の第2の走査電極への走査パルスの印加後に、第3の回路により複数の第3の走査電極に順に走査パルスが印加される。それにより、第3の走査電極上の選択された放電セルにおいて書込み放電が発生する。

【0025】

上記のように、第2および第3の走査電極上の放電セルには、初期化期間の終了時に十分な量の電荷が残されている。従って、第1の走査電極に走査パルスが印加されている間に第2および第3の走査電極上の放電セルの壁電荷が減少しても、第2および第3の走査電極への走査パルスの印加時に第2および第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第2および第3の走査電極上の放電セルに放電不良が発生することを防止することができる。さらに、第2の走査電極に走査パルスが印加されている間に第3の走査電極上の壁電荷が減少しても、第3の走査電極への走査パルスの印加時に第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第3の走査電極上の放電セルに放電不良が発生することを防止することができる。

【0026】

また、壁電荷が減少しても第2および第3の走査電極上の放電セルに良好に書込み動作を発生させることが可能であるので、書込み期間において壁電荷の減少を防止するために第2および第3の走査電極を高い電位に保持する必要がない。それにより、プラズマディスプレイパネルの駆動コストを低減しつつ駆動性能を向上させることが可能になる。

【0027】

また、初期化期間において第2および第3の走査電極上の放電セルに適度に放電が発生することにより、初期化期間の終了時にそれらの放電セルに過剰に電荷が残ることが防止される。それにより、第1の走査電極に走査パルスが印加される際に第2および第3の走査電極上の放電セルで誤放電が発生することが防止される。

【0028】

また、書込み期間においては、走査パルスが印加される期間を除いて第2および第3の走査電極が第3の電位よりも高い第4の電位に保持される。この場合、第2および第3の走査電極上の放電セルにおける電荷の状態が安定する。それにより、第2および第3の走査電極上の放電セルで誤放電が発生することをより確実に防止することができる。

【図面の簡単な説明】

【0029】

【図1】本発明の一実施の形態であるプラズマディスプレイ装置におけるプラズマディスプレイパネルの一部を示す分解斜視図

【図2】同プラズマディスプレイパネルの電極配列図

【図3】同プラズマディスプレイ装置の回路ブロック図

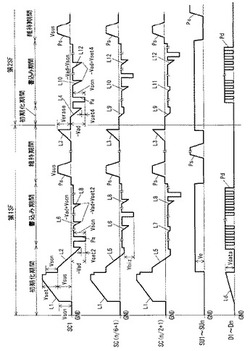

【図4】同プラズマディスプレイ装置のサブフィールド構成における一駆動例である3相駆動波形図

【図5】同プラズマディスプレイ装置のサブフィールド構成における他の駆動例である2相駆動波形図

【図6】同プラズマディスプレイ装置の3相駆動時の走査電極駆動回路の構成を示す回路図

【図7】同プラズマディスプレイ装置の制御信号の論理と走査ICの状態との対応関係を示す図

【図8】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第1のタイミング図

【図9】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第2のタイミング図

【図10】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第3のタイミング図

【図11】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第4のタイミング図

【図12】同プラズマディスプレイ装置の2相駆動時の走査電極駆動回路の構成を示す回路図

【図13】同プラズマディスプレイ装置の走査電極駆動回路の2相駆動動作時にトランジスタに与えられる制御信号の第1のタイミング図

【図14】同プラズマディスプレイ装置の走査電極駆動回路の2相駆動動作時にトランジスタに与えられる制御信号の第2のタイミング図

【図15】同プラズマディスプレイ装置の比較回路およびその周辺部分の構成を示す図

【図16】同プラズマディスプレイ装置の1相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【図17】同プラズマディスプレイ装置の3相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【図18】同プラズマディスプレイ装置の2相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【発明を実施するための最良の形態】

【0030】

以下、本発明の実施の形態に係るプラズマディスプレイパネルの駆動装置、駆動方法およびプラズマディスプレイ装置について、図面を用いて詳細に説明する。

【0031】

(1)第1の実施の形態

(1−1)パネルの構成

図1は、本発明の第1の実施の形態に係るプラズマディスプレイ装置におけるプラズマディスプレイパネルの一部を示す分解斜視図である。プラズマディスプレイパネル(以下、パネルと略記する)10は、互いに対向配置されたガラス製の前面基板21および背面基板31を備える。前面基板21および背面基板31の間に放電空間が形成される。前面基板21上には複数対の走査電極22および維持電極23が互いに平行に形成されている。各対の走査電極22および維持電極23が表示電極を構成する。走査電極22および維持電極23を覆うように誘電体層24が形成され、誘電体層24上には保護層25が形成されている。

【0032】

背面基板31上には絶縁体層33で覆われた複数のデータ電極32が設けられ、絶縁体層33上に井桁状の隔壁34が設けられている。また、絶縁体層33の表面および隔壁34の側面に蛍光体層35が設けられている。そして、複数対の走査電極22および維持電極23と複数のデータ電極32とが垂直に交差するように前面基板21と背面基板31とが対向配置され、前面基板21と背面基板31との間に放電空間が形成されている。放電空間には、放電ガスとして、例えばネオンとキセノンとの混合ガスが封入されている。なお、パネルの構造は上述したものに限られず、例えばストライプ状の隔壁を備えた構造を用いてもよい。

【0033】

図2は本発明の第1の実施の形態におけるパネルの電極配列図である。行方向に沿ってn本の走査電極SC1〜SCn(図1の走査電極22)およびn本の維持電極SU1〜SUn(図1の維持電極23)が配列され、列方向に沿ってm本のデータ電極D1〜Dm(図1のデータ電極32)が配列されている。nは偶数であり、mは2以上の自然数である。そして、1対の走査電極SCi(i=1〜n)および維持電極SUi(i=1〜n)と1つのデータ電極Dj(j=1〜m)とが交差した部分に放電セルDCが形成されている。それにより、放電空間内にm×n個の放電セルが形成されている。

【0034】

(1−2)プラズマディスプレイ装置の構成

図3は本発明の第1の実施の形態に係るプラズマディスプレイ装置の回路ブロック図である。このプラズマディスプレイ装置は、パネル10、画像信号処理回路51、データ電極駆動回路52、走査電極駆動回路53、維持電極駆動回路54、タイミング発生回路55、APL検出器56および電源回路(図示せず)を備える。画像信号処理回路51は、画像信号sigをパネル10の画素数に応じた画像データに変換し、各画素の画像データを複数のサブフィールドに対応する複数のビットに分割し、それらをデータ電極駆動回路52に出力する。

【0035】

データ電極駆動回路52は、サブフィールド毎の画像データを各データ電極D1〜Dmに対応する信号に変換し、その信号に基づいて各データ電極D1〜Dmを駆動する。APL検出器56は、画像信号sigのAPL(平均画像レベル;Average Picture Level)を検出し、検出したAPLを示す信号をタイミング発生回路55へ出力する。ここで、APLとは、1フレームにおける画像信号sigの輝度レベルの平均をいい、1画面の画像の全体的な明るさを表している。本実施の形態では、1フレームは1フィールドに等しい。

【0036】

タイミング発生回路55は、水平同期信号H、垂直同期信号VおよびAPL検出器56が検出した平均輝度レベルAPLに基づいてタイミング信号を発生し、それらのタイミング信号をそれぞれの駆動回路ブロック(画像信号処理回路51、データ電極駆動回路52、走査電極駆動回路53および維持電極駆動回路54)へ供給する。

【0037】

走査電極駆動回路53は、タイミング信号に基づいて走査電極SC1〜SCnに駆動波形を供給し、維持電極駆動回路54はタイミング信号に基づいて維持電極SU1〜SUnに駆動波形を供給する。なお、走査電極駆動回路53は、後述するように、初期化期間において走査電極(SC1,SC2,…,SC(n/6))、走査電極(SC(n/6+1),SC(n/6+2),…,SC(n/2))と走査電極(SC(n/2+1),SC(n/2+2),SC(n))と、走査電極群を2:4:6に分割し、それぞれに異なる駆動波形を印加する3相駆動動作および走査電極(SC1,SC2,…SC(n/3))と走査電極(SC(n/3+1),SC(n/3+2),…SC(n))と、走査電極群を4:8に分割し、それぞれに異なる駆動波形を印加する2相駆動動作とを選択的に行うことができる。ここで、nは6の倍数である。

【0038】

また、本実施の形態においては、タイミング発生回路55は、APL検出器56により検出されるAPLに基づいて、1相駆動動作のためのタイミング信号および3相駆動動作のためのタイミング信号を選択的に発生し、発生したタイミング信号を走査電極駆動回路53へ供給する。それにより、走査電極SC1〜SCnが1相駆動動作または3相駆動動作により駆動される。

【0039】

以下の説明においては、3相駆動動作時においては、走査電極(SC1,SC2,…,SC(n/6))を第1の走査電極群と称し、走査電極(SC(n/6+1),SC(n/6+2),…,SC(n/2))を第2の走査電極群と称し、走査電極(SC(n/2+1),SC(n/2+2),…SC(n))を第3の走査電極群と称する。また、維持電極(SU1,SU2,…,SU(n/6))を第1の維持電極群と称し、維持電極(SU(n/6+1),SU(n/6+2),…,SU(n/2))を第2の維持電極群と称し、維持電極(SU(n/2+1),SU(n/2+2),SU(n))を第3の維持電極群と称する。さらに、第1の走査電極群および第1の維持電極群により構成される複数の放電セルを第1の放電セル群と称し、第2の走査電極群および第2の維持電極群により構成される複数の放電セルを第2の放電セル群と称し、第3の走査電極群および第3の維持電極群により構成される複数の放電セルを第3の放電セル群と称する。

【0040】

また、2相駆動動作時においては名称を変え、走査電極(SC1,SC2,…SC(n/3))を第4の走査電極群と称し、走査電極(SC(n/3+1),SC(n/3+2),…SC(n))を第5の走査電極群と称する。また、維持電極(SU1,SU2,…SU(n/3))を第4の維持電極群、維持電極(SU(n/3+1),SU(n/3+2),…SU(n))を第5の維持電極群と称する。さらに、第4の走査電極群および第4の維持電極群により構成される複数の放電セルを第4の放電セル群と称し、第5の走査電極群と第5の維持電極群により構成される複数の放電セルを第5の放電セル群と称する。

【0041】

(1−3)サブフィールド構成

次に、サブフィールド構成について説明する。サブフィールド法では、1フィールド(1/60秒=16.67msec)が時間軸上で複数のサブフィールドに分割され、複数のサブフィールドに輝度重みがそれぞれ設定されている。例えば、1フィールドが時間軸上で10個のサブフィールド(以下、第1SF、第2SF、・・・、および第10SFと呼ぶ)に分割され、それらのサブフィールドがそれぞれ1、2、3、6、11、18、30、44、60および81の輝度重みを有する。

【0042】

図4および図5は、図3のプラズマディスプレイ装置のサブフィールド構成における、走査電極駆動回路53の駆動動作時に各電極に印加される駆動波形を示す図である。なお、図4は、走査電極駆動回路53の3相駆動動作時に各電極に印加される駆動波形を示し、図5は走査電極駆動回路53の2相駆動動作時に各電極に印加される駆動波形を示す。図4には、第1の走査電極群(SC1,SC2,…,SC(n/6))の1本の走査電極SC1、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))の1本の走査電極SC(n/6+1)、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の1本の走査電極SC(n/2+1)、維持電極SU1〜SUn、およびデータ電極D1〜Dmの駆動波形が示される。なお、図4には、1フィールドの第1SFの初期化期間から第2SFの維持期間までが示される。また、図5には、第4の走査電極群(SC1,SC2,…SC(n/3))の1本の走査電極SC1、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))の1本の走査電極SC(n/3+1)、維持電極SU1〜SUn、およびデータ電極D1〜Dmの駆動波形が示される。なお、図5には、1フィールドの第1SFの初期化期間から第2SFの維持期間までが示される。

【0043】

(a)3相駆動動作時の駆動波形

まず、走査電極駆動回路53の3相駆動動作時に各電極に印加される駆動波形について説明する。図4に示すように、第1SFの初期化期間の前半部では、データ電極D1〜Dmに電位0V(接地電位)からVdaに緩やかに上昇するランプ波形Ldを印加し、維持電極SU1〜SUnを接地電位に保持し、走査電極SC1〜SCnにランプ波形L1を印加する。このランプ波形L1は、放電開始電圧以下の正の電位Vscnから放電開始電圧を超える正の電位(Vsus+Vset)に向かって緩やかに上昇する。すると、全ての放電セルにおいて1回目の微弱な初期化放電が起こり、走査電極SC1〜SCn上に負の壁電荷が蓄えられるとともに維持電極SU1〜SUn上およびデータ電極D1〜Dm上に正の壁電荷が蓄えられる。ここで、電極を覆う誘電体層または蛍光体層上等に蓄積した壁電荷により生じる電圧を電極上の壁電圧という。

【0044】

続く初期化期間の後半部では、データ電極D1〜Dmを接地電位に保持し、維持電極SU1〜SUnを正の電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))にVsusから(−Vad+Vset2)に向かって緩やかに下降するランプ波形L2を印加する。すると、第1の放電セル群において2回目の微弱な初期化放電が起こる。これにより、第1の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0045】

一方、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L5を印加する。これにより、第2の放電セル群および第3の放電セル群において2回目の微弱な初期化放電が起こる。その後、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。なお、Vhizは、Vset2およびVset4よりも大きい。

【0046】

ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))に印加されるランプ波形L2は(−Vad+Vset2)まで下降するのに対して、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),SC(n))に印加されるランプ波形L5は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第2の放電セル群、第3の放電セル群においては2回目の初期化放電によって移動する電荷の量が第1の放電セル群に比べて少ない。それにより、2回目の初期化放電後、第2の放電セル群および第3の放電セル群には、第1の放電セル群より多くの壁電荷が保持される。

【0047】

続く第1SFの書込み期間の前半部では、維持電極SU1〜SUnを一旦電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、1行目の走査電極SC1に負の走査パルスPa(=−Vad)を印加するとともに、データ電極D1〜Dmのうち1行目において発光すべき放電セルのデータ電極Dk(kは1〜mのいずれか)に正の書込みパルスPd(=Vda)を印加する。すると、データ電極Dkと走査電極SC1との交差部の電圧は、外部印加電圧(Pd−Pa)にデータ電極Dk上の壁電圧および走査電極SC1上の壁電圧が加算された値となり、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC1との間および維持電極SU1と走査電極SC1との間で書込み放電が発生する。その結果、その放電セルの走査電極SC1上に正の壁電荷が蓄積され、維持電極SU1上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。

【0048】

このようにして、1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dh(h≠k)と走査電極SC1との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。

【0049】

以上の書込み動作を、第1の放電セル群において(3n−2)行目のセルに順次行う。

【0050】

第1の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。

【0051】

一方、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L7を印加する。ここでも、上述したランプ波形L2とランプ波形L5の関係と同様に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L7は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第3の放電セル群においては、第1の放電セル群3回目の初期化放電によって移動する電荷の量が第1の放電セル群および第2の放電セル群に比べて少ない。それにより、3回目の初期化放電後、第3の放電セル群には、第2の放電セル群より多くの壁電荷が保持される。さらに、第2の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L8を印加する。

【0052】

その後、上記同様の書込み動作を第3の放電セル群において(3n)行目の放電セル群に順次行う。ここで、書込み動作として第1の走査電極群(SC1,SC2,…,SC(n/6))に走査パルスPaが印加される期間には、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第2の放電セル群および第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第2の放電セル群および第3の放電セル群には第1の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第2の放電セル群および第3の放電セル群の壁電荷が減少しても、第2の放電セル群および第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0053】

さらに、書込み動作として第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaが印加される期間には、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第3の放電セル群には第2の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第3の放電セル群の壁電荷が減少しても、第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0054】

また、本実施の形態においては、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。すると、第2の放電セル群において3回目の微弱な初期化放電が起こる。これにより、第2の放電セル群において、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。但し、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L7は(−Vad+Vset2)より高い(−Vad+Vhiz)までしか下降しないため、第3の放電セル群にはまだ十分な量の壁電荷が保持される。

【0055】

さらに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に走査パルスPaを印加する直前に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L8を印加する。すると、第3の放電セル群において4回目の微弱な初期化放電が起こる。これにより、第3の放電セル群において、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の3相駆動動作時には、第1SFの初期化期間において第1の放電セル群に属する全ての放電セルの初期化動作(第1の放電セル群の全セル初期化動作)が行われ、第1SFの初期化期間および書込み期間において第2の放電セル群に属する全ての放電セルの初期化動作(第2の放電セル群の全セル初期化動作)が行われ、その後第1SFの初期化期間および書込み期間において第3の放電セル群に属する全ての放電セルの初期化動作(第3の放電セル群の全セル初期化動作)が行われる。

【0056】

第1SFの書込み期間の中間部(上記ランプ波形L6の印加後)では、維持電極SU1〜SUnを電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、n/6+1行目の走査電極SC(n/6+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/6+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/6+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC(n/6+1)との間および維持電極SU(n/6+1)と走査電極SC(n/6+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/6+1)上に正の壁電荷が蓄積され、維持電極SU(n/6+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。このようにして、n/6+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/6+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。以上の書込み動作を、第2の放電セル群において、n/6+1行目の放電セルから、n/2行目の放電セルに至るまで順次行う。

【0057】

また、第1SFの書込み期間の後半部(上記ランプ波形L8の印加後)では、維持電極SU1〜SUnを電位Veに保持し、走査電極SC1〜SC(n)を一旦電位(−Vad+Vscn)に保持する。次に、n/2+1行目の走査電極SC(n/2+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/2+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/2+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC2との間および維持電極SU(n/2+1)と走査電極SC(n/2+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/2+1)上に正の壁電荷が蓄積され、維持電極SU(n/2+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。

【0058】

このようにして、n/2+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/2+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。以上の書込み動作を、第3の放電セル群において、(n/2+1)行目の放電セルから(n)行目の放電セルに至るまで順次行い、書込み期間が終了する。

【0059】

続く維持期間では、維持電極SU1〜SUnを接地電位に戻し、走査電極SC1〜SCnに維持期間の最初の維持パルスPs(=Vsus)を印加する。このとき、書込み期間で書込み放電が発生した放電セルにおいては、走査電極SCiと維持電極SUiとの間の電圧は、維持パルスPs(=Vsus)に走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が加算された値となり、放電開始電圧を超える。それにより、走査電極SCiと維持電極SUiとの間で維持放電が起こり、放電セルが発光する。その結果、走査電極SCi上に負の壁電荷が蓄積され、維持電極SUi上に正の壁電荷が蓄積され、データ電極Dk上に正の壁電荷が蓄積される。

【0060】

書込み期間で書込み放電が発生しなかった放電セルでは維持放電は起こらず、初期化期間の終了時における壁電荷の状態が保持される。続いて、走査電極SC1〜SCnを接地電位に戻し、維持電極SU1〜SUnに維持パルスPsを印加する。すると、維持放電が起こった放電セルでは、維持電極SUiと走査電極SCiとの間の電圧が放電開始電圧を超えるので、再び維持電極SUiと走査電極SCiとの間で維持放電が起こり、維持電極SUi上に負の壁電荷が蓄積され、走査電極SCi上に正の壁電荷が蓄積される。

【0061】

以降同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加することにより、書込み期間において書込み放電が発生した放電セルでは維持放電が継続して行われる。維持パルスPsの印加後、維持電極SU1〜SUnおよびデータ電極D1〜Dmを接地電位に保持した状態で、走査電極SC1〜SCnにランプ波形L3を印加する。このランプ波形L3は、接地電位から正の電位Veraseに向かって緩やかに上昇する。これにより、維持放電が起こった放電セルにおいて、走査電極SCiと維持電極SUiとの間の電圧が放電開始電圧を超え、維持電極SUiと走査電極SCiとの間で微弱な消去放電が発生する。

【0062】

第2SFの初期化期間では、維持電極SU1〜SUnを電位Veに保持し、データ電極D1〜Dmを接地電位に保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))に接地電位から(−Vad+Vset4)に向かって緩やかに下降するランプ波形L4を印加する。すると、第1の放電セル群のうち前のサブフィールド(図4では、第1SF)の維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。それにより、第1の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0063】

第1の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては、放電が発生することはなく、前のサブフィールドの初期化期間の終了時における壁電荷の状態がそのままの状態よりやや低い値に保たれる。一方、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L9を印加する。その後、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。この場合、第2の放電セル群および第3の放電セル群のうち前のサブフィールドの維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。

【0064】

ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))に印加されるランプ波形L4は(−Vad+Vset4)まで下降するのに対して、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L9は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第2の放電セル群および第3の放電セル群においては、第1の放電セル群に比べて移動する電荷の量が少ない。そのため、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第1の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。

【0065】

なお、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては放電が発生しない。

【0066】

続く第2SFの書込み期間の前半部では、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の前半部と同様の駆動波形を印加する。

【0067】

第1の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。

【0068】

一方、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L11を印加する。その後、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に印加されるランプ波形L10は(−Vad+Vset4)まで下降するのに対して、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L11は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第3の放電セル群においては、第1の放電セル群および第2の放電セル群に比べて移動する電荷の量が少ない。そのため、第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第1の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。

【0069】

さらに、第2の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L12を印加する。

【0070】

ここで、第2SFの書込み期間において第1の走査電極群(SC1,SC2,…,SC(n/6))に走査パルスPaが印加される期間には、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第2の放電セル群および第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第2SFの初期化期間終了時に多くの壁電荷が保持されている。従って、上記の期間においてそれらの放電セルの壁電荷が減少しても、それらの放電セルにはまだ十分な量の壁電荷が保持されている。

【0071】

さらに、第2SFの書込み期間において第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaが印加される期間には、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第3の放電セル群には第2の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第3の放電セル群の壁電荷が減少しても、第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0072】

また、本実施の形態においては、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。すると、第2の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて微弱な初期化放電が起こる。これにより、第2の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。但し、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L11は(−Vad+Vset4)より高い(−Vad+Vhiz)までしか下降しないため、第3の放電セル群にはまだ十分な量の壁電荷が保持される。

【0073】

さらに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に走査パルスPaを印加する直前に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L12を印加する。すると、第3の放電セル群において4回目の微弱な初期化放電が起こる。これにより、第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の3相駆動動作時には、第2SFの初期化期間において第1の放電セル群に対する選択初期化動作が行われ、第2SFの初期化期間および書込み期間において第2の放電セル群および第3の放電セル群に対する選択初期化動作が行われる。なお、選択初期化動作とは、直前のサブフィールドで維持放電が起こった放電セルで選択的に初期化放電を発生させる動作を言う。

【0074】

第2SFの書込み期間の中間部以降(上記ランプ波形L10の印加後)では、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の中間部以降と同様の駆動波形を印加する。

【0075】

第2SFの維持期間には、第1SFの維持期間と同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加する。それにより、書込み期間において書込み放電が発生した放電セルで維持放電が行われる。

【0076】

また、第3SF以降のサブフィールドでは、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第2SFと同様の駆動波形を印加する。

【0077】

(b)2相駆動動作時の駆動波形

次に、走査電極駆動回路53の2相駆動動作時に各電極に印加される駆動波形について説明する。なお、図5に示すランプ波形L1〜L4は、図4のランプ波形L1〜L4と同様である。第1SFの初期化期間の前半部では、データ電極D1〜Dmの電位をVdaに保持し、維持電極SU1〜SUnを接地電位に保持し、走査電極SC1〜SCnにランプ波形L1を印加する。それにより、全ての放電セルにおいて1回目の微弱な初期化放電が起こり、走査電極SC1〜SCn上に負の壁電荷が蓄えられるとともに維持電極SU1〜SUn上およびデータ電極D1〜Dm上に正の壁電荷が蓄えられる。

【0078】

続く初期化期間の後半部では、データ電極D1〜Dmを接地電位に保持し、維持電極SU1〜SUnを正の電位Veに保持し、第4の走査電極群(SC1,SC2,…SC(n/3))にVsusから(−Vad+Vset2)に向かって緩やかに下降するランプ波形L2を印加する。すると、第1の放電セル群において2回目の微弱な初期化放電が起こる。これにより、第1の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。一方、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L5を印加する。これにより、第2の放電セル群において2回目の微弱な初期化放電が起こる。その後、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。

【0079】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に印加されるランプ波形L2は(−Vad+Vset2)まで下降するのに対して、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に印加されるランプ波形L5は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第5の放電セル群においては2回目の初期化放電によって移動する電荷の量が第4の放電セル群に比べて少ない。それにより、2回目の初期化放電後、第5の放電セル群には、第4の放電セル群より多くの壁電荷が保持される。

【0080】

第1SFの書込み期間の前半部では、図4で説明したように、第4の放電セル群において1行目の放電セルからn/3行目の放電セルに至るまで書込み動作を順次行う。

【0081】

第4の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。

【0082】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に走査パルスPaが印加される期間には、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には走査パルスPaが印加されない。この期間において、第5の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第5の放電セル群には第4の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第5の放電セル群の壁電荷が減少しても、第5の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0083】

また、本実施の形態においては、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に走査パルスPaを印加する直前に、走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。すると、第5の放電セル群において3回目の微弱な初期化放電が起こる。これにより、第5の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の2相駆動動作時には、第1SFの初期化期間において第1の放電セル群に属する全ての放電セルの初期化動作(第4の放電セル群の全セル初期化動作)が行われ、第1SFの初期化期間および書込み期間において第5の放電セル群に属する全ての放電セルの初期化動作(第5の放電セル群の全セル初期化動作)が行われる。

【0084】

第1SFの書込み期間の後半部(上記ランプ波形L6の印加後)では、維持電極SU1〜SUnを再び電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、n/3+1行目の走査電極SC(n/3+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/3+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/3+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC(n/3+1)との間および維持電極SU(n/3+1)と走査電極SC(n/3+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/3+1)上に正の壁電荷が蓄積され、維持電極SU(n/3+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。このようにして、n/3+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/3+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。

【0085】

以上の書込み動作を、第5の放電セル群において、n/3+1行目の放電セルから(n)行目の放電セルに至るまで順次行い、書込み期間が終了する。

【0086】

続く維持期間では、図4で説明したように、走査電極SC1〜SCnおよび維持電極SU1〜SUnに交互に維持パルスPsを印加する。それにより、書込み期間において書込み放電が発生した放電セルにおいて維持放電が発生する。維持パルスPsの印加後、図4で説明したように、走査電極SC1〜SCnにランプ波形L3を印加する。これにより、維持放電が起こった放電セルにおいて、微弱な消去放電が発生する。その結果、走査電極SCiに負の壁電荷が蓄積され、維持電極SUiに正の壁電荷が蓄積される。このとき、データ電極Dk上には正の壁電荷が蓄積される。その後、走査電極SC1〜SCnを接地電位に戻し、維持期間における維持動作を終了する。

【0087】

第2SFの初期化期間では、維持電極SU1〜SUnを電位Veに保持し、データ電極D1〜Dmを接地電位に保持し、第4の走査電極群(SC1,SC2,…SC(n/3))に接地電位から(−Vad+Vset4)に向かって緩やかに下降するランプ波形L4を印加する。すると、第4の放電セル群のうち前のサブフィールド(図5では、第1SF)の維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。それにより、第4の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0088】

第4の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては、放電が発生することはなく、前のサブフィールドの初期化期間の終了時における壁電荷の状態がそのまま保たれる。一方、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L9を印加する。その後、第2の走査電極群を一旦電位(−Vad+Vhiz)に保持する。この場合、第5の放電セル群のうち前のサブフィールドの維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。

【0089】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に印加されるランプ波形L4は(−Vad+Vset4)まで下降するのに対して、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に印加されるランプ波形L9は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第5の放電セル群においては、第4の放電セル群に比べて移動する電荷の量が少ない。そのため、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第4の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。なお、第5の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては放電が発生しない。

【0090】

第2SFの書込み期間の前半部では、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の前半部と同様の駆動波形を印加する。

【0091】

第4の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。ここで、第2SFの書込み期間において第4の走査電極群(SC1,SC2,…SC(n/3))に走査パルスPaが印加される期間には、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には走査パルスPaが印加されない。この期間において、第5の放電セル群の壁電荷は減少する。しかしながら、上述したように、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第2SFの初期化期間終了時に多くの壁電荷が保持されている。従って、上記の期間においてそれらの放電セルの壁電荷が減少しても、それらの放電セルにはまだ十分な量の壁電荷が保持されている。

【0092】

また、本実施の形態においては、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に走査パルスPaを印加する直前に、走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。すると、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて微弱な初期化放電が起こる。これにより、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の2相駆動動作時には、第2SFの初期化期間において第4の放電セル群に対する選択初期化動作が行われ、第2SFの初期化期間および書込み期間において第5の放電セル群に対する選択初期化動作が行われる。なお、選択初期化動作とは、直前のサブフィールドで維持放電が起こった放電セルで選択的に初期化放電を発生させる動作をいう。

【0093】

第2SFの書込み期間の後半部では、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の後半部と同様の駆動波形を印加する。第2SFの維持期間には、第1SFの維持期間と同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加する。それにより、書込み期間において書込み放電が発生した放電セルで維持放電が行われる。また、第3SF以降のサブフィールドでは、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第2SFと同様の駆動波形を印加する。

【0094】

(1−4)走査電極駆動回路53の構成

図6は走査電極駆動回路53の構成を示す回路図である。

【0095】

走査電極駆動回路53は、第1の駆動回路DR1、第2の駆動回路DR2、第3の駆動回路DR3、直流電源200、回収回路300、比較回路400、ダイオードD10,D11およびnチャネル電界効果トランジスタ(以下、トランジスタと略記する)Q3〜Q9を含む。

【0096】

第1の駆動回路DR1は、複数の走査IC100を含む。各走査IC100は、ノードN1とノードN2との間に接続されるとともに、第1の走査電極群(SC1,SC2,…,SC(n/6))に属する走査電極SC1,SC2,…,SC(n/6)の各々に接続される。各走査IC100は、対応する走査電極SC1,SC2,…,SC(n/6)をノードN1およびノードN2に選択的に接続する。

【0097】

第1の駆動回路DR1には、制御信号S51A,S52Aが与えられる。制御信号S51A,S52Aの論理に応じて走査IC100の状態が切り替わる。走査IC100の詳細については後述する。第2の駆動回路DR2は、複数の走査IC110を含む。各走査IC110は、ノードN1とノードN2との間に接続されるとともに、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に属する走査電極SC(n/6+1),SC(n/6+2),…,SC(n/2)の各々に接続される。各走査IC110は、対応する走査電極SC(n/6+1),SC(n/6+2),…,SC(n/2)をノードN1およびノードN2に選択的に接続する。

【0098】

第2の駆動回路DR2には、制御信号S51B,S52Bが与えられる。制御信号S51B,S52Bの論理に応じて走査IC110の状態が切り替わる。走査IC110の詳細については後述する。

【0099】

第3の駆動回路DR3は、複数の走査IC120を含む。各走査IC120は、ノードN1とノードN2との間に接続されるとともに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に属する走査電極SC(n/2+1),SC(n/2+2),…SC(n)の各々に接続される。各走査IC120は、対応する走査電極(SC(n/2+1),SC(n/2+2),…SC(n))をノードN1およびノードN2に選択的に接続する。第3の駆動回路DR3には、制御信号S51C,S52Cが与えられる。制御信号S51C,S52Cの論理に応じて走査IC120の状態が切り替わる。走査IC120の詳細については後述する。

【0100】

電圧Vscnを受ける電源端子V10は、ダイオードD10を介してノードN3に接続される。直流電源200は、ノードN1とノードN3との間に接続される。この直流電源200は、電解コンデンサからなり、電圧Vscnを保持するフローティング電源として働く。ノードN2とノードN3との間には、保護抵抗R1が接続される。以下、ノードN1の電位をVFGNDとし、ノードN3の電位をVscnFとする。ノードN3の電位VscnFは、ノードN1の電位VFGNDに電圧Vscnを加算した値を有する。すなわち、VscnF=VFGND+Vscnとなる。

【0101】

トランジスタQ3は、電圧(Vset+(Vsus−Vscn))を受ける電源端子V11とノードN4との間に接続され、ゲートには制御信号S3が与えられる。トランジスタQ4は、ノードN1とノードN4との間に接続され、ゲートには制御信号S4が与えられる。トランジスタQ5は、ノードN1と負の電圧(−Vad)を受ける電源端子V12との間に接続され、ゲートには制御信号S5が与えられる。制御信号S4は制御信号S5の反転信号である。また、トランジスタQ3,Q5にはゲート抵抗RGおよびコンデンサCGが接続される。なお、トランジスタQ6にもゲート抵抗およびコンデンサが接続されるが、図示は省略する。

【0102】

トランジスタQ6は、電圧Vsusを受ける電源端子V13とノードN5との間に接続される。トランジスタQ6のベースには制御信号S6が与えられる。トランジスタQ7は、ノードN4とノードN5との間に接続される。トランジスタQ7のゲートには制御信号S7が与えられる。トランジスタQ8は、ノードN4と接地端子との間に接続され、ベースには制御信号S8が与えられる。電圧Veraseを受ける電源端子V14とノードN4との間に、トランジスタQ9およびダイオードD11が接続される。トランジスタQ9のベースには制御信号S9が与えられる。

【0103】

回収回路300は、ノードN4とノードN5との間に接続される。回収回路300は、上記の維持期間において、複数の放電セルから電荷を回収して蓄積するとともに、蓄積した電荷を再び複数に放電セルに与える。比較回路400は、電源端子V12とノードN1との間に接続される。比較回路400の詳細については後述する。

【0104】

(1−5)走査ICの詳細

次に、走査IC100,110,120の詳細について説明する。上記のように、走査IC100の状態は制御信号S51A,S52Aの論理に応じて切り替わり、走査IC110の状態は制御信号S51B,S52Bの論理に応じて切り替わり、走査IC120の状態は制御信号S51C,S52Cの論理に応じて切り替わる。

【0105】

図7は、制御信号S51A,S52Aの論理と走査IC100の状態との対応関係を示す図である。制御信号S51B,S52Bの論理と走査IC110の状態との対応関係および制御信号S51C,S52Cの論理と走査IC120の状態との対応関係は、制御信号S51A,S52Aの論理と走査IC100の状態との対応関係と同様である。図7に示すように、制御信号S51A,S52Aがともにハイレベル(Hi)である場合、各走査IC100は“All−Hi”(オールハイ)の状態になる。“All−Hi”の状態では、全ての走査IC100が、対応する走査電極をノードN2に接続する。すなわち、走査電極SC1,SC2,…,SC(n/6)の電位がノードN2およびノードN3の電位と等しくなる。

【0106】

制御信号S51Aがハイレベルであり、制御信号S52Aがローレベル(Lo)である場合、各走査IC100が“All−Lo”(オールロー)の状態になる。“All−Lo”の状態では、全ての走査IC100が、対応する走査電極をノードN1に接続する。すなわち、走査電極SC1,SC2,…,SC(n/6)の電位がノードN1の電位と等しくなる。制御信号S51Aがローレベルであり、制御信号S52Aがハイレベルである場合、各走査IC100が“DATA”(データ)の状態になる。“DATA”の状態では、各走査IC100が順に対応する走査電極をノードN1に接続する。この場合、書込み期間において、走査電極(SC1,SC2,…,SC(n/6)に順に書込みパルスが印加される。制御信号S51A,S52Aがともにローレベルである場合、各走査IC100が“HiZ”(ハイインピーダンス)の状態になる。“HiZ”の状態では、全ての走査IC100が、対応する走査電極をノードN1およびノードN2から遮断する。

【0107】

(1−6)走査電極駆動回路の動作

次に、走査電極駆動回路53の動作について説明する。2相駆動動作時の走査電極駆動回路53の動作は、3相駆動動作時の走査電極駆動回路53の動作に基づいて容易に説明できるので、ここでは、まず3相駆動動作時の走査電極駆動回路53の動作を説明する。

【0108】

(1−6−1)3相駆動動作時の走査電極駆動回路の動作

図8〜図11は、3相駆動動作時の走査電極駆動回路53の動作について説明するための各制御信号のタイミング図である。図8は第1SFの初期化期間における各制御信号のタイミング図であり、図9は第1SFの書込み期間における各制御信号のタイミング図である。また、図10は第2SFの初期化期間における各制御信号のタイミング図であり、図11は第2SFの書込み期間における各制御信号のタイミング図である。なお、図8〜図11には、制御信号S3〜S8,S51A,S52A,S51B,S52B,S51C,S52Cおよび走査IC100,走査IC110,走査IC120(図中においてIC100,IC110およびIC120と略記)の状態が示される。また、図8〜図11の最上段には、実線で走査電極SC1の電位の変化が示され、一点鎖線で走査電極SC2の電位の変化が示され、破線で走査電極SC3の電位の変化が示される。

【0109】

(1−6−1−1)第1SF

図8の第1SFにおける初期化期間の開始時点t0では、制御信号S51A,S51B,S51Cがハイレベルにあり、制御信号S52A,S52B,S52Cがローレベルにある。それにより、走査IC100,110,120がそれぞれ“All−Lo”の状態になっている。また、制御信号S3,S5,S6がローレベルにあり、制御信号S4,S7,S8がハイレベルにある。それにより、トランジスタQ3,Q5,Q6がオフし、トランジスタQ4,Q7,Q8がオンしている。

【0110】

従って、ノードN1は接地電位(0V)となっており、ノードN3の電位VscnFはVscnとなっている。また、走査IC100,110,120がそれぞれ“All−Lo”の状態であるので、走査電極SC1,SC2,SC3の電位は接地電位となっている。

【0111】

時点t1で、制御信号S52A,S52B,S52Cがハイレベルになる。それにより、走査IC100,110,120がそれぞれ“All−Hi”の状態になる。従って、走査電極SC1,SC2,SC3の電位がVscnに立ち上がる。

【0112】

時点t2で、制御信号S3がハイレベルになり、制御信号S7,S8がローレベルになる。それにより、トランジスタQ3がオンし、トランジスタQ7,Q8がオフする。それにより、トランジスタQ3に接続されたゲート抵抗RGおよびコンデンサCGにより構成されるRC積分回路により、ノードN1の電位VFGNDが(Vset+(Vsus−Vscn)まで緩やかに上昇する。また、ノードN3の電位VscnFが(Vsus+Vset)まで緩やかに上昇する。このとき、走査IC100,110,120がそれぞれ“All−Hi”の状態であるので、走査電極SC1,SC2,SC3の電位が(Vsus+Vset)まで緩やかに上昇する。

【0113】

時点t3で、制御信号S3がローレベルになり、制御信号S6,S7がハイレベルになる。それにより、トランジスタQ3がオフし、トランジスタQ6,Q7がオンする。その結果、ノードN1の電位VFGNDがVsusまで低下し、ノードN3の電位VscnFが(Vscn+Vsus)まで低下する。このとき、走査IC100,110,120がそれぞれ“All−Hi”の状態であるので、走査電極SC1,SC2,SC3の電位が(Vscn+Vsus)まで低下する。

【0114】

時点t4で、制御信号S52A,S52B,S52Cがローレベルになる。それにより、走査IC100,110,120がそれぞれ“All−Lo”の状態になる。このとき、ノードN1の電位VFGNDの電位はVsusとなっているので、走査電極SC1,SC2,SC3の電位がVsusまで低下する。

【0115】

時点t5で、制御信号S4,S6,S7がローレベルになり、制御信号S5,S8がハイレベルになる。それにより、トランジスタQ4,Q6,Q7がオフし、トランジスタQ5,Q8がオンする。その結果、トランジスタQ5に接続されたゲート抵抗RGおよびコンデンサCGにより構成されるRC積分回路により、ノードN1の電位VFGNDが(−Vad)に向かって緩やかに低下する。このとき、走査IC100,110,120がそれぞれ“All−Lo”の状態にあるので。走査電極SC1,SC2,SC3の電位が(−Vad)に向かって緩やかに低下する。

【0116】

走査電極SC1,SC2,SC3の電位(ノードN1の電位)が(−Vad+Vhiz)になる時点t5aで、制御信号S51B,S51Cがローレベルになる。それにより、走査IC110,120が“HiZ”の状態になる。その結果、走査電極SC2,SC3の電位が(−Vad+Vhiz)に維持される。なお、時点t5aにおける制御信号S51B,S51Cの切り替えは、図6の比較回路400によって行われる。後述の時点t6,t11,t12,t15,t16,t22,t23,t28,t29,t32,t33においても、比較回路400によって制御信号S52A,S51B,S52B,S51C,S52Cの切り替えが行われる。比較回路400の詳細については後述する。

【0117】

走査電極SC1の電位(ノードN1の電位)が(−Vad+Vset2)になる時点t6で、制御信号S51Aがローレベルになり、制御信号S52Aがハイレベルになる。それにより、走査IC100が“DATA”の状態になる。また、制御信号S51B,S52B,S51C,S52Cがハイレベルになり、走査IC110,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC2,SC3の電位が(−Vad+Vscn)まで上昇する。

【0118】

図9に示すように、第1SFにおける書込み期間の前半部(時点t7〜t10の期間)には、走査IC100が“DATA”の状態に維持される。それにより、走査電極SC1,SC4,…,SCn−2が順にノードN1に接続される。このとき、ノードN1の電位VFGNDは(−Vad)になっている。そのため、走査電極SC1,SC4,…,SCn−2の電位が順に(−Vad)まで低下する。図10においては、時点t8〜t9の期間に走査電極SC1の電位が(−Vad)に低下する。

【0119】

一方、走査IC110,120は“All−Hi”の状態に維持される。それにより、走査電極SC2,SC3の電位は(−Vad+Vscn)に維持される。時点t10で、制御信号S51Aがハイレベルになり、制御信号S52A,S52B,S52Cがローレベルになる。それにより、走査IC100,110,120がそれぞれ“All−Lo”の状態になる。従って、走査電極SC1,SC2,SC3の電位が(−Vad)に向かって緩やかに低下する。

【0120】

走査電極SC1,SC2,SC3の電位(ノードN1の電位)が(−Vad+Vhiz)になる時点t11で、制御信号S51Cがローレベルになる。それにより、走査IC120が“HiZ”の状態になる。その結果、走査電極SC3の電位が(−Vad+Vhiz)に維持される。走査電極SC1,SC2の電位(ノードN1の電位)が(−Vad+Vset2)になる時点t12で、制御信号S51Bがローレベルになり、制御信号S52Bがハイレベルになる。それにより、走査IC110が“DATA”の状態になる。また、制御信号S51A,S52A,S51C,S52Cがハイレベルになり、走査IC100,120が“All−Hi”の状態になる。このとき、ノードN3の電位VscnFは(−Vad+Vscn)になっている。従って、走査電極SC1,SC2,SC3の電位が(−Vad+Vscn)まで上昇する。

【0121】

図9に示すように、第1SFにおける書込み期間の中半部(時点t12〜t15の期間)には、走査IC110が“DATA”の状態に維持される。それにより、走査電極SC2,SC5,…,SCn−1が順にノードN1に接続される。このとき、ノードN1の電位VFGNDは(−Vad)になっている。そのため、走査電極SC2,SC5,…,SCn−1の電位が順に(−Vad)まで低下する。図9においては、時点t13〜t14の期間に走査電極SC2の電位が(−Vad)に低下する。

【0122】

一方、走査IC100,120は“All−Hi”の状態に維持される。それにより、走査電極SC1,SC3の電位は(−Vad+Vscn)に維持される。

【0123】

時点t15で、制御信号S51Bがハイレベルになり、制御信号S52A,S52B,S52Cがローレベルになる。それにより、走査IC100,110,120がそれぞれ“All−Lo”の状態になる。従って、走査電極SC1,SC2,SC3の電位が(−Vad)に向かって緩やかに低下する。

【0124】

走査電極SC1,SC2,SC3の電位(ノードN1の電位)が(−Vad+Vset2)になる時点t16で、制御信号S51Cがローレベルになり、制御信号S52Cがハイレベルになる。それによって、走査IC120が“DATA”の状態になる。また、制御信号S51A,S52A,S51B,S52Bがハイレベルになり、走査IC100,110が“All−Hi”の状態になる。このとき、ノードN3の電位VscnFは(−Vad+Vscn)になっている。従って、走査電極SC1,SC2,SC3の電位が(−Vad+Vscn)まで上昇する。

【0125】

図9に示すように、第1SFにおける書込み期間の後半部(時点t16〜t19の期間)には、走査IC120が“DATA”の状態に維持される。それにより、走査電極SC3,SC6,…,SCnが順にノードN1に接続される。このとき、ノードN1の電位VFGNDは(−Vad)になっている。そのため、走査電極SC3,SC6,…,SCnの電位が順に(−Vad)まで低下する。図9においては、時点t17〜t18の期間に走査電極SC3の電位が(−Vad)に低下する。

【0126】

一方、走査IC100,110は“All−Hi”の状態に維持される。それにより、走査電極SC1,SC2の電位は(−Vad+Vscn)に維持される。

【0127】

(1−6−1−2)第2SF以降のサブフィールド

図10は、第2SFの初期化期間における各制御信号のタイミング図である。図10に示すように、第2SFの初期化期間の開始時点t20では、制御信号S51A,S51B,S51Cがハイレベルにあり、制御信号S52A,S52B,S52Cがローレベルにある。それにより、走査IC100,110,120がそれぞれ“All−Lo”の状態になっている。また、制御信号S3,S5,S6がローレベルにあり、制御信号S4,S7,S8がハイレベルにある。それにより、トランジスタQ3,Q5,Q6がオフし、トランジスタQ4,Q7,Q8がオンしている。従ってノードN1の電位VFGNDは接地電位となっており、ノードN3の電位VscnFはVscnとなっている。また、走査IC100,110,120がそれぞれ“All−Lo”の状態であるので、走査電極SC1,SC2,SC3の電位は接地電位となっている。

【0128】

時点t21で制御信号S4,S7がローレベルになり、制御信号S5がハイレベルになる。それにより、トランジスタQ4,Q7がオフになり、トランジスタQ5がオンになる。その結果、トランジスタQ5に接続されたゲート抵抗RGおよびコンデンサCGにより構成されるRC積分回路により、ノードN1の電位VFGNDが(−Vad)に向かって緩やかに低下する。このとき、走査IC100,110,120がそれぞれ“All−Lo”の状態であるので、走査電極SC1,SC2,SC3の電位が(−Vad)に向かって緩やかに低下する。

【0129】

走査電極SC1,SC2,SC3の電位(ノードN1の電位)が(−Vad+Vhiz)になる時点t22で、制御信号S51B,S51Cがローレベルになる。それにより、走査IC110,120が“HiZ”の状態になる。その結果、走査電極SC2,SC3の電位が(−Vad+Vhiz)に維持される。

【0130】

走査電極SC1の電位(ノードN1の電位)が(−Vad+Vset4)になる時点t23で、制御信号S51Aがローレベルになり、制御信号S52Aがハイレベルになる。それにより、走査IC100が“DATA”の状態になる。また、制御信号S51B,S52B,S51C,S52Cがハイレベルになり、走査IC110,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC2,SC3の電位が(−Vad+Vscn)まで上昇する。

【0131】

次に、図11は第2SFの書込み期間における各制御信号のタイミング図である。図11に示すように、第2SFの書込み期間には、時点t24〜t37の期間において、各制御信号が図9の時点t7〜t19の期間と同様に変化する。なお、図11においては、時点t25〜t26の期間に走査電極SC1の電位が(−Vad)に低下する。

【0132】

走査電極SC3の電位(ノードN1の電位)が(−Vad+Vhiz)になる時点t28で、制御信号S51Cがローレベルになる。それにより、走査IC120が“HiZ”の状態になる。その結果、走査電極SC3の電位が(−Vad+Vhiz)に維持される。走査電極SC1,SC2の電位(ノードN1の電位)が(−Vad+Vset4)になる時点t29で、制御信号S52Aがハイレベルになる。それにより、走査IC100が“All−Hi”の状態になる。また、制御信号S51Bがローレベルになり、制御信号S52Bがハイレベルになる。それにより、走査IC110が“DATA”の状態になる。さらに、制御信号S51C,S52Cがハイレベルになる。それにより、走査IC120が“All− Hi”の状態になる。このとき、ノードN3の電位VscnFは(−Vad+Vscn)になっている。従って、走査電極SC1,SC2,SC3の電位が(−Vad+Vscn)まで上昇する。

【0133】

時点t29〜t36の期間には、各制御信号が図9の時点t12〜t19の期間と同様に変化する。なお、図11においては、時点t30〜t31の期間に走査電極SC2の電位が(−Vad)に低下し、時点t34〜t35の期間に走査電極SC3の電位が(−Vad)に低下する。第3SF以降のサブフィールドでは、各制御信号が第2SFと同様に変化する。

【0134】

(1−6−2)2相駆動動作時の走査電極駆動回路の動作

次に、2相駆動動作時の走査電極駆動回路53の動作について説明する。

【0135】

2相駆動動作時は、(1−4)で説明した図6の走査電極駆動回路53について、第1,第2および第3の駆動回路DR1,DR2およびDR3の変わりに、図12のように第4の駆動回路DR4および第5の駆動回路DR5を用いる。その他構成は図6の走査電極駆動回路53と変わりはない。

【0136】

第4の駆動回路DR4は、複数の走査IC130を含む。各走査IC130は、ノードN1とノードN2との間に接続されるとともに、第4の走査電極群(SC1,SC2,…SC(n/3))に属する走査電極SC1,SC2,…SC(n/3)の各々に接続される。各走査IC130は、対応する走査電極SC1,SC2,…SC(n/3)をノードN1およびノードN2に選択的に接続する。第4の駆動回路DR4には、制御信号S51D,S52Dが与えられる。制御信号S51D,S52Dの論理に応じて走査IC130の状態が切り替わる。走査IC130の詳細については、(1−5)で説明したIC100,110,120と同様である。

【0137】

第5の駆動回路DR5は、複数の走査IC140を含む。各走査IC140は、ノードN1とノードN2との間に接続されるとともに、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に属する走査電極SC(n/3+1),SC(n/3+2),…SC(n)の各々に接続される。各走査IC140は、対応する走査電極SC(n/3+1),SC(n/3+2),…SC(n)をノードN1およびノードN2に選択的に接続する。第5の駆動回路DR5には、制御信号S51E,S52Eが与えられる。制御信号S51E,S52Eの論理に応じて走査IC140の状態が切り替わる。走査IC140の詳細については、(1−5)で説明したIC100,110,120と同様である。

【0138】

図13、図14は、2相駆動動作時の2相駆動動作時の走査電極駆動回路53の動作について説明するための各制御信号のタイミング図である。図13は、第1SFの書込み期間における各制御信号のタイミング図であり、図14は第2SFの書込み期間における各制御信号のタイミング図である。図13,14には、制御信号S3〜S8,S51D,S52D,S51E,S52Eおよび走査IC130、走査IC140(図中ではIC130およびIC140と略記)の状態が示される。基本的には、IC130の動作が図8のIC100と同様の、IC140の動作が図8のIC110と同様の動作を行う。図13、図14のタイミング図が図8〜図11のタイミング図と異なるのは以下の点である。

【0139】

図13に示すように、走査電極駆動回路53の2相駆動動作時の動作は、S52Dがt12〜16の期間でハイレベルになり、IC130が“All−Hi”の状態になる。また、S51Eがt12〜t19の期間でローレベルとなり、S52Eがt12〜t19の間でハイレベルとなるため、IC140がt12〜19の期間で“DATA”の状態になる。

【0140】

図14に示すように、走査電極駆動回路53の2相駆動動作時の動作は、S52Dがt29〜t36の期間でハイレベルになり、IC130が“All−Hi”の状態になる。また、S51Eがt29〜t36の期間でローレベルとなり、S52Eがt29〜t36の期間でハイレベルとなるため、IC140がt29〜t36の期間で“DATA”の状態になる。

【0141】

(1−7)比較回路

(1−7−1)構成

次に、比較回路400の詳細について説明する。図15は、比較回路400およびその周辺部分の構成を具体的に示す回路図である。図15に示すように、比較回路400は、コンパレータCN1,CN2、ANDゲート回路AG1,AG2、電源V21〜V24、スイッチSW1〜SW3およびセレクタ401を含む。

【0142】

コンパレータCN1の負側の入力端子はノードN1に接続される。コンパレータCN1の正側の入力端子はノードN11に接続される。ノードN11と電源端子V12との間に、電源V21,V22,V23がそれぞれスイッチ回路SW1,SW2,SW3を介して並列に接続される。電源V21は電圧Vset2を保持し、電源V23は電圧Vset4を保持する。なお、Vset2は例えば6Vであり、Vset4は例えば10Vである。コンパレータCN1の出力端子は、ANDゲート回路AG1の一方の入力端子に接続される。ANDゲート回路AG1の他方の入力端子には、制御信号S21が与えられる。

【0143】

ANDゲート回路AG1の出力端子は第1の駆動回路DR1および第2の駆動回路DR2に接続される。特定のタイミングにおいて、ANDゲート回路AG1からの出力信号が制御信号S52Aとして第1の駆動回路DR1に与えられ、制御信号S52Bとして第2の駆動回路DR2に与えられる。

【0144】

コンパレータCN2の正側の入力端子はノードN1に接続される。コンパレータCN2の負側の入力端子は、電源V24を介して電源端子V12に接続される。電源V24は電圧Vhizを保持する。それにより、コンパレータCN2の負側の入力端子の電位は(−Vad+Vhiz)に保持される。なお、Vhizは例えば70Vである。コンパレータCN2の出力端子は、ANDゲート回路AG2の一方の入力端子に接続され、コンパレータCN3の出力端子は、ANDゲート回路AG3の一方の入力端子に接続される。ANDゲート回路AG2の他方の入力端子には、制御信号S22が与えられ、ANDゲート回路AG3の他方の入力端子には、制御信号S24が与えられる。

【0145】

ANDゲート回路AG2の出力端子はセレクタ401の一方の入力端子に接続される。セレクタ401の他方の入力端子には制御信号S23が与えられる。セレクタ401の出力端子は第2の駆動回路DR2に接続される。特定のタイミングにおいて、ANDゲート回路AG2からの出力信号および制御信号S23の一方がセレクタ401によって選択的に制御信号S51Bとして第2の駆動回路DR2に与えられる。

【0146】

また、ANDゲート回路AG3の出力端子はセレクタ402の一方の入力端子に接続される。セレクタ402の他方の入力端子には制御信号S25が与えられる。セレクタ402の出力端子は第3の駆動回路DR3に接続される。特定のタイミングにおいて、ANDゲート回路AG3からの出力信号および制御信号S25の一方がセレクタ402によって選択的に制御信号S51Cとして第2の駆動回路DR3に与えられる。

【0147】

なお、図15の例では、ノードN1と電源端子V12との間にnチャネル電界効果トランジスタ(以下、トランジスタと略記する)Q5aが接続されている。トランジスタQ5がオフした状態でトランジスタQ5aがオンすることにより、ノードN1の電位が瞬時に−Vadに下降する。

【0148】

(1−7−2)動作

次に、図15の比較回路400の動作について説明する。まず、図8の時点t5〜t6の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52B,S51C,S52Cとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW1がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset2)に維持される。また、制御信号S21,S22,S24がハイレベルに維持される。

【0149】

時点t5から時点t5aに至るまでの期間には、ノードN1の電位が(−Vad+Vhiz)よりも高い。そのため、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より高くなり、出力端子の電位がローレベルになる。従って、ANDゲート回路AG1の出力端子の電位がローレベルとなり、制御信号S52A,S52B,S52Cがローレベルになる。また、コンパレータCN2,CN3の負側の入力端子の電位が正側の入力端子の電位より低くなり、出力端子の電位がハイレベルになる。従って、ANDゲート回路AG2,AG3の出力端子の電位はハイレベルになる。セレクタ401は、ANDゲート回路AG2からの出力信号を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402は、ANDゲート回路AG3からの出力信号を制御信号S51Cとして第3の駆動回路DR3に与える。すなわち、制御信号S51B,S51Cがハイレベルになる。この場合、走査IC100,110,120が“All−Lo”の状態で維持され、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が緩やかに下降する。

【0150】

時点t5aでノードN1の電位が(−Vad+Vhiz)になると、コンパレータCN2,CN3の出力端子の電位がローレベルになる。それにより、ANDゲート回路AG2,AG3の出力端子の電位がローレベルになり、制御信号S51B,S51Cがローレベルになる。その結果、走査IC110,120が“Hiz”の状態になり、走査電極SC2,SC3の電位が(−Vad+Vhiz)に維持される。

【0151】

続いて、時点t6でノードN1の電位が(−Vad+Vset2)になると、コンパレータCN1の出力端子の電位がハイレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、セレクタ401がハイレベルの制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え,セレクタ402がハイレベルの制御信号S25をS51Cとして第3の駆動回路DR3に与える。そのため、走査IC100が“DATA”の状態になり、走査IC110,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0152】

次に、図9の時点t10〜t12の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52Bとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW1がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset2)に維持される。また、制御信号S21,S22,S24がハイレベルで維持される。また、セレクタ401は、制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402は、制御信号S25を制御信号S51Cとして第3の駆動回路DR3に与える。

【0153】

時点t10から時点t11に至るまでの期間には、ノードN1の電位が(−Vad+Vhiz)よりも高い。そのため、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より高くなり、出力端子の電位がローレベルになる。従って、ANDゲート回路AG1の出力端子の電位がローレベルとなり、制御信号S52A,S52B,S52Cがローレベルになる。また、コンパレータCN2,CN3の負側の入力端子の電位が正側の入力端子の電位より低くなり、出力端子の電位がハイレベルになる。従って、ANDゲート回路AG2,AG3の出力端子の電位はハイレベルになる。

【0154】

時点t11で、ノードN1の電位が(−Vad+Vhiz)になると、コンパレータCN3の出力端子の電位がローレベルになる。それにより、ANDゲート回路AG3の出力端子の電位がローレベルになり、制御信号S51Cがローレベルになる。その結果、走査IC120が“Hiz”の状態になり、走査電極SC3の電位が(−Vad+Vhiz)に維持される。

【0155】

続いて、時点t12でノードN1の電位が(−Vad+Vset2)になると、コンパレータCN1の出力端子の電位がハイレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、制御信号S23がローレベルになり、制御信号S51Bがローレベルになる。そして、セレクタ401がローレベルの制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402がハイレベルの制御信号S25をS51Cとして第3の駆動回路DR3に与える。そのため、走査IC110が“DATA”の状態になり、走査IC100,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0156】

次に、図9の時点t15〜t16の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52B,S51C,S52Cとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW1がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset2)に維持される。また、制御信号S21,S22,S24がハイレベルで維持される。また、セレクタ401は、制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402は制御信号S25を制御信号S51Cとして第3の駆動回路DR3に与える。

【0157】

時点t15から時点t16に至るまでの期間には、ノードN1の電位が(−Vad+Vset2)よりも高い。そのため、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より高くなり、出力端子の電位がローレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がローレベルになり、制御信号S52A,S52B,S52Cがローレベルになる。また、制御信号S23,S25がハイレベルに維持され、制御信号S51B,S51Cがハイレベルに維持される。この場合、走査IC100,110,120が“All−Lo”の状態で維持され、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が緩やかに下降する。

【0158】

時点t16でノードN1の電位が(−Vad+Vset2)になると、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より低くなる。それにより、コンパレータCN1の出力端子の電位がハイレベルになる。そのため、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、制御信号S25がローレベルになり、制御信号S51Cがローレベルになる。従って、走査IC100,110が“All−Hi”の状態になり、走査IC120が“DATA”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0159】

次に、図10の時点t21〜t23の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52B,S51C,S52Cとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW3がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset4)に維持される。また、制御信号S21,S22,S24がハイレベルに維持される。

【0160】

時点t21から時点t23に至るまでの期間には、図9の時点t5から時点t6に至るまでの期間と同様に走査回路400が動作する。

【0161】

時点t23でノードN1の電位が(−Vad+Vset4)になると、コンパレータCN1の出力端子の電位がハイレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、セレクタ401がハイレベルの制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402がハイレベルの制御信号S25を制御信号S51Cとして第3の駆動回路DR3に与える。従って、走査IC100が“DATA”の状態になり、走査IC110,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0162】

次に、図11の時点t27〜t29の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52B,S51C,S52Cとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW3がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset4)に維持される。また、制御信号S21,S22,S24がハイレベルで維持される。また、セレクタ401は、制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402は制御信号S25を制御信号S51Cとして第3の駆動回路DR3に与える。

【0163】

時点t27から時点t28に至るまでの期間には、ノードN1の電位が(−Vad+Vhiz)よりも高い。そのため、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より高くなり、出力端子の電位がローレベルになる。従って、ANDゲート回路AG1の出力端子の電位がローレベルとなり、制御信号S52A,S52B,S52Cがローレベルになる。また、コンパレータCN2,CN3の負側の入力端子の電位が正側の入力端子の電位より低くなり、出力端子の電位がハイレベルになる。従って、ANDゲート回路AG2,AG3の出力端子の電位はハイレベルになる。

【0164】

時点t28で、ノードN1の電位が(−Vad+Vhiz)になると、コンパレータCN3の出力端子の電位がローレベルになる。それにより、ANDゲート回路AG3の出力端子の電位がローレベルになり、制御信号S51Cがローレベルになる。その結果、走査IC120が“Hiz”の状態になり、走査電極SC3の電位が(−Vad+Vhiz)に維持される。

【0165】

続いて、時点t29でノードN1の電位が(−Vad+Vset4)になると、コンパレータCN1の出力端子の電位がハイレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、制御信号S23がローレベルになり、制御信号S51Bがローレベルになる。そして、セレクタ401がローレベルの制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402がハイレベルの制御信号S25をS51Cとして第3の駆動回路DR3に与える。そのため、走査IC110が“DATA”の状態になり、走査IC100,120が“All−Hi”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0166】

次に、図11の時点t32〜t33の期間における比較回路400の動作を説明する。この期間には、比較回路400からの出力信号が制御信号S52A,S51B,S52B,S51C,S52Cとして第1、第2および第3の駆動回路DR1,DR2,DR3に与えられる。なお、この期間においては、スイッチSW3がオンされ、コンパレータCN1の正側の入力端子の電位が(−Vad+Vset4)に維持される。また、制御信号S21,S22,S24がハイレベルで維持される。また、セレクタ401は、制御信号S23を制御信号S51Bとして第2の駆動回路DR2に与え、セレクタ402は制御信号S25を制御信号S51Cとして第3の駆動回路DR3に与える。

【0167】

時点t32から時点t33に至るまでの期間には、ノードN1の電位が(−Vad+Vset4)よりも高い。そのため、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より高くなり、出力端子の電位がローレベルになる。それにより、ANDゲート回路AG1の出力端子の電位がローレベルになり、制御信号S52A,S52B,S52Cがローレベルになる。また、制御信号S23,S25がハイレベルに維持され、制御信号S51B,S51Cがハイレベルに維持される。この場合、走査IC100,110,120が“All−Lo”の状態で維持され、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が緩やかに下降する。

【0168】

時点t33でノードN1の電位が(−Vad+Vset4)になると、コンパレータCN1の負側の入力端子の電位が正側の入力端子の電位より低くなる。それにより、コンパレータCN1の出力端子の電位がハイレベルになる。そのため、ANDゲート回路AG1の出力端子の電位がハイレベルになり、制御信号S52A,S52B,S52Cがハイレベルになる。また、制御信号S25がローレベルになり、制御信号S51Cがローレベルになる。

【0169】

従って、走査IC100,110が“All−Hi”の状態になり、走査IC120が“DATA”の状態になる。その結果、走査電極SC1,SC(n/6+1),SC(n/2+1)の電位が(−Vad+Vscn)に上昇する。

【0170】

(1−8)第1の実施の形態の効果

以上のように、本実施の形態においては、3相駆動動作および2相駆動動作が選択的に実行される。3相駆動動作においては、初期化期間における初期化放電時(第1SFにおいては2回目の微弱放電時)に、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を第1の走査電極群(SC1,SC2,…,SC(n/6))よりも高い電位(−Vad+Vhiz)に保持する。この場合、初期化放電によって第2および第3の放電セル群で移動する電荷の量が、第1の放電セル群で移動する電荷の量に比べて少なくなる。それにより、書込み期間の開始時点において、第2および第3の放電セル群に十分な量の電荷を蓄積することができる。

【0171】

従って、第2および第3の放電セル群の各放電セルに走査パルスPaが印加されるまでに、各放電セルに蓄積されている壁電荷が減少したとしても、第2および第3の放電セル群において壁電荷の減少による放電不良が発生することを防止することができる。

【0172】

また、書込み期間において第1の放電セル群に対する走査パルスPaの印加が終了した後に、第2の放電セル群の所定の放電セルにおいて微弱放電を発生させている。それにより、第2の放電セル群の各放電セルに走査パルスPaが印加される直前に、第2の放電セル群の各放電セルを書込み動作に適した状態にすることができる。その結果、第2の放電セル群の各放電セルにおいて壁電荷の減少による放電不良が発生することを確実に防止することができる。同様に、書込み期間において第2の放電セル群に対する走査パルスPaの印加が終了した後に、第3の放電セル群の所定の放電セルにおいて微弱放電を発生させるため、第3の放電セル群の各放電セルにおいて壁電荷の減少による放電不良が発生することを確実に防止することができる。

【0173】

一方、初期化期間の終了時に第2および第3の放電セル群に過剰に電荷が蓄積されていると、第2および第3の放電セル群における壁電圧が高い状態で維持され、書込み期間において第2および第3の放電セル群で誤放電が発生しやすくなる。具体的には、書込み期間の前半部に、第1の放電セル群における書込み放電のための書込みパルスがデータ電極D1,D2,…,Dmに印加されると、第2および第3の放電セル群で誤放電が発生する。

【0174】

そこで、本実施の形態では、初期化期間において第2および第3の放電セル群に適度に初期化放電を発生させる。それにより、第2および第3の放電セル群に過剰に電荷が残留することが防止される。従って、第1の放電セル群の書込み動作時に、第2および第3の放電セル群で誤放電が発生することが防止される。

【0175】

また、初期化期間終了後、書込み期間においても第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の電位を(−Vad+Vhiz)に保持したままであると、第2および第3の放電セル群が放電開始電圧で維持された状態で第1の放電セル群の書込み動作が行われる。その場合にも、第2および第3の放電セル群での誤放電が発生しやすくなる。

【0176】

そこで、本実施の形態では、初期化期間の終了時に、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の電位を(−Vad+Vhiz)から(−Vad+Vscn)に上昇させている。これにより、書込み期間において第2および第3の放電セル群で誤放電が発生することをより確実に防止することができる。

【0177】

以上の結果から、1相駆動では図16のように、Vset2電位を第3の放電セル群で放電不良が発生しないように設定することによって、第1の放電セル群に蓄積される電荷が過剰となり、第1の放電セル群で誤放電が発生してしまうのに対し、3相駆動を用いることによって図17のように、第3の放電セル群における放電不良を防止しつつ、第1の放電セル群における誤放電も同時に抑制することも可能となる。

【0178】

また一般に、初期化動作の終了から走査パルスの印加までに、壁電荷は対数関数的に減少する。つまり、放電不良を確実に防止するために必要となるVset2電圧が、書込み順に対して対数関数的に増加することとなる。それゆえ、走査ラインを1:1に分割する2相駆動では、第1の放電セル群のうち、書込み順が後半になるセルにおいて放電不良が発生するリスクを伴う。つまり、図17のように走査ラインを2:4:6に分割する3相駆動か、あるいは図18のように走査ラインを4:8に分割する2相駆動をパネル特性に応じて選択的に行うことによって、後半セルで書込み不良を確実に防止しつつ、前半セルでの誤放電を確実に防止し、パネルの動作性能を向上させることができる。

【産業上の利用可能性】

【0179】

本発明は、種々の画像を表示するプラズマディスプレイ表示装置、特に表示電極の本数が多く使用されて高解像度を表示可能にするディスプレイ装置に利用することができる。

【符号の説明】

【0180】

10 プラズマディスプレイパネル

52 データ電極駆動回路

53 走査電極駆動回路

54 維持電極駆動回路

55 タイミング発生回路

56 APL検出器

100,110,120,130,140 走査IC

300 回収回路

400 比較回路

CG コンデンサ

D1〜Dm,Dj データ電極

DR1 第1の駆動回路

DR2 第2の駆動回路

DR3 第3の駆動回路

DR4 第4の駆動回路

DR5 第5の駆動回路

L1〜L12,Ld ランプ波形

RG ゲート抵抗

N1〜N5,N11 ノード

Pa 走査パルス

Ps 維持パルス

Q3〜Q9 トランジスタ

SC1〜SCn,SCi 走査電極

SU1〜SUn,SUi 維持電極

【技術分野】

【0001】

本発明は、プラズマディスプレイパネルの駆動方法ならびにそれを用いたプラズマディスプレイ装置に関する。

【背景技術】

【0002】

プラズマディスプレイパネル(以下、「パネル」と略記する)として代表的な交流面放電型パネルは、対向配置された前面板と背面板との間に多数の放電セルを備える。

【0003】

前面板は、前面ガラス基板、複数の表示電極、誘電体層および保護層により構成される。各表示電極は、一対の走査電極および維持電極からなる。複数の表示電極は、前面ガラス基板上に互いに平行に形成され、それらの表示電極を覆うように誘電体層および保護層が形成されている。

【0004】

背面板は、背面ガラス基板、複数のデータ電極、誘電体層、複数の隔壁および蛍光体層により構成される。背面ガラス基板上に複数のデータ電極が平行に形成され、それらを覆うように誘電体層が形成されている。その誘電体層上にデータ電極と平行に複数の隔壁がそれぞれ形成され、誘電体層の表面と隔壁の側面とにR(赤)、G(緑)およびB(青)の蛍光体層が形成されている。

【0005】

そして、表示電極とデータ電極とが立体交差するように前面板と背面板とが対向配置されて密封され、内部の放電空間には放電ガスが封入されている。表示電極とデータ電極とが対向する部分に放電セルが形成される。

【0006】

このような構成を有するパネルにおいて、各放電セル内でガス放電により紫外線が発生し、その紫外線でR、GおよびBの蛍光体が励起されて発光する。それにより、カラー表示が行われる。

【0007】

パネルを駆動する方法としてはサブフィールド法が用いられている(例えば、特許文献1参照)。サブフィールド法では、1フィールド期間が複数のサブフィールドに分割され、それぞれのサブフィールドで各放電セルを発光または非発光させることにより階調表示が行われる。各サブフィールドは、初期化期間、書込み期間および維持期間を有する。

【0008】

初期化期間においては、各走査電極に初期化パルスが印加され、各放電セルで初期化放電が行われる。それにより、各放電セルにおいて、続く書込み動作のために必要な壁電荷が形成される。

【0009】

書込み期間では、走査電極に順次走査パルスを印加するとともに、データ電極には表示すべき画像信号に対応した書込みパルスを印加する。それにより、走査電極とデータ電極との間で選択的に書込み放電が発生し、選択的な壁電荷形成が行われる。

【0010】

続く維持期間では、表示させるべき輝度に応じた所定の回数の維持パルスを走査電極と維持電極との間に印加する。それにより、書込み放電による壁電荷形成が行われた放電セルで選択的に放電が起こり、その放電セルが発光する。

【0011】

複数の走査電極は走査電極駆動回路により駆動され、複数の維持電極は維持電極駆動回路により駆動され、複数のデータ電極はデータ電極駆動回路により駆動される。

【0012】

一方、書込み期間における走査電極への走査パルス電圧の印加は、各走査電極に対して順次に行われるため、特に高精細化されたパネルにおいては、走査電極数の増加によって書込みに費やす時間が長くなってしまう。そのため、書込み期間の最後の方に書込み動作がなされる放電セルでは、書込み期間の最初の方に書込み動作がなされる放電セルに比べて、壁電荷の消失量が多く、書込み放電が不安定になりやすい。そこで、書込み期間の最後の方に書込み動作がなされる放電セルに合わせて壁電荷の量を調整するように波形を設計すると、今度は書込み期間の最初の方で書込み動作が行われる放電セルにおいて壁電荷が過剰となるため、書込み放電が強くなり、壁電荷が隣接セルに移動してしまい、結果誤放電が発生するという問題が起こる。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2006−18298号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

ところで、上述したように、書込み期間においては、複数の走査電極に走査パルスが順次印加される。従って、複数の放電セルのうち走査パルスが印加される順番が遅い放電セルにおいては、初期化パルスが印加されてから走査パルスが印加されるまでの間の時間が長くなる。

【0015】

ここで、初期化放電によって放電セルに形成された壁電荷は、他の放電セルに書込み放電を発生させるためにデータ電極に印加される書込みパルスの影響を受けて徐々に減少する。この放電セルに形成された壁電荷は、走査パルスが印加される走査電極の順序に対して、対数関数的に減少する。そのため、走査パルスが印加される順番が遅い放電セルにおいては、その放電セルに走査パルスおよび書込みパルスが印加されるまでに壁電荷が減少し、書込み放電の放電不良が発生する場合がある。

【0016】

その書込み不良を防止するために、走査パルスが印加される順番が遅い放電セルで放電不良が発生しないように波形を設計すると、今度は走査パルスが印加される順番が早い放電セルに蓄積される壁電荷量が過剰となるため、書込み放電強度が強くなり、壁電荷が隣接セルに移動してしまい、誤放電が発生してしまう。

【0017】

本発明の目的は、書込み放電の放電不良と誤放電とを防止することができるプラズマディスプレイパネルの駆動装置および駆動方法ならびにそれを用いたプラズマディスプレイ装置を提供することである。

【課題を解決するための手段】

【0018】

これらの課題を解決するために本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、複数の第1、第2および第3の走査電極、複数の維持電極ならびに複数のデータ電極の交差部にそれぞれ放電セルを有するプラズマディスプレイパネルを、1フィールド期間を複数のサブフィールドに分けて駆動する駆動装置であって、複数の第1の走査電極を駆動する第1の回路と、複数の第2の走査電極を駆動する第2の回路と、複数の第3の走査電極を駆動する第3の回路とを備え、複数の第1、第2および第3の回路は、複数のサブフィールドのうち少なくとも1つのサブフィールドにおいて、パネル特性に応じて3相駆動動作を行い、第1の回路は、3相駆動動作時には、サブフィールドの初期化期間において第1の電位から第2の電位に下降する第1のランプ波形を複数の第1の走査電極に印加し、書込み期間において複数の第1の走査電極に順に走査パルスを印加し、第2の回路は、3相駆動動作時には、初期化期間において第1の電位から第2の電位よりも高い第3の電位に下降する第2のランプ波形を複数の第2の走査電極に印加し、書込み期間において複数の第2の走査電極を第3の電位よりも高い第4の電位に保持しつつ複数の第1の走査電極への走査パルスの印加後に複数の第2の走査電極に順に走査パルスを印加し、第3の回路は、3相駆動動作時には、初期化期間において第2のランプ波形を複数の第3の走査電極に印加し、書込み期間において複数の第3の走査電極を第4の電位に保持しつつ複数の第2の走査電極への走査パルスの印加後に複数の第3の走査電極に順に走査パルスを印加し、第3の回路が駆動する複数の第3の走査電極の数が最も多く、第2の回路が駆動する複数の第2の走査電極の数が次に多く、第1の回路が駆動する複数の第1の走査電極の数が最も少ないことを特徴とするものである。

【0019】

また本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、3相駆動動作時に第2の回路が、書込み期間において複数の第1の走査電極への走査パルスの印加後で、複数の第2の走査電極への走査パルスの印加前に、第4の電位以下の第5の電位へ下降する第3のランプ波形を複数の第2の走査電極に印加し、第3の回路は、3相駆動動作時には、書込み期間において複数の第1の走査電極への走査パルスの印加後で、複数の第2の走査電極への走査パルスの印加前に、第4の電位以下で第5の電位よりも高い第6の電位へ下降する第4のランプ波形を複数の第3の走査電極に印加するものであってもよい。

【0020】

また本発明のプラズマディスプレイパネルの駆動装置またはその駆動方法は、3相駆動動作時に第3の駆動回路が、書込み期間において複数の第2の走査電極への走査パルスの印加後で複数の第3の走査電極への走査パルスの印加前に第4の電位以下の第7の電位へ下降する第5のランプ波形を複数の第3の走査電極に印加するものであってもよい。

【0021】

本発明によれば、第1の走査電極に走査パルスが印加されている間に第2の走査電極上の放電セルの壁電荷が減少しても、第2の走査電極への走査パルスの印加時に第2の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができ、同様に第2の走査電極に走査パルスが印加されている間に第3の走査電極上の放電セルの壁電荷が減少しても、第3の走査電極への走査パルスの印加時に第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第2、第3の走査電極上の放電セルに放電不良や誤放電が発生することを防止することができる。

【発明の効果】

【0022】

この駆動装置においては、複数のサブフィールドのうち少なくとも1つのサブフィールドにおいて、第1、第2および第3の回路により3相駆動動作が行われる。3相駆動動作時には、初期化期間において、第1の回路により第1の電位から第2の電位に下降する第1のランプ波形が複数の第1の走査電極に印加される。それにより、第1の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。その結果、第1の走査電極上の放電セルにおける壁電荷の量が書込み動作に適した状態になる。また、初期化期間において、第2の回路により第1の電位から第3の電位に下降する第2のランプ波形が複数の第2の走査電極に印加される。それにより、第2の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。

【0023】

ここで、第1のランプ波形が第2の電位まで下降するのに対して、第2のランプ波形は第2の電位よりも高い第3の電位までしか下降しない。そのため、第2の走査電極上の放電セルで移動する電荷の量は、第1の走査電極上の放電セルで移動する電荷の量よりも少ない。それにより、初期化期間の終了時に、第2の走査電極上の放電セルには十分な量の壁電荷が残る。同様に、初期化期間において、第3の回路により第1の電位から第3の電位に下降する第2のランプ波形が複数の第3の走査電極に印加される。それにより、第3の走査電極上の放電セルに微弱な放電が発生し、その放電セルの壁電荷の量が減少する。そのため、初期化期間の終了時に、第3の走査電極上の放電セルには十分な量の壁電荷が残る。

【0024】

書込み期間においては、第1の回路により複数の第1の走査電極に順に走査パルスが印加される。それにより、第1の走査電極上の選択された放電セルにおいて書込み放電が発生する。また、複数の第1の走査電極への走査パルスの印加後に、第2の回路により複数の第2の走査電極に順に走査パルスが印加される。それにより、第2の走査電極上の選択された放電セルにおいて書込み放電が発生する。また、複数の第2の走査電極への走査パルスの印加後に、第3の回路により複数の第3の走査電極に順に走査パルスが印加される。それにより、第3の走査電極上の選択された放電セルにおいて書込み放電が発生する。

【0025】

上記のように、第2および第3の走査電極上の放電セルには、初期化期間の終了時に十分な量の電荷が残されている。従って、第1の走査電極に走査パルスが印加されている間に第2および第3の走査電極上の放電セルの壁電荷が減少しても、第2および第3の走査電極への走査パルスの印加時に第2および第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第2および第3の走査電極上の放電セルに放電不良が発生することを防止することができる。さらに、第2の走査電極に走査パルスが印加されている間に第3の走査電極上の壁電荷が減少しても、第3の走査電極への走査パルスの印加時に第3の走査電極上の放電セルにおける壁電荷の量を書込み動作に適した状態にすることができる。その結果、書込み期間において第3の走査電極上の放電セルに放電不良が発生することを防止することができる。

【0026】

また、壁電荷が減少しても第2および第3の走査電極上の放電セルに良好に書込み動作を発生させることが可能であるので、書込み期間において壁電荷の減少を防止するために第2および第3の走査電極を高い電位に保持する必要がない。それにより、プラズマディスプレイパネルの駆動コストを低減しつつ駆動性能を向上させることが可能になる。

【0027】

また、初期化期間において第2および第3の走査電極上の放電セルに適度に放電が発生することにより、初期化期間の終了時にそれらの放電セルに過剰に電荷が残ることが防止される。それにより、第1の走査電極に走査パルスが印加される際に第2および第3の走査電極上の放電セルで誤放電が発生することが防止される。

【0028】

また、書込み期間においては、走査パルスが印加される期間を除いて第2および第3の走査電極が第3の電位よりも高い第4の電位に保持される。この場合、第2および第3の走査電極上の放電セルにおける電荷の状態が安定する。それにより、第2および第3の走査電極上の放電セルで誤放電が発生することをより確実に防止することができる。

【図面の簡単な説明】

【0029】

【図1】本発明の一実施の形態であるプラズマディスプレイ装置におけるプラズマディスプレイパネルの一部を示す分解斜視図

【図2】同プラズマディスプレイパネルの電極配列図

【図3】同プラズマディスプレイ装置の回路ブロック図

【図4】同プラズマディスプレイ装置のサブフィールド構成における一駆動例である3相駆動波形図

【図5】同プラズマディスプレイ装置のサブフィールド構成における他の駆動例である2相駆動波形図

【図6】同プラズマディスプレイ装置の3相駆動時の走査電極駆動回路の構成を示す回路図

【図7】同プラズマディスプレイ装置の制御信号の論理と走査ICの状態との対応関係を示す図

【図8】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第1のタイミング図

【図9】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第2のタイミング図

【図10】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第3のタイミング図

【図11】同プラズマディスプレイ装置の走査電極駆動回路の3相駆動動作時にトランジスタに与えられる制御信号の第4のタイミング図

【図12】同プラズマディスプレイ装置の2相駆動時の走査電極駆動回路の構成を示す回路図

【図13】同プラズマディスプレイ装置の走査電極駆動回路の2相駆動動作時にトランジスタに与えられる制御信号の第1のタイミング図

【図14】同プラズマディスプレイ装置の走査電極駆動回路の2相駆動動作時にトランジスタに与えられる制御信号の第2のタイミング図

【図15】同プラズマディスプレイ装置の比較回路およびその周辺部分の構成を示す図

【図16】同プラズマディスプレイ装置の1相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【図17】同プラズマディスプレイ装置の3相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【図18】同プラズマディスプレイ装置の2相駆動動作時におけるVset2電位の上下限と走査ラインの関係を示す図

【発明を実施するための最良の形態】

【0030】

以下、本発明の実施の形態に係るプラズマディスプレイパネルの駆動装置、駆動方法およびプラズマディスプレイ装置について、図面を用いて詳細に説明する。

【0031】

(1)第1の実施の形態

(1−1)パネルの構成

図1は、本発明の第1の実施の形態に係るプラズマディスプレイ装置におけるプラズマディスプレイパネルの一部を示す分解斜視図である。プラズマディスプレイパネル(以下、パネルと略記する)10は、互いに対向配置されたガラス製の前面基板21および背面基板31を備える。前面基板21および背面基板31の間に放電空間が形成される。前面基板21上には複数対の走査電極22および維持電極23が互いに平行に形成されている。各対の走査電極22および維持電極23が表示電極を構成する。走査電極22および維持電極23を覆うように誘電体層24が形成され、誘電体層24上には保護層25が形成されている。

【0032】

背面基板31上には絶縁体層33で覆われた複数のデータ電極32が設けられ、絶縁体層33上に井桁状の隔壁34が設けられている。また、絶縁体層33の表面および隔壁34の側面に蛍光体層35が設けられている。そして、複数対の走査電極22および維持電極23と複数のデータ電極32とが垂直に交差するように前面基板21と背面基板31とが対向配置され、前面基板21と背面基板31との間に放電空間が形成されている。放電空間には、放電ガスとして、例えばネオンとキセノンとの混合ガスが封入されている。なお、パネルの構造は上述したものに限られず、例えばストライプ状の隔壁を備えた構造を用いてもよい。

【0033】

図2は本発明の第1の実施の形態におけるパネルの電極配列図である。行方向に沿ってn本の走査電極SC1〜SCn(図1の走査電極22)およびn本の維持電極SU1〜SUn(図1の維持電極23)が配列され、列方向に沿ってm本のデータ電極D1〜Dm(図1のデータ電極32)が配列されている。nは偶数であり、mは2以上の自然数である。そして、1対の走査電極SCi(i=1〜n)および維持電極SUi(i=1〜n)と1つのデータ電極Dj(j=1〜m)とが交差した部分に放電セルDCが形成されている。それにより、放電空間内にm×n個の放電セルが形成されている。

【0034】

(1−2)プラズマディスプレイ装置の構成

図3は本発明の第1の実施の形態に係るプラズマディスプレイ装置の回路ブロック図である。このプラズマディスプレイ装置は、パネル10、画像信号処理回路51、データ電極駆動回路52、走査電極駆動回路53、維持電極駆動回路54、タイミング発生回路55、APL検出器56および電源回路(図示せず)を備える。画像信号処理回路51は、画像信号sigをパネル10の画素数に応じた画像データに変換し、各画素の画像データを複数のサブフィールドに対応する複数のビットに分割し、それらをデータ電極駆動回路52に出力する。

【0035】

データ電極駆動回路52は、サブフィールド毎の画像データを各データ電極D1〜Dmに対応する信号に変換し、その信号に基づいて各データ電極D1〜Dmを駆動する。APL検出器56は、画像信号sigのAPL(平均画像レベル;Average Picture Level)を検出し、検出したAPLを示す信号をタイミング発生回路55へ出力する。ここで、APLとは、1フレームにおける画像信号sigの輝度レベルの平均をいい、1画面の画像の全体的な明るさを表している。本実施の形態では、1フレームは1フィールドに等しい。

【0036】

タイミング発生回路55は、水平同期信号H、垂直同期信号VおよびAPL検出器56が検出した平均輝度レベルAPLに基づいてタイミング信号を発生し、それらのタイミング信号をそれぞれの駆動回路ブロック(画像信号処理回路51、データ電極駆動回路52、走査電極駆動回路53および維持電極駆動回路54)へ供給する。

【0037】

走査電極駆動回路53は、タイミング信号に基づいて走査電極SC1〜SCnに駆動波形を供給し、維持電極駆動回路54はタイミング信号に基づいて維持電極SU1〜SUnに駆動波形を供給する。なお、走査電極駆動回路53は、後述するように、初期化期間において走査電極(SC1,SC2,…,SC(n/6))、走査電極(SC(n/6+1),SC(n/6+2),…,SC(n/2))と走査電極(SC(n/2+1),SC(n/2+2),SC(n))と、走査電極群を2:4:6に分割し、それぞれに異なる駆動波形を印加する3相駆動動作および走査電極(SC1,SC2,…SC(n/3))と走査電極(SC(n/3+1),SC(n/3+2),…SC(n))と、走査電極群を4:8に分割し、それぞれに異なる駆動波形を印加する2相駆動動作とを選択的に行うことができる。ここで、nは6の倍数である。

【0038】

また、本実施の形態においては、タイミング発生回路55は、APL検出器56により検出されるAPLに基づいて、1相駆動動作のためのタイミング信号および3相駆動動作のためのタイミング信号を選択的に発生し、発生したタイミング信号を走査電極駆動回路53へ供給する。それにより、走査電極SC1〜SCnが1相駆動動作または3相駆動動作により駆動される。

【0039】

以下の説明においては、3相駆動動作時においては、走査電極(SC1,SC2,…,SC(n/6))を第1の走査電極群と称し、走査電極(SC(n/6+1),SC(n/6+2),…,SC(n/2))を第2の走査電極群と称し、走査電極(SC(n/2+1),SC(n/2+2),…SC(n))を第3の走査電極群と称する。また、維持電極(SU1,SU2,…,SU(n/6))を第1の維持電極群と称し、維持電極(SU(n/6+1),SU(n/6+2),…,SU(n/2))を第2の維持電極群と称し、維持電極(SU(n/2+1),SU(n/2+2),SU(n))を第3の維持電極群と称する。さらに、第1の走査電極群および第1の維持電極群により構成される複数の放電セルを第1の放電セル群と称し、第2の走査電極群および第2の維持電極群により構成される複数の放電セルを第2の放電セル群と称し、第3の走査電極群および第3の維持電極群により構成される複数の放電セルを第3の放電セル群と称する。

【0040】

また、2相駆動動作時においては名称を変え、走査電極(SC1,SC2,…SC(n/3))を第4の走査電極群と称し、走査電極(SC(n/3+1),SC(n/3+2),…SC(n))を第5の走査電極群と称する。また、維持電極(SU1,SU2,…SU(n/3))を第4の維持電極群、維持電極(SU(n/3+1),SU(n/3+2),…SU(n))を第5の維持電極群と称する。さらに、第4の走査電極群および第4の維持電極群により構成される複数の放電セルを第4の放電セル群と称し、第5の走査電極群と第5の維持電極群により構成される複数の放電セルを第5の放電セル群と称する。

【0041】

(1−3)サブフィールド構成

次に、サブフィールド構成について説明する。サブフィールド法では、1フィールド(1/60秒=16.67msec)が時間軸上で複数のサブフィールドに分割され、複数のサブフィールドに輝度重みがそれぞれ設定されている。例えば、1フィールドが時間軸上で10個のサブフィールド(以下、第1SF、第2SF、・・・、および第10SFと呼ぶ)に分割され、それらのサブフィールドがそれぞれ1、2、3、6、11、18、30、44、60および81の輝度重みを有する。

【0042】

図4および図5は、図3のプラズマディスプレイ装置のサブフィールド構成における、走査電極駆動回路53の駆動動作時に各電極に印加される駆動波形を示す図である。なお、図4は、走査電極駆動回路53の3相駆動動作時に各電極に印加される駆動波形を示し、図5は走査電極駆動回路53の2相駆動動作時に各電極に印加される駆動波形を示す。図4には、第1の走査電極群(SC1,SC2,…,SC(n/6))の1本の走査電極SC1、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))の1本の走査電極SC(n/6+1)、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の1本の走査電極SC(n/2+1)、維持電極SU1〜SUn、およびデータ電極D1〜Dmの駆動波形が示される。なお、図4には、1フィールドの第1SFの初期化期間から第2SFの維持期間までが示される。また、図5には、第4の走査電極群(SC1,SC2,…SC(n/3))の1本の走査電極SC1、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))の1本の走査電極SC(n/3+1)、維持電極SU1〜SUn、およびデータ電極D1〜Dmの駆動波形が示される。なお、図5には、1フィールドの第1SFの初期化期間から第2SFの維持期間までが示される。

【0043】

(a)3相駆動動作時の駆動波形

まず、走査電極駆動回路53の3相駆動動作時に各電極に印加される駆動波形について説明する。図4に示すように、第1SFの初期化期間の前半部では、データ電極D1〜Dmに電位0V(接地電位)からVdaに緩やかに上昇するランプ波形Ldを印加し、維持電極SU1〜SUnを接地電位に保持し、走査電極SC1〜SCnにランプ波形L1を印加する。このランプ波形L1は、放電開始電圧以下の正の電位Vscnから放電開始電圧を超える正の電位(Vsus+Vset)に向かって緩やかに上昇する。すると、全ての放電セルにおいて1回目の微弱な初期化放電が起こり、走査電極SC1〜SCn上に負の壁電荷が蓄えられるとともに維持電極SU1〜SUn上およびデータ電極D1〜Dm上に正の壁電荷が蓄えられる。ここで、電極を覆う誘電体層または蛍光体層上等に蓄積した壁電荷により生じる電圧を電極上の壁電圧という。

【0044】

続く初期化期間の後半部では、データ電極D1〜Dmを接地電位に保持し、維持電極SU1〜SUnを正の電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))にVsusから(−Vad+Vset2)に向かって緩やかに下降するランプ波形L2を印加する。すると、第1の放電セル群において2回目の微弱な初期化放電が起こる。これにより、第1の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0045】

一方、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L5を印加する。これにより、第2の放電セル群および第3の放電セル群において2回目の微弱な初期化放電が起こる。その後、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。なお、Vhizは、Vset2およびVset4よりも大きい。

【0046】

ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))に印加されるランプ波形L2は(−Vad+Vset2)まで下降するのに対して、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),SC(n))に印加されるランプ波形L5は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第2の放電セル群、第3の放電セル群においては2回目の初期化放電によって移動する電荷の量が第1の放電セル群に比べて少ない。それにより、2回目の初期化放電後、第2の放電セル群および第3の放電セル群には、第1の放電セル群より多くの壁電荷が保持される。

【0047】

続く第1SFの書込み期間の前半部では、維持電極SU1〜SUnを一旦電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、1行目の走査電極SC1に負の走査パルスPa(=−Vad)を印加するとともに、データ電極D1〜Dmのうち1行目において発光すべき放電セルのデータ電極Dk(kは1〜mのいずれか)に正の書込みパルスPd(=Vda)を印加する。すると、データ電極Dkと走査電極SC1との交差部の電圧は、外部印加電圧(Pd−Pa)にデータ電極Dk上の壁電圧および走査電極SC1上の壁電圧が加算された値となり、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC1との間および維持電極SU1と走査電極SC1との間で書込み放電が発生する。その結果、その放電セルの走査電極SC1上に正の壁電荷が蓄積され、維持電極SU1上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。

【0048】

このようにして、1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dh(h≠k)と走査電極SC1との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。

【0049】

以上の書込み動作を、第1の放電セル群において(3n−2)行目のセルに順次行う。

【0050】

第1の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。

【0051】

一方、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L7を印加する。ここでも、上述したランプ波形L2とランプ波形L5の関係と同様に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L7は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第3の放電セル群においては、第1の放電セル群3回目の初期化放電によって移動する電荷の量が第1の放電セル群および第2の放電セル群に比べて少ない。それにより、3回目の初期化放電後、第3の放電セル群には、第2の放電セル群より多くの壁電荷が保持される。さらに、第2の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L8を印加する。

【0052】

その後、上記同様の書込み動作を第3の放電セル群において(3n)行目の放電セル群に順次行う。ここで、書込み動作として第1の走査電極群(SC1,SC2,…,SC(n/6))に走査パルスPaが印加される期間には、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第2の放電セル群および第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第2の放電セル群および第3の放電セル群には第1の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第2の放電セル群および第3の放電セル群の壁電荷が減少しても、第2の放電セル群および第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0053】

さらに、書込み動作として第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaが印加される期間には、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第3の放電セル群には第2の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第3の放電セル群の壁電荷が減少しても、第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0054】

また、本実施の形態においては、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。すると、第2の放電セル群において3回目の微弱な初期化放電が起こる。これにより、第2の放電セル群において、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。但し、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L7は(−Vad+Vset2)より高い(−Vad+Vhiz)までしか下降しないため、第3の放電セル群にはまだ十分な量の壁電荷が保持される。

【0055】

さらに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に走査パルスPaを印加する直前に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L8を印加する。すると、第3の放電セル群において4回目の微弱な初期化放電が起こる。これにより、第3の放電セル群において、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の3相駆動動作時には、第1SFの初期化期間において第1の放電セル群に属する全ての放電セルの初期化動作(第1の放電セル群の全セル初期化動作)が行われ、第1SFの初期化期間および書込み期間において第2の放電セル群に属する全ての放電セルの初期化動作(第2の放電セル群の全セル初期化動作)が行われ、その後第1SFの初期化期間および書込み期間において第3の放電セル群に属する全ての放電セルの初期化動作(第3の放電セル群の全セル初期化動作)が行われる。

【0056】

第1SFの書込み期間の中間部(上記ランプ波形L6の印加後)では、維持電極SU1〜SUnを電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、n/6+1行目の走査電極SC(n/6+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/6+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/6+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC(n/6+1)との間および維持電極SU(n/6+1)と走査電極SC(n/6+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/6+1)上に正の壁電荷が蓄積され、維持電極SU(n/6+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。このようにして、n/6+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/6+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。以上の書込み動作を、第2の放電セル群において、n/6+1行目の放電セルから、n/2行目の放電セルに至るまで順次行う。

【0057】

また、第1SFの書込み期間の後半部(上記ランプ波形L8の印加後)では、維持電極SU1〜SUnを電位Veに保持し、走査電極SC1〜SC(n)を一旦電位(−Vad+Vscn)に保持する。次に、n/2+1行目の走査電極SC(n/2+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/2+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/2+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC2との間および維持電極SU(n/2+1)と走査電極SC(n/2+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/2+1)上に正の壁電荷が蓄積され、維持電極SU(n/2+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。

【0058】

このようにして、n/2+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/2+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。以上の書込み動作を、第3の放電セル群において、(n/2+1)行目の放電セルから(n)行目の放電セルに至るまで順次行い、書込み期間が終了する。

【0059】

続く維持期間では、維持電極SU1〜SUnを接地電位に戻し、走査電極SC1〜SCnに維持期間の最初の維持パルスPs(=Vsus)を印加する。このとき、書込み期間で書込み放電が発生した放電セルにおいては、走査電極SCiと維持電極SUiとの間の電圧は、維持パルスPs(=Vsus)に走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が加算された値となり、放電開始電圧を超える。それにより、走査電極SCiと維持電極SUiとの間で維持放電が起こり、放電セルが発光する。その結果、走査電極SCi上に負の壁電荷が蓄積され、維持電極SUi上に正の壁電荷が蓄積され、データ電極Dk上に正の壁電荷が蓄積される。

【0060】

書込み期間で書込み放電が発生しなかった放電セルでは維持放電は起こらず、初期化期間の終了時における壁電荷の状態が保持される。続いて、走査電極SC1〜SCnを接地電位に戻し、維持電極SU1〜SUnに維持パルスPsを印加する。すると、維持放電が起こった放電セルでは、維持電極SUiと走査電極SCiとの間の電圧が放電開始電圧を超えるので、再び維持電極SUiと走査電極SCiとの間で維持放電が起こり、維持電極SUi上に負の壁電荷が蓄積され、走査電極SCi上に正の壁電荷が蓄積される。

【0061】

以降同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加することにより、書込み期間において書込み放電が発生した放電セルでは維持放電が継続して行われる。維持パルスPsの印加後、維持電極SU1〜SUnおよびデータ電極D1〜Dmを接地電位に保持した状態で、走査電極SC1〜SCnにランプ波形L3を印加する。このランプ波形L3は、接地電位から正の電位Veraseに向かって緩やかに上昇する。これにより、維持放電が起こった放電セルにおいて、走査電極SCiと維持電極SUiとの間の電圧が放電開始電圧を超え、維持電極SUiと走査電極SCiとの間で微弱な消去放電が発生する。

【0062】

第2SFの初期化期間では、維持電極SU1〜SUnを電位Veに保持し、データ電極D1〜Dmを接地電位に保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))に接地電位から(−Vad+Vset4)に向かって緩やかに下降するランプ波形L4を印加する。すると、第1の放電セル群のうち前のサブフィールド(図4では、第1SF)の維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。それにより、第1の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0063】

第1の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては、放電が発生することはなく、前のサブフィールドの初期化期間の終了時における壁電荷の状態がそのままの状態よりやや低い値に保たれる。一方、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L9を印加する。その後、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。この場合、第2の放電セル群および第3の放電セル群のうち前のサブフィールドの維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。

【0064】

ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))に印加されるランプ波形L4は(−Vad+Vset4)まで下降するのに対して、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L9は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第2の放電セル群および第3の放電セル群においては、第1の放電セル群に比べて移動する電荷の量が少ない。そのため、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第1の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。

【0065】

なお、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては放電が発生しない。

【0066】

続く第2SFの書込み期間の前半部では、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の前半部と同様の駆動波形を印加する。

【0067】

第1の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。

【0068】

一方、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L11を印加する。その後、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。ここで、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に印加されるランプ波形L10は(−Vad+Vset4)まで下降するのに対して、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L11は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第3の放電セル群においては、第1の放電セル群および第2の放電セル群に比べて移動する電荷の量が少ない。そのため、第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第1の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。

【0069】

さらに、第2の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L12を印加する。

【0070】

ここで、第2SFの書込み期間において第1の走査電極群(SC1,SC2,…,SC(n/6))に走査パルスPaが印加される期間には、第2の走査電極群(SC(3n−1))および第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第2の放電セル群および第3の放電セル群の壁電荷は減少する。しかしながら、上述したように、第2の放電セル群および第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第2SFの初期化期間終了時に多くの壁電荷が保持されている。従って、上記の期間においてそれらの放電セルの壁電荷が減少しても、それらの放電セルにはまだ十分な量の壁電荷が保持されている。

【0071】

さらに、第2SFの書込み期間において第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaが印加される期間には、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))には走査パルスPaが印加されない。この期間において、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第3の放電セル群には第2の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第3の放電セル群の壁電荷が減少しても、第3の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0072】

また、本実施の形態においては、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に、第1の走査電極群(SC1,SC2,…,SC(n/6))および第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。すると、第2の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて微弱な初期化放電が起こる。これにより、第2の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。但し、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に走査パルスPaを印加する直前に第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に印加されるランプ波形L11は(−Vad+Vset4)より高い(−Vad+Vhiz)までしか下降しないため、第3の放電セル群にはまだ十分な量の壁電荷が保持される。

【0073】

さらに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に走査パルスPaを印加する直前に、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L12を印加する。すると、第3の放電セル群において4回目の微弱な初期化放電が起こる。これにより、第3の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUi上の壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の3相駆動動作時には、第2SFの初期化期間において第1の放電セル群に対する選択初期化動作が行われ、第2SFの初期化期間および書込み期間において第2の放電セル群および第3の放電セル群に対する選択初期化動作が行われる。なお、選択初期化動作とは、直前のサブフィールドで維持放電が起こった放電セルで選択的に初期化放電を発生させる動作を言う。

【0074】

第2SFの書込み期間の中間部以降(上記ランプ波形L10の印加後)では、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の中間部以降と同様の駆動波形を印加する。

【0075】

第2SFの維持期間には、第1SFの維持期間と同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加する。それにより、書込み期間において書込み放電が発生した放電セルで維持放電が行われる。

【0076】

また、第3SF以降のサブフィールドでは、第1の走査電極群(SC1,SC2,…,SC(n/6))、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第2SFと同様の駆動波形を印加する。

【0077】

(b)2相駆動動作時の駆動波形

次に、走査電極駆動回路53の2相駆動動作時に各電極に印加される駆動波形について説明する。なお、図5に示すランプ波形L1〜L4は、図4のランプ波形L1〜L4と同様である。第1SFの初期化期間の前半部では、データ電極D1〜Dmの電位をVdaに保持し、維持電極SU1〜SUnを接地電位に保持し、走査電極SC1〜SCnにランプ波形L1を印加する。それにより、全ての放電セルにおいて1回目の微弱な初期化放電が起こり、走査電極SC1〜SCn上に負の壁電荷が蓄えられるとともに維持電極SU1〜SUn上およびデータ電極D1〜Dm上に正の壁電荷が蓄えられる。

【0078】

続く初期化期間の後半部では、データ電極D1〜Dmを接地電位に保持し、維持電極SU1〜SUnを正の電位Veに保持し、第4の走査電極群(SC1,SC2,…SC(n/3))にVsusから(−Vad+Vset2)に向かって緩やかに下降するランプ波形L2を印加する。すると、第1の放電セル群において2回目の微弱な初期化放電が起こる。これにより、第1の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。一方、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には、Vsusから(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L5を印加する。これにより、第2の放電セル群において2回目の微弱な初期化放電が起こる。その後、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))を一旦電位(−Vad+Vhiz)に保持する。

【0079】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に印加されるランプ波形L2は(−Vad+Vset2)まで下降するのに対して、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に印加されるランプ波形L5は(−Vad+Vset2)よりも高い(−Vad+Vhiz)までしか下降しない。そのため、第5の放電セル群においては2回目の初期化放電によって移動する電荷の量が第4の放電セル群に比べて少ない。それにより、2回目の初期化放電後、第5の放電セル群には、第4の放電セル群より多くの壁電荷が保持される。

【0080】

第1SFの書込み期間の前半部では、図4で説明したように、第4の放電セル群において1行目の放電セルからn/3行目の放電セルに至るまで書込み動作を順次行う。

【0081】

第4の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。

【0082】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に走査パルスPaが印加される期間には、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には走査パルスPaが印加されない。この期間において、第5の放電セル群の壁電荷は減少する。しかしながら、上述したように、初期化期間が終了した時点で、第5の放電セル群には第4の放電セル群より多くの壁電荷が保持されている。従って、上記の期間において第5の放電セル群の壁電荷が減少しても、第5の放電セル群にはまだ十分な量の壁電荷が保持されている。

【0083】

また、本実施の形態においては、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に走査パルスPaを印加する直前に、走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset2)に向かって緩やかに下降するランプ波形L6を印加する。すると、第5の放電セル群において3回目の微弱な初期化放電が起こる。これにより、第5の放電セル群において、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の2相駆動動作時には、第1SFの初期化期間において第1の放電セル群に属する全ての放電セルの初期化動作(第4の放電セル群の全セル初期化動作)が行われ、第1SFの初期化期間および書込み期間において第5の放電セル群に属する全ての放電セルの初期化動作(第5の放電セル群の全セル初期化動作)が行われる。

【0084】

第1SFの書込み期間の後半部(上記ランプ波形L6の印加後)では、維持電極SU1〜SUnを再び電位Veに保持し、走査電極SC1〜SCnを一旦電位(−Vad+Vscn)に保持する。次に、n/3+1行目の走査電極SC(n/3+1)に負の走査パルスPaを印加するとともに、データ電極D1〜Dmのうちn/3+1行目において発光すべき放電セルのデータ電極Dkに正の書込みパルスPdを印加する。すると、データ電極Dkと走査電極SC(n/3+1)との交差部の電圧は、放電開始電圧を超える。それにより、データ電極Dkと走査電極SC(n/3+1)との間および維持電極SU(n/3+1)と走査電極SC(n/3+1)との間で書込み放電が発生する。その結果、その放電セルの走査電極SC(n/3+1)上に正の壁電荷が蓄積され、維持電極SU(n/3+1)上に負の壁電荷が蓄積され、データ電極Dk上にも負の壁電荷が蓄積される。このようにして、n/3+1行目において発光すべき放電セルで書込み放電が発生して各電極上に壁電荷を蓄積させる書込み動作が行われる。一方、書込みパルスPdが印加されなかったデータ電極Dhと走査電極SC(n/3+1)との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。

【0085】

以上の書込み動作を、第5の放電セル群において、n/3+1行目の放電セルから(n)行目の放電セルに至るまで順次行い、書込み期間が終了する。

【0086】

続く維持期間では、図4で説明したように、走査電極SC1〜SCnおよび維持電極SU1〜SUnに交互に維持パルスPsを印加する。それにより、書込み期間において書込み放電が発生した放電セルにおいて維持放電が発生する。維持パルスPsの印加後、図4で説明したように、走査電極SC1〜SCnにランプ波形L3を印加する。これにより、維持放電が起こった放電セルにおいて、微弱な消去放電が発生する。その結果、走査電極SCiに負の壁電荷が蓄積され、維持電極SUiに正の壁電荷が蓄積される。このとき、データ電極Dk上には正の壁電荷が蓄積される。その後、走査電極SC1〜SCnを接地電位に戻し、維持期間における維持動作を終了する。

【0087】

第2SFの初期化期間では、維持電極SU1〜SUnを電位Veに保持し、データ電極D1〜Dmを接地電位に保持し、第4の走査電極群(SC1,SC2,…SC(n/3))に接地電位から(−Vad+Vset4)に向かって緩やかに下降するランプ波形L4を印加する。すると、第4の放電セル群のうち前のサブフィールド(図5では、第1SF)の維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。それにより、第4の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。

【0088】

第4の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては、放電が発生することはなく、前のサブフィールドの初期化期間の終了時における壁電荷の状態がそのまま保たれる。一方、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には、接地電位から(−Vad+Vhiz)に向かって緩やかに下降するランプ波形L9を印加する。その後、第2の走査電極群を一旦電位(−Vad+Vhiz)に保持する。この場合、第5の放電セル群のうち前のサブフィールドの維持期間で維持放電が起こった放電セルでは微弱な初期化放電が発生する。

【0089】

ここで、第4の走査電極群(SC1,SC2,…SC(n/3))に印加されるランプ波形L4は(−Vad+Vset4)まで下降するのに対して、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に印加されるランプ波形L9は(−Vad+Vset4)よりも高い(−Vad+Vhiz)までしか下降しない。それにより、第5の放電セル群においては、第4の放電セル群に比べて移動する電荷の量が少ない。そのため、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第4の放電セル群の各放電セルよりも多くの壁電荷が蓄積された状態になる。なお、第5の放電セル群のうち前のサブフィールドで維持放電が起こらなかった放電セルにおいては放電が発生しない。

【0090】

第2SFの書込み期間の前半部では、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の前半部と同様の駆動波形を印加する。

【0091】

第4の放電セル群における書込み動作の終了後、維持電極SU1〜SUnを電位Veに保持し、全ての走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。ここで、第2SFの書込み期間において第4の走査電極群(SC1,SC2,…SC(n/3))に走査パルスPaが印加される期間には、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))には走査パルスPaが印加されない。この期間において、第5の放電セル群の壁電荷は減少する。しかしながら、上述したように、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルには、第2SFの初期化期間終了時に多くの壁電荷が保持されている。従って、上記の期間においてそれらの放電セルの壁電荷が減少しても、それらの放電セルにはまだ十分な量の壁電荷が保持されている。

【0092】

また、本実施の形態においては、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))に走査パルスPaを印加する直前に、走査電極SC1〜SCnに接地電位から負の電位(−Vad+Vset4)に向かって緩やかに下降するランプ波形L10を印加する。すると、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて微弱な初期化放電が起こる。これにより、第5の放電セル群のうち前のサブフィールドで維持放電が起こった放電セルにおいて、走査電極SCi上の壁電圧および維持電極SUiの壁電圧が弱められ、データ電極Dk上の壁電圧も書込み動作に適した値に調整される。すなわち、走査電極駆動回路53の2相駆動動作時には、第2SFの初期化期間において第4の放電セル群に対する選択初期化動作が行われ、第2SFの初期化期間および書込み期間において第5の放電セル群に対する選択初期化動作が行われる。なお、選択初期化動作とは、直前のサブフィールドで維持放電が起こった放電セルで選択的に初期化放電を発生させる動作をいう。

【0093】

第2SFの書込み期間の後半部では、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第1SFの書込み期間の後半部と同様の駆動波形を印加する。第2SFの維持期間には、第1SFの維持期間と同様に、走査電極SC1〜SCnと維持電極SU1〜SUnとに予め定められた数の維持パルスPsを交互に印加する。それにより、書込み期間において書込み放電が発生した放電セルで維持放電が行われる。また、第3SF以降のサブフィールドでは、第4の走査電極群(SC1,SC2,…SC(n/3))、第5の走査電極群(SC(n/3+1),SC(n/3+2),…SC(n))、維持電極SU1〜SUnおよびデータ電極D1〜Dmに対して第2SFと同様の駆動波形を印加する。

【0094】

(1−4)走査電極駆動回路53の構成

図6は走査電極駆動回路53の構成を示す回路図である。

【0095】

走査電極駆動回路53は、第1の駆動回路DR1、第2の駆動回路DR2、第3の駆動回路DR3、直流電源200、回収回路300、比較回路400、ダイオードD10,D11およびnチャネル電界効果トランジスタ(以下、トランジスタと略記する)Q3〜Q9を含む。

【0096】

第1の駆動回路DR1は、複数の走査IC100を含む。各走査IC100は、ノードN1とノードN2との間に接続されるとともに、第1の走査電極群(SC1,SC2,…,SC(n/6))に属する走査電極SC1,SC2,…,SC(n/6)の各々に接続される。各走査IC100は、対応する走査電極SC1,SC2,…,SC(n/6)をノードN1およびノードN2に選択的に接続する。

【0097】

第1の駆動回路DR1には、制御信号S51A,S52Aが与えられる。制御信号S51A,S52Aの論理に応じて走査IC100の状態が切り替わる。走査IC100の詳細については後述する。第2の駆動回路DR2は、複数の走査IC110を含む。各走査IC110は、ノードN1とノードN2との間に接続されるとともに、第2の走査電極群(SC(n/6+1),SC(n/6+2),…,SC(n/2))に属する走査電極SC(n/6+1),SC(n/6+2),…,SC(n/2)の各々に接続される。各走査IC110は、対応する走査電極SC(n/6+1),SC(n/6+2),…,SC(n/2)をノードN1およびノードN2に選択的に接続する。

【0098】

第2の駆動回路DR2には、制御信号S51B,S52Bが与えられる。制御信号S51B,S52Bの論理に応じて走査IC110の状態が切り替わる。走査IC110の詳細については後述する。

【0099】

第3の駆動回路DR3は、複数の走査IC120を含む。各走査IC120は、ノードN1とノードN2との間に接続されるとともに、第3の走査電極群(SC(n/2+1),SC(n/2+2),…SC(n))に属する走査電極SC(n/2+1),SC(n/2+2),…SC(n)の各々に接続される。各走査IC120は、対応する走査電極(SC(n/2+1),SC(n/2+2),…SC(n))をノードN1およびノードN2に選択的に接続する。第3の駆動回路DR3には、制御信号S51C,S52Cが与えられる。制御信号S51C,S52Cの論理に応じて走査IC120の状態が切り替わる。走査IC120の詳細については後述する。

【0100】

電圧Vscnを受ける電源端子V10は、ダイオードD10を介してノードN3に接続される。直流電源200は、ノードN1とノードN3との間に接続される。この直流電源200は、電解コンデンサからなり、電圧Vscnを保持するフローティング電源として働く。ノードN2とノードN3との間には、保護抵抗R1が接続される。以下、ノードN1の電位をVFGNDとし、ノードN3の電位をVscnFとする。ノードN3の電位VscnFは、ノードN1の電位VFGNDに電圧Vscnを加算した値を有する。すなわち、VscnF=VFGND+Vscnとなる。

【0101】

トランジスタQ3は、電圧(Vset+(Vsus−Vscn))を受ける電源端子V11とノードN4との間に接続され、ゲートには制御信号S3が与えられる。トランジスタQ4は、ノードN1とノードN4との間に接続され、ゲートには制御信号S4が与えられる。トランジスタQ5は、ノードN1と負の電圧(−Vad)を受ける電源端子V12との間に接続され、ゲートには制御信号S5が与えられる。制御信号S4は制御信号S5の反転信号である。また、トランジスタQ3,Q5にはゲート抵抗RGおよびコンデンサCGが接続される。なお、トランジスタQ6にもゲート抵抗およびコンデンサが接続されるが、図示は省略する。

【0102】

トランジスタQ6は、電圧Vsusを受ける電源端子V13とノードN5との間に接続される。トランジスタQ6のベースには制御信号S6が与えられる。トランジスタQ7は、ノードN4とノードN5との間に接続される。トランジスタQ7のゲートには制御信号S7が与えられる。トランジスタQ8は、ノードN4と接地端子との間に接続され、ベースには制御信号S8が与えられる。電圧Veraseを受ける電源端子V14とノードN4との間に、トランジスタQ9およびダイオードD11が接続される。トランジスタQ9のベースには制御信号S9が与えられる。

【0103】

回収回路300は、ノードN4とノードN5との間に接続される。回収回路300は、上記の維持期間において、複数の放電セルから電荷を回収して蓄積するとともに、蓄積した電荷を再び複数に放電セルに与える。比較回路400は、電源端子V12とノードN1との間に接続される。比較回路400の詳細については後述する。

【0104】

(1−5)走査ICの詳細

次に、走査IC100,110,120の詳細について説明する。上記のように、走査IC100の状態は制御信号S51A,S52Aの論理に応じて切り替わり、走査IC110の状態は制御信号S51B,S52Bの論理に応じて切り替わり、走査IC120の状態は制御信号S51C,S52Cの論理に応じて切り替わる。

【0105】