プリント基板およびその放射ノイズ抑制方法

【課題】電源端子ノイズ抑制を目的としたインプット・インピーダンス(Z11)低減手法やノイズ伝播抑制を目的としたトランスファー・インピーダンス(Z21)低減手法に関する検討が行われてきたが、EMI対策には、プリント基板単体とシステム全体(チップ+パッケージ+ボード)との協調設計により、システム全体の放射ノイズを抑制する必要がある。

【解決手段】LSIを実装したプリント基板において、LSI端子からプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、LSIを含んだシステム全体での評価を行ない、放射ノイズを抑制する。

【解決手段】LSIを実装したプリント基板において、LSI端子からプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、LSIを含んだシステム全体での評価を行ない、放射ノイズを抑制する。

【発明の詳細な説明】

【技術分野】

【0001】

放射ノイズの原因は(a)高速信号系コモンモード放射、(b)パッケージ・ヒートシンクなどからの放射、(c)スリット等による放射、(d)電源系共振、(e)ケーブルからの放射などであり、本発明は、これらの内(d)電源系共振から発生する放射ノイズの抑制に関し、中でも半導体集積回路(LSI)を含んだ電源供給系全体のトランスファー・インピーダンス(Z21)が低減されたプリント基板およびその放射ノイズを抑制する方法に関する。

【背景技術】

【0002】

従来、電源系共振から発生する放射ノイズの抑制には、コンデンサによる対策が一般的で、プリント基板単体での対策が主流であり、電源系のノイズ低減のためにはトランスファー・インピーダンス(Z21)を扱うことは少なく、コンデンサの配置方法による電圧変動の抑制、実測をベースとしたカット アンド トライの対策となっていた。

【0003】

また、半導体の動作に伴う電流量の増加により、電源端子ノイズが増加し、この電源端子ノイズがプリント基板を伝播し、不要電磁放射(EMI)の原因となっている。

【0004】

特許文献1には、LSIの電源端子近傍に搭載するデカップリングコンデンサの数量をLSIごとに最適化することで、高周波電源電流を抑制し、実装スペースの削減と資材コストを削減すると共に、回路の安定動作とEMIを低減することを可能としたプリント基板の設計方法が提案されているが、これはLSI設計工程で設計が完了したLSIの出力バッファ種別などの設計情報やパターン設計工程で設計が完了した設計情報を用いるものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−73716号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

これまで、電源端子ノイズ抑制を目的としたインプット・インピーダンス(Z11)低減手法やノイズ伝播抑制を目的としたトランスファー・インピーダンス(Z21)低減手法に関する検討が行われてきたが、これらは、プリント基板単体での評価であり、プリント基板単体とシステム全体(チップ+パッケージ+ボード)とでは、インピーダンス特性が異なるため、プリント基板単体ではなくLSIとボードの協調設計により、システム全体の電源ノイズを検証することで、EMI対策を実施する必要がある。

【0007】

本発明は、LSIやパターン設計工程の設計情報が完了していない場合であっても、LSI内部のチップからプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、LSIを含んだシステム全体での評価を行ない、放射ノイズが抑制されたプリント基板を提供しようとするものである。

【課題を解決するための手段】

【0008】

請求項1の発明は、プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路(LSI)のノイズ周波数と一致しないように制御されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0009】

請求項2の発明は、ノイズ源となる半導体集積回路(LSI)からプリント基板端までのトランスファー・インピーダンス(Z21)の低減により、反共振(高インピーダンス点)がノイズ周波数と一致しないように制御されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0010】

請求項3の発明は、前記トランスファー・インピーダンス(Z21)の低減が、半導体集積回路(LSI)のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調して設計されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0011】

請求項4の発明は、前記協調が、コンデンサの変更によるものであることを特徴とするものであって、コンデンサを選択することによって、放射ノイズが抑制されたプリント基板となる。

【0012】

請求項5の発明は、プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路(LSI)のノイズ周波数と一致しないように制御するプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0013】

請求項6の発明は、前記制御が、ノイズ源となる半導体集積回路(LSI)からプリント基板端までのトランスファー・インピーダンス(Z21)を低減させて、反共振(高インピーダンス点)とノイズ周波数とを一致させないようにするプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0014】

請求項7の発明は、半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調させて、前記トランスファー・インピーダンス(Z21)を低減するプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0015】

請求項8の発明は、前記協調が、コンデンサの変更によるものであることを特徴とするものであって、コンデンサを選択することによって、プリント基板の放射ノイズを抑制することができる。

【発明の効果】

【0016】

本発明によれば、設計情報が完了していない場合であっても、LSIからプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、放射ノイズが低減され、さらにLSIのインピーダンスモデルと、プリント基板のインピーダンスモデルとを協調させることにより放射ノイズが低減されたプリント基板となる。

【図面の簡単な説明】

【0017】

【図1】本発明のプリント基板評価ボードの概略図である。

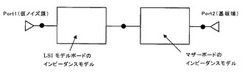

【図2】LSIモデルボードおよびマザーボードのインピーダンスモデル解析のためのシミュレーション回路である。

【図3】実施例1のマザーボードにLSIモデルボードを実装したときのプリント基板評価ボードの電流波形のFFT結果である。

【図4】実施例1のZ21と放射ノイズの関係を示す測定結果である。

【図5】実施例2のZ21と放射ノイズの関係を示す測定結果である。

【図6】実施例3のZ21と放射ノイズの関係を示す測定結果である。

【図7】実施例4のZ21と放射ノイズの関係を示す測定結果である。

【図8】実施例5のZ21と放射ノイズの関係を示す測定結果である。

【図9】実施例6のZ21と放射ノイズの関係を示す測定結果である。

【図10】実施例7のZ21と放射ノイズの関係を示す測定結果である。

【図11】実施例8のZ21と放射ノイズの関係を示す測定結果である。

【発明を実施するための形態】

【0018】

LSIモデルボードとマザーボードの作製

任意の電源インピーダンス特性を得るために、図1に示すように、それぞれのボードにコンデンサを実装し、両ボードの組み合わせにより、ノイズの発生し易い(し難い)評価ボードを作製した。

【0019】

LSIモデルボード

回路構成は水晶発振器、Shift Register、EXOR、Buffer/DriverからなるPRBS信号発生ボードで、クロック周波数は48MHzとした。評価対象をBuffer/Driverのノイズに限定するため、その他ICとは電源供給を分離し、ボードは汎用BGAパッケージをモデルとする32mm×32mmサイズの900BallのBGAとした。

【0020】

マザーボード

基板中央にLSIモデルボードが実装可能で、安定化電源から電源供給を受け、LSIモデルボード直下および基板全体の電源グラウンド間にコンデンサを実装可能とした。

【0021】

電流プロファイル取得

電流測定用抵抗(0.05Ω)の両端の電位差を測定し、I=V/Rより電流波形を計算した。また、電流波形をFFTし、周波数データを取得した。測定にはデジタルオシロスコープ(Agilent Technologies社DSA90804A)を用いた。

【0022】

電源インピーダンスシミュレーション

図2のようなシミュレーション回路において、LSIモデルボード、マザーボードのインピーダンスモデルを平面電磁界解析(Ansys社SIWave)よりSパラメータを用いて抽出し、ノイズ源IC(Buffer/Driver)の内部インピーダンスをZ11測定より算出し、LCRの集中定数としてモデル化した。なお、本形態では、ノイズ源ICの電源端子を仮のノイズ源とし、ポートを付与した。

【0023】

基板端電圧測定

スペクトラムアナライザ(ADVANTEST社R3131A)を用いて基板端電圧を測定し、基板端4箇所の測定結果がほぼ同じであることを確認の上、代表1箇所の測定とした。

【0024】

放射ノイズ測定

また、プリント基板の放射ノイズ抑制効果を測るために、小型電波暗室(外形寸法:7m×3m×3m、アンテナ〜試供体間距離:3m、アンテナ高:1m(固定))にて、放射ノイズを測定した。評価ボードはターンテーブル中央に配置し、安定化電源はテーブル下に配置し、EMC MEASUREMENT SYSTEM(東陽テクニカ社)により測定した。

【0025】

電流プロファイルのFFT結果より、図3に示すように、クロック周波数(48MHz)の3次高調波(144MHz)までの電流成分が顕著であり、当該プリント基板は、これらの周波数での放射ノイズを抑制することが必要であり、48MHzのノイズを抑制するためには0.01μFのコンデンサが、96MHzのノイズを抑制するためには2200pFのコンデンサが、144MHzのノイズを抑制するためには1000pFのコンデンサが有効であることより、これらを組み合わせた。

【0026】

LSIモデルボード、マザーボードに実装するコンデンサを表1のようにし、放射ノイズの評価を行った。コンデンサはノイズ周波数でトランスファー・インピーダンス(Z21)が高くなる、または低くなるように選択した。

【0027】

【表1】

【0028】

表2にノイズ周波数毎のZ21と基板端電圧を示す。

【0029】

【表2】

【0030】

Z21と基板端電圧には相関があり、クロック周波数(48MHz)とその高調波(96MHz、144MHz)が高インピーダンスとなる条件では、ノイズが大きくなり、Z21はノイズ伝播に寄与している。

【0031】

また、遠方界放射ノイズ測定結果より、表3および図4から11に示すように、Z21の増減傾向と放射ノイズレベルの増減傾向は一致する。

【0032】

【表3】

【0033】

プリント基板の放射ノイズを抑制するためには、LSIからプリント基板端までのトランスファー・インピーダンス(Z21)を低減し、さらにLSIのインピーダンスモデルと、プリント基板のインピーダンスモデルとを協調させることが効果的であり、得られるプリント基板は放射ノイズが低減されたプリント基板となる。

【符号の説明】

【0034】

1:プリント基板、2:マザーボード、3:LSIモデルボード、4:ノイズ源、5:大容量コンデンサ、6:チョークコイル、7:外部電源、8:グラウンド、9:電源

【技術分野】

【0001】

放射ノイズの原因は(a)高速信号系コモンモード放射、(b)パッケージ・ヒートシンクなどからの放射、(c)スリット等による放射、(d)電源系共振、(e)ケーブルからの放射などであり、本発明は、これらの内(d)電源系共振から発生する放射ノイズの抑制に関し、中でも半導体集積回路(LSI)を含んだ電源供給系全体のトランスファー・インピーダンス(Z21)が低減されたプリント基板およびその放射ノイズを抑制する方法に関する。

【背景技術】

【0002】

従来、電源系共振から発生する放射ノイズの抑制には、コンデンサによる対策が一般的で、プリント基板単体での対策が主流であり、電源系のノイズ低減のためにはトランスファー・インピーダンス(Z21)を扱うことは少なく、コンデンサの配置方法による電圧変動の抑制、実測をベースとしたカット アンド トライの対策となっていた。

【0003】

また、半導体の動作に伴う電流量の増加により、電源端子ノイズが増加し、この電源端子ノイズがプリント基板を伝播し、不要電磁放射(EMI)の原因となっている。

【0004】

特許文献1には、LSIの電源端子近傍に搭載するデカップリングコンデンサの数量をLSIごとに最適化することで、高周波電源電流を抑制し、実装スペースの削減と資材コストを削減すると共に、回路の安定動作とEMIを低減することを可能としたプリント基板の設計方法が提案されているが、これはLSI設計工程で設計が完了したLSIの出力バッファ種別などの設計情報やパターン設計工程で設計が完了した設計情報を用いるものである。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−73716号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

これまで、電源端子ノイズ抑制を目的としたインプット・インピーダンス(Z11)低減手法やノイズ伝播抑制を目的としたトランスファー・インピーダンス(Z21)低減手法に関する検討が行われてきたが、これらは、プリント基板単体での評価であり、プリント基板単体とシステム全体(チップ+パッケージ+ボード)とでは、インピーダンス特性が異なるため、プリント基板単体ではなくLSIとボードの協調設計により、システム全体の電源ノイズを検証することで、EMI対策を実施する必要がある。

【0007】

本発明は、LSIやパターン設計工程の設計情報が完了していない場合であっても、LSI内部のチップからプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、LSIを含んだシステム全体での評価を行ない、放射ノイズが抑制されたプリント基板を提供しようとするものである。

【課題を解決するための手段】

【0008】

請求項1の発明は、プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路(LSI)のノイズ周波数と一致しないように制御されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0009】

請求項2の発明は、ノイズ源となる半導体集積回路(LSI)からプリント基板端までのトランスファー・インピーダンス(Z21)の低減により、反共振(高インピーダンス点)がノイズ周波数と一致しないように制御されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0010】

請求項3の発明は、前記トランスファー・インピーダンス(Z21)の低減が、半導体集積回路(LSI)のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調して設計されたプリント基板であって、得られたプリント基板は、放射ノイズが抑制されたものになる。

【0011】

請求項4の発明は、前記協調が、コンデンサの変更によるものであることを特徴とするものであって、コンデンサを選択することによって、放射ノイズが抑制されたプリント基板となる。

【0012】

請求項5の発明は、プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路(LSI)のノイズ周波数と一致しないように制御するプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0013】

請求項6の発明は、前記制御が、ノイズ源となる半導体集積回路(LSI)からプリント基板端までのトランスファー・インピーダンス(Z21)を低減させて、反共振(高インピーダンス点)とノイズ周波数とを一致させないようにするプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0014】

請求項7の発明は、半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調させて、前記トランスファー・インピーダンス(Z21)を低減するプリント基板の放射ノイズ抑制方法であって、得られるプリント基板は、放射ノイズが抑制されたものになる。

【0015】

請求項8の発明は、前記協調が、コンデンサの変更によるものであることを特徴とするものであって、コンデンサを選択することによって、プリント基板の放射ノイズを抑制することができる。

【発明の効果】

【0016】

本発明によれば、設計情報が完了していない場合であっても、LSIからプリント基板端までのトランスファー・インピーダンス(Z21)を制御することにより、放射ノイズが低減され、さらにLSIのインピーダンスモデルと、プリント基板のインピーダンスモデルとを協調させることにより放射ノイズが低減されたプリント基板となる。

【図面の簡単な説明】

【0017】

【図1】本発明のプリント基板評価ボードの概略図である。

【図2】LSIモデルボードおよびマザーボードのインピーダンスモデル解析のためのシミュレーション回路である。

【図3】実施例1のマザーボードにLSIモデルボードを実装したときのプリント基板評価ボードの電流波形のFFT結果である。

【図4】実施例1のZ21と放射ノイズの関係を示す測定結果である。

【図5】実施例2のZ21と放射ノイズの関係を示す測定結果である。

【図6】実施例3のZ21と放射ノイズの関係を示す測定結果である。

【図7】実施例4のZ21と放射ノイズの関係を示す測定結果である。

【図8】実施例5のZ21と放射ノイズの関係を示す測定結果である。

【図9】実施例6のZ21と放射ノイズの関係を示す測定結果である。

【図10】実施例7のZ21と放射ノイズの関係を示す測定結果である。

【図11】実施例8のZ21と放射ノイズの関係を示す測定結果である。

【発明を実施するための形態】

【0018】

LSIモデルボードとマザーボードの作製

任意の電源インピーダンス特性を得るために、図1に示すように、それぞれのボードにコンデンサを実装し、両ボードの組み合わせにより、ノイズの発生し易い(し難い)評価ボードを作製した。

【0019】

LSIモデルボード

回路構成は水晶発振器、Shift Register、EXOR、Buffer/DriverからなるPRBS信号発生ボードで、クロック周波数は48MHzとした。評価対象をBuffer/Driverのノイズに限定するため、その他ICとは電源供給を分離し、ボードは汎用BGAパッケージをモデルとする32mm×32mmサイズの900BallのBGAとした。

【0020】

マザーボード

基板中央にLSIモデルボードが実装可能で、安定化電源から電源供給を受け、LSIモデルボード直下および基板全体の電源グラウンド間にコンデンサを実装可能とした。

【0021】

電流プロファイル取得

電流測定用抵抗(0.05Ω)の両端の電位差を測定し、I=V/Rより電流波形を計算した。また、電流波形をFFTし、周波数データを取得した。測定にはデジタルオシロスコープ(Agilent Technologies社DSA90804A)を用いた。

【0022】

電源インピーダンスシミュレーション

図2のようなシミュレーション回路において、LSIモデルボード、マザーボードのインピーダンスモデルを平面電磁界解析(Ansys社SIWave)よりSパラメータを用いて抽出し、ノイズ源IC(Buffer/Driver)の内部インピーダンスをZ11測定より算出し、LCRの集中定数としてモデル化した。なお、本形態では、ノイズ源ICの電源端子を仮のノイズ源とし、ポートを付与した。

【0023】

基板端電圧測定

スペクトラムアナライザ(ADVANTEST社R3131A)を用いて基板端電圧を測定し、基板端4箇所の測定結果がほぼ同じであることを確認の上、代表1箇所の測定とした。

【0024】

放射ノイズ測定

また、プリント基板の放射ノイズ抑制効果を測るために、小型電波暗室(外形寸法:7m×3m×3m、アンテナ〜試供体間距離:3m、アンテナ高:1m(固定))にて、放射ノイズを測定した。評価ボードはターンテーブル中央に配置し、安定化電源はテーブル下に配置し、EMC MEASUREMENT SYSTEM(東陽テクニカ社)により測定した。

【0025】

電流プロファイルのFFT結果より、図3に示すように、クロック周波数(48MHz)の3次高調波(144MHz)までの電流成分が顕著であり、当該プリント基板は、これらの周波数での放射ノイズを抑制することが必要であり、48MHzのノイズを抑制するためには0.01μFのコンデンサが、96MHzのノイズを抑制するためには2200pFのコンデンサが、144MHzのノイズを抑制するためには1000pFのコンデンサが有効であることより、これらを組み合わせた。

【0026】

LSIモデルボード、マザーボードに実装するコンデンサを表1のようにし、放射ノイズの評価を行った。コンデンサはノイズ周波数でトランスファー・インピーダンス(Z21)が高くなる、または低くなるように選択した。

【0027】

【表1】

【0028】

表2にノイズ周波数毎のZ21と基板端電圧を示す。

【0029】

【表2】

【0030】

Z21と基板端電圧には相関があり、クロック周波数(48MHz)とその高調波(96MHz、144MHz)が高インピーダンスとなる条件では、ノイズが大きくなり、Z21はノイズ伝播に寄与している。

【0031】

また、遠方界放射ノイズ測定結果より、表3および図4から11に示すように、Z21の増減傾向と放射ノイズレベルの増減傾向は一致する。

【0032】

【表3】

【0033】

プリント基板の放射ノイズを抑制するためには、LSIからプリント基板端までのトランスファー・インピーダンス(Z21)を低減し、さらにLSIのインピーダンスモデルと、プリント基板のインピーダンスモデルとを協調させることが効果的であり、得られるプリント基板は放射ノイズが低減されたプリント基板となる。

【符号の説明】

【0034】

1:プリント基板、2:マザーボード、3:LSIモデルボード、4:ノイズ源、5:大容量コンデンサ、6:チョークコイル、7:外部電源、8:グラウンド、9:電源

【特許請求の範囲】

【請求項1】

プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路のノイズ周波数と一致しないように制御されていることを特徴とするプリント基板。

【請求項2】

前記制御が、ノイズ源となる半導体集積回路からプリント基板端までのトランスファー・インピーダンスの低減によるものであることを特徴とする請求項1記載のプリント基板。

【請求項3】

前記トランスファー・インピーダンスの低減が、半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調して設計されたものであることを特徴とする請求項2記載のプリント基板。

【請求項4】

前記協調が、コンデンサの変更によるものであることを特徴とする請求項3記載のプリント基板。

【請求項5】

プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路のノイズ周波数と一致しないように制御することを特徴とする放射ノイズ抑制方法。

【請求項6】

前記制御が、ノイズ源となる半導体集積回路からプリント基板端までのトランスファー・インピーダンスを低減させて制御することを特徴とする請求項5記載の放射ノイズ抑制方法。

【請求項7】

半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調させて、前記トランスファー・インピーダンスを低減することを特徴とする請求項6記載の放射ノイズ抑制方法。

【請求項8】

前記協調が、コンデンサの変更によるものであることを特徴とする請求項7記載の放射ノイズ抑制方法。

【請求項1】

プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路のノイズ周波数と一致しないように制御されていることを特徴とするプリント基板。

【請求項2】

前記制御が、ノイズ源となる半導体集積回路からプリント基板端までのトランスファー・インピーダンスの低減によるものであることを特徴とする請求項1記載のプリント基板。

【請求項3】

前記トランスファー・インピーダンスの低減が、半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調して設計されたものであることを特徴とする請求項2記載のプリント基板。

【請求項4】

前記協調が、コンデンサの変更によるものであることを特徴とする請求項3記載のプリント基板。

【請求項5】

プリント基板上のコンデンサやプリント基板の寄生成分(インダクタンスおよびキャパシタンス)による反共振(高インピーダンス点)が半導体集積回路のノイズ周波数と一致しないように制御することを特徴とする放射ノイズ抑制方法。

【請求項6】

前記制御が、ノイズ源となる半導体集積回路からプリント基板端までのトランスファー・インピーダンスを低減させて制御することを特徴とする請求項5記載の放射ノイズ抑制方法。

【請求項7】

半導体集積回路のインピーダンスモデルと、前記プリント基板のインピーダンスモデルとを協調させて、前記トランスファー・インピーダンスを低減することを特徴とする請求項6記載の放射ノイズ抑制方法。

【請求項8】

前記協調が、コンデンサの変更によるものであることを特徴とする請求項7記載の放射ノイズ抑制方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−45856(P2013−45856A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2011−182077(P2011−182077)

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000100698)アイカ工業株式会社 (566)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成23年8月24日(2011.8.24)

【出願人】(000100698)アイカ工業株式会社 (566)

【Fターム(参考)】

[ Back to top ]