プログラマブルコントローラ

【課題】入出力ユニットの不用意な保守交換を防止することのできるプログラマブルコントローラを得る。

【解決手段】マイクロプロセッサ111と協働するシステムメモリ114A、シーケンスプログラムが外部ツール108を介して転送書込みされるプログラムメモリ115A、データメモリ116を有する基本ユニット110Aと、複数の入出力ユニット120、130、140、150とを備え、入出力ユニット120、130、140、150には、固体識別のための管理番号が付与されていて、運転前に基本ユニット110A内の管理情報格納領域199Aに転送保存されている。運転開始時に、管理番号の情報が変化していると運転停止されるので、入出力ユニット120、130、140、150を保守交換するときには、暗証番号を用いて管理番号の変更処理を行う。

【解決手段】マイクロプロセッサ111と協働するシステムメモリ114A、シーケンスプログラムが外部ツール108を介して転送書込みされるプログラムメモリ115A、データメモリ116を有する基本ユニット110Aと、複数の入出力ユニット120、130、140、150とを備え、入出力ユニット120、130、140、150には、固体識別のための管理番号が付与されていて、運転前に基本ユニット110A内の管理情報格納領域199Aに転送保存されている。運転開始時に、管理番号の情報が変化していると運転停止されるので、入出力ユニット120、130、140、150を保守交換するときには、暗証番号を用いて管理番号の変更処理を行う。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、マイクロプロセッサを内蔵した基本ユニットと、基本ユニットに対して着脱自在に接続される複数の入出力ユニットとによって構成されたプログラマブルコントローラにおいて、入出力ユニットのうちの入力ユニットに関連した操作および検出信号と、基本ユニット内のプログラムメモリに格納されたシーケンス制御プログラム(以下、「シーケンスプログラム」という)の内容とに応動して、入出力ユニットのうちの出力ユニットに接続された表示および駆動負荷を制御するプログラマブルコントローラに関し、特に入出力ユニットの保守管理を改善して安全性を向上させるための新規な技術に関するものである。

【背景技術】

【0002】

従来から、マイクロプロセッサを内蔵して、操作スイッチや各種センサなどの入力信号の動作状態と、プログラムメモリに格納されているシーケンスプログラムとに応動して、各種アクチェータや表示機器などの電気負荷の駆動制御を行うプログラマブルコントローラは、よく知られている。

【0003】

この種のプログラマブルコントローラにおいて、マイクロプロセッサおよび各種メモリを内蔵した基本ユニット(CPUユニット)と、入力インタフェース回路を内蔵した入力ユニットと、出力インタフェース回路を内蔵した出力ユニットと、からなる複数の入出力ユニットは、相互にバス接続された複数のコネクタを有するマザーボード台板上の各コネクタに接続されるか、または、各入出力ユニットが孤立筐体に収納されてフラットケーブルによって相互にバス接続されるなど、様々な構造形態のものが広く実用化されている。

【0004】

また、上記のような各種形態のプログラマブルコントローラにおいては、システム管理者以外のものが不用意にシーケンスプログラムを変更または盗用して、予定外の運転が行われないようにするために、様々なプログラム保護手段が提案されている。

【0005】

従来のプログラマブルコントローラにおいて、たとえば、プログラミング装置ごとの固有パスワードをパスワード登録部に登録しておき、作成したプログラムをプログラマブルコントローラに送る際のプログラム本体を含むプログラム格納コマンドに、固有パスワードを組み込むようにしたプログラミング方法が提案されている(たとえば、特許文献1参照)。

【0006】

上記特許文献1によれば、プログラマブルコントローラにおいては、プログラム格納処理部でプログラム番号とパスワードとの両方が一致した場合のみに、プログラム格納部の旧プログラムを新プログラムに書換え、プログラム番号が一致してもパスワードが異なる場合には書換えを禁止する。これにより、ユーザプログラムの使用者がシステムプログラムを変更できないようにするとともに、変更が必要な際には、システムプログラムの変更が容易となり、ハードおよびソフトが複雑化することなく、メモリの利用効率の悪化も回避するようにしている。

【0007】

一方、プログラマブルコントローラが使用されているか否かは別として、システム管理者以外の他者による消耗部品の交換を回避するための安全対策として、消耗部品にメモリを設けて管理する技術も提案されている(たとえば、特許文献2参照)。

【0008】

上記特許文献2に記載の印刷制御装置および印刷制御方法、プログラム、ならびに記憶媒体によれば、消耗部品情報取得部は、交換可能な消耗部品(トナーカートリッジ)の内部に設けられたメモリに格納されている所定情報(カートリッジ情報)を取得し、パラメータ切換部は、カートリッジ情報に基づいて、中間調変換部の中間調パラメータを選択して設定する。これにより、プリンタ制御ユニットにおける機能範囲を決定し、消耗部品を交換する際に不適切な消耗部品の場合には、印刷装置における機能範囲を制限して、消耗部品の誤使用を防止している。

【0009】

【特許文献1】特開平10−116108号公報(図1、要約)

【特許文献2】特開2003−015482号公報(図2、要約)

【発明の開示】

【発明が解決しようとする課題】

【0010】

従来のプログラマブルコントローラは、たとえば特許文献1のプログラミング方法の場合には、シーケンスプログラムの変更または盗用が防止されており、シーケンスプログラムが格納されている基本ユニットの保守交換を第3者が行うことができないようになっているものの、基本ユニットに対して着脱自在に接続される多数の入出力ユニットについては自由に交換することが可能であり、徹底した安全管理を行うことができないという課題があった。

【0011】

一方、特許文献2の印刷制御装置の場合には、限定された消耗部品がユーザによって交換可能となっているが、たとえ交換可能な消耗部品であっても、システム管理者以外の第3者による取替えを禁止したい場合に、単なる品種情報のみでは十分な禁止対策を実現することができないという課題があった。また、たとえば、新たに開発された異種の消耗部品が、既存の印刷制御装置の1つには適用可能であるものの、他の印刷制御装置には適用不可能な場合には、市場での混乱を招くという課題があった。

【0012】

この発明は、たとえ適用可能な入出力ユニットであっても、システム管理者以外の第3者による取替えを禁止し、システム管理者であれば容易に取替え交換を可能にしたプログラマブルコントローラを得ることを目的とする。

また、この発明は、適用可能な入出力ユニットであれば、システム管理者の許可のもとで、第3者が自由に取替え交換を行うことのできるプログラマブルコントローラを得ることを目的とする。

さらに、この発明は、運転開始前に入出力ユニットに対する局番設定を必要とする形式のものにおいて、局番設定操作と連動して入出力ユニットの交換可否を設定することのできるプログラマブルコントローラを得ることを目的とする。

【課題を解決するための手段】

【0013】

この発明によるプログラマブルコントローラは、マイクロプロセッサと、マイクロプロセッサと協働するシステムメモリと、外部で作成されたシーケンスプログラムが外部ツールを介して転送書込みされるプログラムメモリと、入出力情報および制御情報を記憶するデータメモリと、を有する基本ユニットと、基本ユニットを搭載した基本筐体または基本台板に共載されるか、もしくは、増設筐体または増設台板に延長接続されて、複数の制御信号線および複数ビットのデータバスを介して直列接続される複数の入出力ユニットと、を備え、複数の入出力ユニットは、外部入力センサまたは外部負荷に接続された入出力インタフェース回路を含み、入出力インタフェース回路は、マイクロプロセッサに対して選択的に交信接続されるように構成されたプログラマブルコントローラであって、システムメモリは、管理番号の初期保存手段、照合判定手段、編成異常処理手段および編成変更手段を構成する制御プログラムを含み、プログラムメモリおよびデータメモリの少なくとも一方には、管理情報格納領域が設けられ、管理情報格納領域には、操作対象者を限定する暗証番号の情報と、入出力ユニットを特定する管理番号の情報とが格納され、管理番号は、入出力ユニットに付与されて、マイクロプロセッサによって少なくとも読出しが可能な固体識別番号からなり、固体識別番号は、入出力ユニットが代替可能な同一品種であっても、複数の入出力ユニットごとに異なる番号からなり、初期保存手段は、入出力ユニットに格納されている管理番号と、管理情報格納領域に格納されている入出力ユニットの管理番号とを一致させておく手段からなり、照合判定手段は、少なくともプログラマブルコントローラの運転開始に際して、入出力ユニットに格納されている管理番号と、管理情報格納領域に格納されている入出力ユニットの管理番号とが一致しているか否かを判定する手段からなり、編成異常処理手段は、照合判定手段による判定結果が不一致を示す場合に機能して、プログラマブルコントローラの作動状態を停止または現状保持するか、異常状態であることを管理情報格納領域に書込み記憶するか、もしくは、少なくとも異常発生を警報表示する手段からなり、編成変更手段は、管理情報格納領域に対してあらかじめ書込み保存されている暗証番号と同じ暗証番号が、外部ツールから入力されたことに応答して機能し、初期保存手段によって既に記憶されている管理番号をクリアして、新たに初期保存処理を実行する手段からなるものである。

【発明の効果】

【0014】

この発明によれば、暗証番号によって管理されている基本ユニットと、基本ユニットに接続されて管理番号が付与されている入出力ユニットを備え、初期登録された編成が変化すると、暗証番号を用いた編成変更処理を行わなければ、プログラマブルコントローラの運転が禁止されるか警告表示が行われ、たとえ同一品種の入出力ユニットであってもエンドユーザによって不用意に入出力ユニットを保守交換することができず、暗証番号を知っているシステム管理者のみによって保守交換が行われるので、システムの安全性を向上させることができる。また、同一品種であっても仕様の異なる新型の入出力ユニットが、保守対象となったプログラマブルコントローラに適用可能か否かは、システム管理者によって判断されて使用されるので、市場でのバージョンアップ管理に混乱を招くことがないという効果がある。

【発明を実施するための最良の形態】

【0015】

実施の形態1.

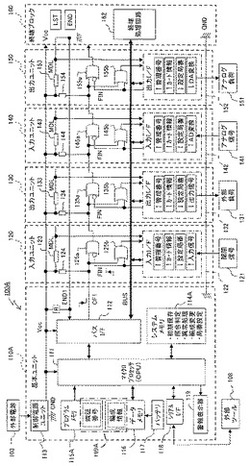

以下、図面を参照しながら、この発明の実施の形態1について詳細に説明する。図1はこの発明の実施の形態1に係るプログラマブルコントローラの全体構成を示すブロック図である。図1において、プログラマブルコントローラ100Aは、基本ユニット110Aと、複数の入出力ユニット120、130、140、150と、終端ブロック160と、により構成されている。ここでは、入力ユニット120、140と、出力ユニット130、150とを総称して、入出力ユニットという。

【0016】

基本ユニット110Aは、外部電源103(たとえば、AC100V〜240Vの商用電源)から給電されるとともに、脱着コネクタ(図示せず)を介して外部ツール108(たとえば、パーソナルコンピュータ)に接続されており、制御プログラムの書込みや運転状態の監視を行うことができるようになっている。

【0017】

基本ユニット110Aの内部には、主要部となるマイクロプロセッサ(CPU)111と、マイクロプロセッサ111に接続されたバスインタフェース回路112と、各部に電源を供給する制御電源ユニット113と、マイクロプロセッサ111に属するシステムメモリ114A(たとえば、マスクROMメモリまたはフラッシュメモリなどの不揮発メモリ)、プログラムメモリ115A(たとえば、不揮発フラッシュメモリ)およびデータメモリ116(たとえば、RAMメモリ)と、データメモリ116の一部領域をバックアップするバッテリ117(たとえば、リチウムバッテリ)と、マイクロプロセッサ111に接続されたシリアルインタフェース118および警報表示器119(たとえば、複数個の発光ダイオードまたはセブンセグメント表示器)と、が設けられている。

【0018】

基本ユニット110A内の上記構成要素のうち、マイクロプロセッサ111、バスインタフェース回路112、システムメモリ114A、プログラムメモリ115A、データメモリ116およびシリアルインタフェース118は、相互にバス接続されている。なお、制御電源ユニット113は、基本ユニット110Aの外部に設置することも可能であり、その場合、基本ユニット110Aは、外部の制御電源ユニット113とCPUユニットとによって構成されることになる。

【0019】

制御電源ユニット113は、外部電源103から給電され、入力信号回路(図示せず)に対して安定化電圧(たとえば、DC24V)を供給するとともに、定電圧電源線Vccに対して安定化電圧(たとえば、DC5V)を供給する。定電圧電源線Vccは、グランド回路GNDとともに各部に配線されている。

【0020】

システムメモリ114Aは、各種の制御プログラム(図2〜図7とともに後述する)を含むとともに、プログラムメモリ115Aに格納されたシーケンス言語によるシーケンスプログラムをマイクロプロセッサ111に対応した機械言語に変換してマイクロプロセッサ111を作動させるようになっており、製品の出荷段階でメーカによって格納されたプログラムを有している。

【0021】

プログラムメモリ115Aには、外部ツール108を用いてユーザによって作成されたシーケンスプログラムが、シリアルインタフェース118を介して書込まれている。プログラムメモリ115Aは、たとえば、ブロック単位で一括消去が可能な主ブロックおよび副ブロックを有するフラッシュメモリからなり、主ブロックには、シーケンスプログラムが転送格納されている。副ブロックは、管理情報格納領域199A(後述する)の一部を構成しており、暗証番号が格納されるようになっている。

【0022】

データメモリ116(RAMメモリ)は、入出力信号情報や、補助リレー、タイマ、カウンタおよびデータレジスタなどのデバイス(プログラマブルコントローラ100Aの内部のデバイスとなって、ユーザに開放されている)の作動状態が格納される。

【0023】

データメモリ116の一部の領域は、バッテリ117によってバックアップされており、プログラマブルコントローラ100Aに対する電源が遮断されても、記憶状態が保持されるようになっている。また、データメモリ116のバッテリバックアップ領域のさらに一部の領域は、管理情報格納領域199Aとして使用され、管理情報格納領域199Aには、入出力ユニットの管理番号の情報(後述する編成情報)が格納されるようになっている。

【0024】

なお、プログラムメモリ115Aは、バッテリバックアップされたRAMメモリであってもよく、フラッシュメモリまたはEPROMなどによる不揮発メモリを内蔵したメモリカセットを装着することによって、プログラムメモリ領域を不揮発メモリ化することも可能である。警報表示器119は、マイクロプロセッサ111の作動状態、すなわち、電源の到来、正常運転状態、各種異常発生状態などを表示するようになっている。

【0025】

接続確認信号END1の伝送線は、プルアップ抵抗Rを介して定電圧電源線Vccに接続されるとともに、入出力ユニット120、130、140、150を貫通して、終端ブロック160の終端処理確認回路ENDによってグランド回路GNDに接続されている。接続確認信号END1は、論理レベル「L」(ロウ)となることによって、終端ブロック160が装着されたことを認識するための信号であり、バスインタフェース回路112を介してマイクロプロセッサ111に入力されている。

【0026】

貫通バス信号線BUSは、たとえば16ビットのデータバスおよび各種の制御信号線を含み、バスインタフェース回路112から入出力ユニット120、130、140、150を貫通して、終端ブロック160に至る多数の信号配線を構成している。

【0027】

マイクロプロセッサ111は、バスインタフェース回路112を介して局番設定検索信号CF1を発生する。局番設定検索信号CF1は、局番設定処理を実行する場合に、論理レベル「L」となり、初段の入出力ユニット(入力ユニット120)に局番設定指令を供給するようになっている。

【0028】

入力ユニット120は、コネクタ(図示せず)を介して基本ユニット110Aの端面位置に接続されており、入力ユニット120には、入力端子台(図示せず)を介して、外部の開閉信号121が入力されている。開閉信号121は、たとえば操作盤に設けられた各種の操作スイッチや、アクチェータの動作を確認するためのセンサスイッチから生成される。1台の入力ユニット120には、たとえば8点の入力信号が接続可能であるが、さらに多くの開閉信号121が接続される場合には、入力ユニット120の接続台数が増設されるようになっている。

【0029】

入力ユニット120は、入力インタフェース回路122と、プルアップ抵抗123、124と、選択切換回路125a、125bと、により構成されている。入力インタフェース回路122は、データセレクタを介して開閉信号121(入力信号)を貫通バス信号線BUSに接続する入力信号回路と、カード情報格納メモリと、局番設定メモリと、管理番号格納メモリと、を有する。

【0030】

出力ユニット130は、出力インタフェース回路132と、プルアップ抵抗133、134と、選択切換回路135a、135bと、により構成されている。出力インタフェース回路132は、出力信号回路が異なる点を除けば、入力インタフェース回路122と同様の構成を有し、外部負荷131に接続されている。

【0031】

入力ユニット140は、入力インタフェース回路142と、プルアップ抵抗143、144と、選択切換回路145a、145bと、により構成されている。入力インタフェース回路142は、アナログ信号141(入力信号)をデジタル変換するAD変換器が異なる点を除けば、入力インタフェース回路122と同様の構成を有する。

【0032】

出力ユニット150は、出力インタフェース回路152と、プルアップ抵抗153、154と、選択切換回路155a、155bと、により構成されている。出力インタフェース回路152は、DA変換器が異なる点を除けば、出力インタフェース回路132と同様の構成を有し、アナログ負荷151に接続されている。

ここでは、入力インタフェース回路122、142と、出力インタフェース回路132、152とを総称して、入出力インタフェース回路という。

【0033】

入力ユニット120内において、プルアップ抵抗123の一端は、定電圧電源線Vcc(たとえば、DC5V)に接続されている。プルアップ抵抗123の他端は、入力インタフェース回路122内のカード情報格納メモリに接続されており、カード情報格納メモリに、接続位置信号MDLを供給して接続位置論理情報として記憶するようになっている。

【0034】

なお、終端ブロック160に接続される最終段の出力ユニット150の場合には、プルアップ抵抗153の他端が、終端ブロック160内の接続位置確認回路LSTによってグランド回路GNDに接続されており、接続位置信号(接続位置論理情報)MDLが、論理レベル「L」となるように構成されている。これに対し、中間位置にある他の入出力ユニット120、130、140の場合には、接続位置信号MDLは、論理レベル「H」(ハイ)となっている。

【0035】

一対の論理和素子からなる選択切換回路125a、125bにおいて、それぞれの第1の入力端子は、プルアップ抵抗124に接続されており、プルアップ抵抗124を介して常時は論理レベル「H」に設定されている。一方の選択切換回路125aの第2の入力端子には、入力インタフェース回路122内のカード情報格納メモリに格納されている局番設定完了信号(個別完了論理情報)FINの反転論理信号が入力され、他方の選択切換回路125bの第2の入力端子には、カード情報格納メモリに格納されている局番設定完了信号FINがそのまま入力されている。局番設定完了信号FINは、局番設定が完了していると、論理レベル「H」となる。

【0036】

局番設定検索信号CF1は、選択切換回路125a、125bのそれぞれの第1の入力端子に印加されており、局番設定を行うために局番設定検索信号CF1を論理レベル「L」とした場合に、たとえば入力ユニット120の局番設定が未完了であれば、選択切換回路125bの出力が論理レベル「L」となって、入力ユニット120がマイクロプロセッサ111との交信権を得ることになる。

【0037】

マイクロプロセッサ111との交信権を取得した入出力ユニットは、貫通バス信号線BUSを介して、マイクロプロセッサ111に対してカード情報や管理番号の情報を送信する。また、カード情報および管理番号の情報を受信したマイクロプロセッサ111は、次のタイミングで設定された局番情報(以下、「設定局番」ともいう)の値を、貫通バス信号線BUSを介して送信し、設定局番に該当する入出力ユニットの入力インタフェース回路内の局番設定メモリに書込む。

【0038】

続いて、マイクロプロセッサ111により設定局番が書き込まれた入出力ユニットは、書込み設定された局番情報を、マイクロプロセッサ111に対して確認返信する。これにより、マイクロプロセッサ111から局番設定完了信号FINが送信され、該当する入出力ユニットは、局番設定完了信号FINをカード情報として記憶する。

【0039】

初段の入力ユニット120の局番設定が完了すると、選択切換回路125aの第2の入力は、論理レベル「L」となり、局番設定検索信号CF1の論理レベル「L」が次段の選択切換回路135a、135bの第1の入力端子に印加される。以下、同様にして、局番設定の順次処理が実行されることになる。

【0040】

出力ユニット130は、コネクタ(図示せず)を介して入力ユニット120の端面位置に接続されており、出力ユニット130には、出力端子台(図示せず)を介して、外部負荷131が接続されている。外部負荷131は、たとえば、操作盤に設けられた各種の表示ランプ、アクチェータ駆動用の電磁弁、または、モータ駆動用の電磁継電器などからなる。1台の出力ユニット130には、たとえば8点の出力信号が接続可能であるが、さらに多くの外部負荷131が接続される場合には、出力ユニット130の接続台数が増設されるようになっている。

【0041】

出力ユニット130内において、出力インタフェース回路132は、外部負荷131を駆動するための駆動信号のラッチメモリを貫通バス信号線BUSに接続する出力信号回路と、カード情報格納メモリと、局番設定メモリと、管理番号格納メモリと、を有する。プルアップ抵抗133、134および選択切換回路135a、135bは、入力ブロック120の場合と同様に構成されている。

【0042】

入力ユニット140には、たとえば4点のアナログ信号141が入力されている。入力ユニット140内において、入力インタフェース回路142内の多チャンネルAD変換器は、アナログ信号141をデジタル変換し、4チャンネルのアナログ入力に対する各12ビットのデジタル変換データをマイクロプロセッサ111に送信するようになっている。

【0043】

出力ユニット150には、たとえば4点のアナログ負荷151が接続されている。出力ユニット150内において、出力インタフェース回路152内の多チャンネルDA変換器は、マイクロプロセッサ111から送信された4チャンネル12ビットのデジタルデータをアナログ変換し、変換後のアナログ信号をアナログ負荷151に供給するようになっている。

【0044】

入出力ユニット140、150の内部にも、入出力ユニット120、130の場合と同様に、カード情報格納メモリ、局番設定メモリおよび管理番号格納メモリを有する入出力インタフェース回路142、152が設けられている。また、プルアップ抵抗143、144、153、154、および、選択切換回路145a、145b、155a、155bは、それぞれ入出力ユニット120、130の場合と同様に構成されている。

【0045】

最終段の入出力ユニット(出力ユニット150)に接続された終端ブロック160は、貫通バス信号線BUSの末端位置に接続された終端処理回路162を備えている。終端処理回路162は、高速信号の反射防止用のインピーダンス素子を、グランド回路GNDまたは定電圧電源線Vccに対して接続するためのプルダウン回路またはプルアップ回路により構成されている。

【0046】

終端ブロック160内の接続位置確認回路LSTは、最終段に接続された出力ユニット150内のプルアップ抵抗153の他端を、終端ブロック160内でグランド回路GNDに接続して論理反転させる回路を構成している。なお、プルアップ抵抗123、133、143、153をプルダウン抵抗に変更し、終端ブロック160内で定電圧電源線Vccに接続して論理反転させるようにしてもよい。

【0047】

終端ブロック160内の終端処理確認回路ENDは、ロウレベルの論理発生回路を構成しており、終端ブロック160が接続されていることを示すロウレベルの接続確認信号END1を生成し、各入出力ユニット120〜150を貫通してマイクロプロセッサ111に伝達する。なお、接続確認信号END1の伝送線に設けられたプルアップ抵抗Rをプルダウン抵抗に変更し、終端ブロック160内の終端処理確認回路ENDにおいて、定電圧電源線Vccに接続することにより、ハイレベルの論理信号を与えるようにしてもよい。

【0048】

入出力ユニット120〜150内のカード情報格納メモリに格納されるカード情報は、少なくとも、入出力インタフェース回路122〜152が入力インタフェース回路であるかまたは出力インタフェース回路であるかを識別する品種別論理情報と、局番設定処理が完了しているか否かの設定状態を識別する局番設定完了信号(個別完了論理情報)FINと、入出力インタフェース回路122〜152の接続位置が最終接続位置であるか、または最終接続位置以外の中間接続位置であるかを識別する接続位置信号(接続位置論理情報)MDLと、を含む。

【0049】

なお、品種別論理情報としては、ON/OFF信号(開閉信号121、外部負荷131)用の入出力ユニットであるか否か、アナログ(アナログ信号141、アナログ負荷151)用の入出力ユニットであるか否か、の識別信号も付加されている。たとえば、アナログ用の入出力ユニットである場合には、マイクロプロセッサ111と多チャンネルAD変換器または多チャンネルDA変換器との間で、複数回の読出しまたは書込み操作が行われるようになっている。

【0050】

また、ON/OFF信号用の入出力ユニットである場合も、大小2種類(16点単位、8点単位)の入出力ユニットがあるので、8点単位のものか、または16点単位のものかを識別する信号も付加されている。また、入出力各8点の混合入出力ユニットが適用されてもよいが、いずれの場合も、たとえば入力8点、または出力8点当たりで1つの局番が割り振られるようになっている。

【0051】

また、アナログ信号用の入出力ユニットである場合も、大小2種類(8点単位、4点単位)の入出力ユニットがあるので、4点単位、8点単位、または、入力4点かつ出力4点の混合タイプなどに応じて、異なる品種別論理情報が与えられるようになっている。

【0052】

また、局番は、たとえば、アナログ4点単位で1つの局番が割り振られるようになっている。各種の品種別論理情報は、データバスに対して接続または解放するために設けられたデータセレクタの複数ビットの入力端子を、プリント基板によってグランド回路GNDに接続するか、または定電圧電源線Vccに接続するか、によって決定される配線パターン情報となっている。品種別論理情報の記憶手段は、ここでは総称として個別メモリとしているが、実際には読出しおよび書込みの行えるメモリが使用されなくてもよい。

【0053】

貫通バス信号線BUSは、必要時に入出力インタフェース回路122〜152に対する局番指定用のアドレスバスとして使用され、また、必要時にカード情報や管理番号の情報を読出すか、外部からの入力信号を読出すための読出し用のデータバスとして使用され、さらに、局番設定信号や外部負荷131に対する制御出力データを書込むための書込み用のデータバスとして使用される。

【0054】

上記の貫通バス信号線BUSの使い分けは、マイクロプロセッサ111が発生するコマンドデータに依存して決定される。また、多数の入出力情報を有するアナログ用の入出力インタフェース回路142、152に対しては、複数回の交信によって全データの転送が行われ、読み書きの実行タイミングは、マイクロプロセッサ111が発生する制御信号(タイミング信号)に基づいて決定される。

【0055】

以上の説明では、ON/OFF入出力の場合には、入力8点または出力8点に対して1つの局番を付与し、アナログ入出力の場合には、入力4チャンネルまたは出力4チャンネルに対して1つの局番を付与したが、これは単なる一例であって、さらに多い入出力点数や入出力チャンネルのものに対して、または、入出力混合のものに対して1つの局番を付与する仕様としてもよい。

【0056】

この発明の実施の形態1に係るプログラマブルコントローラ100Aにおいて、入出力ユニット120、130、140、150には、固体識別のための管理番号が付与されており、各管理番号は、運転前に、基本ユニット110A内の管理情報格納領域199Aに転送保存されている。運転開始時に、管理番号の情報が変化していると運転停止されるので、入出力ユニット120、130、140、150を保守交換する場合には、暗証番号を用いて管理番号の変更処理が行われる。これにより、入出力ユニット120、130、140、150の不用意な保守交換を防止することのできるプログラマブルコントローラ100Aが得られる。

【0057】

次に、図2〜図7のフローチャートを参照しながら、図1に示したこの発明の実施の形態1による動作について詳細に説明する。図2はプログラマブルコントローラ100Aの運転(RUN)動作を示している。

【0058】

図2において、ステップ205、206は、第1および第2の管理忌避手段に対応し、ステップ207aは照合判定手段に対応し、ステップ208、209bは、編成異常検出手段および編成異常処理手段に対応し、ステップ213a、213bは、それぞれ脱落異常検出手段に対応している。

【0059】

まず、電源スイッチ(図示せず)が投入されて(ステップ200)、外部電源103からプログラマブルコントローラ100Aに給電されると、マイクロプロセッサ111が動作を開始し(ステップ201)、マイクロプロセッサ111は、現場のオペレータの操作によるRUN/STOP(運転/停止)指令入力(図示せず)の状態を参照して、RUN入力の有無を判定する(ステップ202a)。

【0060】

ステップ202aにおいて、RUNスイッチが閉路(ON)されていてRUN入力有り(すなわち、YES)と判定されれば、続いて、プログラマブルコントローラ100Aの運転準備が完了しているか否かを判定し(ステップ203a)、準備完了している(すなわち、YES)と判定されればステップ204に移行し、また、準備完了していない(すなわち、NO)と判定されればステップ203bに移行する。

【0061】

ステップ203aにおいては、準備完了か否かを判定する。具体的には、ステップ314(図4とともに後述する)によって編成完了フラグのセット状態(編成記憶完了を示す)が管理情報格納領域199Aに格納されているか否かを判定する。または、ステップ502(図7とともに後述する)によってシーケンスプログラムがプログラムメモリ115Aに格納され、代表としてEND命令が書込まれているか否かを判定する。これにより、編成完了フラグがセットされ、かつEND命令が書込まれていれば、準備完了と判定することができる。

【0062】

一方、ステップ202aにおいて、RUNスイッチが開路(OFF)されていてSTOPモードである(すなわち、NO)と判定されれば、ステップ209a(後述する)でセットされた初回フラグをリセットし(ステップ202b)、中継端子Aを介して、図4内のステップ301に移行する。

【0063】

ステップ203aに続くステップ203bにおいては、準備未完了状態であることを警報表示器119によって表示し、動作終了ステップ210に移行する。動作終了ステップ210において、マイクロプロセッサ111は、他の制御動作を実行して、所定時間以内に動作開始処理(ステップ201)に復帰移行し、循環動作する。

【0064】

つまり、準備完了していない状態で、RUNスイッチが閉路(ON)されると、ステップ201、202a、203a、203b、210、201が循環動作して、RUNスイッチが開路(OFF)されるのを待機する状態となり、RUNスイッチが開路(OFF)されたことによって、図4内のステップ301に移行するようになっている。

【0065】

ステップ204においては、RUNモードでの初回動作であるか否かを判定する。具体的には、ステップ209aによって初回フラグがセットされているか否かを監視することによって、RUNモードでの初回動作であるか否かを判定する。もし、初回動作である(すなわち、YES)と判定されればステップ205に移行し、初回動作でない(すなわち、NO)と判定されれば、ステップ211(後述する)に移行する。

【0066】

ステップ205においては、暗証番号の有無を判定する。具体的には、ステップ554a(図6とともに後述する)で暗証番号が入力されて管理情報格納領域199Aに格納されているか否かにより、暗証番号の有無を判定する。もし、暗証番号が有り(すなわち、YES)と判定されればステップ206に移行し、暗証番号が格納されていない(すなわち、NO)と判定されればステップ207bに移行する。

【0067】

ステップ206においては、管理番号による管理の要否を判定する。具体的には、ステップ358b(図3とともに後述する)によって管理番号による管理が必要であるとの編成指令が送信されて、編成指令が管理情報格納領域199Aに格納されているか否かにより、管理の要否を判定する。もし、管理が必要である(すなわち、YES)と判定されればステップ207aに移行し、管理が不要である(すなわち、NO)と判定されれば、ステップ207bに移行する。

【0068】

ステップ207aにおいては、現在のカード編成状態を読出し、管理および編成を確認する。このとき、マイクロプロセッサ111は、既に設定完了している局番を指定し、これに応答して指定された局番の入出力ユニットが自分のカード情報および管理番号の情報をマイクロプロセッサ111に送信する。これにより、管理番号を含むカード編成を確認することができる。

【0069】

ステップ207bにおいては、現在のカード編成状態を読出して確認する。具体的には、基本ユニット110A内のマイクロプロセッサ111は、既に設定完了している局番を指定し、これに応答して、指定された局番の入出力ユニットは、自分のカード情報をマイクロプロセッサ111に送信する。これにより、マイクロプロセッサ111は、管理番号を除外したカード編成を確認することができる。

【0070】

続いて、ステップ313(図4とともに後述する)で記憶されたカード編成情報と、ステップ207aまたは207bによって確認された現在のカード編成状態とを比較し、比較結果が不一致であるか否かにより編成が異常であるか否かを判定する(ステップ208)。ステップ208における比較結果が不一致であって編成が異常である(すなわち、YES)と判定されれば、ステップ209bに移行し、比較結果が一致であって編成が正常(すなわち、NO)と判定されれば、ステップ213aに移行する。

【0071】

ステップ209bにおいては、カード編成異常の発生をデータメモリ116に書込み記憶するとともに、異常表示LEDからなる警報表示器119を点滅表示して異常報知を行い、さらに、出力ユニット130、150の出力発生を停止状態(または、現状保持状態)にして、動作終了ステップ210に移行する。なお、ステップ209bにおいて、出力ユニット130、150の出力停止状態または現状保持状態の選択は、データメモリ115Aに対してあらかじめ選択パラメータを設定しておくことによって決定される。

【0072】

一方、ステップ213aにおいて、マイクロプロセッサ111は、接続確認信号END1の論理レベルを判定することにより、入出力ユニット120、130、140、150および終端ブロック160が正常に接続されている(終端OK)か否かを判定する。

【0073】

ステップ213aにおいて、接続確認信号END1の論理レベルが「H」であって異常状態である(すなわち、NO)と判定されれば、ステップ209bに移行し、論理レベルが「L」であって正常である(すなわち、YES)と判定されれば、初回フラグをセットして(ステップ209a)、後述する入力処理(ステップ215)に移行する。

【0074】

一方、ステップ204により初回動作でない(すなわち、NO)と判定された場合に実行されるステップ211においては、図7内のステップ502によりプログラムメモリ115Aに書込まれたシーケンスプログラムを実行する。

【0075】

続いて、上記シーケンスプログラムの中にあるEND命令が実行されたか否かを判定し(ステップ212)、END命令が実行されていない(すなわち、NO)と判定されれば、ステップ211に復帰してEND命令が実行されるまでステップ211を繰り返し循環実行する。そして、ステップ212において、END命令が実行された(すなわち、YES)と判定されれば、次の判定処理(ステップ213b)に移行する。

【0076】

つまり、ステップ211、212により一巡のシーケンスプログラムが実行された後、続いて、接続確認信号END1の論理レベルを判定することにより、入出力ユニット120、130、140、150および終端ブロック160が正常に接続されている(終端OK)か否かを判定する(ステップ213b)。

【0077】

ステップ213bにおいて、接続確認信号END1の論理レベルが「H」であって異常状態である(すなわち、NO)と判定されれば、前述のステップ209bに移行し、論理レベルが「L」であって正常である(すなわち、YES)と判定されれば、ステップ211によるシーケンスプログラムの実行結果として、出力ユニット130、150に対する制御出力信号の書込み(出力処理)を実行する(ステップ214)。

【0078】

最後に、ステップ214に続いて、また、前述の初回フラグのセット(ステップ209a)に続いて、入力処理(ステップ215)が実行され、マイクロプロセッサ111は、入力ユニット120、140から入力信号を読出して、データメモリ116に転送する。以下、ステップ202aに復帰し、RUN/STOPスイッチがRUN状態を維持していて、準備完了(すなわち、YES)と判定されれば、ステップ204を経て、再びシーケンスプログラムの実行(ステップ211)が繰り返される。

【0079】

なお、ステップ214における出力信号の書込み、ならびに、ステップ215における入力信号の読出しに際しては、マイクロプロセッサ111によって指定された局番と一致する設定局番を有する入出力ユニットが、マイクロプロセッサ111との交信権を取得するようになっている。

【0080】

以上の動作を整理して概括説明すると、ステップ205は、第1の管理忌避手段として機能し、暗証番号が入力されていないときには管理番号の照合を行わないようにする。また、ステップ206は、第2の管理忌避手段として機能し、ステップ554aによって暗証番号が入力されていても、ステップ358aによって管理番号の照合を行わない編成指令が与えられているときには、ステップ207bによって管理番号を除外したカード編成のみをチェックする。

【0081】

ステップ207a、207bは、照合判定手段として機能し、ステップ358bによって管理番号が必要であるとして編成指令が出されたときに、管理番号およびカード編成情報の両方について、現在の状態とステップ313によって編成記憶されたときの状態とを比較判定する。

【0082】

ステップ208は、ステップ207a、207b(照合判定手段)と関連した編成異常検出手段として機能し、ステップ207aまたはステップ207bによる確認結果に異常があるか否かを検出し、入出力インタフェース回路122、132、142、152から得られるカード情報および管理番号の情報の現在状態が、カード編成記憶手段(ステップ313)に記憶されているカード情報および管理番号と一致しているか否かを判定する。

【0083】

ステップ209bは、編成異常処理手段として機能し、編成異常検出手段(ステップ208)が編成異常を検出した場合、または、脱落異常検出手段(ステップ213a、213b)によって終端異常が検出された場合に機能して、異常状態をデータメモリ116に書込み記憶するとともに、異常発生を警報表示器119に表示させ、制御出力を停止状態または現状保持状態にする。

【0084】

ステップ213aは、第1の異常判定手段または脱落異常検出手段として機能し、運転開始時に実行されて、終端ブロック160が未接続であるか、接続されていてもコネクタの接触不良などによって接続確認信号END1が論理レベル「L」にならないときに、終端処理未完了の判定を行う。ステップ213bは、第1の異常判定手段として機能し、運転中に実行される。

【0085】

次に、図1とともに、図3および図4のフローチャートを参照しながら、この発明の実施の形態1による編成操作について説明する。図3のフローチャートは、基本ユニット110Aに接続された外部ツール108の動作を示し、図4のフローチャートは、図2内の中継端子Aに続くマイクロプロセッサ111の動作を示している。

【0086】

なお、マイクロプロセッサ111と外部ツール108との間では、シリアルインタフェース118を介して交信が行われており、一方が送信して他方が受信すると、受信確認の返信が行われ、送信指令内容が受信側で実行されると、実行確認返信が行われるようになっているが、図3および図4においては、簡略化のため、両者の連携動作については図示を省略する。

【0087】

図3において、まず、外部ツール108が接続されたことによって、外部ツール108内のマイクロプロセッサ(図示せず)が動作を開始し(ステップ350)、暗証番号の有無(暗証番号が登録されているか否か)を検索判定して(ステップ351)、暗証番号が登録されている(すなわち、YES)と判定されれば、ステップ352に移行し、暗証番号が登録されていない(すなわち、NO)と判定されれば、ステップ354に移行する。

【0088】

ステップ352においては、マイクロプロセッサ111との間の暗証番号の入力処理により確認送信が行われる。続いて、マイクロプロセッサ111に既に登録されていた暗証番号と、ステップ352で外部ツール108から入力された暗証番号とが一致しているか否かを判定し(ステップ353)、両者が一致している(すなわち、YES)と判定されれば、ステップ354に移行し、不一致である(すなわち、NO)と判定されれば、ステップ359に移行する。なお、暗証番号の照合判定処理は、外部ツール108側で実行されてもよいが、実際には、基本ユニット110A側で実行され、判定結果を外部ツール108に返信するようになっている。

【0089】

ステップ354において、外部ツール108は、基本ユニット110Aの管理情報格納領域199Aの内容を読出す。続いて、ステップ354の読出し結果に応じて、編成完了フラグがセットされていた(編成が完了)か否かを判定し(ステップ355a)、編成完了(すなわち、YES)と判定されれば、ステップ356に移行し、編成未完了(すなわち、NO)と判定されれば、ステップ357に移行する。

【0090】

ステップ356においては、画面表示された編成変更要否のボタンのうち、どちらかがオペレータによって選択されることに応答して、編成変更が必要であるか否かを判定し、編成変更が必要である(すなわち、YES)と判定されれば、ステップ357に移行し、編成変更が必要でない(すなわち、NO)と判定されれば、中継端子Xを経由して、図6内のステップ550に移行する。

【0091】

ステップ357においては、管理番号の要否を決定する選択ボタンの画面表示が行われ、オペレータが管理番号の要否を決定してどちらかのボタンを押すことに応答して、管理番号が必要であるか否かを判定し、管理番号が必要でない(すなわち、NO)と判定されれば、ステップ358aに移行し、管理番号が必要である(すなわち、YES)と判定されれば、ステップ358bに移行する。

【0092】

ステップ358aにおいては、管理番号による管理を行わない場合の編成指令を送信し、ステップ355bに移行する。また、ステップ358bにおいては、管理番号による管理を行う場合の編成指令を送信し、ステップ355bに移行する。なお、ステップ358a、358bにおいては、それぞれ編成指令が送信されるとともに、ステップ314(図4とともに後述する)でセットされていた編成完了フラグがリセットされる。

【0093】

ステップ355bにおいては、ステップ358a、358bでリセットされた編成完了フラグが、後述のステップ314によって再度セットされるか否かを監視して、編成が完了したか否かを判定し、編成完了フラグのセットが未完了(すなわち、NO)と判定されれば、ステップ357に復帰する。

【0094】

また、ステップ355bにおいて、既に選択されているステップ358aまたはステップ358bが引き続き送信されて、ステップ314によって編成完了フラグがセットされている(すなわち、YES)と判定されれば、中継端子Xを介して図6内のステップ550に移行する。

【0095】

一方、ステップ353で暗証番号の不一致が判定された場合に実行されるステップ359においては、外部ツール108に対して異常表示が行われ、動作終了ステップ460に移行する。このとき、所定時間内に、再度、動作開始ステップ350に復帰移行するようになっている。なお、オペレータは、ステップ359による異常表示画面に応じて、暗証番号の再入力を行うか、または、暗証番号が不明な場合には、全データの消去処理を行う。

【0096】

図4の処理ルーチンは、図2内のステップ202bに続いて実行される。図4において、ステップ210は、前述(図2参照)と同様の動作終了処理である。ステップ302は、編成変更手段を構成し、ステップ303は、第1の異常判定手段を構成し、ステップ304は、設定異常処理手段を構成し、ステップ310は、第3の異常判定手段を構成し、ステップ313は、カード編成記憶手段を構成している。また、ステップ210、304、305、310、311a、311b、312、400は、局番設定手段を構成している。

【0097】

図4において、まず、マイクロプロセッサ111は、ステップ314(後述する)で編成完了フラグがセットされたか否かにより、編成記憶が完了しているか否かを判定する(ステップ301)。なお、初回動作においては、編成記憶が完了していない(すなわち、NO)と判定されて、ステップ303に移行し、次回動作においては、編成完了フラグがセットされている(すなわち、YES)と判定されて、ステップ302に移行する。

【0098】

ステップ302においては、ステップ358aまたはステップ358bによる編成指令を受信したか否かを判定し、受信している(すなわち、YES)と判定されれば、ステップ303に移行し、編成指令を受信していない(すなわち、NO)と判定されれば、中継端子Bを介して図7内のステップ500に移行する。

【0099】

ステップ303においては、接続確認信号END1の論理レベルに応じて、終端ブロック160が接続されている(終端処理が完了)か否かを判定し、終端ブロック160が接続されていて接続確認信号END1の論理レベルが「L」であり、終端処理が完了している(すなわち、YES)と判定されれば、ステップ305に移行する。

【0100】

また、ステップ303において、終端ブロック160が接続されていないか、またはコネクタの接触不良によって一部の入出力ユニットが脱落状態となり、接続確認信号END1の論理レベルが「H」となって、終端処理が完了していない(すなわち、NO)と判定されれば、ステップ304に移行する。

【0101】

ステップ304においては、異常状態をデータメモリ116に記憶するとともに、警報表示器119の異常表示LEDを点滅表示して異常報知し、動作終了ステップ210に移行する。動作終了ステップ210において、マイクロプロセッサ111は、他の制御動作を実行した後、図2内の動作開始ステップ201に移行する。

【0102】

したがって、ステップ303において、終端ブロック160が未接続(すなわち、NO)と判定された場合には、図2および図3内のステップ201、202a、202b、301、303、304、210、201を循環動作して異常警報が持続し、この状態を脱出するためには、電源スイッチ(図示せず)を開路する必要がある。

【0103】

ステップ305においては、図3内のステップ358aまたはステップ358bによる編成指令を受信しているか否かを判定し、受信していない(すなわち、NO)と判定されれば、ステップ305に復帰して編成指令の待機動作を行い、編成指令を受信した(すなわち、YES)と判定されれば、ステップ400に移行して局番設定処理(図5とともに後述する)を実行した後、ステップ310に移行する。

【0104】

ステップ310においては、図5内のステップ414bで受信した局番情報および管理番号の情報が、ステップ413a(図5参照)で送信した設定局番やステップ404(図5参照)で読出した管理番号と一致しているか否かにより、局番情報および管理番号の情報が正常であるか否かを判定する。ステップ310において、各情報が相互に一致していて正常である(すなわち、YES)と判定されれば、ステップ311aに移行し、相互に不一致であって正常でない(すなわち、NO)と判定されれば、ステップ304に移行する。

【0105】

ステップ311aにおいて、マイクロプロセッサ111は、ステップ310による局番設定の対象となった入出力ユニットに対して、各ユニットに関する局番設定が完了したことを個別完了論理情報として送信する。また、ステップ311bにおいて、個別完了論理情報を受信した入出力ユニットは、カード情報の1つである局番設定完了信号FINの論理レベルを「H」にする。

【0106】

ステップ311aに続いて、マイクロプロセッサ111は、図5内のステップ412による最終位置記憶の有無によってすべての局番設定が完了したか否かを判定し(ステップ312)、全体の局番設定が未完了である(すなわち、NO)と判定されれば、ステップ305に復帰して引き続き局番設定処理を実行し、すべての局番設定が完了している(すなわち、YES)と判定されれば、ステップ313に移行する。

【0107】

ステップ313においては、設定された局番情報(設定局番)、カード情報および管理番号の情報の対応を、カード編成情報として記憶して、ステップ314に移行する。ステップ314においては、編成完了フラグをセットして、動作終了ステップ210に移行し、所定時間以内に、引き続いて動作開始ステップ201に移行するようになっている。なお、ステップ314でセットされる編成完了フラグは、管理情報格納領域199Aに格納されるので、プログラマブルコントローラ100Aの電源が遮断されても、記憶情報として保存される。

【0108】

以上の動作を整理して概括説明すると、ステップ302は、編成変更手段として機能し、既に設定されている編成情報を変更する。また、ステップ303は、第1の異常判定手段として機能し、局番設定手段320の実行前に終端処理未完了を判定し、終端ブロック160が未接続であるか、接続されていてもコネクタの接触不良などによって接続確認信号END1が論理レベル「L」にならないときに、終端処理未完了と判定する。

【0109】

ステップ304は、設定異常処理手段として機能し、第1または第3の異常判定手段(ステップ303、310)が異常を検出したときに機能して、異常状態をデータメモリ116に書込み記憶するとともに、警報表示器119により異常発生を警報表示する。

【0110】

ステップ310は、第3の異常判定手段として機能し、マイクロプロセッサ111が送信した局番情報や読出済みの管理番号の情報に対して、確認返信された設定局番や管理番号が不一致であるときに、異常状態であることを判定する。

【0111】

ステップ313は、カード編成記憶手段として機能し、局番設定の完了時に、管理番号の情報とカード情報と局番情報(設定局番)との対応状態を、管理情報格納領域199Aに書込み記憶する。局番設定手段320(ステップ305〜312)による局番設定動作は、電源投入後の初回動作で実行される。

【0112】

なお、暗証番号が未登録であっても、図4内のステップ354、355a、356からステップ357に移行することによって編成指令を発生することはできるが、一旦、暗証番号が登録されると、ステップ353によって暗証番号の一致確認が行われなければ、編成変更が行えないようになっている。

【0113】

次に、図5のフローチャートを参照しながら、図4内の局番設定処理(ステップ400)について詳細に説明する。図5において、ステップ404は、初期保存手段を構成し、ステップ406は、第2の異常判定手段を構成し、ステップ407は、設定異常処理手段を構成している。また、ステップ413b、414a(破線ブロック参照)は、入出力ユニット120〜150の動作を示している。

【0114】

まず、マイクロプロセッサ111は、図4内のステップ305の判定結果が「YES」の場合に、図5のサブルーチンの動作を開始する(ステップ401)。続いて、マイクロプロセッサ111は、局番設定検索信号CF1の論理レベルを「H」から「L」に切換えて送出し、局番設定を開始する(ステップ402)。

【0115】

このとき、局番設定検索信号CF1が論理レベル「L」となったことにより、各入出力ユニット120〜150内の選択切換回路125b、135b、145b、155bのうち、まずは選択切換回路125bの出力が論理レベル「L」となって、入力ユニット120がマイクロプロセッサ111との交信権を得ることになる。

【0116】

続いて、ステップ358b(図3参照)によって管理番号による管理が必要であることを示す編成指令が送信され、この編成指令が管理情報格納領域199Aに格納されているか否かにより、管理が必要であるか否かを判定する(ステップ403)。

【0117】

ステップ403において、管理番号による管理要(すなわち、YES)と判定されれば、マイクロプロセッサ111は、最初に交信権を取得した入力ユニット120が貫通バス信号線BUSに送出した管理番号の情報を読出して記憶し(ステップ404)、続いて、入力ユニット120が貫通バス信号線BUSに送出したカード情報を読出して記憶する(ステップ405)。一方、ステップ403において、管理不要(すなわち、NO)と判定されれば、ステップ404を実行せずに、ステップ405に移行する。

【0118】

続いて、ステップ405によって正常なカード情報が得られたか否かを判定し(ステップ406)、カード情報が正常に受信された(すなわち、YES)と判定されれば、ステップ411に移行し、カード情報が正常に受信されなかった(すなわち、NO)と判定されれば、ステップ407に移行する。

【0119】

なお、ステップ406においては、最終接続位置よりも以前の入出力インタフェース回路122、132、142からカード情報が得られない場合、または、カード情報の中の接続位置信号MDLが論理レベル「L」となる入出力インタフェースが発見されない場合に、異常判定が行われる。

【0120】

ステップ407において、マイクロプロセッサ111は、異常状態をデータメモリ116に記憶するとともに、警報表示器119の異常表示LEDを点滅表示して異常報知し、動作終了ステップ210に移行する。

【0121】

ステップ411において、マイクロプロセッサ111は、ステップ405によって読出されたカード情報が中間カードであるか否かを判定する。具体的には、読出されたカード情報の中で、接続位置信号MDLの論理レベルを判定することにより、対象となっている入出力ユニットが、中間接続位置のものであるか、それ以外(最終接続位置)のものであるかを判定する。

【0122】

ステップ411において、カード情報が中間位置のものである(すなわち、YES)と判定されれば、ステップ413aに移行し、中間位置でなく最終位置のものである(すなわち、NO)と判定されれば、ステップ412に移行する。ステップ412においては、これから局番設定が行われる入出力ユニットが、最終接続位置のものであることを記憶してから、ステップ413aに移行する。

【0123】

ステップ413aにおいて、マイクロプロセッサ111は、設定局番の値を、貫通バス信号線BUS内のデータバスに送出する。このとき、ステップ413aに応動して、交信権を取得している入出力ユニットは、貫通バス信号線BUSを介して、設定局番を受信して自身の入出力インタフェース内の局番設定メモリに書込み、設定記憶する(ステップ413b)。また、局番設定を終えた入出力ユニットは、貫通バス信号線BUSを介して、局番情報および管理番号の情報を、マイクロプロセッサ111に対して順次確認返信する(ステップ414a)。

【0124】

ステップ413aに続いて、マイクロプロセッサ111は、ステップ414aによる局番情報および管理番号の返信情報を受信し(ステップ414b)、復帰(リターン)ステップ415を介して、図4内のステップ310に移行する。

【0125】

以上の動作を整理して概括説明すると、ステップ404は、初期保存手段として機能し、入出力ユニットに格納されている管理番号を読出して、管理情報格納領域199Aに転送書込みを行う。

【0126】

ステップ406は、第2の異常判定手段として機能し、最終接続位置よりも以前の入出力インタフェース回路122、132、142からカード情報が得られない場合、または最終接続位置の入出力インタフェース回路(出力インタフェース回路152)が所定時間を経過しても発見されない場合に、異常状態であることを判定する。

【0127】

ステップ407は、設定異常処理手段として機能し、第2の異常判定手段(ステップ406)が異常を検出したときに機能して、異常状態をデータメモリ116に書込み記憶するとともに、異常発生を警報表示する。

【0128】

次に、前述の図3および図4に関連した図6および図7のフローチャートを参照しながら、この発明の実施の形態1によるプログラム転送操作について説明する。図6は基本ユニット110Aに接続された外部ツール108の動作を示し、図7はマイクロプロセッサ111の動作を示している。

【0129】

なお、前述のように、マイクロプロセッサ111と外部ツール108との間では、シリアルインタフェース118を介して交信が行われ、一方が送信して他方が受信すると、受信確認の返信が行われ、送信指令内容が受信側で実行されると、実行確認返信が行われるようになっているが、図6および図7においては、簡略化のため、両者の連携動作については図示を省略する。

【0130】

図6において、まず、図3内の中継端子Xに続いて、オペレータの操作により、外部ツール108の設定がプログラム転送モードに設定され(ステップ550)、続いて、暗証番号の有無が確認(検索チェック)される(ステップ551)。なお、ステップ551においては、暗証番号が既に登録されているか否かがチェックされ、たとえ暗証番号が登録されていても、その番号が表示されるわけではない。

【0131】

続いて、ステップ551の検索チェックに基づき、暗証番号の有無を判定し(ステップ552)、暗証番号が登録されている(すなわち、YES)と判定されればステップ554bに移行し、未登録である(すなわち、NO)と判定されれば、ステップ553に移行する。

【0132】

ステップ553においては、暗証番号の要否を判定する。具体的には、暗証番号の登録が必要であるか否(不必要である)かの選択ボタンが画面表示され、オペレータが必要側を選択すると、暗証番号が必要(すなわち、YES)と判定されてステップ554aに移行し、不要側を選択すると、暗証番号が不要(すなわち、NO)と判定されてステップ559aに移行する。

【0133】

ステップ554aにおいては、オペレータの操作により暗証番号が入力されて、入力された暗証番号が管理情報格納領域199Aに転送されることにより、暗証番号の設定送信が行われる。続いて、暗証番号を読出し確認して、暗証番号の設定確認を行い(ステップ555)、ステップ559aに移行する。

【0134】

一方、ステップ554bにおいては、オペレータの操作により暗証番号が入力され、暗証番号の確認送信が行われる。続いて、ステップ554bで入力された暗証番号と既に登録されていた暗証番号とが一致しているか否かを判定し(ステップ556)、一致している(すなわち、YES)と判定されれば、ステップ558に移行し、不一致である(すなわち、NO)と判定されれば、ステップ557に移行する。

【0135】

ステップ557においては、暗証番号が不一致であることを示すメッセージが画面表示され、続いて、動作終了ステップ560に移行し、所定時間内に、再度動作開始ステップ350(図3参照)に移行する。ステップ557の異常表示画面に基づいて、オペレータは、暗証番号の再入力を行うか、または、暗証番号が不明であるときには全データの消去処理を行う。

【0136】

一方、ステップ558においては、暗証番号の変更が必要であるか否かが判定される。具体的には、暗証番号の変更を行うか否かの選択ボタンが画面表示され、オペレータにより変更の選択ボタンが操作されると、暗証番号の変更が必要(すなわち、YES)と判定されてステップ553に移行し、変更不要の選択ボタンが操作されると、暗証番号の変更が不要(すなわち、NO)と判定されてステップ559aに移行する。

【0137】

ステップ559aにおいては、プログラムの転送指令が行われる。具体的には、オペレータの操作により、外部ツール108で作成したシーケンスプログラムの転送指令ボタンを押すことによって行われる。続いて、シーケンスプログラムが送信され、プログラムの転送を相互に確認して(ステップ559b)、動作終了ステップ560に移行する。

【0138】

図7の処理ルーチンは、図4内のステップ302に続いて実行される。図7において、まず、マイクロプロセッサ111は、外部ツール108が接続されてプログラムモードとしての通信が行われているか否かにより、プログラムモードを受信しているか否かを判定し(ステップ500)、プログラムモードを受信している(すなわち、YES)と判定されれば、ステップ501に移行する。

【0139】

また、ステップ500において、外部ツール108が接続されていないか、または外部ツール108が接続されていてもモニタモードとしての通信が行われている(すなわち、NO)と判定されれば、直ちに動作終了ステップ210に移行する。

【0140】

ステップ501においては、図6内のステップ559aによるプログラム転送指令を受信したか否かを判定し、転送指令を受信している(すなわち、YES)と判定されれば、ステップ502に移行し、転送指令を受信していない(すなわち、NO)と判定されれば、動作終了ステップ210に移行する。

【0141】

ステップ502においては、外部ツール108で作成されたシーケンスプログラムがプログラムメモリ115Aに転送される。続いて、転送が完了したか否かを判定し(ステップ503)、転送が完了していない(すなわち、NO)と判定されれば、ステップ502に復帰して転送処理を継続し、転送が完了した(すなわち、YES)と判定されれば、動作終了ステップ210に移行する。

【0142】

なお、編成完了状態において外部ツール108が接続されず、RUN/STOPスイッチがSTOP状態にある場合には、マイクロプロセッサ111は、図2内のステップ201、202a、202bと、図4内のステップ301、302と、図7内のステップ500、210とを循環動作し、RUN/STOPスイッチがRUN状態になるか、または、外部ツール108が接続されてプログラムモードが選択されるのを、待機している状態となる。

【0143】

また、前述の図2において、ステップ213bからなる脱落異常検出手段は、シーケンスプログラムのEND命令を実行するごとに機能するのに対し、ステップ208によるカード編成異常の有無の判定は、RUNモードになった初回の動作で一括して機能しているが、他の形態でカード編成異常の有無を判定してもよい。

【0144】

たとえば、シーケンスプログラムのEND命令を実行するごとに、1つの入出力ユニットに関するカード編成異常をチェックし、順次他の入出力ユニットに関するカード編成チェックを実行して、シーケンスプログラムの演算周期に大きな影響を与えないようにしながら、運転中であっても複数の演算サイクルにわたって順次カード編成異常の有無をチェックすることもできる。また、この場合、たとえばプログラマブルコントローラ100Aの演算周期が10msecであれば、不必要に高頻度に編成チェックが行われることになるが、編成異常チェック処理は、図9とともに後述するシーケンスプログラムの中で適正の頻度で実行することもできる。

【0145】

以上のように、この発明の実施の形態1によれば、あらかじめ保持している暗証番号によって管理されている基本ユニット110Aと、基本ユニット110Aに対して自由に着脱接続されて各々の管理番号が付与されている入出力ユニット120〜150と、を備えたプログラマブルコントローラ100Aに対し、初期登録された編成が変化すると、暗証番号を用いた編成変更処理を行わなければ、プログラマブルコントローラ100Aの運転が禁止されるか警告表示が行われる。

【0146】

したがって、たとえ同一品種の入出力ユニットであっても、エンドユーザによって不用意に入出力ユニットを保守交換することはできず、暗証番号を知っているシステム管理者のみによって保守交換が行われるので、システムの安全性を向上させることができる。また、同一品種であっても仕様の異なる新型の入出力ユニットが、保守対象となったプログラマブルコントローラ100Aに適用可能か否かは、システム管理者によって判断されて使用されるので、市場でのバージョンアップ管理に混乱を招くことがないという効果がある。

【0147】

なお、上記説明では、プログラマブルコントローラ100Aは、基本ユニット110Aと入出力ユニット120〜150がそれぞれ孤立した筐体内に収納され、連結コネクタによって相互に接続されるユニット型の場合を示したが、基本ユニット110Aや各入出力ユニット120〜150を共通の台板上に設置してもよい。この場合、台板は、マザーボードによって相互にバス接続された複数のコネクタを有し、各入出力ユニット120〜150をコネクタに接続するような形態としてもよい。

【0148】

また、マザーボードによって入出力ユニット120〜150をバス接続する形式の場合には、マザーボードに設けられたプリント配線によって多数のデータバスやアドレスバスが容易に生成されるので、データバスとアドレスバスとを分離独立させることにより、局番設定手段320(ステップ305〜312)を大幅に簡略化することができる。すなわち、マザーボード上にたとえば16個のコネクタが接続されている場合には、交信対象となるコネクタは、4本のアドレスバスによって簡単に指定することができる。また、入出力ユニット120〜150に関するカード情報も、数本のデータバスによって基本ユニット110Aに送信することができる。

【0149】

また、上記説明では、運転開始前に順次局番設定を行うようにしたユニット型のプログラマブルコントローラ100Aにおいて、局番設定を行いながら順次管理番号の情報を読出すようにしたが、局番設定が完了してから、設定局番を指定しながら管理番号の情報を読出すようにしてもよい。

【0150】

また、管理番号による保守交換の制限管理を行うか否かの選択手段である管理忌避手段(ステップ205、206)について述べたが、複数の入出力ユニット120〜150の中の特定の入出力ユニットのみを制限管理し、他の入出力ユニットについては自由に保守交換が可能となるようにしてもよい。

【0151】

また、管理番号による保守交換の制限管理機能を有する新型の基本ユニット110Aに対して、管理番号の保存機能を有していない旧型の入出力ユニットを接続可能にするための除外処理を行うこともできる。

また、入出力ユニット120〜150とは別に、基本ユニット110Aを独立した基本筐体内に収納したが、後述の実施の形態2で説明するように、基本筐体の中に基本ユニット110Aと入出力ユニット120〜150とを混合して組み込んでもよい。

【0152】

さらに、管理情報格納領域199Aとして、暗証番号の格納領域には、不揮発フラッシュメモリであるプログラムメモリ115Aの一部領域を利用し、局番対応のカード情報や管理番号の情報などの編成情報の格納領域には、データメモリ116のバッテリバックアップ領域を利用したが、管理情報格納領域199Aは、プログラムメモリ115Aまたはデータメモリ116のどちらか一方に集約してもよく、専用の小型EEPROMメモリをプログラムメモリまたはデータメモリの一部領域として適用してもよい。

【0153】

以上のように、この発明の実施の形態1によるプログラマブルコントローラ100Aは、マイクロプロセッサ111と、マイクロプロセッサ111と協働するシステムメモリ114Aと、ユーザによって外部で作成されたシーケンスプログラムが外部ツール108から転送書込みされるプログラムメモリ115Aと、入出力情報および制御情報を記憶するデータメモリ116と、を有する基本ユニット110Aを備えている。

【0154】

また、プログラマブルコントローラ100Aは、基本ユニット110Aを搭載した基本筐体または基本台板に共載されるか、もしくは、増設筐体または増設台板に延長接続されて、複数の制御信号線および複数ビットのデータバスを介して直列接続される複数の入出力ユニット120〜150を備え、複数の入出力ユニット120〜150は、外部入力センサまたは外部負荷131に接続された入出力インタフェース回路122〜152を含み、入出力インタフェース回路は、マイクロプロセッサ111に対して選択的に交信接続されるように構成されている。

【0155】

システムメモリ114Aは、管理番号の初期保存手段(ステップ404)と、照合判定手段(ステップ207a)と、編成異常処理手段(ステップ209b)と、編成変更手段(ステップ302)とを構成する制御プログラムを含み、プログラムメモリ115Aおよびデータメモリ116の少なくとも一方には、管理情報格納領域199Aが設けられている。

【0156】

管理情報格納領域199Aには、操作対象者を限定する暗証番号の情報と、入出力ユニット120〜150を特定する管理番号の情報とが格納されている。管理番号は、入出力ユニット120〜150に個別に付与されて、マイクロプロセッサ111によって少なくとも読出しが可能な固体識別番号からなり、固体識別番号は、入出力ユニット120〜150が代替可能な同一品種であっても、複数の入出力ユニット120〜150ごとに異なる番号からなる。

【0157】

初期保存手段(ステップ404)は、入出力ユニット120〜150に格納されている管理番号と、管理情報格納領域199Aに格納されている入出力ユニット120〜150の管理番号とを一致させておく手段からなる。

照合判定手段(ステップ207a)は、少なくともプログラマブルコントローラ100Aの運転開始に際して、入出力ユニット120〜150に格納されている管理番号と、管理情報格納領域199Aに格納されている入出力ユニット120〜150の管理番号とが一致しているか否かを判定する手段からなる。

【0158】

編成異常処理手段(ステップ209b)は、照合判定手段(ステップ207a)による判定結果が不一致を示す場合に機能して、プログラマブルコントローラ100Aの作動状態を停止または現状保持するか、異常状態であることを管理情報格納領域199Aに書込み記憶するか、もしくは、少なくとも異常発生を警報表示する手段からなる。

編成変更手段(ステップ302)は、管理情報格納領域199Aに対してあらかじめ書込み保存されている暗証番号と同じ暗証番号が、外部ツール108から入力されたことに応答して機能し、初期保存手段(ステップ404)によって既に記憶されている管理番号をクリアして、新たに初期保存処理を実行する手段からなる。

【0159】

管理番号は、入出力ユニット120〜150で使用される専用集積回路素子に内蔵されて、少なくとも読出しが可能な不揮発メモリに格納された部品のシリアル番号からなるか、または、入出力ユニット120〜150の製造工程において、入出力ユニット120〜150を構成するプリント基板上に搭載されて、少なくとも読出しが可能な不揮発メモリに格納された入出力ユニット120〜150のシリアル番号からなる。

【0160】

管理情報格納領域199Aとなるプログラムメモリ115Aまたはデータメモリ116は、不揮発メモリからなるか、または、少なくともプログラマブルコントローラ100Aの電源が遮断されてもバッテリ117によって記憶状態が保存されるRAMメモリからなる。また、初期保存手段(ステップ404)および編成変更手段(ステップ302)は、入出力ユニット120〜150に格納されているシリアル番号を管理情報格納領域199Aに転送保存する手段からなる。

【0161】

すなわち、入出力ユニット120〜150には、入出力ユニット120〜150の製造メーカによってあらかじめ管理番号が登録されていて、各々の管理番号を基本ユニットに読出して初期編成を行うようになっている。したがって、システム管理者は、管理番号を作成または管理する必要がなく、誤って重複番号が使用されることがないという効果がある。

【0162】

また、編成変更手段(ステップ302)で使用される暗証番号は、シーケンスプログラムを保護するための暗証番号と同一番号からなり、外部ツール108から管理情報格納領域199Aに書込まれて、一旦記憶されると、同一番号の暗証番号が外部ツール108から入力されない限り、プログラムメモリ115Aに格納されたシーケンスプログラムの書換えおよび読出しの少なくとも一方が禁止されるようになっている。したがって、管理番号の編成変更を行うための暗証番号は、シーケンスプログラムを保護するための暗証番号と一致しているので、システム管理者は、2種類の暗証番号を管理する必要がなく、取り扱いが混乱しないという効果がある。

【0163】

システムメモリ114Aは、複数の入出力ユニット120〜150のすべてに対して一括適用される第1および第2の管理忌避手段(ステップ205、206)の少なくとも一方を構成する制御プログラムをさらに含み、複数の入出力ユニット120〜150は、管理番号の情報に加えて、機種コード番号の情報をさらに含む。

【0164】

第1の管理忌避手段(ステップ205)は、管理情報格納領域199Aに対して暗証番号が書込み保存されていないときには、照合判定手段(ステップ207a)および編成異常処理手段(ステップ209b)による管理番号の照合および異常処理の実行を禁止し、入出力ユニットが固体識別用の管理番号を有しているにも関わらず同一品種のものであれば、入出力ユニットの保守交換を自由に可能にする手段からなる。

【0165】

第2の管理忌避手段(ステップ206)は、管理情報格納領域199Aに対して暗証番号が書込み保存されていても、管理情報格納領域199Aに対して管理忌避指令が書込み保存されている場合には、照合判定手段(ステップ207a)および編成異常処理手段(ステップ209b)による管理番号の照合および異常処理の実行を禁止し、入出力ユニットが固体識別用の管理番号を有しているにも関わらず同一品種のものであれば、入出力ユニットの保守交換を自由に可能にする手段からなる。

【0166】

このように、第1、第2の管理忌避手段(ステップ205、206)によって、管理番号による入出力ユニット120〜150の適用管理を免除することができるようになっているので、入出力ユニット120〜150は、固体識別のための管理番号を有しているにも関わらず、システム管理者の判断によって同一品種のものであれば、自由に保守交換することができ、入出力ユニット120〜150の標準化を実現することができる。また、システム管理者によって管理番号を作成または登録する場合であっても、管理忌避状態にしておけば、入出力ユニット120〜150に対する管理番号の設定が不要となり、操作を単純化することができる。

【0167】

また、システムメモリ114Aは、複数の入出力ユニット120〜150の各々に対して個別適用される第1または第2の適用除外手段の少なくとも一方を構成する制御プログラムをさらに含み、複数の入出力ユニット120〜150は、機種コード番号の情報を含む。

【0168】

第1の適用除外手段は、入出力ユニットが管理番号の情報を有していない旧式の入出力ユニットである場合に適用されて、照合判定手段(ステップ207a)において管理番号の照合を免除するための除外情報を管理情報格納領域199Aに格納保存する手段からなる。また、第2の適用除外手段は、入出力ユニットが管理番号の情報を有しているにも関わらず、照合判定手段において管理番号の照合を免除するための除外情報を管理情報格納領域199Aに格納保存する手段からなる。これにより、第1、第2の適用除外手段によって照合判定を免除された特定の入出力ユニットは、同一品種のものであれば保守交換が自由に可能となる。

【0169】

このように、第1、第2の適用除外手段によって、管理番号による入出力ユニットの適用管理を、特定の入出力ユニットに限って免除することができるので、管理番号の情報を有していない旧式の入出力ユニットの場合には、入出力ユニットの交換を自由に行えることになるが、使用すること自体は可能となる効果がある。また、管理番号の情報を有する入出力ユニット120〜150であっても、システム管理者が認めた例外的な入出力ユニットに限って、保守交換を自由に行うことができる効果がある。

【0170】

また、基本ユニット110Aは、基本筐体に格納され、複数の入出力ユニット120〜150は、基本筐体または増設筐体に格納されて、ユニット型のプログラマブルコントローラ100Aを構成している。システムメモリ114Aは、複数の入出力ユニット120〜150に対する識別番号を設定するための局番設定手段320を構成する制御プログラムをさらに含み、入出力インタフェース回路122〜152は、局番情報と、カード情報と、管理番号の情報とが格納される個別メモリを含む。

【0171】

カード情報は、少なくとも、入出力インタフェース回路122〜152が入力インタフェース回路であるか、または出力インタフェース回路であるかを識別する品種別論理情報と、入出力インタフェース回路122〜152の接続位置が最終接続位置であるか、または最終接続位置以外の中間接続位置であるかを識別する接続位置信号(接続位置論理情報)MDLと、を含む。

【0172】

複数の制御信号線および複数ビットのデータバスの末端位置には、終端処理回路162、接続位置確認回路LSTおよび終端処理確認回路ENDを含む終端ブロック160が接続されている。終端処理回路162は、終端ブロック160内の開放信号線端末に接続されて、整合回路素子となるインピーダンス素子をグランド回路GNDまたは定電圧電源線Vccに対して接続するプルダウン回路またはプルアップ回路からなる。

【0173】

接続位置確認回路LSTは、入出力インタフェース回路に付加されて接続位置信号(接続位置論理情報)MDLを得るためのプルアップ抵抗123〜153(または、プルダウン抵抗)を、終端ブロック160内でグランド回路GNDまたは定電圧電源線Vccに接続して論理反転させる回路からなる。

終端処理確認回路ENDは、終端ブロック160が接続されていることを、入出力ユニット120〜150を貫通して、接続確認信号END1としてマイクロプロセッサ111に伝達するためのロウレベルまたはハイレベルの論理発生回路からなる。

【0174】

局番設定手段320は、システムメモリ114Aに格納された制御プログラムに基づき、マイクロプロセッサ111の運転開始時にマイクロプロセッサ111よって実行されて、終端ブロック160の接続が確認された状態において、初段の入出力インタフェース回路(入力インタフェース回路122)から接続位置信号(接続位置論理情報)MDLによって確認された終端接続位置の入出力インタフェース回路(出力インタフェース回路152)に対して順次に異なる局番を割付設定する手段からなり、局番設定手段320による局番設定の順次処理の実行過程中または完了後に、初期保存手段(ステップ404)による初期保存処理が実行され、各局番の入出力ユニット120〜150に対するカード情報および管理番号の情報からなる一連情報が、管理情報格納領域199Aに書込み保存される。

【0175】

このように、入出力ユニット120〜150と基本ユニット110Aとの交信に必要となる入出力ユニットの局番を、局番設定手段320によってあらかじめ設定しておく必要がある入出力ユニットを使用した場合に、接続確認信号END1によって終端ブロック160の接続が確認されるとともに、接続位置信号(接続位置論理情報)MDLによって増設ユニットの接続位置が中間位置であるか最終接続位置であるかを認識して、局番設定が行われ、局番設定の過程または局番設定後に管理番号の初期保存が行われるので、終端ブロック160が未接続であって信号が不安定な状態で局番設定が行われることがなく、局番や管理番号の誤設定を防止することができる。

【0176】

なお、カード情報の中の品種別論理情報は、プリント基板に設けられた配線パターンによって決定される固定情報であるのに対し、接続位置論理情報(接続位置信号MDL)は、入出力インタフェース回路122〜152の接続位置によって変化する可変情報であるが、可変情報からなる接続位置信号MDLも、終端ブロック160内の配線パターンである終端処理確認回路ENDによって決定される論理情報となっている。したがって、複雑な制御動作に依存せず、既存のデータバスを利用して、マイクロプロセッサ111に接続位置情報を伝達することができる。

【0177】

また、入出力インタフェース回路122〜152は、マイクロプロセッサ111が発生する局番設定検索信号CF1を受信して、局番設定の完了に応答して順次後段に接続された入出力インタフェース回路122〜152に局番設定検索信号CF1を伝達するための選択切換回路125a、125b〜155a、155bをさらに含む。また、カード情報は、局番設定が完了しているか否かの設定状態を識別して、選択切換回路125a、125b〜155a、155bを切り換える局番設定完了信号(個別完了論理情報)FINをさらに含む。

【0178】

局番設定手段320は、マイクロプロセッサ111により実行される手段であって、局番設定検索信号CF1を受信した入出力インタフェース回路122〜152のカード情報を、データバスを介して読出して、入出力インタフェース回路122〜152に対応した局番情報を、データバスを介して個別メモリに書込む手段からなる。

【0179】

マイクロプロセッサ111は、局番設定が完了した後に、データバスを介して局番指定を行い、指定された局番の入出力インタフェース回路122〜152との間で、データバスを介して入出力情報を交信するように構成されている。

【0180】

このように、局番設定完了信号(個別完了論理情報)FINに応動する選択切換回路125a、125b〜155a、155bによって、局番設定を必要とする入出力ユニット120〜150が順次選択されるので、複数の入出力インタフェース回路122〜152に対して、選択切換回路125a、125b〜155a、155bにより漏れなく確実に局番設定を行うことができる。また、接続位置信号(接続位置論理情報)MDLによって検出される最終接続位置の入出力インタフェース回路(出力インタフェース回路152)まで局番設定を行えばよいという効果がある。

【0181】

また、システムメモリ114Aは、第1の異常判定手段(ステップ303)と、第2および第3の異常判定手段(ステップ406、310)との少なくとも一方の異常判定手段と、設定異常処理手段(ステップ304、407)とを有する運転前の異常判定および処理手段を構成する制御プログラムをさらに含む。

【0182】

第1の異常判定手段(ステップ303)は、終端処理確認回路ENDによる接続確認信号END1の論理レベルが終端ブロック160の未接続状態(論理レベル「H」)を示す場合に、異常状態であることを判定する手段からなる。

【0183】

第2の異常判定手段(ステップ406)は、最終接続位置よりも以前の入出力インタフェース回路122〜142からカード情報が得られない場合、または、最終接続位置の入出力インタフェース回路(出力インタフェース回路152)が所定時間を経過しても発見されない場合に、異常状態であることを判定する手段からなる。

【0184】

第3の異常判定手段(ステップ310)は、送信した局番情報に対して確認返信された設定局番が不一致である場合と、管理番号の情報が得られない場合とにおいて、異常状態であることを判定する手段からなる。

【0185】

設定異常処理手段(ステップ304、407)は、第1、第2または第3の異常判定手段(ステップ303、406、310)が異常判定した場合に機能して、異常状態を管理情報格納領域199Aに書込み記憶するか、または、少なくとも異常発生を警報表示する手段からなる。

【0186】

このように、第1、第2または第3の異常判定手段(ステップ303、406、310)により、終端ブロックの脱落異常、カード情報の受信異常、局番情報や管理番号の情報の読出確認異常に応動して設定異常処理が実行されるので、プログラマブルコントローラ100Aの運転開始前に正常な設定が行われたか否かを確認することによって、安全性を向上させることができる。また、異常発生状態を管理情報格納領域199Aに書込み保存しておくことにより、異常発生の要因を識別して、保守点検が容易になる効果がある。

【0187】

また、システムメモリ114Aは、カード編成記憶手段(ステップ313)、編成異常検出手段(ステップ208)、脱落異常検出手段(ステップ213a、213b)および編成異常処理手段(ステップ209b)を有する運転中の異常判定および処理手段を構成する制御プログラムをさらに含む。

【0188】

カード編成記憶手段(ステップ313)は、局番設定の完了時に、カード情報と管理番号の情報と設定局番との対応状態を、管理情報格納領域199Aに書込み記憶する手段からなる。

脱落異常検出手段(ステップ213a、213b)は、終端処理確認回路ENDによる接続確認信号END1の論理レベルに基づき、少なくとも運転開始時において終端ブロック160が未接続状態となった場合に、異常状態であることを判定する手段からなる。

編成異常検出手段(ステップ208)は、局番指定して読出された入出力インタフェース回路122〜152から得られるカード情報または管理番号の情報が、カード編成記憶手段(ステップ313)によって記憶されている情報と一致しているか否かを少なくとも運転開始時に判定する手段からなる。

編成異常処理手段(ステップ209b)は、編成異常検出手段(ステップ208)が編成異常を検出した場合、または、脱落異常検出手段(ステップ213a、213b)が終端ブロック160の脱落異常を検出した場合に機能して、プログラマブルコントローラ100Aの作動状態を停止または現状保持するか、異常状態を管理情報格納領域199Aに書込み記憶するか、もしくは、少なくとも異常発生を警報表示する手段からなる。

【0189】

このように、運転開始時および運転中に異常状態を検出して、運転停止または異常表示を行うので、たとえば入出力ユニット120〜150が不用意に保守交換された場合、または、運転中に終端ブロック160の脱落異常が発生した場合に対し、制御の安全性を向上させることができる。

【0190】

実施の形態2.

次に、図8〜図12を参照しながら、この発明の実施の形態2について説明する。図8はこの発明の実施の形態2に係るプログラマブルコントローラ100Bの全体構成を示すブロック図である。図8のプログラマブルコントローラ100Bは、基本筐体内に既に局番設定が行われている入出力ユニット170a、170b、180を有する。

【0191】

この場合、管理番号があらかじめ入出力ユニット170a、170b、180に格納されておらず、システム管理者によって独自に設定される点が、前述(図1参照)の実施の形態1とは異なる。以下、前述の実施の形態1との相違点に注目して説明する。なお、図8において、前述と同一または相当部分に対しては、同一符号が付されるか、または同一符号の後に「B」が付されている。

【0192】

図8において、プログラマブルコントローラ100Bは、基本筐体110に収納された基本ユニット110Bおよび入出力ユニット170a、170bと、増設筐体(図示せず)に収納された入出力ユニット180および終端ブロック160と、を備えている。基本ユニット110Bの内部には、マイクロプロセッサ111、バスインタフェース回路112、システムメモリ114B、プログラムメモリ115B、データメモリ116、シリアルインタフェース118が設けられており、これらは互いにバス接続されている。

【0193】

データメモリ116の一部領域は、バッテリ117でバックアップされており、プログラムメモリ115Bの一部領域とともに、管理情報格納領域199Bを構成している。制御電源ユニット113および警報表示器119は、前述と同様に構成されている。基本筐体110の内部には、基本ユニット110Bに加えて、プリント基板で構成された入出力ユニット170a、170bが内蔵されている。入出力ユニット170a内の入力ユニットは、たとえば図1内の入力ユニット120に相当し、入出力ユニット170b内の出力ユニットは、たとえば図1内の出力ユニット130に相当する。入出力ユニット170a、170bは、独立した筐体が設けられることなく、基本筐体110内に組み込まれている。

【0194】

同様に、入出力ユニット180は、図1内の入出力ユニット120、130、140、150のいずれかのユニットを代表している。入出力要素101aは、たとえば図1内の開閉信号121に相当し、入出力要素101bは、たとえば図1内の外部負荷131に相当し、入出力要素101cは、適用された増設筐体ユニット180の品種に応じて、図1内の開閉信号121、外部負荷131、アナログ信号141またはアナログ負荷151に相当している。

【0195】

各入出力ユニット内の入出力インタフェース回路172a、172b、182は、カード情報格納メモリと、局番設定メモリと、管理番号設定メモリと、入出力信号回路、多チャンネルAD変換器または多チャンネルDA変換器と、を有する。選択切換回路175a、175b、185は、図1内の選択切換回路125a、125bと同様に、一対の論理和素子によって構成されている。

【0196】

ただし、後述するように、基本筐体110内の入出力インタフェース回路172a、172bに関しては、あらかじめ固定の局番が割付設定されている場合には、基本筐体110内の最終位置に配置されている選択切換回路175b以外の選択切換回路175aは不要であり、マイクロプロセッサ111が発生する局番設定検索信号CF1は、最終位置の入出力インタフェース回路172bに直接供給されるようになっている。

【0197】

また、固定局番が割付設定されている入出力基板上の入出力ユニット170a、170bのうち、終端ブロック160が接続されることのない内側の入出力基板170aに対する接続位置信号MDLは、省略することも可能である。

【0198】

また、基本筐体110内の最終位置の選択切換回路175bは、前述(図1)の一対の論理和素子によるハードウエア構成としてもよいが、ハードウエアを使用せずに、マイクロプロセッサ111の制御動作によって機能する選択切換手段で代替することも可能である。この場合、マイクロプロセッサ111は、まず局番「00」を指定して、入出力ユニット170aから機種コード情報(後述する)を読出して、基本筐体110内の入出力ユニット170a、170bの編成を確認した後に、局番設定検索信号CF1を入出力ユニット180に対して送出すればよい。

【0199】

また、入出力ユニット170a、170bが同一プリント基板上に搭載されている場合には、本願の主旨からすれば、管理番号は個々には不要であって、代表的に1つの管理番号を与えてもよい。

【0200】

基本筐体110に内蔵される入出力点数の規模には様々なものがあり、適用される用途の制御点数規模に応じたものが選択可能になっているが、たとえば制御出力点数よりも多い入力点数を必要としたり、提供される基本筐体110内の入出力ユニット170a、170bの入出力点数が実態用途に比べて不足していたり、アナログ入出力を必要とする場合などには、増設筐体に収納された入出力ユニット180が適宜増設使用される。ただし、基本筐体110に内蔵された入出力のみでまかなえる用途の場合には、増設筐体を使用する必要はなく、終端ブロック160が基本筐体110の端面に直接接続されるようになっている。

【0201】

基本筐体110の内部に設けられた入出力インタフェース回路172a、172bの局番設定は、図1内の入出力ユニット120、130と同様に順次に割付設定されてもよいが、図8の例では、入力インタフェース172aには局番「00」が既に割り付けられ、出力インタフェース回路172bには局番「01」が既に割り付けられていて、入出力ユニット180は、局番「02」から順次設定されるようになっている。

【0202】

また、入出力インタフェース回路172a、172b内のカード情報格納メモリには、品種別論理情報、個別完了論理情報および接続位置論理情報(接続位置信号MDL)に加えて、基本筐体110に内蔵された入出力インタフェース回路172a、172bであることを識別するための内外識別論理情報が付加されている。

【0203】

さらに、最前位置の入出力インタフェース回路172a内のカード情報には、基本筐体110内の入出力編成の種別を示す機種コード情報が含まれている。機種コード情報としては、たとえば、基本筐体110内の「入力点数/出力点数」が「8点/8点」のもの、「16点/16点」のもの、「32点/32点」のもの、「64点/64点」のものに応じて、2ビットで4種類の機種コードが与えられるようになっている。

【0204】

これらのカード情報のうち、基本筐体110の端面位置に設置される入出力インタフェース回路172bの接続位置論理情報は、終端ブロック160が接続されているか否かによって論理レベルが変化するが、その他のカード情報および局番情報は、すべて固定の情報である。

【0205】

各種の固定された品種別論理情報は、データバスに対して接続(または、解放)するために設けられたデータセレクタの複数ビットの入力端子を、プリント基板によってグランド回路GNDに接続するか、または、定電圧電源線Vccに接続するかによって決定される配線パターン情報となっている。ここでは、品種別論理情報の格納領域を、個別メモリと総称しているが、実態としては、読み書きの行えるメモリは使用されていない。

【0206】

次に、図9〜図12のフローチャートを参照しながら、図8のように構成されたこの発明の実施の形態2による動作について説明する。図9〜図12は、前述の図2〜図5に対応しており、以下、図2〜図5との相違点に注目して説明する。なお、各図において、前述と同一の符号は同一処理または相当処理を示しており、新たに付加された符号(前述と異なる処理)について説明する。また、プログラム操作を示す前述(図6、図7)のフローチャートは、この発明の実施の形態2においてもそのまま適用されるものとする。

【0207】

まず、運転動作を示す図9においては、ステップ212とステップ214との間に、前述(図2参照)のステップ213bに代えて、ステップ700(点検時期判定手段)が設けられている。また、ステップ213aとステップ215との間には、前述(図2参照)のステップ209aに代えて、ステップ709a(初回フラグのセット処理、点検フラグのリセット処理)が設けられている。

【0208】

ステップ700においては、ステップ211のシーケンスプログラムの中で所定の点検フラグがセットされたか否かにより、点検フラグが作動したか否かを判定し、点検フラグがセットされている(すなわち、YES)と判定されれば、ステップ205に移行して、ステップ208(編成異常検出手段)または脱落異常検出手段(ステップ213a)を実行する。また、ステップ700において、点検フラグがセットされていない(すなわち、NO)と判定されれば、ステップ214に移行する。

【0209】

前述(図2)の場合では、ステップ204が初回動作判定処理を実行したときのみにステップ208やステップ213aが実行され、運転中においては、ステップ212がEND命令の実行判定を行うごとに、脱落異常検出手段となるステップ213bが実行されるので、編成異常検出手段(ステップ208)が軽視され、脱落異常検出手段(ステップ213b)が過剰に重視されて傾向になる。

【0210】

一方、この発明の実施の形態2によれば、図9のように、シーケンスプログラムの中で適時に点検フラグをセットしておくことにより、点検フラグがセットされているときのみに点検処理が実行され、ステップ208、213aによる異常点検が実行された後には、ステップ709aによって点検フラグのリセットが行われるようになっている。なお、ステップ709aでは、初回フラグのセットも行われ、その結果として、ステップ204での判定結果が「NO」に変化するようになっている。

【0211】

次に、編成操作を示す図10および図11において、図10においては、前述(図3参照)のステップ358bに代えて、ステップ858bが設けられている。また、図11においては、前述(図3参照)の局番設定手段320に対応した局番設定手段820内のステップ305の後に、ステップ806、807が追加され、続いて、ステップ400に対応したステップ900が実行される。

【0212】

図10内のステップ858bにおいては、前述の管理要を示す編成指令を送信して既存の編成完了フラグをリセットする処理に加えて、各局番に対応した管理番号テーブルをオペレータによって作成して、ステップ807(後述する)により、管理番号を管理情報格納領域199Bに送信して転送保存するようになっている。

【0213】

図11内のステップ900の動作については、図12とともに後述する。図11において、ステップ305とステップ900の間には、ステップ806、807が挿入されており、ステップ305の判定結果が「YES」であってステップ358aまたはステップ858bによる編成指令を受信した場合には、ステップ806に移行する。

【0214】

ステップ806においては、図10内のステップ358aの処理に基づき管理要を受信したか否かを判定し、ステップ358aによる管理番号不要の編成指令を受信した(すなわち、NO)と判定されれば、ステップ900に移行し、ステップ858bによる管理要の編成指令を受信した(すなわち、YES)と判定されれば、ステップ807に移行する。

【0215】

ステップ807においては、ステップ858bで作成された局番対応の管理番号の情報を一括受信し、管理番号の情報を管理情報格納領域199Bに転送格納する。このとき、管理番号は、外部ツール108から管理情報格納領域199Bに一括転送される。以下、ステップ304〜312により構成された局番設定手段820の中核となる局番設定処理(ステップ900)に移行する。

【0216】

次に、図12のフローチャートを参照しながら、図11内の局番設定処理(ステップ900)について詳細に説明する。図12において、ステップ901、904、913a、913b、914a、914b、915は、それぞれ、前述(図5参照)のステップ401、404、413a、413b、414a、414b、415に対応している。この場合、前述のステップ406とステップ411との間には、ステップ911、920〜923、210が挿入されており、ステップ922は、カード編成記憶手段(基本筐体のみ)を構成している。

【0217】

まず、図12のサブルーチンの動作開始ステップ901は、図11内のステップ806またはステップ807から移行して活性化される。続いて、マイクロプロセッサ111は、局番設定検索信号CF1の論理レベルを「H」から「L」にして局番設定を開始し(ステップ402)、局番設定検索信号CF1が論理レベル「L」となったことによって、選択切換回路175b、185のうち、まずは入出力ユニット170b内の選択切換回路175bの出力が論理レベル「L」となって、入出力ユニット170bがマイクロプロセッサ111との交信権を取得することになる。

【0218】

続いて、ステップ858b(図10参照)によって管理番号による管理が必要であるとの編成指令が送信され、管理要の編成指令が管理情報格納領域199Bに格納されているか否かを判定し(ステップ403)、管理要(すなわち、YES)と判定されれば、ステップ904に移行し、管理不要(すなわち、NO)と判定されれば、ステップ405に移行する。

【0219】

ステップ904においては、交信権を取得した入出力ユニット170bに対する管理番号を転送用の送信バッファに格納する。続いて、交信権を取得した入出力ユニット170bが貫通バス信号線BUSに送出したカード情報を、マイクロプロセッサ111が読出し(ステップ405)、ステップ405によって正常なカード情報が得られたか否かを判定する(ステップ406)。ステップ406において、正常なカード情報が得られた(すなわち、YES)と判定されれば、ステップ911に移行し、正常なカード情報が得られない(すなわち、NO)と判定されれば、ステップ407に移行する。

【0220】

なお、ステップ406においては、最終接続位置よりも以前の入出力インタフェース回路からカード情報が得られない場合、または、カード情報の中の接続位置信号MDLが論理レベル「L」となる入出力インタフェース回路が発見されない場合に、異常状態であることを判定する。ステップ407においては、異常状態をデータメモリ116に記憶するとともに、警報表示器119の異常表示LEDを点滅表示して異常報知し、続いて、動作終了ステップ210に移行する。

【0221】

ステップ911においては、ステップ405で読出されたカード情報が機種コード情報を有する基本筐体110内の基本カードであるか否かを判定し、基本筐体110内の基本カードである(すなわち、YES)と判定されれば、ステップ920に移行し、基本筐体110内の基本カードでない(すなわち、NO)と判定されれば、ステップ411に移行する。なお、ステップ911での初回実行時の判定結果は「YES」となり、次回動作時の判定結果は「NO」となるのが正常である。

【0222】

ステップ920においては、ステップ405で読出されたカード情報の接続位置論理情報(接続位置信号MDL)を参照する。終端ブロック160が基本筐体110に直接取付けられていれば、接続位置信号MDLは論理レベル「L」であり、入出力ユニット180が介在していれば、接続位置信号MDLは論理レベル「H」となっている。

【0223】

次に、ステップ920(カード情報読出)に続いて、接続位置信号MDLの論理レベルを判定することにより、増設筐体が接続されている(増段有り)か否かを判定し(ステップ921)、増設筐体が接続されていない(すなわち、NO)と判定されれば、ステップ922に移行し、増設筐体が接続されている(すなわち、YES)と判定されれば、中継端子Dを介してステップ312(図11参照)に移行する。

【0224】

ステップ922においては、ステップ405で読出されたカード情報の中の機種コード情報に基づいて、既に設定されている局番に対応した入出力別の品種情報であるカード編成情報を、管理情報格納領域199B内に記憶する。以下、カード編成の記憶(ステップ922)が完了すると、編成完了フラグをセットして(ステップ923)、動作終了ステップ210に移行する。

【0225】

一方、ステップ911の判定結果が「NO」の場合に実行されるステップ411においては、ステップ405で読出されたカード情報の中で、接続位置信号MDLの論理レベルを判定することにより、対象となっている入出力ユニットが、最終接続位置よりも以前の中間接続位置のものであるか否か(最終接続位置のものであるか)を判定し、中間位置のものである(すなわち、YES)と判定されれば、ステップ913aに移行し、最終位置のものである(すなわち、NO)と判定されれば、ステップ412に移行する。

【0226】

ステップ412においては、これから局番設定の行われる入出力ユニットが最終接続位置のものであることを記憶して、ステップ913aに移行する。一方、ステップ913aにおいては、マイクロプロセッサ111が設定局番の値と、ステップ904で抽出した管理番号の値とを、順次データバスに送出する。

【0227】

ステップ913aの処理動作に応動して、交信権を取得している入出力ユニットは、貫通バス信号線BUSを介して設定局番および管理番号を受信して、局番設定メモリおよび管理番号設定メモリに書込みを行い(ステップ913b)、局番設定および管理番号の設定を終えた入出力ユニットは、貫通バス信号線BUSを介して局番情報および管理番号の情報を順次確認返信する(ステップ914a)。

【0228】

ステップ913aに続いて実行されるステップ914bにおいては、ステップ914aによる局番および管理番号の返信情報を受信する。以下、復帰ステップ915を介して、図11内のステップ310に移行する。

【0229】

以上の動作を整理して概括説明すると、ステップ904およびステップ913bは、初期保存手段として機能し、外部ツール108で設定されて管理情報格納領域199Bに格納された管理番号を、入出力ユニット170a、170b、180の管理番号設定用メモリに転送する。

【0230】

また、ステップ406は、前述と同様に第2の異常判定手段として機能し、最終接続位置よりも以前の入出力インタフェース回路172a、172bからカード情報が得られない場合、または、最終接続位置の入出力インタフェース回路182が所定時間を経過しても発見されない場合に、異常状態であることを判定する。

ステップ407は、前述と同様に設定異常処理手段として機能し、第2の異常判定手段(ステップ406)が異常を検出したときに機能して、異常状態をデータメモリ116に書込み記憶するとともに、異常発生を警報表示する。

【0231】

ステップ922は、増設筐体が使用されていない場合のカード編成記憶手段として機能し、基本筐体110内の入出力ユニット170a、170bに関する管理番号とカード情報と設定局番との対応状態を管理情報格納領域199Aに書込み記憶する。

【0232】

以上のように、この発明の実施の形態2によるプログラマブルコントローラ100Bは、マイクロプロセッサ111と、マイクロプロセッサ111と協働するシステムメモリ114Bと、ユーザにより外部で作成されたシーケンスプログラムが外部ツール108から転送書込みされるプログラムメモリ115Bと、入出力情報および制御情報を記憶するデータメモリ116と、を有する基本ユニット110Bと、基本ユニット110Bを搭載した基本筐体110(または、基本台板)に共載されるか、または増設筐体(または、増設台板)に延長接続される複数の入出力ユニット170a、170b、180と、を備えている。

【0233】

複数の入出力ユニット170a、170b、180は、入出力要素101a〜101c(外部入力センサまたは外部負荷)に接続された入出力インタフェース回路172a、172b、182を含み、入出力インタフェース回路172a、172b、182は、マイクロプロセッサ111に対して選択的に交信接続されるように構成されたプログラマブルコントローラ100Bを構成している。

【0234】

システムメモリ114Bは、管理番号の初期保存手段(ステップ904、913b)と、照合判定手段(ステップ207a)と、編成異常処理手段(ステップ209b)と、編成変更手段(ステップ302)と、を構成する制御プログラムを含む。また、プログラムメモリ115Bおよびデータメモリ116の少なくとも一方には、管理情報格納領域199Bが設けられている。管理情報格納領域199Bには、操作対象者を限定する暗証番号の情報と入出力ユニット170a、170b、180を特定する管理番号の情報とが格納されている。

【0235】

管理番号は、入出力ユニット170a、170b、180を構成するプリント基板上に搭載されて、書込みおよび読出しが可能な不揮発メモリに格納されたユーザ指定の固体識別番号からなる。管理情報格納領域199Bとなるプログラムメモリ115Bまたはデータメモリ116は、不揮発メモリからなるか、または、少なくともプログラマブルコントローラ100Bの電源が遮断されてもバッテリ117によって記憶状態が保存されるRAMメモリからなる。

【0236】

初期保存手段(ステップ904、913b)および編成変更手段(ステップ302)は、外部ツール108を介して管理情報格納領域199Bに書込まれたユーザ指定の固体識別番号を、入出力ユニット170a、170b、180に設けられた不揮発メモリに転送する手段からなる。

【0237】

このように、入出力ユニット170a、170b、180の管理番号は、システム管理者によって作成または登録され、この管理番号を基本ユニット110Bおよび入出力ユニット170a、170b、180に書込むことにより初期編成が行われるので、システム管理者は、自分が作成する管理番号に特別な意味を持たせ、たとえば登録年月を示す管理番号であれば、将来において入出力ユニット170a、170b、180の耐用年数を知ることができる。

【0238】

また、基本ユニット110Bは、基本筐体110に格納され、複数の入出力ユニット170a、170b、180の一部は、基本筐体110に内蔵され、複数の入出力ユニット170a、170b、180の他の一部は、基本筐体110の端面位置に設置される増設筐体に格納されて、ユニット型のプログラマブルコントローラ100Bを構成する。

【0239】

基本筐体110に内蔵された入出力ユニット170a、170bの複数の入出力インタフェース回路172a、172bに対しては、あらかじめ所定の局番情報が固定的に付与されている。システムメモリ114Bは、増設筐体内の入出力インタフェース回路182に対する識別番号を設定するための局番設定手段820を構成する制御プログラムを含む。

【0240】

基本筐体110または増設筐体内の各入出力インタフェース回路172a、172b、182は、局番情報とカード情報と管理番号の情報とが格納される個別メモリを含む。カード情報は、少なくとも、入出力インタフェース回路172a、172b、182が入力インタフェース回路であるか、または出力インタフェース回路であるかを識別する品種別論理情報と、入出力インタフェース回路172a、172b、182の接続位置が最終接続位置であるか、または最終接続位置以外の中間接続位置であるかを識別する接続位置信号(接続位置論理情報)MDLと、入出力インタフェース回路172a、172b、182が基本筐体110内のものであるか否かを示すとともに、基本筐体110内のものである場合には基本ユニット110Bの入出力編成の種別を示す機種コード情報と、を含む。

【0241】

複数の制御信号線および複数ビットのデータバスの末端位置には、終端処理回路162、接続位置確認回路LSTおよび終端処理確認回路ENDを含む終端ブロック160が接続されている。

【0242】

終端処理回路162は、終端ブロック160内の開放信号線端末に接続されて、整合回路素子となるインピーダンス素子をグランド回路GNDまたは定電圧電源線Vccに対して接続するプルダウン回路またはプルアップ回路からなる。

【0243】

接続位置確認回路LSTは、入出力インタフェース回路に付加されて接続位置信号(接続位置論理情報)MDLを得るためのプルアップ抵抗またはプルダウン抵抗を、終端ブロック160内でグランド回路GNDまたは定電圧電源線Vccに接続して論理反転させる回路からなる。

【0244】

終端処理確認回路ENDは、終端ブロック160が接続されていることを、入出力ユニット170a、170b、180を貫通して、接続確認信号END1としてマイクロプロセッサ111に伝達するためのロウレベルまたはハイレベルの論理発生回路からなる。

【0245】

局番設定手段820は、システムメモリ114Bに格納された制御プログラムに基づき、マイクロプロセッサ111の運転開始時にマイクロプロセッサ111よって実行されて、終端ブロック160の接続が確認された状態において、基本筐体110内の入出力インタフェース回路172a、172bに付与されている局番に続く局番を、増設筐体に対する初段の入出力インタフェース回路182から、接続位置信号(接続位置論理情報)MDLによって確認された終端接続位置の入出力インタフェース回路に対して、順次に割付設定する手段からなる。

【0246】

これにより、局番設定手段820による局番設定の順次処理の実行過程中または完了後に、初期保存手段(ステップ904、913b)による初期保存処理が実行され、各局番の入出力ユニット170a、170b、180に対するカード情報および管理番号の情報からなる一連情報が、管理情報格納領域199Bに書込み保存される。

【0247】

このように、入出力ユニット170a、170b、180と基本ユニット110Bとの交信に必要となる入出力ユニットの局番を、局番設定手段820によってあらかじめ設定しておく必要がある入出力ユニットを使用した場合に、接続確認信号END1によって終端ブロック160の接続が確認されるとともに、接続位置信号(接続位置論理情報)MDLによって増設ユニットの接続位置が中間位置であるか最終接続位置であるかを認識し、基本ユニット110Bの機種コード情報によって初段の増設入出力ユニット(入出力ユニット180)の局番を認識して局番設定が行われ、局番設定の過程または局番設定完了後に管理番号の初期保存が行われるので、終端ブロック160が未接続であって信号が不安定な状態で局番設定が行われることがなく、局番や管理番号の誤設定を防止することができる。

【0248】

なお、カード情報の中の品種別論理情報は、プリント基板に設けられた配線パターンによって決定される固定情報であるのに対し、接続位置論理情報(接続位置信号MDL)は、入出力インタフェース回路172a、172b、182の接続位置によって変化する可変情報であるが、可変情報の接続位置信号MDLも、終端ブロック160内の配線パターンである終端処理確認回路ENDによって決定される論理情報となっているので、複雑な制御動作に依存せず、既存のデータバスを利用してマイクロプロセッサ111に接続位置情報を伝達することができる。

【0249】

また、基本筐体110内の入出力ユニット170a、170bの局番は、既に固定局番が割り付けられているので、局番設定の能率を向上させることができるとともに、少なくとも基本筐体110内での局番設定を誤ることがないという効果がある。

【0250】

また、基本筐体に内蔵された最終段の入出力ユニット170bまたはシステムメモリ114Bは、入出力インタフェース回路172bのカード情報の読出しを完了したことに応答して、マイクロプロセッサ111が発生する局番設定検索信号CF1を、後段に接続された入出力ユニット180内の入出力インタフェース回路182に対して送信するための選択切換手段175bを構成する論理回路または制御プログラムをさらに含む。

【0251】

基本筐体110に内蔵された最終段の入出力インタフェース回路172bのカード情報は、カード情報の読出しが完了しているか否かの状態を識別して、選択切換手段175bを切り換える局番設定完了信号(個別完了論理情報)FINをさらに含む。

【0252】

増設筐体に内蔵された入出力インタフェース回路182は、マイクロプロセッサ111が発生する局番設定検索信号CF1を受信して、局番設定の完了に応答して順次後段に接続された入出力インタフェース回路に局番設定検索信号CF1を伝達するための選択切換回路185が付加されている。

増設筐体に内蔵された入出力インタフェース回路182のカード情報は、局番設定が完了しているか否かの設定状態を識別して選択切換回路185を切り換える局番設定完了信号(個別完了論理情報)FINをさらに含む。

【0253】

局番設定手段820は、マイクロプロセッサにより実行される手段であって、データバスを介して読出された基本筐体110内の最終段の入出力インタフェース回路172bのカード情報内の接続位置信号(接続位置論理情報)MDLが中間接続位置であった場合に実行され、カード情報内の機種コード情報に基づいて、次段に接続された増設筐体内の入出力インタフェース回路182に対応した局番情報を、データバスを介して個別メモリに書込む手段からなる。

【0254】

これにより、基本筐体110内の入出力インタフェース回路172bに付与されている局番に続く局番を、増設筐体内の初段の入出力インタフェース回路182から、接続位置信号(接続位置論理情報)MDLによって確認された終端接続位置の入出力インタフェース回路に対して順次に割付設定し、マイクロプロセッサ111は、割付設定が完了した後に、データバスを介して局番指定を行い、指定された局番の入出力インタフェース回路172a、172b、180との間で、データバスを介して入出力情報を交信する。

【0255】

このように、局番設定完了信号(個別完了論理情報)FINに応動する選択切換回路175a、175b、185によって、局番設定を必要とする入出力ユニット170a、170b、180が順次選択されるので、複数の入出力インタフェース回路172a、172b、182に対して、選択切換回路175a、175b、185により漏れなく確実に局番設定を行うことができる。また、基本筐体110内の最終入出力ユニットの局番に続く局番から、接続位置信号(接続位置論理情報)MDLによって検出される最終接続位置の入出力インタフェース回路まで局番設定を行えばよいという効果がある。

【0256】

また、システムメモリ114Bは、カード編成記憶手段(ステップ313、922)と、編成異常検出手段(ステップ208)と、脱落異常検出手段(ステップ213a)と、編成異常処理手段(ステップ209b)とを有する運転中の異常判定および処理手段を構成する制御プログラムをさらに含む。

【0257】

カード編成記憶手段(ステップ313、922)は、局番設定の完了時に、カード情報と管理番号の情報と設定局番(局番情報)との対応状態を、管理情報格納領域199Bに書込み記憶する手段からなる。

【0258】

脱落異常検出手段(ステップ213a)は、終端処理確認回路ENDによる接続確認信号END1の論理レベルに基づき、少なくとも運転開始時において終端ブロック160が未接続状態となった場合に、異常状態であることを判定する手段からなる。

【0259】

編成異常検出手段(ステップ208)は、局番指定して読出された入出力インタフェース回路172a、172b、182から得られるカード情報または管理番号の情報が、カード編成記憶手段(ステップ313)によって記憶されている情報と一致しているか否かを少なくとも運転開始時に判定する手段からなる。

【0260】

編成異常処理手段(ステップ209b)は、編成異常検出手段(ステップ208)が編成異常を検出した場合、または、脱落異常検出手段(ステップ213a)が終端ブロック160の脱落異常を検出した場合に機能して、プログラマブルコントローラ100Bの作動状態を停止または現状保持するか、異常状態を管理情報格納領域199Bに書込み記憶するか、もしくは、少なくとも異常発生を警報表示する手段からなる。

【0261】

このように、運転開始時および運転中に異常状態を検出して、運転停止または異常表示を行うようので、たとえば入出力ユニット170a、170b、180が不用意に保守交換されていた場合や、運転中に終端ブロック160の脱落異常が発生した場合に、制御の安全性を向上させることができる。

【0262】

また、システムメモリ114Bは、点検時期判定手段(ステップ700)を構成する制御プログラムをさらに含み、点検時期判定手段(ステップ700)は、プログラムメモリ115Bに格納されているシーケンスプログラムにより実行されて、点検指令フラグがセットされているか否かを判定し、点検フラグがセットされている場合に、脱落異常検出手段(ステップ213a)および編成異常検出手段(ステップ208)の少なくとも一方を実行して、異常状態が検出された場合には、編成異常処理手段(ステップ209b)を実行する手段からなる。

【0263】

このように、運転開始時とシーケンスプログラムで指令された運転中の適時とにおいて異常状態を検出して、運転停止または異常表示を行うので、たとえば入出力ユニット170a、170b、180が不用意に保守交換されていた場合や、運転中に終端ブロック160の脱落異常が発生した場合に、制御の安全性を向上させることができる。また、運転中の異常判定処理をユーザのシーケンスプログラムで適時に実行することができる効果がある。

【図面の簡単な説明】

【0264】

【図1】この発明の実施の形態1に係るプログラマブルコントローラの全体構成を示すブロック図である。

【図2】この発明の実施の形態1による運転動作を示すフローチャートである。

【図3】この発明の実施の形態1による外部ツールでの編成操作を示すフローチャートである。

【図4】この発明の実施の形態1によるマイクロプロセッサでの編成操作を示すフローチャートである。

【図5】図4内の局番設定処理(ステップ400)を詳細に示すフローチャートである。

【図6】この発明の実施の形態1による外部ツールでのプログラム操作を示すフローチャートである。

【図7】この発明の実施の形態1によるマイクロプロセッサでのプログラム操作を示すフローチャートである。

【図8】この発明の実施の形態2に係るプログラマブルコントローラの全体構成を示すブロック図である。

【図9】この発明の実施の形態2による運転動作を示すフローチャートである。

【図10】この発明の実施の形態2による外部ツールでの編成操作を示すフローチャートである。

【図11】この発明の実施の形態2によるマイクロプロセッサでの編成操作を示すフローチャートである。

【図12】図11内の局番設定処理(ステップ900)を詳細に示すフローチャートである。

【符号の説明】

【0265】

100A、100B プログラマブルコントローラ、205 第1の管理忌避手段、108 外部ツール、206 第2の管理忌避手段、110 基本筐体、207a 照合判定手段、110A、110B 基本ユニット、208 編成異常検出手段、111 マイクロプロセッサ、209b 編成異常処理手段、114A、114B システムメモリ(局番設定手段)、213a、213b 脱落異常検出手段、115A、115B プログラムメモリ、116 データメモリ、302 編成変更手段、120、130、140、150 入出力ユニット、303 第1の異常判定手段(終端異常)、122、132、142、152 入出力インタフェース回路、304 設定異常処理手段、125a、125b、135a、135b、145a、145b、155a、155b 選択切換回路、310 第3の異常判定手段(局番情報、管理番号)、313、922 カード編成記憶手段、160 終端ブロック、320、820 局番設定手段、162 終端処理回路、170a、170b、180 入出力ユニット、404、904、913b 初期保存手段、172a、172b、182 入出力インタフェース回路、406 第2の異常判定手段(カード情報受信)、175a、185 選択切換回路、407 設定異常処理手段、175b 選択切換回路(選択切換手段)、700 点検時期判定手段、199A、199B 管理情報格納領域、922 カード編成記憶手段、CF1 局番設定検索信号、FIN 局番設定完了信号(個別完了論理情報)、MDL 接続位置信号(接続位置論理情報)、GND グランド回路、Vcc 定電圧電源線、LST 接続位置確認回路、END 終端処理確認回路、END1 接続確認信号。

【技術分野】

【0001】

この発明は、マイクロプロセッサを内蔵した基本ユニットと、基本ユニットに対して着脱自在に接続される複数の入出力ユニットとによって構成されたプログラマブルコントローラにおいて、入出力ユニットのうちの入力ユニットに関連した操作および検出信号と、基本ユニット内のプログラムメモリに格納されたシーケンス制御プログラム(以下、「シーケンスプログラム」という)の内容とに応動して、入出力ユニットのうちの出力ユニットに接続された表示および駆動負荷を制御するプログラマブルコントローラに関し、特に入出力ユニットの保守管理を改善して安全性を向上させるための新規な技術に関するものである。

【背景技術】

【0002】

従来から、マイクロプロセッサを内蔵して、操作スイッチや各種センサなどの入力信号の動作状態と、プログラムメモリに格納されているシーケンスプログラムとに応動して、各種アクチェータや表示機器などの電気負荷の駆動制御を行うプログラマブルコントローラは、よく知られている。

【0003】

この種のプログラマブルコントローラにおいて、マイクロプロセッサおよび各種メモリを内蔵した基本ユニット(CPUユニット)と、入力インタフェース回路を内蔵した入力ユニットと、出力インタフェース回路を内蔵した出力ユニットと、からなる複数の入出力ユニットは、相互にバス接続された複数のコネクタを有するマザーボード台板上の各コネクタに接続されるか、または、各入出力ユニットが孤立筐体に収納されてフラットケーブルによって相互にバス接続されるなど、様々な構造形態のものが広く実用化されている。

【0004】

また、上記のような各種形態のプログラマブルコントローラにおいては、システム管理者以外のものが不用意にシーケンスプログラムを変更または盗用して、予定外の運転が行われないようにするために、様々なプログラム保護手段が提案されている。

【0005】

従来のプログラマブルコントローラにおいて、たとえば、プログラミング装置ごとの固有パスワードをパスワード登録部に登録しておき、作成したプログラムをプログラマブルコントローラに送る際のプログラム本体を含むプログラム格納コマンドに、固有パスワードを組み込むようにしたプログラミング方法が提案されている(たとえば、特許文献1参照)。

【0006】

上記特許文献1によれば、プログラマブルコントローラにおいては、プログラム格納処理部でプログラム番号とパスワードとの両方が一致した場合のみに、プログラム格納部の旧プログラムを新プログラムに書換え、プログラム番号が一致してもパスワードが異なる場合には書換えを禁止する。これにより、ユーザプログラムの使用者がシステムプログラムを変更できないようにするとともに、変更が必要な際には、システムプログラムの変更が容易となり、ハードおよびソフトが複雑化することなく、メモリの利用効率の悪化も回避するようにしている。

【0007】

一方、プログラマブルコントローラが使用されているか否かは別として、システム管理者以外の他者による消耗部品の交換を回避するための安全対策として、消耗部品にメモリを設けて管理する技術も提案されている(たとえば、特許文献2参照)。

【0008】

上記特許文献2に記載の印刷制御装置および印刷制御方法、プログラム、ならびに記憶媒体によれば、消耗部品情報取得部は、交換可能な消耗部品(トナーカートリッジ)の内部に設けられたメモリに格納されている所定情報(カートリッジ情報)を取得し、パラメータ切換部は、カートリッジ情報に基づいて、中間調変換部の中間調パラメータを選択して設定する。これにより、プリンタ制御ユニットにおける機能範囲を決定し、消耗部品を交換する際に不適切な消耗部品の場合には、印刷装置における機能範囲を制限して、消耗部品の誤使用を防止している。

【0009】

【特許文献1】特開平10−116108号公報(図1、要約)

【特許文献2】特開2003−015482号公報(図2、要約)

【発明の開示】

【発明が解決しようとする課題】

【0010】

従来のプログラマブルコントローラは、たとえば特許文献1のプログラミング方法の場合には、シーケンスプログラムの変更または盗用が防止されており、シーケンスプログラムが格納されている基本ユニットの保守交換を第3者が行うことができないようになっているものの、基本ユニットに対して着脱自在に接続される多数の入出力ユニットについては自由に交換することが可能であり、徹底した安全管理を行うことができないという課題があった。

【0011】

一方、特許文献2の印刷制御装置の場合には、限定された消耗部品がユーザによって交換可能となっているが、たとえ交換可能な消耗部品であっても、システム管理者以外の第3者による取替えを禁止したい場合に、単なる品種情報のみでは十分な禁止対策を実現することができないという課題があった。また、たとえば、新たに開発された異種の消耗部品が、既存の印刷制御装置の1つには適用可能であるものの、他の印刷制御装置には適用不可能な場合には、市場での混乱を招くという課題があった。

【0012】

この発明は、たとえ適用可能な入出力ユニットであっても、システム管理者以外の第3者による取替えを禁止し、システム管理者であれば容易に取替え交換を可能にしたプログラマブルコントローラを得ることを目的とする。

また、この発明は、適用可能な入出力ユニットであれば、システム管理者の許可のもとで、第3者が自由に取替え交換を行うことのできるプログラマブルコントローラを得ることを目的とする。

さらに、この発明は、運転開始前に入出力ユニットに対する局番設定を必要とする形式のものにおいて、局番設定操作と連動して入出力ユニットの交換可否を設定することのできるプログラマブルコントローラを得ることを目的とする。

【課題を解決するための手段】

【0013】

この発明によるプログラマブルコントローラは、マイクロプロセッサと、マイクロプロセッサと協働するシステムメモリと、外部で作成されたシーケンスプログラムが外部ツールを介して転送書込みされるプログラムメモリと、入出力情報および制御情報を記憶するデータメモリと、を有する基本ユニットと、基本ユニットを搭載した基本筐体または基本台板に共載されるか、もしくは、増設筐体または増設台板に延長接続されて、複数の制御信号線および複数ビットのデータバスを介して直列接続される複数の入出力ユニットと、を備え、複数の入出力ユニットは、外部入力センサまたは外部負荷に接続された入出力インタフェース回路を含み、入出力インタフェース回路は、マイクロプロセッサに対して選択的に交信接続されるように構成されたプログラマブルコントローラであって、システムメモリは、管理番号の初期保存手段、照合判定手段、編成異常処理手段および編成変更手段を構成する制御プログラムを含み、プログラムメモリおよびデータメモリの少なくとも一方には、管理情報格納領域が設けられ、管理情報格納領域には、操作対象者を限定する暗証番号の情報と、入出力ユニットを特定する管理番号の情報とが格納され、管理番号は、入出力ユニットに付与されて、マイクロプロセッサによって少なくとも読出しが可能な固体識別番号からなり、固体識別番号は、入出力ユニットが代替可能な同一品種であっても、複数の入出力ユニットごとに異なる番号からなり、初期保存手段は、入出力ユニットに格納されている管理番号と、管理情報格納領域に格納されている入出力ユニットの管理番号とを一致させておく手段からなり、照合判定手段は、少なくともプログラマブルコントローラの運転開始に際して、入出力ユニットに格納されている管理番号と、管理情報格納領域に格納されている入出力ユニットの管理番号とが一致しているか否かを判定する手段からなり、編成異常処理手段は、照合判定手段による判定結果が不一致を示す場合に機能して、プログラマブルコントローラの作動状態を停止または現状保持するか、異常状態であることを管理情報格納領域に書込み記憶するか、もしくは、少なくとも異常発生を警報表示する手段からなり、編成変更手段は、管理情報格納領域に対してあらかじめ書込み保存されている暗証番号と同じ暗証番号が、外部ツールから入力されたことに応答して機能し、初期保存手段によって既に記憶されている管理番号をクリアして、新たに初期保存処理を実行する手段からなるものである。

【発明の効果】

【0014】

この発明によれば、暗証番号によって管理されている基本ユニットと、基本ユニットに接続されて管理番号が付与されている入出力ユニットを備え、初期登録された編成が変化すると、暗証番号を用いた編成変更処理を行わなければ、プログラマブルコントローラの運転が禁止されるか警告表示が行われ、たとえ同一品種の入出力ユニットであってもエンドユーザによって不用意に入出力ユニットを保守交換することができず、暗証番号を知っているシステム管理者のみによって保守交換が行われるので、システムの安全性を向上させることができる。また、同一品種であっても仕様の異なる新型の入出力ユニットが、保守対象となったプログラマブルコントローラに適用可能か否かは、システム管理者によって判断されて使用されるので、市場でのバージョンアップ管理に混乱を招くことがないという効果がある。

【発明を実施するための最良の形態】

【0015】

実施の形態1.

以下、図面を参照しながら、この発明の実施の形態1について詳細に説明する。図1はこの発明の実施の形態1に係るプログラマブルコントローラの全体構成を示すブロック図である。図1において、プログラマブルコントローラ100Aは、基本ユニット110Aと、複数の入出力ユニット120、130、140、150と、終端ブロック160と、により構成されている。ここでは、入力ユニット120、140と、出力ユニット130、150とを総称して、入出力ユニットという。

【0016】

基本ユニット110Aは、外部電源103(たとえば、AC100V〜240Vの商用電源)から給電されるとともに、脱着コネクタ(図示せず)を介して外部ツール108(たとえば、パーソナルコンピュータ)に接続されており、制御プログラムの書込みや運転状態の監視を行うことができるようになっている。

【0017】

基本ユニット110Aの内部には、主要部となるマイクロプロセッサ(CPU)111と、マイクロプロセッサ111に接続されたバスインタフェース回路112と、各部に電源を供給する制御電源ユニット113と、マイクロプロセッサ111に属するシステムメモリ114A(たとえば、マスクROMメモリまたはフラッシュメモリなどの不揮発メモリ)、プログラムメモリ115A(たとえば、不揮発フラッシュメモリ)およびデータメモリ116(たとえば、RAMメモリ)と、データメモリ116の一部領域をバックアップするバッテリ117(たとえば、リチウムバッテリ)と、マイクロプロセッサ111に接続されたシリアルインタフェース118および警報表示器119(たとえば、複数個の発光ダイオードまたはセブンセグメント表示器)と、が設けられている。

【0018】

基本ユニット110A内の上記構成要素のうち、マイクロプロセッサ111、バスインタフェース回路112、システムメモリ114A、プログラムメモリ115A、データメモリ116およびシリアルインタフェース118は、相互にバス接続されている。なお、制御電源ユニット113は、基本ユニット110Aの外部に設置することも可能であり、その場合、基本ユニット110Aは、外部の制御電源ユニット113とCPUユニットとによって構成されることになる。

【0019】

制御電源ユニット113は、外部電源103から給電され、入力信号回路(図示せず)に対して安定化電圧(たとえば、DC24V)を供給するとともに、定電圧電源線Vccに対して安定化電圧(たとえば、DC5V)を供給する。定電圧電源線Vccは、グランド回路GNDとともに各部に配線されている。

【0020】

システムメモリ114Aは、各種の制御プログラム(図2〜図7とともに後述する)を含むとともに、プログラムメモリ115Aに格納されたシーケンス言語によるシーケンスプログラムをマイクロプロセッサ111に対応した機械言語に変換してマイクロプロセッサ111を作動させるようになっており、製品の出荷段階でメーカによって格納されたプログラムを有している。

【0021】

プログラムメモリ115Aには、外部ツール108を用いてユーザによって作成されたシーケンスプログラムが、シリアルインタフェース118を介して書込まれている。プログラムメモリ115Aは、たとえば、ブロック単位で一括消去が可能な主ブロックおよび副ブロックを有するフラッシュメモリからなり、主ブロックには、シーケンスプログラムが転送格納されている。副ブロックは、管理情報格納領域199A(後述する)の一部を構成しており、暗証番号が格納されるようになっている。

【0022】

データメモリ116(RAMメモリ)は、入出力信号情報や、補助リレー、タイマ、カウンタおよびデータレジスタなどのデバイス(プログラマブルコントローラ100Aの内部のデバイスとなって、ユーザに開放されている)の作動状態が格納される。

【0023】

データメモリ116の一部の領域は、バッテリ117によってバックアップされており、プログラマブルコントローラ100Aに対する電源が遮断されても、記憶状態が保持されるようになっている。また、データメモリ116のバッテリバックアップ領域のさらに一部の領域は、管理情報格納領域199Aとして使用され、管理情報格納領域199Aには、入出力ユニットの管理番号の情報(後述する編成情報)が格納されるようになっている。

【0024】

なお、プログラムメモリ115Aは、バッテリバックアップされたRAMメモリであってもよく、フラッシュメモリまたはEPROMなどによる不揮発メモリを内蔵したメモリカセットを装着することによって、プログラムメモリ領域を不揮発メモリ化することも可能である。警報表示器119は、マイクロプロセッサ111の作動状態、すなわち、電源の到来、正常運転状態、各種異常発生状態などを表示するようになっている。

【0025】

接続確認信号END1の伝送線は、プルアップ抵抗Rを介して定電圧電源線Vccに接続されるとともに、入出力ユニット120、130、140、150を貫通して、終端ブロック160の終端処理確認回路ENDによってグランド回路GNDに接続されている。接続確認信号END1は、論理レベル「L」(ロウ)となることによって、終端ブロック160が装着されたことを認識するための信号であり、バスインタフェース回路112を介してマイクロプロセッサ111に入力されている。

【0026】

貫通バス信号線BUSは、たとえば16ビットのデータバスおよび各種の制御信号線を含み、バスインタフェース回路112から入出力ユニット120、130、140、150を貫通して、終端ブロック160に至る多数の信号配線を構成している。

【0027】

マイクロプロセッサ111は、バスインタフェース回路112を介して局番設定検索信号CF1を発生する。局番設定検索信号CF1は、局番設定処理を実行する場合に、論理レベル「L」となり、初段の入出力ユニット(入力ユニット120)に局番設定指令を供給するようになっている。

【0028】

入力ユニット120は、コネクタ(図示せず)を介して基本ユニット110Aの端面位置に接続されており、入力ユニット120には、入力端子台(図示せず)を介して、外部の開閉信号121が入力されている。開閉信号121は、たとえば操作盤に設けられた各種の操作スイッチや、アクチェータの動作を確認するためのセンサスイッチから生成される。1台の入力ユニット120には、たとえば8点の入力信号が接続可能であるが、さらに多くの開閉信号121が接続される場合には、入力ユニット120の接続台数が増設されるようになっている。

【0029】

入力ユニット120は、入力インタフェース回路122と、プルアップ抵抗123、124と、選択切換回路125a、125bと、により構成されている。入力インタフェース回路122は、データセレクタを介して開閉信号121(入力信号)を貫通バス信号線BUSに接続する入力信号回路と、カード情報格納メモリと、局番設定メモリと、管理番号格納メモリと、を有する。

【0030】

出力ユニット130は、出力インタフェース回路132と、プルアップ抵抗133、134と、選択切換回路135a、135bと、により構成されている。出力インタフェース回路132は、出力信号回路が異なる点を除けば、入力インタフェース回路122と同様の構成を有し、外部負荷131に接続されている。

【0031】

入力ユニット140は、入力インタフェース回路142と、プルアップ抵抗143、144と、選択切換回路145a、145bと、により構成されている。入力インタフェース回路142は、アナログ信号141(入力信号)をデジタル変換するAD変換器が異なる点を除けば、入力インタフェース回路122と同様の構成を有する。

【0032】

出力ユニット150は、出力インタフェース回路152と、プルアップ抵抗153、154と、選択切換回路155a、155bと、により構成されている。出力インタフェース回路152は、DA変換器が異なる点を除けば、出力インタフェース回路132と同様の構成を有し、アナログ負荷151に接続されている。

ここでは、入力インタフェース回路122、142と、出力インタフェース回路132、152とを総称して、入出力インタフェース回路という。

【0033】

入力ユニット120内において、プルアップ抵抗123の一端は、定電圧電源線Vcc(たとえば、DC5V)に接続されている。プルアップ抵抗123の他端は、入力インタフェース回路122内のカード情報格納メモリに接続されており、カード情報格納メモリに、接続位置信号MDLを供給して接続位置論理情報として記憶するようになっている。

【0034】

なお、終端ブロック160に接続される最終段の出力ユニット150の場合には、プルアップ抵抗153の他端が、終端ブロック160内の接続位置確認回路LSTによってグランド回路GNDに接続されており、接続位置信号(接続位置論理情報)MDLが、論理レベル「L」となるように構成されている。これに対し、中間位置にある他の入出力ユニット120、130、140の場合には、接続位置信号MDLは、論理レベル「H」(ハイ)となっている。

【0035】

一対の論理和素子からなる選択切換回路125a、125bにおいて、それぞれの第1の入力端子は、プルアップ抵抗124に接続されており、プルアップ抵抗124を介して常時は論理レベル「H」に設定されている。一方の選択切換回路125aの第2の入力端子には、入力インタフェース回路122内のカード情報格納メモリに格納されている局番設定完了信号(個別完了論理情報)FINの反転論理信号が入力され、他方の選択切換回路125bの第2の入力端子には、カード情報格納メモリに格納されている局番設定完了信号FINがそのまま入力されている。局番設定完了信号FINは、局番設定が完了していると、論理レベル「H」となる。

【0036】

局番設定検索信号CF1は、選択切換回路125a、125bのそれぞれの第1の入力端子に印加されており、局番設定を行うために局番設定検索信号CF1を論理レベル「L」とした場合に、たとえば入力ユニット120の局番設定が未完了であれば、選択切換回路125bの出力が論理レベル「L」となって、入力ユニット120がマイクロプロセッサ111との交信権を得ることになる。

【0037】

マイクロプロセッサ111との交信権を取得した入出力ユニットは、貫通バス信号線BUSを介して、マイクロプロセッサ111に対してカード情報や管理番号の情報を送信する。また、カード情報および管理番号の情報を受信したマイクロプロセッサ111は、次のタイミングで設定された局番情報(以下、「設定局番」ともいう)の値を、貫通バス信号線BUSを介して送信し、設定局番に該当する入出力ユニットの入力インタフェース回路内の局番設定メモリに書込む。

【0038】

続いて、マイクロプロセッサ111により設定局番が書き込まれた入出力ユニットは、書込み設定された局番情報を、マイクロプロセッサ111に対して確認返信する。これにより、マイクロプロセッサ111から局番設定完了信号FINが送信され、該当する入出力ユニットは、局番設定完了信号FINをカード情報として記憶する。

【0039】

初段の入力ユニット120の局番設定が完了すると、選択切換回路125aの第2の入力は、論理レベル「L」となり、局番設定検索信号CF1の論理レベル「L」が次段の選択切換回路135a、135bの第1の入力端子に印加される。以下、同様にして、局番設定の順次処理が実行されることになる。

【0040】

出力ユニット130は、コネクタ(図示せず)を介して入力ユニット120の端面位置に接続されており、出力ユニット130には、出力端子台(図示せず)を介して、外部負荷131が接続されている。外部負荷131は、たとえば、操作盤に設けられた各種の表示ランプ、アクチェータ駆動用の電磁弁、または、モータ駆動用の電磁継電器などからなる。1台の出力ユニット130には、たとえば8点の出力信号が接続可能であるが、さらに多くの外部負荷131が接続される場合には、出力ユニット130の接続台数が増設されるようになっている。

【0041】

出力ユニット130内において、出力インタフェース回路132は、外部負荷131を駆動するための駆動信号のラッチメモリを貫通バス信号線BUSに接続する出力信号回路と、カード情報格納メモリと、局番設定メモリと、管理番号格納メモリと、を有する。プルアップ抵抗133、134および選択切換回路135a、135bは、入力ブロック120の場合と同様に構成されている。

【0042】

入力ユニット140には、たとえば4点のアナログ信号141が入力されている。入力ユニット140内において、入力インタフェース回路142内の多チャンネルAD変換器は、アナログ信号141をデジタル変換し、4チャンネルのアナログ入力に対する各12ビットのデジタル変換データをマイクロプロセッサ111に送信するようになっている。

【0043】

出力ユニット150には、たとえば4点のアナログ負荷151が接続されている。出力ユニット150内において、出力インタフェース回路152内の多チャンネルDA変換器は、マイクロプロセッサ111から送信された4チャンネル12ビットのデジタルデータをアナログ変換し、変換後のアナログ信号をアナログ負荷151に供給するようになっている。

【0044】

入出力ユニット140、150の内部にも、入出力ユニット120、130の場合と同様に、カード情報格納メモリ、局番設定メモリおよび管理番号格納メモリを有する入出力インタフェース回路142、152が設けられている。また、プルアップ抵抗143、144、153、154、および、選択切換回路145a、145b、155a、155bは、それぞれ入出力ユニット120、130の場合と同様に構成されている。

【0045】

最終段の入出力ユニット(出力ユニット150)に接続された終端ブロック160は、貫通バス信号線BUSの末端位置に接続された終端処理回路162を備えている。終端処理回路162は、高速信号の反射防止用のインピーダンス素子を、グランド回路GNDまたは定電圧電源線Vccに対して接続するためのプルダウン回路またはプルアップ回路により構成されている。

【0046】

終端ブロック160内の接続位置確認回路LSTは、最終段に接続された出力ユニット150内のプルアップ抵抗153の他端を、終端ブロック160内でグランド回路GNDに接続して論理反転させる回路を構成している。なお、プルアップ抵抗123、133、143、153をプルダウン抵抗に変更し、終端ブロック160内で定電圧電源線Vccに接続して論理反転させるようにしてもよい。

【0047】

終端ブロック160内の終端処理確認回路ENDは、ロウレベルの論理発生回路を構成しており、終端ブロック160が接続されていることを示すロウレベルの接続確認信号END1を生成し、各入出力ユニット120〜150を貫通してマイクロプロセッサ111に伝達する。なお、接続確認信号END1の伝送線に設けられたプルアップ抵抗Rをプルダウン抵抗に変更し、終端ブロック160内の終端処理確認回路ENDにおいて、定電圧電源線Vccに接続することにより、ハイレベルの論理信号を与えるようにしてもよい。

【0048】

入出力ユニット120〜150内のカード情報格納メモリに格納されるカード情報は、少なくとも、入出力インタフェース回路122〜152が入力インタフェース回路であるかまたは出力インタフェース回路であるかを識別する品種別論理情報と、局番設定処理が完了しているか否かの設定状態を識別する局番設定完了信号(個別完了論理情報)FINと、入出力インタフェース回路122〜152の接続位置が最終接続位置であるか、または最終接続位置以外の中間接続位置であるかを識別する接続位置信号(接続位置論理情報)MDLと、を含む。

【0049】

なお、品種別論理情報としては、ON/OFF信号(開閉信号121、外部負荷131)用の入出力ユニットであるか否か、アナログ(アナログ信号141、アナログ負荷151)用の入出力ユニットであるか否か、の識別信号も付加されている。たとえば、アナログ用の入出力ユニットである場合には、マイクロプロセッサ111と多チャンネルAD変換器または多チャンネルDA変換器との間で、複数回の読出しまたは書込み操作が行われるようになっている。

【0050】

また、ON/OFF信号用の入出力ユニットである場合も、大小2種類(16点単位、8点単位)の入出力ユニットがあるので、8点単位のものか、または16点単位のものかを識別する信号も付加されている。また、入出力各8点の混合入出力ユニットが適用されてもよいが、いずれの場合も、たとえば入力8点、または出力8点当たりで1つの局番が割り振られるようになっている。

【0051】

また、アナログ信号用の入出力ユニットである場合も、大小2種類(8点単位、4点単位)の入出力ユニットがあるので、4点単位、8点単位、または、入力4点かつ出力4点の混合タイプなどに応じて、異なる品種別論理情報が与えられるようになっている。

【0052】

また、局番は、たとえば、アナログ4点単位で1つの局番が割り振られるようになっている。各種の品種別論理情報は、データバスに対して接続または解放するために設けられたデータセレクタの複数ビットの入力端子を、プリント基板によってグランド回路GNDに接続するか、または定電圧電源線Vccに接続するか、によって決定される配線パターン情報となっている。品種別論理情報の記憶手段は、ここでは総称として個別メモリとしているが、実際には読出しおよび書込みの行えるメモリが使用されなくてもよい。

【0053】

貫通バス信号線BUSは、必要時に入出力インタフェース回路122〜152に対する局番指定用のアドレスバスとして使用され、また、必要時にカード情報や管理番号の情報を読出すか、外部からの入力信号を読出すための読出し用のデータバスとして使用され、さらに、局番設定信号や外部負荷131に対する制御出力データを書込むための書込み用のデータバスとして使用される。

【0054】

上記の貫通バス信号線BUSの使い分けは、マイクロプロセッサ111が発生するコマンドデータに依存して決定される。また、多数の入出力情報を有するアナログ用の入出力インタフェース回路142、152に対しては、複数回の交信によって全データの転送が行われ、読み書きの実行タイミングは、マイクロプロセッサ111が発生する制御信号(タイミング信号)に基づいて決定される。

【0055】

以上の説明では、ON/OFF入出力の場合には、入力8点または出力8点に対して1つの局番を付与し、アナログ入出力の場合には、入力4チャンネルまたは出力4チャンネルに対して1つの局番を付与したが、これは単なる一例であって、さらに多い入出力点数や入出力チャンネルのものに対して、または、入出力混合のものに対して1つの局番を付与する仕様としてもよい。

【0056】

この発明の実施の形態1に係るプログラマブルコントローラ100Aにおいて、入出力ユニット120、130、140、150には、固体識別のための管理番号が付与されており、各管理番号は、運転前に、基本ユニット110A内の管理情報格納領域199Aに転送保存されている。運転開始時に、管理番号の情報が変化していると運転停止されるので、入出力ユニット120、130、140、150を保守交換する場合には、暗証番号を用いて管理番号の変更処理が行われる。これにより、入出力ユニット120、130、140、150の不用意な保守交換を防止することのできるプログラマブルコントローラ100Aが得られる。

【0057】

次に、図2〜図7のフローチャートを参照しながら、図1に示したこの発明の実施の形態1による動作について詳細に説明する。図2はプログラマブルコントローラ100Aの運転(RUN)動作を示している。

【0058】

図2において、ステップ205、206は、第1および第2の管理忌避手段に対応し、ステップ207aは照合判定手段に対応し、ステップ208、209bは、編成異常検出手段および編成異常処理手段に対応し、ステップ213a、213bは、それぞれ脱落異常検出手段に対応している。

【0059】

まず、電源スイッチ(図示せず)が投入されて(ステップ200)、外部電源103からプログラマブルコントローラ100Aに給電されると、マイクロプロセッサ111が動作を開始し(ステップ201)、マイクロプロセッサ111は、現場のオペレータの操作によるRUN/STOP(運転/停止)指令入力(図示せず)の状態を参照して、RUN入力の有無を判定する(ステップ202a)。

【0060】

ステップ202aにおいて、RUNスイッチが閉路(ON)されていてRUN入力有り(すなわち、YES)と判定されれば、続いて、プログラマブルコントローラ100Aの運転準備が完了しているか否かを判定し(ステップ203a)、準備完了している(すなわち、YES)と判定されればステップ204に移行し、また、準備完了していない(すなわち、NO)と判定されればステップ203bに移行する。

【0061】

ステップ203aにおいては、準備完了か否かを判定する。具体的には、ステップ314(図4とともに後述する)によって編成完了フラグのセット状態(編成記憶完了を示す)が管理情報格納領域199Aに格納されているか否かを判定する。または、ステップ502(図7とともに後述する)によってシーケンスプログラムがプログラムメモリ115Aに格納され、代表としてEND命令が書込まれているか否かを判定する。これにより、編成完了フラグがセットされ、かつEND命令が書込まれていれば、準備完了と判定することができる。

【0062】

一方、ステップ202aにおいて、RUNスイッチが開路(OFF)されていてSTOPモードである(すなわち、NO)と判定されれば、ステップ209a(後述する)でセットされた初回フラグをリセットし(ステップ202b)、中継端子Aを介して、図4内のステップ301に移行する。

【0063】

ステップ203aに続くステップ203bにおいては、準備未完了状態であることを警報表示器119によって表示し、動作終了ステップ210に移行する。動作終了ステップ210において、マイクロプロセッサ111は、他の制御動作を実行して、所定時間以内に動作開始処理(ステップ201)に復帰移行し、循環動作する。

【0064】

つまり、準備完了していない状態で、RUNスイッチが閉路(ON)されると、ステップ201、202a、203a、203b、210、201が循環動作して、RUNスイッチが開路(OFF)されるのを待機する状態となり、RUNスイッチが開路(OFF)されたことによって、図4内のステップ301に移行するようになっている。

【0065】

ステップ204においては、RUNモードでの初回動作であるか否かを判定する。具体的には、ステップ209aによって初回フラグがセットされているか否かを監視することによって、RUNモードでの初回動作であるか否かを判定する。もし、初回動作である(すなわち、YES)と判定されればステップ205に移行し、初回動作でない(すなわち、NO)と判定されれば、ステップ211(後述する)に移行する。

【0066】

ステップ205においては、暗証番号の有無を判定する。具体的には、ステップ554a(図6とともに後述する)で暗証番号が入力されて管理情報格納領域199Aに格納されているか否かにより、暗証番号の有無を判定する。もし、暗証番号が有り(すなわち、YES)と判定されればステップ206に移行し、暗証番号が格納されていない(すなわち、NO)と判定されればステップ207bに移行する。

【0067】

ステップ206においては、管理番号による管理の要否を判定する。具体的には、ステップ358b(図3とともに後述する)によって管理番号による管理が必要であるとの編成指令が送信されて、編成指令が管理情報格納領域199Aに格納されているか否かにより、管理の要否を判定する。もし、管理が必要である(すなわち、YES)と判定されればステップ207aに移行し、管理が不要である(すなわち、NO)と判定されれば、ステップ207bに移行する。

【0068】

ステップ207aにおいては、現在のカード編成状態を読出し、管理および編成を確認する。このとき、マイクロプロセッサ111は、既に設定完了している局番を指定し、これに応答して指定された局番の入出力ユニットが自分のカード情報および管理番号の情報をマイクロプロセッサ111に送信する。これにより、管理番号を含むカード編成を確認することができる。

【0069】

ステップ207bにおいては、現在のカード編成状態を読出して確認する。具体的には、基本ユニット110A内のマイクロプロセッサ111は、既に設定完了している局番を指定し、これに応答して、指定された局番の入出力ユニットは、自分のカード情報をマイクロプロセッサ111に送信する。これにより、マイクロプロセッサ111は、管理番号を除外したカード編成を確認することができる。

【0070】

続いて、ステップ313(図4とともに後述する)で記憶されたカード編成情報と、ステップ207aまたは207bによって確認された現在のカード編成状態とを比較し、比較結果が不一致であるか否かにより編成が異常であるか否かを判定する(ステップ208)。ステップ208における比較結果が不一致であって編成が異常である(すなわち、YES)と判定されれば、ステップ209bに移行し、比較結果が一致であって編成が正常(すなわち、NO)と判定されれば、ステップ213aに移行する。

【0071】

ステップ209bにおいては、カード編成異常の発生をデータメモリ116に書込み記憶するとともに、異常表示LEDからなる警報表示器119を点滅表示して異常報知を行い、さらに、出力ユニット130、150の出力発生を停止状態(または、現状保持状態)にして、動作終了ステップ210に移行する。なお、ステップ209bにおいて、出力ユニット130、150の出力停止状態または現状保持状態の選択は、データメモリ115Aに対してあらかじめ選択パラメータを設定しておくことによって決定される。

【0072】

一方、ステップ213aにおいて、マイクロプロセッサ111は、接続確認信号END1の論理レベルを判定することにより、入出力ユニット120、130、140、150および終端ブロック160が正常に接続されている(終端OK)か否かを判定する。

【0073】

ステップ213aにおいて、接続確認信号END1の論理レベルが「H」であって異常状態である(すなわち、NO)と判定されれば、ステップ209bに移行し、論理レベルが「L」であって正常である(すなわち、YES)と判定されれば、初回フラグをセットして(ステップ209a)、後述する入力処理(ステップ215)に移行する。

【0074】

一方、ステップ204により初回動作でない(すなわち、NO)と判定された場合に実行されるステップ211においては、図7内のステップ502によりプログラムメモリ115Aに書込まれたシーケンスプログラムを実行する。

【0075】

続いて、上記シーケンスプログラムの中にあるEND命令が実行されたか否かを判定し(ステップ212)、END命令が実行されていない(すなわち、NO)と判定されれば、ステップ211に復帰してEND命令が実行されるまでステップ211を繰り返し循環実行する。そして、ステップ212において、END命令が実行された(すなわち、YES)と判定されれば、次の判定処理(ステップ213b)に移行する。

【0076】

つまり、ステップ211、212により一巡のシーケンスプログラムが実行された後、続いて、接続確認信号END1の論理レベルを判定することにより、入出力ユニット120、130、140、150および終端ブロック160が正常に接続されている(終端OK)か否かを判定する(ステップ213b)。

【0077】

ステップ213bにおいて、接続確認信号END1の論理レベルが「H」であって異常状態である(すなわち、NO)と判定されれば、前述のステップ209bに移行し、論理レベルが「L」であって正常である(すなわち、YES)と判定されれば、ステップ211によるシーケンスプログラムの実行結果として、出力ユニット130、150に対する制御出力信号の書込み(出力処理)を実行する(ステップ214)。

【0078】

最後に、ステップ214に続いて、また、前述の初回フラグのセット(ステップ209a)に続いて、入力処理(ステップ215)が実行され、マイクロプロセッサ111は、入力ユニット120、140から入力信号を読出して、データメモリ116に転送する。以下、ステップ202aに復帰し、RUN/STOPスイッチがRUN状態を維持していて、準備完了(すなわち、YES)と判定されれば、ステップ204を経て、再びシーケンスプログラムの実行(ステップ211)が繰り返される。

【0079】

なお、ステップ214における出力信号の書込み、ならびに、ステップ215における入力信号の読出しに際しては、マイクロプロセッサ111によって指定された局番と一致する設定局番を有する入出力ユニットが、マイクロプロセッサ111との交信権を取得するようになっている。

【0080】

以上の動作を整理して概括説明すると、ステップ205は、第1の管理忌避手段として機能し、暗証番号が入力されていないときには管理番号の照合を行わないようにする。また、ステップ206は、第2の管理忌避手段として機能し、ステップ554aによって暗証番号が入力されていても、ステップ358aによって管理番号の照合を行わない編成指令が与えられているときには、ステップ207bによって管理番号を除外したカード編成のみをチェックする。

【0081】

ステップ207a、207bは、照合判定手段として機能し、ステップ358bによって管理番号が必要であるとして編成指令が出されたときに、管理番号およびカード編成情報の両方について、現在の状態とステップ313によって編成記憶されたときの状態とを比較判定する。

【0082】

ステップ208は、ステップ207a、207b(照合判定手段)と関連した編成異常検出手段として機能し、ステップ207aまたはステップ207bによる確認結果に異常があるか否かを検出し、入出力インタフェース回路122、132、142、152から得られるカード情報および管理番号の情報の現在状態が、カード編成記憶手段(ステップ313)に記憶されているカード情報および管理番号と一致しているか否かを判定する。

【0083】

ステップ209bは、編成異常処理手段として機能し、編成異常検出手段(ステップ208)が編成異常を検出した場合、または、脱落異常検出手段(ステップ213a、213b)によって終端異常が検出された場合に機能して、異常状態をデータメモリ116に書込み記憶するとともに、異常発生を警報表示器119に表示させ、制御出力を停止状態または現状保持状態にする。

【0084】

ステップ213aは、第1の異常判定手段または脱落異常検出手段として機能し、運転開始時に実行されて、終端ブロック160が未接続であるか、接続されていてもコネクタの接触不良などによって接続確認信号END1が論理レベル「L」にならないときに、終端処理未完了の判定を行う。ステップ213bは、第1の異常判定手段として機能し、運転中に実行される。

【0085】

次に、図1とともに、図3および図4のフローチャートを参照しながら、この発明の実施の形態1による編成操作について説明する。図3のフローチャートは、基本ユニット110Aに接続された外部ツール108の動作を示し、図4のフローチャートは、図2内の中継端子Aに続くマイクロプロセッサ111の動作を示している。

【0086】

なお、マイクロプロセッサ111と外部ツール108との間では、シリアルインタフェース118を介して交信が行われており、一方が送信して他方が受信すると、受信確認の返信が行われ、送信指令内容が受信側で実行されると、実行確認返信が行われるようになっているが、図3および図4においては、簡略化のため、両者の連携動作については図示を省略する。

【0087】

図3において、まず、外部ツール108が接続されたことによって、外部ツール108内のマイクロプロセッサ(図示せず)が動作を開始し(ステップ350)、暗証番号の有無(暗証番号が登録されているか否か)を検索判定して(ステップ351)、暗証番号が登録されている(すなわち、YES)と判定されれば、ステップ352に移行し、暗証番号が登録されていない(すなわち、NO)と判定されれば、ステップ354に移行する。

【0088】

ステップ352においては、マイクロプロセッサ111との間の暗証番号の入力処理により確認送信が行われる。続いて、マイクロプロセッサ111に既に登録されていた暗証番号と、ステップ352で外部ツール108から入力された暗証番号とが一致しているか否かを判定し(ステップ353)、両者が一致している(すなわち、YES)と判定されれば、ステップ354に移行し、不一致である(すなわち、NO)と判定されれば、ステップ359に移行する。なお、暗証番号の照合判定処理は、外部ツール108側で実行されてもよいが、実際には、基本ユニット110A側で実行され、判定結果を外部ツール108に返信するようになっている。

【0089】

ステップ354において、外部ツール108は、基本ユニット110Aの管理情報格納領域199Aの内容を読出す。続いて、ステップ354の読出し結果に応じて、編成完了フラグがセットされていた(編成が完了)か否かを判定し(ステップ355a)、編成完了(すなわち、YES)と判定されれば、ステップ356に移行し、編成未完了(すなわち、NO)と判定されれば、ステップ357に移行する。

【0090】

ステップ356においては、画面表示された編成変更要否のボタンのうち、どちらかがオペレータによって選択されることに応答して、編成変更が必要であるか否かを判定し、編成変更が必要である(すなわち、YES)と判定されれば、ステップ357に移行し、編成変更が必要でない(すなわち、NO)と判定されれば、中継端子Xを経由して、図6内のステップ550に移行する。

【0091】

ステップ357においては、管理番号の要否を決定する選択ボタンの画面表示が行われ、オペレータが管理番号の要否を決定してどちらかのボタンを押すことに応答して、管理番号が必要であるか否かを判定し、管理番号が必要でない(すなわち、NO)と判定されれば、ステップ358aに移行し、管理番号が必要である(すなわち、YES)と判定されれば、ステップ358bに移行する。

【0092】

ステップ358aにおいては、管理番号による管理を行わない場合の編成指令を送信し、ステップ355bに移行する。また、ステップ358bにおいては、管理番号による管理を行う場合の編成指令を送信し、ステップ355bに移行する。なお、ステップ358a、358bにおいては、それぞれ編成指令が送信されるとともに、ステップ314(図4とともに後述する)でセットされていた編成完了フラグがリセットされる。

【0093】

ステップ355bにおいては、ステップ358a、358bでリセットされた編成完了フラグが、後述のステップ314によって再度セットされるか否かを監視して、編成が完了したか否かを判定し、編成完了フラグのセットが未完了(すなわち、NO)と判定されれば、ステップ357に復帰する。

【0094】

また、ステップ355bにおいて、既に選択されているステップ358aまたはステップ358bが引き続き送信されて、ステップ314によって編成完了フラグがセットされている(すなわち、YES)と判定されれば、中継端子Xを介して図6内のステップ550に移行する。

【0095】

一方、ステップ353で暗証番号の不一致が判定された場合に実行されるステップ359においては、外部ツール108に対して異常表示が行われ、動作終了ステップ460に移行する。このとき、所定時間内に、再度、動作開始ステップ350に復帰移行するようになっている。なお、オペレータは、ステップ359による異常表示画面に応じて、暗証番号の再入力を行うか、または、暗証番号が不明な場合には、全データの消去処理を行う。

【0096】

図4の処理ルーチンは、図2内のステップ202bに続いて実行される。図4において、ステップ210は、前述(図2参照)と同様の動作終了処理である。ステップ302は、編成変更手段を構成し、ステップ303は、第1の異常判定手段を構成し、ステップ304は、設定異常処理手段を構成し、ステップ310は、第3の異常判定手段を構成し、ステップ313は、カード編成記憶手段を構成している。また、ステップ210、304、305、310、311a、311b、312、400は、局番設定手段を構成している。

【0097】

図4において、まず、マイクロプロセッサ111は、ステップ314(後述する)で編成完了フラグがセットされたか否かにより、編成記憶が完了しているか否かを判定する(ステップ301)。なお、初回動作においては、編成記憶が完了していない(すなわち、NO)と判定されて、ステップ303に移行し、次回動作においては、編成完了フラグがセットされている(すなわち、YES)と判定されて、ステップ302に移行する。

【0098】

ステップ302においては、ステップ358aまたはステップ358bによる編成指令を受信したか否かを判定し、受信している(すなわち、YES)と判定されれば、ステップ303に移行し、編成指令を受信していない(すなわち、NO)と判定されれば、中継端子Bを介して図7内のステップ500に移行する。

【0099】

ステップ303においては、接続確認信号END1の論理レベルに応じて、終端ブロック160が接続されている(終端処理が完了)か否かを判定し、終端ブロック160が接続されていて接続確認信号END1の論理レベルが「L」であり、終端処理が完了している(すなわち、YES)と判定されれば、ステップ305に移行する。

【0100】

また、ステップ303において、終端ブロック160が接続されていないか、またはコネクタの接触不良によって一部の入出力ユニットが脱落状態となり、接続確認信号END1の論理レベルが「H」となって、終端処理が完了していない(すなわち、NO)と判定されれば、ステップ304に移行する。

【0101】

ステップ304においては、異常状態をデータメモリ116に記憶するとともに、警報表示器119の異常表示LEDを点滅表示して異常報知し、動作終了ステップ210に移行する。動作終了ステップ210において、マイクロプロセッサ111は、他の制御動作を実行した後、図2内の動作開始ステップ201に移行する。

【0102】

したがって、ステップ303において、終端ブロック160が未接続(すなわち、NO)と判定された場合には、図2および図3内のステップ201、202a、202b、301、303、304、210、201を循環動作して異常警報が持続し、この状態を脱出するためには、電源スイッチ(図示せず)を開路する必要がある。

【0103】

ステップ305においては、図3内のステップ358aまたはステップ358bによる編成指令を受信しているか否かを判定し、受信していない(すなわち、NO)と判定されれば、ステップ305に復帰して編成指令の待機動作を行い、編成指令を受信した(すなわち、YES)と判定されれば、ステップ400に移行して局番設定処理(図5とともに後述する)を実行した後、ステップ310に移行する。

【0104】

ステップ310においては、図5内のステップ414bで受信した局番情報および管理番号の情報が、ステップ413a(図5参照)で送信した設定局番やステップ404(図5参照)で読出した管理番号と一致しているか否かにより、局番情報および管理番号の情報が正常であるか否かを判定する。ステップ310において、各情報が相互に一致していて正常である(すなわち、YES)と判定されれば、ステップ311aに移行し、相互に不一致であって正常でない(すなわち、NO)と判定されれば、ステップ304に移行する。

【0105】