プログラムにより動作する装置における、プログラムの更新方法、再起動の方法、及びプログラムの更新方法を実行するプログラム

【課題】無線基地局(BTS)において、プログラムのバージョンアップ動作中或いはその前後にリセット等が生じた場合であっても、短時間で正常にBTSを再起動させる。

【解決手段】更新後のプログラムを第1のメモリ206にダウンロードする第1の工程と、プログラム更新中であることを記憶する第2の工程と、前記更新後のプログラムを前記第1のメモリ206から不揮発性メモリである第2のメモリ205へとコピーする第3の工程と、前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、を前記順序で含み、再起動の際には、プログラム更新中であることが記憶されている場合には、前記第1のメモリ206に格納されたプログラムを実行し、プログラム更新が終了したことが記憶されている場合には、前記第2のメモリ205に格納されたプログラムを実行する。

【解決手段】更新後のプログラムを第1のメモリ206にダウンロードする第1の工程と、プログラム更新中であることを記憶する第2の工程と、前記更新後のプログラムを前記第1のメモリ206から不揮発性メモリである第2のメモリ205へとコピーする第3の工程と、前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、を前記順序で含み、再起動の際には、プログラム更新中であることが記憶されている場合には、前記第1のメモリ206に格納されたプログラムを実行し、プログラム更新が終了したことが記憶されている場合には、前記第2のメモリ205に格納されたプログラムを実行する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プログラムにより動作する装置における、プログラムの更新方法に関し、特に、プログラムを更新中或いはその前後に装置の再起動が行われても、装置が正常に起動し得るプログラムの更新方法に関する。

【0002】

また、本発明は、プログラムにより動作する装置の再起動の方法に関し、特に、プログラムを更新中或いはその前後に装置の再起動が行われても、装置が正常に起動し得る再起動の方法に関する。

【背景技術】

【0003】

従来のプログラムの更新方法及び装置の再起動の方法の一例を、移動通信網を例にとって説明する。一般的な移動通信網の構成を概念的に図1に示す。図1において、移動通信網は、無線基地局(BTS)101、基地局制御局(BSC)102、移動通信交換局(MSC)103、移動通信保守監視卓(OMC)104、及び移動通信端末(MS)105より構成されている。BTS(101)は、MSC(103)、BSC(102)、OMC(104)と伝送路で接続されている。伝送路の中には、例えば、OMC(104)からBTS(101)に到達する、BTS(101)が動作するためのプログラムを送受信するための信号が対上位局信号210として導通している。BTS(101)は、BSC(102)からの制御信号によりBSC(102)からの音声及び非音声(データ)信号を高周波信号に変換し空間に放射し、またMS(105)が音声及び非音声信号を高周波信号に変換し空間に放射した高周波信号を受信しBSC(102)に送信する。BSC(102)は、MSC(103)により制御され、通常、数十台のBTSを配下に接続し、主にその無線回線を制御する。MSC(103)は、通常、数十台のBSCを配下に接続し、主に移動通信網の有線回線交換制御を行う。OMC(104)は、MSC(例えば103)、BSC(例えば102)、及びBTS(例えば101)と接続される。OMC(104)は、MSC(例えば103)、BSC(例えば102)、及びBTS(例えば101)の状態を監視・確認し、また、それらのリセットを遠隔的に制御することができる。OMC(104)は、各装置が動作するためのプログラムを格納し、必要に応じてそのプログラムを各装置に遠隔的にダウンロードさせることができる。

【0004】

従来の一般的なBTSの内部構成を概念的に図7に示す。図7において、BTS(701)は、伝送路インタフェース(IF)部702と、書き込み制御部703と、起動用読み出し専用メモリ(起動用ROM)704と、不揮発性記憶部705と、揮発性記憶部706と、それらを結ぶ装置内バス(707)と、から構成されている。書き込み機能部703は、CPU(Central Processing Unit)(図示せず)を用いて実現されている。さらに、このBTS(701)は、BSC(102)及びMSC(103)を介して、移動通信保守監視卓(OMC)104との間で、対上位局信号710を送受信する。

【0005】

このBTS(701)の運用中に、不揮発性記憶部705に格納されたプログラムのバージョンアップが必要になる場合がある。

【0006】

このバージョンアップは、図8に示す工程で行われる。図8はBTS(701)の書き込み制御部(703)の動作の一例である。すなわち、ダウンロード開始信号を受信すると(S800)、書き込み制御部(703)は、OMC(104)からMSC(103)及びBSC(102)を介して、更新プログラムを伝送路IF部(702)により受信し、不揮発性記憶部705に格納する(S801)。

【0007】

或いは、このバージョンアップは、図9に示す工程で行われる。図9はBTS(701)の書き込み制御部(703)の動作の他の一例である。すなわち、ダウンロード開始信号を受信すると(S900)、書き込み制御部(703)は、OMC(104)からMSC(103)及びBSC(102)を介して、更新プログラムを伝送路IF部(702)により受信し、揮発性記憶部706に格納する(S901)。さらに、書き込み制御部703は、その更新プログラムを揮発性記憶部706から不揮発性記憶部705にコピーする(S902)。

【0008】

ところで、BTSのプログラムのこのようなバージョンアップ動作中に、電源断或いはリセット(以下リセット等という)が生じると、BTSが起動できなくなることがあった。具体的には、以下の通りである。

【0009】

例えば、図8に示す工程で、書き込み制御部703が更新プログラムを不揮発性記憶部705に書き込んでいる最中(S801)に、BTS(701)にリセットが実行されたとする。その後再起動する際に、BTS(701)のCPUは起動用ROM(704)に格納された初期処理のプログラムに従って、不揮発性記憶部705に格納されたプログラムを実行する。しかし、不揮発性記憶部705には書き込み制御部703が更新プログラムを書き込んでいる途中(S801)であったため、旧プログラムも更新プログラムも不完全にしか格納されておらず、BTS(701)は起動できない。

【0010】

また、例えば、図9に示す工程で、書き込み制御部703がOMC(104)から受信して揮発性記憶部706に一旦格納した更新プログラムを揮発性記憶部706から不揮発性記憶部705にコピーしている最中(S902)に、BTS(701)にリセットが実行された場合も同様である。

【0011】

この問題を解決するために、いくつかの技術が提案されている。

【0012】

例えば、特許文献1には、とりあえず再起動を試み、もし再起動に失敗した場合には、旧プログラムで再度の再起動を行なうという方法が記載されている。また、特許文献2には、プログラムをリモートダウンローダとメインの制御プログラムに分け、それぞれ別個に上位装置から転送し、リモートダウンローダについてのみ新旧のバージョンをフラッシュROM中のそれぞれ異なる領域に格納するという2面管理がなされている。この場合、新リモートダウンローダは旧リモートダウンローダによりダウンロードされ、メインの制御プログラムの新しいバージョンは新リモートダウンローダによりダウンロードされる。さらに、特許文献3には、更新プログラムを一時格納メモリにダウンロードする前に、一時格納メモリに格納されていた旧プログラムをバックアップメモリに保存しておき、更新指示コマンドを受信する前に装置が再起動した場合には、バックアップメモリにある旧プログラムをプログラムエリアに転送して装置運用を開始する方法が記載されている。

【0013】

【特許文献1】特開2001−134428号公報

【特許文献2】特開2004−102893号公報

【特許文献3】特開平9−325891号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

特許文献1記載の方法では、実際に装置を再起動することによって新プログラムが正常かどうかを判定している。このため、新プログラムに問題があった場合、BTSが正常な動作を再開するまでには、再起動、失敗判定、再度の再起動という複雑な工程が必要であり、長時間を要するという問題がある。特許文献2には、メインの制御プログラムのダウンロード中にリセット等が生じた場合に装置を正常に再起動させる方法については、開示がない。したがって、いかなる場合にも正常にBTSを再起動させるという課題は解決されていない。特許文献3記載の方法では、一時格納メモリとバックアップメモリとプログラムエリアとの計3セットのメモリが必要である。しかも、リセット等が生じた場合には、一時格納メモリからバックアップメモリへの旧プログラムの転送と、バックアップメモリからプログラムエリアへの旧プログラムの転送との計2回の転送が必要である。よって、ソフトウエアおよびハードウエアに掛かる負荷が大きく、コストに課題を有している。

【0015】

本発明の目的は、従来の方式のこのような課題を解決することである。すなわち、本発明は、BTSにおいて、プログラムのバージョンアップ動作中或いはその前後にリセット等が生じた場合であっても、短時間で正常にBTSを再起動させることを目的としている。また、本発明は、できる限り少ないハードウェア或いはできる限り少ない工程で、これらの目的を安価に実現することを、目的としている。

【課題を解決するための手段】

【0016】

本発明のプログラムの更新方法は、更新後のプログラムを第1のメモリにダウンロードする第1の工程と、プログラム更新中であることを記憶する第2の工程と、前記更新後のプログラムを前記第1のメモリから前記不揮発性メモリである第2のメモリへとコピーする第3の工程と、前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、を前記順序で少なくとも含むことを特徴とする。

【0017】

本発明のプログラムの更新方法は、或いは、前記第3の工程の前に、前記第3の工程を実行する中央演算処理装置の使用率と所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を行うことを特徴とする。

【0018】

本発明のプログラムの更新方法は、或いは、前記第3の工程において、前記更新後のプログラムの一部を前記第1のメモリから不揮発性メモリである第2のメモリへコピーするごとに、前記第3の工程を実行する前記中央演算処理装置の使用率と前記所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を継続することを特徴とする。

本発明のプログラムの更新方法は、或いは、前記所定のサイズが可変であることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記所定の値が可変であることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記第1のメモリが揮発性メモリであることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記第1のメモリが不揮発性メモリであることを特徴とする。

本発明のプログラムの更新方法は、或いは、当該装置が移動通信網の基地局であることを特徴とする。

【0019】

本発明の再起動の方法は、プログラム更新中であることが記憶されている場合には、第1のメモリに格納されたプログラムを実行し、プログラム更新が終了したことが記憶されている場合には、不揮発性メモリである第2のメモリに格納されたプログラムを実行することを特徴とする。

本発明のプログラムは、上記プログラムの更新方法を実行することを特徴とする。

或いは、本発明のプログラムは、上記再起動の方法を実行することを特徴とする。

【発明の効果】

【0020】

本発明によれば、BTSにおいて、更新プログラムのバージョンアップ動作中或いはその前後にリセット等が生じた場合であっても、再起動に失敗することなく、短時間で正常にBTSを再起動させることができる。また、本発明によれば、少ないハードウェア或いは少ない工程で、正常にBTSを再起動することができる。

【発明を実施するための最良の形態】

【0021】

本発明を移動体通信網に適用した実施の形態について、図面を用いて説明する。

《実施例1》

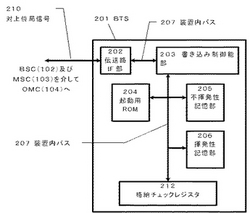

本発明の第1の実施例であるBTSの構成を概念的に図2に示す。図2において、BTS(201)は、伝送路IF部202と、書き込み制御部203と、起動用ROM(204)と、不揮発性記憶部205と、揮発性記憶部206と、格納チェックレジスタ212と、伝送路それらを結ぶ装置内バス(207)と、から構成されている。さらに、このBTS(201)は、BSC(102)及びMSC(103)を介して、移動通信保守監視卓(OMC)104との間で、対上位局信号210を送受信する。

【0022】

伝送路IF部202は、伝送路にてOMC(104)と、装置内バス(207)にて書き込み制御部203と、それぞれ接続されている。書き込み制御部203は、装置内バス(207)にて伝送路IF部202と、装置内バス(207)にて不揮発性記憶部205、揮発性記憶部206、及び格納チェックレジスタ212とに接続されている。書き込み制御部203は、CPU(図示せず)を用いて実現されている。なお、本実施例では、一のCPUが、書き込み制御部203だけでなく、他の制御部(図示せず)によっても使用されるが、複数のCPUに処理は分散しても構わない。起動用ROM(204)は、リセット解除又はBTSの電源投入後に、書き込み制御部203等に使用されているCPUがいちばん最初に読み込むプログラムが格納されており、そのプログラムにはCPUが最初に実行すべき処理が記述されている。不揮発性記憶部205は、BTS(201)が動作するためのプログラムを格納することができ、不揮発性のメモリで構成されている。よって、BTS(201)にリセットが実行されても、或いは、電源が切断されても、格納されたBTS(201)が動作するためのプログラムは消去されない。揮発性記憶部206は、BTS(201)が動作するためのプログラムを書き込み制御部(203)が受信した場合に、一時的にそのプログラムを格納することができ、揮発性のメモリで構成されている。また、揮発性記憶部206に書かれたプログラムは、リセット後のCPUの初期処理にて通常クリアされるが、後述の格納チェックレジスタ212の値が“0”であった場合には、揮発性記憶部206をクリアしないよう、起動用ROM(204)に格納されたプログラムに記述されている。揮発性記憶部206のような揮発性メモリは、不揮発性記憶部205のような不揮発性のメモリに比べ、一般に高速にデータを書き込み・読み出しが可能である。書き込み制御部203は装置内バス(207)経由で格納チェックレジスタ212にアクセスすることができ、“0”又は“1”を書き込むことができる。また、BTS(201)にリセットが実行されても、或いは、電源が切断されても、格納チェックレジスタ212に一度設定された値は変化することがない。格納チェックレジスタ212の値を変更できるのは書き込み制御部203だけである。

【0023】

本実施例のBTSを含む移動通信網の構成は、図1に概念的に示した従来の一般的なものと同様である。

【0024】

このBTS(201)の運用中に、不揮発性記憶部205に格納されたプログラムのバージョンアップが必要になった場合、そのバージョンアップは図3に示すような工程で行われる。すなわち、BTS(201)がダウンロード信号を受信すると(S300)、BTS(201)は新しいプログラムのダウンロードを開始する(S301)。具体的には、OMC(104)より送信された、BTS(201)が動作するための新しいプログラムは、MSC(103)及びBSC(102)を介して、まずBTS(201)内の伝送路IF部202で受信され、装置内バス(207)を経由し書き込み制御部203へ転送される。書き込み制御部203は、装置内バス(207)経由で、BTS(201)が動作するための新しいプログラムを揮発性記憶部206に格納する。揮発性記憶部206への格納が完了すると、書き込み制御部203は格納チェックレジスタ212の値を“0”とする(S302)。書き込み制御部203は、揮発性記憶部206に格納された新しいBTS(201)が動作するためのプログラムを不揮発性記憶部205へコピーする(S303)。コピーが終了すると、書き込み制御部203は格納チェックレジスタ212の値を“1”とする(S304)。これで、新しいBTS(201)が動作するためのプログラムの一連の工程は完了する(S305)。この後、BTS(201)にはリセットが実行される。

【0025】

BTS(201)のリセット解除又は電源投入後に、BTS(201)のCPUは起動用ROM(204)に格納されたプログラムを読み出して、それに基づいて処理を実行する。図4はその処理を示すフローチャートである。図4において、CPUは、リセットが解除されると(S400)、まず格納チェックレジスタ212に格納された値を確認する(S401)。格納チェックレジスタ212に格納された値が0であれば、揮発性記憶部205に格納されているプログラムで起動すべき状況であるので(図3の区間B)、揮発性記憶部205からプログラムを読み込み(S402)、それに制御を渡すことにより装置を起動する(S403)。格納チェックレジスタ212に格納された値が1であれば、不揮発性記憶部206に格納されているプログラムで起動すべき状況であるので(図3の区間A又は区間C)、不揮発性記憶部206からプログラムを読み込み(S405)、それに制御を渡すことにより装置を起動する(S406)。

【0026】

本実施例では、BTS(201)内に格納チェックレジスタ212を配置し、ダウンロード時に図3に示した処理を、再起動時に図4に示した処理を、それぞれ行うことにより、図3の区間A、区間B、及び区間Cのいかなるタイミングでリセットが実行されても、或いは、電源が切断されても、BTS(201)は、一回目で再起動に成功する。このために追加したハードウェアは格納チェックレジスタ212だけである。また、ダウンロードしたプログラムの転送回数も、揮発性記憶部206から不揮発性記憶部205への一回のみで足りる。

【0027】

《実施例2》

本発明の第2の実施例では、BTS(201)の運用中に、不揮発性記憶部205に格納されたプログラムのバージョンアップが必要になった場合、そのバージョンアップは図5に示すような工程で行われるという点が、実施例1と異なっている。なお、本実施例のBTSの構成は、図2に概念的に示した第1の実施例と同様である。また、本実施例のBTSを含む移動通信網の構成は、図1に概念的に示した従来の一般的なものと同様である。

【0028】

図5において、BTS(201)がダウンロード信号を受信すると(S500)、BTS(201)は新しいプログラムのダウンロードを開始する(S501)。具体的には、OMC(104)より送信された、BTS(201)が動作するための新しいプログラムは、MSC(103)及びBSC(102)を介して、まずBTS(201)内の伝送路IF部202で受信され、装置内バス(207)を経由し書き込み制御部203へ転送される。書き込み制御部203は、装置内バス(207)経由で、BTS(201)が動作するための新しいプログラムを揮発性記憶部206に格納する。揮発性記憶部206への格納が完了すると、書き込み制御部203は格納チェックレジスタ212の値を“0”とする(S502)。書き込み制御部203は、CPUの使用率を確認する(S503)。CPUの使用率がX%以上の場合には(S504)、再びCPUの使用率を確認し(S503)、CPUの使用率がX%未満となるまで待つためのループに入る。CPUの使用率がX%未満の場合には(S504)、揮発性記憶部206に格納された新しいBTS(201)が動作するためのプログラムを不揮発性記憶部205へ予め定められたAバイトだけコピーする(S505)。まだ全データのコピーが終了していない場合には(S506)、再びCPUの使用率の確認に戻る(S503)。X及びAの値は、一連の工程を通じて一定であってもよいし、一定でなくともよい。全データのコピーが終了した場合には(S506)、格納チェックレジスタ212の値を“1”とする(S507)。これで、新しいBTS(201)が動作するためのプログラムの一連の工程は完了する(S508)。この後、BTS(201)にはリセットが実行される。

【0029】

BTS(201)のリセット解除又は電源投入後に、CPUは起動用ROM(204)に格納されたプログラムを読み出して、それに基づいて処理を実行する。本実施例におけるその処理を示すフローチャートは実施例1と同様に、図4にて示される。図4において、CPUは、まず格納チェックレジスタ212に格納された値を確認する。格納チェックレジスタ212に格納された値が0であれば、揮発性記憶部205に格納されているプログラムで起動すべき状況であるので(図5の区間B')、揮発性記憶部205からプログラムを読み込み、それに制御を渡すことにより装置を起動する。格納チェックレジスタ212に格納された値が1であれば、不揮発性記憶部206に格納されているプログラムで起動すべき状況であるので(図5の区間A'又は区間C')、不揮発性記憶部206からプログラムを読み込み、それに制御を渡すことにより装置を起動する。

【0030】

本実施例では、図5に示したように、揮発性記憶部206から不揮発性記憶部205へコピーする際に、CPUの使用率を測定し、それがX%以上であった場合にはX%未満になるまでコピーを行わない。すなわち、図6に示す区間HのようにCPUの使用率が高い場合にはコピーは行われない。通常、前述のように、書き込み制御部203はCPUを他の制御部(図示せず)と共有しているが、本実施例では、このような構成により、新プログラムのコピーというさほど緊急性の高くない作業により他の制御部の作業が圧迫されてしまうという問題がない。

【0031】

更に、本実施例では、揮発性記憶部206から不揮発性記憶部205へのコピーをAバイト単位に行っている。すなわち、Aバイトだけコピーを実施したら、再びCPUの使用率を測定し、それがX%以上であった場合にはX%未満になるまでコピーを行わない。これにより、他の制御部の作業の圧迫防止(上記)をより細かい時間単位で精密に制御することが可能となっている。なお、この構成は、本発明のBTS(201)が、図5の区間A'、区間B'、及び区間C'のいかなるタイミングでリセットが実行されても、或いは、電源が切断されても、一回で再起動に成功するため、揮発性記憶部206から不揮発性記憶部205へのコピーを短時間で済ませる必要がなくなったことにより、初めて可能となったものである。

【0032】

上記実施例では、移動通信網のBTSを例にとって説明したが、本発明の実施は上記実施例に限られるものではない。本発明は、携帯電話機、Personal Digital Assistant、パーソナルコンピュータなどのコンピュータなど様々な機器において支障なく実施することができる。また、上記実施例2では、X及びAの値は予め定められていたが、これらの双方又は一方をOMC(104)からの指示等により可変とすることもできる。このような構成により、どの程度のCPU使用率であればコピーを強行するか、どの程度細かい時間間隔でコピー可否を判定するか、などを遠隔制御することができる。

【図面の簡単な説明】

【0033】

【図1】一般的な移動通信網の構成の概念図である。

【図2】本発明の第1の実施例であるBTSの構成を示す概念図である。

【図3】本発明の第1の実施例であるBTSにおいて、プログラムのバージョンアップが行われる際の工程を示すフローチャートである。

【図4】本発明の第1の実施例であるBTSにおいて、リセット解除又はBTSの電源投入後に、CPUが行う処理を示すフローチャートである。

【図5】本発明の第2の実施例であるBTSにおいて、プログラムのバージョンアップが行われる際の工程を示すフローチャートである。

【図6】本発明の第2の実施例で、CPUの使用率の一例を示すグラフである。

【図7】従来の一般的なBTSの構成を示す概念図である。

【図8】従来の一般的なBTSにおいてプログラムのバージョンアップを行う際に、書き込み制御部が実行する処理の一例を示すフローチャートである。

【図9】従来の一般的なBTSにおいてプログラムのバージョンアップを行う際に、書き込み制御部が実行する処理の他の一例を示すフローチャートである。

【符号の説明】

【0034】

101 無線基地局(BTS)

102 基地局制御局(BSC)

103 移動通信交換局(MSC)

104 移動通信保守監視卓(OMC)

105 移動通信端末(MS)

201 BTS

202 伝送路IF部

203 書き込み制御部

204 起動用ROM

205 不揮発性記憶部

206 揮発性記憶部

207 装置内バス

210 対上位局信号

212 格納チェックレジスタ

701 BTS

702 伝送路IF部

703 書き込み制御部

704 起動用ROM

705 不揮発性記憶部

706 揮発性記憶部

707 装置内バス

710 対上位局信号

【技術分野】

【0001】

本発明は、プログラムにより動作する装置における、プログラムの更新方法に関し、特に、プログラムを更新中或いはその前後に装置の再起動が行われても、装置が正常に起動し得るプログラムの更新方法に関する。

【0002】

また、本発明は、プログラムにより動作する装置の再起動の方法に関し、特に、プログラムを更新中或いはその前後に装置の再起動が行われても、装置が正常に起動し得る再起動の方法に関する。

【背景技術】

【0003】

従来のプログラムの更新方法及び装置の再起動の方法の一例を、移動通信網を例にとって説明する。一般的な移動通信網の構成を概念的に図1に示す。図1において、移動通信網は、無線基地局(BTS)101、基地局制御局(BSC)102、移動通信交換局(MSC)103、移動通信保守監視卓(OMC)104、及び移動通信端末(MS)105より構成されている。BTS(101)は、MSC(103)、BSC(102)、OMC(104)と伝送路で接続されている。伝送路の中には、例えば、OMC(104)からBTS(101)に到達する、BTS(101)が動作するためのプログラムを送受信するための信号が対上位局信号210として導通している。BTS(101)は、BSC(102)からの制御信号によりBSC(102)からの音声及び非音声(データ)信号を高周波信号に変換し空間に放射し、またMS(105)が音声及び非音声信号を高周波信号に変換し空間に放射した高周波信号を受信しBSC(102)に送信する。BSC(102)は、MSC(103)により制御され、通常、数十台のBTSを配下に接続し、主にその無線回線を制御する。MSC(103)は、通常、数十台のBSCを配下に接続し、主に移動通信網の有線回線交換制御を行う。OMC(104)は、MSC(例えば103)、BSC(例えば102)、及びBTS(例えば101)と接続される。OMC(104)は、MSC(例えば103)、BSC(例えば102)、及びBTS(例えば101)の状態を監視・確認し、また、それらのリセットを遠隔的に制御することができる。OMC(104)は、各装置が動作するためのプログラムを格納し、必要に応じてそのプログラムを各装置に遠隔的にダウンロードさせることができる。

【0004】

従来の一般的なBTSの内部構成を概念的に図7に示す。図7において、BTS(701)は、伝送路インタフェース(IF)部702と、書き込み制御部703と、起動用読み出し専用メモリ(起動用ROM)704と、不揮発性記憶部705と、揮発性記憶部706と、それらを結ぶ装置内バス(707)と、から構成されている。書き込み機能部703は、CPU(Central Processing Unit)(図示せず)を用いて実現されている。さらに、このBTS(701)は、BSC(102)及びMSC(103)を介して、移動通信保守監視卓(OMC)104との間で、対上位局信号710を送受信する。

【0005】

このBTS(701)の運用中に、不揮発性記憶部705に格納されたプログラムのバージョンアップが必要になる場合がある。

【0006】

このバージョンアップは、図8に示す工程で行われる。図8はBTS(701)の書き込み制御部(703)の動作の一例である。すなわち、ダウンロード開始信号を受信すると(S800)、書き込み制御部(703)は、OMC(104)からMSC(103)及びBSC(102)を介して、更新プログラムを伝送路IF部(702)により受信し、不揮発性記憶部705に格納する(S801)。

【0007】

或いは、このバージョンアップは、図9に示す工程で行われる。図9はBTS(701)の書き込み制御部(703)の動作の他の一例である。すなわち、ダウンロード開始信号を受信すると(S900)、書き込み制御部(703)は、OMC(104)からMSC(103)及びBSC(102)を介して、更新プログラムを伝送路IF部(702)により受信し、揮発性記憶部706に格納する(S901)。さらに、書き込み制御部703は、その更新プログラムを揮発性記憶部706から不揮発性記憶部705にコピーする(S902)。

【0008】

ところで、BTSのプログラムのこのようなバージョンアップ動作中に、電源断或いはリセット(以下リセット等という)が生じると、BTSが起動できなくなることがあった。具体的には、以下の通りである。

【0009】

例えば、図8に示す工程で、書き込み制御部703が更新プログラムを不揮発性記憶部705に書き込んでいる最中(S801)に、BTS(701)にリセットが実行されたとする。その後再起動する際に、BTS(701)のCPUは起動用ROM(704)に格納された初期処理のプログラムに従って、不揮発性記憶部705に格納されたプログラムを実行する。しかし、不揮発性記憶部705には書き込み制御部703が更新プログラムを書き込んでいる途中(S801)であったため、旧プログラムも更新プログラムも不完全にしか格納されておらず、BTS(701)は起動できない。

【0010】

また、例えば、図9に示す工程で、書き込み制御部703がOMC(104)から受信して揮発性記憶部706に一旦格納した更新プログラムを揮発性記憶部706から不揮発性記憶部705にコピーしている最中(S902)に、BTS(701)にリセットが実行された場合も同様である。

【0011】

この問題を解決するために、いくつかの技術が提案されている。

【0012】

例えば、特許文献1には、とりあえず再起動を試み、もし再起動に失敗した場合には、旧プログラムで再度の再起動を行なうという方法が記載されている。また、特許文献2には、プログラムをリモートダウンローダとメインの制御プログラムに分け、それぞれ別個に上位装置から転送し、リモートダウンローダについてのみ新旧のバージョンをフラッシュROM中のそれぞれ異なる領域に格納するという2面管理がなされている。この場合、新リモートダウンローダは旧リモートダウンローダによりダウンロードされ、メインの制御プログラムの新しいバージョンは新リモートダウンローダによりダウンロードされる。さらに、特許文献3には、更新プログラムを一時格納メモリにダウンロードする前に、一時格納メモリに格納されていた旧プログラムをバックアップメモリに保存しておき、更新指示コマンドを受信する前に装置が再起動した場合には、バックアップメモリにある旧プログラムをプログラムエリアに転送して装置運用を開始する方法が記載されている。

【0013】

【特許文献1】特開2001−134428号公報

【特許文献2】特開2004−102893号公報

【特許文献3】特開平9−325891号公報

【発明の開示】

【発明が解決しようとする課題】

【0014】

特許文献1記載の方法では、実際に装置を再起動することによって新プログラムが正常かどうかを判定している。このため、新プログラムに問題があった場合、BTSが正常な動作を再開するまでには、再起動、失敗判定、再度の再起動という複雑な工程が必要であり、長時間を要するという問題がある。特許文献2には、メインの制御プログラムのダウンロード中にリセット等が生じた場合に装置を正常に再起動させる方法については、開示がない。したがって、いかなる場合にも正常にBTSを再起動させるという課題は解決されていない。特許文献3記載の方法では、一時格納メモリとバックアップメモリとプログラムエリアとの計3セットのメモリが必要である。しかも、リセット等が生じた場合には、一時格納メモリからバックアップメモリへの旧プログラムの転送と、バックアップメモリからプログラムエリアへの旧プログラムの転送との計2回の転送が必要である。よって、ソフトウエアおよびハードウエアに掛かる負荷が大きく、コストに課題を有している。

【0015】

本発明の目的は、従来の方式のこのような課題を解決することである。すなわち、本発明は、BTSにおいて、プログラムのバージョンアップ動作中或いはその前後にリセット等が生じた場合であっても、短時間で正常にBTSを再起動させることを目的としている。また、本発明は、できる限り少ないハードウェア或いはできる限り少ない工程で、これらの目的を安価に実現することを、目的としている。

【課題を解決するための手段】

【0016】

本発明のプログラムの更新方法は、更新後のプログラムを第1のメモリにダウンロードする第1の工程と、プログラム更新中であることを記憶する第2の工程と、前記更新後のプログラムを前記第1のメモリから前記不揮発性メモリである第2のメモリへとコピーする第3の工程と、前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、を前記順序で少なくとも含むことを特徴とする。

【0017】

本発明のプログラムの更新方法は、或いは、前記第3の工程の前に、前記第3の工程を実行する中央演算処理装置の使用率と所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を行うことを特徴とする。

【0018】

本発明のプログラムの更新方法は、或いは、前記第3の工程において、前記更新後のプログラムの一部を前記第1のメモリから不揮発性メモリである第2のメモリへコピーするごとに、前記第3の工程を実行する前記中央演算処理装置の使用率と前記所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を継続することを特徴とする。

本発明のプログラムの更新方法は、或いは、前記所定のサイズが可変であることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記所定の値が可変であることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記第1のメモリが揮発性メモリであることを特徴とする。

本発明のプログラムの更新方法は、或いは、前記第1のメモリが不揮発性メモリであることを特徴とする。

本発明のプログラムの更新方法は、或いは、当該装置が移動通信網の基地局であることを特徴とする。

【0019】

本発明の再起動の方法は、プログラム更新中であることが記憶されている場合には、第1のメモリに格納されたプログラムを実行し、プログラム更新が終了したことが記憶されている場合には、不揮発性メモリである第2のメモリに格納されたプログラムを実行することを特徴とする。

本発明のプログラムは、上記プログラムの更新方法を実行することを特徴とする。

或いは、本発明のプログラムは、上記再起動の方法を実行することを特徴とする。

【発明の効果】

【0020】

本発明によれば、BTSにおいて、更新プログラムのバージョンアップ動作中或いはその前後にリセット等が生じた場合であっても、再起動に失敗することなく、短時間で正常にBTSを再起動させることができる。また、本発明によれば、少ないハードウェア或いは少ない工程で、正常にBTSを再起動することができる。

【発明を実施するための最良の形態】

【0021】

本発明を移動体通信網に適用した実施の形態について、図面を用いて説明する。

《実施例1》

本発明の第1の実施例であるBTSの構成を概念的に図2に示す。図2において、BTS(201)は、伝送路IF部202と、書き込み制御部203と、起動用ROM(204)と、不揮発性記憶部205と、揮発性記憶部206と、格納チェックレジスタ212と、伝送路それらを結ぶ装置内バス(207)と、から構成されている。さらに、このBTS(201)は、BSC(102)及びMSC(103)を介して、移動通信保守監視卓(OMC)104との間で、対上位局信号210を送受信する。

【0022】

伝送路IF部202は、伝送路にてOMC(104)と、装置内バス(207)にて書き込み制御部203と、それぞれ接続されている。書き込み制御部203は、装置内バス(207)にて伝送路IF部202と、装置内バス(207)にて不揮発性記憶部205、揮発性記憶部206、及び格納チェックレジスタ212とに接続されている。書き込み制御部203は、CPU(図示せず)を用いて実現されている。なお、本実施例では、一のCPUが、書き込み制御部203だけでなく、他の制御部(図示せず)によっても使用されるが、複数のCPUに処理は分散しても構わない。起動用ROM(204)は、リセット解除又はBTSの電源投入後に、書き込み制御部203等に使用されているCPUがいちばん最初に読み込むプログラムが格納されており、そのプログラムにはCPUが最初に実行すべき処理が記述されている。不揮発性記憶部205は、BTS(201)が動作するためのプログラムを格納することができ、不揮発性のメモリで構成されている。よって、BTS(201)にリセットが実行されても、或いは、電源が切断されても、格納されたBTS(201)が動作するためのプログラムは消去されない。揮発性記憶部206は、BTS(201)が動作するためのプログラムを書き込み制御部(203)が受信した場合に、一時的にそのプログラムを格納することができ、揮発性のメモリで構成されている。また、揮発性記憶部206に書かれたプログラムは、リセット後のCPUの初期処理にて通常クリアされるが、後述の格納チェックレジスタ212の値が“0”であった場合には、揮発性記憶部206をクリアしないよう、起動用ROM(204)に格納されたプログラムに記述されている。揮発性記憶部206のような揮発性メモリは、不揮発性記憶部205のような不揮発性のメモリに比べ、一般に高速にデータを書き込み・読み出しが可能である。書き込み制御部203は装置内バス(207)経由で格納チェックレジスタ212にアクセスすることができ、“0”又は“1”を書き込むことができる。また、BTS(201)にリセットが実行されても、或いは、電源が切断されても、格納チェックレジスタ212に一度設定された値は変化することがない。格納チェックレジスタ212の値を変更できるのは書き込み制御部203だけである。

【0023】

本実施例のBTSを含む移動通信網の構成は、図1に概念的に示した従来の一般的なものと同様である。

【0024】

このBTS(201)の運用中に、不揮発性記憶部205に格納されたプログラムのバージョンアップが必要になった場合、そのバージョンアップは図3に示すような工程で行われる。すなわち、BTS(201)がダウンロード信号を受信すると(S300)、BTS(201)は新しいプログラムのダウンロードを開始する(S301)。具体的には、OMC(104)より送信された、BTS(201)が動作するための新しいプログラムは、MSC(103)及びBSC(102)を介して、まずBTS(201)内の伝送路IF部202で受信され、装置内バス(207)を経由し書き込み制御部203へ転送される。書き込み制御部203は、装置内バス(207)経由で、BTS(201)が動作するための新しいプログラムを揮発性記憶部206に格納する。揮発性記憶部206への格納が完了すると、書き込み制御部203は格納チェックレジスタ212の値を“0”とする(S302)。書き込み制御部203は、揮発性記憶部206に格納された新しいBTS(201)が動作するためのプログラムを不揮発性記憶部205へコピーする(S303)。コピーが終了すると、書き込み制御部203は格納チェックレジスタ212の値を“1”とする(S304)。これで、新しいBTS(201)が動作するためのプログラムの一連の工程は完了する(S305)。この後、BTS(201)にはリセットが実行される。

【0025】

BTS(201)のリセット解除又は電源投入後に、BTS(201)のCPUは起動用ROM(204)に格納されたプログラムを読み出して、それに基づいて処理を実行する。図4はその処理を示すフローチャートである。図4において、CPUは、リセットが解除されると(S400)、まず格納チェックレジスタ212に格納された値を確認する(S401)。格納チェックレジスタ212に格納された値が0であれば、揮発性記憶部205に格納されているプログラムで起動すべき状況であるので(図3の区間B)、揮発性記憶部205からプログラムを読み込み(S402)、それに制御を渡すことにより装置を起動する(S403)。格納チェックレジスタ212に格納された値が1であれば、不揮発性記憶部206に格納されているプログラムで起動すべき状況であるので(図3の区間A又は区間C)、不揮発性記憶部206からプログラムを読み込み(S405)、それに制御を渡すことにより装置を起動する(S406)。

【0026】

本実施例では、BTS(201)内に格納チェックレジスタ212を配置し、ダウンロード時に図3に示した処理を、再起動時に図4に示した処理を、それぞれ行うことにより、図3の区間A、区間B、及び区間Cのいかなるタイミングでリセットが実行されても、或いは、電源が切断されても、BTS(201)は、一回目で再起動に成功する。このために追加したハードウェアは格納チェックレジスタ212だけである。また、ダウンロードしたプログラムの転送回数も、揮発性記憶部206から不揮発性記憶部205への一回のみで足りる。

【0027】

《実施例2》

本発明の第2の実施例では、BTS(201)の運用中に、不揮発性記憶部205に格納されたプログラムのバージョンアップが必要になった場合、そのバージョンアップは図5に示すような工程で行われるという点が、実施例1と異なっている。なお、本実施例のBTSの構成は、図2に概念的に示した第1の実施例と同様である。また、本実施例のBTSを含む移動通信網の構成は、図1に概念的に示した従来の一般的なものと同様である。

【0028】

図5において、BTS(201)がダウンロード信号を受信すると(S500)、BTS(201)は新しいプログラムのダウンロードを開始する(S501)。具体的には、OMC(104)より送信された、BTS(201)が動作するための新しいプログラムは、MSC(103)及びBSC(102)を介して、まずBTS(201)内の伝送路IF部202で受信され、装置内バス(207)を経由し書き込み制御部203へ転送される。書き込み制御部203は、装置内バス(207)経由で、BTS(201)が動作するための新しいプログラムを揮発性記憶部206に格納する。揮発性記憶部206への格納が完了すると、書き込み制御部203は格納チェックレジスタ212の値を“0”とする(S502)。書き込み制御部203は、CPUの使用率を確認する(S503)。CPUの使用率がX%以上の場合には(S504)、再びCPUの使用率を確認し(S503)、CPUの使用率がX%未満となるまで待つためのループに入る。CPUの使用率がX%未満の場合には(S504)、揮発性記憶部206に格納された新しいBTS(201)が動作するためのプログラムを不揮発性記憶部205へ予め定められたAバイトだけコピーする(S505)。まだ全データのコピーが終了していない場合には(S506)、再びCPUの使用率の確認に戻る(S503)。X及びAの値は、一連の工程を通じて一定であってもよいし、一定でなくともよい。全データのコピーが終了した場合には(S506)、格納チェックレジスタ212の値を“1”とする(S507)。これで、新しいBTS(201)が動作するためのプログラムの一連の工程は完了する(S508)。この後、BTS(201)にはリセットが実行される。

【0029】

BTS(201)のリセット解除又は電源投入後に、CPUは起動用ROM(204)に格納されたプログラムを読み出して、それに基づいて処理を実行する。本実施例におけるその処理を示すフローチャートは実施例1と同様に、図4にて示される。図4において、CPUは、まず格納チェックレジスタ212に格納された値を確認する。格納チェックレジスタ212に格納された値が0であれば、揮発性記憶部205に格納されているプログラムで起動すべき状況であるので(図5の区間B')、揮発性記憶部205からプログラムを読み込み、それに制御を渡すことにより装置を起動する。格納チェックレジスタ212に格納された値が1であれば、不揮発性記憶部206に格納されているプログラムで起動すべき状況であるので(図5の区間A'又は区間C')、不揮発性記憶部206からプログラムを読み込み、それに制御を渡すことにより装置を起動する。

【0030】

本実施例では、図5に示したように、揮発性記憶部206から不揮発性記憶部205へコピーする際に、CPUの使用率を測定し、それがX%以上であった場合にはX%未満になるまでコピーを行わない。すなわち、図6に示す区間HのようにCPUの使用率が高い場合にはコピーは行われない。通常、前述のように、書き込み制御部203はCPUを他の制御部(図示せず)と共有しているが、本実施例では、このような構成により、新プログラムのコピーというさほど緊急性の高くない作業により他の制御部の作業が圧迫されてしまうという問題がない。

【0031】

更に、本実施例では、揮発性記憶部206から不揮発性記憶部205へのコピーをAバイト単位に行っている。すなわち、Aバイトだけコピーを実施したら、再びCPUの使用率を測定し、それがX%以上であった場合にはX%未満になるまでコピーを行わない。これにより、他の制御部の作業の圧迫防止(上記)をより細かい時間単位で精密に制御することが可能となっている。なお、この構成は、本発明のBTS(201)が、図5の区間A'、区間B'、及び区間C'のいかなるタイミングでリセットが実行されても、或いは、電源が切断されても、一回で再起動に成功するため、揮発性記憶部206から不揮発性記憶部205へのコピーを短時間で済ませる必要がなくなったことにより、初めて可能となったものである。

【0032】

上記実施例では、移動通信網のBTSを例にとって説明したが、本発明の実施は上記実施例に限られるものではない。本発明は、携帯電話機、Personal Digital Assistant、パーソナルコンピュータなどのコンピュータなど様々な機器において支障なく実施することができる。また、上記実施例2では、X及びAの値は予め定められていたが、これらの双方又は一方をOMC(104)からの指示等により可変とすることもできる。このような構成により、どの程度のCPU使用率であればコピーを強行するか、どの程度細かい時間間隔でコピー可否を判定するか、などを遠隔制御することができる。

【図面の簡単な説明】

【0033】

【図1】一般的な移動通信網の構成の概念図である。

【図2】本発明の第1の実施例であるBTSの構成を示す概念図である。

【図3】本発明の第1の実施例であるBTSにおいて、プログラムのバージョンアップが行われる際の工程を示すフローチャートである。

【図4】本発明の第1の実施例であるBTSにおいて、リセット解除又はBTSの電源投入後に、CPUが行う処理を示すフローチャートである。

【図5】本発明の第2の実施例であるBTSにおいて、プログラムのバージョンアップが行われる際の工程を示すフローチャートである。

【図6】本発明の第2の実施例で、CPUの使用率の一例を示すグラフである。

【図7】従来の一般的なBTSの構成を示す概念図である。

【図8】従来の一般的なBTSにおいてプログラムのバージョンアップを行う際に、書き込み制御部が実行する処理の一例を示すフローチャートである。

【図9】従来の一般的なBTSにおいてプログラムのバージョンアップを行う際に、書き込み制御部が実行する処理の他の一例を示すフローチャートである。

【符号の説明】

【0034】

101 無線基地局(BTS)

102 基地局制御局(BSC)

103 移動通信交換局(MSC)

104 移動通信保守監視卓(OMC)

105 移動通信端末(MS)

201 BTS

202 伝送路IF部

203 書き込み制御部

204 起動用ROM

205 不揮発性記憶部

206 揮発性記憶部

207 装置内バス

210 対上位局信号

212 格納チェックレジスタ

701 BTS

702 伝送路IF部

703 書き込み制御部

704 起動用ROM

705 不揮発性記憶部

706 揮発性記憶部

707 装置内バス

710 対上位局信号

【特許請求の範囲】

【請求項1】

プログラムにより動作する装置において当該プログラムを更新する方法であって、

更新後のプログラムを第1のメモリにダウンロードする第1の工程と、

プログラム更新中であることを記憶する第2の工程と、

前記更新後のプログラムを前記第1のメモリから不揮発性メモリである第2のメモリへコピーする第3の工程と、

前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、

を前記順序で少なくとも含む、プログラムの更新方法。

【請求項2】

前記請求項1に記載のプログラムの更新方法であって、

前記第3の工程の前に、前記第3の工程を実行する中央演算処理装置の使用率と所定の値との比較を行い、

前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を行なうことを特徴とするプログラムの更新方法。

【請求項3】

前記請求項1に記載のプログラムの更新方法であって、

前記第3の工程において、前記更新後のプログラムの一部を前記第1のメモリから不揮発性メモリである第2のメモリへコピーするごとに、前記第3の工程を実行する前記中央演算処理装置の使用率と前記所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を継続することを特徴とするプログラムの更新方法。

【請求項4】

前記請求項3に記載のプログラムの更新方法であって、

前記所定のサイズが可変であることを特徴とするプログラムの更新方法。

【請求項5】

前記請求項2乃至請求項4のいずれかに記載のプログラムの更新方法であって、

前記所定の値が可変であることを特徴とするプログラムの更新方法。

【請求項6】

前記請求項1乃至請求項5のいずれかに記載のプログラムの更新方法であって、

前記第1のメモリが揮発性メモリであることを特徴とするプログラムの更新方法。

【請求項7】

前記請求項1乃至請求項8のいずれかに記載のプログラムの更新方法であって、

当該装置が移動通信網の基地局であることを特徴とするプログラムの更新方法。

【請求項8】

前記請求項1乃至請求項7のいずれかに記載のプログラムの更新方法を採用したプログラムにより動作する装置における再起動の方法であって、

プログラム更新中であることが記憶されている場合には、前記第1のメモリに格納されたプログラムを実行し、

プログラム更新が終了したことが記憶されている場合には、前記不揮発性メモリである第2のメモリに格納されたプログラムを実行することを特徴とする再起動の方法。

【請求項9】

前記請求項1乃至請求項7のいずれかに記載のプログラムの更新方法を実行するプログラム。

【請求項1】

プログラムにより動作する装置において当該プログラムを更新する方法であって、

更新後のプログラムを第1のメモリにダウンロードする第1の工程と、

プログラム更新中であることを記憶する第2の工程と、

前記更新後のプログラムを前記第1のメモリから不揮発性メモリである第2のメモリへコピーする第3の工程と、

前記プログラム更新中であることの記憶にかえて、プログラム更新が終了したことを記憶する第4の工程と、

を前記順序で少なくとも含む、プログラムの更新方法。

【請求項2】

前記請求項1に記載のプログラムの更新方法であって、

前記第3の工程の前に、前記第3の工程を実行する中央演算処理装置の使用率と所定の値との比較を行い、

前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を行なうことを特徴とするプログラムの更新方法。

【請求項3】

前記請求項1に記載のプログラムの更新方法であって、

前記第3の工程において、前記更新後のプログラムの一部を前記第1のメモリから不揮発性メモリである第2のメモリへコピーするごとに、前記第3の工程を実行する前記中央演算処理装置の使用率と前記所定の値との比較を行い、前記使用率が前記所定の値未満或いは以下の場合には、前記第3の工程を継続することを特徴とするプログラムの更新方法。

【請求項4】

前記請求項3に記載のプログラムの更新方法であって、

前記所定のサイズが可変であることを特徴とするプログラムの更新方法。

【請求項5】

前記請求項2乃至請求項4のいずれかに記載のプログラムの更新方法であって、

前記所定の値が可変であることを特徴とするプログラムの更新方法。

【請求項6】

前記請求項1乃至請求項5のいずれかに記載のプログラムの更新方法であって、

前記第1のメモリが揮発性メモリであることを特徴とするプログラムの更新方法。

【請求項7】

前記請求項1乃至請求項8のいずれかに記載のプログラムの更新方法であって、

当該装置が移動通信網の基地局であることを特徴とするプログラムの更新方法。

【請求項8】

前記請求項1乃至請求項7のいずれかに記載のプログラムの更新方法を採用したプログラムにより動作する装置における再起動の方法であって、

プログラム更新中であることが記憶されている場合には、前記第1のメモリに格納されたプログラムを実行し、

プログラム更新が終了したことが記憶されている場合には、前記不揮発性メモリである第2のメモリに格納されたプログラムを実行することを特徴とする再起動の方法。

【請求項9】

前記請求項1乃至請求項7のいずれかに記載のプログラムの更新方法を実行するプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2006−277511(P2006−277511A)

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願番号】特願2005−97879(P2005−97879)

【出願日】平成17年3月30日(2005.3.30)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

【公開日】平成18年10月12日(2006.10.12)

【国際特許分類】

【出願日】平成17年3月30日(2005.3.30)

【出願人】(390010179)埼玉日本電気株式会社 (1,228)

【Fターム(参考)】

[ Back to top ]