プログラムダウンロードの自動化システム

【課題】ROMからRAMへのプログラムコードの複写を専用のプログラム制御を用いることなく可能とし、これによりプログラムコードの縮減並びに電源立上げ時の起動時間の短縮を図ることを可能にする。

【解決手段】ROM17から読み出されたプログラムコードのデータがRAM13に複写されたか否かを示す複写情報を格納する複写管理メモリ22と、CPU12が読み込むデータの複写情報を複写管理メモリ22で確認し、この確認した複写情報が複写済みを示す場合、RAM13から該当のデータを読み出してCPU12に送出し、その確認した複写情報が未複写を示す場合、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出するメモリ制御部21とを有することにある。

【解決手段】ROM17から読み出されたプログラムコードのデータがRAM13に複写されたか否かを示す複写情報を格納する複写管理メモリ22と、CPU12が読み込むデータの複写情報を複写管理メモリ22で確認し、この確認した複写情報が複写済みを示す場合、RAM13から該当のデータを読み出してCPU12に送出し、その確認した複写情報が未複写を示す場合、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出するメモリ制御部21とを有することにある。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、CPU(Central Processing Unit)が用いるプログラムの格納メモリとしてシリアルI/F(又はパラレルI/F)のROMを有し、電源を立ち上げた起動時にCPUがROMからプログラムコードを一旦読み込んでRAMに複写した後に、CPUがRAMに複写されたプログラムコードを用いて所定のプログラム動作を行う、プログラムダウンロードの自動化システムに関する。

【背景技術】

【0002】

従来のプログラムダウンロードの自動化システムの構成図を図9に示す。この図9に示す自動化システムは、内部バス10に接続されたCPU12、RAM(Random Access Memory)13及びシリアルI/F(インタフェース)14が、1つの半導体パッケージとしてのASIC(Application Specific Integrated

Circuit)15に収容され、ASIC15の外部に配置されたシリアルI/Fを持つROM(Read Only Memory)17がシリアルI/F14に接続されて構成されている。なお、CPU12、RAM13、及びシリアルI/F14が1つの半導体パッケージに収容されているのは、CPU12とRAM13間のアクセス速度を高速化し、後述のようにRAM13に転送されたプログラムコードを高速にリードするためである。

【0003】

CPU12は、自動化システムの制御を司り、RAM13は、プログラムやCPU12の制御に必要なデータを格納する揮発性メモリである。シリアルI/F14は、ROM17と内部バス10との間でデータを順次伝送する。ROM17は、CPU12を制御するためのプログラムコードを格納するシリアルI/F方式の不揮発性メモリである。

【0004】

このような構成の自動化システムの動作を図10に示すタイムチャートを参照して説明する。図10はROM17に格納されたプログラムコードをRAM13に複写する動作を示すタイムチャートである。ROM17にはCPU12が所定の動作を実行するためのプログラムコードが予め記憶されている。

【0005】

自動化システムの電源投入時の起動時には、まず、CPU12が、図10に示す時刻t1〜t2において(a)に示すアドレスAP1(R)を指定することによって、時刻t2〜t3において、内部バス10及びシリアルI/F14を介してROM17にアクセスし、時刻t3〜t4において、ROM17に記憶されたプログラムコードのデータDp1をリード(R)する。このリードしたデータDp1をRAM13の記憶領域のアドレスAp2(W)を指定して、時刻t4〜t5においてRAM13に書き込んで複写(W)する。

【0006】

このようなアクセスを全てのプログラムコードの複写が完了するまで繰り返す。この複写が完了すると、CPU12はプログラムの実行をRAM13に複写されたプログラムコードをアクセスすることにより行う。この種の技術として特許文献1,2に記載の技術がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平10−097427号公報

【特許文献1】特開平07−225686号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述した従来の自動化システムによれば、CPU12がROM17からRAM13へプログラムコードを複写するための専用のプログラムが必要となると共にそのプログラムの実行が必要となり、また、プログラム実行のためにROM17からリードしたプログラムコードをRAM13へ複写するために、再度ROM17からプログラムコードをリードする必要がある。更に、ROM17に記憶された複写対象のプログラムコードの一部に使用されないコードがあっても、そのコード部分のみを外してRAM13に転送するのは非効率である。例えば、プログラムコードに不要のコードが虫食い状態に存在する場合などには、その不要コード部分のみを外してRAM13に転送することは、転送プログラムの複雑化や制御メモリの増大を招くので、プログラムコード全体を一括して転送する方が効率がよい。しかし、プログラムコード全体の量が膨大であると、一括転送する転送時間が長くなってしまう。

【0009】

これらの理由から、プログラムコードの複写の際に無駄な動作が発生し、このため電源立上げ時の起動時間が長くなってしまい、また、複写専用のプログラムが必要なので、プログラムコードが増大してしまうといった問題がある。

【0010】

本発明は上記した課題を解決するためになされたものであり、ROMからRAMへのプログラムコードの複写を専用のプログラム制御を用いることなく可能とし、これによりプログラムコードの縮減並びに電源立上げ時の起動時間の短縮を図ることができる、プログラムダウンロードの自動化システムを提供することを目的とする。

【課題を解決するための手段】

【0011】

上記した課題を解決するために本発明は、CPUが用いるプログラムコードの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリに複写されたか否かを示す複写情報を格納する複写管理メモリと、前記CPUが読み込むデータの前記複写情報を前記複写管理メモリから確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリから該当のデータを読み出して前記CPUに送出し、前記確認した複写情報が未複写を示す場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部と、を有することを特徴とする。

【0012】

この構成によれば、電源起動時にCPUがプログラムコードのデータを読み込む際に、メモリ制御部が複写管理メモリを確認しながら行うので、従来のようなCPUが不揮発性メモリから揮発性メモリへプログラムコードを複写するための専用のプログラムが不要となり、そのプログラムの実行も無くなる。従って、プログラムコードの縮減を図ることができる。また、2回目以降のCPUのデータの読み込みでは揮発性メモリからデータを読み込むのでアクセス時間が大幅に短縮される。従って、電源立上げ時の起動時間の短縮を図ることができる。

【0013】

また、本発明において、前記メモリ制御部は、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出した後、前記複写管理メモリにおける揮発性メモリへの未複写の複写状態を示す該当複写情報を複写済みとすることを特徴とする。

【0014】

この構成によれば、揮発性メモリへのデータ複写後に、当該複写状態を示す複写情報を適正に複写管理メモリに記憶することができる。

【0015】

また、本発明において、前記複写管理メモリの複写情報が複写済みの際に前記メモリ制御部により前記揮発性メモリから読み出されるデータにエラーがあることを検出する、前記メモリ制御部に接続されたエラー検出手段を備え、前記メモリ制御部は、前記エラー検出手段で前記データに複数ビットのエラーがあると検出された場合、前記エラー検出データに対応するデータを前記不揮発性メモリから読み出し、この読み出しデータを前記揮発性メモリに複写すると共に前記CPUへ送出することを特徴とする。

【0016】

この構成によれば、ECCチェックでは、通常データの72ビット当たり1ビットまではエラーを修正できるが、2ビット以上エラーがあれば修正不可能である。しかし、本発明のECCチェックでは、2ビット以上エラーがあっても、それに対応するデータを不揮発性メモリから読み出し、これをCPUへ送出すると共に揮発性メモリへ複写するようにしたので、結果的に2ビットエラーを修正することができる。

【0017】

また、本発明において、前記CPU、前記揮発性メモリ、前記複写管理メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項1〜3の何れか1つに記載のプログラムダウンロードの自動化システム。

【0018】

この構成によれば、CPU、揮発性メモリ、複写管理メモリ、メモリ制御部の各要素が内部バスで接続されるのでアクセス速度を高速化して、データ転送を高速に行うことができる。

【0019】

また、本発明は、CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、前記揮発性メモリは、前記不揮発性メモリから読み出されたプログラムコードのデータを格納する揮発性メモリ領域と、この揮発性メモリ領域から読み出されるデータにエラーがあることを検出するエラー検出領域と、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリ領域に複写されたか否かを示す複写情報を格納する複写管理領域とを有し、前記CPUが読み込むデータの前記複写情報を前記複写管理領域で確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリ領域から読み出されるデータのエラー検出を行い、このエラー検出で複数ビットのエラーがあった場合又は前記複写管理領域での複写情報が未複写である場合に、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリ領域に複写すると共に前記CPUへ送出するメモリ制御部と、を有することを特徴とする。

【0020】

この構成によれば、CPUへの送出データが揮発性メモリへの複写済みか否かをチェックする動作と、複写済みの際に揮発性メモリからリードしたデータをECCチェックする動作を1つの揮発性メモリの1回のリードアクセス動作により行えるので、効率の良いデータ読み出し制御を行うことができる。

【0021】

また、本発明は、CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムコードを前記CPUが用いて動作を行うプログラムダウンロードの自動化システムにおいて、前記揮発性メモリの格納データが前記電源起動時に複数ビットのエラーとなるように設定しておき、前記CPUが読み込むデータを前記揮発性メモリから読み出す際に、この読み出しデータにエラーがなければ前記揮発性メモリからそのデータを読み出して前記CPUに送出し、前記読み出しデータに複数ビットのエラーが有る場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部、を有することを特徴とする。

【0022】

この構成によれば、電源起動時に、メモリ制御部が揮発性メモリの格納データが必ず2ビット以上のエラーとなるように制御するので、1回目では揮発性メモリのデータが必ず2ビット以上エラーとなる。従って、メモリ制御部21がCPU12へのデータを読み込んだ際にECCチェックで必ず2ビットエラーが検出されるので、不揮発性メモリから対応するデータを読み込んで揮発性メモリに複写する。従って、2度目以降にCPUが必要なデータをメモリ制御部が揮発性メモリから読み込む場合、ECCチェックはOKとなってエラーの無いデータを読み出すことができる。このため、本発明の他の構成で必要であった複写管理メモリ又は複写管理領域が不要となるので、その分小型化を図ることができる。

【0023】

また、本発明において、前記CPU、前記揮発性メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする。

【0024】

この構成によれば、CPU、揮発性メモリ、メモリ制御部の各要素が内部バスで接続されるのでアクセス速度を高速化して、データ転送を高速に行うことができる。

【発明の効果】

【0025】

本発明によれば、ROMからRAMへのプログラムコードの複写を専用のプログラム制御を用いることなく可能とし、これによりプログラムコードの縮減並びに電源立上げ時の起動時間の短縮を図ることができるプログラムダウンロードの自動化システムを提供することができる。

【図面の簡単な説明】

【0026】

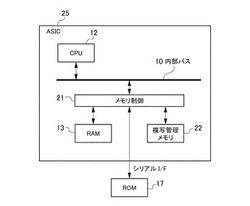

【図1】本実施形態に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図2】複写管理メモリのビット構成を示す図である。

【図3】本実施形態に係るプログラムダウンロードの自動化システムの複写情報が未複写の際の動作を説明するためのタイムチャートである。

【図4】本実施形態に係るプログラムダウンロードの自動化システムの複写情報が複写済みの際の動作を説明するためのタイムチャートである。

【図5】本実施形態の応用例1に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図6】本実施形態の応用例1の不揮発性メモリのビット構成並びにECCチェック及び複写管理の状態を示す図である。

【図7】本実施形態の応用例1のECCエラー時の自動化システムの動作を説明するためのタイムチャートである。

【図8】本実施形態の応用例2に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図9】従来のプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図10】従来のプログラムダウンロードの自動化システムの動作を説明するためのタイムチャートである。

【発明を実施するための形態】

【0027】

以下、添付図面を参照して本発明を実施するための実施の形態(以下、単に本実施形態という)について詳細に説明する。

(実施形態の構成)

図1は、本実施形態に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。本実施形態に係るプログラムダウンロードの自動化システム(以降、単に自動化システムともいう)は、内部バス10で接続されたCPU12及びメモリ制御部21と、メモリ制御部21に接続されたRAM13及び複写管理メモリ22とが、1つの半導体パッケージとしてのASIC25に収容され、このASIC25の外部に配置されたシリアルI/Fを持つROM17がメモリ制御部21に接続されて構成されている。

【0028】

CPU12は、自動化システム(不図示)の制御を司り、RAM13は、プログラムやCPU12の制御に必要なデータを格納する揮発性メモリである。ROM17は、CPU12を制御するためのプログラムコードを格納するシリアルI/F方式の不揮発性メモリである。

【0029】

複写管理メモリ22は、メモリ制御部21の制御でROM17からリードされたプログラムコードがRAM13に複写されたか否かを管理するものであり、図2に示すビット構成となっている。このビット構成は、下から上に向かう列方向が0,1,2,…,nと増加するnアドレスで、且つ右から左へ向かう行方向が0,1,2,3,…,28,29,30,31と順にビット数が増加する32ビットの複写情報の格納領域(複写情報領域という)を備え、各複写情報領域にプログラムコードの複写時に「1」、未複写時に「0」となる複写情報が格納されている。

【0030】

メモリ制御部21は、複写管理メモリ22の複写情報領域に格納された複写情報を確認して読込対象のプログラムコードが無い場合、そのプログラムコードをROM17から読み込み、これを内部バス10を介してCPU12へ送出すると共にRAM13に書き込んで複写し、この後、複写管理メモリ22の該当の複写情報領域に複写情報「1」を記憶する制御を行う。一方、プログラムコードが有る場合、RAM13からそのプログラムコードをリードして内部バス10を介してCPU12へ送出する。

【0031】

つまり、CPU12は、必要なプログラムコードをリードするためのアドレスをメモリ制御部21に送り、メモリ制御部21はそのアドレスに応じた複写管理メモリ22の複写情報領域に「0」か「1」が立っているか確認する。「1」がたっていればRAM13からプログラムコードをリードしてCPU12へ送る。「0」が立っていればそのアドレスのプログラムコードをROM17からリードしてRAM13及びCPU12へ送った後、複写管理メモリ22の該当複写情報領域に「1」を立てる。

(実施形態の動作)

以下、図1に示す本実施形態に係るプログラムダウンロードの自動化システム1の動作について、図3、図4のタイムチャートを参照しながら詳細に説明する。

【0032】

まず、図3のタイムチャートを用いて、複写管理メモリ22の複写情報領域に未複写時の情報「0」が格納されている場合の動作について説明する。なお、(R)はリード、(W)はライトを表す。

【0033】

自動化システムの電源投入時の起動時に、まず、CPU12が、図3に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードしている。これによりメモリ制御部21は、(c)に示すように複写管理メモリ22からアドレスAc1(R)のプログラムコードのデータがRAM13内にあるか否かを確認するために複写情報のリードを行い、同時にアドレスAc1のデータが格納されるように割り当てられているRAM13の記憶領域からデータDr1(R)をリードする。

【0034】

この際、複写管理メモリ22からリードした複写情報からアドレスAc1のデータDc1がRAM13には複写されていないと判断、つまり時刻t2〜t3の(d)に示すように未複写と判断されると、RAM13からリードしたデータDr1を破棄する。この場合、その破棄データに相当するデータDr1を、時刻t3〜t5の(g)に示すようにROM17からリードする。

【0035】

メモリ制御部21は、そのリードしたデータDr1を、時刻t5〜t6の(b)に示すようにCPU12へ送出すると同時に、時刻t4〜t5の(e)に示すようにRAM13のライト用の該当アドレスAr1(W)を指定し、時刻t5〜t6の(f)に示すようにRAM13に複写する。この複写時に、時刻t4〜t5の(c)に示すように複写管理メモリ22のアドレスAc1(W)においてRAM13にデータDr1を複写したことを示す「1」が立てられる。

【0036】

次に、図4のタイムチャートを用いて、複写管理メモリ22の複写情報領域に複写済みの情報「1」が格納されている場合の動作について説明する。

【0037】

自動化システムの電源投入時の起動時に、まず、CPU12が、図4に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードしている。これによりメモリ制御部21は、(c)に示すように複写管理メモリ22からアドレスAc1(R)のデータがRAM13内にあるか否かを確認するために複写情報のリードを行い、同時に(f)に示すようにアドレスAc1のデータが格納されるように割り当てられているRAM13の記憶領域からデータDr1(R)をリードする。

【0038】

この際、複写管理メモリ22からリードした複写情報からアドレスAc1のデータDc1がRAM13に複写済みであると判断、つまり時刻t2〜t3の(d)に示すように複写済みと判断されると、RAM13からリードしたデータDr1を(b)に示すようにCPU12へ送出する。この際、ROM17へのアクセスは実行されない。

(実施形態の効果)

以上説明のように本実施形態に係るプログラムダウンロードの自動化システムによれば、CPU12が用いるプログラムの格納メモリとしてROM17を有し、電源起動時にROM17からRAM13に複写されたプログラムコードを用いてCPU12が動作を行う。本実施形態の特徴は、ROM17から読み出されたプログラムコードのデータがRAM13に複写されたか否かを示す複写情報を格納する複写管理メモリ22と、CPU12が読み込むデータの複写情報を複写管理メモリ22で確認し、この確認した複写情報が複写済みを示す場合、RAM13から該当のデータを読み出してCPU12に送出し、その確認した複写情報が未複写を示す場合、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出するメモリ制御部21とを有することにある。

【0039】

この構成によれば、電源起動時にCPU12がプログラムコードのデータを読み込む際に、メモリ制御部21が複写管理メモリ22を確認しながら行うので、従来のようなCPU12がROM17からRAM13へプログラムコードを複写するための専用のプログラムが不要となり、そのプログラムの実行も無くなる。従って、プログラムコードの縮減を図ることができる。

【0040】

また、本実施形態では2回目以降のCPU12のデータの読み込みではRAM13からデータを読み込むのでアクセス時間が大幅に短縮される。従って、電源立上げ時の起動時間の短縮を図ることができる。

【0041】

また、上記のメモリ制御部21は、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出した後、複写管理メモリ22におけるRAM13への複写状態を示す該当複写情報を複写済みとするようにした。

【0042】

これによって、RAM13へのデータ複写後に、当該複写状態を示す複写情報を適正に複写管理メモリ22に記憶することができる。

(実施形態の応用例1)

また、本実施形態の応用例1として、図1に示したプログラムダウンロードの自動化システムを、図5に示すように、ASIC25内において、メモリ制御部21に内部バス10にエラー検出手段としてのECC(Error Check Correct)27を追加して接続した構成とする。

【0043】

ECC27は、CPU12がプログラムコードのデータをRAM13から読み込む際に、そのデータにエラーがないか否かをチェック(ECCチェック)する。通常ECCではデータ72ビット当り1ビットまではエラーを修正できるが、2ビット以上エラーがあれば修正不可能となっている。本応用例1のECC27では、2ビット以上、即ち、3ビット又は4ビット等の複数ビットのエラーの修復が可能である。

【0044】

ここで、図6に示すように、RAM13のビット構成は各アドレス「0000」…「001C」…毎のデータが32ビット(bit)となっており、ECC27のECCコードECC0は、アドレス「0000」と「0008」とのデータ64ビットから生成された8ビットとなっている。複写管理メモリ22の複写管理0は、アドレス「0000」と「0008」とのデータをROM17からRAM13へ複写したか否かを表す2ビットの情報である。

【0045】

このような構成の自動化システムの動作は、図7に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードする際、時刻t2〜t3の(e)に示すように、そのデータAP1(R)に対応する複写情報Dc1(R)が「1」であった場合、(c)に示すようにRAM13からデータAP1(R)に対応するデータDr1(R)をリードする。この際、(d)に示すように、そのデータDe1(R)がECCチェックにより2ビットエラーと判定された場合、時刻t3〜t4の(f)に示すように再度それに対応するデータをROM17からリードし、このリードデータを、時刻t4〜t5の(b)及び(c)に示すようにCPU12へ送出すると共にRAM13へ複写する。この際、(d)に示すようにECCチェックの状態はエラー無しとなる。

【0046】

このようにRAM13のデータに2ビットエラーがあっても、それに対応するデータをROM17からリードしてRAM13に複写するので、結果的に2ビットエラーを修正することができる。

(実施形態の応用例2)

更に、本実施形態の応用例2として、図1に示したプログラムダウンロードの自動化システムを、図8に示すように、複写管理メモリ22を無くし、上記のRAM13に代え、RAM領域13a、ECC領域13b及び複写管理メモリ22としての複写管理領域13cから成るRAM13−1を用いて構成した。但し、RAM領域13a、ECC領域13b及び複写管理領域13cはRAM13−1内に一体に構成されているが、各々の関係は上記の図6に示した構成と同じである。

【0047】

この構成のRAM13−1においても、上記応用例1と略同様の動作を行うが次の点で異なる。即ち、メモリ制御部21がCPU12へ送出するデータが複写管理領域13cの複写情報から複写済みか否かを確認し、複写済みであればRAM領域13aからCPU12へ送出するデータをリードし、このデータのエラーをECC領域13bのECCチェックによって確認する。従って、CPU12への送出データがRAM13への複写済みか否かをチェックする動作と、複写済みの際にRAM13からリードしたデータをECCチェックする動作を1つのRAM13−1内で行えるので、効率の良いデータ読み出し制御を行うことができる。

【0048】

この他、上記応用例1又は2において、電源投入の初期化時に、メモリ制御部21がRAM13の格納データが必ず2ビット以上のエラーとなるように設定するようにしてもよい。この場合、RAM13のデータが必ず2ビット以上エラーとなっているので、1回目ではメモリ制御部21がCPU12へのデータを読み込んだ際にECCチェックで2ビットエラーが必ず検出されるため、ROM17から対応するデータを読み込んでRAM13に複写する。

【0049】

従って、2度目以降にCPU12が必要なデータをメモリ制御部21がRAM13から読み込む場合、ECCチェックはOKとなってエラーの無いデータをリードすることができる。このため、複写管理メモリ22又は複写管理領域13cでの複写情報による複写済みかいなかの判断は不要となる。つまり、複写管理メモリ22又は複写管理領域13cが不要となるので、上記応用例1又は2よりも、その分小型化を図ることができる。

【0050】

上記の本実施形態において、ASIC25は1つの半導体パッケージであれば市販のマイコンであってもよい。また、ECC領域13bを64ビットに対して8ビットとしたがビット数が異なっていても良く、ECCチェック演算を行うデータが32ビット離れたものでなくても良い。

【0051】

更に、複写管理メモリ22又は複写管理領域13cのビットは32ビットに対して1ビットとしたが、管理単位ビットを変えても良い。例えば、Instruction Cacheを持つシステム等で256ビット単位でROM17をリードする場合、256ビットに対して複写管理ビットを1ビット割り当てる等を行うようにしてもよい。

【0052】

ROM17は、シリアルI/FでなくてもパラレルI/Fでもよい。パラレルI/Fであっても、ROM17が8ビットバス、RAM13が32ビットバスの場合や、ROM17のI/FよりRAM13のI/Fが速い場合など、ROM17のデータをRAM13に複写して使用することがあるので、本発明の構成方法を用いれば同様の効果が得られる。

【0053】

以上、本発明の好ましい実施形態について詳述したが、本発明の技術的範囲予測は上記実施形態に記載の範囲予測には限定されないことは言うまでもない。上記実施形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。またその様な変更または改良を加えた形態も本発明の技術的範囲予測に含まれ得ることが、特許請求の範囲予測の記載から明らかである。

【符号の説明】

【0054】

10・・内部バス、12・・CPU、13・・RAM、17・・ROM、21・・メモリ制御部、22・・複写管理メモリ、22・・ASIC、27・・ECC、13−1・・RAM、13a・・RAM領域、13b・・ECC領域、13c・・複写管理領域。

【技術分野】

【0001】

本発明は、CPU(Central Processing Unit)が用いるプログラムの格納メモリとしてシリアルI/F(又はパラレルI/F)のROMを有し、電源を立ち上げた起動時にCPUがROMからプログラムコードを一旦読み込んでRAMに複写した後に、CPUがRAMに複写されたプログラムコードを用いて所定のプログラム動作を行う、プログラムダウンロードの自動化システムに関する。

【背景技術】

【0002】

従来のプログラムダウンロードの自動化システムの構成図を図9に示す。この図9に示す自動化システムは、内部バス10に接続されたCPU12、RAM(Random Access Memory)13及びシリアルI/F(インタフェース)14が、1つの半導体パッケージとしてのASIC(Application Specific Integrated

Circuit)15に収容され、ASIC15の外部に配置されたシリアルI/Fを持つROM(Read Only Memory)17がシリアルI/F14に接続されて構成されている。なお、CPU12、RAM13、及びシリアルI/F14が1つの半導体パッケージに収容されているのは、CPU12とRAM13間のアクセス速度を高速化し、後述のようにRAM13に転送されたプログラムコードを高速にリードするためである。

【0003】

CPU12は、自動化システムの制御を司り、RAM13は、プログラムやCPU12の制御に必要なデータを格納する揮発性メモリである。シリアルI/F14は、ROM17と内部バス10との間でデータを順次伝送する。ROM17は、CPU12を制御するためのプログラムコードを格納するシリアルI/F方式の不揮発性メモリである。

【0004】

このような構成の自動化システムの動作を図10に示すタイムチャートを参照して説明する。図10はROM17に格納されたプログラムコードをRAM13に複写する動作を示すタイムチャートである。ROM17にはCPU12が所定の動作を実行するためのプログラムコードが予め記憶されている。

【0005】

自動化システムの電源投入時の起動時には、まず、CPU12が、図10に示す時刻t1〜t2において(a)に示すアドレスAP1(R)を指定することによって、時刻t2〜t3において、内部バス10及びシリアルI/F14を介してROM17にアクセスし、時刻t3〜t4において、ROM17に記憶されたプログラムコードのデータDp1をリード(R)する。このリードしたデータDp1をRAM13の記憶領域のアドレスAp2(W)を指定して、時刻t4〜t5においてRAM13に書き込んで複写(W)する。

【0006】

このようなアクセスを全てのプログラムコードの複写が完了するまで繰り返す。この複写が完了すると、CPU12はプログラムの実行をRAM13に複写されたプログラムコードをアクセスすることにより行う。この種の技術として特許文献1,2に記載の技術がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平10−097427号公報

【特許文献1】特開平07−225686号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述した従来の自動化システムによれば、CPU12がROM17からRAM13へプログラムコードを複写するための専用のプログラムが必要となると共にそのプログラムの実行が必要となり、また、プログラム実行のためにROM17からリードしたプログラムコードをRAM13へ複写するために、再度ROM17からプログラムコードをリードする必要がある。更に、ROM17に記憶された複写対象のプログラムコードの一部に使用されないコードがあっても、そのコード部分のみを外してRAM13に転送するのは非効率である。例えば、プログラムコードに不要のコードが虫食い状態に存在する場合などには、その不要コード部分のみを外してRAM13に転送することは、転送プログラムの複雑化や制御メモリの増大を招くので、プログラムコード全体を一括して転送する方が効率がよい。しかし、プログラムコード全体の量が膨大であると、一括転送する転送時間が長くなってしまう。

【0009】

これらの理由から、プログラムコードの複写の際に無駄な動作が発生し、このため電源立上げ時の起動時間が長くなってしまい、また、複写専用のプログラムが必要なので、プログラムコードが増大してしまうといった問題がある。

【0010】

本発明は上記した課題を解決するためになされたものであり、ROMからRAMへのプログラムコードの複写を専用のプログラム制御を用いることなく可能とし、これによりプログラムコードの縮減並びに電源立上げ時の起動時間の短縮を図ることができる、プログラムダウンロードの自動化システムを提供することを目的とする。

【課題を解決するための手段】

【0011】

上記した課題を解決するために本発明は、CPUが用いるプログラムコードの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリに複写されたか否かを示す複写情報を格納する複写管理メモリと、前記CPUが読み込むデータの前記複写情報を前記複写管理メモリから確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリから該当のデータを読み出して前記CPUに送出し、前記確認した複写情報が未複写を示す場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部と、を有することを特徴とする。

【0012】

この構成によれば、電源起動時にCPUがプログラムコードのデータを読み込む際に、メモリ制御部が複写管理メモリを確認しながら行うので、従来のようなCPUが不揮発性メモリから揮発性メモリへプログラムコードを複写するための専用のプログラムが不要となり、そのプログラムの実行も無くなる。従って、プログラムコードの縮減を図ることができる。また、2回目以降のCPUのデータの読み込みでは揮発性メモリからデータを読み込むのでアクセス時間が大幅に短縮される。従って、電源立上げ時の起動時間の短縮を図ることができる。

【0013】

また、本発明において、前記メモリ制御部は、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出した後、前記複写管理メモリにおける揮発性メモリへの未複写の複写状態を示す該当複写情報を複写済みとすることを特徴とする。

【0014】

この構成によれば、揮発性メモリへのデータ複写後に、当該複写状態を示す複写情報を適正に複写管理メモリに記憶することができる。

【0015】

また、本発明において、前記複写管理メモリの複写情報が複写済みの際に前記メモリ制御部により前記揮発性メモリから読み出されるデータにエラーがあることを検出する、前記メモリ制御部に接続されたエラー検出手段を備え、前記メモリ制御部は、前記エラー検出手段で前記データに複数ビットのエラーがあると検出された場合、前記エラー検出データに対応するデータを前記不揮発性メモリから読み出し、この読み出しデータを前記揮発性メモリに複写すると共に前記CPUへ送出することを特徴とする。

【0016】

この構成によれば、ECCチェックでは、通常データの72ビット当たり1ビットまではエラーを修正できるが、2ビット以上エラーがあれば修正不可能である。しかし、本発明のECCチェックでは、2ビット以上エラーがあっても、それに対応するデータを不揮発性メモリから読み出し、これをCPUへ送出すると共に揮発性メモリへ複写するようにしたので、結果的に2ビットエラーを修正することができる。

【0017】

また、本発明において、前記CPU、前記揮発性メモリ、前記複写管理メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項1〜3の何れか1つに記載のプログラムダウンロードの自動化システム。

【0018】

この構成によれば、CPU、揮発性メモリ、複写管理メモリ、メモリ制御部の各要素が内部バスで接続されるのでアクセス速度を高速化して、データ転送を高速に行うことができる。

【0019】

また、本発明は、CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、前記揮発性メモリは、前記不揮発性メモリから読み出されたプログラムコードのデータを格納する揮発性メモリ領域と、この揮発性メモリ領域から読み出されるデータにエラーがあることを検出するエラー検出領域と、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリ領域に複写されたか否かを示す複写情報を格納する複写管理領域とを有し、前記CPUが読み込むデータの前記複写情報を前記複写管理領域で確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリ領域から読み出されるデータのエラー検出を行い、このエラー検出で複数ビットのエラーがあった場合又は前記複写管理領域での複写情報が未複写である場合に、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリ領域に複写すると共に前記CPUへ送出するメモリ制御部と、を有することを特徴とする。

【0020】

この構成によれば、CPUへの送出データが揮発性メモリへの複写済みか否かをチェックする動作と、複写済みの際に揮発性メモリからリードしたデータをECCチェックする動作を1つの揮発性メモリの1回のリードアクセス動作により行えるので、効率の良いデータ読み出し制御を行うことができる。

【0021】

また、本発明は、CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムコードを前記CPUが用いて動作を行うプログラムダウンロードの自動化システムにおいて、前記揮発性メモリの格納データが前記電源起動時に複数ビットのエラーとなるように設定しておき、前記CPUが読み込むデータを前記揮発性メモリから読み出す際に、この読み出しデータにエラーがなければ前記揮発性メモリからそのデータを読み出して前記CPUに送出し、前記読み出しデータに複数ビットのエラーが有る場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部、を有することを特徴とする。

【0022】

この構成によれば、電源起動時に、メモリ制御部が揮発性メモリの格納データが必ず2ビット以上のエラーとなるように制御するので、1回目では揮発性メモリのデータが必ず2ビット以上エラーとなる。従って、メモリ制御部21がCPU12へのデータを読み込んだ際にECCチェックで必ず2ビットエラーが検出されるので、不揮発性メモリから対応するデータを読み込んで揮発性メモリに複写する。従って、2度目以降にCPUが必要なデータをメモリ制御部が揮発性メモリから読み込む場合、ECCチェックはOKとなってエラーの無いデータを読み出すことができる。このため、本発明の他の構成で必要であった複写管理メモリ又は複写管理領域が不要となるので、その分小型化を図ることができる。

【0023】

また、本発明において、前記CPU、前記揮発性メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする。

【0024】

この構成によれば、CPU、揮発性メモリ、メモリ制御部の各要素が内部バスで接続されるのでアクセス速度を高速化して、データ転送を高速に行うことができる。

【発明の効果】

【0025】

本発明によれば、ROMからRAMへのプログラムコードの複写を専用のプログラム制御を用いることなく可能とし、これによりプログラムコードの縮減並びに電源立上げ時の起動時間の短縮を図ることができるプログラムダウンロードの自動化システムを提供することができる。

【図面の簡単な説明】

【0026】

【図1】本実施形態に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図2】複写管理メモリのビット構成を示す図である。

【図3】本実施形態に係るプログラムダウンロードの自動化システムの複写情報が未複写の際の動作を説明するためのタイムチャートである。

【図4】本実施形態に係るプログラムダウンロードの自動化システムの複写情報が複写済みの際の動作を説明するためのタイムチャートである。

【図5】本実施形態の応用例1に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図6】本実施形態の応用例1の不揮発性メモリのビット構成並びにECCチェック及び複写管理の状態を示す図である。

【図7】本実施形態の応用例1のECCエラー時の自動化システムの動作を説明するためのタイムチャートである。

【図8】本実施形態の応用例2に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図9】従来のプログラムダウンロードの自動化システムの構成を示すブロック図である。

【図10】従来のプログラムダウンロードの自動化システムの動作を説明するためのタイムチャートである。

【発明を実施するための形態】

【0027】

以下、添付図面を参照して本発明を実施するための実施の形態(以下、単に本実施形態という)について詳細に説明する。

(実施形態の構成)

図1は、本実施形態に係るプログラムダウンロードの自動化システムの構成を示すブロック図である。本実施形態に係るプログラムダウンロードの自動化システム(以降、単に自動化システムともいう)は、内部バス10で接続されたCPU12及びメモリ制御部21と、メモリ制御部21に接続されたRAM13及び複写管理メモリ22とが、1つの半導体パッケージとしてのASIC25に収容され、このASIC25の外部に配置されたシリアルI/Fを持つROM17がメモリ制御部21に接続されて構成されている。

【0028】

CPU12は、自動化システム(不図示)の制御を司り、RAM13は、プログラムやCPU12の制御に必要なデータを格納する揮発性メモリである。ROM17は、CPU12を制御するためのプログラムコードを格納するシリアルI/F方式の不揮発性メモリである。

【0029】

複写管理メモリ22は、メモリ制御部21の制御でROM17からリードされたプログラムコードがRAM13に複写されたか否かを管理するものであり、図2に示すビット構成となっている。このビット構成は、下から上に向かう列方向が0,1,2,…,nと増加するnアドレスで、且つ右から左へ向かう行方向が0,1,2,3,…,28,29,30,31と順にビット数が増加する32ビットの複写情報の格納領域(複写情報領域という)を備え、各複写情報領域にプログラムコードの複写時に「1」、未複写時に「0」となる複写情報が格納されている。

【0030】

メモリ制御部21は、複写管理メモリ22の複写情報領域に格納された複写情報を確認して読込対象のプログラムコードが無い場合、そのプログラムコードをROM17から読み込み、これを内部バス10を介してCPU12へ送出すると共にRAM13に書き込んで複写し、この後、複写管理メモリ22の該当の複写情報領域に複写情報「1」を記憶する制御を行う。一方、プログラムコードが有る場合、RAM13からそのプログラムコードをリードして内部バス10を介してCPU12へ送出する。

【0031】

つまり、CPU12は、必要なプログラムコードをリードするためのアドレスをメモリ制御部21に送り、メモリ制御部21はそのアドレスに応じた複写管理メモリ22の複写情報領域に「0」か「1」が立っているか確認する。「1」がたっていればRAM13からプログラムコードをリードしてCPU12へ送る。「0」が立っていればそのアドレスのプログラムコードをROM17からリードしてRAM13及びCPU12へ送った後、複写管理メモリ22の該当複写情報領域に「1」を立てる。

(実施形態の動作)

以下、図1に示す本実施形態に係るプログラムダウンロードの自動化システム1の動作について、図3、図4のタイムチャートを参照しながら詳細に説明する。

【0032】

まず、図3のタイムチャートを用いて、複写管理メモリ22の複写情報領域に未複写時の情報「0」が格納されている場合の動作について説明する。なお、(R)はリード、(W)はライトを表す。

【0033】

自動化システムの電源投入時の起動時に、まず、CPU12が、図3に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードしている。これによりメモリ制御部21は、(c)に示すように複写管理メモリ22からアドレスAc1(R)のプログラムコードのデータがRAM13内にあるか否かを確認するために複写情報のリードを行い、同時にアドレスAc1のデータが格納されるように割り当てられているRAM13の記憶領域からデータDr1(R)をリードする。

【0034】

この際、複写管理メモリ22からリードした複写情報からアドレスAc1のデータDc1がRAM13には複写されていないと判断、つまり時刻t2〜t3の(d)に示すように未複写と判断されると、RAM13からリードしたデータDr1を破棄する。この場合、その破棄データに相当するデータDr1を、時刻t3〜t5の(g)に示すようにROM17からリードする。

【0035】

メモリ制御部21は、そのリードしたデータDr1を、時刻t5〜t6の(b)に示すようにCPU12へ送出すると同時に、時刻t4〜t5の(e)に示すようにRAM13のライト用の該当アドレスAr1(W)を指定し、時刻t5〜t6の(f)に示すようにRAM13に複写する。この複写時に、時刻t4〜t5の(c)に示すように複写管理メモリ22のアドレスAc1(W)においてRAM13にデータDr1を複写したことを示す「1」が立てられる。

【0036】

次に、図4のタイムチャートを用いて、複写管理メモリ22の複写情報領域に複写済みの情報「1」が格納されている場合の動作について説明する。

【0037】

自動化システムの電源投入時の起動時に、まず、CPU12が、図4に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードしている。これによりメモリ制御部21は、(c)に示すように複写管理メモリ22からアドレスAc1(R)のデータがRAM13内にあるか否かを確認するために複写情報のリードを行い、同時に(f)に示すようにアドレスAc1のデータが格納されるように割り当てられているRAM13の記憶領域からデータDr1(R)をリードする。

【0038】

この際、複写管理メモリ22からリードした複写情報からアドレスAc1のデータDc1がRAM13に複写済みであると判断、つまり時刻t2〜t3の(d)に示すように複写済みと判断されると、RAM13からリードしたデータDr1を(b)に示すようにCPU12へ送出する。この際、ROM17へのアクセスは実行されない。

(実施形態の効果)

以上説明のように本実施形態に係るプログラムダウンロードの自動化システムによれば、CPU12が用いるプログラムの格納メモリとしてROM17を有し、電源起動時にROM17からRAM13に複写されたプログラムコードを用いてCPU12が動作を行う。本実施形態の特徴は、ROM17から読み出されたプログラムコードのデータがRAM13に複写されたか否かを示す複写情報を格納する複写管理メモリ22と、CPU12が読み込むデータの複写情報を複写管理メモリ22で確認し、この確認した複写情報が複写済みを示す場合、RAM13から該当のデータを読み出してCPU12に送出し、その確認した複写情報が未複写を示す場合、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出するメモリ制御部21とを有することにある。

【0039】

この構成によれば、電源起動時にCPU12がプログラムコードのデータを読み込む際に、メモリ制御部21が複写管理メモリ22を確認しながら行うので、従来のようなCPU12がROM17からRAM13へプログラムコードを複写するための専用のプログラムが不要となり、そのプログラムの実行も無くなる。従って、プログラムコードの縮減を図ることができる。

【0040】

また、本実施形態では2回目以降のCPU12のデータの読み込みではRAM13からデータを読み込むのでアクセス時間が大幅に短縮される。従って、電源立上げ時の起動時間の短縮を図ることができる。

【0041】

また、上記のメモリ制御部21は、ROM17から該当のデータを読み出し、RAM13に複写すると共にCPU12へ送出した後、複写管理メモリ22におけるRAM13への複写状態を示す該当複写情報を複写済みとするようにした。

【0042】

これによって、RAM13へのデータ複写後に、当該複写状態を示す複写情報を適正に複写管理メモリ22に記憶することができる。

(実施形態の応用例1)

また、本実施形態の応用例1として、図1に示したプログラムダウンロードの自動化システムを、図5に示すように、ASIC25内において、メモリ制御部21に内部バス10にエラー検出手段としてのECC(Error Check Correct)27を追加して接続した構成とする。

【0043】

ECC27は、CPU12がプログラムコードのデータをRAM13から読み込む際に、そのデータにエラーがないか否かをチェック(ECCチェック)する。通常ECCではデータ72ビット当り1ビットまではエラーを修正できるが、2ビット以上エラーがあれば修正不可能となっている。本応用例1のECC27では、2ビット以上、即ち、3ビット又は4ビット等の複数ビットのエラーの修復が可能である。

【0044】

ここで、図6に示すように、RAM13のビット構成は各アドレス「0000」…「001C」…毎のデータが32ビット(bit)となっており、ECC27のECCコードECC0は、アドレス「0000」と「0008」とのデータ64ビットから生成された8ビットとなっている。複写管理メモリ22の複写管理0は、アドレス「0000」と「0008」とのデータをROM17からRAM13へ複写したか否かを表す2ビットの情報である。

【0045】

このような構成の自動化システムの動作は、図7に示す時刻t1〜t2において(a)に示すアドレスAp1(R)をリードする際、時刻t2〜t3の(e)に示すように、そのデータAP1(R)に対応する複写情報Dc1(R)が「1」であった場合、(c)に示すようにRAM13からデータAP1(R)に対応するデータDr1(R)をリードする。この際、(d)に示すように、そのデータDe1(R)がECCチェックにより2ビットエラーと判定された場合、時刻t3〜t4の(f)に示すように再度それに対応するデータをROM17からリードし、このリードデータを、時刻t4〜t5の(b)及び(c)に示すようにCPU12へ送出すると共にRAM13へ複写する。この際、(d)に示すようにECCチェックの状態はエラー無しとなる。

【0046】

このようにRAM13のデータに2ビットエラーがあっても、それに対応するデータをROM17からリードしてRAM13に複写するので、結果的に2ビットエラーを修正することができる。

(実施形態の応用例2)

更に、本実施形態の応用例2として、図1に示したプログラムダウンロードの自動化システムを、図8に示すように、複写管理メモリ22を無くし、上記のRAM13に代え、RAM領域13a、ECC領域13b及び複写管理メモリ22としての複写管理領域13cから成るRAM13−1を用いて構成した。但し、RAM領域13a、ECC領域13b及び複写管理領域13cはRAM13−1内に一体に構成されているが、各々の関係は上記の図6に示した構成と同じである。

【0047】

この構成のRAM13−1においても、上記応用例1と略同様の動作を行うが次の点で異なる。即ち、メモリ制御部21がCPU12へ送出するデータが複写管理領域13cの複写情報から複写済みか否かを確認し、複写済みであればRAM領域13aからCPU12へ送出するデータをリードし、このデータのエラーをECC領域13bのECCチェックによって確認する。従って、CPU12への送出データがRAM13への複写済みか否かをチェックする動作と、複写済みの際にRAM13からリードしたデータをECCチェックする動作を1つのRAM13−1内で行えるので、効率の良いデータ読み出し制御を行うことができる。

【0048】

この他、上記応用例1又は2において、電源投入の初期化時に、メモリ制御部21がRAM13の格納データが必ず2ビット以上のエラーとなるように設定するようにしてもよい。この場合、RAM13のデータが必ず2ビット以上エラーとなっているので、1回目ではメモリ制御部21がCPU12へのデータを読み込んだ際にECCチェックで2ビットエラーが必ず検出されるため、ROM17から対応するデータを読み込んでRAM13に複写する。

【0049】

従って、2度目以降にCPU12が必要なデータをメモリ制御部21がRAM13から読み込む場合、ECCチェックはOKとなってエラーの無いデータをリードすることができる。このため、複写管理メモリ22又は複写管理領域13cでの複写情報による複写済みかいなかの判断は不要となる。つまり、複写管理メモリ22又は複写管理領域13cが不要となるので、上記応用例1又は2よりも、その分小型化を図ることができる。

【0050】

上記の本実施形態において、ASIC25は1つの半導体パッケージであれば市販のマイコンであってもよい。また、ECC領域13bを64ビットに対して8ビットとしたがビット数が異なっていても良く、ECCチェック演算を行うデータが32ビット離れたものでなくても良い。

【0051】

更に、複写管理メモリ22又は複写管理領域13cのビットは32ビットに対して1ビットとしたが、管理単位ビットを変えても良い。例えば、Instruction Cacheを持つシステム等で256ビット単位でROM17をリードする場合、256ビットに対して複写管理ビットを1ビット割り当てる等を行うようにしてもよい。

【0052】

ROM17は、シリアルI/FでなくてもパラレルI/Fでもよい。パラレルI/Fであっても、ROM17が8ビットバス、RAM13が32ビットバスの場合や、ROM17のI/FよりRAM13のI/Fが速い場合など、ROM17のデータをRAM13に複写して使用することがあるので、本発明の構成方法を用いれば同様の効果が得られる。

【0053】

以上、本発明の好ましい実施形態について詳述したが、本発明の技術的範囲予測は上記実施形態に記載の範囲予測には限定されないことは言うまでもない。上記実施形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。またその様な変更または改良を加えた形態も本発明の技術的範囲予測に含まれ得ることが、特許請求の範囲予測の記載から明らかである。

【符号の説明】

【0054】

10・・内部バス、12・・CPU、13・・RAM、17・・ROM、21・・メモリ制御部、22・・複写管理メモリ、22・・ASIC、27・・ECC、13−1・・RAM、13a・・RAM領域、13b・・ECC領域、13c・・複写管理領域。

【特許請求の範囲】

【請求項1】

CPUが用いるプログラムコードの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、

前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリに複写されたか否かを示す複写情報を格納する複写管理メモリと、

前記CPUが読み込むデータの前記複写情報を前記複写管理メモリから確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリから該当のデータを読み出して前記CPUに送出し、前記確認した複写情報が未複写を示す場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部と、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項2】

前記メモリ制御部は、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出した後、前記複写管理メモリにおける揮発性メモリへの未複写の複写状態を示す該当複写情報を複写済みとすることを特徴とする請求項1記載のプログラムダウンロードの自動化システム。

【請求項3】

前記複写管理メモリの複写情報が複写済みの際に前記メモリ制御部により前記揮発性メモリから読み出されるデータにエラーがあることを検出する、前記メモリ制御部に接続されたエラー検出手段を備え、

前記メモリ制御部は、前記エラー検出手段で前記データに複数ビットのエラーがあると検出された場合、前記エラー検出データに対応するデータを前記不揮発性メモリから読み出し、この読み出しデータを前記揮発性メモリに複写すると共に前記CPUへ送出することを特徴とする請求項1又は2記載のプログラムダウンロードの自動化システム。

【請求項4】

前記CPU、前記揮発性メモリ、前記複写管理メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項1〜3の何れか1つに記載のプログラムダウンロードの自動化システム。

【請求項5】

CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、

前記揮発性メモリは、前記不揮発性メモリから読み出されたプログラムコードのデータを格納する揮発性メモリ領域と、この揮発性メモリ領域から読み出されるデータにエラーがあることを検出するエラー検出領域と、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリ領域に複写されたか否かを示す複写情報を格納する複写管理領域とを有し、

前記CPUが読み込むデータの前記複写情報を前記複写管理領域で確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリ領域から読み出されるデータのエラー検出を行い、このエラー検出で複数ビットのエラーがあった場合又は前記複写管理領域での複写情報が未複写である場合に、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリ領域に複写すると共に前記CPUへ送出するメモリ制御部と、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項6】

CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムコードを前記CPUが用いて動作を行うプログラムダウンロードの自動化システムにおいて、

前記揮発性メモリの格納データが前記電源起動時に複数ビットのエラーとなるように設定しておき、前記CPUが読み込むデータを前記揮発性メモリから読み出す際に、この読み出しデータにエラーがなければ前記揮発性メモリからそのデータを読み出して前記CPUに送出し、前記読み出しデータに複数ビットのエラーが有る場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項7】

前記CPU、前記揮発性メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項5又は6記載のプログラムダウンロードの自動化システム。

【請求項1】

CPUが用いるプログラムコードの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、

前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリに複写されたか否かを示す複写情報を格納する複写管理メモリと、

前記CPUが読み込むデータの前記複写情報を前記複写管理メモリから確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリから該当のデータを読み出して前記CPUに送出し、前記確認した複写情報が未複写を示す場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部と、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項2】

前記メモリ制御部は、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出した後、前記複写管理メモリにおける揮発性メモリへの未複写の複写状態を示す該当複写情報を複写済みとすることを特徴とする請求項1記載のプログラムダウンロードの自動化システム。

【請求項3】

前記複写管理メモリの複写情報が複写済みの際に前記メモリ制御部により前記揮発性メモリから読み出されるデータにエラーがあることを検出する、前記メモリ制御部に接続されたエラー検出手段を備え、

前記メモリ制御部は、前記エラー検出手段で前記データに複数ビットのエラーがあると検出された場合、前記エラー検出データに対応するデータを前記不揮発性メモリから読み出し、この読み出しデータを前記揮発性メモリに複写すると共に前記CPUへ送出することを特徴とする請求項1又は2記載のプログラムダウンロードの自動化システム。

【請求項4】

前記CPU、前記揮発性メモリ、前記複写管理メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項1〜3の何れか1つに記載のプログラムダウンロードの自動化システム。

【請求項5】

CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムダウンロードの自動化システムにおいて、

前記揮発性メモリは、前記不揮発性メモリから読み出されたプログラムコードのデータを格納する揮発性メモリ領域と、この揮発性メモリ領域から読み出されるデータにエラーがあることを検出するエラー検出領域と、前記不揮発性メモリから読み出されたプログラムコードのデータが前記揮発性メモリ領域に複写されたか否かを示す複写情報を格納する複写管理領域とを有し、

前記CPUが読み込むデータの前記複写情報を前記複写管理領域で確認し、この確認した複写情報が複写済みを示す場合、前記揮発性メモリ領域から読み出されるデータのエラー検出を行い、このエラー検出で複数ビットのエラーがあった場合又は前記複写管理領域での複写情報が未複写である場合に、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリ領域に複写すると共に前記CPUへ送出するメモリ制御部と、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項6】

CPUが用いるプログラムの格納メモリとして不揮発性メモリを有し、前記CPUが実行する前記プログラムコードを、電源起動時に前記不揮発性メモリから揮発性メモリに複写するプログラムコードを前記CPUが用いて動作を行うプログラムダウンロードの自動化システムにおいて、

前記揮発性メモリの格納データが前記電源起動時に複数ビットのエラーとなるように設定しておき、前記CPUが読み込むデータを前記揮発性メモリから読み出す際に、この読み出しデータにエラーがなければ前記揮発性メモリからそのデータを読み出して前記CPUに送出し、前記読み出しデータに複数ビットのエラーが有る場合、前記不揮発性メモリから該当のデータを読み出し、前記揮発性メモリに複写すると共に前記CPUへ送出するメモリ制御部、

を有することを特徴とするプログラムダウンロードの自動化システム。

【請求項7】

前記CPU、前記揮発性メモリ、前記メモリ制御部は、1つの半導体パッケージに収容されていることを特徴とする請求項5又は6記載のプログラムダウンロードの自動化システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−37520(P2013−37520A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−172818(P2011−172818)

【出願日】平成23年8月8日(2011.8.8)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月8日(2011.8.8)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

[ Back to top ]