プログラム保護装置および通信装置

【課題】改竄されたプログラムを実行中または実行後であっても、プログラムの改竄を検出することができるプログラム保護装置、および通信装置を提供する。

【解決手段】内部RAM−PROM−B6および外部RAM/PROM4は、所定の処理を実行する処理プログラムを記憶する。内部RAM−PROM−A8は、処理プログラムの改竄を検出する改竄検出プログラムを記憶する。CPU1は、改竄検出プログラムを実行する。CPU2は、処理プログラムを実行する。FPGA61は、CPU1、CPU2、内部RAM/PROM−A8、内部RAM/PROM−B6を含む。

【解決手段】内部RAM−PROM−B6および外部RAM/PROM4は、所定の処理を実行する処理プログラムを記憶する。内部RAM−PROM−A8は、処理プログラムの改竄を検出する改竄検出プログラムを記憶する。CPU1は、改竄検出プログラムを実行する。CPU2は、処理プログラムを実行する。FPGA61は、CPU1、CPU2、内部RAM/PROM−A8、内部RAM/PROM−B6を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プログラム保護装置および通信装置に関する。

【背景技術】

【0002】

従来から、プログラムの不正な読出しや改竄を阻止する装置が採用されている。たとえば、特許文献1(特開平11−39158号公報)に記載された実行プログラムの保護装置は、所定の実行プログラムが走行する前に、実行プログラムが改竄されていることを検出する改竄検出手段と、改竄検出手段において改竄が検出されると、実行プログラムの実行を直ちに停止する実行停止手段とを有する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−39158号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1の記載の装置では、プログラムを実行するプロセッサと、プログラムの改竄を検出するプロセッサは、同一である。

【0005】

したがって、プロセッサが、不正アクセス者によって改竄検出機能を無効にするように改竄されたプログラムを実行すれば、そのプロセッサは、もはやプログラムの改竄を検出することができなくなってしまう。そのため、特許文献1の装置では、プログラムを実行する前にプログラムの改竄を検出する必要があった。

【0006】

それゆえに、本発明の目的は、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができるプログラム保護装置、および通信装置を提供することである。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明は、プログラム保護装置であって、所定の処理を実行する処理プログラムを記憶する第1の記憶部と、処理プログラムの改竄を検出する改竄検出プログラムを記憶する第2の記憶部と、改竄検出プログラムを実行する第1のプロセッサと、処理プログラムを実行する第2のプロセッサとを備える。プログラム保護装置は、少なくとも一部の機能が、フィールドプログラマブルゲートアレイによって実現され、フィールドプログラマブルゲートアレイは、少なくとも第1のプロセッサ、第2のプロセッサ、および第2の記憶部を含む。

【発明の効果】

【0008】

本発明によれば、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができるプログラム保護装置、および通信装置を提供することである。

【図面の簡単な説明】

【0009】

【図1】本発明の実施形態の無線基地局の構成を表わす図である。

【図2】本発明の実施形態のコンフィギュレーションデータの構成を表わす図である。

【図3】通信プログラム、ロジックデータ、処理プログラム#1、および処理プログラム#2によって実行される機能を表わすブロック図である。

【図4】本発明の実施形態のメモリマップの構成を表わす図である。

【図5】処理プログラムの編集時のMD1A、MD1Bの作成手順を表わすフローチャートである。

【図6】CPU1の改竄検出プログラムの実行による改善検出処理手順を表わすフローチャートである。

【図7】CPU2の処理手順を表わすフローチャートである。

【発明を実施するための形態】

【0010】

以下、本発明の実施形態について図面を参照して説明する。

(構成)

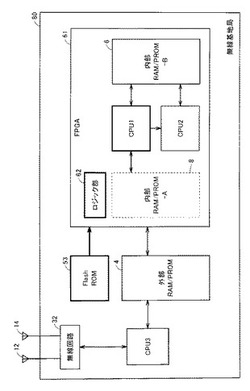

図1は、本発明の実施形態の無線基地局の構成を表わす図である。

【0011】

図1を参照して、この無線基地局80は、第1のアンテナ12と、第2のアンテナ14と、無線回路32と、CPU(Central Processing Unit)3と、FlashROM(Read Only Memory)53と、外部RAM(Random Access Memory)/PROM(Programmable Read Only Memory)4と、FPGA(Field-Programmable Gate Array:フィールドプログラマブルゲートアレイ)61とを備える。

【0012】

この無線基地局80は、従来のアダプティブアレイ演算機能を有しない無線基地局に、アダプティブアレイ演算処理を追加したものである。アダプティブアレイ演算処理の一部については、製造業者にとってノウハウを伴うことから秘匿できることが望ましい。そのため、本実施の形態では、耐タンパ性を有するFPGA61にアダプティブアレイ演算処理を組み込むこととする。具体的には、FPGA61内のCPUが、FPGA内部のRAM/ROM内のプログラムを用いてアダプティブアレイ演算機能を実行する。また、FPGA61を追加することによって、FPGA61によるロジック処理も利用できるので、本実施の形態では、FPGA61によって従来の無線基地局の通信処理の一部も実行することとする。

【0013】

あるいは、アダプティブアレイ演算機能を有する無線基地局の製造販売の依頼を受けた製造業者は、秘匿を要するアダプティブアレイ演算機能をFPGA61に組み込み、その他の通信機能をFPGA61外で処理するようにしてもよい。このようにすることで、無線基地局の購入者にアダプティブアレイ演算機能のノウハウが流出するのを防止することができる。

【0014】

FPGA61は、ロジック部62と、CPU1と、CPU2と、内部RAM/PROM−A8と、内部RAM/PROM−B6と備える。

【0015】

無線回路32は、無線周波数帯にアップコンバートするアップコンバータ、アップコンバートされた信号を増幅する電力増幅回路、増幅された信号のうち所望帯域の信号成分のみを通過させて第1のアンテナ12および第2のアンテナ14へ出力するバンドパスフィルタなどを含む。また、無線回路32は、第1のアンテナ12および第2のアンテナ14から出力される信号のうち所望帯域の信号成分のみを通過させるバンドパスフィルタ、RF信号を増幅する低雑音増幅回路、RF信号をダウンコンバートするダウンコータなどを含む。

【0016】

無線回路32へ出力する送信信号の処理、無線回路32から出力される受信信号の処理は、CPU1、CPU2、CPU3、およびロジック部62で行なわれる。

【0017】

FlashROM53は、暗号化されたコンフィギュレーションデータを記憶する。

図2は、本発明の実施形態のコンフィギュレーションデータの構成を表わす図である。

【0018】

コンフィギュレーションデータは、ロジックデータとCPUデータとが結合されたデータである。ロジックデータは、FPGA61のロジックデバイスの設計データである。

【0019】

CPUデータは、CPU1で利用されるCPU1データおよびCPU2で利用されるCPU2データからなる。

【0020】

CPU1データは、改竄検出プログラムと、MD1A、MD2Aとからなる。

改竄検出プログラムは、処理プログラム#1と処理プログラム#2の改竄を検出する。

【0021】

MD1Aは、処理プログラム#1を編集する際に作成された処理プログラム#1のMD(メッセージ・ダイジェスト)である。

【0022】

MD2Aは、処理プログラム#2を編集する際に作成された処理プログラム#2のMD(メッセージ・ダイジェスト)である。

【0023】

ここで、メッセージ・ダイジェストは、一方向ハッシュ関数を使った演算によって、プログラム(原文)から生成されるデータである。プログラムが改竄された場合に、改竄前後で、メッセージ・ダイジェストが変化する。

【0024】

CPU2データは、処理プログラム#1と処理プログラム#2とからなる。

CPU2で処理する処理プログラムを処理プログラム#1と処理プログラム#2に分けたのは、処理プログラムの容量が、FPGA61内の内部RAM/PROM−B6の容量よりも大きいので、処理プログラム全体をFPGA61内の内部RAM/PROM−B6に記憶できないからである。それゆえ、本実施の形態では、処理プログラムを秘匿性が要求される処理プログラム#1と秘匿性が要求されない処理プログラム#2に分割して、処理プログラム#1を耐タンパ性が相対的に高いFPGA61内の内部RAM/PROM−B6に記憶し、処理プログラム#2を耐タンパ性が相対的に低い外部RAM/PROM4に記憶する。処理プログラム#1と処理プログラム#2の内容については、後述する。

【0025】

外部RAM/PROM4は、CPU3で実行される通信制御プログラムを記憶する。外部RAM/PROM4は、さらに、コンフィギュレーションデータが復号されることによって得られる処理プログラム#2を記憶する。処理プログラム#2は、秘匿性が相対的に低いプログラムであるので、FPGA61の外の改竄および窃取の可能性が相対的に高いメモリであるFPGA61の外部のメモリに記憶される。処理プログラム#2は、秘匿性が相対的に低いプログラムであるが、これが改竄され、改竄された処理プログラム#2を実行したCPUは、改竄者の意図する不正な処理を実行し、処理プログラム#1を外部に出力したりするおそれがある。これを防止するために、本実施の形態では、改竄プログラムと、処理プログラム#1、#2を実行するCPUを別個のものにする。

【0026】

FlashROM53から、FPGA61へは暗号化されたコンフィギュレーションデータが送られ、FPGA61側で暗号化されたコンフィギュレーションデータを復号する。したがって、コンフィギュレーションデータのFPGA61の伝送は、秘匿の危険性は比較的少ない。

【0027】

ロジック部62は、ロジックデータが展開されて、論理処理を実行する。

内部RAM/PROM−A8は、コンフィギュレーションデータが復号されることによって得られる改竄検出プログラム、MD1A、およびMD2Aを記憶する。内部RAM/PROM−B6は、さらに、MD1B、およびMD2Bを記憶する。

【0028】

MD1Bは、改竄検出プログラムを実行することによって作成された処理プログラム#1のMD(メッセージ・ダイジェスト)である。

【0029】

MD2Bは、改竄検出プログラムを実行することによって作成された処理プログラム#2のMD(メッセージ・ダイジェスト)である。

【0030】

内部RAM/PROM−B6は、コンフィギュレーションデータが復号されることによって得られる処理プログラム#1を記憶する。処理プログラム#1は、秘匿性が要求されるプログラムであるので、FPGA61内の窃取の可能性が相対的に低いメモリに記憶される。

【0031】

CPU3は、外部RAM/PROM4に記憶された通信制御プログラムを実行する。

CPU1は、内部RAM/PROM−A8に記憶された改竄検出プログラムを実行する。改竄検出プログラムはFPGA61内にあるので改竄される危険性が少ない。仮に、CPU1が、改竄された改竄検出プログラムを実行した場合には、制御が不正アクセス者に乗っ取られる危険性があるが、本実施の形態では、改竄検出プログラムを改竄されるのを防止することによって、そのような危険性を排除している。

【0032】

CPU2は、内部RAM/PROM−B6に記憶された処理プログラム#1および外部RAM/PROM4に記憶された処理プログラム#2を実行する。

【0033】

図3は、通信プログラム、ロジックデータ、処理プログラム#1、および処理プログラム#2によって実行される機能を表わすブロック図である。

【0034】

図3を参照して、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行し、FPGA61内のロジック部62がロジックデータによって設定された論理処理を実行することによって、CP(Cyclic Prefix)除去部18と、FFT(Fast Fourier Transform)部20と、イコライザ26と、復調部28と、制御部30と、変調部40と、IFFT部36と、CP付加部34の機能を実行する。

【0035】

CP除去部18は、無線回路32から出力される信号からCPを除去する。

FFT部20は、CP除去部18から出力される時間領域の信号をFFTによって、周波数領域の信号に変換して、複数のサブキャリアに復調する。

【0036】

イコライザ26は、伝送路の特性によって変化を受けた受信信号の波形の復元や変化の最小化を目的に、受信信号の周波数特性を調整する。

【0037】

復調部28は、受信信号を復調する。

変調部40は、送信信号を変調する。

【0038】

IFFT部36は、複数のサブキャリア信号(周波数領域の信号)をIFFTによって、時間領域の信号(OFDMA(Orthogonal Frequency Division Multiple Access)シンボル)に変換する。

【0039】

CP付加部34は、OFDMAシンボルの後尾部分と同じ信号をCPとしてOFDMAシンボルの先頭に付加する。

【0040】

制御部30は、上述の各機能部の実行を制御する。

CPU2は、処理プログラム#1を実行することによって、ウエイト算出部24および受信重み付け部22として機能する。また、CPU2は、処理プログラム#2を実行することによって、送信重み付け部38として機能する。

【0041】

ウエイト算出部24は、第1のアンテナ12および第2のアンテナ14で受信し、無線回路32で処理されたトレーニング信号から伝送路を推定して、ウエイトベクトルを算出する。

【0042】

受信重み付け部22は、第1のアンテナ12および第2のアンテナ14で受信し無線回路32で処理された受信信号をウエイト算出部24で算出されたウエイトベクトルで重み付け加算する。

【0043】

送信重み付け部38は、外部から供給された送信信号をウエイト算出部24で算出されたウエイトベクトルで重み付けして、第1のアンテナ12および第2のアンテナ14へ供給する。

【0044】

(メモリマップの構成)

図4は、本発明の実施形態のメモリマップの構成を表わす図である。

【0045】

図4を参照して、CPU1は、内部RAM/PROM−A8に格納された改竄検出プログラム、実行停止プログラム、MD1A、MD2A、MD1B、MD2Bにアクセスする。

【0046】

CPU2は、外部RAM/PROM4に記憶された処理プログラム#2と内部RAM/PROM−B6に記憶された処理プログラム#1にアクセスする。

【0047】

(動作)

図5は、処理プログラムの編集時のMD1A、MD1Bの作成手順を表わすフローチャートである。

【0048】

まず、編集装置のCPUは、処理プログラム#1をRAMへロードする(ステップS101)。

【0049】

次に、編集装置のCPUは、ロードした処理プログラム#1のMD(MD1Aとする)を作成する(ステップS102)。

【0050】

次に、編集装置のCPUは、作成した処理プログラム#1のMDであるMD1Aをコンフィギュレーションデータの一部として組込む(ステップS103)。

【0051】

次に、編集装置のCPUは、処理プログラム#2をRAMへロードする(ステップS104)。

【0052】

次に、編集装置のCPUは、ロードした処理プログラム#2のMD(MD2Aとする)を作成する(ステップS105)。

【0053】

次に、編集装置のCPUは、作成した処理プログラム#2のMDであるMD2Aをコンフィギュレーションデータとの一部として組込む(ステップS106)。

【0054】

(CPU1の動作)

図6は、CPU1の改竄検出プログラムの実行による改善検出処理手順を表わすフローチャートである。

【0055】

まず、パワーオンリセットがあったとき(ステップS201でYES)、システムがリセットされたとき(ステップS202でYES)、または実行タイミング時に(ステップS203でYES)、CPU1は、処理プログラム#1のMD(MD1Bとする)を作成して、内部RAM/PROM−A8に記憶する(ステップS204)。

【0056】

CPU1は、内部RAM/PROM−A8に記憶されたMD1AとMD1Bとが1ビットでも異なる場合には(ステップS205でNO)、CPU2に停止を指示する(ステップS208)。

【0057】

CPU1は、改竄検出プログラムを実行することによって、MD1AとMD1Bとが同一の場合には(ステップS205でYES)、さらに、処理プログラム#2のMD(MD2Bとする)を作成して、内部RAM/PROM−A8に記憶する(ステップS206)。

【0058】

CPU1は、内部RAM/PROM−A8に記憶されたMD2AとMD2Bとが1ビットでも異なる場合には(ステップS207でNO)、CPU2に停止を指示する(ステップS208)。

【0059】

(CPU2の動作)

図7は、CPU2の処理手順を表わすフローチャートである。

【0060】

図7を参照して、CPU2は、CPU1から停止指示がない場合には(ステップS301でNO)、処理プログラム#1と処理プログラム#2を実行する(ステップS302)。

【0061】

CPU2は、CPU1から停止指示があった場合には(ステップS301でYES)、処理プログラム#1と処理プログラム#2の実行を停止する(ステップS303)。

【0062】

以上のように、本実施の形態によれば、改竄検出プログラムと、処理プログラムとを別個のCPUで実行することによって、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができる。

【0063】

(変形例)

本発明の実施形態では、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行し、FPGA61内のロジック部62がロジックデータによって設定された論理処理を実行することによって、従来の無線基地局の機能(CP除去部と、FFT部と、イコライザと、復調部と、制御部と、変調部と、IFFT部と、CP付加部)を実行することとしたが、これに限定するものではない。

【0064】

すなわち、FPGA61にロジックデータによる論理処理を実行させないこととし、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行することによって、上述の従来の無線基地局の機能を実行することとしてもよい。このようにした場合には、FPGA61は、アダプティブアレイ演算処理とプログラムの改竄検出処理とを専ら担当することになるので、従来の無線基地局の装置にFPGA61およびFlashROM53を取り付けるだけで、耐タンパ性を有するアダプティブアレイ演算処理を追加することができる。また、この無線基地局の利用者が、アダプティブアレイ演算機能を利用したくない場合には、無線基地局の装置からFPGA61およびFlashROM53を取り外せばよい。

【0065】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0066】

1〜3 CPU、4 外部RAM/PROM、6 内部RAM/PROM−B、8 内部RAM/PROM−A、12,14 アンテナ、18 CP除去部、20 FFT部、22 受信重み付け部、24 ウエイト算出部、26 イコライザ、28 復調部、30 制御部、32 無線回路、34 CP付加部、36 IFFT部、38 送信重み付け部、40 変調部、53 FlashROM、61 FPGA、62 ロジック部、80 無線基地局。

【技術分野】

【0001】

本発明は、プログラム保護装置および通信装置に関する。

【背景技術】

【0002】

従来から、プログラムの不正な読出しや改竄を阻止する装置が採用されている。たとえば、特許文献1(特開平11−39158号公報)に記載された実行プログラムの保護装置は、所定の実行プログラムが走行する前に、実行プログラムが改竄されていることを検出する改竄検出手段と、改竄検出手段において改竄が検出されると、実行プログラムの実行を直ちに停止する実行停止手段とを有する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−39158号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1の記載の装置では、プログラムを実行するプロセッサと、プログラムの改竄を検出するプロセッサは、同一である。

【0005】

したがって、プロセッサが、不正アクセス者によって改竄検出機能を無効にするように改竄されたプログラムを実行すれば、そのプロセッサは、もはやプログラムの改竄を検出することができなくなってしまう。そのため、特許文献1の装置では、プログラムを実行する前にプログラムの改竄を検出する必要があった。

【0006】

それゆえに、本発明の目的は、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができるプログラム保護装置、および通信装置を提供することである。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明は、プログラム保護装置であって、所定の処理を実行する処理プログラムを記憶する第1の記憶部と、処理プログラムの改竄を検出する改竄検出プログラムを記憶する第2の記憶部と、改竄検出プログラムを実行する第1のプロセッサと、処理プログラムを実行する第2のプロセッサとを備える。プログラム保護装置は、少なくとも一部の機能が、フィールドプログラマブルゲートアレイによって実現され、フィールドプログラマブルゲートアレイは、少なくとも第1のプロセッサ、第2のプロセッサ、および第2の記憶部を含む。

【発明の効果】

【0008】

本発明によれば、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができるプログラム保護装置、および通信装置を提供することである。

【図面の簡単な説明】

【0009】

【図1】本発明の実施形態の無線基地局の構成を表わす図である。

【図2】本発明の実施形態のコンフィギュレーションデータの構成を表わす図である。

【図3】通信プログラム、ロジックデータ、処理プログラム#1、および処理プログラム#2によって実行される機能を表わすブロック図である。

【図4】本発明の実施形態のメモリマップの構成を表わす図である。

【図5】処理プログラムの編集時のMD1A、MD1Bの作成手順を表わすフローチャートである。

【図6】CPU1の改竄検出プログラムの実行による改善検出処理手順を表わすフローチャートである。

【図7】CPU2の処理手順を表わすフローチャートである。

【発明を実施するための形態】

【0010】

以下、本発明の実施形態について図面を参照して説明する。

(構成)

図1は、本発明の実施形態の無線基地局の構成を表わす図である。

【0011】

図1を参照して、この無線基地局80は、第1のアンテナ12と、第2のアンテナ14と、無線回路32と、CPU(Central Processing Unit)3と、FlashROM(Read Only Memory)53と、外部RAM(Random Access Memory)/PROM(Programmable Read Only Memory)4と、FPGA(Field-Programmable Gate Array:フィールドプログラマブルゲートアレイ)61とを備える。

【0012】

この無線基地局80は、従来のアダプティブアレイ演算機能を有しない無線基地局に、アダプティブアレイ演算処理を追加したものである。アダプティブアレイ演算処理の一部については、製造業者にとってノウハウを伴うことから秘匿できることが望ましい。そのため、本実施の形態では、耐タンパ性を有するFPGA61にアダプティブアレイ演算処理を組み込むこととする。具体的には、FPGA61内のCPUが、FPGA内部のRAM/ROM内のプログラムを用いてアダプティブアレイ演算機能を実行する。また、FPGA61を追加することによって、FPGA61によるロジック処理も利用できるので、本実施の形態では、FPGA61によって従来の無線基地局の通信処理の一部も実行することとする。

【0013】

あるいは、アダプティブアレイ演算機能を有する無線基地局の製造販売の依頼を受けた製造業者は、秘匿を要するアダプティブアレイ演算機能をFPGA61に組み込み、その他の通信機能をFPGA61外で処理するようにしてもよい。このようにすることで、無線基地局の購入者にアダプティブアレイ演算機能のノウハウが流出するのを防止することができる。

【0014】

FPGA61は、ロジック部62と、CPU1と、CPU2と、内部RAM/PROM−A8と、内部RAM/PROM−B6と備える。

【0015】

無線回路32は、無線周波数帯にアップコンバートするアップコンバータ、アップコンバートされた信号を増幅する電力増幅回路、増幅された信号のうち所望帯域の信号成分のみを通過させて第1のアンテナ12および第2のアンテナ14へ出力するバンドパスフィルタなどを含む。また、無線回路32は、第1のアンテナ12および第2のアンテナ14から出力される信号のうち所望帯域の信号成分のみを通過させるバンドパスフィルタ、RF信号を増幅する低雑音増幅回路、RF信号をダウンコンバートするダウンコータなどを含む。

【0016】

無線回路32へ出力する送信信号の処理、無線回路32から出力される受信信号の処理は、CPU1、CPU2、CPU3、およびロジック部62で行なわれる。

【0017】

FlashROM53は、暗号化されたコンフィギュレーションデータを記憶する。

図2は、本発明の実施形態のコンフィギュレーションデータの構成を表わす図である。

【0018】

コンフィギュレーションデータは、ロジックデータとCPUデータとが結合されたデータである。ロジックデータは、FPGA61のロジックデバイスの設計データである。

【0019】

CPUデータは、CPU1で利用されるCPU1データおよびCPU2で利用されるCPU2データからなる。

【0020】

CPU1データは、改竄検出プログラムと、MD1A、MD2Aとからなる。

改竄検出プログラムは、処理プログラム#1と処理プログラム#2の改竄を検出する。

【0021】

MD1Aは、処理プログラム#1を編集する際に作成された処理プログラム#1のMD(メッセージ・ダイジェスト)である。

【0022】

MD2Aは、処理プログラム#2を編集する際に作成された処理プログラム#2のMD(メッセージ・ダイジェスト)である。

【0023】

ここで、メッセージ・ダイジェストは、一方向ハッシュ関数を使った演算によって、プログラム(原文)から生成されるデータである。プログラムが改竄された場合に、改竄前後で、メッセージ・ダイジェストが変化する。

【0024】

CPU2データは、処理プログラム#1と処理プログラム#2とからなる。

CPU2で処理する処理プログラムを処理プログラム#1と処理プログラム#2に分けたのは、処理プログラムの容量が、FPGA61内の内部RAM/PROM−B6の容量よりも大きいので、処理プログラム全体をFPGA61内の内部RAM/PROM−B6に記憶できないからである。それゆえ、本実施の形態では、処理プログラムを秘匿性が要求される処理プログラム#1と秘匿性が要求されない処理プログラム#2に分割して、処理プログラム#1を耐タンパ性が相対的に高いFPGA61内の内部RAM/PROM−B6に記憶し、処理プログラム#2を耐タンパ性が相対的に低い外部RAM/PROM4に記憶する。処理プログラム#1と処理プログラム#2の内容については、後述する。

【0025】

外部RAM/PROM4は、CPU3で実行される通信制御プログラムを記憶する。外部RAM/PROM4は、さらに、コンフィギュレーションデータが復号されることによって得られる処理プログラム#2を記憶する。処理プログラム#2は、秘匿性が相対的に低いプログラムであるので、FPGA61の外の改竄および窃取の可能性が相対的に高いメモリであるFPGA61の外部のメモリに記憶される。処理プログラム#2は、秘匿性が相対的に低いプログラムであるが、これが改竄され、改竄された処理プログラム#2を実行したCPUは、改竄者の意図する不正な処理を実行し、処理プログラム#1を外部に出力したりするおそれがある。これを防止するために、本実施の形態では、改竄プログラムと、処理プログラム#1、#2を実行するCPUを別個のものにする。

【0026】

FlashROM53から、FPGA61へは暗号化されたコンフィギュレーションデータが送られ、FPGA61側で暗号化されたコンフィギュレーションデータを復号する。したがって、コンフィギュレーションデータのFPGA61の伝送は、秘匿の危険性は比較的少ない。

【0027】

ロジック部62は、ロジックデータが展開されて、論理処理を実行する。

内部RAM/PROM−A8は、コンフィギュレーションデータが復号されることによって得られる改竄検出プログラム、MD1A、およびMD2Aを記憶する。内部RAM/PROM−B6は、さらに、MD1B、およびMD2Bを記憶する。

【0028】

MD1Bは、改竄検出プログラムを実行することによって作成された処理プログラム#1のMD(メッセージ・ダイジェスト)である。

【0029】

MD2Bは、改竄検出プログラムを実行することによって作成された処理プログラム#2のMD(メッセージ・ダイジェスト)である。

【0030】

内部RAM/PROM−B6は、コンフィギュレーションデータが復号されることによって得られる処理プログラム#1を記憶する。処理プログラム#1は、秘匿性が要求されるプログラムであるので、FPGA61内の窃取の可能性が相対的に低いメモリに記憶される。

【0031】

CPU3は、外部RAM/PROM4に記憶された通信制御プログラムを実行する。

CPU1は、内部RAM/PROM−A8に記憶された改竄検出プログラムを実行する。改竄検出プログラムはFPGA61内にあるので改竄される危険性が少ない。仮に、CPU1が、改竄された改竄検出プログラムを実行した場合には、制御が不正アクセス者に乗っ取られる危険性があるが、本実施の形態では、改竄検出プログラムを改竄されるのを防止することによって、そのような危険性を排除している。

【0032】

CPU2は、内部RAM/PROM−B6に記憶された処理プログラム#1および外部RAM/PROM4に記憶された処理プログラム#2を実行する。

【0033】

図3は、通信プログラム、ロジックデータ、処理プログラム#1、および処理プログラム#2によって実行される機能を表わすブロック図である。

【0034】

図3を参照して、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行し、FPGA61内のロジック部62がロジックデータによって設定された論理処理を実行することによって、CP(Cyclic Prefix)除去部18と、FFT(Fast Fourier Transform)部20と、イコライザ26と、復調部28と、制御部30と、変調部40と、IFFT部36と、CP付加部34の機能を実行する。

【0035】

CP除去部18は、無線回路32から出力される信号からCPを除去する。

FFT部20は、CP除去部18から出力される時間領域の信号をFFTによって、周波数領域の信号に変換して、複数のサブキャリアに復調する。

【0036】

イコライザ26は、伝送路の特性によって変化を受けた受信信号の波形の復元や変化の最小化を目的に、受信信号の周波数特性を調整する。

【0037】

復調部28は、受信信号を復調する。

変調部40は、送信信号を変調する。

【0038】

IFFT部36は、複数のサブキャリア信号(周波数領域の信号)をIFFTによって、時間領域の信号(OFDMA(Orthogonal Frequency Division Multiple Access)シンボル)に変換する。

【0039】

CP付加部34は、OFDMAシンボルの後尾部分と同じ信号をCPとしてOFDMAシンボルの先頭に付加する。

【0040】

制御部30は、上述の各機能部の実行を制御する。

CPU2は、処理プログラム#1を実行することによって、ウエイト算出部24および受信重み付け部22として機能する。また、CPU2は、処理プログラム#2を実行することによって、送信重み付け部38として機能する。

【0041】

ウエイト算出部24は、第1のアンテナ12および第2のアンテナ14で受信し、無線回路32で処理されたトレーニング信号から伝送路を推定して、ウエイトベクトルを算出する。

【0042】

受信重み付け部22は、第1のアンテナ12および第2のアンテナ14で受信し無線回路32で処理された受信信号をウエイト算出部24で算出されたウエイトベクトルで重み付け加算する。

【0043】

送信重み付け部38は、外部から供給された送信信号をウエイト算出部24で算出されたウエイトベクトルで重み付けして、第1のアンテナ12および第2のアンテナ14へ供給する。

【0044】

(メモリマップの構成)

図4は、本発明の実施形態のメモリマップの構成を表わす図である。

【0045】

図4を参照して、CPU1は、内部RAM/PROM−A8に格納された改竄検出プログラム、実行停止プログラム、MD1A、MD2A、MD1B、MD2Bにアクセスする。

【0046】

CPU2は、外部RAM/PROM4に記憶された処理プログラム#2と内部RAM/PROM−B6に記憶された処理プログラム#1にアクセスする。

【0047】

(動作)

図5は、処理プログラムの編集時のMD1A、MD1Bの作成手順を表わすフローチャートである。

【0048】

まず、編集装置のCPUは、処理プログラム#1をRAMへロードする(ステップS101)。

【0049】

次に、編集装置のCPUは、ロードした処理プログラム#1のMD(MD1Aとする)を作成する(ステップS102)。

【0050】

次に、編集装置のCPUは、作成した処理プログラム#1のMDであるMD1Aをコンフィギュレーションデータの一部として組込む(ステップS103)。

【0051】

次に、編集装置のCPUは、処理プログラム#2をRAMへロードする(ステップS104)。

【0052】

次に、編集装置のCPUは、ロードした処理プログラム#2のMD(MD2Aとする)を作成する(ステップS105)。

【0053】

次に、編集装置のCPUは、作成した処理プログラム#2のMDであるMD2Aをコンフィギュレーションデータとの一部として組込む(ステップS106)。

【0054】

(CPU1の動作)

図6は、CPU1の改竄検出プログラムの実行による改善検出処理手順を表わすフローチャートである。

【0055】

まず、パワーオンリセットがあったとき(ステップS201でYES)、システムがリセットされたとき(ステップS202でYES)、または実行タイミング時に(ステップS203でYES)、CPU1は、処理プログラム#1のMD(MD1Bとする)を作成して、内部RAM/PROM−A8に記憶する(ステップS204)。

【0056】

CPU1は、内部RAM/PROM−A8に記憶されたMD1AとMD1Bとが1ビットでも異なる場合には(ステップS205でNO)、CPU2に停止を指示する(ステップS208)。

【0057】

CPU1は、改竄検出プログラムを実行することによって、MD1AとMD1Bとが同一の場合には(ステップS205でYES)、さらに、処理プログラム#2のMD(MD2Bとする)を作成して、内部RAM/PROM−A8に記憶する(ステップS206)。

【0058】

CPU1は、内部RAM/PROM−A8に記憶されたMD2AとMD2Bとが1ビットでも異なる場合には(ステップS207でNO)、CPU2に停止を指示する(ステップS208)。

【0059】

(CPU2の動作)

図7は、CPU2の処理手順を表わすフローチャートである。

【0060】

図7を参照して、CPU2は、CPU1から停止指示がない場合には(ステップS301でNO)、処理プログラム#1と処理プログラム#2を実行する(ステップS302)。

【0061】

CPU2は、CPU1から停止指示があった場合には(ステップS301でYES)、処理プログラム#1と処理プログラム#2の実行を停止する(ステップS303)。

【0062】

以上のように、本実施の形態によれば、改竄検出プログラムと、処理プログラムとを別個のCPUで実行することによって、改竄された処理プログラムを実行中または実行後であっても、処理プログラムの改竄を検出することができる。

【0063】

(変形例)

本発明の実施形態では、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行し、FPGA61内のロジック部62がロジックデータによって設定された論理処理を実行することによって、従来の無線基地局の機能(CP除去部と、FFT部と、イコライザと、復調部と、制御部と、変調部と、IFFT部と、CP付加部)を実行することとしたが、これに限定するものではない。

【0064】

すなわち、FPGA61にロジックデータによる論理処理を実行させないこととし、CPU3が、外部RAM/PROM4に記憶された通信制御プログラムを実行することによって、上述の従来の無線基地局の機能を実行することとしてもよい。このようにした場合には、FPGA61は、アダプティブアレイ演算処理とプログラムの改竄検出処理とを専ら担当することになるので、従来の無線基地局の装置にFPGA61およびFlashROM53を取り付けるだけで、耐タンパ性を有するアダプティブアレイ演算処理を追加することができる。また、この無線基地局の利用者が、アダプティブアレイ演算機能を利用したくない場合には、無線基地局の装置からFPGA61およびFlashROM53を取り外せばよい。

【0065】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0066】

1〜3 CPU、4 外部RAM/PROM、6 内部RAM/PROM−B、8 内部RAM/PROM−A、12,14 アンテナ、18 CP除去部、20 FFT部、22 受信重み付け部、24 ウエイト算出部、26 イコライザ、28 復調部、30 制御部、32 無線回路、34 CP付加部、36 IFFT部、38 送信重み付け部、40 変調部、53 FlashROM、61 FPGA、62 ロジック部、80 無線基地局。

【特許請求の範囲】

【請求項1】

プログラム保護装置であって、

所定の処理を実行する処理プログラムを記憶する第1の記憶部と、

前記処理プログラムの改竄を検出する改竄検出プログラムを記憶する第2の記憶部と、

前記改竄検出プログラムを実行する第1のプロセッサと、

前記処理プログラムを実行する第2のプロセッサとを備え、

前記プログラム保護装置は、少なくとも一部の機能が、フィールドプログラマブルゲートアレイによって実現され、

前記フィールドプログラマブルゲートアレイは、少なくとも前記第1のプロセッサ、前記第2のプロセッサ、および前記第2の記憶部を含む、プログラム保護装置。

【請求項2】

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記処理プログラムの改竄が検出された場合に、前記第2のプロセッサに対して停止指示を送り、

前記第2のプロセッサは、前記第1のプロセッサから停止指示を受けたときには、前記処理プログラムの実行を停止する、請求項1記載のプログラム保護装置。

【請求項3】

前記処理プログラムは、秘匿性が要求される第1のプログラムと、秘匿性が要求されない第2のプログラムとから構成され、

前記第1の記憶部は、前記フィールドプログラマブルゲートアレイ内の内部メモリと、前記フィールドプログラマブルゲートアレイ外の外部メモリで構成され、

前記第1のプログラムは、前記内部メモリに記憶され、

前記第2のプログラムは、前記外部メモリに記憶される、請求項1記載のプログラム保護装置。

【請求項4】

前記第2の記憶部は、前記第1のプログラムの編集時に作成された前記第1のプログラムのメッセージ・ダイジェストである第1のメッセージ・ダイジェストを記憶し、

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記第1のプログラムのメッセージダイジェストである第2のメッセージ・ダイジェストを作成し、前記第2の記憶部内の前記第1のメッセージ・ダイジェストと前記第2のメッセージ・ダイジェストが一致するか否かによって、前記第1のプログラムの改竄を検出する、請求項3記載のプログラム保護装置。

【請求項5】

前記第2の記憶部は、前記第2のプログラムの編集時に作成された前記第2のプログラムのメッセージ・ダイジェストである第1のメッセージ・ダイジェストを記憶し、

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記第2のプログラムのメッセージダイジェストである第2のメッセージ・ダイジェストを作成し、前記第2の記憶部内の前記第1のメッセージ・ダイジェストと前記第2のメッセージ・ダイジェストが一致するか否かによって、前記第2のプログラムの改竄を検出する、請求項3記載のプログラム保護装置。

【請求項6】

前記プログラム保護装置は、通信装置内に設けられ、

前記処理プログラムは、複数のアンテナを用いたアダプティブアレイ演算処理を実行するプログラムである、請求項3記載のプログラム保護装置。

【請求項7】

前記第1のプログラムは、前記複数のアンテナで受信した信号からウエイトベクトルを算出する処理と、前記複数のアンテナで受信した受信信号を前記ウエイトベクトルで重み付け加算する処理とを実行するプログラムであり、

前記第2のプログラムは、送信信号を前記ウエイトベクトルで重み付けして、複数のアンテナへ供給する処理を実行するプログラムである、請求項6記載のプログラム保護装置。

【請求項8】

複数のアンテナと、

前記複数のアンテナと接続された無線回路と、

請求項6または7に記載のプログラム保護装置とを備える、通信装置。

【請求項1】

プログラム保護装置であって、

所定の処理を実行する処理プログラムを記憶する第1の記憶部と、

前記処理プログラムの改竄を検出する改竄検出プログラムを記憶する第2の記憶部と、

前記改竄検出プログラムを実行する第1のプロセッサと、

前記処理プログラムを実行する第2のプロセッサとを備え、

前記プログラム保護装置は、少なくとも一部の機能が、フィールドプログラマブルゲートアレイによって実現され、

前記フィールドプログラマブルゲートアレイは、少なくとも前記第1のプロセッサ、前記第2のプロセッサ、および前記第2の記憶部を含む、プログラム保護装置。

【請求項2】

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記処理プログラムの改竄が検出された場合に、前記第2のプロセッサに対して停止指示を送り、

前記第2のプロセッサは、前記第1のプロセッサから停止指示を受けたときには、前記処理プログラムの実行を停止する、請求項1記載のプログラム保護装置。

【請求項3】

前記処理プログラムは、秘匿性が要求される第1のプログラムと、秘匿性が要求されない第2のプログラムとから構成され、

前記第1の記憶部は、前記フィールドプログラマブルゲートアレイ内の内部メモリと、前記フィールドプログラマブルゲートアレイ外の外部メモリで構成され、

前記第1のプログラムは、前記内部メモリに記憶され、

前記第2のプログラムは、前記外部メモリに記憶される、請求項1記載のプログラム保護装置。

【請求項4】

前記第2の記憶部は、前記第1のプログラムの編集時に作成された前記第1のプログラムのメッセージ・ダイジェストである第1のメッセージ・ダイジェストを記憶し、

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記第1のプログラムのメッセージダイジェストである第2のメッセージ・ダイジェストを作成し、前記第2の記憶部内の前記第1のメッセージ・ダイジェストと前記第2のメッセージ・ダイジェストが一致するか否かによって、前記第1のプログラムの改竄を検出する、請求項3記載のプログラム保護装置。

【請求項5】

前記第2の記憶部は、前記第2のプログラムの編集時に作成された前記第2のプログラムのメッセージ・ダイジェストである第1のメッセージ・ダイジェストを記憶し、

前記第1のプロセッサは、前記改竄検出プログラムを実行することによって、前記第2のプログラムのメッセージダイジェストである第2のメッセージ・ダイジェストを作成し、前記第2の記憶部内の前記第1のメッセージ・ダイジェストと前記第2のメッセージ・ダイジェストが一致するか否かによって、前記第2のプログラムの改竄を検出する、請求項3記載のプログラム保護装置。

【請求項6】

前記プログラム保護装置は、通信装置内に設けられ、

前記処理プログラムは、複数のアンテナを用いたアダプティブアレイ演算処理を実行するプログラムである、請求項3記載のプログラム保護装置。

【請求項7】

前記第1のプログラムは、前記複数のアンテナで受信した信号からウエイトベクトルを算出する処理と、前記複数のアンテナで受信した受信信号を前記ウエイトベクトルで重み付け加算する処理とを実行するプログラムであり、

前記第2のプログラムは、送信信号を前記ウエイトベクトルで重み付けして、複数のアンテナへ供給する処理を実行するプログラムである、請求項6記載のプログラム保護装置。

【請求項8】

複数のアンテナと、

前記複数のアンテナと接続された無線回路と、

請求項6または7に記載のプログラム保護装置とを備える、通信装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−174228(P2012−174228A)

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願番号】特願2011−38886(P2011−38886)

【出願日】平成23年2月24日(2011.2.24)

【出願人】(000006633)京セラ株式会社 (13,660)

【Fターム(参考)】

【公開日】平成24年9月10日(2012.9.10)

【国際特許分類】

【出願日】平成23年2月24日(2011.2.24)

【出願人】(000006633)京セラ株式会社 (13,660)

【Fターム(参考)】

[ Back to top ]