プロセッサ及び半導体装置

【課題】実施形態は、データの入出力を遮断するための所定の信号を入力するためのピンを半導体チップに設けることなく、かつ別のプロセッサを半導体チップに内蔵することもなく、内部の秘密情報の漏洩を防止することができるプロセッサ及び半導体装置を提供することを目的とする。

【解決手段】CPU2は、JTAG-I/F4からのデータの入力及びJTAG-I/F4へのデータの出力を制御するアドレスデコーダ23と、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証ユニット26と、所定の認証信号の有無に応じて、出力すべきデータのJTAG-I/F4への出力を制御するセレクタ24と、を有する。

【解決手段】CPU2は、JTAG-I/F4からのデータの入力及びJTAG-I/F4へのデータの出力を制御するアドレスデコーダ23と、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証ユニット26と、所定の認証信号の有無に応じて、出力すべきデータのJTAG-I/F4への出力を制御するセレクタ24と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、プロセッサ及び半導体装置に関する。

【背景技術】

【0002】

従来より、パーソナルコンピュータ(以下、PCという)やエンジニアリングワークステーション(以下、EWSという)上で動作するデバッグプログラム、すなわちデバッガ、を利用して、マイクロプロセッサ等の動作を制御し、そのマイクロプロセッサの動作状態の監視、プログラムあるいはメモリの内容の参照及び修正、等が行われている。

【0003】

例えば、デバッグプログラムが動作するPCやEWSを、JTAG(Joint Test Action Group) ICE(インサーキット・エミュレータ)を介して、マイクロプロセッサを内蔵するSoC(System On Chip)に接続する。そして、ソフトウェアの開発や不具合解析を行なうオペレータが、PCやEWSのデバッグプログラム上でSoC内のマイクロプロセッサに対する操作を行なうと、その内容は、JTAG-ICEを介してSoC 内の JTAGインターフェース(I/F)に伝達される。JTAG I/Fは、オペレータの操作を、マイクロプロセッサに対してのデバッグのための割り込み要求(以下、デバッグ割り込み要求という)と、オペレータがデバッグのために意図するマイクロプロセッサの動作を実現する割り込みハンドラ(以下、デバッグ割り込みハンドラという)の提供とデータの入出力という動作に変換する。このようなSoCに内蔵されている、内部回路通信用インターフェースとしてのJTAGI/Fを利用すると、マイクロプロセッサの動作状況やメモリの内容等を容易に把握することが可能となる。よって、このような手法は、SoC及びプログラムの開発、不具合解析等にきわめて有用である。

【0004】

一方で、このような手法を用いると、SoC等の半導体装置の開発終了後、半導体装置が市場に出回った後でも、マイクロプロセッサ内の秘匿性の高いプログラム、秘匿性の高いデータ等の秘密情報の読み出しが可能となってしまうという虞がある。

そこで、半導体装置の開発の終了後、秘匿性の高い処理が半導体装置のマイクロプロセッサのプログラムで実行される場合、JTAGI/Fを通しての秘密情報の漏洩を防ぐために、プログラムや処理データを保護するための機構が半導体装置内に必要であった。例えば、外部からの所定の信号に応じてデータの入出力を遮断する回路をSoC内に設けたり、別のプロセッサをSoCに設けJTAGI/Fとの接続を制御させたり、JTAG I/F とプロセッサの接続を制御するための装置をJTAG I/Fに接続する等の方法が、秘密情報の保護のために、提案されている。

【0005】

しかし、外部からの所定の信号の入出力のためのピンを半導体チップに設けたり、別のマイクロプロセッサをJTAGI/Fとの接続制御のためだけに設けることは、半導体装置のコストの増大、チップサイズの大型化に繋がるという問題がある。また、JTAG I/Fとプロセッサの接続制御装置の操作をJTAG I/Fの操作で直接行なうことは、セキュリティ上の問題や、悪意のある者による解析の対象になりやすいという問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−165534号公報

【特許文献2】特開2007−94632号公報

【特許文献3】特開2002−358137号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

そこで、実施形態は、データの入出力を遮断するための所定の信号を入力するためのピンを半導体チップに設けることなく、かつ別のプロセッサを半導体チップに内蔵することもなく、内部の秘密情報の漏洩を防止することができるプロセッサ及び半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

実施形態によれば、内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部を有するプロセッサにおいて、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部と、前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部と、を有するプロセッサが提供される。

【図面の簡単な説明】

【0009】

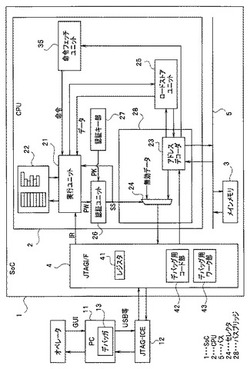

【図1】第1の実施形態に係わる、SoCを含むデバッグシステムの構成を説明するためのブロック図である。

【図2】第1の実施形態に係わる、認証ユニット26の構成を示すブロック図である。

【図3】第1の実施形態に係わる、デバッガ13の起動時のPC11の処理の流れを示すフローチャートである。

【図4】第1の実施形態に係わる、デバッグ割り込みハンドラの処理の流れの例を示すフローチャートである。

【図5】第1の実施形態に係わる、認証がされなかった場合に、得られるデータの例を説明するための図である。

【図6】第2の実施形態に係わる、SoCを含むデバッグシステムの構成を説明するためのブロック図である。

【図7】第2の実施形態に係わる、無効データ生成ユニット51の構成を示すブロック図である。

【図8】第2の実施形態に係わる、認証がされなかった場合に、得られるデータの例を説明するための図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して実施形態を説明する。

(第1の実施形態)

(構成)

まず、図1に基づき、本実施形態に係わるデバッグシステムの構成を説明する。図1は、本実施形態に係るSoCを含むデバッグシステムの構成を説明するためのブロック図である。

【0011】

半導体装置である1チップのSoC1は、マイクロプロセッサとしてのCPU2と、DRAM等のメインメモリ3と、内部回路通信用インターフェースとしてのJTAGI/F4とを含んで構成されている。CPU2とメインメモリ3は、バス5を介してデータの送受信が互いに可能に接続されている。

【0012】

SoC1は、PC(あるいはEWS)11及びJTAG-ICE12を含むデバッグ装置に、接続可能となっており、図1では、JTAG-ICE12を介してPC11に接続されている。PC11とJTAG-ICE12は、USB等のケーブルで接続されている。PC11は、デバッグプログラムであるデバッガ13を有している。PC11は、図示しないキーボード、マウスなどの入力装置とモニタを有し、ユーザからのGUIを介する指示に基づいて、SoC1をデバッグするためのデバッガ13を実行可能に構成されている。

【0013】

SoC1のCPU2は、ALU等の演算ユニットを含む実行ユニット21、複数の汎用レジスタ及び複数の制御レジスタを含むレジスタ群22、アドレスデコーダ23、命令フェッチユニット35及びロードストアユニット25を含むプロセッサである。実行ユニット21は、レジスタ群22を用いながら、命令フェッチユニット35により読み出した命令をデコードして、プログラムの実行を行う。

実行ユニット21が実行する通常のプログラム及びデータは、メインメモリ3内に存在する。よって、アドレスデコーダ23は、実行ユニット21により指定されたアドレスへのアクセスを制御し、通常のプログラムの命令列をフェッチするときは、メインメモリ3へアクセスする。しかし、実行ユニット21がデバッグ割り込みハンドラの命令列をフェッチするときは、その命令列の先頭アドレスは、JTAGI/F4内のデバッグ用コード記憶部41にあるので、アドレスデコーダ23は、JTAGI/F4へのアクセスを行うように、アクセス先の切り換えを行う。データの書き込み要求があったときも、アドレスデコーダ23は、アドレスに応じて、同様にアクセス先を切り換える。すなわち、アドレスデコーダ23は、JTAGI/F4からのデータの入力及びJTAGI/F4へのデータの出力を制御する入出力制御部を構成する。

【0014】

内部回路通信用インターフェースとしてのJTAGI/F4は、シリアル通信を用いて、半導体チップ内部に設けられたテスト用の回路にアクセスし、そのチップの端子の状態を操作したり、チップの内部回路との通信をするためのインターフェースである。

【0015】

JTAGI/F4は、レジスタ41を有する。レジスタ41には、オペレータが入力した各種コマンドに対応するコードが入力される。さらに、JTAGI/F4は、デバッグ用コード部42と、デバッグ用ワーク部43とを含む。デバッグ用コード部42には、デバッガ13からのデバッグ割り込みハンドラの命令列、すなわちデバッグ割り込み処理プログラム、がストアされる記憶領域である。デバッグ用コード部42は、デバッグ割り込み信号に対応するデバッグ割り込み処理プログラムを記憶するデバッグ割り込み処理プログラム記憶部である。デバッグ用ワーク部43は、デバッグ用ワーク領域として利用される記憶領域である。

【0016】

JTAGI/F4は、レジスタ41に所定のコードが設定されると、デバッグ割り込み信号IRをCPU2へ出力する。

実行ユニット21は、例えばパルス信号であるデバッグ割り込み信号IRを受信すると、命令フェッチユニット35を介して、割り込みハンドラの命令列のエントリーアドレスである所定のアドレスからデータを読み出して実行する。そのエントリーアドレスのデータは、JTAGI/F4のデバッグ用コード部42に記憶されているので、アドレスデコーダ23は、そのエントリーアドレスへのアクセスがあると、JTAGI/F4にアクセスしてデバッグ割り込みハンドラの命令列を読み出す。

【0017】

実行ユニット21は、JTAGI/F4のデバッグ用コード部42から読み出されたデバッグ割り込みハンドラの命令列を実行し、その実行結果を、JTAGI/F4の所定のレジスタ(図示せず)へ出力する。その実行結果の情報は、JTAG-ICE12を介して、デバッガ13により読み出し可能であり、デバッガ13は、その実行結果の情報を、GUIを介して、モニタに表示して、ユーザに知らしめることが可能である。

【0018】

ロードストアユニット25は、実行ユニット21からメインメモリ3あるいはJTAGI/F4へのデータのストア、及びメインメモリ3あるいはJTAGI/F4から実行ユニット21へのデータのロードを行うハードウェア回路である。

【0019】

CPU2は、認証ユニット26、認証キー部27及びバスブリッジ28を、さらに含む。後述するように、デバッグ割り込みハンドラの実行により、パスワードPWが、認証ユニット26に供給される。認証ユニット26は、その供給されたパスワードと、認証キー部27にストアされている所定のキーPKとに基づいて、所定の認証処理を行うハードウェア回路である。供給されたパスワードPWと、認証キー部27にストアされている所定のキーPKとを用いた所定の認証演算により、所定の結果が得られると、認証ユニット26は、認証信号として選択信号SSを出力する。よって、認証処理部である認証ユニット26は、入力されたパスワードPWと所定のキーPKとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する。

【0020】

認証キー部27には、所定のキーPKのデータが設定されており、認証ユニット26により読み出し可能なハードウェア回路である。

【0021】

バスブリッジ28は、上記のアドレスデコーダ23と、セレクタ24を含んで構成されている。バスブリッジ28は、CPU2と、SoC1内のバス5とJTAGI/F4との間のインターフェースであり、セレクタ24は、JTAGI/F4との間に設けられている。

【0022】

アドレスデコーダ23は、JTAGI/F4との間でのデータの入出力を制御する入出力制御部であり、ロードストアユニット25によってロード及びストアするデータのアドレスに応じて、メインメモリ3とJTAGI/F4へのアクセスを切り換える。

セレクタ24は、選択信号SSの有無に応じて、出力すべきデータのJTAGI/F4への出力を制御する出力制御部である。具体的には、セレクタ24は、出力すべきデータと所定のデータのいずれかを選択する。セレクタ24は、アドレスデコーダ23からJTAGI/F4への出力線の途中にのみ、設けられており、JTAGI/F4からの入力線及びデバッグ割り込み入力線には、セレクタは、設けられていない。すなわち、セレクタ24は、JTAGI/F4へのデータの出力だけを制御する出力制御部を構成する。

【0023】

セレクタ24は、通常、アドレスデコーダ23からの出力データを遮断し、所定のデータとして無効データを選択して出力する。無効データは、例えばハードウェア回路により設定されて生成される、固定データ、ここでは「0」、である。しかし、セレクタ24は、選択信号SSを受信すると、アドレスデコーダ23の出力を選択して、出力するように構成されている。すなわち、セレクタ24は、所定の認証信号である選択信号SSが出力されないときは、出力すべきデータのJTAGI/F4への出力を禁止する。そして、セレクタ24は、選択信号SSが出力されたときは、出力すべきデータをJTAGI/F4へ出力するように、出力すべきデータの出力を制御する。

【0024】

よって、パスワードPWが適切に認証されると、セレクタ24は、アドレスデコーダ23の出力を選択するので、CPU2の情報は、JTAGI/F4を介して、デバッガ13に供給可能となる。そして、選択信号SSが出力されていない場合は、セレクタ24は、出力すべきデータのJTAGI/F4への出力を禁止して、所定のデータを出力する。

【0025】

後述するように、デバッグコマンドの処理が終了して、認証解除処理が実行されると、セレクタ24は、無効データの出力を選択するように切り替わるので、CPU2とJTAGI/F4の間は、遮断状態となり、CPU2の情報のデバッガ13への供給はできなくなる。

【0026】

図2は、認証ユニット26の構成を示すブロック図である。

認証ユニット26は、パスワード入力用レジスタ31、認証演算器32、期待値レジスタ33及び比較器34を含んで構成されている。

【0027】

パスワード入力用レジスタ31には、後述するように、デバッグ割り込みハンドラの実行において、実行ユニット21からパスワードPWが入力されて保持される。パスワード入力用レジスタ31は、CPU2の実行ユニット21がアクセスできるアドレス空間上に配置されている。期待値レジスタ33には、所定の期待値EVがストアされている。

認証演算器32には、パスワード入力用レジスタ31のパスワードPWと、認証キー部27からの認証キーPKの2つのデータが入力される。認証演算器32は、所定の認証演算を行う。その所定の認証演算は、ハードウェア回路により行うようにしてもよいし、実行ユニット21が実行するプログラムであってもよい。所定の認証演算の演算結果ORが、比較器34の2つの入力の一方に入力され、期待値レジスタ33の期待値EVが、比較器34の2つの入力の他方に入力される。

比較器34は、演算結果ORと期待値EVの2つデータと比較し、一致すると、認証信号としての選択信号SSを、セレクタ24へ供給する。

【0028】

(動作)

次に、上述したデバッグシステムの処理を説明する。

図3は、デバッガ13の起動時のPC11の処理の流れを示すフローチャートである。

【0029】

PC11において、ユーザがデバッガ13の起動を指示すると、PC11は、デバッガ13を起動する(S1)。

そして、PC11は、GUIを介してユーザにパスワードPWの入力を促し、パスワード入力処理を実行する(S2)。パスワードPWは、PC11中のRAMあるいはレジスタ等の一時記憶の記憶領域に保持される。このデータは、デバッガ13の処理が終了すると、消去される。パスワードPWの入力処理は、例えばユーザのログイン時の処理であってもよい。

【0030】

パスワードPWが入力されると、PC11は、パスワードPWを、JTAGI/F4のデバッグ用ワーク部43内の所定の記憶領域に書き込む。

その後、PC11は、デバッガ13によるデバッグ処理を実行する(S4)。デバッグ処理においては、ユーザは、SoC1に対して、所定のプログラムの実行、実行途中でのブレイク、ステップ実行、等のデバッグコマンド(以下、単にコマンドともいう)を指示することができる。

【0031】

例えば、デバッガの処理は、SoC1内でデバッグ対象のプログラムの実行中に行われ、そのプログラムの検査者であるユーザは、そのプログラムの実行中に、PC11に所望のコマンドを入力する。入力されたコマンドは、JTAG-ICE12を介して、JTAGI/F4のレジスタ41に入力される。

その入力されたコマンドに対応するコードがJTAGI/F4のレジスタ41に入力されると、JTAGI/F4は、デバッグ割り込み信号IRを実行ユニット21に供給する。

【0032】

実行ユニット21は、JTAGI/F4からデバッグ割り込み信号IRを受信すると、実行中の処理を中断し、命令フェッチユニット35を介して、JTAGI/F4のデバッグ用コード部42からデバッグ割り込みハンドラ(プログラム)を読み出して実行する。

【0033】

図4は、そのようなコマンドが入力されたときのデバッグ割り込みハンドラの処理の流れの例を示すフローチャートである。デバッグ割り込みハンドラは、デバッガ13により、デバッグ用コード部42に転送されて格納される。

【0034】

デバッグ割り込みハンドラのプログラムは、デバッグ割り込み信号IRの元となった、入力されたコマンドに対応する命令列を含むコマンド実行部(S14〜S16)と、そのコマンド実行の前に認証ユニット26に所定の認証処理を実行させるための命令列を含む認証実行指示部(S11〜S13)を含む。実行ユニット21は、認証実行指示部の処理を行って、その後にコマンド実行部の処理を実行する。すなわち、実行ユニット21は、デバッグ割り込み信号を受信すると、デバッグ用コード部42からデバッグ割り込み処理プログラムを読み出して、認証ユニット26に対して所定の認証処理の実行をさせた後に、コマンド実行部の処理を実行する。

【0035】

まず、実行ユニット21は、その認証実行指示部の処理として、上記のS3でデバッグ用ワーク部43に書き込まれたパスワードPWを、そのデバッグ用ワーク部43から読み出す(S11)。

そして、実行ユニット21は、読み出したパスワードPWを、認証ユニット26のパスワード入力レジスタ31に設定し(S12)、所定の時間Tpだけ待つ(S13)。

【0036】

CPU2は、デバッグ割り込み信号IRを受信すると、認証実行指示部の処理により、認証ユニット26による所定の認証処理を実行する。そして、ユーザが入力したパスワードPWが認証ユニット26に入力されると、認証ユニット26の認証演算器32は、パスワードPWと所定キーPKとを用いて所定の認証演算を実行する。演算結果ORと期待値EVが一致すると、比較器34は、選択信号SSをセレクタ24に供給する。所定の時間Tpは、この認証演算に係る時間を考慮して設定される。

【0037】

以上の認証実行指示部の処理が終了すると、実行ユニット21は、コマンド実行部の処理を実行する。すなわち、ユーザの入力したコマンドに対応する命令列の読み出しが行われ(S14)、実行ユニット21は、その読み出した命令列を実行する(S15)。

【0038】

例えば、入力されたコマンドが、SoC1内のあるレジスタからデータを読み出して、JTAGI/F4の所定のレジスタに格納するというコマンドである場合、実行ユニット21は、そのコマンドに対応する命令列を実行して、読み出したデータを、JTAGI/F4の所定のレジスタへ出力する。

【0039】

CPU2からJTAGI/F4へのデータの出力は、セレクタ24を介して行われる。よって、選択信号SSがセレクタ24に供給されていれば、セレクタ24は、アドレスデコーダ23の出力を選択して出力する。よって、CPU2のデータがJTAGI/F4に出力される。

【0040】

しかし、認証ユニット26により認証されなかったときは、選択信号SSは出力されないので、セレクタ24は、無効データを選択してJTAGI/F4に出力する。

図5は、認証がされなかった場合に、得られるデータの例を説明するための図である。ここでは、無効データは「0」である。図5は、メモリダンプの出力あるいは表示の例D1、命令を逆アセンブルしたときの出力あるいは表示の例D2、汎用レジスタの出力あるいは表示の例D3を含んでいる。

【0041】

ユーザが正しいパスワードPWを入力しないで、デバッグ命令を入力すると、例えば、「0x800000」のアドレスからメモリダンプをすると、D1に示すように、データは、全て「0」となり、正しい値は表示されない。セレクタ24が、無効データ「0」を選択して出力するからである。同様に、例えば、「0x200000」のアドレスから逆アセンブルしても命令は、D2に示すように、「0」であるため、「NOP」が出力される。さらに、同様に、汎用レジスタの内容表示も、D3に示すように、全て「0」となる。

【0042】

図4に戻り、命令列の実行が終了すると、実行ユニット21は、認証解除の処理を実行する(S16)。認証解除処理は、デバッグ割り込みの終了処理、すなわち認証ユニット26に書き込まれたパスワードPWの消去処理、及び割り込みハンドラの終了命令の実行処理を含む。すなわち、デバッグ割り込みハンドラは、所定の認証処理による認証の解除を行う認証解除処理を含み、CPU2は、コマンド実行部の処理の実行後、認証ユニット26に対して、所定の認証処理による認証解除を行う認証解除処理を実行することによって、認証ユニット26が選択信号SSを出力しないようにする。認証解除処理が終了した後、デバッグ割り込みの発生により中断していたプログラムの実行が再開される。

【0043】

上述したように、デバッグ割り込みハンドラは、上述した認証処理のための命令列を含む認証実行指示部と、コマンドに対応する命令列を含むコマンド実行部を含み、デバッグ割り込みが発生すると、まず認証実行指示処理が実行され、適切に認証されると、CPU2からJTAGI/F4へのデータ出力が可能なようにセレクタが制御される。適切に認証されなければ、CPU2からJTAGI/F4へのデータ出力ができないようにセレクタが制御される。その後、ユーザからのコマンドに対応する命令列が実行されるので、正しく認証されなければ、コマンドの実行結果として、CPU2内のデータがJTAGI/F4へ出力されない。正しく認証されなければ、無効データがJTAGI/F4に出力される。

さらに、デバッグコマンドが実行されるときだけ、CPU2からJTAGI/F4へのデータ出力ができるようにセレクタが制御されるので、秘密データの秘匿性は高い。

【0044】

従って、本実施形態によれば、正しいパスワードPWを入力しないと、デバッガ13は、デバッグコマンドの実行結果を得られない。

また、本実施形態では、CPU2からの出力データの遮断がされていても、デバッガ13からのユーザのコマンドに応じた、ブレイク、ステップ実行等のデバッグ命令は実行されるので、図5のような表示が行われる。従って、鍵データ、プログラムなどの秘密データの秘匿性は保たれる。

【0045】

以上のように、上述した実施形態の半導体装置によれば、半導体装置が秘密データを有する場合あるいは秘匿性のあるプログラムを実行する場合に、データの入出力を遮断するための所定の信号を入力するためのピンを半導体装置に設けることなく、あるいは別のプロセッサを半導体装置に内蔵することもなく、SoC等の半導体装置の外部との接続を遮断して、マイクロプロセッサからの秘密情報の漏洩を防止することができる。

【0046】

例えば、悪意のある者によるプロセッサの内部解析に対しても、JTAG IF とマイクロプロセッサが遮断状態のときにマイクロプロセッサからは無効データが出力されるため、プロセッサの動作状況の解析作業は、困難なものとなる。

【0047】

(第2の実施形態)

第1の実施形態では、認証が正しくされないと、所定のデータとして、固定データがJTAGI/F4に出力されているが、第2の実施形態は、認証が正しくされないときは、無効データ生成ユニットの生成した固定でないデータを、所定のデータとして、JTAGI/F4へ出力するようにした点で、第1の実施形態と異なる。その生成データは、出力すべきデータは異なるデータである。

【0048】

以下、第2の実施形態の説明において、第1の実施形態と同じ構成要素については、同じ符号を用いて説明し、説明は省略し、主に異なる点を説明する。

図6は、本実施形態に係るSoCを含むデバッグシステムの構成を説明するためのブロック図である。

図6に示すように、バスブリッジ28は、無効データ生成ユニット51を含む。無効データ生成ユニット51には、アドレスデコーダ23の出力DOが入力される。出力制御部としてのセレクタ24は、アドレスデコーダ23と無効データ生成ユニット51の2つの出力のうち、一方を、選択信号SSの有無に応じて選択して出力する。

【0049】

図7は、無効データ生成ユニット51の構成を示すブロック図である。無効データ生成ユニット51は、関数部52と、乱数発生器53を含む。乱数発生器53は、乱数RNを生成して出力する回路である。関数部52は、アドレスデコーダ23の出力DOと、乱数発生器53の出力する乱数RNの2つのデータを入力して、その2つのデータを用いて所定の関数演算を行ってその演算結果を、無効データDXとして出力する回路である。

【0050】

セレクタ24は、選択信号SSの有無に応じて、無効データ生成ユニット51の生成データである無効データDXとアドレスデコーダ23の出力データDOのいずれか一方を選択する。

本実施形態においても、認証が正しくされないと、無効データ生成ユニット51により生成された無効データDXがJTAGI/F4に出力される。

【0051】

関数部52の処理内容は、種々取り得る。例えば、関数部52は、乱数RNに基づいて、出力されるべきデータDOの途中において、偽データを挿入あるいは加算して出力するような関数処理、あるいは、乱数RNに基づいて、出力されるべきデータDOの途中にランダムな長さの偽データを含ませる関数処理、あるいは、ランダムに乱数RNに基づいて、出力されるべきデータDO中のランダムな桁を偽データで置き換える(例えば、1ビットだけ「1」と「0」を変更する)関数処理、等である。

【0052】

また、乱数RNの代わりにカウンタ値を用いて、そのカウント値に応じて、所定のオフセット値を加算した値を出力する、前の値と同じ値を出力する、等の関数でもよい。さらに、関数部52は、前と同じ値のときは、所定のオフセット値を加算した値を出力する関数処理でもよい。

さらに、関数部52はこれらの方法を組み合わせた関数処理、あるいは、時間データに応じてこれらの方法を切り換える関数処理でもよい。

【0053】

図8は、本実施形態において、認証がされなかった場合に、得られるデータの例を説明するための図である。図8は、メモリダンプの出力あるいは表示の例DD1、命令を逆アセンブルしたときの出力あるいは表示の例DD2、汎用レジスタの出力あるいは表示の例DD3を含んでいる。

【0054】

ユーザは、正しいパスワードPWを入力しないで、デバッグ命令を入力すると、例えば、「0x800000」のアドレスからメモリダンプをすると、DD1に示すように、データは、ランダムなデータとなり、正しい値は表示されない。同様に、例えば、「0x200000」のアドレスから逆アセンブルしても命令は、DD2に示すように、ランダムなデータが出力される。さらに、同様に、汎用レジスタの内容表示も、DD3に示すように、全てランダムなデータとなる。

【0055】

図5の場合と比較すると、図5の場合は、全て同じ値「0」であるので、ユーザは、正しいデータが出力されていない、あるいは出力が遮断されていると判るが、図8の場合は、無効データ生成ユニット28において生成されたランダムなデータが表示されているので、ユーザは、偽データが出力されていることさえ、直ぐには判別できない。

【0056】

例えば悪意のあるユーザにより、秘密データの取得のための解析がされる場合に、図8の表示では、正しいデータと偽データとの区別が付かないので、そのユーザは、CPU2の出力データが遮断されていることを、判定することができない。

【0057】

従って、本実施形態の半導体装置は、第1の実施形態と同様の効果を有すると共に、適切に認証がされないときには、無効データ生成部の生成したデータを出力するようにしたので、正しい値と偽データとの区別が難しいという効果を有する。

【0058】

以上のように、上述した各実施形態の半導体装置によれば、半導体装置が、秘密データあるいは秘匿性のあるプログラムを実行する場合に、データの入出力を遮断するための所定の信号を入力するためのピンを半導体装置に設けることなく、あるいは別のプロセッサを半導体装置に内蔵することもなく、SoC等の半導体装置の外部との接続を遮断して、プロセッサからの秘密情報の漏洩を防止することができる。

【0059】

なお、以上の説明は、SoC上に1つのCPUが搭載されている例で説明したが、複数のマイクロプロセッサが搭載されているSoCにおいても、各CPUからの出力データが出力される1又は2以上の出力線上に、上述したようなセレクタを配置することによって、上述した実施形態の構成は適用可能であり、プロセッサからの秘密情報の漏洩を防止することができる。

【0060】

本発明は、上述した実施の形態に限定されるものではなく、本発明の要旨を変えない範囲において、種々の変更、改変等が可能である。

【符号の説明】

【0061】

1 SoC、2 CPU、3 メインメモリ、4 JTAGI/F、5 バス、11 PC、12 JTAG-ICE、13 デバッガ、21 実行ユニット、22 レジスタ群、23 アドレスデコーダ、24 セレクタ、25 ロードストアユニット、26 認証ユニット、27 認証キー部、28 バスブリッジ、31 パスワード入力用レジスタ、32 認証演算器、33 期待値レジスタ、34 比較器、41 レジスタ、42 デバッグ用コード部、43 デバッグ用ワーク部、51 無効データ生成ユニット、52 関数部、53 乱数発生器

【技術分野】

【0001】

本発明の実施形態は、プロセッサ及び半導体装置に関する。

【背景技術】

【0002】

従来より、パーソナルコンピュータ(以下、PCという)やエンジニアリングワークステーション(以下、EWSという)上で動作するデバッグプログラム、すなわちデバッガ、を利用して、マイクロプロセッサ等の動作を制御し、そのマイクロプロセッサの動作状態の監視、プログラムあるいはメモリの内容の参照及び修正、等が行われている。

【0003】

例えば、デバッグプログラムが動作するPCやEWSを、JTAG(Joint Test Action Group) ICE(インサーキット・エミュレータ)を介して、マイクロプロセッサを内蔵するSoC(System On Chip)に接続する。そして、ソフトウェアの開発や不具合解析を行なうオペレータが、PCやEWSのデバッグプログラム上でSoC内のマイクロプロセッサに対する操作を行なうと、その内容は、JTAG-ICEを介してSoC 内の JTAGインターフェース(I/F)に伝達される。JTAG I/Fは、オペレータの操作を、マイクロプロセッサに対してのデバッグのための割り込み要求(以下、デバッグ割り込み要求という)と、オペレータがデバッグのために意図するマイクロプロセッサの動作を実現する割り込みハンドラ(以下、デバッグ割り込みハンドラという)の提供とデータの入出力という動作に変換する。このようなSoCに内蔵されている、内部回路通信用インターフェースとしてのJTAGI/Fを利用すると、マイクロプロセッサの動作状況やメモリの内容等を容易に把握することが可能となる。よって、このような手法は、SoC及びプログラムの開発、不具合解析等にきわめて有用である。

【0004】

一方で、このような手法を用いると、SoC等の半導体装置の開発終了後、半導体装置が市場に出回った後でも、マイクロプロセッサ内の秘匿性の高いプログラム、秘匿性の高いデータ等の秘密情報の読み出しが可能となってしまうという虞がある。

そこで、半導体装置の開発の終了後、秘匿性の高い処理が半導体装置のマイクロプロセッサのプログラムで実行される場合、JTAGI/Fを通しての秘密情報の漏洩を防ぐために、プログラムや処理データを保護するための機構が半導体装置内に必要であった。例えば、外部からの所定の信号に応じてデータの入出力を遮断する回路をSoC内に設けたり、別のプロセッサをSoCに設けJTAGI/Fとの接続を制御させたり、JTAG I/F とプロセッサの接続を制御するための装置をJTAG I/Fに接続する等の方法が、秘密情報の保護のために、提案されている。

【0005】

しかし、外部からの所定の信号の入出力のためのピンを半導体チップに設けたり、別のマイクロプロセッサをJTAGI/Fとの接続制御のためだけに設けることは、半導体装置のコストの増大、チップサイズの大型化に繋がるという問題がある。また、JTAG I/Fとプロセッサの接続制御装置の操作をJTAG I/Fの操作で直接行なうことは、セキュリティ上の問題や、悪意のある者による解析の対象になりやすいという問題がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−165534号公報

【特許文献2】特開2007−94632号公報

【特許文献3】特開2002−358137号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

そこで、実施形態は、データの入出力を遮断するための所定の信号を入力するためのピンを半導体チップに設けることなく、かつ別のプロセッサを半導体チップに内蔵することもなく、内部の秘密情報の漏洩を防止することができるプロセッサ及び半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

実施形態によれば、内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部を有するプロセッサにおいて、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部と、前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部と、を有するプロセッサが提供される。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係わる、SoCを含むデバッグシステムの構成を説明するためのブロック図である。

【図2】第1の実施形態に係わる、認証ユニット26の構成を示すブロック図である。

【図3】第1の実施形態に係わる、デバッガ13の起動時のPC11の処理の流れを示すフローチャートである。

【図4】第1の実施形態に係わる、デバッグ割り込みハンドラの処理の流れの例を示すフローチャートである。

【図5】第1の実施形態に係わる、認証がされなかった場合に、得られるデータの例を説明するための図である。

【図6】第2の実施形態に係わる、SoCを含むデバッグシステムの構成を説明するためのブロック図である。

【図7】第2の実施形態に係わる、無効データ生成ユニット51の構成を示すブロック図である。

【図8】第2の実施形態に係わる、認証がされなかった場合に、得られるデータの例を説明するための図である。

【発明を実施するための形態】

【0010】

以下、図面を参照して実施形態を説明する。

(第1の実施形態)

(構成)

まず、図1に基づき、本実施形態に係わるデバッグシステムの構成を説明する。図1は、本実施形態に係るSoCを含むデバッグシステムの構成を説明するためのブロック図である。

【0011】

半導体装置である1チップのSoC1は、マイクロプロセッサとしてのCPU2と、DRAM等のメインメモリ3と、内部回路通信用インターフェースとしてのJTAGI/F4とを含んで構成されている。CPU2とメインメモリ3は、バス5を介してデータの送受信が互いに可能に接続されている。

【0012】

SoC1は、PC(あるいはEWS)11及びJTAG-ICE12を含むデバッグ装置に、接続可能となっており、図1では、JTAG-ICE12を介してPC11に接続されている。PC11とJTAG-ICE12は、USB等のケーブルで接続されている。PC11は、デバッグプログラムであるデバッガ13を有している。PC11は、図示しないキーボード、マウスなどの入力装置とモニタを有し、ユーザからのGUIを介する指示に基づいて、SoC1をデバッグするためのデバッガ13を実行可能に構成されている。

【0013】

SoC1のCPU2は、ALU等の演算ユニットを含む実行ユニット21、複数の汎用レジスタ及び複数の制御レジスタを含むレジスタ群22、アドレスデコーダ23、命令フェッチユニット35及びロードストアユニット25を含むプロセッサである。実行ユニット21は、レジスタ群22を用いながら、命令フェッチユニット35により読み出した命令をデコードして、プログラムの実行を行う。

実行ユニット21が実行する通常のプログラム及びデータは、メインメモリ3内に存在する。よって、アドレスデコーダ23は、実行ユニット21により指定されたアドレスへのアクセスを制御し、通常のプログラムの命令列をフェッチするときは、メインメモリ3へアクセスする。しかし、実行ユニット21がデバッグ割り込みハンドラの命令列をフェッチするときは、その命令列の先頭アドレスは、JTAGI/F4内のデバッグ用コード記憶部41にあるので、アドレスデコーダ23は、JTAGI/F4へのアクセスを行うように、アクセス先の切り換えを行う。データの書き込み要求があったときも、アドレスデコーダ23は、アドレスに応じて、同様にアクセス先を切り換える。すなわち、アドレスデコーダ23は、JTAGI/F4からのデータの入力及びJTAGI/F4へのデータの出力を制御する入出力制御部を構成する。

【0014】

内部回路通信用インターフェースとしてのJTAGI/F4は、シリアル通信を用いて、半導体チップ内部に設けられたテスト用の回路にアクセスし、そのチップの端子の状態を操作したり、チップの内部回路との通信をするためのインターフェースである。

【0015】

JTAGI/F4は、レジスタ41を有する。レジスタ41には、オペレータが入力した各種コマンドに対応するコードが入力される。さらに、JTAGI/F4は、デバッグ用コード部42と、デバッグ用ワーク部43とを含む。デバッグ用コード部42には、デバッガ13からのデバッグ割り込みハンドラの命令列、すなわちデバッグ割り込み処理プログラム、がストアされる記憶領域である。デバッグ用コード部42は、デバッグ割り込み信号に対応するデバッグ割り込み処理プログラムを記憶するデバッグ割り込み処理プログラム記憶部である。デバッグ用ワーク部43は、デバッグ用ワーク領域として利用される記憶領域である。

【0016】

JTAGI/F4は、レジスタ41に所定のコードが設定されると、デバッグ割り込み信号IRをCPU2へ出力する。

実行ユニット21は、例えばパルス信号であるデバッグ割り込み信号IRを受信すると、命令フェッチユニット35を介して、割り込みハンドラの命令列のエントリーアドレスである所定のアドレスからデータを読み出して実行する。そのエントリーアドレスのデータは、JTAGI/F4のデバッグ用コード部42に記憶されているので、アドレスデコーダ23は、そのエントリーアドレスへのアクセスがあると、JTAGI/F4にアクセスしてデバッグ割り込みハンドラの命令列を読み出す。

【0017】

実行ユニット21は、JTAGI/F4のデバッグ用コード部42から読み出されたデバッグ割り込みハンドラの命令列を実行し、その実行結果を、JTAGI/F4の所定のレジスタ(図示せず)へ出力する。その実行結果の情報は、JTAG-ICE12を介して、デバッガ13により読み出し可能であり、デバッガ13は、その実行結果の情報を、GUIを介して、モニタに表示して、ユーザに知らしめることが可能である。

【0018】

ロードストアユニット25は、実行ユニット21からメインメモリ3あるいはJTAGI/F4へのデータのストア、及びメインメモリ3あるいはJTAGI/F4から実行ユニット21へのデータのロードを行うハードウェア回路である。

【0019】

CPU2は、認証ユニット26、認証キー部27及びバスブリッジ28を、さらに含む。後述するように、デバッグ割り込みハンドラの実行により、パスワードPWが、認証ユニット26に供給される。認証ユニット26は、その供給されたパスワードと、認証キー部27にストアされている所定のキーPKとに基づいて、所定の認証処理を行うハードウェア回路である。供給されたパスワードPWと、認証キー部27にストアされている所定のキーPKとを用いた所定の認証演算により、所定の結果が得られると、認証ユニット26は、認証信号として選択信号SSを出力する。よって、認証処理部である認証ユニット26は、入力されたパスワードPWと所定のキーPKとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する。

【0020】

認証キー部27には、所定のキーPKのデータが設定されており、認証ユニット26により読み出し可能なハードウェア回路である。

【0021】

バスブリッジ28は、上記のアドレスデコーダ23と、セレクタ24を含んで構成されている。バスブリッジ28は、CPU2と、SoC1内のバス5とJTAGI/F4との間のインターフェースであり、セレクタ24は、JTAGI/F4との間に設けられている。

【0022】

アドレスデコーダ23は、JTAGI/F4との間でのデータの入出力を制御する入出力制御部であり、ロードストアユニット25によってロード及びストアするデータのアドレスに応じて、メインメモリ3とJTAGI/F4へのアクセスを切り換える。

セレクタ24は、選択信号SSの有無に応じて、出力すべきデータのJTAGI/F4への出力を制御する出力制御部である。具体的には、セレクタ24は、出力すべきデータと所定のデータのいずれかを選択する。セレクタ24は、アドレスデコーダ23からJTAGI/F4への出力線の途中にのみ、設けられており、JTAGI/F4からの入力線及びデバッグ割り込み入力線には、セレクタは、設けられていない。すなわち、セレクタ24は、JTAGI/F4へのデータの出力だけを制御する出力制御部を構成する。

【0023】

セレクタ24は、通常、アドレスデコーダ23からの出力データを遮断し、所定のデータとして無効データを選択して出力する。無効データは、例えばハードウェア回路により設定されて生成される、固定データ、ここでは「0」、である。しかし、セレクタ24は、選択信号SSを受信すると、アドレスデコーダ23の出力を選択して、出力するように構成されている。すなわち、セレクタ24は、所定の認証信号である選択信号SSが出力されないときは、出力すべきデータのJTAGI/F4への出力を禁止する。そして、セレクタ24は、選択信号SSが出力されたときは、出力すべきデータをJTAGI/F4へ出力するように、出力すべきデータの出力を制御する。

【0024】

よって、パスワードPWが適切に認証されると、セレクタ24は、アドレスデコーダ23の出力を選択するので、CPU2の情報は、JTAGI/F4を介して、デバッガ13に供給可能となる。そして、選択信号SSが出力されていない場合は、セレクタ24は、出力すべきデータのJTAGI/F4への出力を禁止して、所定のデータを出力する。

【0025】

後述するように、デバッグコマンドの処理が終了して、認証解除処理が実行されると、セレクタ24は、無効データの出力を選択するように切り替わるので、CPU2とJTAGI/F4の間は、遮断状態となり、CPU2の情報のデバッガ13への供給はできなくなる。

【0026】

図2は、認証ユニット26の構成を示すブロック図である。

認証ユニット26は、パスワード入力用レジスタ31、認証演算器32、期待値レジスタ33及び比較器34を含んで構成されている。

【0027】

パスワード入力用レジスタ31には、後述するように、デバッグ割り込みハンドラの実行において、実行ユニット21からパスワードPWが入力されて保持される。パスワード入力用レジスタ31は、CPU2の実行ユニット21がアクセスできるアドレス空間上に配置されている。期待値レジスタ33には、所定の期待値EVがストアされている。

認証演算器32には、パスワード入力用レジスタ31のパスワードPWと、認証キー部27からの認証キーPKの2つのデータが入力される。認証演算器32は、所定の認証演算を行う。その所定の認証演算は、ハードウェア回路により行うようにしてもよいし、実行ユニット21が実行するプログラムであってもよい。所定の認証演算の演算結果ORが、比較器34の2つの入力の一方に入力され、期待値レジスタ33の期待値EVが、比較器34の2つの入力の他方に入力される。

比較器34は、演算結果ORと期待値EVの2つデータと比較し、一致すると、認証信号としての選択信号SSを、セレクタ24へ供給する。

【0028】

(動作)

次に、上述したデバッグシステムの処理を説明する。

図3は、デバッガ13の起動時のPC11の処理の流れを示すフローチャートである。

【0029】

PC11において、ユーザがデバッガ13の起動を指示すると、PC11は、デバッガ13を起動する(S1)。

そして、PC11は、GUIを介してユーザにパスワードPWの入力を促し、パスワード入力処理を実行する(S2)。パスワードPWは、PC11中のRAMあるいはレジスタ等の一時記憶の記憶領域に保持される。このデータは、デバッガ13の処理が終了すると、消去される。パスワードPWの入力処理は、例えばユーザのログイン時の処理であってもよい。

【0030】

パスワードPWが入力されると、PC11は、パスワードPWを、JTAGI/F4のデバッグ用ワーク部43内の所定の記憶領域に書き込む。

その後、PC11は、デバッガ13によるデバッグ処理を実行する(S4)。デバッグ処理においては、ユーザは、SoC1に対して、所定のプログラムの実行、実行途中でのブレイク、ステップ実行、等のデバッグコマンド(以下、単にコマンドともいう)を指示することができる。

【0031】

例えば、デバッガの処理は、SoC1内でデバッグ対象のプログラムの実行中に行われ、そのプログラムの検査者であるユーザは、そのプログラムの実行中に、PC11に所望のコマンドを入力する。入力されたコマンドは、JTAG-ICE12を介して、JTAGI/F4のレジスタ41に入力される。

その入力されたコマンドに対応するコードがJTAGI/F4のレジスタ41に入力されると、JTAGI/F4は、デバッグ割り込み信号IRを実行ユニット21に供給する。

【0032】

実行ユニット21は、JTAGI/F4からデバッグ割り込み信号IRを受信すると、実行中の処理を中断し、命令フェッチユニット35を介して、JTAGI/F4のデバッグ用コード部42からデバッグ割り込みハンドラ(プログラム)を読み出して実行する。

【0033】

図4は、そのようなコマンドが入力されたときのデバッグ割り込みハンドラの処理の流れの例を示すフローチャートである。デバッグ割り込みハンドラは、デバッガ13により、デバッグ用コード部42に転送されて格納される。

【0034】

デバッグ割り込みハンドラのプログラムは、デバッグ割り込み信号IRの元となった、入力されたコマンドに対応する命令列を含むコマンド実行部(S14〜S16)と、そのコマンド実行の前に認証ユニット26に所定の認証処理を実行させるための命令列を含む認証実行指示部(S11〜S13)を含む。実行ユニット21は、認証実行指示部の処理を行って、その後にコマンド実行部の処理を実行する。すなわち、実行ユニット21は、デバッグ割り込み信号を受信すると、デバッグ用コード部42からデバッグ割り込み処理プログラムを読み出して、認証ユニット26に対して所定の認証処理の実行をさせた後に、コマンド実行部の処理を実行する。

【0035】

まず、実行ユニット21は、その認証実行指示部の処理として、上記のS3でデバッグ用ワーク部43に書き込まれたパスワードPWを、そのデバッグ用ワーク部43から読み出す(S11)。

そして、実行ユニット21は、読み出したパスワードPWを、認証ユニット26のパスワード入力レジスタ31に設定し(S12)、所定の時間Tpだけ待つ(S13)。

【0036】

CPU2は、デバッグ割り込み信号IRを受信すると、認証実行指示部の処理により、認証ユニット26による所定の認証処理を実行する。そして、ユーザが入力したパスワードPWが認証ユニット26に入力されると、認証ユニット26の認証演算器32は、パスワードPWと所定キーPKとを用いて所定の認証演算を実行する。演算結果ORと期待値EVが一致すると、比較器34は、選択信号SSをセレクタ24に供給する。所定の時間Tpは、この認証演算に係る時間を考慮して設定される。

【0037】

以上の認証実行指示部の処理が終了すると、実行ユニット21は、コマンド実行部の処理を実行する。すなわち、ユーザの入力したコマンドに対応する命令列の読み出しが行われ(S14)、実行ユニット21は、その読み出した命令列を実行する(S15)。

【0038】

例えば、入力されたコマンドが、SoC1内のあるレジスタからデータを読み出して、JTAGI/F4の所定のレジスタに格納するというコマンドである場合、実行ユニット21は、そのコマンドに対応する命令列を実行して、読み出したデータを、JTAGI/F4の所定のレジスタへ出力する。

【0039】

CPU2からJTAGI/F4へのデータの出力は、セレクタ24を介して行われる。よって、選択信号SSがセレクタ24に供給されていれば、セレクタ24は、アドレスデコーダ23の出力を選択して出力する。よって、CPU2のデータがJTAGI/F4に出力される。

【0040】

しかし、認証ユニット26により認証されなかったときは、選択信号SSは出力されないので、セレクタ24は、無効データを選択してJTAGI/F4に出力する。

図5は、認証がされなかった場合に、得られるデータの例を説明するための図である。ここでは、無効データは「0」である。図5は、メモリダンプの出力あるいは表示の例D1、命令を逆アセンブルしたときの出力あるいは表示の例D2、汎用レジスタの出力あるいは表示の例D3を含んでいる。

【0041】

ユーザが正しいパスワードPWを入力しないで、デバッグ命令を入力すると、例えば、「0x800000」のアドレスからメモリダンプをすると、D1に示すように、データは、全て「0」となり、正しい値は表示されない。セレクタ24が、無効データ「0」を選択して出力するからである。同様に、例えば、「0x200000」のアドレスから逆アセンブルしても命令は、D2に示すように、「0」であるため、「NOP」が出力される。さらに、同様に、汎用レジスタの内容表示も、D3に示すように、全て「0」となる。

【0042】

図4に戻り、命令列の実行が終了すると、実行ユニット21は、認証解除の処理を実行する(S16)。認証解除処理は、デバッグ割り込みの終了処理、すなわち認証ユニット26に書き込まれたパスワードPWの消去処理、及び割り込みハンドラの終了命令の実行処理を含む。すなわち、デバッグ割り込みハンドラは、所定の認証処理による認証の解除を行う認証解除処理を含み、CPU2は、コマンド実行部の処理の実行後、認証ユニット26に対して、所定の認証処理による認証解除を行う認証解除処理を実行することによって、認証ユニット26が選択信号SSを出力しないようにする。認証解除処理が終了した後、デバッグ割り込みの発生により中断していたプログラムの実行が再開される。

【0043】

上述したように、デバッグ割り込みハンドラは、上述した認証処理のための命令列を含む認証実行指示部と、コマンドに対応する命令列を含むコマンド実行部を含み、デバッグ割り込みが発生すると、まず認証実行指示処理が実行され、適切に認証されると、CPU2からJTAGI/F4へのデータ出力が可能なようにセレクタが制御される。適切に認証されなければ、CPU2からJTAGI/F4へのデータ出力ができないようにセレクタが制御される。その後、ユーザからのコマンドに対応する命令列が実行されるので、正しく認証されなければ、コマンドの実行結果として、CPU2内のデータがJTAGI/F4へ出力されない。正しく認証されなければ、無効データがJTAGI/F4に出力される。

さらに、デバッグコマンドが実行されるときだけ、CPU2からJTAGI/F4へのデータ出力ができるようにセレクタが制御されるので、秘密データの秘匿性は高い。

【0044】

従って、本実施形態によれば、正しいパスワードPWを入力しないと、デバッガ13は、デバッグコマンドの実行結果を得られない。

また、本実施形態では、CPU2からの出力データの遮断がされていても、デバッガ13からのユーザのコマンドに応じた、ブレイク、ステップ実行等のデバッグ命令は実行されるので、図5のような表示が行われる。従って、鍵データ、プログラムなどの秘密データの秘匿性は保たれる。

【0045】

以上のように、上述した実施形態の半導体装置によれば、半導体装置が秘密データを有する場合あるいは秘匿性のあるプログラムを実行する場合に、データの入出力を遮断するための所定の信号を入力するためのピンを半導体装置に設けることなく、あるいは別のプロセッサを半導体装置に内蔵することもなく、SoC等の半導体装置の外部との接続を遮断して、マイクロプロセッサからの秘密情報の漏洩を防止することができる。

【0046】

例えば、悪意のある者によるプロセッサの内部解析に対しても、JTAG IF とマイクロプロセッサが遮断状態のときにマイクロプロセッサからは無効データが出力されるため、プロセッサの動作状況の解析作業は、困難なものとなる。

【0047】

(第2の実施形態)

第1の実施形態では、認証が正しくされないと、所定のデータとして、固定データがJTAGI/F4に出力されているが、第2の実施形態は、認証が正しくされないときは、無効データ生成ユニットの生成した固定でないデータを、所定のデータとして、JTAGI/F4へ出力するようにした点で、第1の実施形態と異なる。その生成データは、出力すべきデータは異なるデータである。

【0048】

以下、第2の実施形態の説明において、第1の実施形態と同じ構成要素については、同じ符号を用いて説明し、説明は省略し、主に異なる点を説明する。

図6は、本実施形態に係るSoCを含むデバッグシステムの構成を説明するためのブロック図である。

図6に示すように、バスブリッジ28は、無効データ生成ユニット51を含む。無効データ生成ユニット51には、アドレスデコーダ23の出力DOが入力される。出力制御部としてのセレクタ24は、アドレスデコーダ23と無効データ生成ユニット51の2つの出力のうち、一方を、選択信号SSの有無に応じて選択して出力する。

【0049】

図7は、無効データ生成ユニット51の構成を示すブロック図である。無効データ生成ユニット51は、関数部52と、乱数発生器53を含む。乱数発生器53は、乱数RNを生成して出力する回路である。関数部52は、アドレスデコーダ23の出力DOと、乱数発生器53の出力する乱数RNの2つのデータを入力して、その2つのデータを用いて所定の関数演算を行ってその演算結果を、無効データDXとして出力する回路である。

【0050】

セレクタ24は、選択信号SSの有無に応じて、無効データ生成ユニット51の生成データである無効データDXとアドレスデコーダ23の出力データDOのいずれか一方を選択する。

本実施形態においても、認証が正しくされないと、無効データ生成ユニット51により生成された無効データDXがJTAGI/F4に出力される。

【0051】

関数部52の処理内容は、種々取り得る。例えば、関数部52は、乱数RNに基づいて、出力されるべきデータDOの途中において、偽データを挿入あるいは加算して出力するような関数処理、あるいは、乱数RNに基づいて、出力されるべきデータDOの途中にランダムな長さの偽データを含ませる関数処理、あるいは、ランダムに乱数RNに基づいて、出力されるべきデータDO中のランダムな桁を偽データで置き換える(例えば、1ビットだけ「1」と「0」を変更する)関数処理、等である。

【0052】

また、乱数RNの代わりにカウンタ値を用いて、そのカウント値に応じて、所定のオフセット値を加算した値を出力する、前の値と同じ値を出力する、等の関数でもよい。さらに、関数部52は、前と同じ値のときは、所定のオフセット値を加算した値を出力する関数処理でもよい。

さらに、関数部52はこれらの方法を組み合わせた関数処理、あるいは、時間データに応じてこれらの方法を切り換える関数処理でもよい。

【0053】

図8は、本実施形態において、認証がされなかった場合に、得られるデータの例を説明するための図である。図8は、メモリダンプの出力あるいは表示の例DD1、命令を逆アセンブルしたときの出力あるいは表示の例DD2、汎用レジスタの出力あるいは表示の例DD3を含んでいる。

【0054】

ユーザは、正しいパスワードPWを入力しないで、デバッグ命令を入力すると、例えば、「0x800000」のアドレスからメモリダンプをすると、DD1に示すように、データは、ランダムなデータとなり、正しい値は表示されない。同様に、例えば、「0x200000」のアドレスから逆アセンブルしても命令は、DD2に示すように、ランダムなデータが出力される。さらに、同様に、汎用レジスタの内容表示も、DD3に示すように、全てランダムなデータとなる。

【0055】

図5の場合と比較すると、図5の場合は、全て同じ値「0」であるので、ユーザは、正しいデータが出力されていない、あるいは出力が遮断されていると判るが、図8の場合は、無効データ生成ユニット28において生成されたランダムなデータが表示されているので、ユーザは、偽データが出力されていることさえ、直ぐには判別できない。

【0056】

例えば悪意のあるユーザにより、秘密データの取得のための解析がされる場合に、図8の表示では、正しいデータと偽データとの区別が付かないので、そのユーザは、CPU2の出力データが遮断されていることを、判定することができない。

【0057】

従って、本実施形態の半導体装置は、第1の実施形態と同様の効果を有すると共に、適切に認証がされないときには、無効データ生成部の生成したデータを出力するようにしたので、正しい値と偽データとの区別が難しいという効果を有する。

【0058】

以上のように、上述した各実施形態の半導体装置によれば、半導体装置が、秘密データあるいは秘匿性のあるプログラムを実行する場合に、データの入出力を遮断するための所定の信号を入力するためのピンを半導体装置に設けることなく、あるいは別のプロセッサを半導体装置に内蔵することもなく、SoC等の半導体装置の外部との接続を遮断して、プロセッサからの秘密情報の漏洩を防止することができる。

【0059】

なお、以上の説明は、SoC上に1つのCPUが搭載されている例で説明したが、複数のマイクロプロセッサが搭載されているSoCにおいても、各CPUからの出力データが出力される1又は2以上の出力線上に、上述したようなセレクタを配置することによって、上述した実施形態の構成は適用可能であり、プロセッサからの秘密情報の漏洩を防止することができる。

【0060】

本発明は、上述した実施の形態に限定されるものではなく、本発明の要旨を変えない範囲において、種々の変更、改変等が可能である。

【符号の説明】

【0061】

1 SoC、2 CPU、3 メインメモリ、4 JTAGI/F、5 バス、11 PC、12 JTAG-ICE、13 デバッガ、21 実行ユニット、22 レジスタ群、23 アドレスデコーダ、24 セレクタ、25 ロードストアユニット、26 認証ユニット、27 認証キー部、28 バスブリッジ、31 パスワード入力用レジスタ、32 認証演算器、33 期待値レジスタ、34 比較器、41 レジスタ、42 デバッグ用コード部、43 デバッグ用ワーク部、51 無効データ生成ユニット、52 関数部、53 乱数発生器

【特許請求の範囲】

【請求項1】

内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部と、

入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部と、

前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部と、

を有することを特徴とするプロセッサ。

【請求項2】

前記出力制御部は、前記所定の認証信号が出力されない場合、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を禁止して、所定のデータを出力することを特徴とする請求項1に記載のプロセッサ。

【請求項3】

前記所定のデータは、固定データであることを特徴とする請求項2に記載のプロセッサ。

【請求項4】

前記所定のデータは、前記出力すべきデータとは異なるデータを生成するデータ生成部の生成データであることを特徴とする請求項2に記載のプロセッサ。

【請求項5】

プロセッサの内部回路通信用インターフェース部と、

前記内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部、及び、前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部を有するプロセッサと

を有することを特徴とする半導体装置。

【請求項1】

内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部と、

入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部と、

前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部と、

を有することを特徴とするプロセッサ。

【請求項2】

前記出力制御部は、前記所定の認証信号が出力されない場合、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を禁止して、所定のデータを出力することを特徴とする請求項1に記載のプロセッサ。

【請求項3】

前記所定のデータは、固定データであることを特徴とする請求項2に記載のプロセッサ。

【請求項4】

前記所定のデータは、前記出力すべきデータとは異なるデータを生成するデータ生成部の生成データであることを特徴とする請求項2に記載のプロセッサ。

【請求項5】

プロセッサの内部回路通信用インターフェース部と、

前記内部回路通信用インターフェース部からのデータの入力及び前記内部回路通信用インターフェース部へのデータの出力を制御する入出力制御部、入力されたパスワードと所定のキーとを用いて所定の認証処理を実行し、認証された場合に所定の認証信号を出力する認証処理部、及び、前記所定の認証信号の有無に応じて、前記出力すべきデータの前記内部回路通信用インターフェース部への出力を制御する出力制御部を有するプロセッサと

を有することを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−118884(P2012−118884A)

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願番号】特願2010−269664(P2010−269664)

【出願日】平成22年12月2日(2010.12.2)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願日】平成22年12月2日(2010.12.2)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]