プロトコルスタックのタイミングの管理

【課題】トンネリングインターコネクトを介してトンネリングを実行する場合に、トンネリングされるプロトコルの明示的および暗示的なタイマを管理するメカニズムを提供する。

【解決手段】方法は、トンネリングインターコネクトに結合されているプロトコルスタックにおいて通信を受信する段階と、トンネリングインターコネクトに対応付けられている遅延に対応するべく、通信種類は、変更後タイミングに影響されるか否かを決定する段階と、少なくとも1つのスタックロジックのタイミングを調整して、遅延に対応する段階と、調整されたタイミングを用いて通信を処理する段階とを備える。

【解決手段】方法は、トンネリングインターコネクトに結合されているプロトコルスタックにおいて通信を受信する段階と、トンネリングインターコネクトに対応付けられている遅延に対応するべく、通信種類は、変更後タイミングに影響されるか否かを決定する段階と、少なくとも1つのスタックロジックのタイミングを調整して、遅延に対応する段階と、調整されたタイミングを用いて通信を処理する段階とを備える。

【発明の詳細な説明】

【背景技術】

【0001】

コンピュータプラットフォームは通常、さまざまなインターコネクトを用いて互いに結合された半導体素子を多数備えている。このようなインターコネクトまたはリンクは、プロトコルが異なっていることが多く、リンク上で実行される通信は、リンクが異なると、実行速度が異なり、準拠するプロトコルも異なる。一部のシステムでは、入出力(I/O)プロトコルの通信は、別のインターコネクトにおいてトンネリングされ得る。トンネリングは一般的に、第1のプロトコルに準拠した通信を受け取り、第2のプロトコルにしたがって動作するインターコネクトを介して当該通信を提供することを含む。例えば、第1のプロトコルのパケットに第2のプロトコルのヘッダを適用して、当該パケットをインターコネクトを介して送信することによって、第1のプロトコルのパケットがトンネリングされる。多くの場合、このようなプロトコルトンネリングは非常に上位のレベルで実行され、これら2つのプロトコルが有するソフトウェア抽象化が同じである一方、プロトコル間で共有されているハードウェアはない。このように、ソフトウェア互換性、性能、製品化までの時間において、上述したようなトンネリングによる利点は非常に小さい。

【図面の簡単な説明】

【0002】

【図1】本発明の一実施形態に係る、共有物理層を介したリンクへのプロトコルスタックの接続を示すブロック図である。

【0003】

【図2】本発明の別の実施形態に係る、共有物理層に結合されている複数の通信スタックを備えるシステムを示すブロック図である。

【0004】

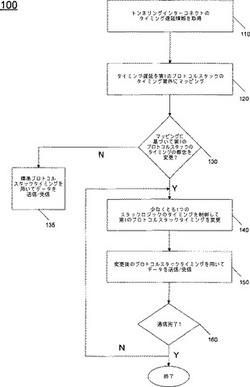

【図3】本発明の一実施形態に係る方法を説明するためのフローチャートである。

【0005】

【図4】本発明の別の実施形態に係る、プロトコルスタックのインターフェースを動作させる方法を説明するためのフローチャートである。

【0006】

【図5】本発明の一実施形態に係るシステムを示すブロック図である。

【発明を実施するための形態】

【0007】

さまざまな実施形態によると、1以上の既存のIOプロトコルが、比較的低位のレベルで、別のインターコネクトにおいてトンネリングされ得る。本明細書では、「別のインターコネクト」を「トンネリングインターコネクト」と呼ぶことにする。一実施形態によると、このようなインターコネクトの一例として統合型(converged)IO(CIO)が挙げられる。CIOは、PCI Express(登録商標)仕様書の基本仕様書バージョン2.0(2007年1月17日発行)に従った(以降では、PCIe(登録商標)仕様書と呼ぶ)、PCIe(Peripheral Component Interconnect Express)プロトコルの通信、または、同様のプロトコルの通信をトンネリングするべく用いることができる。CIOの場合、PCIeハードウェアスタックの多くは直接実装されるので、ソフトウェア互換性、性能、および製品化までの時間において、利点が得られる。すなわち、低位のレベルのトンネリングにおいて、トンネリングされるプロトコルスタックは大半が実装されている。これとは対照的に、高位のレベルのトンネリングの場合は、ソフトウェアアーキテクチャは保存されるが、トンネリングされるプロトコルからのパケット、符号化、または有線用プロトコルメカニズムを必ずしも用いるわけではない。このように低位のトンネリングによって、PCIeプロトコルスタックのパケットを、例えば、トンネリングパケットにCIOヘッダを適合させることによって、CIOインターコネクトを介してトンネリングすることができる。このように送信されたトンネリングパケットを受信機が受信すると、受信機のCIOプロトコルスタックはヘッダを復号化して、受信機の対応PCIeプロトコルスタックにPCIeパケットを渡すことができる。

【0008】

しかし、統合型インターコネクトに対するこのようなアプローチによって、抽象化という、より高位で行われるプロトコルのトンネリングとは対照的に、低位トンネリングに起因する問題が生じる。つまり、プロトコルのタイミングについて制約が潜在的に課されていることが多い。このような制約は、インターコネクトプロトコルのトンネリングされていない元々のインスタンス化では満足させられていたことが自明であるが、インターコネクトプロトコルをトンネリングする場合には、トンネリングに用いられるインターコネクトによる遅延が発生するために、管理するのがより困難になり得る。このような遅延は、トンネリングインターコネクト自身によって生じる場合もあり、または、その他のトンネリングされたプロトコルによるトラフィックによって生じる場合もある。

【0009】

本発明の実施形態は、トンネリングインターコネクトを介してトンネリングを実行する場合に、トンネリングされるプロトコルの明示的および暗示的なタイマを管理するメカニズムを提供する。本明細書で説明する実施形態ではCIOを介してトンネリングされるPCIeプロトコルを一例として用いるが、本発明の範囲はこれに限定されるものではなく、同様の原理は、その他のトンネリングインターコネクト、および、有線インターコネクトおよび無線インターコネクトを始めとする、トンネリングに用いられるその他のインターコネクトにも応用され得ると理解されたい。

【0010】

インターコネクトに関する、明示的および暗示的な、タイミング要件は、大きく分けて2つのカテゴリーに分類され得る。本明細書では、リンクタイミング要件および掛け時計タイミング要件と呼ぶ。リンクタイミング要件は、リンクプロトコル等の低位レベルに対応付けられており、リンク動作を円滑化して、検証に関する問題を最低限に抑えることを目的として通常設けられている。掛け時計タイミング要件は、高位レベルにおいて観察可能なイベント、例えば、オペレーティングシステム(OS)およびアプリケーションソフトウェアに対応付けられている。リンクタイミング要件は、プロトコルトンネリングによって生じる遅延に直接影響を受ける可能性があり、本発明の実施形態によって問題解決を図る要件である。通常、リンクタイミング要件は、約10マイクロ秒(μs)未満のオーダーであり得るが、掛け時計タイミング要件は、約10マイクロ秒(μs)よりも大きい。掛け時計タイミング要件は、プロトコルのトンネリングによって生じる比較的短時間(例えば、マイクロ秒)の遅延に影響されない程度に十分長い時間値(例えば、ミリ秒(ms))に対応付けられていることが多いので、プロトコルトンネリングには基本的に影響されない。また、このような要件は、特定のインターコネクトプロトコルを伝送するべく用いられるハードウェアメカニズムに関わらず(本来のもの、または、トンネリング用)等しく望ましい、アプリケーションソフトウェアにおいてユーザに見える動作停止(stall)の発生を防ぐというような、特性に対応付けられている。

【0011】

以下に記載する表1は、PCIeに対応付けられている多数のタイミング要件を一覧にしたものであり、各要件と本開示との関係を示す。「説明」部分の記載は、PCI Express(登録商標)仕様書から引用していることに留意されたい。

【表1】

表1は、一部を例示することを目的とするものであって、PCIeにおけるタイミング関連の要件を全て完全に網羅したものではないことに留意されたい。

【0012】

リンクタイミング要件は、PCIeスタック自身によって「測定」されるので、PCIeスタックの時間に対する概念が変わると、このようなタイミング要件を感知する方法も変化し得る。このような構成を実現するべく、時間変更を実現するためのメカニズムが、スタックタイミングをいつ、そして、どのように変更するかを決定するためのハードウェア、ソフトウェアまたはファームウェアと共に、提供されるとしてよい。

【0013】

PCIeスタックの時間の概念を変更するメカニズムは、複数の方法で実現することができる。例えば、PCIeスタックロジックにおけるさまざまな要素に対するクロックをゲーティングまたはオフに制御して、対象となるロジックの時間を止めることによって、実現することができる。尚、この方法によれば、利用されていないPCIeスタックロジックの電力消費を低減するという効果もさらに得られる。ほかの実施形態によると、時間をカウントすべき場合を指し示す明示的な制御信号を、PCIeスタックロジックに追加することができる。スタック全体を1つの単位として制御することは一般的に十分ではなく、スタックのサブ構成要素は、プロトコルメカニズムが異なれば、異なるロジックブロックに対する影響も異なるので、半独立制御が実行され得る。同様に、リンクタイミング要件を遵守するべく、全ての通信についてタイミング変更が必要となるわけではない。一実施形態によると、制御ロジックを用いてPCIeスタックの時間の概念をいつおよびどのように調整するかを決定するとしてよく、当該ロジックはPCIeスタックの一部であってよい。

【0014】

図1は、PCIeスタック(およびその他のトンネリングされたプロトコル)が共有トンネリングリンクにインターフェースされる様子を示すブロック図である。一実施形態によると、共有トンネリングリンクは、CIOリンクであってよい。図1に示すように、システム10は、第1のスタック20aと、第2のスタック20b(プロトコルスタック20と総称する)とを備える。一実施形態によると、第1のプロトコルスタック20aは、PCIeスタックであってよく、第2のプロトコルスタック20bは、ユニバーサルシリアルバス(USB)、ディスプレイインターコネクト、またはその他の同様のプロトコルスタックであってよい。図示の便宜上、PCIeプロトコルスタックの詳細のみを示す。具体的には、プロトコルスタック20aは、トランザクション層22と、データリンク層24と、インターフェースまたはガスケット層26とを有する。インターフェースまたはガスケット層26は、PCIeプロトコルとトンネリングプロトコルとの間のインターフェースとして機能する。このようなインターフェースロジックの動作の詳細は後述する。

【0015】

図1に示すように、統合型IO層は、第1および第2のプロトコルスタック20と、リンク70との間に結合されるとしてよい。リンク70は、一実施形態によると、光リンク、電気リンク、またはその他の同様のリンクであってよい。図1に示すように、CIOプロトコルスタックは、CIOプロトコルトランスポート層30と、物理層の論理ブロック40と、物理層の電気ブロック50と、物理層の光ブロック60とを有するとしてよい。このように、ブロック40から60は、物理層と通信している複数のプロトコルによって共有されて、これらの複数のプロトコルの情報をリンク70によってトンネリングする共通物理層として機能する。

【0016】

図2は、共有物理層に結合されている複数の通信スタックを備えるシステムを示す図である。具体的には、図2では、PCIe送信(Tx)および受信(Rx)スタック20aに加えて、複数のその他の送信および受信スタック20b−20dが設けられるとしてよい。同図に示すように、一対のマルチプレクサ35aおよび35b(マルチプレクサ35と総称する)が、これらのスタックと共有物理層40−60との間に、結合されているとしてよい。マルチプレクサ35は、プロトコルトランスポート層制御30の制御下で、動作させられるとしてよい。図2に示すように、CIOプロトコルトランスポート(PT)層30は、PCIeおよびその他のプロトコルをトンネリングするための、マルチプレクシングメカニズム(マルチプレクサ35aおよび35bに基づく)および制御メカニズムを実装する。PT層制御30は、送信機の抽象化と、送信機とは別個である受信機の操作を実装する。このような構造はこの説明の残りの部分でも用いるが、本発明の実施形態は、例えば、同時に送信機および受信機を抽象化することによって、または、単一の双方向接続を用いることによって、送信機および受信機を別々に制御するその他の種類のインターコネクトに応用され得る。

【0017】

インターコネクトのタイミング制御を実装する方法は、実施形態によって異なるとしてよい。例えば、一部の実装によると、動的遅延バインディング(dynamic late binding)が生じるとしてよく、その結果、そのようなインターフェースロジックが、結合されるべきトンネリングインターコネクトを動的に決定でき、トンネリングインターコネクトに対応するべくプロトコルのタイミング要件を動的に制御する。ほかの実施形態によると、設計者は、システム開発時において、1以上のプロトコルスタックによって使用されるべきトンネリングインターコネクトを決定するとしてよく、このため、当該トンネリングインターコネクトによって影響され得るリンクタイミング要件が、システム設計時において決定され得る。このため、トンネリングインターコネクトとプロトコルスタックとの間で、例えばインターフェースロジックにおいて、プロトコルスタックのタイミングを制御するロジックが組み込まれ得る。プロトコルスタックのタイミングの制御は、例えば、トンネリングインターコネクトによって発生したさらなる遅延に対応するべくプロトコルスタックのタイミングの概念を変更することによって、実現する。

【0018】

図3は、リンクタイミング要件を処理するための上述した方法の実装例、つまり、プロトコルスタックが共通物理層または別の物理層に動的に結合され得るように、インターフェースロジックによって実装され得る動的遅延バインディングの実装例を示す図である。具体的に説明すると、図3は、例えば、プロトコルスタック(所与のプロトコルの標準スタックであってよい)と、さまざまなプロトコルのパケットをトンネリングすることができる統合型インターコネクトのような共通物理層との間の通信のためのプロトコルスタックのインターフェースロジックで実装され得る方法100を説明するためのフローチャートである。図3に示すように、方法100は、トンネリングインターコネクトのタイミング遅延情報を取得することによって開始されるとしてよい(ブロック110)。この情報を取得する方法としては、さまざまな方法が実装され得る。例えば、一実施形態によると、共有物理層が、インターフェースロジックに対して所定の遅延情報の一覧を提供するとしてよい。これに代えて、インターフェースロジックは、共通物理層との間で発生しているパケット通信を分析して、タイミング遅延情報を決定するとしてもよい。より一般的には、一部の実施形態では所定の方法でタイミング情報を取得して、その他の実装でこのタイミング情報を動的に算出するとしてよい。それぞれについていくつかバリエーションが考えられ、例えば、人間が予め決定する場合と機械が予め決定する場合とがあってよく、または、算出される場合には、一度チェックするとしてもよいし、もしくは、定期的にチェックを繰り返すとしてもよい。尚、このような情報については例としてさまざまなものが考えられ、通信の性質および関連するロジックの実体に応じて、通信の種類によって発生する遅延も異なる。

【0019】

図3に戻って、ブロック120に進む。ブロック120では、タイミング遅延情報が、第1のプロトコルスタックのタイミング要件に対してマッピングされるとしてよい。一例を挙げると、プロトコルスタックのタイミング要件は、上記の表1において記載したように、リンク層通信によって異なるとしてよい。そして、ひし形130に進み、マッピングに基づいて、第1のプロトコルスタックのタイミングの概念を変更する必要があるか否かを決定するとしてよい。すなわち、共通物理層内に存在し得るレイテンシのために、当該プロトコルスタックの所定のロジックに対応付けられている1以上のタイマを、例えば、加速、減速、ディセーブル等することによって、制御することができる。このようなタイミングの概念の変更が必要ない場合には、ブロック135に進み、プロトコルスタックの標準タイミングを用いてデータを送信および/または受信するとしてよい。

【0020】

図3を参照しつつさらに説明すると、タイミングの概念を変更すべきであると決定される場合、ブロック140に進み、少なくとも1つのスタックロジックのタイミングを制御して、第1のプロトコルスタックのタイミングを変更するとしてよい。上述したように、このようなタイミングの変更は、タイマを制御すること、所定の間隔をカウントするように(またはしないように)ロジックを制御すること等に基づいて実現され得る。このようなタイミングの制御が実行された後、変更後のプロトコルスタックタイミングを用いて、所望のデータを送信/受信するとしてよい(ブロック150)。さらに図3に示すように、続いて、通信、つまり、所定のトランザクションが完了したか否かを判断するとしてよい(ひし形160)。完了していれば、当該方法を終了するとしてよい。完了していない場合は、ブロック140および150を繰り返すべく戻る。図3に図示する実施形態における具体的な実装に基づいて説明したが、本発明の範囲は、これに限定されない。

【0021】

例えば、その他の実装例においては、所定のプロトコルスタックは、遅延が既知である既知のトンネリングインターコネクトを介してトンネリングされるように、システム設計が固定されるとしてもよい。したがって、システム設計時には、当該トンネリングインターコネクトに関して発生する可能性のあるいずれの遅延についても対応するべく、必要に応じて、さまざまなプロトコルトランザクションのタイミングの制御を実行するロジックが実装され得る。上記の表1は、リンク層タイミング要件の例を示している。

【0022】

図4は、本発明の別の実施形態に係るプロトコルスタックのインターフェースを動作させる方法を示すフローチャートである。図4に示すように、方法200は、静的設計パラメータに基づいて、必要に応じて、プロトコルスタックのタイミングの概念を変更することができるインターフェースロジックによって実装され得る。図4に示すように、方法200は、トンネリングインターコネクトに対する通信またはトンネリングインターコネクトからの通信を受信することによって開始され得る(ブロック205)。このため、当該通信は、プロトコルスタックのインターフェースロジックにおいて、出力方向または入力方向で、受信される。インターフェースロジックではさまざまな種類の通信が処理されるとしてよい。例えば、肯定的応答(ACK)等のさまざまなプロトコルパケット、電力管理、フロー制御等に用いられる制御パケット、データパケットの送信および受信であってよい。

【0023】

パケットの種類に基づいて、所定の通信の種類が、変更後タイミングに影響されるか否かを、インターフェースロジックにおいて決定するとしてよい(ひし形210)。例えば、インターフェースロジックは、所定の表を含むとしてもよいし、所定の表に対応付けられているとしてもよい(不揮発性メモリに存在するとしてよい)。この表は、トランザクションの種類と、その種類の通信についてプロトコルスタックのタイミングの概念を変更すべきか否かとを特定しており、さらに、適用可能な遅延の指定、タイミングを変更するべくインターフェースロジックが適用すべき制御方策の種類を示す命令またはその他の識別子を記載する。尚、この表は複数の部分に分割されているとしてよく、それぞれの部分は、所定のスタックに対応付けられており、それぞれの部分が、あるスタック−トンネリングインターコネクト関係専用のマッピングを提供している。

【0024】

さらに図4を参照しつつ説明すると、変更が必要ない場合、標準のプロトコルスタックタイミングを用いて通信を処理するとしてよく、標準のプロトコルスタックタイミングを用いてデータを送信/受信してよい(ブロック220)。タイミングの概念を変更すべきであると決定される場合、ブロック230に進み、少なくとも1つのスタックロジックのタイミングを制御して、タイミングを変更するとしてよい。そして、変更後のプロトコルスタックタイミングを用いて所望のデータを送信/受信するとしてよい(ブロック240)。さらに図4に示すように、通信、つまり、所定のトランザクションが完了したか否かを決定するとしてよい(ひし形260)。完了している場合、当該方法を終了するとしてよい。完了していない場合、ブロック230および240を繰り返すべく戻る。リンクタイミング要件を処理する静的制御はこのように実現され得る。

【0025】

上記の図3および図4に示すように、所定の通信の種類についてタイミング制御を変更することができる一方、その他の通信の種類については、変更なしで、通常のプロトコルスタックタイミングに従って処理が進められるとしてよい。以下の説明では、リンクタイミング要件に対応するべく、プロトコルスタックのタイミングを変更し得る場合の例をいくつか紹介する。

【0026】

一実施形態によると、PT層制御30は、PCIeに割り当てられる送信機「スロット」を提供し得る。尚、この送信機「スロット」は、送信すべきPCIeトラフィックが存在しない場合、その他の種類のトラフィックにも利用可能である。このため、第1のプロトコルスタックに割り当てられたスロットは、第1のプロトコルスタックが何も送信しない場合には、別のプロトコルスタックによって用いられるとしてもよい。同様に、受信機においても、PCIeトラフィックが受信されるはずだが、ほかの構成要素が送信すべきPCIeトラフィックを有していないか、または、別の種類のより優先度が高いトラフィックを有しているかという理由で、受信機がその期間中PCIeトラフィックを一切受信しないという期間があり得る。

【0027】

「PCIe期間」という考え方をPCIeスタックに正確に伝える上で、受信時刻および送信時刻はある程度別個に考えることができる。表1に記載した、L0s呼び出しポリシーおよび「L1が終了すると・・・」という要件のような、一部の場合によると、時刻が測定されるのは、1つの観点のみからである(このような場合は、送信機の観点である)。

【0028】

しかし、Ack/Nakプロトコルの場合は、受信機および送信機の観点が両方とも考慮される必要がある。物理PCIeポートに基づいて送信パイプラインを伝播する際に特定のレイテンシを仮定して決定された、トランザクション層パケット(TLP)が送信された、PCIe送信機の観点での時間は、CIO送信パイプラインの遅延が異なっている場合には、不正確である場合がある。ほかの構成要素(つまり、受信機)は、自身のPCIeスタックが共有リンク上においてPCIe時間を割り当てられた場合にのみ応答が可能である。この割り当ては、自身の(受信機の)時間の概念を調整する必要がある旨を意味するものとして、受信機には感知される。PCIeスタックは、送信パイプラインの遅延を50ナノ秒(ns)と予測しているが、CIOリンクの送信パイプライン遅延は70nsだと仮定する。この場合、差分に対処するべく、20nsだけ、送信機の時間の概念を(この遅延を認識しているかどうかに応じて決まるプロトコルの側面について)停止または調整する必要がある。このようにすることで、送信機は、受信機(共有物理層によって遅延され得る)からのACK信号について適切な長さの時間だけ待機して、不適切にエラー信号が発行されないようにする。

【0029】

受信機の場合は、ほかの構成要素の送信機がPCIeに対して割り当てた時間(利用した時間ではない)を考慮しなければならない。一部のケースでは、受信機に直接通知されるが、その他のケースでは、ほかの構成要素の受信機が時間の概念をどれだけ進めるべきかを指し示すメッセージ等のトンネリングプロトコルメカニズムが、トンネリングされたプロトコルのそれぞれについて、設けられるとしてよい。例えば、PCIe送信機に2つの100nsスロットが割り当てられるが、送信すべきPCIeトラフィックが少ないために、そのうち1つのみが送信機によって利用される場合、受信機は200nsを考慮しなければならない。このように、ほかの構成要素が送信に利用可能なスロットを利用せずに、タイミングルールを守らない場合、ルールを守らなかったことは受信機において認識可能である。これは、(割り当てられたものではなく)使用された送信スロットのみを考慮する場合には、この限りでない。

【0030】

尚、所定のプロトコルについては多岐にわたる最適化が可能であるとしてよい。例えば、既知の帯域幅トラフィックは、実際に与えられているリンク抽象化には関係なく、カウンタメカニズムを用いて考慮するとしてよい。プロトコルの受信割り当ておよび送信割り当てが等しいことが保証されている場合、片方のみ(例えば、送信機)が、他方(受信機)の時間の概念が一致すべきであると理解していると考えてよい。

【0031】

先述したように、本発明の実施形態は、CIOまたはPCI等の具体的な内容に左右されるものでは一切なく、ディスプレイ、USB、ネットワーク等のトンネリングされるその他のプロトコルに適用され得る。本発明の実施形態はさらに、その他のトンネリングプロトコル/環境、例えば、有線または無線USBインターコネクトを介したトンネリングPCIeにも適用される。

【0032】

本発明の一実施形態に応じてトンネリングを実行することによって、より汎用度が高いハードウェアから成る一般的なハードウェア群によって、より多くの個別のIOアプリケーションで要件を満たすことができる。例えば、プラットフォームは12個のUSBポート、8個のPCIeポート、およびさまざまな特定用途向けのポート(例えば、ディスプレイ)を備えるとしてよい。トンネリングによって、これらのポートは、例えば16個の複合型ポートから成るポート群にまとめることができ、各ポートは、従前のポートのいずれ(1または複数)としても利用することができる。

【0033】

本発明の実施形態は、多くの異なる種類のシステムで実装することができる。図5は、シリアルリンクであるトンネリングインターコネクトによってコントローラハブに結合された複数のデバイスを備える、本発明の一実施形態に係るシステムを示すブロック図である。システム300は、コントローラハブ315に結合されている、プロセッサ305と、システムメモリ310とを備える。プロセッサ305は、マイクロプロセッサ、ホストプロセッサ、埋め込み型プロセッサ、コプロセッサ等のプロセッサを含む任意の処理素子を含む。プロセッサ305は、フロントサイドバス(FSB)306を介して、コントローラハブ315に結合されている。一実施形態によると、FSB306は、シリアル方式のポイントツーポイント(PtP)インターコネクトである。

【0034】

システムメモリ310は、ランダムアクセスメモリ(RAM)、不揮発性(NV)メモリ等の、システム300が備えるデバイスがアクセス可能なメモリなど、任意のメモリデバイスを含む。システムメモリ310は、メモリインターフェース316を介して、コントローラハブ315に結合される。

【0035】

一実施形態によると、コントローラハブ315は、PCIeインターコネクト階層構造において、ルートハブまたはルートコントローラである。コントローラハブ315の例を挙げると、チップセット、メモリコントローラハブ(MCH)、ノースブリッジ、入出力コントローラハブ(ICH)、サウスブリッジ、およびルートコントローラ/ハブがある。尚、コントローラハブ315は、シリアルリンク319を介して、スイッチ/ブリッジ320に結合される。入出力モジュール317および321は、インターフェース/ポート317および321と呼ばれることもあるが、コントローラハブ315とスイッチ320との間の通信を実現するべく層状プロトコルスタックを含む/実装する。一実施形態によると、スイッチ320には複数のデバイスを結合することができる。

【0036】

スイッチ320は、デバイス325からのパケット/メッセージを、上流、つまり、階層構造を上方向に、コントローラハブ315に対してルーティングすると共に、下流、つまり、階層構造を下方向に、コントローラハブ315から離れるように、デバイス325へとパケット/メッセージをルーティングする。IOモジュール322および326は、スイッチ320とデバイス325との間の通信を実行するべく、層状プロトコルスタックを実装する。一実施形態によると、IOモジュール326は、複数のプロトコルスタック、つまり、スタック327および328のパケットをトンネリングするためのトンネリング物理層であってよい。デバイス325は、電子システムに結合される、任意の内部または外部のデバイスまたは構成要素を含む。例えば、IOデバイス、ネットワークインターフェースコントローラ(NIC)、拡張カード、オーディオプロセッサ、ネットワークプロセッサ、ハードドライブ、ストレージデバイス、モニタ、プリンタ、マウス、キーボード、ルータ、ポータブルストレージデバイス、ファイヤワイヤデバイス、ユニバーサルシリアルバス(USB)デバイス、スキャナー、およびその他の入出力デバイスが挙げられる。

【0037】

コントローラハブ315にはさらに、シリアルリンク332を介して、グラフィクスアクセラレータ330が接続されている。一実施形態によると、グラフィクスアクセラレータ330は、MCHに結合され、MCHはICHに結合されている。スイッチ320は、そしてIOデバイス325は、ICHに結合されている。IOモジュール331および318もまた、グラフィクスアクセラレータ330とコントローラハブ315との間において通信を実行するべく、層状プロトコルスタックを実装する。

【0038】

本発明の実施形態は、符号で実装されるとしてよく、命令を格納しており、当該命令を実行するようにシステムをプログラミングするべく用いられる格納媒体に格納されるとしてよい。このような格納媒体は、これらに限定されるものではないが、フロッピーディスク(登録商標)、光ディスク、コンパクトディスクリードオンリーメモリ(CD−ROM)、書き換え可能コンパクトディスク(CD−RW)、および光磁気ディスク等の任意の種類のディスク、リードオンリーメモリ(ROM)、ダイナミックランダムアクセスメモリ(DRAM)およびスタティックランダムアクセスメモリ(SRAM)のようなランダムアクセスメモリ(RAM)、消去可能なプログラム可能リードオンリーメモリ(EPROM(登録商標))、フラッシュメモリ、電気的に消去可能なプログラム可能リードオンリーメモリ(EEPROM(登録商標))、磁気カードあるいは光カード等の半導体デバイス、または、電子的に命令を格納するのに適しているその他の任意の種類の媒体を含むとしてよい。

【0039】

限られた数の実施形態に基づいて本発明を説明してきたが、当業者であれば、多くの変形および変更に想到するであろう。本願の請求項はこのような変形および変更を全て、本発明の真の精神および範囲内にあるものとして、含むものである。

【背景技術】

【0001】

コンピュータプラットフォームは通常、さまざまなインターコネクトを用いて互いに結合された半導体素子を多数備えている。このようなインターコネクトまたはリンクは、プロトコルが異なっていることが多く、リンク上で実行される通信は、リンクが異なると、実行速度が異なり、準拠するプロトコルも異なる。一部のシステムでは、入出力(I/O)プロトコルの通信は、別のインターコネクトにおいてトンネリングされ得る。トンネリングは一般的に、第1のプロトコルに準拠した通信を受け取り、第2のプロトコルにしたがって動作するインターコネクトを介して当該通信を提供することを含む。例えば、第1のプロトコルのパケットに第2のプロトコルのヘッダを適用して、当該パケットをインターコネクトを介して送信することによって、第1のプロトコルのパケットがトンネリングされる。多くの場合、このようなプロトコルトンネリングは非常に上位のレベルで実行され、これら2つのプロトコルが有するソフトウェア抽象化が同じである一方、プロトコル間で共有されているハードウェアはない。このように、ソフトウェア互換性、性能、製品化までの時間において、上述したようなトンネリングによる利点は非常に小さい。

【図面の簡単な説明】

【0002】

【図1】本発明の一実施形態に係る、共有物理層を介したリンクへのプロトコルスタックの接続を示すブロック図である。

【0003】

【図2】本発明の別の実施形態に係る、共有物理層に結合されている複数の通信スタックを備えるシステムを示すブロック図である。

【0004】

【図3】本発明の一実施形態に係る方法を説明するためのフローチャートである。

【0005】

【図4】本発明の別の実施形態に係る、プロトコルスタックのインターフェースを動作させる方法を説明するためのフローチャートである。

【0006】

【図5】本発明の一実施形態に係るシステムを示すブロック図である。

【発明を実施するための形態】

【0007】

さまざまな実施形態によると、1以上の既存のIOプロトコルが、比較的低位のレベルで、別のインターコネクトにおいてトンネリングされ得る。本明細書では、「別のインターコネクト」を「トンネリングインターコネクト」と呼ぶことにする。一実施形態によると、このようなインターコネクトの一例として統合型(converged)IO(CIO)が挙げられる。CIOは、PCI Express(登録商標)仕様書の基本仕様書バージョン2.0(2007年1月17日発行)に従った(以降では、PCIe(登録商標)仕様書と呼ぶ)、PCIe(Peripheral Component Interconnect Express)プロトコルの通信、または、同様のプロトコルの通信をトンネリングするべく用いることができる。CIOの場合、PCIeハードウェアスタックの多くは直接実装されるので、ソフトウェア互換性、性能、および製品化までの時間において、利点が得られる。すなわち、低位のレベルのトンネリングにおいて、トンネリングされるプロトコルスタックは大半が実装されている。これとは対照的に、高位のレベルのトンネリングの場合は、ソフトウェアアーキテクチャは保存されるが、トンネリングされるプロトコルからのパケット、符号化、または有線用プロトコルメカニズムを必ずしも用いるわけではない。このように低位のトンネリングによって、PCIeプロトコルスタックのパケットを、例えば、トンネリングパケットにCIOヘッダを適合させることによって、CIOインターコネクトを介してトンネリングすることができる。このように送信されたトンネリングパケットを受信機が受信すると、受信機のCIOプロトコルスタックはヘッダを復号化して、受信機の対応PCIeプロトコルスタックにPCIeパケットを渡すことができる。

【0008】

しかし、統合型インターコネクトに対するこのようなアプローチによって、抽象化という、より高位で行われるプロトコルのトンネリングとは対照的に、低位トンネリングに起因する問題が生じる。つまり、プロトコルのタイミングについて制約が潜在的に課されていることが多い。このような制約は、インターコネクトプロトコルのトンネリングされていない元々のインスタンス化では満足させられていたことが自明であるが、インターコネクトプロトコルをトンネリングする場合には、トンネリングに用いられるインターコネクトによる遅延が発生するために、管理するのがより困難になり得る。このような遅延は、トンネリングインターコネクト自身によって生じる場合もあり、または、その他のトンネリングされたプロトコルによるトラフィックによって生じる場合もある。

【0009】

本発明の実施形態は、トンネリングインターコネクトを介してトンネリングを実行する場合に、トンネリングされるプロトコルの明示的および暗示的なタイマを管理するメカニズムを提供する。本明細書で説明する実施形態ではCIOを介してトンネリングされるPCIeプロトコルを一例として用いるが、本発明の範囲はこれに限定されるものではなく、同様の原理は、その他のトンネリングインターコネクト、および、有線インターコネクトおよび無線インターコネクトを始めとする、トンネリングに用いられるその他のインターコネクトにも応用され得ると理解されたい。

【0010】

インターコネクトに関する、明示的および暗示的な、タイミング要件は、大きく分けて2つのカテゴリーに分類され得る。本明細書では、リンクタイミング要件および掛け時計タイミング要件と呼ぶ。リンクタイミング要件は、リンクプロトコル等の低位レベルに対応付けられており、リンク動作を円滑化して、検証に関する問題を最低限に抑えることを目的として通常設けられている。掛け時計タイミング要件は、高位レベルにおいて観察可能なイベント、例えば、オペレーティングシステム(OS)およびアプリケーションソフトウェアに対応付けられている。リンクタイミング要件は、プロトコルトンネリングによって生じる遅延に直接影響を受ける可能性があり、本発明の実施形態によって問題解決を図る要件である。通常、リンクタイミング要件は、約10マイクロ秒(μs)未満のオーダーであり得るが、掛け時計タイミング要件は、約10マイクロ秒(μs)よりも大きい。掛け時計タイミング要件は、プロトコルのトンネリングによって生じる比較的短時間(例えば、マイクロ秒)の遅延に影響されない程度に十分長い時間値(例えば、ミリ秒(ms))に対応付けられていることが多いので、プロトコルトンネリングには基本的に影響されない。また、このような要件は、特定のインターコネクトプロトコルを伝送するべく用いられるハードウェアメカニズムに関わらず(本来のもの、または、トンネリング用)等しく望ましい、アプリケーションソフトウェアにおいてユーザに見える動作停止(stall)の発生を防ぐというような、特性に対応付けられている。

【0011】

以下に記載する表1は、PCIeに対応付けられている多数のタイミング要件を一覧にしたものであり、各要件と本開示との関係を示す。「説明」部分の記載は、PCI Express(登録商標)仕様書から引用していることに留意されたい。

【表1】

表1は、一部を例示することを目的とするものであって、PCIeにおけるタイミング関連の要件を全て完全に網羅したものではないことに留意されたい。

【0012】

リンクタイミング要件は、PCIeスタック自身によって「測定」されるので、PCIeスタックの時間に対する概念が変わると、このようなタイミング要件を感知する方法も変化し得る。このような構成を実現するべく、時間変更を実現するためのメカニズムが、スタックタイミングをいつ、そして、どのように変更するかを決定するためのハードウェア、ソフトウェアまたはファームウェアと共に、提供されるとしてよい。

【0013】

PCIeスタックの時間の概念を変更するメカニズムは、複数の方法で実現することができる。例えば、PCIeスタックロジックにおけるさまざまな要素に対するクロックをゲーティングまたはオフに制御して、対象となるロジックの時間を止めることによって、実現することができる。尚、この方法によれば、利用されていないPCIeスタックロジックの電力消費を低減するという効果もさらに得られる。ほかの実施形態によると、時間をカウントすべき場合を指し示す明示的な制御信号を、PCIeスタックロジックに追加することができる。スタック全体を1つの単位として制御することは一般的に十分ではなく、スタックのサブ構成要素は、プロトコルメカニズムが異なれば、異なるロジックブロックに対する影響も異なるので、半独立制御が実行され得る。同様に、リンクタイミング要件を遵守するべく、全ての通信についてタイミング変更が必要となるわけではない。一実施形態によると、制御ロジックを用いてPCIeスタックの時間の概念をいつおよびどのように調整するかを決定するとしてよく、当該ロジックはPCIeスタックの一部であってよい。

【0014】

図1は、PCIeスタック(およびその他のトンネリングされたプロトコル)が共有トンネリングリンクにインターフェースされる様子を示すブロック図である。一実施形態によると、共有トンネリングリンクは、CIOリンクであってよい。図1に示すように、システム10は、第1のスタック20aと、第2のスタック20b(プロトコルスタック20と総称する)とを備える。一実施形態によると、第1のプロトコルスタック20aは、PCIeスタックであってよく、第2のプロトコルスタック20bは、ユニバーサルシリアルバス(USB)、ディスプレイインターコネクト、またはその他の同様のプロトコルスタックであってよい。図示の便宜上、PCIeプロトコルスタックの詳細のみを示す。具体的には、プロトコルスタック20aは、トランザクション層22と、データリンク層24と、インターフェースまたはガスケット層26とを有する。インターフェースまたはガスケット層26は、PCIeプロトコルとトンネリングプロトコルとの間のインターフェースとして機能する。このようなインターフェースロジックの動作の詳細は後述する。

【0015】

図1に示すように、統合型IO層は、第1および第2のプロトコルスタック20と、リンク70との間に結合されるとしてよい。リンク70は、一実施形態によると、光リンク、電気リンク、またはその他の同様のリンクであってよい。図1に示すように、CIOプロトコルスタックは、CIOプロトコルトランスポート層30と、物理層の論理ブロック40と、物理層の電気ブロック50と、物理層の光ブロック60とを有するとしてよい。このように、ブロック40から60は、物理層と通信している複数のプロトコルによって共有されて、これらの複数のプロトコルの情報をリンク70によってトンネリングする共通物理層として機能する。

【0016】

図2は、共有物理層に結合されている複数の通信スタックを備えるシステムを示す図である。具体的には、図2では、PCIe送信(Tx)および受信(Rx)スタック20aに加えて、複数のその他の送信および受信スタック20b−20dが設けられるとしてよい。同図に示すように、一対のマルチプレクサ35aおよび35b(マルチプレクサ35と総称する)が、これらのスタックと共有物理層40−60との間に、結合されているとしてよい。マルチプレクサ35は、プロトコルトランスポート層制御30の制御下で、動作させられるとしてよい。図2に示すように、CIOプロトコルトランスポート(PT)層30は、PCIeおよびその他のプロトコルをトンネリングするための、マルチプレクシングメカニズム(マルチプレクサ35aおよび35bに基づく)および制御メカニズムを実装する。PT層制御30は、送信機の抽象化と、送信機とは別個である受信機の操作を実装する。このような構造はこの説明の残りの部分でも用いるが、本発明の実施形態は、例えば、同時に送信機および受信機を抽象化することによって、または、単一の双方向接続を用いることによって、送信機および受信機を別々に制御するその他の種類のインターコネクトに応用され得る。

【0017】

インターコネクトのタイミング制御を実装する方法は、実施形態によって異なるとしてよい。例えば、一部の実装によると、動的遅延バインディング(dynamic late binding)が生じるとしてよく、その結果、そのようなインターフェースロジックが、結合されるべきトンネリングインターコネクトを動的に決定でき、トンネリングインターコネクトに対応するべくプロトコルのタイミング要件を動的に制御する。ほかの実施形態によると、設計者は、システム開発時において、1以上のプロトコルスタックによって使用されるべきトンネリングインターコネクトを決定するとしてよく、このため、当該トンネリングインターコネクトによって影響され得るリンクタイミング要件が、システム設計時において決定され得る。このため、トンネリングインターコネクトとプロトコルスタックとの間で、例えばインターフェースロジックにおいて、プロトコルスタックのタイミングを制御するロジックが組み込まれ得る。プロトコルスタックのタイミングの制御は、例えば、トンネリングインターコネクトによって発生したさらなる遅延に対応するべくプロトコルスタックのタイミングの概念を変更することによって、実現する。

【0018】

図3は、リンクタイミング要件を処理するための上述した方法の実装例、つまり、プロトコルスタックが共通物理層または別の物理層に動的に結合され得るように、インターフェースロジックによって実装され得る動的遅延バインディングの実装例を示す図である。具体的に説明すると、図3は、例えば、プロトコルスタック(所与のプロトコルの標準スタックであってよい)と、さまざまなプロトコルのパケットをトンネリングすることができる統合型インターコネクトのような共通物理層との間の通信のためのプロトコルスタックのインターフェースロジックで実装され得る方法100を説明するためのフローチャートである。図3に示すように、方法100は、トンネリングインターコネクトのタイミング遅延情報を取得することによって開始されるとしてよい(ブロック110)。この情報を取得する方法としては、さまざまな方法が実装され得る。例えば、一実施形態によると、共有物理層が、インターフェースロジックに対して所定の遅延情報の一覧を提供するとしてよい。これに代えて、インターフェースロジックは、共通物理層との間で発生しているパケット通信を分析して、タイミング遅延情報を決定するとしてもよい。より一般的には、一部の実施形態では所定の方法でタイミング情報を取得して、その他の実装でこのタイミング情報を動的に算出するとしてよい。それぞれについていくつかバリエーションが考えられ、例えば、人間が予め決定する場合と機械が予め決定する場合とがあってよく、または、算出される場合には、一度チェックするとしてもよいし、もしくは、定期的にチェックを繰り返すとしてもよい。尚、このような情報については例としてさまざまなものが考えられ、通信の性質および関連するロジックの実体に応じて、通信の種類によって発生する遅延も異なる。

【0019】

図3に戻って、ブロック120に進む。ブロック120では、タイミング遅延情報が、第1のプロトコルスタックのタイミング要件に対してマッピングされるとしてよい。一例を挙げると、プロトコルスタックのタイミング要件は、上記の表1において記載したように、リンク層通信によって異なるとしてよい。そして、ひし形130に進み、マッピングに基づいて、第1のプロトコルスタックのタイミングの概念を変更する必要があるか否かを決定するとしてよい。すなわち、共通物理層内に存在し得るレイテンシのために、当該プロトコルスタックの所定のロジックに対応付けられている1以上のタイマを、例えば、加速、減速、ディセーブル等することによって、制御することができる。このようなタイミングの概念の変更が必要ない場合には、ブロック135に進み、プロトコルスタックの標準タイミングを用いてデータを送信および/または受信するとしてよい。

【0020】

図3を参照しつつさらに説明すると、タイミングの概念を変更すべきであると決定される場合、ブロック140に進み、少なくとも1つのスタックロジックのタイミングを制御して、第1のプロトコルスタックのタイミングを変更するとしてよい。上述したように、このようなタイミングの変更は、タイマを制御すること、所定の間隔をカウントするように(またはしないように)ロジックを制御すること等に基づいて実現され得る。このようなタイミングの制御が実行された後、変更後のプロトコルスタックタイミングを用いて、所望のデータを送信/受信するとしてよい(ブロック150)。さらに図3に示すように、続いて、通信、つまり、所定のトランザクションが完了したか否かを判断するとしてよい(ひし形160)。完了していれば、当該方法を終了するとしてよい。完了していない場合は、ブロック140および150を繰り返すべく戻る。図3に図示する実施形態における具体的な実装に基づいて説明したが、本発明の範囲は、これに限定されない。

【0021】

例えば、その他の実装例においては、所定のプロトコルスタックは、遅延が既知である既知のトンネリングインターコネクトを介してトンネリングされるように、システム設計が固定されるとしてもよい。したがって、システム設計時には、当該トンネリングインターコネクトに関して発生する可能性のあるいずれの遅延についても対応するべく、必要に応じて、さまざまなプロトコルトランザクションのタイミングの制御を実行するロジックが実装され得る。上記の表1は、リンク層タイミング要件の例を示している。

【0022】

図4は、本発明の別の実施形態に係るプロトコルスタックのインターフェースを動作させる方法を示すフローチャートである。図4に示すように、方法200は、静的設計パラメータに基づいて、必要に応じて、プロトコルスタックのタイミングの概念を変更することができるインターフェースロジックによって実装され得る。図4に示すように、方法200は、トンネリングインターコネクトに対する通信またはトンネリングインターコネクトからの通信を受信することによって開始され得る(ブロック205)。このため、当該通信は、プロトコルスタックのインターフェースロジックにおいて、出力方向または入力方向で、受信される。インターフェースロジックではさまざまな種類の通信が処理されるとしてよい。例えば、肯定的応答(ACK)等のさまざまなプロトコルパケット、電力管理、フロー制御等に用いられる制御パケット、データパケットの送信および受信であってよい。

【0023】

パケットの種類に基づいて、所定の通信の種類が、変更後タイミングに影響されるか否かを、インターフェースロジックにおいて決定するとしてよい(ひし形210)。例えば、インターフェースロジックは、所定の表を含むとしてもよいし、所定の表に対応付けられているとしてもよい(不揮発性メモリに存在するとしてよい)。この表は、トランザクションの種類と、その種類の通信についてプロトコルスタックのタイミングの概念を変更すべきか否かとを特定しており、さらに、適用可能な遅延の指定、タイミングを変更するべくインターフェースロジックが適用すべき制御方策の種類を示す命令またはその他の識別子を記載する。尚、この表は複数の部分に分割されているとしてよく、それぞれの部分は、所定のスタックに対応付けられており、それぞれの部分が、あるスタック−トンネリングインターコネクト関係専用のマッピングを提供している。

【0024】

さらに図4を参照しつつ説明すると、変更が必要ない場合、標準のプロトコルスタックタイミングを用いて通信を処理するとしてよく、標準のプロトコルスタックタイミングを用いてデータを送信/受信してよい(ブロック220)。タイミングの概念を変更すべきであると決定される場合、ブロック230に進み、少なくとも1つのスタックロジックのタイミングを制御して、タイミングを変更するとしてよい。そして、変更後のプロトコルスタックタイミングを用いて所望のデータを送信/受信するとしてよい(ブロック240)。さらに図4に示すように、通信、つまり、所定のトランザクションが完了したか否かを決定するとしてよい(ひし形260)。完了している場合、当該方法を終了するとしてよい。完了していない場合、ブロック230および240を繰り返すべく戻る。リンクタイミング要件を処理する静的制御はこのように実現され得る。

【0025】

上記の図3および図4に示すように、所定の通信の種類についてタイミング制御を変更することができる一方、その他の通信の種類については、変更なしで、通常のプロトコルスタックタイミングに従って処理が進められるとしてよい。以下の説明では、リンクタイミング要件に対応するべく、プロトコルスタックのタイミングを変更し得る場合の例をいくつか紹介する。

【0026】

一実施形態によると、PT層制御30は、PCIeに割り当てられる送信機「スロット」を提供し得る。尚、この送信機「スロット」は、送信すべきPCIeトラフィックが存在しない場合、その他の種類のトラフィックにも利用可能である。このため、第1のプロトコルスタックに割り当てられたスロットは、第1のプロトコルスタックが何も送信しない場合には、別のプロトコルスタックによって用いられるとしてもよい。同様に、受信機においても、PCIeトラフィックが受信されるはずだが、ほかの構成要素が送信すべきPCIeトラフィックを有していないか、または、別の種類のより優先度が高いトラフィックを有しているかという理由で、受信機がその期間中PCIeトラフィックを一切受信しないという期間があり得る。

【0027】

「PCIe期間」という考え方をPCIeスタックに正確に伝える上で、受信時刻および送信時刻はある程度別個に考えることができる。表1に記載した、L0s呼び出しポリシーおよび「L1が終了すると・・・」という要件のような、一部の場合によると、時刻が測定されるのは、1つの観点のみからである(このような場合は、送信機の観点である)。

【0028】

しかし、Ack/Nakプロトコルの場合は、受信機および送信機の観点が両方とも考慮される必要がある。物理PCIeポートに基づいて送信パイプラインを伝播する際に特定のレイテンシを仮定して決定された、トランザクション層パケット(TLP)が送信された、PCIe送信機の観点での時間は、CIO送信パイプラインの遅延が異なっている場合には、不正確である場合がある。ほかの構成要素(つまり、受信機)は、自身のPCIeスタックが共有リンク上においてPCIe時間を割り当てられた場合にのみ応答が可能である。この割り当ては、自身の(受信機の)時間の概念を調整する必要がある旨を意味するものとして、受信機には感知される。PCIeスタックは、送信パイプラインの遅延を50ナノ秒(ns)と予測しているが、CIOリンクの送信パイプライン遅延は70nsだと仮定する。この場合、差分に対処するべく、20nsだけ、送信機の時間の概念を(この遅延を認識しているかどうかに応じて決まるプロトコルの側面について)停止または調整する必要がある。このようにすることで、送信機は、受信機(共有物理層によって遅延され得る)からのACK信号について適切な長さの時間だけ待機して、不適切にエラー信号が発行されないようにする。

【0029】

受信機の場合は、ほかの構成要素の送信機がPCIeに対して割り当てた時間(利用した時間ではない)を考慮しなければならない。一部のケースでは、受信機に直接通知されるが、その他のケースでは、ほかの構成要素の受信機が時間の概念をどれだけ進めるべきかを指し示すメッセージ等のトンネリングプロトコルメカニズムが、トンネリングされたプロトコルのそれぞれについて、設けられるとしてよい。例えば、PCIe送信機に2つの100nsスロットが割り当てられるが、送信すべきPCIeトラフィックが少ないために、そのうち1つのみが送信機によって利用される場合、受信機は200nsを考慮しなければならない。このように、ほかの構成要素が送信に利用可能なスロットを利用せずに、タイミングルールを守らない場合、ルールを守らなかったことは受信機において認識可能である。これは、(割り当てられたものではなく)使用された送信スロットのみを考慮する場合には、この限りでない。

【0030】

尚、所定のプロトコルについては多岐にわたる最適化が可能であるとしてよい。例えば、既知の帯域幅トラフィックは、実際に与えられているリンク抽象化には関係なく、カウンタメカニズムを用いて考慮するとしてよい。プロトコルの受信割り当ておよび送信割り当てが等しいことが保証されている場合、片方のみ(例えば、送信機)が、他方(受信機)の時間の概念が一致すべきであると理解していると考えてよい。

【0031】

先述したように、本発明の実施形態は、CIOまたはPCI等の具体的な内容に左右されるものでは一切なく、ディスプレイ、USB、ネットワーク等のトンネリングされるその他のプロトコルに適用され得る。本発明の実施形態はさらに、その他のトンネリングプロトコル/環境、例えば、有線または無線USBインターコネクトを介したトンネリングPCIeにも適用される。

【0032】

本発明の一実施形態に応じてトンネリングを実行することによって、より汎用度が高いハードウェアから成る一般的なハードウェア群によって、より多くの個別のIOアプリケーションで要件を満たすことができる。例えば、プラットフォームは12個のUSBポート、8個のPCIeポート、およびさまざまな特定用途向けのポート(例えば、ディスプレイ)を備えるとしてよい。トンネリングによって、これらのポートは、例えば16個の複合型ポートから成るポート群にまとめることができ、各ポートは、従前のポートのいずれ(1または複数)としても利用することができる。

【0033】

本発明の実施形態は、多くの異なる種類のシステムで実装することができる。図5は、シリアルリンクであるトンネリングインターコネクトによってコントローラハブに結合された複数のデバイスを備える、本発明の一実施形態に係るシステムを示すブロック図である。システム300は、コントローラハブ315に結合されている、プロセッサ305と、システムメモリ310とを備える。プロセッサ305は、マイクロプロセッサ、ホストプロセッサ、埋め込み型プロセッサ、コプロセッサ等のプロセッサを含む任意の処理素子を含む。プロセッサ305は、フロントサイドバス(FSB)306を介して、コントローラハブ315に結合されている。一実施形態によると、FSB306は、シリアル方式のポイントツーポイント(PtP)インターコネクトである。

【0034】

システムメモリ310は、ランダムアクセスメモリ(RAM)、不揮発性(NV)メモリ等の、システム300が備えるデバイスがアクセス可能なメモリなど、任意のメモリデバイスを含む。システムメモリ310は、メモリインターフェース316を介して、コントローラハブ315に結合される。

【0035】

一実施形態によると、コントローラハブ315は、PCIeインターコネクト階層構造において、ルートハブまたはルートコントローラである。コントローラハブ315の例を挙げると、チップセット、メモリコントローラハブ(MCH)、ノースブリッジ、入出力コントローラハブ(ICH)、サウスブリッジ、およびルートコントローラ/ハブがある。尚、コントローラハブ315は、シリアルリンク319を介して、スイッチ/ブリッジ320に結合される。入出力モジュール317および321は、インターフェース/ポート317および321と呼ばれることもあるが、コントローラハブ315とスイッチ320との間の通信を実現するべく層状プロトコルスタックを含む/実装する。一実施形態によると、スイッチ320には複数のデバイスを結合することができる。

【0036】

スイッチ320は、デバイス325からのパケット/メッセージを、上流、つまり、階層構造を上方向に、コントローラハブ315に対してルーティングすると共に、下流、つまり、階層構造を下方向に、コントローラハブ315から離れるように、デバイス325へとパケット/メッセージをルーティングする。IOモジュール322および326は、スイッチ320とデバイス325との間の通信を実行するべく、層状プロトコルスタックを実装する。一実施形態によると、IOモジュール326は、複数のプロトコルスタック、つまり、スタック327および328のパケットをトンネリングするためのトンネリング物理層であってよい。デバイス325は、電子システムに結合される、任意の内部または外部のデバイスまたは構成要素を含む。例えば、IOデバイス、ネットワークインターフェースコントローラ(NIC)、拡張カード、オーディオプロセッサ、ネットワークプロセッサ、ハードドライブ、ストレージデバイス、モニタ、プリンタ、マウス、キーボード、ルータ、ポータブルストレージデバイス、ファイヤワイヤデバイス、ユニバーサルシリアルバス(USB)デバイス、スキャナー、およびその他の入出力デバイスが挙げられる。

【0037】

コントローラハブ315にはさらに、シリアルリンク332を介して、グラフィクスアクセラレータ330が接続されている。一実施形態によると、グラフィクスアクセラレータ330は、MCHに結合され、MCHはICHに結合されている。スイッチ320は、そしてIOデバイス325は、ICHに結合されている。IOモジュール331および318もまた、グラフィクスアクセラレータ330とコントローラハブ315との間において通信を実行するべく、層状プロトコルスタックを実装する。

【0038】

本発明の実施形態は、符号で実装されるとしてよく、命令を格納しており、当該命令を実行するようにシステムをプログラミングするべく用いられる格納媒体に格納されるとしてよい。このような格納媒体は、これらに限定されるものではないが、フロッピーディスク(登録商標)、光ディスク、コンパクトディスクリードオンリーメモリ(CD−ROM)、書き換え可能コンパクトディスク(CD−RW)、および光磁気ディスク等の任意の種類のディスク、リードオンリーメモリ(ROM)、ダイナミックランダムアクセスメモリ(DRAM)およびスタティックランダムアクセスメモリ(SRAM)のようなランダムアクセスメモリ(RAM)、消去可能なプログラム可能リードオンリーメモリ(EPROM(登録商標))、フラッシュメモリ、電気的に消去可能なプログラム可能リードオンリーメモリ(EEPROM(登録商標))、磁気カードあるいは光カード等の半導体デバイス、または、電子的に命令を格納するのに適しているその他の任意の種類の媒体を含むとしてよい。

【0039】

限られた数の実施形態に基づいて本発明を説明してきたが、当業者であれば、多くの変形および変更に想到するであろう。本願の請求項はこのような変形および変更を全て、本発明の真の精神および範囲内にあるものとして、含むものである。

【特許請求の範囲】

【請求項1】

第1のプロトコルにしたがってデータを処理する第1のプロトコルスタックであって、前記第1のプロトコルスタックをトンネリングインターコネクトにインターフェースするインターフェースロジックを有する前記第1のプロトコルスタックと、

前記第1のプロトコルスタックをリンクに結合する前記トンネリングインターコネクトと

を備え、

前記インターフェースロジックは、前記トンネリングインターコネクトによるトンネリングによって発生するタイミング遅延に少なくとも部分的に基づいて前記第1のプロトコルスタックの少なくとも1つのタイマを制御する

装置。

【請求項2】

前記インターフェースロジックは、前記タイミング遅延に対応付けられているタイミング遅延情報を、前記第1のプロトコルスタックの少なくとも1つのスタックロジックの、タイミングについての制約を示すタイミング要件に対応付ける

請求項1に記載の装置。

【請求項3】

前記インターフェースロジックは、前記タイミング遅延情報、及び前記タイミング遅延情報に対応付けられている前記タイミング要件に少なくとも部分的に基づいて、前記第1のプロトコルスタックの前記少なくとも1つのタイマを制御することによって、前記第1のプロトコルスタックのタイミングを変更するか否かを判断する

請求項2に記載の装置。

【請求項4】

前記インターフェースロジックは、前記タイミング遅延情報を前記タイミング要件に動的に対応付けして、前記第1のプロトコルスタックは、前記トンネリングインターコネクトの共通物理層または別の物理層に動的に結合される

請求項2に記載の装置。

【請求項5】

前記インターフェースロジックは、前記第1のプロトコルスタックの第1のスタックロジックが、前記第1のプロトコルの、タイミングについての制約を示すリンクタイミング要件を満たすべく、前記第1のスタックロジックに第1のクロック信号を供給する第1のクロックを、予め定められた時間にわたってディセーブルする

請求項1に記載の装置。

【請求項6】

前記トンネリングインターコネクトは、前記トンネリングインターコネクトのプロトコルによって、前記第1のプロトコルのパケットを前記リンクにトンネリングする

請求項5に記載の装置。

【請求項7】

前記リンクは、前記第1のプロトコルスタックと第2のプロトコルスタックとの間で共有する統合型インターコネクトであり、前記第1のプロトコルスタックは、PCIe(Peripheral Component Interconnect Express(登録商標))スタックである

請求項1から6のいずれか1項に記載の装置。

【請求項8】

前記トンネリングインターコネクトは、前記第1のプロトコルスタックに第1のスロットおよび第2のスロットを割り当てて、前記第2のプロトコルスタックに第3のスロットを割り当てる

請求項7に記載の装置。

【請求項9】

前記リンクに結合されており、前記トンネリングインターコネクトによりトンネリングされたパケットを受信する受信機

をさらに備え、

前記受信機は、前記リンクに結合されているインターフェースロジックによって、割り当てられた前記第1のスロットおよび前記第2のスロットを利用する

請求項8に記載の装置。

【請求項10】

トンネリングインターコネクトに結合されている第1のプロトコルスタックのインターフェースロジックにおいて通信を受信する段階と、

前記通信の通信種類に基づいてテーブルにアクセスして、前記通信種類に対応付けられている、前記トンネリングインターコネクトによるトンネリングによって発生するタイミング遅延を示すタイミング遅延情報を取得する段階と、

前記タイミング遅延情報が示す遅延に対応するべく、前記通信の通信種類について前記第1のプロトコルスタックの少なくとも1つのスタックロジックのタイミングを制御するべきか否かを決定する段階と、

前記決定する段階において変更するべきと決定した場合に、前記第1のプロトコルスタックの前記少なくとも1つのスタックロジックのタイミングを調整して、前記遅延に対応する段階と、

調整された前記タイミングを用いて前記第1のプロトコルスタックにおいて前記通信を処理する段階と

を備える方法。

【請求項11】

前記テーブルは、不揮発性メモリに格納されており、前記トンネリングインターコネクトと前記第1のプロトコルスタックとの間のマッピングを含む第1の部分と、前記トンネリングインターコネクトと前記トンネリングインターコネクトに結合されている第2のプロトコルスタックとの間のマッピングを含む第2の部分とを有する

請求項10に記載の方法。

【請求項12】

前記第1のプロトコルスタックと前記第2のプロトコルスタックとの間で前記トンネリングインターコネクトを共有する段階と、

前記第1のプロトコルスタックがあるスロットにおいて通信対象の情報を持たない場合に、前記第2のプロトコルスタックに前記第1のプロトコルスタックの前記スロットを与える段階と

をさらに備える、請求項11に記載の方法。

【請求項13】

前記少なくとも1つのスタックロジックの前記タイミングは、前記少なくとも1つのスタックロジックに結合されているクロックをオフにすることによって調整される

請求項10から12のいずれか1項に記載の方法。

【請求項14】

前記遅延に少なくとも部分的に基づいて、第2のスタックロジックのクロックを遅延させる段階

をさらに備える、請求項13に記載の方法。

【請求項15】

前記クロックを遅延して、予め定められた時間が経過するまで、前記トンネリングインターコネクトによって時間要件が満たされない場合にトリガされる、受信機からの肯定応答を受領していない旨を指し示すエラー信号が発行されないようにする段階

をさらに備える、請求項14に記載の方法。

【請求項16】

リンクに結合されている物理層、および、前記物理層に結合されているプロトコルスタックを有する送信機と、

前記リンクを介して前記送信機に結合されており、第1のプロトコルにしたがってデータを処理する第1のプロトコルスタックを有する受信機と、

前記受信機に結合されているダイナミックランダムアクセスメモリ(DRAM)と

を備え、

前記第1のプロトコルスタックは、トンネリング物理層を介して、前記リンクに前記第1のプロトコルスタックをインターフェースする第1のインターフェースロジックを含み、前記第1のインターフェースロジックは、前記トンネリング物理層によるトンネリングによって発生するタイミング遅延に少なくとも部分的に基づいて、前記第1のプロトコルスタックの少なくとも1つの第1のスタックロジックのタイミングを変更する

システム。

【請求項17】

前記受信機はさらに、第2のプロトコルにしたがってデータを処理する第2のプロトコルスタックを有し、前記第2のプロトコルスタックは、前記タイミング遅延に少なくとも部分的に基づいて前記第2のプロトコルスタックの少なくとも1つの第2のスタックロジックのタイミングを変更する第2のインターフェースロジックを含む

請求項16に記載のシステム。

【請求項18】

前記トンネリング物理層は、前記第1のプロトコルスタックまたは前記第2のプロトコルスタックを選択して前記送信機からのパケットを受信させるコントローラを含む

請求項17に記載のシステム。

【請求項19】

前記第1のインターフェースロジックは、前記トンネリング物理層を介して前記送信機から受信したパケットの通信種類に基づいてテーブルにアクセスして、前記通信種類に対応付けられている、タイミング遅延情報を取得し、前記タイミング遅延情報が示す遅延に対応するべく、前記通信種類について前記第1のプロトコルスタックの前記少なくとも第1のスタックロジックのタイミングを変更するべきか否かを決定する

請求項16から18のいずれか1項に記載のシステム。

【請求項1】

第1のプロトコルにしたがってデータを処理する第1のプロトコルスタックであって、前記第1のプロトコルスタックをトンネリングインターコネクトにインターフェースするインターフェースロジックを有する前記第1のプロトコルスタックと、

前記第1のプロトコルスタックをリンクに結合する前記トンネリングインターコネクトと

を備え、

前記インターフェースロジックは、前記トンネリングインターコネクトによるトンネリングによって発生するタイミング遅延に少なくとも部分的に基づいて前記第1のプロトコルスタックの少なくとも1つのタイマを制御する

装置。

【請求項2】

前記インターフェースロジックは、前記タイミング遅延に対応付けられているタイミング遅延情報を、前記第1のプロトコルスタックの少なくとも1つのスタックロジックの、タイミングについての制約を示すタイミング要件に対応付ける

請求項1に記載の装置。

【請求項3】

前記インターフェースロジックは、前記タイミング遅延情報、及び前記タイミング遅延情報に対応付けられている前記タイミング要件に少なくとも部分的に基づいて、前記第1のプロトコルスタックの前記少なくとも1つのタイマを制御することによって、前記第1のプロトコルスタックのタイミングを変更するか否かを判断する

請求項2に記載の装置。

【請求項4】

前記インターフェースロジックは、前記タイミング遅延情報を前記タイミング要件に動的に対応付けして、前記第1のプロトコルスタックは、前記トンネリングインターコネクトの共通物理層または別の物理層に動的に結合される

請求項2に記載の装置。

【請求項5】

前記インターフェースロジックは、前記第1のプロトコルスタックの第1のスタックロジックが、前記第1のプロトコルの、タイミングについての制約を示すリンクタイミング要件を満たすべく、前記第1のスタックロジックに第1のクロック信号を供給する第1のクロックを、予め定められた時間にわたってディセーブルする

請求項1に記載の装置。

【請求項6】

前記トンネリングインターコネクトは、前記トンネリングインターコネクトのプロトコルによって、前記第1のプロトコルのパケットを前記リンクにトンネリングする

請求項5に記載の装置。

【請求項7】

前記リンクは、前記第1のプロトコルスタックと第2のプロトコルスタックとの間で共有する統合型インターコネクトであり、前記第1のプロトコルスタックは、PCIe(Peripheral Component Interconnect Express(登録商標))スタックである

請求項1から6のいずれか1項に記載の装置。

【請求項8】

前記トンネリングインターコネクトは、前記第1のプロトコルスタックに第1のスロットおよび第2のスロットを割り当てて、前記第2のプロトコルスタックに第3のスロットを割り当てる

請求項7に記載の装置。

【請求項9】

前記リンクに結合されており、前記トンネリングインターコネクトによりトンネリングされたパケットを受信する受信機

をさらに備え、

前記受信機は、前記リンクに結合されているインターフェースロジックによって、割り当てられた前記第1のスロットおよび前記第2のスロットを利用する

請求項8に記載の装置。

【請求項10】

トンネリングインターコネクトに結合されている第1のプロトコルスタックのインターフェースロジックにおいて通信を受信する段階と、

前記通信の通信種類に基づいてテーブルにアクセスして、前記通信種類に対応付けられている、前記トンネリングインターコネクトによるトンネリングによって発生するタイミング遅延を示すタイミング遅延情報を取得する段階と、

前記タイミング遅延情報が示す遅延に対応するべく、前記通信の通信種類について前記第1のプロトコルスタックの少なくとも1つのスタックロジックのタイミングを制御するべきか否かを決定する段階と、

前記決定する段階において変更するべきと決定した場合に、前記第1のプロトコルスタックの前記少なくとも1つのスタックロジックのタイミングを調整して、前記遅延に対応する段階と、

調整された前記タイミングを用いて前記第1のプロトコルスタックにおいて前記通信を処理する段階と

を備える方法。

【請求項11】

前記テーブルは、不揮発性メモリに格納されており、前記トンネリングインターコネクトと前記第1のプロトコルスタックとの間のマッピングを含む第1の部分と、前記トンネリングインターコネクトと前記トンネリングインターコネクトに結合されている第2のプロトコルスタックとの間のマッピングを含む第2の部分とを有する

請求項10に記載の方法。

【請求項12】

前記第1のプロトコルスタックと前記第2のプロトコルスタックとの間で前記トンネリングインターコネクトを共有する段階と、

前記第1のプロトコルスタックがあるスロットにおいて通信対象の情報を持たない場合に、前記第2のプロトコルスタックに前記第1のプロトコルスタックの前記スロットを与える段階と

をさらに備える、請求項11に記載の方法。

【請求項13】

前記少なくとも1つのスタックロジックの前記タイミングは、前記少なくとも1つのスタックロジックに結合されているクロックをオフにすることによって調整される

請求項10から12のいずれか1項に記載の方法。

【請求項14】

前記遅延に少なくとも部分的に基づいて、第2のスタックロジックのクロックを遅延させる段階

をさらに備える、請求項13に記載の方法。

【請求項15】

前記クロックを遅延して、予め定められた時間が経過するまで、前記トンネリングインターコネクトによって時間要件が満たされない場合にトリガされる、受信機からの肯定応答を受領していない旨を指し示すエラー信号が発行されないようにする段階

をさらに備える、請求項14に記載の方法。

【請求項16】

リンクに結合されている物理層、および、前記物理層に結合されているプロトコルスタックを有する送信機と、

前記リンクを介して前記送信機に結合されており、第1のプロトコルにしたがってデータを処理する第1のプロトコルスタックを有する受信機と、

前記受信機に結合されているダイナミックランダムアクセスメモリ(DRAM)と

を備え、

前記第1のプロトコルスタックは、トンネリング物理層を介して、前記リンクに前記第1のプロトコルスタックをインターフェースする第1のインターフェースロジックを含み、前記第1のインターフェースロジックは、前記トンネリング物理層によるトンネリングによって発生するタイミング遅延に少なくとも部分的に基づいて、前記第1のプロトコルスタックの少なくとも1つの第1のスタックロジックのタイミングを変更する

システム。

【請求項17】

前記受信機はさらに、第2のプロトコルにしたがってデータを処理する第2のプロトコルスタックを有し、前記第2のプロトコルスタックは、前記タイミング遅延に少なくとも部分的に基づいて前記第2のプロトコルスタックの少なくとも1つの第2のスタックロジックのタイミングを変更する第2のインターフェースロジックを含む

請求項16に記載のシステム。

【請求項18】

前記トンネリング物理層は、前記第1のプロトコルスタックまたは前記第2のプロトコルスタックを選択して前記送信機からのパケットを受信させるコントローラを含む

請求項17に記載のシステム。

【請求項19】

前記第1のインターフェースロジックは、前記トンネリング物理層を介して前記送信機から受信したパケットの通信種類に基づいてテーブルにアクセスして、前記通信種類に対応付けられている、タイミング遅延情報を取得し、前記タイミング遅延情報が示す遅延に対応するべく、前記通信種類について前記第1のプロトコルスタックの前記少なくとも第1のスタックロジックのタイミングを変更するべきか否かを決定する

請求項16から18のいずれか1項に記載のシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−105344(P2012−105344A)

【公開日】平成24年5月31日(2012.5.31)

【国際特許分類】

【出願番号】特願2012−4950(P2012−4950)

【出願日】平成24年1月13日(2012.1.13)

【分割の表示】特願2009−165061(P2009−165061)の分割

【原出願日】平成21年7月13日(2009.7.13)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

【公開日】平成24年5月31日(2012.5.31)

【国際特許分類】

【出願日】平成24年1月13日(2012.1.13)

【分割の表示】特願2009−165061(P2009−165061)の分割

【原出願日】平成21年7月13日(2009.7.13)

【出願人】(591003943)インテル・コーポレーション (1,101)

【Fターム(参考)】

[ Back to top ]