ヘッド分離式カメラ装置

【課題】ヘッドを分離した場合のクロックの確保(リセット)あるいは遠方に設けたヘッドからの信号の遅れに起因するジッタやスキューの影響を低減可能なヘッド分離式カメラ装置および映像信号処理方法を提供する。

【解決手段】この発明のヘッド分離式カメラ装置および映像信号処理方法は、イメージセンサが取得した映像信号をシリアル変換し、シリアル変換して入力される映像信号をパラレル変換し、パラレル変換された映像信号を後段の映像再生部の特性にあわせて規格化する前段で、規格化する回路への書き込みタイミングを、非同期FIFOメモリにより調整することを特徴とする。

【解決手段】この発明のヘッド分離式カメラ装置および映像信号処理方法は、イメージセンサが取得した映像信号をシリアル変換し、シリアル変換して入力される映像信号をパラレル変換し、パラレル変換された映像信号を後段の映像再生部の特性にあわせて規格化する前段で、規格化する回路への書き込みタイミングを、非同期FIFOメモリにより調整することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、ヘッド分離式カメラ装置に係り、特にヘッド(撮像部)を取り外した場合の信号処理および後段への信号出力等の映像信号処理方法に関する。

【背景技術】

【0002】

CMOS(Complementary Metal-oxide Semiconductor)イメージセンサを用いたカメラ装置が広く普及している。なお、今日、ヘッドすなわち撮像部を分離可能としたもの、あるいはヘッドを遠方に設けたもの等が広く実用化されている。

【0003】

特許文献1には、非同期FIFOを用いるビデオカメラが示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−191389号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1は、ヘッド一体型ビデオカメラにおいて、非同期FIFOを備え、駆動処理部の位相調整回路からの駆動信号に基づいて画像信号をFIFOに書き込み、駆動処理部の基準信号発生回路からの基準信号に基づいて、FIFOから読み出しを行うことを開示する。

【0006】

しかしながら、特許文献1では、ヘッド(撮像部)を分離可能とする構造およびヘッドを分離することに起因する信号処理上の特徴については、言及されていない。

【0007】

この発明の目的は、ヘッドを分離した場合のクロックの確保(リセット)あるいは遠方に設けたヘッドからの信号の遅れに起因するジッタやスキューの影響を低減可能なヘッド分離式カメラ装置および映像信号処理方法を提供することである。

【課題を解決するための手段】

【0008】

この発明は、上記問題点に基づきなされたもので、撮像部と撮像部を制御する制御部とがケーブルにより接続されたヘッド分離式カメラ装置において、制御部より撮像部へ送出した駆動信号により撮像部が含む画像センサを制御し、その画像センサから出力されるクロック信号や同期信号を含む映像信号を制御部で受け取り、非同期FIFOメモリを伴った信号処理回路を経て規格化された映像信号に変換して出力することを特徴とするヘッド分離式カメラ装置を提供するものである。

【発明の効果】

【0009】

この発明の一つの実施の形態は、制御部と撮像部(カメラヘッド)との間、あるいは撮像部と制御部との間に実装される部品のバラツキやケーブルの長さによるスキューやジッタ特性に影響を受けることの無いヘッド分離型カメラシステムを得ることができる。

【0010】

また、フレームメモリのような容量の大きなメモリを必要とせずに、DVIやHD−SDIといった規格化された高速デジタル信号を生成する上で、ジッタ性能が改善され安定したデジタル信号の生成が可能となる。

【0011】

なお、撮像部を分離した場合のFIFOのリセット信号は、本実施の形態において、特に有益である。

【図面の簡単な説明】

【0012】

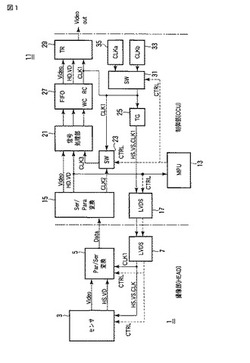

【図1】この発明の実施の形態が適用可能なヘッド分離式カメラ装置の構成の一例を示す概略図。

【図2】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更した構成の一例を示す概略図。

【図3】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更した別の構成の一例を示す概略図。

【図4】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更したさらに別の構成の一例を示す概略図。

【図5】図4に示したヘッド分離式カメラ装置において、リセット(状態変化に対するMPUからFIFOおよび信号処理回路の制御例)タイミングの一例を説明する概略図。

【図6】図1ないし図4に示したヘッド分離式カメラ装置において、カメラの出力解像度やフレームレートを切換える際、あるいは撮像部と制御部を接続するケーブルの挿抜(抜き差し)に関連するリセットタイミングを説明する概略図。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施の一形態について説明する。

【0014】

図1は、この発明を適用したヘッド分離式カメラ装置を示す。なお、以下に「モジュール」と呼称する要素は、ハードウエアで実現するものであってもよいし、CPU(マイクロコンピュータ)等を用いてソフトウエアで実現するものであってもよい。

【0015】

図1に示すヘッド分離式カメラ装置は、撮像部(ヘッド)すなわち撮像モジュール1と制御部(CCU)すなわち制御モジュール11を含む。

【0016】

撮像モジュール1は、CMOS(Complementary Metal-oxide Semiconductor)イメージセンサ3、パラレル−シリアル変換回路5、パラレル−シリアル変換回路5と並列に用意されたLVDS(Low Voltage Differential Signaling)回路7を含む。

【0017】

制御モジュール11は、主制御ブロック(MPU)13、シリアル−パラレル変換回路15、LVDS(Complementary Metal-oxide Semiconductor)回路17、信号処理部21、クロック切り替え器(SW1)23、タイミングジェネレータ(TG)すなわちセンサ駆動信号発生回路25、非同期FIFOメモリ27、トランスミッタ(TR)すなわち出力ドライバ回路29、クロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33、および第2クロックモジュール(CLKa)35を、含む。なお、第1および第2クロックモジュール33、35は、第2クロックモジュール(CLKa)35の発振周波数が60Hzである場合、第1クロックモジュール(CLKb)33の発振周波数が60×1000/1001=59.94Hzである。

【0018】

クロック切り替え器(SW1)23およびクロック切り替え器(SW2)31は、MPU13からのCTRL(コントロール)信号により、第2クロックモジュール(CLKa)35からのクロックを用いるか、第1クロックモジュール(CLKb)33からのクロックを用いるかが選択される。なお、同CTRL(コントロール)信号は、制御モジュール11側のLVDS17およびヘッド(撮像モジュール1)側のLVDS7およびヘッド側のパラレル−シリアル変換回路5にも供給される。また、CTRLは、例えばi2cバスや、3線シリアルバス等を用いることを前提としている。

【0019】

図1に示すヘッド分離式カメラ装置においては、LVDS17、LVDS7を通じて供給されるCLK1(CLK)とCTRL(HS(水平同期)、VS(垂直同期))によりセンサ3による撮像開始が指示され、センサ3から映像信号(Video)、水平方向制御データ(HD)および垂直方向制御データ(VD)が出力される。

【0020】

センサ3からの映像信号(Video)、HDおよびVDは、パラレル−シリアル変換回路5でシリアル変換され、制御モジュール11側のシリアル−パラレル変換回路15へ入力される。

【0021】

シリアル−パラレル変換回路15は、クロック切り替え器(SW1)23により選択されたCLK3(クロック切り替え器(SW2)31によりCKLa35またはCLKb33の一方からのクロックが選択されたCLK1とシリアル−パラレル変換回路15から供給されるCLK2の一方が選択されたクロック)のもとで、信号処理部21へ、映像信号(Video)、HDおよびVDを出力する。

【0022】

信号処理部21は、上述のCLK3のもとで、非同期FIFOメモリ回路(先入れ先出しメモリ)27へ、映像信号(Video)、HDおよびVDを書き込む。

【0023】

一方、FIFOメモリ27からトランスミッタ(TR)すなわち出力ドライバ回路29へは、クロック切り替え器(SW2)31からのCLK1により、映像信号(Video)、HDおよびVDが出力される。すなわち、FIFOメモリ27からトランスミッタ(TR)すなわち出力ドライバ回路29へ読み出す映像信号(Video)、HDおよびVDは、信号処理部21へ供給されるCLK3とは異なる、撮像部駆動信号生成用CLK(クロック切り替え器(SW2)31によりCKLa35またはCLKb33の一方からのクロックが選択されたCLK1)により、読み出される。これにより、例えばヘッド(撮像部)1から供給される映像信号(Video)、HDおよびVDが、ヘッド1と制御モジュール11との間の距離に起因して、ジッタ成分やスキュー成分を伴っていた場合であっても、TR(出力ドライバ回路)29から出力される映像出力(Video out)は、ジッタ成分あるいはスキュー成分が除去された映像信号となる。

【0024】

より詳細には、FIFOメモリ27を持たない一般的な構成においても、制御部11でセンサ駆動信号の生成が行われ、撮像部1を介して戻ってきたCLK信号に同期して映像信号を処理することは同様であり、撮像部1と制御部11との間にあるケーブル(配線)の長さが長くなるにつれて位相差が発生するが、撮像部1から戻ってきたCLK信号と映像信号は同期しているため、そのまま信号処理に使用することでケーブルの長さによって変化する位相差に対処できる利点がある。

【0025】

反面、制御部11で生成したCLK信号は、制御部11から出力され、撮像部1を経て再び制御部11に戻ってくる際に、複数の部品を経由するためにジッタ成分が増加した状態となる。特に、ヘッド分離式カメラ装置においては、撮像部1から制御部11へ撮像した信号を伝送するにあたってケーブルの本数を削減するためにパラレル−シリアル変換回路5によりシリアル変換し、シリアル−パラレル変換回路15によりパラレル変換して伝送する場合が多く、このようなケースでは、撮像部1のパラレル−シリアル変換回路5、制御部11のシリアル−パラレル変換回路15において高速なデジタル信号の変換処理を行うPLL回路の介在に起因して、ジッタ成分が大きくなる。

【0026】

ジッタ成分は、信号処理に(直接的な)影響はないが、近年広く利用されているDVI(Digital Visual Interface)規格やSDI(Serial Digital Interface)規格をはじめとする映像信号は、高速なシリアルデジタル差動信号から成っており、これらの信号に、ジッタ量が規格化されている。この規格値を満たすため、ジッタを軽減する必要性がある。

【0027】

従って、上述の通り、信号処理部21の後に、FIFOメモリ回路27(先入れ先出しメモリ)を追加して、撮像部から戻ってきた信号処理に使用されたCLKでFIFOメモリ27に映像信号(Video)、H(HD)/V(VD)信号、必要に応じて映像データ期間を示すFLD(フィールド期間)信号やDATA ENABLE(データエナーブル)信号を書き込み、センサ駆動信号生成の際に使用される安定的なCLK信号から生成した書き込みCLKと同一周波数のCLK信号を使ってFIFOメモリ27から映像信号および付随する信号をリードし、そのデータをDVIやSDI信号へ変換するICに送信する。これによって、より安定的なCLK信号と映像信号を提供することができる。

【0028】

図2は、図1に示すヘッド分離式カメラ装置における信号処理を変形した例を示し、信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、非同期FIFOメモリ27を挿入する例を示す。なお、映像出力器TXは、一般に送信機としての意味を持つが、図1に示したTR(すなわち出力ドライバ回路)と実質的に同一である(後段に映像出力を送信するという意味で送信機(TX)と称されることがある)。

【0029】

図2における特徴の1つは、発振器として簡略化して示したクロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33および第2クロックモジュール(CLKa)35からのCLK1を、FIFOメモリ27に対するリセットクロックRCLKとして用いる点である。例えば、ヘッド(撮像モジュール)1とCCUすなわち制御モジュール11との間の距離が大きい(ヘッド1が離れた位置に設けられている)場合においては、信号処理部21に映像信号(Video)、HDおよびVDが入力される時点で、ジッタ成分やスキュー成分が無視できない程度に増大されている場合があるため、信号処理部21へ入力する前段で、FIFOメモリ27を用い、ジッタ成分を予め除去することで、後段に出力される映像信号から、ヘッド1とCCU11との間の距離の影響を低減できる。この場合も、FIFOメモリ27へ書き込むCLK信号は、シリアル−パラレル変換後のCLK信号であり、読み出すCLKは、そのCLK信号と同じ周波数のCLK信号で制御部側で生成された発信器(クロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33および第2クロックモジュール(CLKa)35からのCLK1)により生成された信号である。

【0030】

図3は、図2に示すヘッド分離式カメラ装置を、3板式の撮像系(ヘッドがR,G,Bのそれぞれの色成分に対して、独立したCMOSセンサを用いる系)とした例を示す。

【0031】

すなわち、3板式の撮像系(ヘッドがR,G,Bのそれぞれの色成分に対して、独立したCMOSセンサを用いる系)において、ヘッド1とCCU11との間の距離以外に、各CMOSセンサからの信号の遅延等を考慮すべきであり、特に信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、非同期FIFOメモリ27を位置して、信号処理部21へ入力される映像信号から、予めジッタ成分やスキュー成分を除去することが有益である。

【0032】

すなわち、複数のセンサや複数のシリアル化されたLVDS信号を受信するシステムにおいて、各chの信号処理の入力側にFIFOメモリ27を追加することで、ケーブルが長い場合に発生するch間のスキューによりタイミングがずれるのに対して、一定のタイミングで信号処理を行うことができるためジッタやスキューが軽減される。

【0033】

図4は、図1に示すヘッド分離式カメラ装置における信号処理をさらに変形した例を示し、信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、第1のPLL(Phase Loop Lock)回路37と第2のPLL(Phase Loop Lock)回路39を設け、クロック切り替え器(SW2)31により、Xtal1(CKLaに相当)35またはXtal2(Xtal1のリバース)33の一方からのクロックが選択されたCLK(TG25、PLL(1)37,PLL(2)39に供給)と、信号処理部21の前段に設けたクロック切り替え器(SW1)23により、例えばヘッド(撮像部)1が切り離された場合の無信号(クロックなし)状態においても、後段に、映像出力(Video)、HDおよびVD(H/V)を、安定に出力するために有益である。

【0034】

より詳細には、ヘッド分離型カメラシステムでは、ケーブルが外れることにより無信号状態が発生する。また、複数の解像度で撮像できるカメラシステムがある。このように、カメラの出力解像度やフレームレートを切換える際、あるいは撮像部1と制御部11を接続するケーブルの挿抜(抜き差し)が行われた場合にはセンサ(ヘッド1)の駆動タイミングが変化するため、一時的に制御部が受け取るCLK信号が不安定となり、FIFOメモリ27の誤動作や、FIFOメモリ27への書き込みCLKの周波数と読み込みCLKの周波数が乱れ、エンプティやオーバーフロー状態となる可能性がある。

【0035】

このため、こうした操作が行われた後にFIFOメモリ27から正しい映像信号が読み出されなくなる場合があり、DVIやSDI出力のドライバICが誤動作する等、映像がでなくなる可能性がある。

【0036】

ここで、上述のように、CLK信号のPLL回路(1),(2)にRESET信号を設け、PLL回路(1),(2)からLOCK状態を示す信号出力を設ける。以下、発振器(SW(2)31を経由したXtal(1)35またはXtal(2)33の出力)のLOCK状態を示す信号を利用してFIFOメモリ27のRESETを行う。

【0037】

これによって、解像度やフレームレートの切換え時に発生する周波数乱れや、ケーブル挿抜による一時的な無信号状態の期間については、FIFOメモリ27をRESET状態として映像出力を停止させ、PLL回路(1),(2)が安定化状態となったらFIFOメモリ27のRESETを解除し、映像信号の出力を再開する。

【0038】

図5に、図4に説明した状態変化に対するMPUからFIFOおよび信号処理回路の制御例を示す。図5に(図4の)要部を抜き出して説明するが、ケーブル状態(ヘッドの取り外しの有無)に応じて、CLKi(内部クロック)すなわちPLL(1)37からFIF027にリセット信号RSTを供給するよう、マイコン(図4に示したホストI/FまたはGPIOあるいは図1のMPU13)が供給するCLKの手順を設定(固定)することにより、カメラヘッド側であるPLL2に入力されるCLKeが検出できない(安定していない)場合であっても、安定な動作が得られる(図5(a)参照)。

【0039】

また、図5(b)に示すように、CLKi(内部クロック)すなわちPLL(1)37とCLKeすなわちPLL(2)39のANDを取ることにより、マイコン(図4に示したホストI/FまたはGPIOあるいは図1のMPU13)からCLKを選択する工程が不要となる。なお、図5(b)の例では、(ヘッド1側からの)ケーブルの着脱(カメラヘッドの分離(取り外し)の有無)に従い、例えばヘッド無し:PLL2を使用/ヘッド有り:PLL2を非使用、と切り替えることになる。

【0040】

すなわち、RESET(リセット)を実行する場合には、安定的な内部CLK(駆動信号生成用CLK)での動作に切り換えたのち、PLLをRESET(リセット)する。各設定を行い、内部回路の経路を確定させ、再びPLL回路のRESETを行う。これにより、PLL回路が安定化するとLOCK状態を示す信号が出力され、撮像部(ヘッド)1の有無や、設定に関係なくFIFOメモリ27は正常動作を開始し、映像信号(Video)、HD、VDの出力が再開される。

【0041】

なお、図6に一例を示すが、MPU13からカメラヘッド1の有無に伴うリセット(HEAD DETECT<<撮像部(HEAD有→無)>>、<<撮像部(HEAD無→有)>>)、<<フレームレート(FRAME RATE)切り換え>>、<<解像度(RESOLUTION)切り換え>>、<<走査モード(IP MODE)切り換え>>を制御信号を経由して通知するようにし、これに応じて内部回路のCLK信号や映像信号の経路を切換えるとともに、外部からRESET(リセット)制御を行うことで、PLL回路(1)、(2)のRESET処理を行うことができる。

【0042】

より詳細には、図6において、HEAD DETECT<<撮像部(HEAD有→無)>>の場合は、内部CLKへ切り換え([11])、PLLリセット([12])、PLL安定待ち([13])、PLL安定([14])の処理に続いて、FIFOメモリ27のRESETを解除し、映像信号(Video)、HD、VDの出力を再開すればよい。

【0043】

また、HEAD DETECT<<撮像部(HEAD無→有)>>については、内部CLKへ切り換え([21])、PLLリセット([22])に続いて、RESOLUTION(解像度)設定([23])、FRAME RATE(フレームレート)設定([24])、IP MODE(走査モード)設定([25])、を実行し、PLLリセット([26])、PLL安定待ち([27])、PLL安定([28])の処理に続いて、FIFOメモリ27のRESETを解除し、映像信号(Video)、HD、VDの出力を再開すればよい。

【0044】

なお、<<フレームレート(FRAME RATE)切り換え>>、<<解像度(RESOLUTION)切り換え>>、あるいは<<走査モード(IP MODE)切り換え>>については、HEAD DETECT<<撮像部(HEAD無→有)>>の一部を省略した手順と実質的に同等であるから詳細な説明を省略する。

【0045】

以上説明したように、この発明の実施の一形態を適用することにより、部品やケーブルのバラツキによって発生するスキューやジッタを吸収することで安定したデジタル信号を出力できるため、DVIやHD−SDIといった高速デジタル信号を生成する際のジッタが改善され安定したデジタル信号の生成が可能となる。

【0046】

また、ヘッドを分離した場合のクロックの確保(リセット)あるいは遠方に設けたヘッドからの信号の遅れに起因するジッタやスキューの影響を低減可能なヘッド分離式カメラ装置が実現できる。

【0047】

また、フレームメモリのような容量の大きなメモリを必要とせずに、DVIやHD−SDIといった規格化された高速デジタル信号を生成する上で、ジッタ性能が改善され安定したデジタル信号の生成が可能となる。

【0048】

なお、この発明は、上述した各実施の形態に限定されるものではなく、その実施の段階ではその要旨を逸脱しない範囲で種々な変形もしくは変更が可能である。また、各実施の形態は、可能な限り適宜組み合わせて、もしくは一部を削除して実施されてもよく、その場合は、組み合わせもしくは削除に起因したさまざまな効果が得られる。

【符号の説明】

【0049】

1…撮像モジュール(ヘッド/カメラ)、3…CMOS(Complementary Metal-oxide Semiconductor)イメージセンサ、5…パラレル−シリアル変換回路、7…LVDS(Low Voltage Differential Signaling)回路、11…制御(CCU)モジュール、13…主制御ブロック(MPU)、15…シリアル−パラレル変換回路、17…LVDS回路、21…信号処理部、23…クロック切り替え器(SW1)、25…タイミングジェネレータ(センサ駆動信号発生回路)、27…非同期FIFOメモリ、29…トランスミッタ(出力ドライバ回路)、31…クロック切り替え器(SW2)、33…第1クロックモジュール(CLKb/Xtal1)、35…第2クロックモジュール(CLKa/Xtal1)、37…PLL(Phase Loop Lock)回路(1)、39…PLL回路(2)。

【技術分野】

【0001】

この発明は、ヘッド分離式カメラ装置に係り、特にヘッド(撮像部)を取り外した場合の信号処理および後段への信号出力等の映像信号処理方法に関する。

【背景技術】

【0002】

CMOS(Complementary Metal-oxide Semiconductor)イメージセンサを用いたカメラ装置が広く普及している。なお、今日、ヘッドすなわち撮像部を分離可能としたもの、あるいはヘッドを遠方に設けたもの等が広く実用化されている。

【0003】

特許文献1には、非同期FIFOを用いるビデオカメラが示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−191389号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1は、ヘッド一体型ビデオカメラにおいて、非同期FIFOを備え、駆動処理部の位相調整回路からの駆動信号に基づいて画像信号をFIFOに書き込み、駆動処理部の基準信号発生回路からの基準信号に基づいて、FIFOから読み出しを行うことを開示する。

【0006】

しかしながら、特許文献1では、ヘッド(撮像部)を分離可能とする構造およびヘッドを分離することに起因する信号処理上の特徴については、言及されていない。

【0007】

この発明の目的は、ヘッドを分離した場合のクロックの確保(リセット)あるいは遠方に設けたヘッドからの信号の遅れに起因するジッタやスキューの影響を低減可能なヘッド分離式カメラ装置および映像信号処理方法を提供することである。

【課題を解決するための手段】

【0008】

この発明は、上記問題点に基づきなされたもので、撮像部と撮像部を制御する制御部とがケーブルにより接続されたヘッド分離式カメラ装置において、制御部より撮像部へ送出した駆動信号により撮像部が含む画像センサを制御し、その画像センサから出力されるクロック信号や同期信号を含む映像信号を制御部で受け取り、非同期FIFOメモリを伴った信号処理回路を経て規格化された映像信号に変換して出力することを特徴とするヘッド分離式カメラ装置を提供するものである。

【発明の効果】

【0009】

この発明の一つの実施の形態は、制御部と撮像部(カメラヘッド)との間、あるいは撮像部と制御部との間に実装される部品のバラツキやケーブルの長さによるスキューやジッタ特性に影響を受けることの無いヘッド分離型カメラシステムを得ることができる。

【0010】

また、フレームメモリのような容量の大きなメモリを必要とせずに、DVIやHD−SDIといった規格化された高速デジタル信号を生成する上で、ジッタ性能が改善され安定したデジタル信号の生成が可能となる。

【0011】

なお、撮像部を分離した場合のFIFOのリセット信号は、本実施の形態において、特に有益である。

【図面の簡単な説明】

【0012】

【図1】この発明の実施の形態が適用可能なヘッド分離式カメラ装置の構成の一例を示す概略図。

【図2】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更した構成の一例を示す概略図。

【図3】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更した別の構成の一例を示す概略図。

【図4】図1に示したヘッド分離式カメラ装置において、FIFOメモリの位置を変更したさらに別の構成の一例を示す概略図。

【図5】図4に示したヘッド分離式カメラ装置において、リセット(状態変化に対するMPUからFIFOおよび信号処理回路の制御例)タイミングの一例を説明する概略図。

【図6】図1ないし図4に示したヘッド分離式カメラ装置において、カメラの出力解像度やフレームレートを切換える際、あるいは撮像部と制御部を接続するケーブルの挿抜(抜き差し)に関連するリセットタイミングを説明する概略図。

【発明を実施するための形態】

【0013】

以下、図面を参照して、本発明の実施の一形態について説明する。

【0014】

図1は、この発明を適用したヘッド分離式カメラ装置を示す。なお、以下に「モジュール」と呼称する要素は、ハードウエアで実現するものであってもよいし、CPU(マイクロコンピュータ)等を用いてソフトウエアで実現するものであってもよい。

【0015】

図1に示すヘッド分離式カメラ装置は、撮像部(ヘッド)すなわち撮像モジュール1と制御部(CCU)すなわち制御モジュール11を含む。

【0016】

撮像モジュール1は、CMOS(Complementary Metal-oxide Semiconductor)イメージセンサ3、パラレル−シリアル変換回路5、パラレル−シリアル変換回路5と並列に用意されたLVDS(Low Voltage Differential Signaling)回路7を含む。

【0017】

制御モジュール11は、主制御ブロック(MPU)13、シリアル−パラレル変換回路15、LVDS(Complementary Metal-oxide Semiconductor)回路17、信号処理部21、クロック切り替え器(SW1)23、タイミングジェネレータ(TG)すなわちセンサ駆動信号発生回路25、非同期FIFOメモリ27、トランスミッタ(TR)すなわち出力ドライバ回路29、クロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33、および第2クロックモジュール(CLKa)35を、含む。なお、第1および第2クロックモジュール33、35は、第2クロックモジュール(CLKa)35の発振周波数が60Hzである場合、第1クロックモジュール(CLKb)33の発振周波数が60×1000/1001=59.94Hzである。

【0018】

クロック切り替え器(SW1)23およびクロック切り替え器(SW2)31は、MPU13からのCTRL(コントロール)信号により、第2クロックモジュール(CLKa)35からのクロックを用いるか、第1クロックモジュール(CLKb)33からのクロックを用いるかが選択される。なお、同CTRL(コントロール)信号は、制御モジュール11側のLVDS17およびヘッド(撮像モジュール1)側のLVDS7およびヘッド側のパラレル−シリアル変換回路5にも供給される。また、CTRLは、例えばi2cバスや、3線シリアルバス等を用いることを前提としている。

【0019】

図1に示すヘッド分離式カメラ装置においては、LVDS17、LVDS7を通じて供給されるCLK1(CLK)とCTRL(HS(水平同期)、VS(垂直同期))によりセンサ3による撮像開始が指示され、センサ3から映像信号(Video)、水平方向制御データ(HD)および垂直方向制御データ(VD)が出力される。

【0020】

センサ3からの映像信号(Video)、HDおよびVDは、パラレル−シリアル変換回路5でシリアル変換され、制御モジュール11側のシリアル−パラレル変換回路15へ入力される。

【0021】

シリアル−パラレル変換回路15は、クロック切り替え器(SW1)23により選択されたCLK3(クロック切り替え器(SW2)31によりCKLa35またはCLKb33の一方からのクロックが選択されたCLK1とシリアル−パラレル変換回路15から供給されるCLK2の一方が選択されたクロック)のもとで、信号処理部21へ、映像信号(Video)、HDおよびVDを出力する。

【0022】

信号処理部21は、上述のCLK3のもとで、非同期FIFOメモリ回路(先入れ先出しメモリ)27へ、映像信号(Video)、HDおよびVDを書き込む。

【0023】

一方、FIFOメモリ27からトランスミッタ(TR)すなわち出力ドライバ回路29へは、クロック切り替え器(SW2)31からのCLK1により、映像信号(Video)、HDおよびVDが出力される。すなわち、FIFOメモリ27からトランスミッタ(TR)すなわち出力ドライバ回路29へ読み出す映像信号(Video)、HDおよびVDは、信号処理部21へ供給されるCLK3とは異なる、撮像部駆動信号生成用CLK(クロック切り替え器(SW2)31によりCKLa35またはCLKb33の一方からのクロックが選択されたCLK1)により、読み出される。これにより、例えばヘッド(撮像部)1から供給される映像信号(Video)、HDおよびVDが、ヘッド1と制御モジュール11との間の距離に起因して、ジッタ成分やスキュー成分を伴っていた場合であっても、TR(出力ドライバ回路)29から出力される映像出力(Video out)は、ジッタ成分あるいはスキュー成分が除去された映像信号となる。

【0024】

より詳細には、FIFOメモリ27を持たない一般的な構成においても、制御部11でセンサ駆動信号の生成が行われ、撮像部1を介して戻ってきたCLK信号に同期して映像信号を処理することは同様であり、撮像部1と制御部11との間にあるケーブル(配線)の長さが長くなるにつれて位相差が発生するが、撮像部1から戻ってきたCLK信号と映像信号は同期しているため、そのまま信号処理に使用することでケーブルの長さによって変化する位相差に対処できる利点がある。

【0025】

反面、制御部11で生成したCLK信号は、制御部11から出力され、撮像部1を経て再び制御部11に戻ってくる際に、複数の部品を経由するためにジッタ成分が増加した状態となる。特に、ヘッド分離式カメラ装置においては、撮像部1から制御部11へ撮像した信号を伝送するにあたってケーブルの本数を削減するためにパラレル−シリアル変換回路5によりシリアル変換し、シリアル−パラレル変換回路15によりパラレル変換して伝送する場合が多く、このようなケースでは、撮像部1のパラレル−シリアル変換回路5、制御部11のシリアル−パラレル変換回路15において高速なデジタル信号の変換処理を行うPLL回路の介在に起因して、ジッタ成分が大きくなる。

【0026】

ジッタ成分は、信号処理に(直接的な)影響はないが、近年広く利用されているDVI(Digital Visual Interface)規格やSDI(Serial Digital Interface)規格をはじめとする映像信号は、高速なシリアルデジタル差動信号から成っており、これらの信号に、ジッタ量が規格化されている。この規格値を満たすため、ジッタを軽減する必要性がある。

【0027】

従って、上述の通り、信号処理部21の後に、FIFOメモリ回路27(先入れ先出しメモリ)を追加して、撮像部から戻ってきた信号処理に使用されたCLKでFIFOメモリ27に映像信号(Video)、H(HD)/V(VD)信号、必要に応じて映像データ期間を示すFLD(フィールド期間)信号やDATA ENABLE(データエナーブル)信号を書き込み、センサ駆動信号生成の際に使用される安定的なCLK信号から生成した書き込みCLKと同一周波数のCLK信号を使ってFIFOメモリ27から映像信号および付随する信号をリードし、そのデータをDVIやSDI信号へ変換するICに送信する。これによって、より安定的なCLK信号と映像信号を提供することができる。

【0028】

図2は、図1に示すヘッド分離式カメラ装置における信号処理を変形した例を示し、信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、非同期FIFOメモリ27を挿入する例を示す。なお、映像出力器TXは、一般に送信機としての意味を持つが、図1に示したTR(すなわち出力ドライバ回路)と実質的に同一である(後段に映像出力を送信するという意味で送信機(TX)と称されることがある)。

【0029】

図2における特徴の1つは、発振器として簡略化して示したクロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33および第2クロックモジュール(CLKa)35からのCLK1を、FIFOメモリ27に対するリセットクロックRCLKとして用いる点である。例えば、ヘッド(撮像モジュール)1とCCUすなわち制御モジュール11との間の距離が大きい(ヘッド1が離れた位置に設けられている)場合においては、信号処理部21に映像信号(Video)、HDおよびVDが入力される時点で、ジッタ成分やスキュー成分が無視できない程度に増大されている場合があるため、信号処理部21へ入力する前段で、FIFOメモリ27を用い、ジッタ成分を予め除去することで、後段に出力される映像信号から、ヘッド1とCCU11との間の距離の影響を低減できる。この場合も、FIFOメモリ27へ書き込むCLK信号は、シリアル−パラレル変換後のCLK信号であり、読み出すCLKは、そのCLK信号と同じ周波数のCLK信号で制御部側で生成された発信器(クロック切り替え器(SW2)31、第1クロックモジュール(CLKb)33および第2クロックモジュール(CLKa)35からのCLK1)により生成された信号である。

【0030】

図3は、図2に示すヘッド分離式カメラ装置を、3板式の撮像系(ヘッドがR,G,Bのそれぞれの色成分に対して、独立したCMOSセンサを用いる系)とした例を示す。

【0031】

すなわち、3板式の撮像系(ヘッドがR,G,Bのそれぞれの色成分に対して、独立したCMOSセンサを用いる系)において、ヘッド1とCCU11との間の距離以外に、各CMOSセンサからの信号の遅延等を考慮すべきであり、特に信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、非同期FIFOメモリ27を位置して、信号処理部21へ入力される映像信号から、予めジッタ成分やスキュー成分を除去することが有益である。

【0032】

すなわち、複数のセンサや複数のシリアル化されたLVDS信号を受信するシステムにおいて、各chの信号処理の入力側にFIFOメモリ27を追加することで、ケーブルが長い場合に発生するch間のスキューによりタイミングがずれるのに対して、一定のタイミングで信号処理を行うことができるためジッタやスキューが軽減される。

【0033】

図4は、図1に示すヘッド分離式カメラ装置における信号処理をさらに変形した例を示し、信号処理部21の前段(シリアル−パラレル変換回路15と信号処理部21との間)に、第1のPLL(Phase Loop Lock)回路37と第2のPLL(Phase Loop Lock)回路39を設け、クロック切り替え器(SW2)31により、Xtal1(CKLaに相当)35またはXtal2(Xtal1のリバース)33の一方からのクロックが選択されたCLK(TG25、PLL(1)37,PLL(2)39に供給)と、信号処理部21の前段に設けたクロック切り替え器(SW1)23により、例えばヘッド(撮像部)1が切り離された場合の無信号(クロックなし)状態においても、後段に、映像出力(Video)、HDおよびVD(H/V)を、安定に出力するために有益である。

【0034】

より詳細には、ヘッド分離型カメラシステムでは、ケーブルが外れることにより無信号状態が発生する。また、複数の解像度で撮像できるカメラシステムがある。このように、カメラの出力解像度やフレームレートを切換える際、あるいは撮像部1と制御部11を接続するケーブルの挿抜(抜き差し)が行われた場合にはセンサ(ヘッド1)の駆動タイミングが変化するため、一時的に制御部が受け取るCLK信号が不安定となり、FIFOメモリ27の誤動作や、FIFOメモリ27への書き込みCLKの周波数と読み込みCLKの周波数が乱れ、エンプティやオーバーフロー状態となる可能性がある。

【0035】

このため、こうした操作が行われた後にFIFOメモリ27から正しい映像信号が読み出されなくなる場合があり、DVIやSDI出力のドライバICが誤動作する等、映像がでなくなる可能性がある。

【0036】

ここで、上述のように、CLK信号のPLL回路(1),(2)にRESET信号を設け、PLL回路(1),(2)からLOCK状態を示す信号出力を設ける。以下、発振器(SW(2)31を経由したXtal(1)35またはXtal(2)33の出力)のLOCK状態を示す信号を利用してFIFOメモリ27のRESETを行う。

【0037】

これによって、解像度やフレームレートの切換え時に発生する周波数乱れや、ケーブル挿抜による一時的な無信号状態の期間については、FIFOメモリ27をRESET状態として映像出力を停止させ、PLL回路(1),(2)が安定化状態となったらFIFOメモリ27のRESETを解除し、映像信号の出力を再開する。

【0038】

図5に、図4に説明した状態変化に対するMPUからFIFOおよび信号処理回路の制御例を示す。図5に(図4の)要部を抜き出して説明するが、ケーブル状態(ヘッドの取り外しの有無)に応じて、CLKi(内部クロック)すなわちPLL(1)37からFIF027にリセット信号RSTを供給するよう、マイコン(図4に示したホストI/FまたはGPIOあるいは図1のMPU13)が供給するCLKの手順を設定(固定)することにより、カメラヘッド側であるPLL2に入力されるCLKeが検出できない(安定していない)場合であっても、安定な動作が得られる(図5(a)参照)。

【0039】

また、図5(b)に示すように、CLKi(内部クロック)すなわちPLL(1)37とCLKeすなわちPLL(2)39のANDを取ることにより、マイコン(図4に示したホストI/FまたはGPIOあるいは図1のMPU13)からCLKを選択する工程が不要となる。なお、図5(b)の例では、(ヘッド1側からの)ケーブルの着脱(カメラヘッドの分離(取り外し)の有無)に従い、例えばヘッド無し:PLL2を使用/ヘッド有り:PLL2を非使用、と切り替えることになる。

【0040】

すなわち、RESET(リセット)を実行する場合には、安定的な内部CLK(駆動信号生成用CLK)での動作に切り換えたのち、PLLをRESET(リセット)する。各設定を行い、内部回路の経路を確定させ、再びPLL回路のRESETを行う。これにより、PLL回路が安定化するとLOCK状態を示す信号が出力され、撮像部(ヘッド)1の有無や、設定に関係なくFIFOメモリ27は正常動作を開始し、映像信号(Video)、HD、VDの出力が再開される。

【0041】

なお、図6に一例を示すが、MPU13からカメラヘッド1の有無に伴うリセット(HEAD DETECT<<撮像部(HEAD有→無)>>、<<撮像部(HEAD無→有)>>)、<<フレームレート(FRAME RATE)切り換え>>、<<解像度(RESOLUTION)切り換え>>、<<走査モード(IP MODE)切り換え>>を制御信号を経由して通知するようにし、これに応じて内部回路のCLK信号や映像信号の経路を切換えるとともに、外部からRESET(リセット)制御を行うことで、PLL回路(1)、(2)のRESET処理を行うことができる。

【0042】

より詳細には、図6において、HEAD DETECT<<撮像部(HEAD有→無)>>の場合は、内部CLKへ切り換え([11])、PLLリセット([12])、PLL安定待ち([13])、PLL安定([14])の処理に続いて、FIFOメモリ27のRESETを解除し、映像信号(Video)、HD、VDの出力を再開すればよい。

【0043】

また、HEAD DETECT<<撮像部(HEAD無→有)>>については、内部CLKへ切り換え([21])、PLLリセット([22])に続いて、RESOLUTION(解像度)設定([23])、FRAME RATE(フレームレート)設定([24])、IP MODE(走査モード)設定([25])、を実行し、PLLリセット([26])、PLL安定待ち([27])、PLL安定([28])の処理に続いて、FIFOメモリ27のRESETを解除し、映像信号(Video)、HD、VDの出力を再開すればよい。

【0044】

なお、<<フレームレート(FRAME RATE)切り換え>>、<<解像度(RESOLUTION)切り換え>>、あるいは<<走査モード(IP MODE)切り換え>>については、HEAD DETECT<<撮像部(HEAD無→有)>>の一部を省略した手順と実質的に同等であるから詳細な説明を省略する。

【0045】

以上説明したように、この発明の実施の一形態を適用することにより、部品やケーブルのバラツキによって発生するスキューやジッタを吸収することで安定したデジタル信号を出力できるため、DVIやHD−SDIといった高速デジタル信号を生成する際のジッタが改善され安定したデジタル信号の生成が可能となる。

【0046】

また、ヘッドを分離した場合のクロックの確保(リセット)あるいは遠方に設けたヘッドからの信号の遅れに起因するジッタやスキューの影響を低減可能なヘッド分離式カメラ装置が実現できる。

【0047】

また、フレームメモリのような容量の大きなメモリを必要とせずに、DVIやHD−SDIといった規格化された高速デジタル信号を生成する上で、ジッタ性能が改善され安定したデジタル信号の生成が可能となる。

【0048】

なお、この発明は、上述した各実施の形態に限定されるものではなく、その実施の段階ではその要旨を逸脱しない範囲で種々な変形もしくは変更が可能である。また、各実施の形態は、可能な限り適宜組み合わせて、もしくは一部を削除して実施されてもよく、その場合は、組み合わせもしくは削除に起因したさまざまな効果が得られる。

【符号の説明】

【0049】

1…撮像モジュール(ヘッド/カメラ)、3…CMOS(Complementary Metal-oxide Semiconductor)イメージセンサ、5…パラレル−シリアル変換回路、7…LVDS(Low Voltage Differential Signaling)回路、11…制御(CCU)モジュール、13…主制御ブロック(MPU)、15…シリアル−パラレル変換回路、17…LVDS回路、21…信号処理部、23…クロック切り替え器(SW1)、25…タイミングジェネレータ(センサ駆動信号発生回路)、27…非同期FIFOメモリ、29…トランスミッタ(出力ドライバ回路)、31…クロック切り替え器(SW2)、33…第1クロックモジュール(CLKb/Xtal1)、35…第2クロックモジュール(CLKa/Xtal1)、37…PLL(Phase Loop Lock)回路(1)、39…PLL回路(2)。

【特許請求の範囲】

【請求項1】

撮像部と撮像部を制御する制御部とがケーブルにより接続されたヘッド分離式カメラ装置において、

制御部より撮像部へ送出した駆動信号により撮像部が含む画像センサを制御し、その画像センサから出力されるクロック信号や同期信号を含む映像信号を制御部で受け取り、非同期FIFOメモリを伴った信号処理回路を経て規格化された映像信号に変換して出力することを特徴とするヘッド分離式カメラ装置。

【請求項2】

前記非同期FIFOメモリは、前記信号処理回路の前段に位置することを特徴とする請求項1記載のヘッド分離式カメラ装置。

【請求項3】

前記制御部は、前記非同期FIFOメモリの誤動作を低減するリセット信号を、前記非同期FIFOメモリの前段に設けたPLL回路に、所定のタイミングあるいは特定の動作状態が生じた際に供給することを特徴とする請求項1記載のヘッド分離式カメラ装置。

【請求項4】

イメージセンサと前記イメージセンサの出力をシリアル変換する第1の変換回路とを含む撮像部と、

前記第1の変換回路から供給される信号をパラレル変換する第2の変換回路と前記第2の変換回路が出力する映像信号を後段の映像再生部の特性にあわせて規格化する信号処理回路と前記第2の変換回路と前記信号処理回路との間に位置され、前記第2の変換回路から前記信号処理回路に供給する前記映像信号のタイミングを制御する非同期FIFOメモリとを含む制御部と、

を有するヘッド分離式カメラ装置。

【請求項5】

前記イメージセンサは、2以上のセンサを含むことを特徴とする請求項4記載のヘッド分離式カメラ装置。

【請求項6】

前記非同期FIFOメモリの前段に設けたPLL回路により、前記非同期FIFOメモリは、所定のタイミングあるいは特定の動作状態が生じた際にリセット状態が維持されることを特徴とする請求項4または5記載のヘッド分離式カメラ装置。

【請求項7】

イメージセンサが取得した映像信号をシリアル変換し、

シリアル変換して入力される映像信号をパラレル変換し、

パラレル変換された映像信号を後段の映像再生部の特性にあわせて規格化する前段で、規格化する回路への書き込みタイミングを、非同期FIFOメモリにより調整する

ことを特徴とする映像信号処理方法。

【請求項1】

撮像部と撮像部を制御する制御部とがケーブルにより接続されたヘッド分離式カメラ装置において、

制御部より撮像部へ送出した駆動信号により撮像部が含む画像センサを制御し、その画像センサから出力されるクロック信号や同期信号を含む映像信号を制御部で受け取り、非同期FIFOメモリを伴った信号処理回路を経て規格化された映像信号に変換して出力することを特徴とするヘッド分離式カメラ装置。

【請求項2】

前記非同期FIFOメモリは、前記信号処理回路の前段に位置することを特徴とする請求項1記載のヘッド分離式カメラ装置。

【請求項3】

前記制御部は、前記非同期FIFOメモリの誤動作を低減するリセット信号を、前記非同期FIFOメモリの前段に設けたPLL回路に、所定のタイミングあるいは特定の動作状態が生じた際に供給することを特徴とする請求項1記載のヘッド分離式カメラ装置。

【請求項4】

イメージセンサと前記イメージセンサの出力をシリアル変換する第1の変換回路とを含む撮像部と、

前記第1の変換回路から供給される信号をパラレル変換する第2の変換回路と前記第2の変換回路が出力する映像信号を後段の映像再生部の特性にあわせて規格化する信号処理回路と前記第2の変換回路と前記信号処理回路との間に位置され、前記第2の変換回路から前記信号処理回路に供給する前記映像信号のタイミングを制御する非同期FIFOメモリとを含む制御部と、

を有するヘッド分離式カメラ装置。

【請求項5】

前記イメージセンサは、2以上のセンサを含むことを特徴とする請求項4記載のヘッド分離式カメラ装置。

【請求項6】

前記非同期FIFOメモリの前段に設けたPLL回路により、前記非同期FIFOメモリは、所定のタイミングあるいは特定の動作状態が生じた際にリセット状態が維持されることを特徴とする請求項4または5記載のヘッド分離式カメラ装置。

【請求項7】

イメージセンサが取得した映像信号をシリアル変換し、

シリアル変換して入力される映像信号をパラレル変換し、

パラレル変換された映像信号を後段の映像再生部の特性にあわせて規格化する前段で、規格化する回路への書き込みタイミングを、非同期FIFOメモリにより調整する

ことを特徴とする映像信号処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−109611(P2011−109611A)

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願番号】特願2009−265451(P2009−265451)

【出願日】平成21年11月20日(2009.11.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年6月2日(2011.6.2)

【国際特許分類】

【出願日】平成21年11月20日(2009.11.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]