ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータ

【課題】パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できるヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータを提供する。

【解決手段】ヘテロ接合電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップST102と、前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップとを備える。

【解決手段】ヘテロ接合電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップST102と、前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップとを備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体デバイスをモデル化する方法に関連し、特にヘテロ接合電界効果トランジスタ(以下、電界効果トランジスタをFETと称す)の等価回路モデルの作成方法およびそのモデルを含む回路シミュレータに関する。

【背景技術】

【0002】

HEMT(High Electron Mobility Transistor)などを含むヘテロ接合FETは、優れた高周波特性を示し、さまざまなRFアプリケーションなどで使用されている。そのようなデバイスの性能を正確に予測し、またそのようなデバイスを用いて様々な半導体回路設計するためには、半導体デバイスの正確なモデルが必要である。モデルを用いることにより、半導体デバイスや半導体回路の開発おいて、モデルパラメータを抽出しその値をデバイス設計・作成にフィードバックすることや高精度な回路シミュレーションを行うことができる。これにより、半導体デバイスや半導体回路の試作回数を低減し、効率的な開発が可能になる。

【0003】

半導体デバイスの電気特性をモデル化する方法としては2つの方法が良く知れられている。ひとつは物理的なデバイス・シミュレーションであり、もうひとつは等価回路モデリングである。デバイス・シミュレーションは、デバイスの物理的な位置や構造、材料特性を入力パラメータとし、デバイスシミュレータという物理方程式を数値的に解くツールを用いて、電気特性を計算する方法である。例えばシルバコ社のATLAS(登録商標)というデバイスシミュレータでは、デバイスの物理構造を直接入力するため、計算結果と入力パラメータの相関はかなり強く、計算結果をデバイス開発にフィードバックしやすいという長所がある。しかしながら、実際に測定される電気特性を正確にモデル化するデバイスシミュレータの能力は、比較的不正確である。

【0004】

また、デバイス・シミュレーションによるモデル化の短所としては、回路シミュレータとの相性が悪いことが挙げられる。デバイスシミュレータでデバイスの電気特性を計算できたとしても、回路シミュレータとデバイスシミュレータの計算エンジンは全く別物であるので、デバイスシミュレータの計算モデルを回路シミュレータで使用することはできない。つまり、デバイスシミュレータで半導体デバイスの電気特性を計算できても、半導体デバイスを含む回路の電気特性を計算できないという不合理が生じる。

【0005】

次に、等価回路モデリングについて説明する。等価回路モデルとは、抵抗、インダクタ、キャパシタ、電流源などの電気的な素子のネットワークを利用して、デバイスの電気特性を計算するモデルである。特に、電流源や抵抗、キャパシタをゲート電圧やドレイン電圧の非線形の関数で記述することにより、半導体デバイスの非線形性を表現するモデルを大信号等価回路モデルと言う。各パラメータは測定結果と計算結果が一致するようにパラメータフィッティングにより決定する。通常の大信号等価回路モデルではキャパシタCgs、Cgd、電流源Igs、Igd、Idsに非線形性を持たせているが、特に電流源Idsはモデル精度を左右する最も重要な部分である。FETの等価回路モデルとしては、カーティス・エテンベルグモデルが広く使用されている(例えば、非特許文献1参照)。

【0006】

以下に、カーティス・エテンベルグモデルで使用されているドレイン電流源モデルの計算式を示す。

【0007】

【数1】

【0008】

ただし、Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

A0、A1、A2、A3:IdsのVgsに対する変化を表すパラメータ

γ:Idsの立ち上がりを表すパラメータ

β2:ピンチオフ変動を表すパラメータ

Vds0:A0−A3を評価したときのパラメータ

【0009】

上記の各パラメータをI−V特性などの実測値に対してパラメータフィッティングを行い、値を決定する。等価回路モデルは実測値をもとにパラメータの値を決めるため、比較的精度良くデバイスの電気特性を再現することができる。また、等価回路モデルは電気的な素子のネットワークで構成されているため、回路シミュレータとの相性が良く、回路シミュレータにおいて等価回路モデルを含む半導体回路の電気特性を容易に計算することできる。

【0010】

しかしながら、等価回路モデルはそのパラメータとデバイスの物理構造との相関が低いという短所がある。上記モデルにおいても、モデルパラメータはフィッティングパラメータであり、物理的な意味を持っていない。従って、デバイスの物理構造から電気特性を計算したり、モデルパラメータの値から物理量を推定したりすることは難しく、パラメータの値が分かってもデバイス開発にフィードバックすることが困難である。また、パラメータが物理的な意味を持っていないので、パラメータフィッティングの際、適切な初期値を求めることが難しく、初期値によっては局所最小値に陥り計算精度を劣化させるおそれがある。

【先行技術文献】

【非特許文献】

【0011】

【非特許文献1】“A Nonlinear GaAs FET Model for Use in the Design of Output Circuits for Power Amplifiers”, IEEE Trans. Microwave Theory Tech., vol. MTT-33, pp. 1383-1394, Dec. 1985.

【発明の概要】

【発明が解決しようとする課題】

【0012】

この発明は上記の課題を解決するためになされたもので、パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できるヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータを提供することを目的とし、半導体デバイスの効率的な開発に寄与するものである。

【課題を解決するための手段】

【0013】

この発明に係るヘテロ接合電界効果トランジスタの等価回路モデルの作成方法は、ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法であって、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数2】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数3】

P1は次式で定義され、

【数4】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップと、

前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップと

を備えるものである。

【0014】

また、この発明に係る回路シミュレータは、ヘテロ接合電界効果トランジスタの等価回路モデルを用いる回路シミュレータであって、前記等価回路モデルとして、前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数5】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数6】

P1は次式で定義され、

【数7】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む。

【発明の効果】

【0015】

この発明によれば、パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できる。

【図面の簡単な説明】

【0016】

【図1】この発明の実施の形態に係るヘテロ接合FETの等価回路モデルの構成図である。

【図2】この発明の実施の形態に係るFET等価回路モデルの物理パラメータとデバイス構造の関係を示す説明図である。

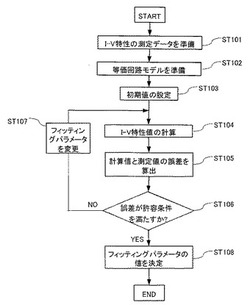

【図3】この発明の実施の形態に係るFET等価回路モデルを作成する方法の手順を示すフローチャートである。

【図4】この発明の実施の形態に係るFET等価回路モデルのパラメータImax、Vp、gmの初期値抽出のための説明図である。

【図5】この発明の実施の形態に係るFET等価回路モデルのパラメータVkneeの初期値抽出のための説明図である。

【図6】この発明の実施の形態に係るFET等価回路モデルによるI−V特性の計算値と測定値の比較を示す図である。

【図7】この発明の実施の形態に係るFETの開発方法の手順を示すフローチャートである。

【図8】この発明の実施の形態に係る別のFETの開発方法の手順を示すフローチャートである。

【図9】この発明の実施の形態に係る等価回路モデルを含む回路のシミュレーションの手順を示すフローチャートである。

【発明を実施するための形態】

【0017】

この発明の実施の形態について図面を参照して説明する。ヘテロ接合FETの等価回路モデルを図1に示す。図1に示すヘテロ接合FETの等価回路モデル1において、非線形ドレイン電流モデル2は、以下に示す式で定義される。

【0018】

【数8】

【0019】

ここで、ψ(Vgs)はドレイン電流のゲート電圧依存性を示しており、Imax(Ta)はドレイン電流の温度依存性を示している。ψ(Vgs)は下記の式で定義される。

【0020】

【数9】

【0021】

ここで、P1は以下の式で表される。

【0022】

【数10】

【0023】

また、Imax(Ta)は以下の式で定義される。

【0024】

【数11】

【0025】

式(6)の各パラメータは次のように定義される。

Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta:周囲温度

TcImax:ドレイン電流の温度係数

【0026】

ここで、Rth、Taは予め別の測定から値を決定でき、Vgs、VdsはIdsを計算するときの制御電圧であるから、これらパラメータのうち値を変更できるモデルパラメータは、Imax、Vknee、gm、Vp、P2、P3、TcImaxの7つである。

【0027】

この発明に係る等価回路モデルは、モデルパラメータとしてデバイスパラメータを用いており、モデルパラメータの意味が明確である。これにより、測定結果から容易にパラメータ初期値を求めることができる。ここで、デバイスパラメータとは、FETを含む半導体デバイスの電気特性を表すパラメータであり、例えばピンチオフ電圧やニー電圧のことを指す。

【0028】

このように、本等価回路モデルは、モデルパラメータを見ればデバイスの特性が分かり、デバイス設計にフィードバックをかけることが容易である。

【0029】

さらに、本等価回路モデルデバイスパラメータと物理パラメータを関係づけることができる。これにより、デバイス構造から直接電気特性を予測することもできる。以下、デバイスパラメータと物理パラメータの関係について説明する。ここで、物理パラメータとは、デバイスの物理的構造や物理的特性を表すパラメータであり、例えばゲート長や移動度などを指す。

【0030】

以下に、デバイスパラメータと物理パラメータの関係式を示す。

【0031】

【数12】

【0032】

ここで、各パラメータの物理的意味は以下に示す通りである。また、物理パラメータとデバイス構造との関係を図2に示す。

q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

【0033】

これらのパラメータのうち、LSG、LGD、LG、dはデバイスの物理構造に関するパラメータであり、一意に決定される。qは物理定数であるから値は固定である。ε0、εAGは材料定数であるから、材料が決まれば決定される。従って、これらのパラメータのうち正確な値が分からないのは、σ、vs、μ、Rc、φb、ΔEcである。ただし、これらのパラメータもオーダー程度の値であれば予め知ることができる。これらのパラメータは、パラメータフィッティングにより、物理パラメータの実効的な値を決定できる。

【0034】

このように、この発明に係る等価回路モデルは、デバイスパラメータと物理パラメータのいずれかをモデルパラメータとすることができる。

【0035】

図3に、この発明における等価回路モデルを作成する手順を示す。まず、FETのI−V特性の測定データを準備する(ST101)。次に、等価回路モデルを準備し(ST102)、モデルパラメータImax、Vknee、gm、Vp、P2、P3、TcImaxの初期値を設定する(ST103)。これらのパラメータを用いてI−V特性を計算し(ST104)、測定結果と計算結果の誤差を算出する(ST105)。誤差が予め定めた許容条件を満たすか判断する(ST106)。満たしていない場合は、パラメータを変更し(ST107)、ST104−ST106を繰り返す。誤差が許容条件を満たす場合は、その値にパラメータを決定し(ST108)、終了する。

【0036】

ST105において誤差Errorは例えば以下の式で算出する。なお、iは測定点を示す。

【0037】

【数13】

【0038】

また、ST103において、Imax、Vknee、gm、Vpの初期値は図4、図5に示すように、測定結果から容易に抽出できる。P2、P3、TcImaxの値は通常小さいので初期値としては0とする。また、Imax、Vknee、gm、Vpは式(7)、(8)、(11)、(10)に物理パラメータを代入して得た値を初期値にしても良いし、物理パラメータ自体をモデルパラメータとしてパラメータフィッティングを行っても良い。

【0039】

以下の表に、図3に示す手順で決定したパラメータ値を示す。

【0040】

【表1】

【0041】

図6に、これらのパラメータ値を用いたこの発明に係る等価回路モデルによる計算結果と測定結果の比較を示す。計算結果と測定結果は良く一致しており、この発明に係る等価回路モデルの有効性が確認できる。

【0042】

このように、モデルパラメータ=デバイスパラメータとするにより、FETの測定データから適切な初期値の抽出を行うことができるため、パラメータフィッティングによる繰り返し演算の回数を低減でき、短時間にFET等価回路モデルを作成できる。また、フィッティングパラメータが局所最適解に収束するおそれも避けられる。

【0043】

次に、本実施の形態に係るFETの開発方法の手順について説明する。等価回路モデルを用いた開発方法は大きく分けて2種類ある。ひとつはFETを作成する前にモデルを用いて特性を計算し、目標性能に対して最適なデバイス設計を行い、FETを試作する方法である。もうひとつはFETを作成した後に特性を実測し、その実測値に対してパラメータフィッティングを行い、得られた値をデバイスの設計にフィードバックするやり方である。

【0044】

前者の方法について図7を参照して説明する。まず、等価回路を準備し(ST301)、デバイス構造、材料定数からモデルに物理パラメータを入力する(ST302)。次にモデルを用いて電流や相互コンダクタンスなど所望の特性を計算し(ST303)、計算した特性が目標性能を満足するか判断する(ST304)。満足していない場合は、FETの物理パラメータを変更し(ST305)、ST302−ST304のステップを繰り返す。目標性能を満足する場合は、その物理パラメータを用いてFETを作成し(ST306)、本手順は終了する。ST306のステップは、得られた物理パラメータをもとにデバイスシミュレータでも特性を確認した後、試作するということとしても良い。

【0045】

次に、後者の方法について図8を参照して説明する。まず、ある物理パラメータに基づいてFETを作成する(ST201)。次に作成したFETの特性を測定し(ST202)、等価回路モデルを準備する(ST203)。次にパラメータフィッティングを行い、計算結果と測定結果が良く一致するパラメータの値を求める(ST204)。そして、得られたパラメータ値をもとにデバイス設計の変更可否を判断する(ST205)。物理パラメータのうち少なくても1つの値を変化させるべきと判断する場合は、FETの物理パラメータを変更して(ST206)、ST202−ST205のステップを繰り返す。いずれのパラメータも変化させるべきでないと判断したときは、本手順は終了する。

【0046】

この発明に係る等価回路モデルは、モデルパラメータを物理パラメータとすることができるため、パラメータフィッティングで得られた値から物理パラメータを推定しなくても、デバイスの設計変更の可否を判断できる。

【0047】

本実施の形態に係るFETを含む回路のシミュレーション方法の手順について図9を参照して説明する。まず、等価回路モデルを含むシミュレーション対象となる回路が準備される(ST401)。次に、この等価回路モデルのパラメータをパラメータフィッティングにより決定し、モデルを作成する(ST402)。等価回路モデルを含む回路を回路シミュレーションにより特性を計算し(ST403)、本手順は終了する。ここで、ST402の等価回路モデルの作成方法は図3に示した手順に該当する。パラメータはデバイスパラメータでも、物理パラメータどちらを用いても良い。

【0048】

このようなパラメータが物理的な意味をもつ等価回路モデルを用いることにより、ゲート長やピンチオフ電圧などのばらつきに対する半導体回路の電気特性のばらつきを計算することができ、歩留まりの良い半導体回路を検討、開発、フィードバックが可能である。

【符号の説明】

【0049】

1 ヘテロ接合FETの等価回路モデル、2 非線形ドレイン電流モデル。

【技術分野】

【0001】

この発明は、半導体デバイスをモデル化する方法に関連し、特にヘテロ接合電界効果トランジスタ(以下、電界効果トランジスタをFETと称す)の等価回路モデルの作成方法およびそのモデルを含む回路シミュレータに関する。

【背景技術】

【0002】

HEMT(High Electron Mobility Transistor)などを含むヘテロ接合FETは、優れた高周波特性を示し、さまざまなRFアプリケーションなどで使用されている。そのようなデバイスの性能を正確に予測し、またそのようなデバイスを用いて様々な半導体回路設計するためには、半導体デバイスの正確なモデルが必要である。モデルを用いることにより、半導体デバイスや半導体回路の開発おいて、モデルパラメータを抽出しその値をデバイス設計・作成にフィードバックすることや高精度な回路シミュレーションを行うことができる。これにより、半導体デバイスや半導体回路の試作回数を低減し、効率的な開発が可能になる。

【0003】

半導体デバイスの電気特性をモデル化する方法としては2つの方法が良く知れられている。ひとつは物理的なデバイス・シミュレーションであり、もうひとつは等価回路モデリングである。デバイス・シミュレーションは、デバイスの物理的な位置や構造、材料特性を入力パラメータとし、デバイスシミュレータという物理方程式を数値的に解くツールを用いて、電気特性を計算する方法である。例えばシルバコ社のATLAS(登録商標)というデバイスシミュレータでは、デバイスの物理構造を直接入力するため、計算結果と入力パラメータの相関はかなり強く、計算結果をデバイス開発にフィードバックしやすいという長所がある。しかしながら、実際に測定される電気特性を正確にモデル化するデバイスシミュレータの能力は、比較的不正確である。

【0004】

また、デバイス・シミュレーションによるモデル化の短所としては、回路シミュレータとの相性が悪いことが挙げられる。デバイスシミュレータでデバイスの電気特性を計算できたとしても、回路シミュレータとデバイスシミュレータの計算エンジンは全く別物であるので、デバイスシミュレータの計算モデルを回路シミュレータで使用することはできない。つまり、デバイスシミュレータで半導体デバイスの電気特性を計算できても、半導体デバイスを含む回路の電気特性を計算できないという不合理が生じる。

【0005】

次に、等価回路モデリングについて説明する。等価回路モデルとは、抵抗、インダクタ、キャパシタ、電流源などの電気的な素子のネットワークを利用して、デバイスの電気特性を計算するモデルである。特に、電流源や抵抗、キャパシタをゲート電圧やドレイン電圧の非線形の関数で記述することにより、半導体デバイスの非線形性を表現するモデルを大信号等価回路モデルと言う。各パラメータは測定結果と計算結果が一致するようにパラメータフィッティングにより決定する。通常の大信号等価回路モデルではキャパシタCgs、Cgd、電流源Igs、Igd、Idsに非線形性を持たせているが、特に電流源Idsはモデル精度を左右する最も重要な部分である。FETの等価回路モデルとしては、カーティス・エテンベルグモデルが広く使用されている(例えば、非特許文献1参照)。

【0006】

以下に、カーティス・エテンベルグモデルで使用されているドレイン電流源モデルの計算式を示す。

【0007】

【数1】

【0008】

ただし、Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

A0、A1、A2、A3:IdsのVgsに対する変化を表すパラメータ

γ:Idsの立ち上がりを表すパラメータ

β2:ピンチオフ変動を表すパラメータ

Vds0:A0−A3を評価したときのパラメータ

【0009】

上記の各パラメータをI−V特性などの実測値に対してパラメータフィッティングを行い、値を決定する。等価回路モデルは実測値をもとにパラメータの値を決めるため、比較的精度良くデバイスの電気特性を再現することができる。また、等価回路モデルは電気的な素子のネットワークで構成されているため、回路シミュレータとの相性が良く、回路シミュレータにおいて等価回路モデルを含む半導体回路の電気特性を容易に計算することできる。

【0010】

しかしながら、等価回路モデルはそのパラメータとデバイスの物理構造との相関が低いという短所がある。上記モデルにおいても、モデルパラメータはフィッティングパラメータであり、物理的な意味を持っていない。従って、デバイスの物理構造から電気特性を計算したり、モデルパラメータの値から物理量を推定したりすることは難しく、パラメータの値が分かってもデバイス開発にフィードバックすることが困難である。また、パラメータが物理的な意味を持っていないので、パラメータフィッティングの際、適切な初期値を求めることが難しく、初期値によっては局所最小値に陥り計算精度を劣化させるおそれがある。

【先行技術文献】

【非特許文献】

【0011】

【非特許文献1】“A Nonlinear GaAs FET Model for Use in the Design of Output Circuits for Power Amplifiers”, IEEE Trans. Microwave Theory Tech., vol. MTT-33, pp. 1383-1394, Dec. 1985.

【発明の概要】

【発明が解決しようとする課題】

【0012】

この発明は上記の課題を解決するためになされたもので、パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できるヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータを提供することを目的とし、半導体デバイスの効率的な開発に寄与するものである。

【課題を解決するための手段】

【0013】

この発明に係るヘテロ接合電界効果トランジスタの等価回路モデルの作成方法は、ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法であって、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数2】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数3】

P1は次式で定義され、

【数4】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップと、

前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップと

を備えるものである。

【0014】

また、この発明に係る回路シミュレータは、ヘテロ接合電界効果トランジスタの等価回路モデルを用いる回路シミュレータであって、前記等価回路モデルとして、前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数5】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数6】

P1は次式で定義され、

【数7】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む。

【発明の効果】

【0015】

この発明によれば、パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できる。

【図面の簡単な説明】

【0016】

【図1】この発明の実施の形態に係るヘテロ接合FETの等価回路モデルの構成図である。

【図2】この発明の実施の形態に係るFET等価回路モデルの物理パラメータとデバイス構造の関係を示す説明図である。

【図3】この発明の実施の形態に係るFET等価回路モデルを作成する方法の手順を示すフローチャートである。

【図4】この発明の実施の形態に係るFET等価回路モデルのパラメータImax、Vp、gmの初期値抽出のための説明図である。

【図5】この発明の実施の形態に係るFET等価回路モデルのパラメータVkneeの初期値抽出のための説明図である。

【図6】この発明の実施の形態に係るFET等価回路モデルによるI−V特性の計算値と測定値の比較を示す図である。

【図7】この発明の実施の形態に係るFETの開発方法の手順を示すフローチャートである。

【図8】この発明の実施の形態に係る別のFETの開発方法の手順を示すフローチャートである。

【図9】この発明の実施の形態に係る等価回路モデルを含む回路のシミュレーションの手順を示すフローチャートである。

【発明を実施するための形態】

【0017】

この発明の実施の形態について図面を参照して説明する。ヘテロ接合FETの等価回路モデルを図1に示す。図1に示すヘテロ接合FETの等価回路モデル1において、非線形ドレイン電流モデル2は、以下に示す式で定義される。

【0018】

【数8】

【0019】

ここで、ψ(Vgs)はドレイン電流のゲート電圧依存性を示しており、Imax(Ta)はドレイン電流の温度依存性を示している。ψ(Vgs)は下記の式で定義される。

【0020】

【数9】

【0021】

ここで、P1は以下の式で表される。

【0022】

【数10】

【0023】

また、Imax(Ta)は以下の式で定義される。

【0024】

【数11】

【0025】

式(6)の各パラメータは次のように定義される。

Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta:周囲温度

TcImax:ドレイン電流の温度係数

【0026】

ここで、Rth、Taは予め別の測定から値を決定でき、Vgs、VdsはIdsを計算するときの制御電圧であるから、これらパラメータのうち値を変更できるモデルパラメータは、Imax、Vknee、gm、Vp、P2、P3、TcImaxの7つである。

【0027】

この発明に係る等価回路モデルは、モデルパラメータとしてデバイスパラメータを用いており、モデルパラメータの意味が明確である。これにより、測定結果から容易にパラメータ初期値を求めることができる。ここで、デバイスパラメータとは、FETを含む半導体デバイスの電気特性を表すパラメータであり、例えばピンチオフ電圧やニー電圧のことを指す。

【0028】

このように、本等価回路モデルは、モデルパラメータを見ればデバイスの特性が分かり、デバイス設計にフィードバックをかけることが容易である。

【0029】

さらに、本等価回路モデルデバイスパラメータと物理パラメータを関係づけることができる。これにより、デバイス構造から直接電気特性を予測することもできる。以下、デバイスパラメータと物理パラメータの関係について説明する。ここで、物理パラメータとは、デバイスの物理的構造や物理的特性を表すパラメータであり、例えばゲート長や移動度などを指す。

【0030】

以下に、デバイスパラメータと物理パラメータの関係式を示す。

【0031】

【数12】

【0032】

ここで、各パラメータの物理的意味は以下に示す通りである。また、物理パラメータとデバイス構造との関係を図2に示す。

q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

【0033】

これらのパラメータのうち、LSG、LGD、LG、dはデバイスの物理構造に関するパラメータであり、一意に決定される。qは物理定数であるから値は固定である。ε0、εAGは材料定数であるから、材料が決まれば決定される。従って、これらのパラメータのうち正確な値が分からないのは、σ、vs、μ、Rc、φb、ΔEcである。ただし、これらのパラメータもオーダー程度の値であれば予め知ることができる。これらのパラメータは、パラメータフィッティングにより、物理パラメータの実効的な値を決定できる。

【0034】

このように、この発明に係る等価回路モデルは、デバイスパラメータと物理パラメータのいずれかをモデルパラメータとすることができる。

【0035】

図3に、この発明における等価回路モデルを作成する手順を示す。まず、FETのI−V特性の測定データを準備する(ST101)。次に、等価回路モデルを準備し(ST102)、モデルパラメータImax、Vknee、gm、Vp、P2、P3、TcImaxの初期値を設定する(ST103)。これらのパラメータを用いてI−V特性を計算し(ST104)、測定結果と計算結果の誤差を算出する(ST105)。誤差が予め定めた許容条件を満たすか判断する(ST106)。満たしていない場合は、パラメータを変更し(ST107)、ST104−ST106を繰り返す。誤差が許容条件を満たす場合は、その値にパラメータを決定し(ST108)、終了する。

【0036】

ST105において誤差Errorは例えば以下の式で算出する。なお、iは測定点を示す。

【0037】

【数13】

【0038】

また、ST103において、Imax、Vknee、gm、Vpの初期値は図4、図5に示すように、測定結果から容易に抽出できる。P2、P3、TcImaxの値は通常小さいので初期値としては0とする。また、Imax、Vknee、gm、Vpは式(7)、(8)、(11)、(10)に物理パラメータを代入して得た値を初期値にしても良いし、物理パラメータ自体をモデルパラメータとしてパラメータフィッティングを行っても良い。

【0039】

以下の表に、図3に示す手順で決定したパラメータ値を示す。

【0040】

【表1】

【0041】

図6に、これらのパラメータ値を用いたこの発明に係る等価回路モデルによる計算結果と測定結果の比較を示す。計算結果と測定結果は良く一致しており、この発明に係る等価回路モデルの有効性が確認できる。

【0042】

このように、モデルパラメータ=デバイスパラメータとするにより、FETの測定データから適切な初期値の抽出を行うことができるため、パラメータフィッティングによる繰り返し演算の回数を低減でき、短時間にFET等価回路モデルを作成できる。また、フィッティングパラメータが局所最適解に収束するおそれも避けられる。

【0043】

次に、本実施の形態に係るFETの開発方法の手順について説明する。等価回路モデルを用いた開発方法は大きく分けて2種類ある。ひとつはFETを作成する前にモデルを用いて特性を計算し、目標性能に対して最適なデバイス設計を行い、FETを試作する方法である。もうひとつはFETを作成した後に特性を実測し、その実測値に対してパラメータフィッティングを行い、得られた値をデバイスの設計にフィードバックするやり方である。

【0044】

前者の方法について図7を参照して説明する。まず、等価回路を準備し(ST301)、デバイス構造、材料定数からモデルに物理パラメータを入力する(ST302)。次にモデルを用いて電流や相互コンダクタンスなど所望の特性を計算し(ST303)、計算した特性が目標性能を満足するか判断する(ST304)。満足していない場合は、FETの物理パラメータを変更し(ST305)、ST302−ST304のステップを繰り返す。目標性能を満足する場合は、その物理パラメータを用いてFETを作成し(ST306)、本手順は終了する。ST306のステップは、得られた物理パラメータをもとにデバイスシミュレータでも特性を確認した後、試作するということとしても良い。

【0045】

次に、後者の方法について図8を参照して説明する。まず、ある物理パラメータに基づいてFETを作成する(ST201)。次に作成したFETの特性を測定し(ST202)、等価回路モデルを準備する(ST203)。次にパラメータフィッティングを行い、計算結果と測定結果が良く一致するパラメータの値を求める(ST204)。そして、得られたパラメータ値をもとにデバイス設計の変更可否を判断する(ST205)。物理パラメータのうち少なくても1つの値を変化させるべきと判断する場合は、FETの物理パラメータを変更して(ST206)、ST202−ST205のステップを繰り返す。いずれのパラメータも変化させるべきでないと判断したときは、本手順は終了する。

【0046】

この発明に係る等価回路モデルは、モデルパラメータを物理パラメータとすることができるため、パラメータフィッティングで得られた値から物理パラメータを推定しなくても、デバイスの設計変更の可否を判断できる。

【0047】

本実施の形態に係るFETを含む回路のシミュレーション方法の手順について図9を参照して説明する。まず、等価回路モデルを含むシミュレーション対象となる回路が準備される(ST401)。次に、この等価回路モデルのパラメータをパラメータフィッティングにより決定し、モデルを作成する(ST402)。等価回路モデルを含む回路を回路シミュレーションにより特性を計算し(ST403)、本手順は終了する。ここで、ST402の等価回路モデルの作成方法は図3に示した手順に該当する。パラメータはデバイスパラメータでも、物理パラメータどちらを用いても良い。

【0048】

このようなパラメータが物理的な意味をもつ等価回路モデルを用いることにより、ゲート長やピンチオフ電圧などのばらつきに対する半導体回路の電気特性のばらつきを計算することができ、歩留まりの良い半導体回路を検討、開発、フィードバックが可能である。

【符号の説明】

【0049】

1 ヘテロ接合FETの等価回路モデル、2 非線形ドレイン電流モデル。

【特許請求の範囲】

【請求項1】

ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法であって、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数1】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数2】

P1は次式で定義され、

【数3】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップと、

前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップと

を備える、ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項2】

請求項1に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記フィッティングステップは、

前記等価回路モデルの各フィッティングパラメータに初期値を設定するステップと、

設定されたパラメータを用いて、回路シミュレーションにより、電界効果トランジスタの特性値を計算するシミュレーションステップと、

前記回路シミュレーションにより得られた特性値と、予め準備された、測定された電界効果トランジスタの特性値との誤差を計算するステップと、

前記誤差が予め定める条件を満たすまで、各フィッティングパラメータの値を変化させながら前記シミュレーションステップと前記誤差を計算するステップを繰り返し行うステップと、

前記繰り返し行うステップの終了時に得られたパラメータの値の組を、前記等価回路モデルに適用することにより、前記ヘテロ接合FETの等価回路を作成するステップと

を含むことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項3】

請求項1に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記非線形ドレイン電流モデルのパラメータImax、Vknee、gm、Vpを次式で定義し、

【数4】

ただし、q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

σ、vs、μ、Rc、φb、ΔEcをフィッティングパラメータとした

ことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項4】

請求項2に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記初期値を設定するステップは、非線形ドレイン電流モデルのパラメータImax、Vknee、gm、Vpに対して、請求項3に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において定義された式を用いて算出した値を初期値とした

ことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項5】

ヘテロ接合電界効果トランジスタの等価回路モデルを用いる回路シミュレータであって、

前記等価回路モデルとして、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数5】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数6】

P1は次式で定義され、

【数7】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む回路シミュレータ。

【請求項6】

請求項5に記載の回路シミュレータにおいて、

パラメータImax、Vknee、gm、Vpを次式で定義した、

【数8】

ただし、q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

非線形ドレイン電流モデルを含むことを特徴とする回路シミュレータ。

【請求項1】

ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法であって、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数1】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数2】

P1は次式で定義され、

【数3】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップと、

前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップと

を備える、ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項2】

請求項1に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記フィッティングステップは、

前記等価回路モデルの各フィッティングパラメータに初期値を設定するステップと、

設定されたパラメータを用いて、回路シミュレーションにより、電界効果トランジスタの特性値を計算するシミュレーションステップと、

前記回路シミュレーションにより得られた特性値と、予め準備された、測定された電界効果トランジスタの特性値との誤差を計算するステップと、

前記誤差が予め定める条件を満たすまで、各フィッティングパラメータの値を変化させながら前記シミュレーションステップと前記誤差を計算するステップを繰り返し行うステップと、

前記繰り返し行うステップの終了時に得られたパラメータの値の組を、前記等価回路モデルに適用することにより、前記ヘテロ接合FETの等価回路を作成するステップと

を含むことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項3】

請求項1に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記非線形ドレイン電流モデルのパラメータImax、Vknee、gm、Vpを次式で定義し、

【数4】

ただし、q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

σ、vs、μ、Rc、φb、ΔEcをフィッティングパラメータとした

ことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項4】

請求項2に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において、

前記初期値を設定するステップは、非線形ドレイン電流モデルのパラメータImax、Vknee、gm、Vpに対して、請求項3に記載のヘテロ接合電界効果トランジスタの等価回路モデルの作成方法において定義された式を用いて算出した値を初期値とした

ことを特徴とするヘテロ接合電界効果トランジスタの等価回路モデルの作成方法。

【請求項5】

ヘテロ接合電界効果トランジスタの等価回路モデルを用いる回路シミュレータであって、

前記等価回路モデルとして、

前記電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

【数5】

ここで、ドレイン電流のゲート電圧依存性を表すψ(Vgs)とドレイン電流の温 度依存性を表すImax(Ta)とは次式で表され、

【数6】

P1は次式で定義され、

【数7】

ただし、Ids:ドレイン・ソース間電流

Vgs:ゲート・ソース間電圧

Vds:ドレイン・ソース間電圧

Imax:最大ドレイン電流

Vknee:ニー電圧

gm:相互コンダクタンス

Vp:ピンチオフ電圧

P2:キャリア密度の2次変調係数

P3:キャリア密度の3次変調係数

Rth:熱抵抗

Ta: 周囲温度

TcImax:ドレイン電流の温度係数

非線形ドレイン電流モデルを含む回路シミュレータ。

【請求項6】

請求項5に記載の回路シミュレータにおいて、

パラメータImax、Vknee、gm、Vpを次式で定義した、

【数8】

ただし、q:素電荷

σ:分極

vs:電子飽和速度

μ:電子移動度

LSG:ゲート・ソース間距離

LGD:ゲート・ドレイン間距離

LG:ゲート長

Rc:コンタクト抵抗

d:電子供給層厚

ε0:真空の誘電率

εAG:電子供給層の比誘電率

φb:障壁高さ

ΔEc:電子供給層厚とバッファ層の伝導帯エネルギーの差

非線形ドレイン電流モデルを含むことを特徴とする回路シミュレータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−114213(P2011−114213A)

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願番号】特願2009−270104(P2009−270104)

【出願日】平成21年11月27日(2009.11.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成23年6月9日(2011.6.9)

【国際特許分類】

【出願日】平成21年11月27日(2009.11.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]