ベクトル乗算処理装置および方法ならびにプログラム

【課題】オペランドのシフトを要することなく消費電力の削減をはかる。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

【解決手段】高速化回路(固定小数点オーバーフロー先見回路5、スティッキービット先見回路6)を備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、高速化回路を使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路4(部分積生成回路41、部分積制御回路42)、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ベクトル乗算処理装置および方法ならびにプログラムに関し、特に、複数のデータ形式を1個の乗算回路で対応可能な技術に関する。

【背景技術】

【0002】

複数のデータ形式に1個の乗算回路で対応可能なベクトル乗算処理装置は、乗算結果算出の高速化のために、固定小数点データ形式のオーバーフロー先見処理や、浮動小数点データ形式のスティッキービット先見処理のための専用のハードウエア回路を実装している。

【0003】

例えば、特許文献1には、浮動小数点データ形式のスティッキービット先見回路を実装し、浮動小数点データの仮数部の乗算動作と並行してスティッキービットを生成することにより高速演算を行う浮動小数点乗算器が開示されている。

【0004】

また、特許文献2には、複数のアレイエレメントを含む部分積アレイで構成されたアレイ乗算器において、部分積アレイの対応する大きさより小さいオペランドについては、アレイの最上位、または列の方にシフトしてオペランド積の計算に使用されるアレイエレメントの数を減少させる技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−259394号公報

【特許文献2】特開2008−533617号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した特許文献1に開示された技術によれば、これらの処理を乗算回路の出力から判定しているため、このような高速化回路を実装している場合に乗算回路中の部分積生成回路にて演算動作を行っても結果として参照しない領域が存在する。ベクトル乗算器の場合、ベクトル要素について連続してパイプライン処理により演算動作を行うことで、要素毎に回路が絶えず動作するため、消費電力が高くなる一因になる。

【0007】

一方、特許文献2に開示された技術によれば、上述した問題は回避されるが、被乗数または乗数、あるいはその両方がシフトされることで使用されないアレイエレメントを生み出しており、このための回路素子が必要になり、また、そのための処理負荷を要する。

【0008】

(発明の目的)

本発明の目的は、高速化回路を実装している場合に、乗算回路中の部分積生成回路にて演算動作を行っても結果として参照されない領域を部分積生成回路で直接抑止することで、オペランドのシフトを要することなく消費電力の削減をはかる、ベクトル乗算処理装置および方法ならびにプログラムを提供することにある。

【課題を解決するための手段】

【0009】

本発明の第1のベクトル乗算処理装置は、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路、を含む。

【0010】

本発明の第2のベクトル乗算処理方法は、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置に用いられるベクトル乗算処理方法であって、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成するステップと、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止するステップと、を有する。

【0011】

本発明の第3のベクトル乗算処理プログラムは、コンピュータ上で実行され、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置のベクトル乗算処理プログラムであって、コンピュータに、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成する部分積生成処理と、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する回路動作抑止処理と、を実行させる。

【発明の効果】

【0012】

本発明によれば、高速化回路を実装している場合に、乗算回路中の部分積生成回路にて演算動作を行っても結果として参照しない領域を部分積生成回路で直接抑止することで、オペランドのシフトを要することなく消費電力の削減をはかる、ベクトル乗算処理装置および方法ならびにプログラムを提供することができる。

【0013】

その理由は、部分積制御回路が、乗算命令とデータ形式とに応じて、部分積生成回路の出力に関して結果的に参照されない特定範囲の回路動作を抑止するからである。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施の形態によるベクトル乗算処理装置の内部構成を示すブロック図である。

【図2】本発明の第1の実施の形態によるベクトル乗算処理装置の乗算回路の内部構成を示すブロック図である。

【図3】本発明の第1の実施の形態によるベクトル乗算処理装置の固定小数点64ビットの部分積生成動作を説明するために引用した模式図である。

【図4】本発明の第1の実施の形態によるベクトル乗算処理装置の固定小数点32ビットの部分積生成動作を説明するために引用した模式図である。

【図5】本発明の第1の実施の形態によるベクトル乗算処理装置の浮動小数点倍精度53ビットの部分積生成動作を説明するために引用した模式図である。

【図6】本発明の第1の実施の形態によるベクトル乗算処理装置の浮動小数点単精度24ビットの部分積生成動作を説明するために引用した模式図である。

【図7】本発明の第1の実施の形態によるベクトル乗算処理装置の乗算回路(部分積生成回路の1ビット分)の内部回路図である。

【図8】本発明の第1の実施の形態によるベクトル乗算処理装置で使用される乗算命令およびデータ形式の一例を示す図である。

【図9】本発明の第2の実施の形態によるベクトル乗算処理装置の内部構成を示すブロック図である。

【図10】本発明の第1の実施の形態によるベクトル乗算処理装置で使用する乗算命令とデータ形式によって区分される制御パターンの種別、および第2の実施の形態による非数の種別について、それぞれ表形式で示した図である。

【発明を実施するための形態】

【0015】

次に、本発明の実施の形態について図面を参照して詳細に説明する。

【0016】

(第1の実施の形態の構成)

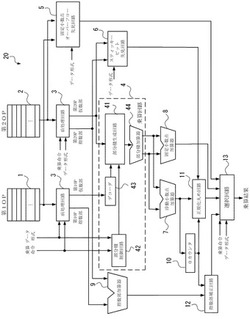

図1は、本発明の第1の実施の形態によるベクトル乗算処理装置の構成を示すブロック図である。

【0017】

図1を参照すると、本実施の形態によるベクトル乗算処理装置20は、ベクトルレジスタ1と、ベクトルレジスタ2と、前処理回路3と、乗算回路4と、固定小数点オーバーフロー先見回路5と、スティッキービット先見回路6と、浮動小数点加算器7と、固定小数点加算器8と、指数部加算器9と、0カウンタ10と、正規化丸め回路11と、指数部補正回路12と、選択回路13と、を含む。

【0018】

ベクトルレジスタ1は、前処理回路3と固定小数点オーバーフロー先見回路5に接続され、第1オペランド(OP)を格納する。ベクトルレジスタ2は、前処理回路3と固定小数点オーバーフロー先見回路5に接続され、第2オペランドを格納する。前処理回路3はベクトルレジスタ1またはベクトルレジスタ2と乗算回路4とスティッキービット先見回路6と指数部加算器9と接続され、ベクトルレジスタ1またはベクトルレジスタ2から供給されるオペランドを乗算命令とデータ形式に従って指数部と仮数部に分割する。

【0019】

乗算回路4は、前処理回路3と浮動小数点加算器7と固定小数点加算器8とに接続され、前処理回路3の出力である仮数部同士について乗算を行い、乗算結果を浮動小数点加算器7と固定小数点加算器8へ出力する。

【0020】

固定小数点オーバーフロー先見回路5は、ベクトルレジスタ1とベクトルレジスタ2と選択回路13とに接続され、第1オペランド及び第2オペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行う。スティッキービット先見回路6は、前処理回路3と正規化丸め回路11とに接続され、第1オペランド仮数部及び第2オペランド仮数部を入力として浮動小数点乗算結果のうち丸め処理に用いるスティッキービットを先見する。

【0021】

浮動小数点加算器7は、乗算回路4と0カウンタ10と正規化丸め回路11とに接続され、乗算回路4の2出力の加算を行い、結果を0カウンタ10と正規化丸め回路11へ出力する。固定小数点加算器8は、乗算回路4と選択回路13とに接続され、乗算回路4の2出力の加算を行い、加算結果のうち有効桁を選択回路13へ出力する。固定小数点加算器8の出力が固定小数点乗算結果となる。

【0022】

指数部加算器9は、前処理回路3と指数部補正回路12とに接続され、前処理回路3の出力である符号の判定及び指数部同士の加算を行い、符号及び指数部加算結果を指数部補正回路12に出力する。0カウンタ10は、浮動小数点加算器7と正規化丸め回路11と指数部補正回路12とに接続され、浮動小数点加算器7の出力を入力として最上位ビット(MSB)からのビット0の数をカウントして正規丸め回路11及び指数部補正回路12へ出力する。

【0023】

正規化丸め回路11は、スティッキービット先見回路6と浮動小数点加算器7と0カウンタ10と選択回路13とに接続され、0カウンタ10の出力に従い浮動小数点加算器7の出力をシフトして正規化を行い、更にスティッキービット先見回路6の出力を入力として丸め処理を行って選択回路13へ出力する。正規化丸め回路11の出力が浮動小数点乗算結果の仮数部となる。指数部補正回路12は、指数部加算器9と0カウンタ10と選択回路13とに接続され、0カウンタ10の出力に従い指数部加算器9の出力のうち指数部加算結果を補正する。指数部補正回路12の出力が浮動小数点乗算結果の指数部となる。

【0024】

選択回路13は、固定小数点オーバーフロー先見回路5と固定小数点加算器8と正規化丸め回路11と指数部補正回路12とに接続され、乗算命令が浮動小数点乗算を示す場合は、指数部補正回路12の符号及び指数部出力と正規化丸め回路11の仮数部出力とを連結し、浮動小数点乗算結果として出力する。乗算命令が固定小数点乗算を示す場合は、固定小数点加算器8の出力を固定小数点の演算結果として出力する。この時に固定小数点オーバーフロー先見回路5の出力がオーバーフローを示している場合にはあらかじめ定められたフォーマット(最大数など)を固定小数点乗算の演算結果として出力する。

【0025】

図2は、図1に示す乗算回路4の内部構成の詳細を説明するために引用した図である。図2を参照すると、乗算回路4は、例えば、64×64ビット乗算アレイで構成される部分積生成回路41と、部分積制御回路42と、デコーダ43と、部分積加算器44とを含む。

【0026】

図2を参照すると、デコーダ43は、前処理回路3と部分積生成回路41と接続され、第1オペランドの仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に出力する。

【0027】

部分積制御回路42は、部分積生成回路41に接続され、乗算命令とデータ形式を入力として得、制御信号(off1、off2、off3、off4)を生成して部分積生成回路41へ出力する。部分積生成回路41は、前処理回路3と部分積制御回路42とデコーダ43と部分積加算器44とに接続され、第2オペランドの仮数部を入力として得、デコーダ43から送出されるデコード信号と、部分積制御回路42により出力されるoff信号とに基づき、第2オペランド仮数部を乗じた部分積を生成する。

【0028】

部分積加算器44は、部分積生成回路41と浮動小数点加算器7と固定小数点加算器8とに接続され、部分積生成回路41の出力であるn個の部分積が2個になるまで加算し、最終的に得られた2つの部分積を浮動小数点加算器7、および固定小数点加算器8に出力する。

【0029】

(第1の実施の形態の動作)

次に、本実施の形態によるベクトル演算処理装置20の動作について、図3〜図8、ならびに図10(a)を参照して詳細に説明する。

【0030】

本実施の形態によるベクトル乗算処理装置20は、乗算命令とデータ形式にしたがいベクトルデータに対する浮動小数点乗算と固定小数点乗算とを同一のハードウェアで行う。ここでは、後述する図8(a)〜(d)に示すIEEE浮動小数点データ形式の倍精度、単精度に加え、固定小数点データ形式の64ビット、32ビットの組み合わせからなる計4個の制御パターン(後述する図10(a)参照)フォーマットに対応するベクトル乗算処理装置を例に説明する。

【0031】

まず、固定小数点乗算を実行する場合の動作について、図3、図4に示す乗算アレイ41の模式図を参照しながら説明する。

【0032】

上述した前処理回路3、乗算回路4、および選択回路12へ送出される乗算命令は、”固定小数点乗算”が指定され、また、データ形式は“64ビット”、または、“32ビット”が指定されるものとする。このとき、前処理回路3は、この乗算命令とデータ形式とにしたがい、ここでは固定小数点乗算であるため、“0”を指数部として指数部加算器9へ、また、固定小数点乗算64ビットならば、例えば、図8(a)に示すように、第1及び第2オペランドのビット全てを仮数部とし、固定小数点乗算32ビットならば、図8(b)に示すように第1及び第2オペランドの有効桁32ビットの下位側32ビット分の“0”を付加と、これを仮数部として乗算回路4へそれぞれ出力する。

【0033】

乗算回路4は、入力された64ビットの第1オペランド仮数部を乗算として、第2オペランド仮数部を被乗数として、乗数の各ビットに被乗数を乗じたもの(部分積)、を図3、図4に示すように、2進数の筆算の形にn段並べ(乗算アレイ)、これを加算することによって積を求める。図3に、固定小数点64ビットの部分積を示す。図3を参照すると、各部分積のうち、下位64ビットの領域が固定小数点乗算64ビットの乗算結果となり、波線部で示される上位64bビットがオーバーフローの検出に用いられる。

【0034】

本実施の形態によるベクトル乗算処理装置20では、固定小数点オーバーフロー先見回路5で、第1及び第2オペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行い、その結果を選択回路12に出力する。このため、図3の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の1/2にあたる領域が未参照領域となる。

【0035】

なお、固定小数点乗算のオーバーフローの先見については、各入力データのMSBからの“0”の数を計上し、合計が一定数以内の場合にオーバーフローとなることが知られている。図4に固定小数点32ビットの部分積を示す。32ビット×32ビット乗算アレイの領域のうち、下位32ビットの領域が固定小数点乗算32ビットの乗算結果となり、波線部で示される上位32ビットがオーバーフローの検出に用いられる。固定小数点乗算64ビットのときと同様、本実施の形態によるベクトル乗算処理装置では、固定小数点オーバーフロー先見回路5で固定小数点乗算結果がオーバーフローするか否かの先見を行うため、図4の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイの全体の1/8にあたる領域が未参照領域となる。

【0036】

図2に示す乗算回路4の構成において、デコーダ43は第1オペランド仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に送信する。部分積生成回路41は、第2オペランド仮数部を入力としてデコーダ43から送出されるデコード信号に部分積制御回路42から送出されるoff信号と第2オペランド仮数部を乗じた部分積を生成し、筆算の形にn段並べる。この時、部分積生成回路41の1ビット分は、図7に示されるように、論理ゲート中にoff信号を入力とするANDゲートを有する。

【0037】

図6において、部分積制御回路42は、乗算命令とデータ形式を入力としてoff信号を生成し、部分積生成回路41へ分配する。off信号は、例えば、図10(a)に表1として示されるように、乗算命令とデータ形式によって、off1、off2、off3、off4の、4個の制御パターンに分類されている。固定小数点乗算64ビットの場合はoff1信号を、固定小数点乗算32ビットの場合はoff2信号を生成するものとする。それぞれのoff信号は、有効時に“0”になるものとする。

【0038】

図7を参照すると、部分積生成回路41に有効なoff信号(値は0)が入力されると、出力は“0”に保たれる。これにより、固定小数点乗算64ビットの場合は、図6のoff1信号を入力とする領域が、固定小数点乗算32ビットの場合はoff2信号を入力とする領域が全て“0”出力になる。

【0039】

説明を図2に戻す。部分積生成回路41の出力である各部分積は、部分積加算器44によってn個の部分積を2個になるまで加算し、最終的に得られた2個の部分積を浮動小数点加算器7、及び固定小数点加算器8に出力する。この加算処理の際に、部分積生成回路41で出力が“0”に保たれる領域は動作しない。図1において、固定小数点加算器8は、乗算回路4の2出力を入力として加算を行い、加算結果のうち有効桁の部分を選択回路12へ出力する。固定小数点加算器8の出力が固定小数点乗算結果になる。選択回路12は、固定小数点加算器8の出力を固定小数点乗算として出力する。演算結果の出力の際に固定小数点オーバーフロー先見回路5の出力がオーバーフローを示している場合にはあらかじめ定められたフォーマット(最大数)を固定小数点乗算結果として出力する。

【0040】

次に、浮動小数点乗算を実行する場合の動作について、図5、図6の乗算アレイの模式図を参照しながら説明する。このとき、前処理回路3及び乗算回路4及び選択回路12に送出される乗算命令は、“浮動小数点乗算”が指定され、データ形式は“64ビット(倍精度)”、または“32ビット(単精度)”が指定される。

【0041】

前処理回路3は、この乗算命令とデータ形式に従い、例えば、図8(c)に示されるように、浮動小数点乗算倍精度ならば、符号(S)1ビットと指数部(E)11ビットの合計12ビットを指数部とし、浮動小数点乗算単精度ならば、符号(S)1ビットと指数部(E)8ビットとを合わせた合計9ビットを指数部として指数部加算器9へ出力する。

【0042】

また、浮動小数点乗算倍精度ならば、図8(d)に示されるように、IEEE浮動小数点データ形式の表現における仮数部の先頭の隠しビット“1”に、第1及び第2オペランドの仮数部(M)52ビットと11ビット分の“0”を付加し、これを仮数部として乗算回路4へ出力する。浮動小数点乗算単精度ならば、IEEE浮動小数点データ形式の表現における仮数部の先頭の隠しビット“1”に、第1及び第2オペランドの仮数部23ビットと40ビット分の“0”を付加し、これを仮数部として乗算回路4へ出力する。前処理回路3で生成された第1及び第2オペランドの指数部は、指数部加算器9で符号の判定、及び指数部の加算を行い、得られた符号と指数部加算結果を指数部補正回路12に出力する。

【0043】

乗算回路4は、入力された64ビットの第1オペランド仮数部を乗数、第2オペランド仮数部を被乗数として、乗数の各ビットに被乗数を乗じた部分積を、図5及び図6に示すように、2進数の筆算の形にn段並べ、これを加算することによって積を求める。図5に、浮動小数点倍精度の部分積が示されている。各部分積のうち、上位53ビットの領域が浮動小数点乗算53ビットの乗算結果となり、54ビット目と55ビット目がIEEE浮動小数点乗算の丸め処理に用いられるラウンドビットとガードビットになる。波線部で示される下位51ビットがIEEE浮動小数点乗算の丸め処理に用いられるスティッキービットの検出に用いられる。

【0044】

本実施の形態によるベクトル乗算処理装置20の構成では、スティッキービット先見回路6で第1及び第2オペランドを入力としてスイッキービットの先見を行い、その結果を正規化丸め回路11に出力するため、図5の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の約34%にあたる領域が未参照領域となる。

【0045】

図6に浮動小数点単精度の部分積が示されている。ここでは、24ビット×24ビット乗算アレイの領域のうち、上位24ビットの領域が浮動小数点乗算24ビットの乗算結果となり、25ビット目と26ビット目がIEEE浮動小数点乗算の丸め処理に用いられるラウンドビットとガードビットになる。また、波線部で示される下位22ビットがIEEE浮動小数点の丸め処理に用いられるスティッキービットの検出に用いられる。浮動小数点乗算53ビットの場合と同様、スティッキービット先見回路6でスティッキービットの先見を行うため、図6の波線部で示される領域は以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の約6%にあたる領域が未参照領域になる。なお、スティッキービットを先見する方法としては上述した特許文献1に詳細に開示されている。

【0046】

説明を図2に戻す。図2は乗算回路4の内部構成の詳細を示すブロック図であり、上述したように、デコーダ43は、第1オペランド仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に出力する。部分積生成回路41は、第2オペランド仮数部を入力したデコーダ43から送出されるデコード信号に第2オペランド仮数部を乗じた部分積を生成し、筆算の形にn段並べる。このとき、部分積生成回路41の1ビット分は、図7に示されるように、論理ゲート中にoff信号を入力とするANDゲートを有する。部分積制御回路42は、乗算命令とデータ形式を入力としてoff信号を生成し、部分積生成回路41へ分配する。off信号は、例えば、図10(a)に表1として示したように、乗算命令とデータ形式によってoff1、off2、off3、off4の4個に分類される。

【0047】

浮動小数点乗算倍精度の場合は、off3信号を生成する。浮動小数点乗算単精度の場合はoff4信号を生成する。それぞれのoff信号は、有効時に“0”になるものとする。図7の1ビット分の部分積生成回路41において、部分積生成回路41に有効なoff信号(値は0)が入力されると、出力は“0”に保たれる。これにより浮動小数点乗算倍精度の場合は、図6のoff3信号を入力とする領域が、浮動小数点乗算単精度の場合はoff4信号を入力とする領域が全て“0”出力となる。

【0048】

図7において、部分積生成回路41の出力である各部分積は、部分積加算器44によってn個の部分積が2個になるまで加算され、最終的に得られた2つの部分積を浮動小数点加算器7及び固定小数点加算器8に出力する。この加算処理の際に、部分積生成回路41で出力が“0”に保たれる領域は動作しない。図1において、浮動小数点加算器7は、部分積加算器44の2出力を加算し、結果を正規化丸め回路11と0カウンタ10へ送信する。0カウンタ10で加算結果のMSBから“0”の数をカウントして正規化のためのシフト数が求められる。このシフト数は、正規化丸め回路11へ送出され、スティッキービット先見回路6から送出されたスティッキービットとともに、正規化丸め回路11で仮数部の正規化及び丸めが行われる。正規化丸め回路11の出力が浮動小数点乗算結果の仮数部になる。

【0049】

このとき、0カウンタ10の出力であるシフト数は指数部補正回路12にも出力され、指数部補正回路12で指数部の補正を行い、浮動小数点乗算結果の符号と指数部を得る。選択回路13は、指数部補正回路12の出力と正規化丸め回路11の出力を合せて浮動小数点乗算の演算結果として出力する。

【0050】

(第1の実施の形態による効果)

本発明の第1の効果は、複数のデータ形式を1個の乗算回路でサポートするベクトル乗算処理装置の消費電力を低減できる、ということである。

【0051】

その理由は、乗算命令とデータ形式毎に乗算回路内にある部分積生成回路の動作の制御を行うことで、部分積生成回路の出力に関して結果として参照しない領域の動作を抑止するからである。

【0052】

(第2の実施の形態の構成)

次に、本発明の第2の実施の形態によるベクトル乗算処理装置20について、図9に示すベクトル演算処理装置20の構成図を用いて説明する。

【0053】

図9に示す本実施の形態によるベクトル乗算処理装置20において、図1に示す第1の実施の形態との差異は、ベクトルレジスタ1、およびベクトルレジスタ2と、乗算回路4との間に、非数検出回路14が付加されていることにある。非数検出回路14は、例えば、図10(b)に表2にとして示されている、IEEE浮動小数点データ形式の非数NaN(Not a Number)を検出し、その検出結果を、乗算回路4内の部分積制御回路42と、選択回路13とに送信する。ここでは、シグナル型のsNaNと、クワイエット型のqNaNが例示されている。他の構成は、図1に示す構成と同じである。

【0054】

(第2の実施の形態の動作)

IEEE浮動小数点演算では、浮動小数点の演算の結果として、不正なオペランドが与えられたために生じた結果を非数NaNとして出力するため、乗算回路4の結果は参照されない。したがって、浮動小数点乗算命令時に非数検出回路14の出力が非数である場合、部分積制御回路42より部分積生成回路41の全ての領域にoff信号を供給すれば、部分積生成回路41以降の回路全体の動作を停止させることが出来、このことにより、一層の消費電力を低減できる。

【0055】

(第2の実施の形態による効果)

本実施の形態によるベクトル乗算処理装置20によれれば、IEEE浮動小数点データ形式の非数を検出し、非数が検出された場合、部分積制御回路42より部分積生成回路41の全ての領域にoff信号を供給することで部分積生成回路41以降の回路全体の動作を停止させることができ、この場合、一層の消費電力の削減が可能になる。

【0056】

なお、図1、図9のベクトル乗算処理装置20の乗算回路4が有する機能は、全てをソフトウェアによって実現しても、あるいはその少なくとも一部をハードウェアで実現してもよい。例えば、乗算回路4が、オーバーフロー先見回路5とスティッキービット先見回路6とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する制御信号を生成し、部分積の生成を制御するデータ処理は、1または複数のプログラムによりコンピュータ上で実現してもよく、また、その少なくとも一部をハードウェアで実現してもよい。

【0057】

以上好ましい実施の形態と実施例をあげて本発明を説明したが、本発明は必ずしも、上述実施の形態及び実施例に限定されるものでなく、その技術的思想の範囲内において様々に変形して実施することができる。

【符号の説明】

【0058】

1、2:ベクトルレジスタ

3:前処理回路

4:乗算回路

5:固定小数点オーバーフロー先見回路

6:スティッキービット先見回路

7:浮動小数点加算器

8:固定小数点加算器

9:指数部加算器

10:0カウンタ

11:正規化丸め回路

12:指数部補正回路

13:選択回路

14:非数検出回路

20:ベクトル乗算処理装置

41:部分積生成回路

42:部分積制御回路

43:デコーダ

44:部分積加算器

【技術分野】

【0001】

本発明は、ベクトル乗算処理装置および方法ならびにプログラムに関し、特に、複数のデータ形式を1個の乗算回路で対応可能な技術に関する。

【背景技術】

【0002】

複数のデータ形式に1個の乗算回路で対応可能なベクトル乗算処理装置は、乗算結果算出の高速化のために、固定小数点データ形式のオーバーフロー先見処理や、浮動小数点データ形式のスティッキービット先見処理のための専用のハードウエア回路を実装している。

【0003】

例えば、特許文献1には、浮動小数点データ形式のスティッキービット先見回路を実装し、浮動小数点データの仮数部の乗算動作と並行してスティッキービットを生成することにより高速演算を行う浮動小数点乗算器が開示されている。

【0004】

また、特許文献2には、複数のアレイエレメントを含む部分積アレイで構成されたアレイ乗算器において、部分積アレイの対応する大きさより小さいオペランドについては、アレイの最上位、または列の方にシフトしてオペランド積の計算に使用されるアレイエレメントの数を減少させる技術が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2000−259394号公報

【特許文献2】特開2008−533617号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した特許文献1に開示された技術によれば、これらの処理を乗算回路の出力から判定しているため、このような高速化回路を実装している場合に乗算回路中の部分積生成回路にて演算動作を行っても結果として参照しない領域が存在する。ベクトル乗算器の場合、ベクトル要素について連続してパイプライン処理により演算動作を行うことで、要素毎に回路が絶えず動作するため、消費電力が高くなる一因になる。

【0007】

一方、特許文献2に開示された技術によれば、上述した問題は回避されるが、被乗数または乗数、あるいはその両方がシフトされることで使用されないアレイエレメントを生み出しており、このための回路素子が必要になり、また、そのための処理負荷を要する。

【0008】

(発明の目的)

本発明の目的は、高速化回路を実装している場合に、乗算回路中の部分積生成回路にて演算動作を行っても結果として参照されない領域を部分積生成回路で直接抑止することで、オペランドのシフトを要することなく消費電力の削減をはかる、ベクトル乗算処理装置および方法ならびにプログラムを提供することにある。

【課題を解決するための手段】

【0009】

本発明の第1のベクトル乗算処理装置は、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路、を含む。

【0010】

本発明の第2のベクトル乗算処理方法は、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置に用いられるベクトル乗算処理方法であって、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成するステップと、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止するステップと、を有する。

【0011】

本発明の第3のベクトル乗算処理プログラムは、コンピュータ上で実行され、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置のベクトル乗算処理プログラムであって、コンピュータに、オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成する部分積生成処理と、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する回路動作抑止処理と、を実行させる。

【発明の効果】

【0012】

本発明によれば、高速化回路を実装している場合に、乗算回路中の部分積生成回路にて演算動作を行っても結果として参照しない領域を部分積生成回路で直接抑止することで、オペランドのシフトを要することなく消費電力の削減をはかる、ベクトル乗算処理装置および方法ならびにプログラムを提供することができる。

【0013】

その理由は、部分積制御回路が、乗算命令とデータ形式とに応じて、部分積生成回路の出力に関して結果的に参照されない特定範囲の回路動作を抑止するからである。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施の形態によるベクトル乗算処理装置の内部構成を示すブロック図である。

【図2】本発明の第1の実施の形態によるベクトル乗算処理装置の乗算回路の内部構成を示すブロック図である。

【図3】本発明の第1の実施の形態によるベクトル乗算処理装置の固定小数点64ビットの部分積生成動作を説明するために引用した模式図である。

【図4】本発明の第1の実施の形態によるベクトル乗算処理装置の固定小数点32ビットの部分積生成動作を説明するために引用した模式図である。

【図5】本発明の第1の実施の形態によるベクトル乗算処理装置の浮動小数点倍精度53ビットの部分積生成動作を説明するために引用した模式図である。

【図6】本発明の第1の実施の形態によるベクトル乗算処理装置の浮動小数点単精度24ビットの部分積生成動作を説明するために引用した模式図である。

【図7】本発明の第1の実施の形態によるベクトル乗算処理装置の乗算回路(部分積生成回路の1ビット分)の内部回路図である。

【図8】本発明の第1の実施の形態によるベクトル乗算処理装置で使用される乗算命令およびデータ形式の一例を示す図である。

【図9】本発明の第2の実施の形態によるベクトル乗算処理装置の内部構成を示すブロック図である。

【図10】本発明の第1の実施の形態によるベクトル乗算処理装置で使用する乗算命令とデータ形式によって区分される制御パターンの種別、および第2の実施の形態による非数の種別について、それぞれ表形式で示した図である。

【発明を実施するための形態】

【0015】

次に、本発明の実施の形態について図面を参照して詳細に説明する。

【0016】

(第1の実施の形態の構成)

図1は、本発明の第1の実施の形態によるベクトル乗算処理装置の構成を示すブロック図である。

【0017】

図1を参照すると、本実施の形態によるベクトル乗算処理装置20は、ベクトルレジスタ1と、ベクトルレジスタ2と、前処理回路3と、乗算回路4と、固定小数点オーバーフロー先見回路5と、スティッキービット先見回路6と、浮動小数点加算器7と、固定小数点加算器8と、指数部加算器9と、0カウンタ10と、正規化丸め回路11と、指数部補正回路12と、選択回路13と、を含む。

【0018】

ベクトルレジスタ1は、前処理回路3と固定小数点オーバーフロー先見回路5に接続され、第1オペランド(OP)を格納する。ベクトルレジスタ2は、前処理回路3と固定小数点オーバーフロー先見回路5に接続され、第2オペランドを格納する。前処理回路3はベクトルレジスタ1またはベクトルレジスタ2と乗算回路4とスティッキービット先見回路6と指数部加算器9と接続され、ベクトルレジスタ1またはベクトルレジスタ2から供給されるオペランドを乗算命令とデータ形式に従って指数部と仮数部に分割する。

【0019】

乗算回路4は、前処理回路3と浮動小数点加算器7と固定小数点加算器8とに接続され、前処理回路3の出力である仮数部同士について乗算を行い、乗算結果を浮動小数点加算器7と固定小数点加算器8へ出力する。

【0020】

固定小数点オーバーフロー先見回路5は、ベクトルレジスタ1とベクトルレジスタ2と選択回路13とに接続され、第1オペランド及び第2オペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行う。スティッキービット先見回路6は、前処理回路3と正規化丸め回路11とに接続され、第1オペランド仮数部及び第2オペランド仮数部を入力として浮動小数点乗算結果のうち丸め処理に用いるスティッキービットを先見する。

【0021】

浮動小数点加算器7は、乗算回路4と0カウンタ10と正規化丸め回路11とに接続され、乗算回路4の2出力の加算を行い、結果を0カウンタ10と正規化丸め回路11へ出力する。固定小数点加算器8は、乗算回路4と選択回路13とに接続され、乗算回路4の2出力の加算を行い、加算結果のうち有効桁を選択回路13へ出力する。固定小数点加算器8の出力が固定小数点乗算結果となる。

【0022】

指数部加算器9は、前処理回路3と指数部補正回路12とに接続され、前処理回路3の出力である符号の判定及び指数部同士の加算を行い、符号及び指数部加算結果を指数部補正回路12に出力する。0カウンタ10は、浮動小数点加算器7と正規化丸め回路11と指数部補正回路12とに接続され、浮動小数点加算器7の出力を入力として最上位ビット(MSB)からのビット0の数をカウントして正規丸め回路11及び指数部補正回路12へ出力する。

【0023】

正規化丸め回路11は、スティッキービット先見回路6と浮動小数点加算器7と0カウンタ10と選択回路13とに接続され、0カウンタ10の出力に従い浮動小数点加算器7の出力をシフトして正規化を行い、更にスティッキービット先見回路6の出力を入力として丸め処理を行って選択回路13へ出力する。正規化丸め回路11の出力が浮動小数点乗算結果の仮数部となる。指数部補正回路12は、指数部加算器9と0カウンタ10と選択回路13とに接続され、0カウンタ10の出力に従い指数部加算器9の出力のうち指数部加算結果を補正する。指数部補正回路12の出力が浮動小数点乗算結果の指数部となる。

【0024】

選択回路13は、固定小数点オーバーフロー先見回路5と固定小数点加算器8と正規化丸め回路11と指数部補正回路12とに接続され、乗算命令が浮動小数点乗算を示す場合は、指数部補正回路12の符号及び指数部出力と正規化丸め回路11の仮数部出力とを連結し、浮動小数点乗算結果として出力する。乗算命令が固定小数点乗算を示す場合は、固定小数点加算器8の出力を固定小数点の演算結果として出力する。この時に固定小数点オーバーフロー先見回路5の出力がオーバーフローを示している場合にはあらかじめ定められたフォーマット(最大数など)を固定小数点乗算の演算結果として出力する。

【0025】

図2は、図1に示す乗算回路4の内部構成の詳細を説明するために引用した図である。図2を参照すると、乗算回路4は、例えば、64×64ビット乗算アレイで構成される部分積生成回路41と、部分積制御回路42と、デコーダ43と、部分積加算器44とを含む。

【0026】

図2を参照すると、デコーダ43は、前処理回路3と部分積生成回路41と接続され、第1オペランドの仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に出力する。

【0027】

部分積制御回路42は、部分積生成回路41に接続され、乗算命令とデータ形式を入力として得、制御信号(off1、off2、off3、off4)を生成して部分積生成回路41へ出力する。部分積生成回路41は、前処理回路3と部分積制御回路42とデコーダ43と部分積加算器44とに接続され、第2オペランドの仮数部を入力として得、デコーダ43から送出されるデコード信号と、部分積制御回路42により出力されるoff信号とに基づき、第2オペランド仮数部を乗じた部分積を生成する。

【0028】

部分積加算器44は、部分積生成回路41と浮動小数点加算器7と固定小数点加算器8とに接続され、部分積生成回路41の出力であるn個の部分積が2個になるまで加算し、最終的に得られた2つの部分積を浮動小数点加算器7、および固定小数点加算器8に出力する。

【0029】

(第1の実施の形態の動作)

次に、本実施の形態によるベクトル演算処理装置20の動作について、図3〜図8、ならびに図10(a)を参照して詳細に説明する。

【0030】

本実施の形態によるベクトル乗算処理装置20は、乗算命令とデータ形式にしたがいベクトルデータに対する浮動小数点乗算と固定小数点乗算とを同一のハードウェアで行う。ここでは、後述する図8(a)〜(d)に示すIEEE浮動小数点データ形式の倍精度、単精度に加え、固定小数点データ形式の64ビット、32ビットの組み合わせからなる計4個の制御パターン(後述する図10(a)参照)フォーマットに対応するベクトル乗算処理装置を例に説明する。

【0031】

まず、固定小数点乗算を実行する場合の動作について、図3、図4に示す乗算アレイ41の模式図を参照しながら説明する。

【0032】

上述した前処理回路3、乗算回路4、および選択回路12へ送出される乗算命令は、”固定小数点乗算”が指定され、また、データ形式は“64ビット”、または、“32ビット”が指定されるものとする。このとき、前処理回路3は、この乗算命令とデータ形式とにしたがい、ここでは固定小数点乗算であるため、“0”を指数部として指数部加算器9へ、また、固定小数点乗算64ビットならば、例えば、図8(a)に示すように、第1及び第2オペランドのビット全てを仮数部とし、固定小数点乗算32ビットならば、図8(b)に示すように第1及び第2オペランドの有効桁32ビットの下位側32ビット分の“0”を付加と、これを仮数部として乗算回路4へそれぞれ出力する。

【0033】

乗算回路4は、入力された64ビットの第1オペランド仮数部を乗算として、第2オペランド仮数部を被乗数として、乗数の各ビットに被乗数を乗じたもの(部分積)、を図3、図4に示すように、2進数の筆算の形にn段並べ(乗算アレイ)、これを加算することによって積を求める。図3に、固定小数点64ビットの部分積を示す。図3を参照すると、各部分積のうち、下位64ビットの領域が固定小数点乗算64ビットの乗算結果となり、波線部で示される上位64bビットがオーバーフローの検出に用いられる。

【0034】

本実施の形態によるベクトル乗算処理装置20では、固定小数点オーバーフロー先見回路5で、第1及び第2オペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行い、その結果を選択回路12に出力する。このため、図3の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の1/2にあたる領域が未参照領域となる。

【0035】

なお、固定小数点乗算のオーバーフローの先見については、各入力データのMSBからの“0”の数を計上し、合計が一定数以内の場合にオーバーフローとなることが知られている。図4に固定小数点32ビットの部分積を示す。32ビット×32ビット乗算アレイの領域のうち、下位32ビットの領域が固定小数点乗算32ビットの乗算結果となり、波線部で示される上位32ビットがオーバーフローの検出に用いられる。固定小数点乗算64ビットのときと同様、本実施の形態によるベクトル乗算処理装置では、固定小数点オーバーフロー先見回路5で固定小数点乗算結果がオーバーフローするか否かの先見を行うため、図4の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイの全体の1/8にあたる領域が未参照領域となる。

【0036】

図2に示す乗算回路4の構成において、デコーダ43は第1オペランド仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に送信する。部分積生成回路41は、第2オペランド仮数部を入力としてデコーダ43から送出されるデコード信号に部分積制御回路42から送出されるoff信号と第2オペランド仮数部を乗じた部分積を生成し、筆算の形にn段並べる。この時、部分積生成回路41の1ビット分は、図7に示されるように、論理ゲート中にoff信号を入力とするANDゲートを有する。

【0037】

図6において、部分積制御回路42は、乗算命令とデータ形式を入力としてoff信号を生成し、部分積生成回路41へ分配する。off信号は、例えば、図10(a)に表1として示されるように、乗算命令とデータ形式によって、off1、off2、off3、off4の、4個の制御パターンに分類されている。固定小数点乗算64ビットの場合はoff1信号を、固定小数点乗算32ビットの場合はoff2信号を生成するものとする。それぞれのoff信号は、有効時に“0”になるものとする。

【0038】

図7を参照すると、部分積生成回路41に有効なoff信号(値は0)が入力されると、出力は“0”に保たれる。これにより、固定小数点乗算64ビットの場合は、図6のoff1信号を入力とする領域が、固定小数点乗算32ビットの場合はoff2信号を入力とする領域が全て“0”出力になる。

【0039】

説明を図2に戻す。部分積生成回路41の出力である各部分積は、部分積加算器44によってn個の部分積を2個になるまで加算し、最終的に得られた2個の部分積を浮動小数点加算器7、及び固定小数点加算器8に出力する。この加算処理の際に、部分積生成回路41で出力が“0”に保たれる領域は動作しない。図1において、固定小数点加算器8は、乗算回路4の2出力を入力として加算を行い、加算結果のうち有効桁の部分を選択回路12へ出力する。固定小数点加算器8の出力が固定小数点乗算結果になる。選択回路12は、固定小数点加算器8の出力を固定小数点乗算として出力する。演算結果の出力の際に固定小数点オーバーフロー先見回路5の出力がオーバーフローを示している場合にはあらかじめ定められたフォーマット(最大数)を固定小数点乗算結果として出力する。

【0040】

次に、浮動小数点乗算を実行する場合の動作について、図5、図6の乗算アレイの模式図を参照しながら説明する。このとき、前処理回路3及び乗算回路4及び選択回路12に送出される乗算命令は、“浮動小数点乗算”が指定され、データ形式は“64ビット(倍精度)”、または“32ビット(単精度)”が指定される。

【0041】

前処理回路3は、この乗算命令とデータ形式に従い、例えば、図8(c)に示されるように、浮動小数点乗算倍精度ならば、符号(S)1ビットと指数部(E)11ビットの合計12ビットを指数部とし、浮動小数点乗算単精度ならば、符号(S)1ビットと指数部(E)8ビットとを合わせた合計9ビットを指数部として指数部加算器9へ出力する。

【0042】

また、浮動小数点乗算倍精度ならば、図8(d)に示されるように、IEEE浮動小数点データ形式の表現における仮数部の先頭の隠しビット“1”に、第1及び第2オペランドの仮数部(M)52ビットと11ビット分の“0”を付加し、これを仮数部として乗算回路4へ出力する。浮動小数点乗算単精度ならば、IEEE浮動小数点データ形式の表現における仮数部の先頭の隠しビット“1”に、第1及び第2オペランドの仮数部23ビットと40ビット分の“0”を付加し、これを仮数部として乗算回路4へ出力する。前処理回路3で生成された第1及び第2オペランドの指数部は、指数部加算器9で符号の判定、及び指数部の加算を行い、得られた符号と指数部加算結果を指数部補正回路12に出力する。

【0043】

乗算回路4は、入力された64ビットの第1オペランド仮数部を乗数、第2オペランド仮数部を被乗数として、乗数の各ビットに被乗数を乗じた部分積を、図5及び図6に示すように、2進数の筆算の形にn段並べ、これを加算することによって積を求める。図5に、浮動小数点倍精度の部分積が示されている。各部分積のうち、上位53ビットの領域が浮動小数点乗算53ビットの乗算結果となり、54ビット目と55ビット目がIEEE浮動小数点乗算の丸め処理に用いられるラウンドビットとガードビットになる。波線部で示される下位51ビットがIEEE浮動小数点乗算の丸め処理に用いられるスティッキービットの検出に用いられる。

【0044】

本実施の形態によるベクトル乗算処理装置20の構成では、スティッキービット先見回路6で第1及び第2オペランドを入力としてスイッキービットの先見を行い、その結果を正規化丸め回路11に出力するため、図5の波線部で示される領域は、以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の約34%にあたる領域が未参照領域となる。

【0045】

図6に浮動小数点単精度の部分積が示されている。ここでは、24ビット×24ビット乗算アレイの領域のうち、上位24ビットの領域が浮動小数点乗算24ビットの乗算結果となり、25ビット目と26ビット目がIEEE浮動小数点乗算の丸め処理に用いられるラウンドビットとガードビットになる。また、波線部で示される下位22ビットがIEEE浮動小数点の丸め処理に用いられるスティッキービットの検出に用いられる。浮動小数点乗算53ビットの場合と同様、スティッキービット先見回路6でスティッキービットの先見を行うため、図6の波線部で示される領域は以降の回路の何れにも参照されることがない。したがって、乗算アレイ全体の約6%にあたる領域が未参照領域になる。なお、スティッキービットを先見する方法としては上述した特許文献1に詳細に開示されている。

【0046】

説明を図2に戻す。図2は乗算回路4の内部構成の詳細を示すブロック図であり、上述したように、デコーダ43は、第1オペランド仮数部を入力として再コード化の処理を行い、デコード信号を部分積生成回路41に出力する。部分積生成回路41は、第2オペランド仮数部を入力したデコーダ43から送出されるデコード信号に第2オペランド仮数部を乗じた部分積を生成し、筆算の形にn段並べる。このとき、部分積生成回路41の1ビット分は、図7に示されるように、論理ゲート中にoff信号を入力とするANDゲートを有する。部分積制御回路42は、乗算命令とデータ形式を入力としてoff信号を生成し、部分積生成回路41へ分配する。off信号は、例えば、図10(a)に表1として示したように、乗算命令とデータ形式によってoff1、off2、off3、off4の4個に分類される。

【0047】

浮動小数点乗算倍精度の場合は、off3信号を生成する。浮動小数点乗算単精度の場合はoff4信号を生成する。それぞれのoff信号は、有効時に“0”になるものとする。図7の1ビット分の部分積生成回路41において、部分積生成回路41に有効なoff信号(値は0)が入力されると、出力は“0”に保たれる。これにより浮動小数点乗算倍精度の場合は、図6のoff3信号を入力とする領域が、浮動小数点乗算単精度の場合はoff4信号を入力とする領域が全て“0”出力となる。

【0048】

図7において、部分積生成回路41の出力である各部分積は、部分積加算器44によってn個の部分積が2個になるまで加算され、最終的に得られた2つの部分積を浮動小数点加算器7及び固定小数点加算器8に出力する。この加算処理の際に、部分積生成回路41で出力が“0”に保たれる領域は動作しない。図1において、浮動小数点加算器7は、部分積加算器44の2出力を加算し、結果を正規化丸め回路11と0カウンタ10へ送信する。0カウンタ10で加算結果のMSBから“0”の数をカウントして正規化のためのシフト数が求められる。このシフト数は、正規化丸め回路11へ送出され、スティッキービット先見回路6から送出されたスティッキービットとともに、正規化丸め回路11で仮数部の正規化及び丸めが行われる。正規化丸め回路11の出力が浮動小数点乗算結果の仮数部になる。

【0049】

このとき、0カウンタ10の出力であるシフト数は指数部補正回路12にも出力され、指数部補正回路12で指数部の補正を行い、浮動小数点乗算結果の符号と指数部を得る。選択回路13は、指数部補正回路12の出力と正規化丸め回路11の出力を合せて浮動小数点乗算の演算結果として出力する。

【0050】

(第1の実施の形態による効果)

本発明の第1の効果は、複数のデータ形式を1個の乗算回路でサポートするベクトル乗算処理装置の消費電力を低減できる、ということである。

【0051】

その理由は、乗算命令とデータ形式毎に乗算回路内にある部分積生成回路の動作の制御を行うことで、部分積生成回路の出力に関して結果として参照しない領域の動作を抑止するからである。

【0052】

(第2の実施の形態の構成)

次に、本発明の第2の実施の形態によるベクトル乗算処理装置20について、図9に示すベクトル演算処理装置20の構成図を用いて説明する。

【0053】

図9に示す本実施の形態によるベクトル乗算処理装置20において、図1に示す第1の実施の形態との差異は、ベクトルレジスタ1、およびベクトルレジスタ2と、乗算回路4との間に、非数検出回路14が付加されていることにある。非数検出回路14は、例えば、図10(b)に表2にとして示されている、IEEE浮動小数点データ形式の非数NaN(Not a Number)を検出し、その検出結果を、乗算回路4内の部分積制御回路42と、選択回路13とに送信する。ここでは、シグナル型のsNaNと、クワイエット型のqNaNが例示されている。他の構成は、図1に示す構成と同じである。

【0054】

(第2の実施の形態の動作)

IEEE浮動小数点演算では、浮動小数点の演算の結果として、不正なオペランドが与えられたために生じた結果を非数NaNとして出力するため、乗算回路4の結果は参照されない。したがって、浮動小数点乗算命令時に非数検出回路14の出力が非数である場合、部分積制御回路42より部分積生成回路41の全ての領域にoff信号を供給すれば、部分積生成回路41以降の回路全体の動作を停止させることが出来、このことにより、一層の消費電力を低減できる。

【0055】

(第2の実施の形態による効果)

本実施の形態によるベクトル乗算処理装置20によれれば、IEEE浮動小数点データ形式の非数を検出し、非数が検出された場合、部分積制御回路42より部分積生成回路41の全ての領域にoff信号を供給することで部分積生成回路41以降の回路全体の動作を停止させることができ、この場合、一層の消費電力の削減が可能になる。

【0056】

なお、図1、図9のベクトル乗算処理装置20の乗算回路4が有する機能は、全てをソフトウェアによって実現しても、あるいはその少なくとも一部をハードウェアで実現してもよい。例えば、乗算回路4が、オーバーフロー先見回路5とスティッキービット先見回路6とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、乗算命令とデータ形式とに応じて、部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する制御信号を生成し、部分積の生成を制御するデータ処理は、1または複数のプログラムによりコンピュータ上で実現してもよく、また、その少なくとも一部をハードウェアで実現してもよい。

【0057】

以上好ましい実施の形態と実施例をあげて本発明を説明したが、本発明は必ずしも、上述実施の形態及び実施例に限定されるものでなく、その技術的思想の範囲内において様々に変形して実施することができる。

【符号の説明】

【0058】

1、2:ベクトルレジスタ

3:前処理回路

4:乗算回路

5:固定小数点オーバーフロー先見回路

6:スティッキービット先見回路

7:浮動小数点加算器

8:固定小数点加算器

9:指数部加算器

10:0カウンタ

11:正規化丸め回路

12:指数部補正回路

13:選択回路

14:非数検出回路

20:ベクトル乗算処理装置

41:部分積生成回路

42:部分積制御回路

43:デコーダ

44:部分積加算器

【特許請求の範囲】

【請求項1】

固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、

前記オーバーフロー先見回路と前記スティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路、

を備えたことを特徴とするベクトル乗算処理装置。

【請求項2】

前記乗算回路は、

前記乗算命令が固定小数点演算命令か浮動小数点乗算命令かを示す命令種別と、前記入力される第1、第2オペラントが有するデータ長とに応じて、前記部分積生成に関して結果として参照されない領域の動作を抑止することを特徴とする請求項1に記載のベクトル乗算処理装置。

【請求項3】

前記乗算回路は、

前記乗算命令とデータ形式にしたがい、前記部分積生成に関して結果として参照されない領域の動作を抑止する制御信号を生成する部分積制御回路と、

前記部分積制御回路により出力される制御信号にしたがい前記第2のオペランドの仮数部から部分積を生成する部分積生成回路と、

を備えたことを特徴とする請求項1または請求項2に記載のベクトル乗算処理装置。

【請求項4】

入力される第1のオペランドと前記第2のオペランドを乗算命令とデータ形式にしたがって指数部と仮数部とに分割する前処理回路と、

前記部分積制御回路と部分積演算回路とを含み、前記第1のオペランドと前記第2のオペランドにそれぞれ接続される前記前処理回路の出力である仮数部の乗算を行う乗算回路と、

前記第1のオペランドと前記第2のオペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行う前記オーバーフロー先見回路と、

前記第1のオペランド仮数部及び第2のオペランド仮数部を入力としてスティッキービットを生成する前記スティッキービット先見回路と、

前記第1のオペランドと前記第2のオペランドにそれぞれ接続される前記前処理回路の出力である符号の判定及び指数部の加算を行う指数部加算器と、

前記乗算回路の出力の加算を行う浮動小数点加算器と、

前記乗算回路の出力の加算を行う固定小数点加算器と、

前記浮動小数点加算器の出力を入力として最上位ビット部位からのビット0の数をカウントする0カウンタと、

前記0カウンタの出力に従い前記浮動小数点加算器の出力をシフトして正規化及び丸めを行う正規化丸め回路と、

前記0カウンタの出力に従い前記指数部加算器の出力を補正する指数部補正回路と、

前記乗算命令が浮動小数点乗算を示す場合は、前記指数部補正回路の符号及び指数部出力と、前記正規化丸め回路の仮数部出力とを連結して浮動小数点乗算結果として出力し、前記乗算命令が固定小数点乗算を示す場合は、前記固定小数点加算器の出力を固定小数点の演算結果として出力する選択回路と、

を備えたことを特徴とする請求項1から請求項3のいずれか1項に記載のベクトル乗算処理装置。

【請求項5】

前記第1のオペランドが格納される第1のベクトルレジスタと、

前記第2のオペランドが格納される第2のベクトルレジスタ2と、

前記第1と第2のベクトルレジスタと、前記乗算回路との間に、不正なオペランドが入力されたために生じる結果を示す非数を検出して前記部分積検出回路を制御する非数検出回路を備え、

前記部分積制御回路は、

前記非数検出回路で非数が検出された場合、前記部分積生成回路の全ての範囲の回路動作を抑止することを特徴とする請求項1から請求項4のいずれか1項に記載のベクトル乗算処理装置。

【請求項6】

固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置に用いられるベクトル乗算処理方法であって、

前記オーバーフロー先見回路と前記スティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成するステップと、

前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止するステップと、

を有することを特徴とするベクトル乗算処理方法。

【請求項7】

コンピュータ上で実行され、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置のベクトル乗算処理プログラムであって、

前記コンピュータに、

前記オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成する部分積生成処理と、

前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する回路動作抑止処理と、

を実行させることを特徴とするベクトル乗算処理プログラム。

【請求項1】

固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置であって、

前記オーバーフロー先見回路と前記スティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成し、前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する乗算回路、

を備えたことを特徴とするベクトル乗算処理装置。

【請求項2】

前記乗算回路は、

前記乗算命令が固定小数点演算命令か浮動小数点乗算命令かを示す命令種別と、前記入力される第1、第2オペラントが有するデータ長とに応じて、前記部分積生成に関して結果として参照されない領域の動作を抑止することを特徴とする請求項1に記載のベクトル乗算処理装置。

【請求項3】

前記乗算回路は、

前記乗算命令とデータ形式にしたがい、前記部分積生成に関して結果として参照されない領域の動作を抑止する制御信号を生成する部分積制御回路と、

前記部分積制御回路により出力される制御信号にしたがい前記第2のオペランドの仮数部から部分積を生成する部分積生成回路と、

を備えたことを特徴とする請求項1または請求項2に記載のベクトル乗算処理装置。

【請求項4】

入力される第1のオペランドと前記第2のオペランドを乗算命令とデータ形式にしたがって指数部と仮数部とに分割する前処理回路と、

前記部分積制御回路と部分積演算回路とを含み、前記第1のオペランドと前記第2のオペランドにそれぞれ接続される前記前処理回路の出力である仮数部の乗算を行う乗算回路と、

前記第1のオペランドと前記第2のオペランドを入力として固定小数点乗算結果がオーバーフローするか否かの先見を行う前記オーバーフロー先見回路と、

前記第1のオペランド仮数部及び第2のオペランド仮数部を入力としてスティッキービットを生成する前記スティッキービット先見回路と、

前記第1のオペランドと前記第2のオペランドにそれぞれ接続される前記前処理回路の出力である符号の判定及び指数部の加算を行う指数部加算器と、

前記乗算回路の出力の加算を行う浮動小数点加算器と、

前記乗算回路の出力の加算を行う固定小数点加算器と、

前記浮動小数点加算器の出力を入力として最上位ビット部位からのビット0の数をカウントする0カウンタと、

前記0カウンタの出力に従い前記浮動小数点加算器の出力をシフトして正規化及び丸めを行う正規化丸め回路と、

前記0カウンタの出力に従い前記指数部加算器の出力を補正する指数部補正回路と、

前記乗算命令が浮動小数点乗算を示す場合は、前記指数部補正回路の符号及び指数部出力と、前記正規化丸め回路の仮数部出力とを連結して浮動小数点乗算結果として出力し、前記乗算命令が固定小数点乗算を示す場合は、前記固定小数点加算器の出力を固定小数点の演算結果として出力する選択回路と、

を備えたことを特徴とする請求項1から請求項3のいずれか1項に記載のベクトル乗算処理装置。

【請求項5】

前記第1のオペランドが格納される第1のベクトルレジスタと、

前記第2のオペランドが格納される第2のベクトルレジスタ2と、

前記第1と第2のベクトルレジスタと、前記乗算回路との間に、不正なオペランドが入力されたために生じる結果を示す非数を検出して前記部分積検出回路を制御する非数検出回路を備え、

前記部分積制御回路は、

前記非数検出回路で非数が検出された場合、前記部分積生成回路の全ての範囲の回路動作を抑止することを特徴とする請求項1から請求項4のいずれか1項に記載のベクトル乗算処理装置。

【請求項6】

固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置に用いられるベクトル乗算処理方法であって、

前記オーバーフロー先見回路と前記スティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成するステップと、

前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止するステップと、

を有することを特徴とするベクトル乗算処理方法。

【請求項7】

コンピュータ上で実行され、固定小数点データ形式のオーバーフロー先見回路と、浮動小数点データ形式のスティッキービット先見回路と、を少なくとも備え、乗算命令に基づき入力される第1オペランドと第2オペランドの積を算出するベクトル乗算処理装置のベクトル乗算処理プログラムであって、

前記コンピュータに、

前記オーバーフロー先見回路とスティッキービット先見回路とを使用し、入力される第1オペランドと第2オペランドとの部分積を生成する部分積生成処理と、

前記乗算命令とデータ形式とに応じて、前記部分積の生成に関し、結果的に参照されない特定範囲の回路動作を抑止する回路動作抑止処理と、

を実行させることを特徴とするベクトル乗算処理プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−238011(P2010−238011A)

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願番号】特願2009−86006(P2009−86006)

【出願日】平成21年3月31日(2009.3.31)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成22年10月21日(2010.10.21)

【国際特許分類】

【出願日】平成21年3月31日(2009.3.31)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]