ベクトル積和演算回路

【課題】 ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことが可能なベクトル積和演算回路を提供する。

【解決手段】 マスクレジスタ31〜33は各オペランド毎にデータの有効/無効を示すマスクビットを格納する。制御回路11〜13は演算モードと各オペランドに付随するマスクビットとから選択信号を生成する。機能セレクタ1〜3は各オペランドを入力とし、オペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを制御回路11〜13からの選択信号にしたがって選択し、積和演算回路の各回路に出力する。

【解決手段】 マスクレジスタ31〜33は各オペランド毎にデータの有効/無効を示すマスクビットを格納する。制御回路11〜13は演算モードと各オペランドに付随するマスクビットとから選択信号を生成する。機能セレクタ1〜3は各オペランドを入力とし、オペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを制御回路11〜13からの選択信号にしたがって選択し、積和演算回路の各回路に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はベクトルデータ積和演算回路に関し、特にベクトルデータであるオペランドを加算回路、減算回路、乗算回路を用いて積和演算を行う浮動小数点積和演算回路を含むベクトル積和演算回路に関する。

【背景技術】

【0002】

浮動小数点は、数値を仮数部と指数部とで表現するもので、例えば数値nは、仮数部をa、指数部をbとすると、n=a・rb (rは基数)で表される。また、指数部は符号を付して表現されたり、ある特定の数を基準とし、その数に対する大小で表すバイアス表現で表される。

【0003】

浮動小数点で表現された数値を用いて演算を行う場合、固定小数点で表現された数値を用いて演算を行う場合に比べ、広い範囲(広いダイナミックレンジ)での数の演算が可能である。このため、扱う数値範囲を広く要求される(広いダイナミックレンジが要求される)用途においては、浮動小数点で表現された数値の演算を行う浮動小数点演算回路が用いられている。

【0004】

例えば、指数部がバイアス表現された2つの数値、m=a・rc と、n=b・rd (但し、c>d)の浮動小数点数値の加算を考えてみる。この場合、加算結果(和)は、m+n=(a+bc-d )・rc となる。このように、浮動小数点数値の加減算を実行する場合には、第1オペランドの指数部と第2オペランドの指数部との減算を行い、その結果から桁合わせを行うために一方の仮数部をシフトする必要がある(例えば、特許文献1参照)。

【0005】

上記の浮動小数点の演算を行うベクトル積和演算回路においては、図9に示すように、ベクトルレジスタ21,22に格納される第1オペランド(以下、第1OPとする)と第2オペランド(以下、第2OPとする)との積を求め、その結果とベクトルレジスタ23に格納される第3オペランド(以下、第3OPとする)との和を求める構成がある。

【0006】

図9において、ベクトル積和演算回路は仮数部乗算回路4と、仮数部加算器5と、指数部加算器6と、指数部減算器7と、シフト回路8と、正規化回路9と、丸め回路10と、0カウンタ14と、指数部補正回路15と、ベクトルレジスタ21と、ベクトルレジスタ22と、ベクトルレジスタ23とから構成されている。

【0007】

この構成において、第1OPと第2OPとの乗算のみを行う場合、第3OPを格納するベクトルレジスタ23の各要素を“0”で埋め、「第1OP*第2OP+“0”」の演算を行う必要がある。

【0008】

また、第1OPあるいは第2OPと第3OPとの加減算を行う場合には、第1OPと第2OPとのうちの対象でない方のベクトルレジスタ21,22の各要素を“1”に書換えて「オペランド*1の乗算」を行った後に、その乗算結果と第3OPとの加減算を行っている。そのため、上記の積和演算回路を用いて2つのオペランドの乗算、あるいは加減算を行う際に、対象でないオペランドデータを格納するベクトルレジスタ21〜23の各要素を書換える必要がある。

【0009】

【特許文献1】特開平08−263269号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上述した従来のベクトル積和演算回路では、積和演算回路を用いて2オペランドの乗算あるいは加減算を行う際に、積和演算回路への入力となる3オペランドのうち、対象でないオペランドデータを格納するベクトルレジスタの各要素を書換える必要があるため、処理に時間が掛かるという問題がある。

【0011】

そこで、本発明の目的は上記の問題点を解消し、ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことができるベクトル積和演算回路を提供することにある。

【課題を解決するための手段】

【0012】

本発明によるベクトル積和演算回路は、少なくとも第1のオペランドと第2のオペランドと第3のオペランドとを入力して、それらの積和を求める積和回路を含むベクトル積和演算回路であって、

外部から指定される演算モードに基いて前記オペランドと予め設定された所定値のデータとのいずれかを選択して前記積和回路に出力する機能セレクタを備えている。

【0013】

すなわち、本発明のベクトル積和演算回路は、各オペランド毎にデータの有効/無効を示すマスクビットを格納するマスクレジスタと、演算モードと各オペランドに付随するマスクビットとから選択信号を生成する制御回路と、各オペランドを入力としかつオペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを選択信号にしたがって選択する機能セレクタとを有している。

【0014】

本発明のベクトル積和演算回路では、上記のような構成を採用し、演算モードとマスクビットとの組合わせを機能セレクタが持つ各機能に割当てることで、ベクトルレジスタの各要素を書換えることなく、マスクビットと演算モードとの切替えのみで様々な演算を行うことによって、2つのオペランドの演算を容易に行うことが可能となる。

【発明の効果】

【0015】

本発明は、以下に述べるような構成及び動作とすることで、ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことができるという効果が得られる。

【発明を実施するための最良の形態】

【0016】

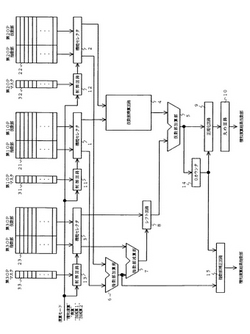

次に、本発明の実施例について図面を参照して説明する。図1は本発明の一実施例によるベクトル積和演算回路の構成を示すブロック図である。図1において、本発明の一実施例によるベクトル積和演算回路は機能セレクタ1〜3と、仮数部乗算回路4と、仮数部加算器5と、指数部加算器6と、指数部減算器7と、シフト回路8と、正規化回路9と、丸め回路10と、制御回路11〜13と、0カウンタ14と、指数部補正回路15と、ベクトルレジスタ21〜23と、マスクレジスタ31〜マスクレジスタ33とから構成されている。

【0017】

ベクトルレジスタ21は機能セレクタ1と接続され、第1オペランド(以下、第1OPとする)を格納する。ベクトルレジスタ22は機能セレクタ2と接続され、第2オペランド(以下、第2OPとする)を格納する。ベクトルレジスタ23は機能セレクタ3と接続され、第3オペランド(以下、第3OPとする)を格納する。

【0018】

マスクレジスタ31は制御回路11と接続され、第1OPの各要素の有効/無効を示すマスクビットを格納する。マスクレジスタ32は制御回路12と接続され、第2OPの各要素の有効/無効を示すマスクビットを格納する。マスクレジスタ33は制御回路13と接続され、第3OPの各要素の有効/無効を示すマスクビットを格納する。

【0019】

制御回路11は機能セレクタ1及びマスクレジスタ31と接続され、マスクレジスタ31から供給される第1OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ1へ出力する。すなわち、制御回路11は機能セレクタ1で“0”が選択される時に制御信号“00”を、機能セレクタ1で“1”が選択される時に制御信号“01”を、機能セレクタ1で第1OPが選択される時に制御信号“10”をそれぞれ生成する。

【0020】

制御回路12は機能セレクタ2及びマスクレジスタ32と接続され、マスクレジスタ32から供給される第2OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ2へ出力する。すなわち、制御回路12は機能セレクタ2で“0”が選択される時に制御信号“00”を、機能セレクタ2で“1”が選択される時に制御信号“01”を、機能セレクタ2で第2OPが選択される時に制御信号“10”をそれぞれ生成する。

【0021】

制御回路13は機能セレクタ3及びマスクレジスタ33と接続され、マスクレジスタ33から供給される第3OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ3へ出力する。すなわち、制御回路13は機能セレクタ3で“0”が選択される時に制御信号“0”を、機能セレクタ3で第3OPが選択される時に制御信号“1”をそれぞれ生成する。

【0022】

機能セレクタ1は制御回路11とベクトルレジスタ21と仮数部乗算回路4と指数部加算器6とにそれぞれ接続され、制御回路11の出力である制御信号にしたがって第1OP、“0”、“1”の何れかを選択し、その選択結果を仮数部乗算回路4及び指数部加算器6に出力する。

【0023】

機能セレクタ2は制御回路12とベクトルレジスタ22と仮数部乗算回路4と指数部加算器6とにそれぞれ接続され、制御回路12の出力である制御信号にしたがって第2OP、“0”、“1”の何れかを選択し、その選択結果を仮数部乗算回路4及び指数部加算器6に出力する。

【0024】

機能セレクタ3は制御回路13とベクトルレジスタ23と指数部減算器7とシフト回路8とにそれぞれ接続され、制御回路13の出力である制御信号にしたがって第3OP、“0”、“1”の何れかを選択し、その選択結果を指数部減算器7及びシフト回路8に出力する。

【0025】

指数部加算器6は機能セレクタ1と機能セレクタ2と指数部減算器7と指数部補正回路15とにそれぞれ接続され、機能セレクタ1,2の出力である選択結果の指数部の加算を行い、指数部加算結果を指数部減算器7及び指数部補正回路15に出力する。

【0026】

指数部減算器7は機能セレクタ3と指数部加算器6とシフト回路8とにそれぞれ接続され、指数部加算器6の出力である指数部加算結果と機能セレクタ3の出力である選択結果の指数部との減算を行い、指数部減算結果をシフト回路8へ出力する。この場合、指数部減算結果は第3OPの仮数部を桁合わせする際のシフト量になる。

【0027】

シフト回路8は機能セレクタ3と指数部減算器7と仮数部加算器5とにそれぞれ接続され、機能セレクタ3の出力である選択結果の仮数部に対して指数部減算器7の出力であるシフト量にしたがってシフト動作を行い、その結果を仮数部加算器5に出力する。

【0028】

仮数部乗算回路4は機能セレクタ1と機能セレクタ2と仮数部加算器5とにそれぞれ接続され、機能セレクタ1,2の出力である選択結果の仮数部同士について乗算を行い、乗算結果を仮数部加算器5に出力する。

【0029】

仮数部加算器5は仮数部乗算回路4とシフト回路8と正規化回路9と0カウンタ14とにそれぞれ接続され、仮数部乗算回路4の出力である乗算結果とシフト回路8の出力であるシフト結果との加算を行い、その結果を正規化回路9及び0カウンタ14へ出力する。

【0030】

0カウンタ14は仮数部加算器5と正規化回路9と指数部補正回路15とにそれぞれ接続され、仮数部加算器5の出力を入力としてMSB(Most Significant Bit)からのビット0の数をカウントして正規化回路9及び指数部補正回路15に出力する。

【0031】

正規化回路9は仮数部加算器5と0カウンタ14と丸め回路10とにそれぞれ接続され、0カウンタ14の出力にしたがって仮数部加算器5の出力をシフトして、その結果を丸め回路10へ出力する。丸め回路10は正規化回路9に接続され、正規化回路9の出力を入力として丸め処理を行う。この丸め処理の結果は積和演算結果の仮数部となる。

【0032】

指数部補正回路15は指数部加算器6と0カウンタ14とにそれぞれ接続され、0カウンタ14の出力にしたがって指数部加算器6の出力を補正する。この補正処理の結果は積和演算結果の指数部となる。

【0033】

図2は図1に示す制御回路11の構成を示す回路図である。図2において、制御回路11は演算モード(“積和演算”、“乗算”、“加減算1”、“加減算2”)の論理積演算を行う論理積回路111〜114と、論理積回路111〜113各々の出力の論理和演算を行う論理和回路115と、論理和回路115の出力とマスクビットとの論理積演算を行う論理積回路116と、論理積回路114の出力とマスクビットとの論理積演算を行う論理積回路117とから構成されている。

【0034】

図3は図1に示す制御回路12の構成を示す回路図である。図3において、制御回路12は演算モードの論理積演算を行う論理積回路121〜124と、論理積回路121〜123各々の出力の論理和演算を行う論理和回路125と、論理和回路125の出力とマスクビットとの論理積演算を行う論理積回路126と、論理積回路124の出力とマスクビットとの論理積演算を行う論理積回路127とから構成されている。

【0035】

図4は図1に示す制御回路13の構成を示す回路図である。図4において、制御回路13は演算モードの論理積演算を行う論理積回路131〜133と、論理積回路131〜133各々の出力の論理和演算を行う論理和回路134と、論理和回路134の出力とマスクビットとの論理積演算を行う論理積回路135とから構成されている。

【0036】

図5は図1に示す機能セレクタ1の構成を示す図である。図5において、機能セレクタ1はセレクタ1a,1bによって構成されている。機能セレクタ1のセレクタ1aは制御回路11からの制御信号にしたがって“0”,“1”,第1OPのいずれかを選択してセレクタ1bに出力し、セレクタ1bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0037】

図6は図1に示す機能セレクタ2の構成を示す図である。図6において、機能セレクタ2はセレクタ2a,2bによって構成されている。機能セレクタ2のセレクタ2aは制御回路12からの制御信号にしたがって“0”,“1”,第2OPのいずれかを選択してセレクタ2bに出力し、セレクタ2bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0038】

図7は図1に示す機能セレクタ3の構成を示す図である。図7において、機能セレクタ3はセレクタ3a,3bによって構成されている。機能セレクタ3のセレクタ3aは制御回路13からの制御信号にしたがって“0”,第1OPのいずれかを選択してセレクタ3bに出力し、セレクタ3bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0039】

図8(a)は図1に示す機能セレクタ1の選択結果を示す図であり、図8(b)は図1に示す機能セレクタ2の選択結果を示す図であり、図8(c)は図1に示す機能セレクタ3の選択結果を示す図である。

【0040】

図8(a)において、機能セレクタ1は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“1”を選択する。

【0041】

図8(b)において、機能セレクタ1は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。機能セレクタ2は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。機能セレクタ2は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“1”を選択する。機能セレクタ2は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。

【0042】

図8(c)において、機能セレクタ3は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。機能セレクタ3は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“0”を選択する。機能セレクタ3は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。機能セレクタ3は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。

【0043】

これら図1〜図8を参照して本発明の一実施例によるベクトル積和演算回路の動作について説明する。本実施例によるベクトル積和演算回路は、ベクトルデータに対するマスク付き浮動小数点積和演算、すなわち、

R=(Ma[i]*A[i])*(Mb[i]*B[i])

+(Mc[i]*C[i])

という計算を行う。ここで、A[i]は第1OP、B[i]は第2OP、C[i]は第3OP、Ma[i]、Mb[i]、Mc[i]はそれぞれ各オペランドOPに対するマスクビットの値を表す。

【0044】

マスクビットは各オペランド毎に設けられ、データの有効/無効を示す。ここではマスクビット=1の時にデータ有効、マスクビット=0の時にデータ無効、とする。尚、本実施例によるベクトル積和演算回路は、A[i]あるいはB[i]を“1”にすることによって2オペランドの加減算器として、またC[i]を“0”にすることによって2オペランドの乗算器として動作する。

【0045】

まず、積和演算を実行する場合の動作について説明する。この場合、制御回路11〜13各々へ送出される演算モードは“積和演算”が指定される。“積和演算”を示す信号=1の際には、他の演算モード“乗算”、“加減算1”、“加減算2”を示す信号はそれぞれ0となり、各モードを示す信号は排他の関係にある。

【0046】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第1OPを選択する制御信号“10”をそれぞれ機能セレクタ1へ送出する。

【0047】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第2OPを選択する制御信号“10”を機能セレクタ2へ送出する。

【0048】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“0”を、マスクビットが「1」ならば第3OPを選択する制御信号“1”を機能セレクタ3へ送出する。

【0049】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0050】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0051】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号にしたがって第3OPを選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。

【0052】

機能セレクタ1〜3各々は演算モードとマスクビットとによって、図8に示すようなデータを選択する。機能セレクタ1,2で選択された第1OP及び第2OPの指数部は指数部加算器6にて加算が行われ、得られた指数部加算結果を指数部減算器7と指数部補正回路15とに出力する。機能セレクタ3で選択された第3OPの指数部は指数部減算器7にて指数部加算器6の出力との差(第1OP及び第2OPの指数部の和から第3OPの指数を引いた値)を求め、その結果をシフト回路8へ送出し、シフト回路8では機能セレクタ3で選択された第3OPの仮数部に対してシフト動作を行う。

【0053】

指数部減算器7の結果の絶対値がシフト回路8で使用するシフトビット数となる。指数部減算器7の結果が負の場合には第3OPの指数の方が大きいので左シフトとなり、指数部減算器7の結果が正の場合には逆に小さいので右シフトとなる。シフトした結果が第1OP及び第2OPの仮数部乗算結果に対する桁合わせした結果となり、これを仮数部加算器5へ送出する。

【0054】

第1OP及び第2OPの仮数部は仮数部乗算回路4に入力され、仮数部乗算回路4にて乗算が行われた結果が仮数部加算器5へ送出される。仮数部加算器5は仮数部乗算回路4の出力である第1OP及び第2OPの仮数部乗算結果とシフト回路8の出力である第3OPの仮数部の桁合わせ結果とを加算し、その結果を正規化回路9と0カウンタ14とに送出する。

【0055】

0カウンタ14では加算結果のMSBからビット0の数をカウントして正規化のためのシフト数が求められる。このシフト数は正規化回路9へ送出され、正規化回路9にて仮数部の正規化が行われる。また、0カウンタ14の出力であるシフト数は指数部補正回路15にも送出され、指数部補正回路15にて指数部の正規化が行われ、積和演算結果の指数部が得られる。正規化回路9の出力に対しては丸め回路10にて丸め処理が行われ、積和演算結果の仮数部が得られる。

【0056】

次に、2オペランドの乗算を実行する場合の動作について説明する。この場合、制御回路11〜13へ送出される演算モードには“乗算”が指定される。“乗算”を示す信号=1の際には、他の演算モード“積和演算”、“加減算1”、“加減算2”を示す信号はそれぞれ0となる。

【0057】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第1OPを選択する制御信号“10”をそれぞれ機能セレクタ1へ送出する。

【0058】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第2OPを選択する制御信号“10”をそれぞれ機能セレクタ2へ送出する。

【0059】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットの値によらず“0”を選択する制御信号“0”を機能セレクタ3へ送出する。これは2オペランドの乗算では必要ない加算項の第3OPを“0”とするためである。

【0060】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0061】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0062】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号“0”にしたがって“0”を選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。以降、第3OPの値は“0”として扱われ、シフト回路8の出力も“0”となる。

【0063】

仮数部加算器5は仮数部乗算回路4の出力である第1OP及び第2OPの仮数部乗算結果と“0”との加算を行うため、仮数部加算器5の出力は第1OP及び第2OPの仮数部乗算結果に等しい。したがって、最終的な演算結果として得られるのは第1OP及び第2OPの乗算結果になる。

【0064】

次に、2オペランドの加減算を実行する場合の動作について説明する。制御回路11〜13各々へ送出される演算モードは“加減算”が指定される。この時、「第1OP+第3OP」の加減算の際には“加減算1”が、「第2OP+第3OP」の加減算の際には“加減算2”がそれぞれ指定される。“加減算1”を示す信号=1の際には他の演算モード“積和演算”、“乗算”、“加減算2”を示す信号はそれぞれ0となり、“加減算2”を示す信号=1の際には他の演算モード“積和演算”、“乗算”、“加減算1”を示す信号がそれぞれ0となる。

【0065】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」でかつ演算モードが“加減算1”ならば第1OPを選択する制御信号“10”を、マスクビットが「1」でかつ演算モードが“加減算2”ならば“1”を選択する制御信号“01”をそれぞれ機能セレクタ1へ送出する。これは「第2OP+第3OP」の加減算の際に、第1OPの値を“1”にすることで、乗算項を、「“1”*第2OP(=第2OP)」とするためである。

【0066】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」でかつ演算モードが“加減算1”ならば“1”を選択する制御信号“01”を、マスクビットが「1」でかつ演算モードが“加減算2”ならば第2OPを選択する制御信号“10”をそれぞれ機能セレクタ2へ送出する。これは「第1OP+第3OP」の加減算の際に、第2OPの値を“1”にすることで、乗算項を、「第1OP*“1”(=第1OP)」とするためである。

【0067】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“0”を、マスクビットが「1」ならば第3OPを選択する制御信号“1”をそれぞれ機能セレクタ3へ送出する。

【0068】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPあるいは“1”を選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0069】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPあるいは“1”を選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0070】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号にしたがって第3OPを選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。

【0071】

仮数部乗算回路4は“1”*第2OPあるいは第1OP*“1”の乗算を行うので、仮数部乗算回路4の出力は第1OPあるいは第2OPの仮数部になる。仮数部加算器5にて桁合わせされた第3OPの仮数部と第1OPあるいは第2OPの仮数部との加算を行う。したがって、最終的な演算結果として得られるのは第1OP及び第3OPの加減算結果、あるいは第2OP及び第3OPの加減算結果になる。

【0072】

尚、演算モードに“加減算1”または“加減算2”を指定し、マスクレジスタ33を“0”で埋めることで、「第1OP*“1”+“0”」、あるいは「“1”*第2OP+“0”」の演算を実現することができる。また、マスクレジスタ31,32を“0”で埋めることで、「“0”+第3OP」の演算を実現することができる。

【0073】

このように、本実施例では、マスクビットと演算モードとの組合わせによって各オペランドデータのバイパス動作を可能にする。以上のように、各オペランドを格納するベクトルレジスタ21〜23それぞれにマスクビットを格納するマスクレジスタ31〜33を設け、各オペランド毎にマスクビットと演算モードとの組合わせから積和演算回路へ入力するデータを選択することによって、ベクトルレジスタ21〜23の各要素を書換えて2オペランドの乗算、あるいは加減算を行う積和演算回路よりも処理時間を短縮することができる。

【0074】

上述したように、本実施例では、ベクトルデータであるオペランド毎にデータの有効/無効を示すマスクビットを設け、マスクビットと演算モードとの組合わせによってデータを選択する機能セレクタ1〜3を設けることによって、ベクトルレジスタ21〜23の各要素を書換えることなく、マスクビットと演算モードとの切替えのみで様々な演算を行うことが可能となるため、積和演算回路で2オペランドの乗算、あるいは加減算を行う際の処理時間を短縮することができる。

【図面の簡単な説明】

【0075】

【図1】本発明の一実施例によるベクトル積和演算回路の構成を示すブロック図である。

【図2】図1に示す制御回路11の構成を示す回路図である。

【図3】図1に示す制御回路12の構成を示す回路図である。

【図4】図1に示す制御回路13の構成を示す回路図である。

【図5】図1に示す機能セレクタ1の構成を示す図である。

【図6】図1に示す機能セレクタ2の構成を示す図である。

【図7】図1に示す機能セレクタ3の構成を示す図である。

【図8】(a)は図1に示す機能セレクタ1の選択結果を示す図、(b)は図1に示す機能セレクタ2の選択結果を示す図、(c)は図1に示す機能セレクタ3の選択結果を示す図である。

【図9】従来例のベクトル積和演算回路の構成を示すブロック図である。

【符号の説明】

【0076】

1〜3 機能セレクタ

1a,1b,2a,

2b,3a,3b セレクタ

4 仮数部乗算回路

5 仮数部加算器

6 指数部加算器

7 指数部減算器

8 シフト回路

9 正規化回路

10 丸め回路

11〜12 制御回路

14 0カウンタ

15 指数部補正回路

21〜23 ベクトルレジスタ

31〜33 マスクレジスタ

111〜114,

116,117,

121〜124,

126,127,

131〜133,

135 論理積回路

115,125,

134 論理和回路

【技術分野】

【0001】

本発明はベクトルデータ積和演算回路に関し、特にベクトルデータであるオペランドを加算回路、減算回路、乗算回路を用いて積和演算を行う浮動小数点積和演算回路を含むベクトル積和演算回路に関する。

【背景技術】

【0002】

浮動小数点は、数値を仮数部と指数部とで表現するもので、例えば数値nは、仮数部をa、指数部をbとすると、n=a・rb (rは基数)で表される。また、指数部は符号を付して表現されたり、ある特定の数を基準とし、その数に対する大小で表すバイアス表現で表される。

【0003】

浮動小数点で表現された数値を用いて演算を行う場合、固定小数点で表現された数値を用いて演算を行う場合に比べ、広い範囲(広いダイナミックレンジ)での数の演算が可能である。このため、扱う数値範囲を広く要求される(広いダイナミックレンジが要求される)用途においては、浮動小数点で表現された数値の演算を行う浮動小数点演算回路が用いられている。

【0004】

例えば、指数部がバイアス表現された2つの数値、m=a・rc と、n=b・rd (但し、c>d)の浮動小数点数値の加算を考えてみる。この場合、加算結果(和)は、m+n=(a+bc-d )・rc となる。このように、浮動小数点数値の加減算を実行する場合には、第1オペランドの指数部と第2オペランドの指数部との減算を行い、その結果から桁合わせを行うために一方の仮数部をシフトする必要がある(例えば、特許文献1参照)。

【0005】

上記の浮動小数点の演算を行うベクトル積和演算回路においては、図9に示すように、ベクトルレジスタ21,22に格納される第1オペランド(以下、第1OPとする)と第2オペランド(以下、第2OPとする)との積を求め、その結果とベクトルレジスタ23に格納される第3オペランド(以下、第3OPとする)との和を求める構成がある。

【0006】

図9において、ベクトル積和演算回路は仮数部乗算回路4と、仮数部加算器5と、指数部加算器6と、指数部減算器7と、シフト回路8と、正規化回路9と、丸め回路10と、0カウンタ14と、指数部補正回路15と、ベクトルレジスタ21と、ベクトルレジスタ22と、ベクトルレジスタ23とから構成されている。

【0007】

この構成において、第1OPと第2OPとの乗算のみを行う場合、第3OPを格納するベクトルレジスタ23の各要素を“0”で埋め、「第1OP*第2OP+“0”」の演算を行う必要がある。

【0008】

また、第1OPあるいは第2OPと第3OPとの加減算を行う場合には、第1OPと第2OPとのうちの対象でない方のベクトルレジスタ21,22の各要素を“1”に書換えて「オペランド*1の乗算」を行った後に、その乗算結果と第3OPとの加減算を行っている。そのため、上記の積和演算回路を用いて2つのオペランドの乗算、あるいは加減算を行う際に、対象でないオペランドデータを格納するベクトルレジスタ21〜23の各要素を書換える必要がある。

【0009】

【特許文献1】特開平08−263269号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

上述した従来のベクトル積和演算回路では、積和演算回路を用いて2オペランドの乗算あるいは加減算を行う際に、積和演算回路への入力となる3オペランドのうち、対象でないオペランドデータを格納するベクトルレジスタの各要素を書換える必要があるため、処理に時間が掛かるという問題がある。

【0011】

そこで、本発明の目的は上記の問題点を解消し、ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことができるベクトル積和演算回路を提供することにある。

【課題を解決するための手段】

【0012】

本発明によるベクトル積和演算回路は、少なくとも第1のオペランドと第2のオペランドと第3のオペランドとを入力して、それらの積和を求める積和回路を含むベクトル積和演算回路であって、

外部から指定される演算モードに基いて前記オペランドと予め設定された所定値のデータとのいずれかを選択して前記積和回路に出力する機能セレクタを備えている。

【0013】

すなわち、本発明のベクトル積和演算回路は、各オペランド毎にデータの有効/無効を示すマスクビットを格納するマスクレジスタと、演算モードと各オペランドに付随するマスクビットとから選択信号を生成する制御回路と、各オペランドを入力としかつオペランドデータと予め設定された所定値(“0”または“1”)とのうちのいずれかを選択信号にしたがって選択する機能セレクタとを有している。

【0014】

本発明のベクトル積和演算回路では、上記のような構成を採用し、演算モードとマスクビットとの組合わせを機能セレクタが持つ各機能に割当てることで、ベクトルレジスタの各要素を書換えることなく、マスクビットと演算モードとの切替えのみで様々な演算を行うことによって、2つのオペランドの演算を容易に行うことが可能となる。

【発明の効果】

【0015】

本発明は、以下に述べるような構成及び動作とすることで、ベクトルレジスタの各要素の書換えを行うことなく、2つのオペランドの演算を容易に行うことができるという効果が得られる。

【発明を実施するための最良の形態】

【0016】

次に、本発明の実施例について図面を参照して説明する。図1は本発明の一実施例によるベクトル積和演算回路の構成を示すブロック図である。図1において、本発明の一実施例によるベクトル積和演算回路は機能セレクタ1〜3と、仮数部乗算回路4と、仮数部加算器5と、指数部加算器6と、指数部減算器7と、シフト回路8と、正規化回路9と、丸め回路10と、制御回路11〜13と、0カウンタ14と、指数部補正回路15と、ベクトルレジスタ21〜23と、マスクレジスタ31〜マスクレジスタ33とから構成されている。

【0017】

ベクトルレジスタ21は機能セレクタ1と接続され、第1オペランド(以下、第1OPとする)を格納する。ベクトルレジスタ22は機能セレクタ2と接続され、第2オペランド(以下、第2OPとする)を格納する。ベクトルレジスタ23は機能セレクタ3と接続され、第3オペランド(以下、第3OPとする)を格納する。

【0018】

マスクレジスタ31は制御回路11と接続され、第1OPの各要素の有効/無効を示すマスクビットを格納する。マスクレジスタ32は制御回路12と接続され、第2OPの各要素の有効/無効を示すマスクビットを格納する。マスクレジスタ33は制御回路13と接続され、第3OPの各要素の有効/無効を示すマスクビットを格納する。

【0019】

制御回路11は機能セレクタ1及びマスクレジスタ31と接続され、マスクレジスタ31から供給される第1OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ1へ出力する。すなわち、制御回路11は機能セレクタ1で“0”が選択される時に制御信号“00”を、機能セレクタ1で“1”が選択される時に制御信号“01”を、機能セレクタ1で第1OPが選択される時に制御信号“10”をそれぞれ生成する。

【0020】

制御回路12は機能セレクタ2及びマスクレジスタ32と接続され、マスクレジスタ32から供給される第2OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ2へ出力する。すなわち、制御回路12は機能セレクタ2で“0”が選択される時に制御信号“00”を、機能セレクタ2で“1”が選択される時に制御信号“01”を、機能セレクタ2で第2OPが選択される時に制御信号“10”をそれぞれ生成する。

【0021】

制御回路13は機能セレクタ3及びマスクレジスタ33と接続され、マスクレジスタ33から供給される第3OPに付随するマスクビットと演算モードとにしたがって選択用の制御信号を生成し、その制御信号を機能セレクタ3へ出力する。すなわち、制御回路13は機能セレクタ3で“0”が選択される時に制御信号“0”を、機能セレクタ3で第3OPが選択される時に制御信号“1”をそれぞれ生成する。

【0022】

機能セレクタ1は制御回路11とベクトルレジスタ21と仮数部乗算回路4と指数部加算器6とにそれぞれ接続され、制御回路11の出力である制御信号にしたがって第1OP、“0”、“1”の何れかを選択し、その選択結果を仮数部乗算回路4及び指数部加算器6に出力する。

【0023】

機能セレクタ2は制御回路12とベクトルレジスタ22と仮数部乗算回路4と指数部加算器6とにそれぞれ接続され、制御回路12の出力である制御信号にしたがって第2OP、“0”、“1”の何れかを選択し、その選択結果を仮数部乗算回路4及び指数部加算器6に出力する。

【0024】

機能セレクタ3は制御回路13とベクトルレジスタ23と指数部減算器7とシフト回路8とにそれぞれ接続され、制御回路13の出力である制御信号にしたがって第3OP、“0”、“1”の何れかを選択し、その選択結果を指数部減算器7及びシフト回路8に出力する。

【0025】

指数部加算器6は機能セレクタ1と機能セレクタ2と指数部減算器7と指数部補正回路15とにそれぞれ接続され、機能セレクタ1,2の出力である選択結果の指数部の加算を行い、指数部加算結果を指数部減算器7及び指数部補正回路15に出力する。

【0026】

指数部減算器7は機能セレクタ3と指数部加算器6とシフト回路8とにそれぞれ接続され、指数部加算器6の出力である指数部加算結果と機能セレクタ3の出力である選択結果の指数部との減算を行い、指数部減算結果をシフト回路8へ出力する。この場合、指数部減算結果は第3OPの仮数部を桁合わせする際のシフト量になる。

【0027】

シフト回路8は機能セレクタ3と指数部減算器7と仮数部加算器5とにそれぞれ接続され、機能セレクタ3の出力である選択結果の仮数部に対して指数部減算器7の出力であるシフト量にしたがってシフト動作を行い、その結果を仮数部加算器5に出力する。

【0028】

仮数部乗算回路4は機能セレクタ1と機能セレクタ2と仮数部加算器5とにそれぞれ接続され、機能セレクタ1,2の出力である選択結果の仮数部同士について乗算を行い、乗算結果を仮数部加算器5に出力する。

【0029】

仮数部加算器5は仮数部乗算回路4とシフト回路8と正規化回路9と0カウンタ14とにそれぞれ接続され、仮数部乗算回路4の出力である乗算結果とシフト回路8の出力であるシフト結果との加算を行い、その結果を正規化回路9及び0カウンタ14へ出力する。

【0030】

0カウンタ14は仮数部加算器5と正規化回路9と指数部補正回路15とにそれぞれ接続され、仮数部加算器5の出力を入力としてMSB(Most Significant Bit)からのビット0の数をカウントして正規化回路9及び指数部補正回路15に出力する。

【0031】

正規化回路9は仮数部加算器5と0カウンタ14と丸め回路10とにそれぞれ接続され、0カウンタ14の出力にしたがって仮数部加算器5の出力をシフトして、その結果を丸め回路10へ出力する。丸め回路10は正規化回路9に接続され、正規化回路9の出力を入力として丸め処理を行う。この丸め処理の結果は積和演算結果の仮数部となる。

【0032】

指数部補正回路15は指数部加算器6と0カウンタ14とにそれぞれ接続され、0カウンタ14の出力にしたがって指数部加算器6の出力を補正する。この補正処理の結果は積和演算結果の指数部となる。

【0033】

図2は図1に示す制御回路11の構成を示す回路図である。図2において、制御回路11は演算モード(“積和演算”、“乗算”、“加減算1”、“加減算2”)の論理積演算を行う論理積回路111〜114と、論理積回路111〜113各々の出力の論理和演算を行う論理和回路115と、論理和回路115の出力とマスクビットとの論理積演算を行う論理積回路116と、論理積回路114の出力とマスクビットとの論理積演算を行う論理積回路117とから構成されている。

【0034】

図3は図1に示す制御回路12の構成を示す回路図である。図3において、制御回路12は演算モードの論理積演算を行う論理積回路121〜124と、論理積回路121〜123各々の出力の論理和演算を行う論理和回路125と、論理和回路125の出力とマスクビットとの論理積演算を行う論理積回路126と、論理積回路124の出力とマスクビットとの論理積演算を行う論理積回路127とから構成されている。

【0035】

図4は図1に示す制御回路13の構成を示す回路図である。図4において、制御回路13は演算モードの論理積演算を行う論理積回路131〜133と、論理積回路131〜133各々の出力の論理和演算を行う論理和回路134と、論理和回路134の出力とマスクビットとの論理積演算を行う論理積回路135とから構成されている。

【0036】

図5は図1に示す機能セレクタ1の構成を示す図である。図5において、機能セレクタ1はセレクタ1a,1bによって構成されている。機能セレクタ1のセレクタ1aは制御回路11からの制御信号にしたがって“0”,“1”,第1OPのいずれかを選択してセレクタ1bに出力し、セレクタ1bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0037】

図6は図1に示す機能セレクタ2の構成を示す図である。図6において、機能セレクタ2はセレクタ2a,2bによって構成されている。機能セレクタ2のセレクタ2aは制御回路12からの制御信号にしたがって“0”,“1”,第2OPのいずれかを選択してセレクタ2bに出力し、セレクタ2bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0038】

図7は図1に示す機能セレクタ3の構成を示す図である。図7において、機能セレクタ3はセレクタ3a,3bによって構成されている。機能セレクタ3のセレクタ3aは制御回路13からの制御信号にしたがって“0”,第1OPのいずれかを選択してセレクタ3bに出力し、セレクタ3bはその選択された信号を指数部選択結果、仮数部選択結果とに分けて出力する。

【0039】

図8(a)は図1に示す機能セレクタ1の選択結果を示す図であり、図8(b)は図1に示す機能セレクタ2の選択結果を示す図であり、図8(c)は図1に示す機能セレクタ3の選択結果を示す図である。

【0040】

図8(a)において、機能セレクタ1は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第1OPを選択する。機能セレクタ1は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“1”を選択する。

【0041】

図8(b)において、機能セレクタ1は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。機能セレクタ2は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。機能セレクタ2は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“1”を選択する。機能セレクタ2は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第2OPを選択する。

【0042】

図8(c)において、機能セレクタ3は演算モードが“積和演算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。機能セレクタ3は演算モードが“乗算”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば“0”を選択する。機能セレクタ3は演算モードが“加減算1”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。機能セレクタ3は演算モードが“加減算2”の場合、マスクビットが「0」であれば“0”を、マスクビットが「1」であれば第3OPを選択する。

【0043】

これら図1〜図8を参照して本発明の一実施例によるベクトル積和演算回路の動作について説明する。本実施例によるベクトル積和演算回路は、ベクトルデータに対するマスク付き浮動小数点積和演算、すなわち、

R=(Ma[i]*A[i])*(Mb[i]*B[i])

+(Mc[i]*C[i])

という計算を行う。ここで、A[i]は第1OP、B[i]は第2OP、C[i]は第3OP、Ma[i]、Mb[i]、Mc[i]はそれぞれ各オペランドOPに対するマスクビットの値を表す。

【0044】

マスクビットは各オペランド毎に設けられ、データの有効/無効を示す。ここではマスクビット=1の時にデータ有効、マスクビット=0の時にデータ無効、とする。尚、本実施例によるベクトル積和演算回路は、A[i]あるいはB[i]を“1”にすることによって2オペランドの加減算器として、またC[i]を“0”にすることによって2オペランドの乗算器として動作する。

【0045】

まず、積和演算を実行する場合の動作について説明する。この場合、制御回路11〜13各々へ送出される演算モードは“積和演算”が指定される。“積和演算”を示す信号=1の際には、他の演算モード“乗算”、“加減算1”、“加減算2”を示す信号はそれぞれ0となり、各モードを示す信号は排他の関係にある。

【0046】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第1OPを選択する制御信号“10”をそれぞれ機能セレクタ1へ送出する。

【0047】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第2OPを選択する制御信号“10”を機能セレクタ2へ送出する。

【0048】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットにしたがってマスクビットが「0」ならば“0”を選択する制御信号“0”を、マスクビットが「1」ならば第3OPを選択する制御信号“1”を機能セレクタ3へ送出する。

【0049】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0050】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0051】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号にしたがって第3OPを選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。

【0052】

機能セレクタ1〜3各々は演算モードとマスクビットとによって、図8に示すようなデータを選択する。機能セレクタ1,2で選択された第1OP及び第2OPの指数部は指数部加算器6にて加算が行われ、得られた指数部加算結果を指数部減算器7と指数部補正回路15とに出力する。機能セレクタ3で選択された第3OPの指数部は指数部減算器7にて指数部加算器6の出力との差(第1OP及び第2OPの指数部の和から第3OPの指数を引いた値)を求め、その結果をシフト回路8へ送出し、シフト回路8では機能セレクタ3で選択された第3OPの仮数部に対してシフト動作を行う。

【0053】

指数部減算器7の結果の絶対値がシフト回路8で使用するシフトビット数となる。指数部減算器7の結果が負の場合には第3OPの指数の方が大きいので左シフトとなり、指数部減算器7の結果が正の場合には逆に小さいので右シフトとなる。シフトした結果が第1OP及び第2OPの仮数部乗算結果に対する桁合わせした結果となり、これを仮数部加算器5へ送出する。

【0054】

第1OP及び第2OPの仮数部は仮数部乗算回路4に入力され、仮数部乗算回路4にて乗算が行われた結果が仮数部加算器5へ送出される。仮数部加算器5は仮数部乗算回路4の出力である第1OP及び第2OPの仮数部乗算結果とシフト回路8の出力である第3OPの仮数部の桁合わせ結果とを加算し、その結果を正規化回路9と0カウンタ14とに送出する。

【0055】

0カウンタ14では加算結果のMSBからビット0の数をカウントして正規化のためのシフト数が求められる。このシフト数は正規化回路9へ送出され、正規化回路9にて仮数部の正規化が行われる。また、0カウンタ14の出力であるシフト数は指数部補正回路15にも送出され、指数部補正回路15にて指数部の正規化が行われ、積和演算結果の指数部が得られる。正規化回路9の出力に対しては丸め回路10にて丸め処理が行われ、積和演算結果の仮数部が得られる。

【0056】

次に、2オペランドの乗算を実行する場合の動作について説明する。この場合、制御回路11〜13へ送出される演算モードには“乗算”が指定される。“乗算”を示す信号=1の際には、他の演算モード“積和演算”、“加減算1”、“加減算2”を示す信号はそれぞれ0となる。

【0057】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第1OPを選択する制御信号“10”をそれぞれ機能セレクタ1へ送出する。

【0058】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」ならば第2OPを選択する制御信号“10”をそれぞれ機能セレクタ2へ送出する。

【0059】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットの値によらず“0”を選択する制御信号“0”を機能セレクタ3へ送出する。これは2オペランドの乗算では必要ない加算項の第3OPを“0”とするためである。

【0060】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0061】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPを選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0062】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号“0”にしたがって“0”を選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。以降、第3OPの値は“0”として扱われ、シフト回路8の出力も“0”となる。

【0063】

仮数部加算器5は仮数部乗算回路4の出力である第1OP及び第2OPの仮数部乗算結果と“0”との加算を行うため、仮数部加算器5の出力は第1OP及び第2OPの仮数部乗算結果に等しい。したがって、最終的な演算結果として得られるのは第1OP及び第2OPの乗算結果になる。

【0064】

次に、2オペランドの加減算を実行する場合の動作について説明する。制御回路11〜13各々へ送出される演算モードは“加減算”が指定される。この時、「第1OP+第3OP」の加減算の際には“加減算1”が、「第2OP+第3OP」の加減算の際には“加減算2”がそれぞれ指定される。“加減算1”を示す信号=1の際には他の演算モード“積和演算”、“乗算”、“加減算2”を示す信号はそれぞれ0となり、“加減算2”を示す信号=1の際には他の演算モード“積和演算”、“乗算”、“加減算1”を示す信号がそれぞれ0となる。

【0065】

制御回路11は、図2に示すように、マスクレジスタ31から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」でかつ演算モードが“加減算1”ならば第1OPを選択する制御信号“10”を、マスクビットが「1」でかつ演算モードが“加減算2”ならば“1”を選択する制御信号“01”をそれぞれ機能セレクタ1へ送出する。これは「第2OP+第3OP」の加減算の際に、第1OPの値を“1”にすることで、乗算項を、「“1”*第2OP(=第2OP)」とするためである。

【0066】

制御回路12は、図3に示すように、マスクレジスタ32から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“00”を、マスクビットが「1」でかつ演算モードが“加減算1”ならば“1”を選択する制御信号“01”を、マスクビットが「1」でかつ演算モードが“加減算2”ならば第2OPを選択する制御信号“10”をそれぞれ機能セレクタ2へ送出する。これは「第1OP+第3OP」の加減算の際に、第2OPの値を“1”にすることで、乗算項を、「第1OP*“1”(=第1OP)」とするためである。

【0067】

制御回路13は、図4に示すように、マスクレジスタ33から供給されるマスクビットにしたがって、マスクビットが「0」ならば“0”を選択する制御信号“0”を、マスクビットが「1」ならば第3OPを選択する制御信号“1”をそれぞれ機能セレクタ3へ送出する。

【0068】

機能セレクタ1は、図5に示すように、制御回路11の出力である制御信号にしたがって第1OPあるいは“1”を選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0069】

機能セレクタ2は、図6に示すように、制御回路12の出力である制御信号にしたがって第2OPあるいは“1”を選択し、選択結果の指数部を指数部加算器6へ、選択結果の仮数部を仮数部乗算回路4へそれぞれ出力する。

【0070】

機能セレクタ3は、図7に示すように、制御回路13の出力である制御信号にしたがって第3OPを選択し、選択結果の指数部を指数部減算器7へ、選択結果の仮数部をシフト回路8へそれぞれ出力する。

【0071】

仮数部乗算回路4は“1”*第2OPあるいは第1OP*“1”の乗算を行うので、仮数部乗算回路4の出力は第1OPあるいは第2OPの仮数部になる。仮数部加算器5にて桁合わせされた第3OPの仮数部と第1OPあるいは第2OPの仮数部との加算を行う。したがって、最終的な演算結果として得られるのは第1OP及び第3OPの加減算結果、あるいは第2OP及び第3OPの加減算結果になる。

【0072】

尚、演算モードに“加減算1”または“加減算2”を指定し、マスクレジスタ33を“0”で埋めることで、「第1OP*“1”+“0”」、あるいは「“1”*第2OP+“0”」の演算を実現することができる。また、マスクレジスタ31,32を“0”で埋めることで、「“0”+第3OP」の演算を実現することができる。

【0073】

このように、本実施例では、マスクビットと演算モードとの組合わせによって各オペランドデータのバイパス動作を可能にする。以上のように、各オペランドを格納するベクトルレジスタ21〜23それぞれにマスクビットを格納するマスクレジスタ31〜33を設け、各オペランド毎にマスクビットと演算モードとの組合わせから積和演算回路へ入力するデータを選択することによって、ベクトルレジスタ21〜23の各要素を書換えて2オペランドの乗算、あるいは加減算を行う積和演算回路よりも処理時間を短縮することができる。

【0074】

上述したように、本実施例では、ベクトルデータであるオペランド毎にデータの有効/無効を示すマスクビットを設け、マスクビットと演算モードとの組合わせによってデータを選択する機能セレクタ1〜3を設けることによって、ベクトルレジスタ21〜23の各要素を書換えることなく、マスクビットと演算モードとの切替えのみで様々な演算を行うことが可能となるため、積和演算回路で2オペランドの乗算、あるいは加減算を行う際の処理時間を短縮することができる。

【図面の簡単な説明】

【0075】

【図1】本発明の一実施例によるベクトル積和演算回路の構成を示すブロック図である。

【図2】図1に示す制御回路11の構成を示す回路図である。

【図3】図1に示す制御回路12の構成を示す回路図である。

【図4】図1に示す制御回路13の構成を示す回路図である。

【図5】図1に示す機能セレクタ1の構成を示す図である。

【図6】図1に示す機能セレクタ2の構成を示す図である。

【図7】図1に示す機能セレクタ3の構成を示す図である。

【図8】(a)は図1に示す機能セレクタ1の選択結果を示す図、(b)は図1に示す機能セレクタ2の選択結果を示す図、(c)は図1に示す機能セレクタ3の選択結果を示す図である。

【図9】従来例のベクトル積和演算回路の構成を示すブロック図である。

【符号の説明】

【0076】

1〜3 機能セレクタ

1a,1b,2a,

2b,3a,3b セレクタ

4 仮数部乗算回路

5 仮数部加算器

6 指数部加算器

7 指数部減算器

8 シフト回路

9 正規化回路

10 丸め回路

11〜12 制御回路

14 0カウンタ

15 指数部補正回路

21〜23 ベクトルレジスタ

31〜33 マスクレジスタ

111〜114,

116,117,

121〜124,

126,127,

131〜133,

135 論理積回路

115,125,

134 論理和回路

【特許請求の範囲】

【請求項1】

少なくとも第1のオペランドと第2のオペランドと第3のオペランドとを入力して、それらの積和を求める積和回路を含むベクトル積和演算回路であって、

外部から指定される演算モードに基いて前記オペランドと予め設定された所定値のデータとのいずれかを選択して前記積和回路に出力する機能セレクタを有することを特徴とするベクトル積和演算回路。

【請求項2】

前記オペランド毎にデータの有効/無効を示すマスクビットを格納するマスクレジスタを含み、

前記機能セレクタは、前記演算モードと前記オペランド各々に付随するマスクビットとに基いて前記オペランドと前記所定値のデータとのいずれかを選択して前記積和回路に出力することを特徴とする請求項1記載のベクトル積和演算回路。

【請求項3】

前記演算モードと前記マスクビットとに基いて前記オペランドと前記所定値のデータとのいずれかを選択させるための選択信号を生成して前記機能セレクタに出力する制御回路を含み、

前記機能セレクタは、前記選択信号にしたがって前記オペランドと前記所定値のデータとのいずれかを選択して前記積和回路に出力することを特徴とする請求項2記載のベクトル積和演算回路。

【請求項4】

前記マスクレジスタと、前記機能セレクタと、前記制御回路とをそれぞれ前記第1のオペランドと第2のオペランドと第3のオペランドとに対応して設けたことを特徴とする請求項3記載のベクトル積和演算回路。

【請求項5】

前記所定値は、2値信号の所定値及びその反転値であることを特徴とする請求項1から請求項4のいずれか記載のベクトル積和演算回路。

【請求項6】

前記積和回路は、前記第1のオペランドと前記第2のオペランドと前記第3のオペランドとをそれぞれ格納する第1〜第3のベクトルレジスタと、前記第1のオペランド及び前記第2のオペランド各々に対応する前記機能セレクタの指数部出力の加算を行う指数部加算回路と、前記第3のオペランドに対応する前記機能セレクタの指数部出力と前記指数部加算回路の出力との減算を行う指数部減算回路と、前記第3のオペランドに対応する前記機能セレクタの仮数部出力な対して前記指数部減算回路の出力であるシフト量にしたがったシフト動作を行うシフト回路と、前記第1のオペランド及び前記第2のオペランド各々に対応する前記機能セレクタの仮数部出力の乗算を行う仮数部乗算回路と、前記仮数部乗算回路の出力と前記シフト回路の出力との加算を行う仮数部加算回路と、前記仮数部加算回路の出力を入力としてMSB(Most Significant Bit)からのビット0の数をカウントする0カウンタと、前記0カウンタの出力にしたがって前記仮数部加算回路の出力をシフトして正規化を行う正規化回路と、前記正規化回路の出力を入力として丸め処理を行う丸め回路と、前記0カウンタの出力にしたがって前記指数部加算回路の出力を補正する指数部補正回路とからなる浮動小数点積和演算器であることを特徴とする請求項3から請求項5のいずれか記載のベクトル積和演算回路。

【請求項1】

少なくとも第1のオペランドと第2のオペランドと第3のオペランドとを入力して、それらの積和を求める積和回路を含むベクトル積和演算回路であって、

外部から指定される演算モードに基いて前記オペランドと予め設定された所定値のデータとのいずれかを選択して前記積和回路に出力する機能セレクタを有することを特徴とするベクトル積和演算回路。

【請求項2】

前記オペランド毎にデータの有効/無効を示すマスクビットを格納するマスクレジスタを含み、

前記機能セレクタは、前記演算モードと前記オペランド各々に付随するマスクビットとに基いて前記オペランドと前記所定値のデータとのいずれかを選択して前記積和回路に出力することを特徴とする請求項1記載のベクトル積和演算回路。

【請求項3】

前記演算モードと前記マスクビットとに基いて前記オペランドと前記所定値のデータとのいずれかを選択させるための選択信号を生成して前記機能セレクタに出力する制御回路を含み、

前記機能セレクタは、前記選択信号にしたがって前記オペランドと前記所定値のデータとのいずれかを選択して前記積和回路に出力することを特徴とする請求項2記載のベクトル積和演算回路。

【請求項4】

前記マスクレジスタと、前記機能セレクタと、前記制御回路とをそれぞれ前記第1のオペランドと第2のオペランドと第3のオペランドとに対応して設けたことを特徴とする請求項3記載のベクトル積和演算回路。

【請求項5】

前記所定値は、2値信号の所定値及びその反転値であることを特徴とする請求項1から請求項4のいずれか記載のベクトル積和演算回路。

【請求項6】

前記積和回路は、前記第1のオペランドと前記第2のオペランドと前記第3のオペランドとをそれぞれ格納する第1〜第3のベクトルレジスタと、前記第1のオペランド及び前記第2のオペランド各々に対応する前記機能セレクタの指数部出力の加算を行う指数部加算回路と、前記第3のオペランドに対応する前記機能セレクタの指数部出力と前記指数部加算回路の出力との減算を行う指数部減算回路と、前記第3のオペランドに対応する前記機能セレクタの仮数部出力な対して前記指数部減算回路の出力であるシフト量にしたがったシフト動作を行うシフト回路と、前記第1のオペランド及び前記第2のオペランド各々に対応する前記機能セレクタの仮数部出力の乗算を行う仮数部乗算回路と、前記仮数部乗算回路の出力と前記シフト回路の出力との加算を行う仮数部加算回路と、前記仮数部加算回路の出力を入力としてMSB(Most Significant Bit)からのビット0の数をカウントする0カウンタと、前記0カウンタの出力にしたがって前記仮数部加算回路の出力をシフトして正規化を行う正規化回路と、前記正規化回路の出力を入力として丸め処理を行う丸め回路と、前記0カウンタの出力にしたがって前記指数部加算回路の出力を補正する指数部補正回路とからなる浮動小数点積和演算器であることを特徴とする請求項3から請求項5のいずれか記載のベクトル積和演算回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2006−338215(P2006−338215A)

【公開日】平成18年12月14日(2006.12.14)

【国際特許分類】

【出願番号】特願2005−160796(P2005−160796)

【出願日】平成17年6月1日(2005.6.1)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

【公開日】平成18年12月14日(2006.12.14)

【国際特許分類】

【出願日】平成17年6月1日(2005.6.1)

【出願人】(000168285)エヌイーシーコンピュータテクノ株式会社 (572)

【Fターム(参考)】

[ Back to top ]